AS7C31026A-10JC中文资料

PALCE22V10-10JC中文资料

• High reliability — Proven Flash EPROM technology — 100% programming and functional testing

I

I

I

I

I

CP/I

6

5

4

3

2

1

PROGRAMMABLE AND ARRAY (132 X 44)

8

10

12

14

16

16

The PALCE22V10, featuring programmable macrocells and variable product terms, provides a device with the flexibility to

implement logic functions in the 500- to 800-gate-array complexity. Since each of the ten output pins may be individually configured as inputs on a temporary or permanent basis, functions requiring up to 21 inputs and only a single output and down to twelve inputs and ten outputs are possible. The ten potential outputs are enabled using product terms. Any output pin may be permanently selected as an output or arbitrarily enabled as an output and an input through the selective use of individual product terms associated with each output. Each of these outputs is achieved through an individual programmable macrocell. These macrocells are programmable to provide a combinatorial or registered inverting or non-inverting output. In a registered mode of operation, the output of the register is fed back into the array, providing current status information to the array. This information is available for establishing the next result in applications such as control state machines. In a combinatorial configuration, the combinatorial output or, if the output is disabled, the signal present on the I/O pin is made available to the array. The flexibility provided by both programmable product term control of the outputs and variable product terms allows a significant gain in functional density through the use of programmable logic.

可控硅参数说明及中英文对照表完整版

为晶闸管在阻断状态下承受断态重复峰值电压VDRM和反向重复峰值电压VRRM时流过元件的正反向峰值漏电流该参数在器件允许工作的最高结温Tjm下测出。

mA

IRRM

Maximum reverse leakage current

反向重复峰值漏电流

mA

IDSM

断态不重复平均电流

门极断路时,在额定结温下对应于断态不重复峰值电压下的平均漏电流。

mA

ID

Off-state leakage current

断态漏电流

-

mA

VGT

Triggering gate voltage

门极触发电压

—可以选择Vgt 25度时max值的β倍。β为门极触发电压—结温特性系数,查数据手册可得,取特性曲线中最低工作温度时的系数。若对器件工作环境温度无特殊需要,通常选择时β取1~1.2倍即可。

A/μs

VDRM

Repetitive peak off-state voltage

断态重复峰值电压

断态重复峰值电压是在门极断路而结温为额定值时,允许重复加在器件上的正向峰值电压.国标规定重复频率为50H,每次持续时间不超高10ms。规定断态重复峰值电压DRM为断态不重复峰值电压(即断态最大瞬时电压)UDSM的90%.断态不重复峰值电压应低于正向转折电压bo,所留裕量大小由生产厂家自行规定。UU

℃

Tstg

Storage Temperature Range

贮存温度

-

℃

TL

Max.Lead Temperature for Soldering Purposes

引脚承受焊锡极限温度

-

℃

Rth(j-mb)

朗耐斯(LG)空调产品说明书

BANCHI GN/PA/PZ/SNACK2100/3100/4100 BT/TN/TNGPos.Codice Caratteristiche Ref.Code Features1RC0724Pannello Panel2SL0621InterruttoreSwitch 3SL0050*Centralina REK 33Controls unit REK 333RC0883☻dal numero seriale 212274Centralina Dixell xr60ccontrols unit Dixell xr 60c 4RC0128SerraturaLock 5RC0230ComandiSportello Door 5RC1019Solo x PA1500-2000TNGR7Sportello Door 6RC0175Perno Pivot 7RC0176Boccola Bush 8RC0175Perno Pivot 9RC0266CondensatoreFiltro Filter 10RC0768Disidratatore GR30Filtro Filter 11Capillare Capillary 12RC0286Condensatore Condenser 13Supporto Support14RC0237Condensatore VentolaFan 15RC0242CoperturaCovering 16RC0664Vaschetta Bowl 17RC0666Serpentina Serpentine 18RC0064Staffa dxStirrup right 19RC1068GN/SNACK 2100-3100 TN 1/4HP-R134a Compressore Compressor 19RC0678GN/SNACK 4100 TN 1/4HP-R134a Compressore Compressor 19RC0231GN2100-3100-4100 BT 1HP-R404a Compressore BT Compressor BT 19RC0047PA 2100 1/4HP-R134a Compressore Compressor 19RC0678PA 3100 1/4HP-R134a Compressore Compressor 21Tubo d'aspirazioneSuction pipe 22RC0665Cerniera Hinge 23RC0725Aggancio Coupling 24RC0235Scatola Box 25RC0049Piede Feet 25RC0853Tipo nuovo DAL 01-06-2012PiedeFoot 26Carcassa Housing27RC0140GN2100 TN/BT 1360X700X850Top coverTop cover 27RC0390GN3100 TN/BT 1795X700X850Top coverTop cover 27RC0391GN4100 TN/BT 2230X700X850Top coverTop cover 27RC0380PA3100 TN/BT 2020X800X850Top coverTop cover 27RC0381PA2100 TN/BT 1510X800X850 Top coverTop cover 27RC0452Snack 2100TN 1360X600X850Top coverTop cover 27RC0453Snack 3100TN 1795X600X850Top coverTop cover 27RC0454Snack 4100TN 2230X600X850Top coverTop cover 27RC0643PZ 2600Granito Granite 27RC0695PZ 3600Granito Granite 27RC1020PA1500TNGR7Granito Granite 27RC1021PA2000TNGR7Granito Granite 28RC0726CoperchioCover 29SL0130SpinaPin 30RC0663Snack 2100-3100-4100 TN VaschettaBowl 30RC0397GN2100-3100-4100 BT/TN Vaschetta Bowl 31RC0285GN/PA2100-3100 GN4100TN PZ2600-2610-3600 Evaporatore TN Evaporator NT 31RC0282GN 2100-3100-4100 BTEvaporatore BT Evaporator BT 31RC0173Snack 2100-3100-4100 TNEvaporatore Evaporator 32SupportoSupport 33RC0654Dal 2010Ventola Fan 33RC0037Fino al 2009Ventola Fan 34CoperturaCovering 35Copertura Covering 36RC0727Aggancio Coupling 37RC0728Supporto Support 38Supporto Support 39Supporto Support 40GUT Kit PA 2100- 3100Guida Guide 40GAR Kit PA 2100- 3100Coppia guida Guide left/right 40CG11Kit GN 2100-3100-4100 TN/BTCoppia guidaGuide left/right40CGG Kit Snack 2100-3100-4100 TN Coppia guidaGuide left/right 40GUT Kit PZ 2600-2610-3600Coppia guida Guide left/right (*): fuori produzione / out of production ☻: ricambio consigliato / spare part suggested Descrizione DescriptionBANCHI GN/PA/PZ/SNACK2100/3100/4100 BT/TN/TNGBANCHI GN/PA/PZ/SNACK 2100-3100-4100 TN-TNG-BTPos.Codice CaratteristicheRef.Code Features40GUT70PA1500TNGR7-PA2000TNGR7Coppia guida Guide left/right41GRP11330X530 GN1/1GrigliaGrill 41GRP64PA 2100-3100 TN 400X600GrigliaGrill 41GRPG Snack 2100-3100-4100 GrigliaGrill 42RC0041☻GN2100-3100-4100 TN/BTGuarnizione Gasket 42RC0162☻PA2100 3100 TN PZ2600 2610 3600TN GuarnizioneGasket 43RC0667Banchi BTPorta sx Door left 43RC0051Banchi TNPorta sx Door left 43RC0053Banchi TNGPorta sx Door left 43RC0369P A2100 3100 TN PZ2600 2610 3600TN Porta sx Door left 43RC1022PA1500TNGR7-PA2000TNGR7Porta sx Door left 44RC0089☻Molla Spring 45CoperturaCovering 46RC0220☻Resistenza TermicoThermic 47RC0137☻GN/PA2100-3100 GN4100TN PZ2600-2610-3600 ResistenzaResistance 47RC0303☻Snack 2100-3100-4100 TN ResistenzaResistance 48RC0109SpiaIndication 49RC0229Motore Motor 50RC0063Staffa sxStirrup left 51RC0668GN 2100-3100- 4100 BTPorta dx Door right 51RC0106GN 2100-3100-4100 TNPorta dx Door right 51RC0554GN 2100-3100-4100 TNGPorta dx Door right 51RC0065PA2100 3100 TN495X630 PZ2600 2610 3600TN Porta dx Door right 51RC1023PA1500TNGR7-PA2000TNGR7Porta dx Door right 52SL0052☻Fino al 2009Sonda PTC Probe PTC 52RC0321☻Dal 2010Sonda NTC Probe NTC (*): fuori produzione / out of production ☻: ricambio consigliato / spare part suggestedDescription BANCHI GN/PA/PZ/SNACK 2100-3100-4100 TN-TNG-BTDescrizione。

AS7C31026A-12中文资料

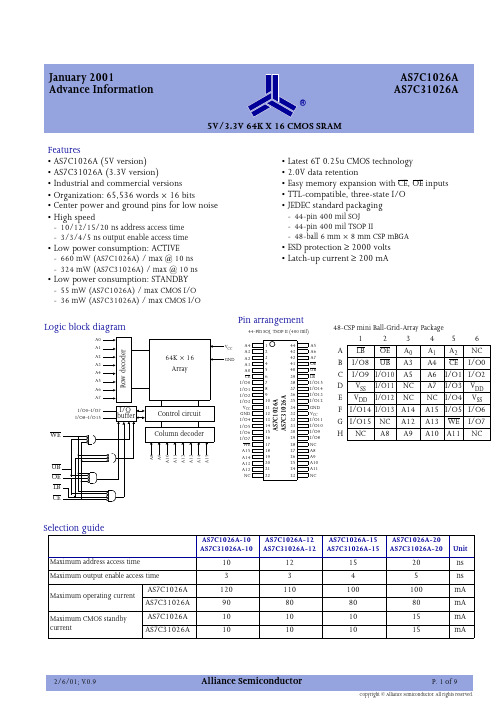

January 2001Advance Information®AS7C1026A AS7C31026A5V/3.3V 64K X 16 CMOS SRAMFeatures•AS7C1026A (5V version)•AS7C31026A (3.3V version)•Industrial and commercial versions •Organization: 65,536 words × 16 bits•Center power and ground pins for low noise •High speed-10/12/15/20 ns address access time -3/3/4/5 ns output enable access time•Low power consumption: ACTIVE-660 mW (AS7C1026A) / max @ 10 ns -324 mW (AS7C31026A) / max @ 10 ns•Low power consumption: STANDBY-55 mW (AS7C1026A) / max CMOS I/O -36 mW (AS7C31026A) / max CMOS I/O•Latest 6T 0.25u CMOS technology •2.0V data retention•Easy memory expansion with CE, OE inputs •TTL-compatible, three-state I/O •JEDEC standard packaging-44-pin 400 mil SOJ -44-pin 400 mil TSOP II-48-ball 6 mm × 8 mm CSP mBGA•ESD protection ≥ 2000 volts •Latch-up current ≥ 200 mALogic block diagramCCPin arrangement567891011121314151617181920I/O13I/O12GND V CC I/O11I/O10I/O9I/O8NC A8A9A10A11NCA0CE I/O0I/O1I/O2I/O3V CC GND I/O4I/O5I/O6I/O7WE A15A14A1344-Pin SOJ, TSOP II (400 mil)2122A12NCUB LB I/O15I/O142A33A24A11A440393837363534333231302928272625242343424144A6A7OE A5A S 7C 1026A A S 7C 31026ASelection guideAS7C1026A-10 AS7C31026A-10AS7C1026A-12AS7C31026A-12AS7C1026A-15AS7C31026A-15AS7C1026A-20AS7C31026A-20UnitMaximum address access time 10121520ns Maximum output enable access time 3345ns Maximum operating current AS7C1026A 120110100100mA AS7C31026A 90808080mA Maximum CMOS standby currentAS7C1026A 10101015mA AS7C31026A10101015mA48-CSP mini Ball-Grid-Array Package123456A LB OE A 0A 1A 2NC B I/O8UB A3A4CE I/O0C I/O9I/O10A5A6I/O1I/O2D V SS I/O11NC A7I/O3V DD E V DD I/O12NC NC I/O4V SS F I/O14I/O13A14A15I/O5I/O6G I/O15NC A12A13WE I/O7HNC A8A9A10A11NC®AS7C1026A AS7C31026AFunctional descriptionThe AS7C1026A and AS7C31026A are high-performance CMOS 1,048,576-bit Static Random Access Memory (SRAM) devices organized as 65,536 words × 16 bits. They are designed for memory applications where fast data access, low power, and simple interfacing are desired.Equal address access and cycle times (t AA , t RC , t WC ) of 10/12/15/20 ns with output enable access times (t OE ) of 3/3/4/5 ns are ideal for high-performance applications.When CE is high the devices enter standby mode. The AS7C1026A is guaranteed not to exceed 55 mW power consumption in CMOS standby mode. The devices also offer 2.0V data retention.A write cycle is accomplished by asserting write enable (WE) and chip enable (CE). Data on the input pins I/O0–I/O15 is written on the rising edge of WE (write cycle 1) or CE (write cycle 2). To avoid bus contention, external devices should drive I/O pins only after outputs have been disabled with output enable (OE) or write enable (WE).A read cycle is accomplished by asserting output enable (OE) and chip enable (CE), with write enable (WE) high. the chips drive I/O pins with the data word referenced by the input address. When either chip enable or output enable is inactive, or write enable is active, output drivers stay in high-impedance mode.The devices provide multiple center power and ground pins, and separate byte enable controls, allowing individual bytes to be written and read. LB controls the lower bits, I/O0–I/O7, and UB controls the higher bits, I/O8–I/O15.All chip inputs and outputs are TTL-compatible, and operation is from a single 5V supply (AS7C1026A) or 3.3V supply (AS7C31026A). the device is packaged in common industry standard packages. Chip scale BGA packaging, easy to use in manufacturing, provides the smallest possible footprint. This 48-ball JEDEC-registered package has a ball pitch of 0.75 mm and external dimensions of 8 mm × 6 mm.Absolute maximum ratingsNote: Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability .Truth tableKey: H = High, L = Low, X = don’t care.ParameterSymbol Min Max Unit Voltage on V CC relative to GND AS7C1026A V t1–0.50+7.0V AS7C31026AV t1–0.50+5.0V Voltage on any pin relative to GND Both V t2–0.50V CC +0.50V Power dissipationBoth P D – 1.0W Storage temperature (plastic)Both T stg –65+150°C Ambient temperature with VCC appliedBoth T bias –55+125°C DC current into outputs (low)BothI OUT–20mACE WE OE LB UB I/O0–I/O7I/O8–I/O15Mode H X X X X High Z High Z Standby (I SB ), I SBI )L H L L H D OUT High Z Read I/O0–I/O7 (I CC )L H L H L HighZ D OUT Read I/O8–I/O15 (I CC)L H L L L D OUT D OUT Read I/O0–I/O15 (I CC )L L X L L D IN D IN Write I/O0–I/O15 (I CC )L L X L H D IN High Z Write I/O0–I/O7 (I CC )L L X H L HighZ D IN Write I/O8–I/O15 (I CC )L LH XH XX HX HHigh ZHigh ZOutput disable (I CC )®AS7C1026A AS7C31026ARecommended operating conditions† VIL min. = –3.0V for pulse width less than t RC /2.DC operating characteristics (over the operating range)1Capacitance (f = 1MHz, T a = 25 °C, V CC = NOMINAL)2ParameterDevice Symbol Min Nominal Max Unit Supply voltage AS7C1026A V CC 4.5 5.0 5.5V AS7C31026A V CC 3.0 3.3 3.6V Input voltageAS7C1026A V IH 2.2–V CC + 0.5V AS7C31026AV IH 2.0–V CC + 0.5V Both V IL †–0.5–0.8V Ambient operating temperaturecommercial T A 0–70o C industrialT A–40–85o CParameterSymTest conditionsDevice-10-12-15-20UnitMin Max Min Max Min MaxMin Max Input leakage current | I LI |V CC = Max V IN = GND to V CC Both –1–1–1–1µA Output leakage current | I LO |V CC = Max CE = V IH ,V OUT = GND to V CC Both –1–1–1–1µA Operating power supply currentI CCV CC = Max, CE ≤ V ILoutputs open, f = f Max = 1/t RC AS7C1026A –120–110–100–100mA AS7C31026A –90–80–80–80mAStandbypower supply currentI SBV CC = Max, CE ≤ V IL , outputs open,f = f Max = 1/t RC AS7C1026A –30–25–20–20mA AS7C31026A –30–25–20–20I SB1V CC = Max, CE ≥ V CC –0.2V ,V IN ≤ GND + 0.2V or V IN ≥ V CC –0.2V , f = 0AS7C1026A –10–10–10–15mA AS7C31026A –10–10–10–15Output voltage V OL I OL = 8 mA, V CC = Min AS7C1026A –0.4–0.4–0.4–0.4V V OHI OH = –4 mA, V CC = MinAS7C31026A 2.4–2.4–2.4–2.4–V Data retention currentI CCDRV CC = 2.0V CE ≥ V CC –0.2V V IN ≥ V CC –0.2V orV IN ≤ 0.2VAS7C1026A 1115mA AS7C31026A1115mAParameterSymbol SignalsTest conditions Max Unit Input capacitance C IN A, CE, WE, OE, LB, UBV IN = 0V 5pF I/O capacitanceC I/OI/OV IN = V OUT = 0V7pF®AS7C1026A AS7C31026ARead cycle (over the operating range)3,9Key to switching waveforms3,6,7,9Read waveform 2 (OE, CE, UB, LB controlled)3,6,8,9ParameterSymbol -10-12-15-20Unit NotesMin Max MinMax MinMax MinMax Read cycle time t RC 10–12–15–20–ns Address access time t AA –10–12–15–20ns 3Chip enable (CE) access time t ACE –10–12–15–20ns 3Output enable (OE) access time t OE –3–3–4–5ns Output hold from address change t OH 2–3–3–3–ns 5CE Low to output in low Z t CLZ 0–0–0–0–ns 4, 5CE High to output in high Z t CHZ –3–3–4–5ns 4, 5OE Low to output in low Z t OLZ 0–0–0–0–ns 4, 5Byte select access time t BA –3–3–4–5ns Byte select Low to low Z t BLZ 0–0–0–0–ns 4, 5Byte select High to high Z t BHZ –5–6–6–8ns 4, 5OE High to output in high Z t OHZ –3–3–4–5ns 4, 5Power up time t PU 0–0–0–0–ns 4, 5Power down timet PD–10–12–15–20ns4, 5Undefined output/don’t careFalling inputRising inputData Address AddressOECELB, UBData IN®AS7C1026A AS7C31026AWrite cycle (over the operating range) 11ParameterSymbol -10-12-15-20Unit NotesMin Max Min Max Min Max Min MaxWrite cycle timet WC 10–12–15–20–ns Chip enable (CE ) to write end t CW 8–10–12–12–ns Address setup to write end t AW 8–9–10–12–ns Address setup time t AS 0–0–0–0–ns Write pulse widtht WP 7–8–9–12–ns Address hold from end of write t AH 0–0–0–0–ns Data valid to write end t DW 5–6–8–10–ns Data hold timet DH 0–0–0–0–ns 5Write enable to output in high Z t WZ –6–6–6–8ns 4, 5Output active from write end t OW 1–1–1–2–ns 4, 5Byte select low to end of writet BW8–10–12–12–nsAS7C1026A AS7C31026A®Data retention characteristics (over the operating range)Data retention waveformAC test conditionsNotes1DuringV CC power-up, a pull-up resistor to V CC on CE is required to meet I SB specification.2This parameter is sampled, but not 100% tested.3For test conditions, see AC T est Conditions , Figures A, B, and C.4These parameters are specified with C L = 5pF, as in Figures B or C. Transition is measured ± 500 mV from steady-state voltage.5This parameter is guaranteed, but not tested.6WE is High for read cycle.7CE and OE are Low for read cycle.8Address valid prior to or coincident with CE transition Low.9All read cycle timings are referenced from the last valid address to the first transitioning address.10CE or WE must be High during address transitions. Either CE or WE asserting high terminates a write cycle.11All write cycle timings are referenced from the last valid address to the first transitioning address.12Not applicable.13C=30pF, except all high Z and low Z parameters where C=5pF.Parameter Symbol Test conditions Min Max Unit V CC for data retention V DR V CC = 2.0V CE ≥ V CC –0.2V V IN ≥ V CC –0.2V orV IN≤ 0.2V2.0–V Data retention currentI CCDR –1 ma Chip deselect to data retention time t CDR 0–ns Operation recovery time t R t RC –ns Input leakage current|I LI |–1µAV CCCEFigure C: 3.3V Output loadThevenin Equivalent:D OUT +1.728V (5V and 3.3V)Figure B: 5V Output load GND+3.0V Figure A: Input pulseD OUTD OUT–Output load: see Figure B or Figure C.–Input pulse level: GND to 3.0V . See Figure A.–Input rise and fall times: 2 ns. See Figure A.–Input and output timing reference levels: 1.5V .®AS7C1026A AS7C31026APackage dimensions44-pin TSOP II Min (mm)Max (mm)A 1.2A10.05A20.951.05b 0.300.45c 0.127 (typical)D18.2818.54E 10.0310.29He 11.5611.96e 0.80 (typical)l0.400.600–5Seating Plane44-pin SOJ44-pin SOJ 400 milMin (in)Max (in)A 0.1280.148A 10.025–A 20.105 1.115B 0.0260.032b 0.0150.020c 0.0070.013D 1.120 1.130E 0.370 NOM E 10.3950.405E 20.4350.445e0.050 NOMePin 1A 1bBAA 2E 2E 1E 2DcAS7C1026A AS7C31026A®Notes1Bump counts: 48 (8 row x 6 column).2Pitch: (x,y) = 0.75 mm x 0.75 mm (typ).3Units: millimeters.4All tolerance are +/- 0.050 unless otherwisespecified.5Typ: typical.6Y is coplanarity: 0.08 (max).MinimumT ypical MaximumA –0.75–B 5.908.008.10B1– 3.75–C 7.908.008.10C1– 5.25–D –0.35–E –– 1.20E1–0.68–E20.220.250.27Y––0.0848-ball FBGABottom View654321Ball A1C1A B C D F G H JA B1Side ViewTop View Ball #A1 indexCSRAM DIEElastomerBDetail ViewAYDie0.3/T µp E2EDieDE1E2E*pin 1 indicator will show asengraved circle and/or Inc. trade mark*®AS7C1026A AS7C31026A© Copyright Alliance Semiconductor Corporation. All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to this document and its products at any time without notice. Alliance assumes no responsibility for any errors that may appear in this document. The data contained herein represents Alliance’s best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in Alliance’s Terms and Conditions of Sale (which are available from Alliance). All sales of Alliance products are made exclusively according to Alliance’s Terms andConditions of Sale. The purchase of products from Alliance does not convey a license under any patent rights, copyrights, mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result 2/6/01; V .0.9Alliance SemiconductorP. 9 of 9Ordering codesPart numbering systemPackage \ Access time V olt/Temp 10 ns12 ns15 ns20 nsPlastic SOJ, 400 mil5V commercial AS7C1026A-10JC AS7C1026A-12JC AS7C1026A-15JC AS7C1026A-20JC 5V industrial AS7C1026A-10JI AS7C1026A-12JI AS7C1026A-15JI AS7C1026A-20JI 3.3V commercial AS7C31026A-10JCAS7C31026A-12JC AS7C31026A-15JC AS7C31026A-20JC TSOP II, 18.4×10.2 mm5V commercial AS7C1026A-10TC AS7C1026A-12TC AS7C1026A-15TC AS7C1026A-20TC 3.3V commercial AS7C31026A-10TCAS7C31026A-12TC AS7C31026A-15TC AS7C31026A-20TC 3.3V industrial AS7C31026A-10TI AS7C31026A-12TI AS7C31026A-15TI AS7C31026A-20TI CSP BGA, 8×6 mm5V commercialAS7C1026A-10BC AS7C1026A-12BC AS7C1026A-15BC AS7C1026A-20BC 3.3V commercial AS7C31026A-10BCAS7C31026A-12BC AS7C31026A-15BC AS7C31026A-20BC 3.3V industrialAS7C31026A-10BIAS7C31026A-12BIAS7C31026A-15BIAS7C31026A-20BIAS7C X1026–XXXCSRAM prefixBlank=5V CMOS 3=3.3V CMOSDevice number Access timePackage: J=SOJ 400 mil T=TSOP type 2, 18.4 × 10.2 mmB=CSP BGA, 8 × 6 mmT emperature range,C= Commercial: 0° C to 70° C I= Industrial: -40° C to 85° C。

美国山特(STPOWER)UPS用户手册

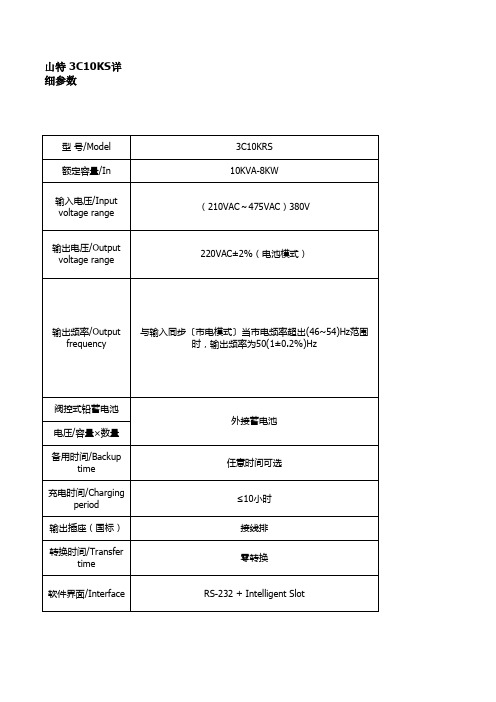

不间断电源系统-upsC6K(S)/C10K(S)/3C10KS/3C15KS/3C20KS 使用手册目录1.简介1.1系统及型号说明1.2常用符号说明1.3外观1.4产品规格与性能⏹一般规格⏹电气性能⏹工作环境2、安装说明2.1拆箱检验2.2输入、输出电源线及保护接地安装2.3长效性外接电池操作程序2.4并机操作3.操作与运行3.1操作3.2运行模式4.电池维护与保养5.处置电池注意事项6.故障排除附录一板指示灯说明附录二板等号显示与工作状态对应表附录三修保保证1.1系统及型号说明本系列UPS 是一种先进的在线式正弦波不间断供电系统,带有旁路维修开关,具有并联冗余的功能,可以为您的精密设备提供可靠、优质的交流电源,其适用范围很广,从电脑设备、通信系统到工业自动控制设备都可以使用。

由于它的在线式设计,不同于后备式UPS ,它对输入电压不断调整、滤波,在市电中断时,会无时间中断地从备用电池上提供后备电源。

在过载或逆变失败情况下,UPS 会转换到旁路状态,由市电供电。

若过载情况消除,UPS 会自动转回到逆变器供电状态。

本手册适用以下型号于CASTLE系列产品:(1)C6K/ C10K:内置电池的标准机型。

以下简称6K/ 10K(2)C6KS/ C10KS:可外接电池的长效机型。

以下简称6KS/ 10KS(3)3C10KS:三相输入单相输出可外接电池的长效机型。

以下简称三相10KS (4)3C15KS:三相输入单相输出,可外接电池的长效机型。

以下简称三相15KS (5)3C20KS:三相输入单相输出,可外接电池的长效机型。

以下简称三相20KS 以上任意一种机型,又分标准版和专业版两种供用户选择,专业版相对标准版增加了EPO开关、手动旁路维护开关。

1.2常用符号说明符号及其含义符号含义符号含义提示注意保护接地高压危险报警消除│打开主机过载指示O 关闭主机电池较热待机或关闭主机循环交流勿与杂物一同放置直流1.3 前后面板示意图前面板1.4产品规格与性能2.1拆包检验(1)打开包装,包装内应有:UPS一台UPS使用手册一本若是6KS,还带有一条UPS至电池柜的电池连接线(2)检查UPS是否在运输过程中损坏,如发现损坏或部件缺少,请勿开机,立即通知承运商和经销商。

正泰电器 GYC7 系列切换电容交流接触器产品目录说明书

本目录仅为提 供有关信息,内容会因技术、标准和工艺的变更而有所变动,且不会因此而预先通知,实时信息请与本公司或本公司授权的代理商联络。

相关部门R创 新 改 变 世 界Innovation changes the worldThe catalogue is for your reference only, Zhaozheng reserves the right to change the content without notice due to the change of technology, standard and technique. For updated information, please contact us or our authorized 产品目录Catalogue资质证书Certifications附录AppendixGYC7 Capacity changeover contactors配件、附件Parts/accessories尺寸、技术寿命特性Dimension\durability\characteristics1/24/3032/4244/4748/5758/6364/6869/9596/113114/127总目录Contents选型指南Selection guideGYC1系列交流接触器GYC1 ContactorsGYC2系列交流接触器GYC2 ContactorsGYC3系列永磁锁扣交流接触器GYC3 Permanent magnetic latching contactorsGYC5系列交流接触器GYC5 ContactorsGYC6系列交流接触器GYC6 ContactorsGYC7系列切换电容交流接触器GYC1GYC2115-800200-1600*GYC2115、150、170GYC3115-630型号GYC51000-3200——GYC6750-1800800-2750GYC7——型号ContactorGYC1系列交流接触器GYC1 Contactors选型指南Selection guide特性Characteristics结构Scheme联锁接触器Interlocked contactors 目录Contents5/67/101112/3适用于交流50\60Hz,电压至1000V,电流至1600A电路中控制各种类型的电动机,控制电阻、电感和电容性电路:加热、照明、功率补偿、变压器控制配电电路、工业配电,绿色电源配电对于动作频繁,使用条件恶劣,建议使用快速动作线圈应用Applications注:1)详见附录MNote: 1) details refer to appendix MGYC1系列接触器选型指南Selection guideIn circuit of AC 50\60Hz, voltage up to 1000V, current up to 600A, controlling motors of different types.Control resistance,inductive,capacitive loads:heating,lighting,power compensation and transformerControl distribution circuit, industrial distribution, green energy distributionFor harsh environment and frequent operations, quick operating coils are recommend 115至800AGYC1 Contactors From 115 to 800A.GYC1系列接触器选型指南Selection guide115至800AGYC1 Contactors From 115 to 800AGYC1系列接触器115至800A控制电路:交流或直流供电 AC/DCGYC1 Contactors From 115 to 800A Array(1) Sinusoidal without interference.GYC1系列接触器115至800A控制电路:交流或直流供电 AC/DC9特 性Characteristic 2)接触器GYC1 115到630可单独提供连接端子防护罩。

焊点控制器JC-3A说明书

JC—3A型电阻焊机焊点监控器使用说明书广西竞成工贸有限公司计数控制器使用说明JC-3A计数监控器,是为了用户加强电阻焊焊接工艺管理,保证所焊接工件符合工艺要求,而专门设计的一款电阻焊机控制器。

技术参数电源电压:AC170-240V工作电压范围:85%-110%计数信号输入:1,触点信号:继电器,行程开关等2,无触点信号:接近开关,光电开关等计数范围:1,夹内或夹外焊点计数器0--992,夹外时间计时器0.1S—99.9S3,工件计数器0--99999信号输入阻抗:≧4.7ΚΩ输入信号电压:≦24VDC功耗:≦12VA安装方式:吊挂式或平面安装式温度范围:-10~50℃湿度范围:相对湿度85%RH最大一、主要功能1、对应所焊接工件的工艺设定的应焊接点数和实际所焊接的焊点数,进行适时监控显示并提示。

2、对应所焊接工件的应焊接数和实际所焊接工件数,进行适时监控显示并提示。

3、对所焊接工件的零部件缺件,进行适时监控显示并提示。

4、本计数控制器在正常监控状态下,设定工艺参数后即可自动化地运行。

5、本计数控制器也可以对因各种内外部因素所引起的差错,对其实施人工补救的措施。

如非自动化的补焊、补件等。

6、所有因各种内外部因素所引起的差错,在实施人工补救措施后,采取人工复位后恢复至自动化状态。

7、方便选择工装调试。

二、安装方法:1、将本计数控制器安装于合适的位置和高度(2米以上),并且固定好。

2、将本计数控制器七芯电缆连接线接入外部开关信号及输出电磁气阀。

3、安装时,电源电压是否符合要求。

将本计数控制器三芯电缆连接线接入空气开关后AC220V电源。

4、将本计数控制器五芯电缆连接线接入焊接控制器的焊接结束信号(A8/B7)。

5、安装气阀时,请注意气体流动方向及接管是否正确。

三、工艺设定(先预置好所需的功能和数值后使用)1、将本计数控制器的电源开关合上,在正常显示状态下,可以设定在夹具上焊点数(夹内设点),工件离开夹具焊点数(即夹外设点),夹具外工件焊点结束判断时间(夹外定时)(时间单位分辨率为0.1S)。

LM1086CT-3.3中文资料

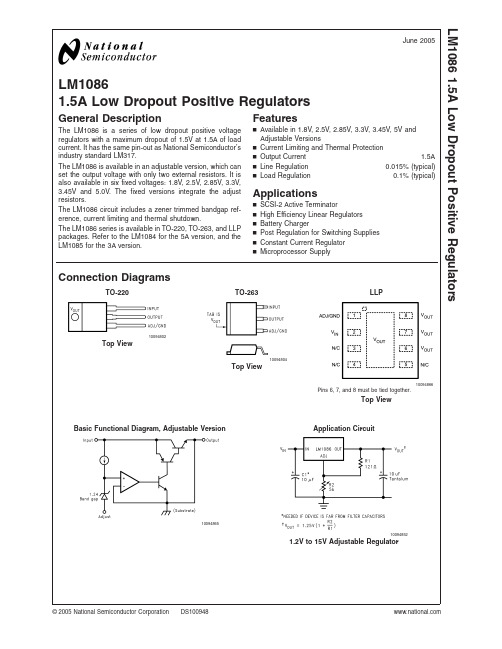

Features

n Available in 1.8V, 2.5V, 2.85V, 3.3V, 3.45V, 5V and Adjustable Versions

n Current Limiting and Thermal Protection

n Ouine Regulation

Symbol

Parameter

Conditions

Min

Typ

Max

Units

(Note 6) (Note 5) (Note 6)

VREF

Reference Voltage

VOUT

Output Voltage (Note 7)

∆VOUT

Line Regulation (Note 8)

LM1086-ADJ IOUT = 10mA, VIN−VOUT = 3V 10mA ≤IOUT ≤ IFULL LOAD, 1.5V ≤ VIN−VOUT ≤ 15V (Note 7) LM1086-1.8 IOUT = 0mA, VIN = 5V 0 ≤ IOUT ≤ IFULL LOAD, 3.3V ≤ VIN ≤ 18V LM1086-2.5 IOUT = 0mA, VIN = 5V 0 ≤ IOUT ≤ IFULL LOAD, 4.0V ≤ VIN ≤ 18V LM1086-2.85 IOUT = 0mA, VIN = 5V 0 ≤ IOUT ≤ IFULL LOAD, 4.35V ≤ VIN ≤ 18V LM1086-3.3 IOUT = 0mA, VIN = 5V 0 ≤ IOUT ≤ IFULL LOAD, 4.75V ≤ VIN ≤ 18V LM1086-3.45 IOUT = 0mA, VIN = 5V 0 ≤ IOUT ≤ IFULL LOAD, 4.95V ≤ VIN ≤ 18V LM1086-5.0 IOUT = 0mA, VIN = 8V 0 ≤ IOUT ≤ IFULL LOAD, 6.5V ≤ VIN ≤ 20V LM1086-ADJ IOUT =10mA, 1.5V≤ (VIN-VOUT) ≤ 15V LM1086-1.8 IOUT = 0mA, 3.3V ≤ VIN ≤ 18V LM1086-2.5 IOUT = 0mA, 4.0V ≤ VIN ≤ 18V

Am27C256-70JC资料

DEVICE NUMBER/DESCRIPTION Am27C256 256 Kilobit (32 K x 8-Bit) CMOS UV EPROM

Valid Combinations AM27C256-45 DC, DCB, DI, DIB AM27C256-55 AM27C256-70 AM27C256-90 AM27C256-120 AM27C256-150 AM27C256-200 AM27C256-255 VCC = 5.0 V ± 5% DC, DCB, DI, DIB DC, DCB, DI, DIB, DE, DEB

DEVICE NUMBER/DESCRIPTION Am27C256 256 Kilobit (32 K x 8-Bit) CMOS OTP EPROM

Valid Combinations AM27C256-55 AM27C256-70 AM27C256-90 AM27C256-120 JC, PC, JI, PI AM27C256-150 AM27C256-200 AM27C256-255 JC, PC

1 2 3 4 5 6 7 8 9 10 11 12 13 14

28 27 26 25 24 23 22 21 20 19 18 17 16 15

VCC A14 A13 A8 A9 A11 OE# (G#) A10 CE# (E#) DQ7 DQ6 DQ5 DQ4 DQ3

08007I-2

4 3 2 1 32 31 30 A6 A5 A4 A3 A2 A1 A0 NC DQ0 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 VSS DU DQ3 DQ4 DQ1 DQ2 DQ5 29 28 27 26 25 24 23 22 21 A8 A9 A11 NC OE# (G#) A10 CE# (E#) DQ7 DQ6

TESCOM中文样本

0-1200, 0-1800

PSIG

铝 316 不锈钢

BB-5 系列: 袖珍型,两级减压

• 重量轻,设计紧凑

6,000 PSIG (414 Bar)

• 级间安全泄放接口

• 活塞感应,使用寿命长

• 无排放功能

0-80, 0-140,

Cv = 0.06

0-220, 0-700,

0-1200 PSIG

用户定制 - 减压及背压 . . . . . . . . . . . . . . . . . . . . . 8 替代燃料 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 阀门 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 新产品SG系列 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 生物技术及医药用调压器 . . . . . . . . . . . . . . . . . . . 10 用户定制成套管路设备装置及系统 . . . . . . . . . . . 10 电子控制调压器 . . . . . . . . . . . . . . . . . . . . . . . . . 11-12 附件 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Tescom 生产及销售网络 ... 遍及全球!

北美 Elk River,明尼苏达州 美国

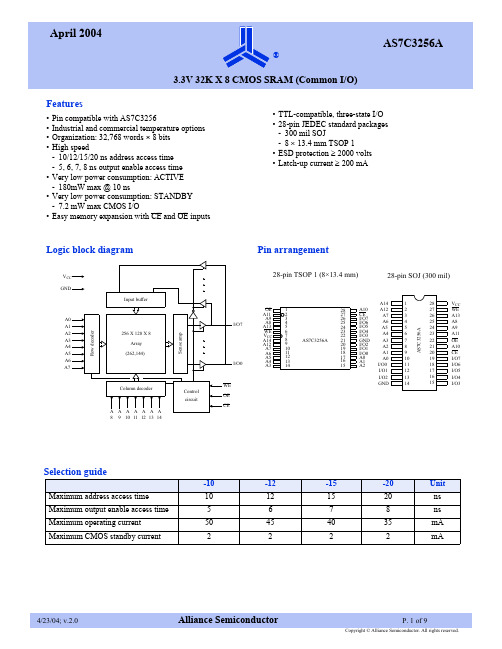

ALLIANCE MEMORY AS7C3256A 说明书

April 2004AS7C3256A3.3V 32K X 8 CMOS SRAM (Common I/O)®Features•Pin compatible with AS7C3256•Industrial and commercial temperature options •Organization: 32,768 words × 8 bits •High speed-10/12/15/20 ns address access time -5, 6, 7, 8 ns output enable access time •Very low power consumption: ACTIVE -180mW max @ 10 ns•Very low power consumption: STANDBY -7.2 mW max CMOS I/O•Easy memory expansion with CE and OE inputs•TTL-compatible, three-state I/O •28-pin JEDEC standard packages -300 mil SOJ-8 × 13.4 mm TSOP 1•ESD protection ≥ 2000 volts •Latch-up current ≥ 200 mALogic block diagram98A71011121314I/O0I/O7V Pin arrangement1234567891011121314282726252423222120191817V CC WE A13A8A9A11OE A10CE I/O7I/O6I/O5I/O4I/O3A14A12A7A6A5A4A3A2A1A0I/O0I/O1I/O2GND AS7C3256A16151234567891011121314282726252423222120191817V CC WE A13A8A9A11OE A10CE I/O7I/O6I/O5I/O4I/O3A14A12A7A6A5A4A3A2A1A0I/O0I/O1I/O2GND A S 7C 3256A161528-pin TSOP 1 (8×13.4 mm)28-pin SOJ (300 mil)Selection guide-10-12-15-20Unit Maximum address access time 10121520ns Maximum output enable access time 5678ns Maximum operating current 50454035mA Maximum CMOS standby current2222mAFunctional descriptionThe AS7C3256A is a 3.3V high-performance CMOS 262,144-bit Static Random-Access Memory (SRAM) device organized as 32,768 words × 8 bits. It is designed for memory applications requiring fast data access at low voltage, including Pentium TM, PowerPC TM, and portable computing. Alliance’s advanced circuit design and process techniques permit 3.3V operation without sacrificing performance or operating margins.The device enters standby mode when CE is high. CMOS standby mode consumes 7.2 mW. Normal operation offers 75% power reduction after initial access, resulting in significant power savings during CPU idle, suspend, and stretch mode. Equal address access and cycle times (t AA, t RC, t WC) of 10/12/15/20 ns with output enable access times (t OE) of 5, 6, 7, 8 ns are ideal for high-performance applications. The chip enable (CE) input permits easy memory expansion with multiple-bank memory organizations.A write cycle is accomplished by asserting chip enable (CE) and write enable (WE) LOW. Data on the input pins I/O0-I/O7 is written on the rising edge of WE (write cycle 1) or CE (write cycle 2). To avoid bus contention, external devices should drive I/O pins only after outputs have been disabled with output enable (OE) or write enable (WE).A read cycle is accomplished by asserting chip enable (CE) and output enable (OE) LOW, with write enable (WE) high. The chip drives I/O pins with the data word referenced by the input address. When chip enable or output enable is high, or write enable is low, output drivers stay in high-impedance mode.All chip inputs and outputs are TTL-compatible. Operation is from a single 3.3 ±0.3V supply. The AS7C3256A is packaged in high volume industry standard packages.Absolute maximum ratingsParameter Symbol Min Max UnitV oltage on V CC relative to GND V t1–0.5+5.0VV oltage on any pin relative to GND V t2–0.5V CC + 0.5V Power dissipation P D– 1.0W Storage temperature (plastic)T stg–65+150o C Ambient temperature with V CC applied T bias–55+125o CDC current into outputs (low)I OUT–20mA Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.Truth tableCE WE OE Data ModeH X X High Z Standby (I SB, I SB1)L H H High Z Output disable (I CC)L H L D OUT Read (I CC)L L X D IN Write (I CC)Key: X = Don’t care, L = Low, H = HighRecommended operating conditions* V ILmin = –1.0V for pulse width less than 5ns.** V IH max = V CC + 2.0V for pulse width less than 5ns.DC operating characteristics (over the operating range)1Capacitance (f = 1MHz, T a = room temperature, V CC = NOMINAL)2ParameterSymbol Min Typical Max Unit Supply voltage V CC 3.0 3.3 3.6V Input voltageV IH ** 2.0–V CC +0.5V V IL *-0.5–0.8VAmbient operating temperaturecommercial T A 0–70oCindustrialT A–40–85o CParameterSymTest conditions-10-12-15-20Unit Min Max Min Max Min Max Min Max Input leakage current |I LI |V CC = Max,V in = GND to V CC –1–1–1–1µA Output leakage current |I LO |V CC= Max,V OUT = GND to V CC –1–1–1–1µA Operatingpower supply currentI CCV CC = Max, CE ≤ V ILf = f Max , I OUT = 0mA–50–45–40–35mAStandby power supply currentI SBV CC = Max, CE > V IH f = f Max–20–20–20–20mAI SB1V CC = Max, CE > V CC –0.2V V IN < 0.2V orV IN > V CC –0.2V , f = 0– 2.0– 2.0– 2.0– 2.0mA Output voltageV OL I OL = 8 mA, V CC =Min –0.4–0.4–0.4–0.4V V OH I OH = –4 mA, V CC =Min 2.4–2.4–2.4–2.4–VParameterSymbol Signals Test conditions Max Unit Input capacitance C IN A, CE , WE , OEV in = 0V 5pF I/O capacitanceC I/OI/OV in = V out = 0V7pFRead cycle (over the operating range)3,9Key to switching waveformsRead waveform 1 (address controlled)3,6,7,9Read waveform 2 (CE controlled)3,6,8,9ParameterSymbol -10-12-15-20Unit NotesMin Max Min Max Min Max Min Max Read cycle time t RC 10–12–15–20–ns Address access time t AA –10–12–15–20ns 3Chip enable (CE) access time t ACE –10–12–15–20ns 3Output enable (OE) access time t OE –5–6–7–8ns Output hold from address change t OH 3–3–3–3–ns5CE LOW to output in low Z t CLZ 3–3–3–3–ns 4, 5CE HIGH to output in high Z t CHZ –3–3–4–5ns 4, 5OE LOW to output in low Z t OLZ 0–0–0–0–ns 4, 5OE HIGH to output in high Z t OHZ –3–3–4–5ns 4, 5Power up time t PU 0–0–0–0–ns 4, 5Power down timet PD–10–12–15–20ns4, 5Undefined output/don’t careFalling inputRising inputAddressD outWrite cycle (over the operating range)11Write waveform 1 (WE controlled)10,11Write waveform 2 (CE controlled)10,11ParameterSymbol -10-12-15-20Unit NotesMin Max Min Max Min Max Min Max Write cycle time t WC 10–12–15–20–ns Chip enable to write end t CW 8–8–10–12–ns Address setup to write end t AW 8–8–10–12–ns Address setup time t AS 0–0–0–0–ns Write pulse width t WP 7–8–9–12–ns Write recovery timet WR 0–0–0–0–ns Address hold from end of write t AH 0–0–0–0–ns Data valid to write end t DW 5–6–8–10–ns Data hold timet DH 0–0–0–0–ns 4, 5Write enable to output in high Z t WZ –5–6–7–8ns 4, 5Output active from write endt OW3–3–3–3–ns 4,5AC test conditionsNotes1During V CC power-up, a pull-up resistor to V CC on CE is required to meet I SB specification.2This parameter is sampled, but not 100% tested.3For test conditions, see AC Test Conditions , Figures A, B.4These parameters are specified with CL = 5pF, as in Figures B. Transition is measured ±500mV from steady-state voltage.5This parameter is guaranteed, but not tested.6WE is High for read cycle.7CE and OE are Low for read cycle.8Address valid prior to or coincident with CE transition Low.9All read cycle timings are referenced from the last valid address to the first transitioning address.10N/A11All write cycle timings are referenced from the last valid address to the first transitioning address.12N/A13C=30pF, except on High Z and Low Z parameters, where C=5pF.13ΩD outD +1.72VFigure B: Output loadThevenin equivalent -Output load: see Figure B-Input pulse level: GND to 3.0V. See Figure A.-Input rise and fall times: 2 ns. See Figure A.-Input and output timing reference levels: 1.5V.GND+3.0V Figure A: Input pulsePackage diagrams 28-pin SOJ Min Max in inchesA 0.1280.148A10.026-A20.0950.105B 0.0260.032b 0.0160.020c 0.0070.010D 0.7200.730E 0.2550.275E10.2950.305E20.3300.340e0.050 BSC28-pin TSOP18×13.4 mm Min Max A1.00 1.20A10.050.15A20.91 1.05b 0.170.27c 0.100.20D 11.7011.90e 0.55 nominal E 7.908.10Hd 13.2013.60L 0.500.70α0°5°eDE1Pin 1bBA1A2cESeating PlaneE2AebEHdD α28-pin SOJ28-pin TSOP1Ordering informationNote: Add suffix ‘N’to the above part number for lead free parts. (Ex. AS7C3256A-10JIN)Part numbering systemPackage / Access time Temperature 10 ns12 ns 15 ns 20 ns Plastic SOJ, 300 mil Commercial AS7C3256A-10JC AS7C3256A-12JC AS7C3256A-15JC AS7C3256A-20JC Industrial AS7C3256A-10JI AS7C3256A-12JI AS7C3256A-15JI AS7C3256A-20JI TSOP 8x13.4mmCommercial AS7C3256A-10TC AS7C3256A-12TC AS7C3256A-15TC AS7C3256A-20TC IndustrialAS7C3256A-10TIAS7C3256A-12TIAS7C3256A-15TIAS7C3256A-20TIAS7C3256A –XXX C or IXSRAM prefix V oltage:3 = 3.3V supplyDevice number Access time Packages:J = SOJ 300 milT = TSOP 8x13.4mmTemperature range: C = 0o C to 70 0C I = -40C to 85CN= Lead Free PartAlliance Semiconductor Corporation 2575, Augustine Drive,Santa Clara, CA 95054Tel: 408 - 855 - 4900Fax: 408 - 855 - Copyright © Alliance Semiconductor All Rights ReservedPart Number: AS7C3256A Document Version: v.2.0© Copyright 2003 Alliance Semiconductor Corporation. All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to this document and its products at any time without notice. Alliance assumes no responsibility for any errors that may appear in this document.The data contained herein represents Alliance's best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in Alliance's Terms and Conditions of Sale (which are available from Alliance). All sales of Alliance products are made exclusively according to Alliance's Terms and Conditions of Sale. The purchase of products from Alliance does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of Alliance products in such life-supporting systems implies that the manufacturer assumes all risk of such use and agrees to indemnify Alliance against all claims arising from such use.AS7C3256A®®。

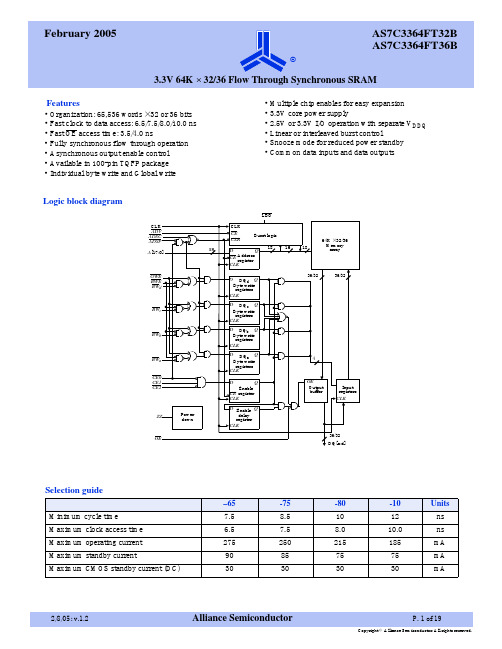

AS7C3364FT36B-65TQI中文资料

Note: Pins 1,30,51,80 are NC for ×32

2/8/05; v.1.2

Alliance Semiconductor

P. 3 of 19

元器件交易网

AS7C3364FT32B AS7C3364FT36B

• Multiple chip enables for easy expansion • 3.3V core power supply • 2.5V or 3.3V I/O operation with separate VDDQ • Linear or interleaved burst control • Snooze mode for reduced power standby • Common data inputs and data outputs

Logic block diagram

CLK ADV ADSC ADSP A[17:0]

GWE BWE BWd

BWc

BWb

BWa

CE0 CE1 CE2

ZZ

OE

LBO

CLK

CE

Q0 Burst logic

CLR

Q1

64K × 32/36

18

D

Q 18

16

18

Memory array

CE

Address register

8.5

10

12

ns

Maximum clock access time

6.5

7.5

8.0

10.0

ns

Maximum operating current

纽泰克产品介绍

纽泰克产品介绍1、公司产品范围:6~35kV环氧树脂浇注式户内单相电流、电压互感器。

2、10kV系列电流互感器:1)AS12/150b/2S、4S:适用于中置柜,柜宽650mm。

A代表电流互感器:150b代表产品宽度(149mm):2S、4S表示此种产品的两种长度,2S对应275mm,4S对应395mm。

S表示带绝缘墙。

额定一次电流:20~1250A。

2)AS12/185h/2、4:适用于中置柜,柜宽800mm。

A代表电流互感器:185h代表产品宽度(184mm):2、4表示两种产品长度,2对应275mm,4对应395mm。

额定一次电流:15~3150A。

3)AD12/200e/3:穿墙式安装,适用于额定一次电流:300~2500A。

4)LMZB1-10:大电流穿心式CT,适用于额定一次电流:2500~5000A,二次绕组最多为四个(额定一次电流较大时)。

3、20kV电流互感器只有一种:AS24/185b/3适用于额定一次电流:15~3150A。

4、35kV电流互感器:1)AN36/250f/2:引进原型号爬电距离较小,很少用。

2)AW36/250f/2:AN36/250f/2的改进型,加大了爬距,一般35kVCT全选此种型号。

适用于额定一次电流:15~3150A,二次绕组最多为四个(额定一次电流较大时)。

5、10kV电压互感器1)相对地连接型的有:REL10、UNE10、URED10。

REL10体积小,二次输出负荷也小,适合小柜型。

UNE10体积大,二次输出负荷也大,还可满足双测量绕组(即二次可以有三个绕组输出)。

适合大柜型。

URED10的体积和参数介于REL10与UNE10之间,带熔断器套管,可用于手车式安装。

相对地连接PT在系统中用星形连接方式:(三相系统用三台PT)。

2)相对相连接型的有:RZL10、UNZ10、URZD10。

RZL10:体积小、输出小、适合小柜型。

UNZ10:体积大、输出大、适合大柜型。

山特产品速查手册说明书

山特产品速查手册SANTAK PRODUCT QUICK REFERENCE 全面保护用心为安全2 | 山特产品速查手册目 录Contents后备式UPSTG-E1000/500, TG1000/500, ET1100/550, K500/K1000 PRO, MT500/1000, TG-BOX 600/850, SP-BOX 在线式UPS塔式C1-3K, 塔式C6-10K, 3C 10-20K, 机架式C1-3kVA Rack, 机架式C6-10kVA Rack, 3C3 Pro (20-200kVA), 3C3 Pro ISO (15 -200kVA), 3C3 HD (20-80kVA), 3C3 HD (400-600kVA),SPU1-20K 电力行业专用 UPS, SIU 10-200K 山特工业级 UPS 灵霄系列PT 3000 (1-3kVA), PT 3000 (6-20kVA)模块式UPSARRAY 3A3 Pro 系列 (15~150kVA), ARRAY 3A3 PT 系列 (25~200kVA), ARRAY 3A3 PT 系列 (60~600kVA)蓄电池C12系列电池, G 系列胶体蓄电池, ARRAY 系列蓄电池, SBC-A 电池柜微模块灵聚2.0微模块产品系列, 灵聚 2.0 Aisle 配电机柜配电单元 (PDU)精密空调全变频小型精密空调 (7.5-20kW), 定频小型精密空调(7.5-20kW), 双轴流小型机房空调, 机房专用空调(25-100kW), 列间精密空调 (SMCRC 系列)机柜S 系列机柜移动电站3-1314-3839-4546-4950-5455-606162-7273 74-75山特后备式TG-E系列UPS⸺美观时尚的“设备守护神”。

TG-E500/1000 UPS功能强大,集智慧、安全、可靠于一身,提升消费者在产品品质、观感、质感方面的使用体验。

山特UPS参数

操作环境/Environment of Performance

温度/0° C-40° C , 湿度/20%-90%

存储高度/Storage height

0-15000m

操作高度/Operation height 外接电池标称电压 保修服务/Warranty Service

0-3000m

192VDC

3年上门维修

428mm × 600mm × 130mm

运输尺寸(宽度×深度×高 度)(mm)

428mm × 600mm × 130mm

净重/Net weight

19.5kg

运输重量/Shipping weight

23kg

主机颜色/Host Color

黑色

听觉噪音/Hearing noise

距设备表面1M处:38 dBA

运输尺寸(宽度× 深度 × 高度)(mm) 净重/Net weight 运输重量/Shipping weight 主机颜色/Host Color 听觉噪音/Hearing noise 操作环境 /Environment of Performance 存储高度/Storage height 操作高度/Operation height 外接电池标称电压 保修服务/Warranty Service

与输入同步〔市电模式〕当市电频率超出(46~54)Hz范围时,输出频率为 50(1±0.2%)Hz

阀控式铅蓄电池 外接蓄电池 电压/容量×数量

备用时间/Backup time

任意时间可选

充电时间/Charging period

≤10小时Leabharlann 输出插座(国标)接线排

转换时间/Transfer time

零转换

AS2350资料

元器件交易网AS23xxSecondary Side Housekeeping CircuitPin Function Description (For AS2333 / AS2350)Pin Number Function Description1V CC Power input to the chip.2+12 V Input for overvoltage and undervoltage for the +12 V rail.3+5 V Input for overvoltage and undervoltage for the +5 V rail.4+3.3/–5 V Input for overvoltage and undervoltage for the +3.3V rail or –5 V rail, depending onproduct option.5–12 V Input for overvoltage and undervoltage for the –12 V rail. This function maydisabled by tying this pin to a positive voltage above 2.4 V.6GND Signal ground and silicon substrate.7HYST Open collector output of the AC undervoltage comparator. A resistor between this pinand AC will provide hysteresis to the AC undervoltage sensing.8OFF Pulling this pin low will reset the FAULT latch and discharge the start-up timingcapacitors, UVB and PG CAP, allowing normal start-up for the system. Pulling this pinhigh will send the FAULT signal high, prompting a system shutdown.9AC Non-inverting input to the AC undervoltage sensing comparator. If the AC pin isless than 2.5 V, POK goes low and UVB cap discharges.10PG CAP A cap to ground provides a delay between undervoltage sensing becoming goodand the POK output going high. Cap discharges whenever an output or ACundervoltage is detected.11POK Open collector output of the undervoltage sensing comparators. This pin goes lowupon an undervoltage condition. Except for the delay set by the PG CAP, this pinalways reflects the actual state of the undervoltage sensing.12DELAY A cap to ground will delay the FAULT signal when the OFF pin is used to shut downthe system. The POK will signal a power fail warning immediately, but the FAULTshutdown of the power supply will be delayed.13UVB A cap to ground provides start-up blanking of the undervoltage sensing portion of theFAULT signal. This pin may also be grounded to prevent undervoltage conditions fromtriggering the FAULT signal. This pin discharges the cap whenever AC goes low orFAULT pin goes high.14V REF 2.5 V Voltage reference. This is a series regulator type reference.15FAULT Open collector output of the overvoltage and undervoltage comparators.16CBD Crow bar drive output of the overvoltage faults only.Pin Function Description (For AS2316)Pin Number Function Description1V CC Power input to the chip.2+12 V Input for overvoltage and undervoltage for the +12 V rail.3+5 V Input for overvoltage and undervoltage for the +5 V rail.4+3.3Input for overvoltage and undervoltage for the +3.3V rail.5–5 V Input for overvoltage and undervoltage for the –5 V rail.6–12 V Input for overvoltage and undervoltage for the –12 V rail. This function maydisabled by tying this pin to a positive voltage above 2.4 V.7GND Signal ground and silicon substrate.8HYST Open collector output of the AC undervoltage comparator. A resistor between this pinand AC will provide hysteresis to the AC undervoltage sensing.9OFF Pulling this pin low will reset the FAULT latch and discharge the start-up timingcapacitors, UVB and PG CAP, allowing normal start-up for the system. Pulling this pinhigh will send the FAULT signal high, prompting a system shutdown.10AC Non-inverting input to the AC undervoltage sensing comparator. If the AC pin isless than 2.5 V, POK goes low and UVB cap discharges.11PG CAP A cap to ground provides a delay between undervoltage sensing becoming goodand the POK output going high. Cap discharges whenever an output or ACundervoltage is detected.12POK Open collector output of the undervoltage sensing comparators. This pin goes lowupon an undervoltage condition. Except for the delay set by the PG CAP, this pinalways reflects the actual state of the undervoltage sensing.13DELAY A cap to ground will delay the FAULT signal when the OFF pin is used to shut downthe system. The POK will signal a power fail warning immediately, but the FAULTshutdown of the power supply will be delayed.14UVB A cap to ground provides start-up blanking of the undervoltage sensing portion of theFAULT signal. This pin may also be grounded to prevent undervoltage conditions fromtriggering the FAULT signal. This pin discharges the cap whenever AC goes low orFAULT pin goes high.15V REF 2.5 V Voltage reference. This is a series regulator type reference.16FAULT Open collector output of the overvoltage and undervoltage comparators.Absolute Maximum RatingsParameterSymbolRatingUnitSupply VoltageV CC 20V Continuous Power Dissipation at 25°C PD 1000mW Junction TemperatureT J 150°C Storage Temperature RangeT STG –65 to 150°C Lead Temperature, Soldering 10 SecondsT L300°CStresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.Typical Thermal ResistancePackage θJA θJC Typical Derating 16L SOIC 65° C/W 45° C/W 10.0 mW/°C 16L PDIP 80° C/W 35° C/W12.5 mW/°CRecommended ConditionsParameter Symbol Rating Unit Supply VoltageV CC5 - 12VElectrical CharacteristicsElectrical Characteristics are guaranteed over full junction temperature range (0 to 105° C). Ambient temperature must be derated based on power dissipation and package thermal characteristics. Unless otherwise specified, the conditions of test are V CC = 12 V;+3.3 V = 3.3 V; +5 V = 5V; +12 V = 12 V; –12 V = –12 V; –5 V = –5 V; OFF = low.Electrical Characteristics are guaranteed over full junction temperature range (0 to 105° C). Ambient temperature must be derated based on power dissipation and package thermal characteristics. Unless otherwise specified, the conditions of test are V CC = 12 V; +3.3 V = 3.3 V; +5 V = 5V; +12 V = 12 V; –12 V = –12 V; –5 V = –5 V.*Temperature deviation is defined as the maximum deviation of the reference over the given temperature range and does not imply an incremental deviation at any given temperature.Typical Performance CurvesNot Available at Time of PublishingTheory of Operationthe outputs of the PSU. Usually, just one or the other output is used depending on the PSU’s cost and system definition. Both methods are in-tended to protect the customer’s system, and the customer, as the first priority.1.2 Undervoltage Faults: POK and FAULT An undervoltage condition is sometimes not con-sidered a catastrophic or dangerous condition,but always one which the customer should be warned about. The POK signal is a logic line to the customer’s system that is specified in most PC type power supply systems. The AS23xx will pull the POK signal low when a UV fault is detected. A UV fault may or may not require the system to shut down, so an undervoltage blank-ing pin is provided (UVB). Grounding this pin will prevent UV faults from propogating to the FAULT pin. CBD does not react to UV faults.1.3 Input Undervoltage: AC and HYST In addition, there is a special undervoltage detec-tion input for sensing the input voltage to the power supply, designated as the AC pin. This pin will cause the POK pin to go low if there is insufficient voltage to run the PSU outputs. Since power supplies must maintain high voltage isola-tion between the primary and secondary sides of the system, the AC pin is usually tied to a divided down and filtered representation of the second-ary side switching waveform. Hysteresis for this function, to provide immunity from line ripple, is configured by the PSU designer and is imple-mented with the HYST pin, which is an open collector output of the AC comparator.Section 2 - PSU Start-up Sequences2.0 System Start-up SequenceWhen the power supply starts up, the AS23xx must not erroneously report a FAULT. In addi-tion, most PC type power supply specificationsThe AS23xx performs housekeeping functions for power supplies, especially switching power supplies for personal computers. The chip re-sides on the secondary side of the power supply (PSU), and it performs three primary functions: 1) monitors the output voltages and reports faults2) sequences the start-up of the PSU 3) sequences the shutdown of the PSU Section 1 - Output Voltages and Faults 1.0 Output Voltage MonitoringThe AS23xx monitors the standard voltage out-puts for PC type power supplies. It has inputs for +12 V, +5 V, +3.3 V, -5 V and -12 V. These inputs are tied directly to the outputs of the PSU, and therefore do not require external dividers to set the error thresholds. These pins are monitored for both overvoltage (OV) and undervoltage (UV)conditions. The spec’s for these thresholds are listed in the data sheet.1.1 Overvoltage Faults: FAULT and CBD An overvoltage condition in a power supply is considered to be a catastrophic and dangerous condition which must result in a safe, complete and near-instantaneous shutdown of the sys-tem. Overvoltages most often result from a break in the system feedback and control cir-cuitry or from a short between outputs. When the AS23xx detects an overvoltage, the fault is latched internally, and the FAULT and CBD pins go high. The FAULT pin is an open collector NPN output which is intended to drive an optocoupler LED for feedback to the primary side controller of the PSU. The CBD pin is an NPN Darlington output which is intended to drive an SCR crowbar circuit which will short circuitrequire a specific timing sequence for the POK signal. Some PSU systems also require an isolated, low voltage, low power remote turn-on switch, rather than a large line cord switch.2.1 VREF Enable of Chip BiasSince the VCC of the AS23xx comes up in a finite amount of time, and since the VREF of the chip and the bias for the comparators are not within specification until approximately 4.2 V of VCC is available, the comparators for OV and UV and most other functions are disabled until VREF is within spec. This prevents the false detection of a FAULT due to an erroneous VREF. Similarly, if VREF is too heavily loaded and gets pulled low out of spec, these functions will also shut off.2.2 Blanking UV’s During Start-up: UVBAs the power supply outputs come up, the undervoltage FAULTs must be blanked to allow the supply to complete its start-up. Putting a capacitor to ground on the UVB pin will allow the PSU designer to set a specific period of time during which undervoltages will not propogate to the FAULT pin. The UVB pin provides a 1 µA current source to charge the cap, and once the UVB pin charges above 2.5 V, the undervoltage sensing is enabled. UVB does not blank undervoltages to the POK pin. The UVB pin is clamped one diode above VREF, or about 3.1 V, allowing fast discharge of the capacitor when the system resets.2.3 POK BiasThe POK pin has some specific requirements based on industry standard PC power supply specifications. At start-up, the POK pin must not rise above 0.4V. The POK pin is an NPN open collector whose base is tied to VCC via a simple resistor. Therefore, once VCC pulls above one diode or about 0.6 V, the POK pin will go low and saturate. If the POK pin external pull-up is to the 5 V output, the POK signal will not go above 0.4V if the VCC of the AS23xx is tied to the 12 V output or an auxilliary rail.2.4 POK Start-up Timing: PGCAPIn addition to 2.3 above, most PC power supplies require the POK pin to remain low until all outputs have been good for at least 100 ms but not more than 500 ms. A cap to ground on the PGCAP pin allows to the PSU designer to set the timing delay between the PSU outputs becoming good and the POK pin going high. The PGCAP pin provides a 1 µA current source to charge the cap, and when the cap charges above 2.5 V, the POK pin goes high. When an undervoltage occurs, the PGCAP pin discharges rapidly and the POK pin goes low. The POK pin does not respond to overvoltages.2.5 Isolated Remote On/Off Switching: OFF and FAULTA low voltage, isolated remote on/off switch may be implemented with the AS23xx OFF pin. If the chip VCC is run off an auxilliary rail, the FAULT signal may be used to start and stop the PSU. When the OFF pin is pulled from high to low or grounded, the FAULT pin resets to a low state, which may be used to drive an optocoupler to enable the primary side PWM controller. Allow-ing the OFF pin to go open circuit or high causes the POK pin to go low immediately, and the FAULT pin will go high after a time delay set by a cap to ground on the DELAY pin. This allows the customer’s system to receive a POK warning before the PSU actually shuts down.Section 3 - PSU Shutdown Sequences3.0 Shutdown SequenceFor normal shutdowns, the primary requirement is that the POK signal should go low some minimum time before the PSU outputs fall out of spec.3.1 Delaying Remote OFF: DELAYIn systems which use the OFF and FAULT pins to provide remote on/off switching, the delay between the OFF pin going high and the FAULT signal going high is programmable with a capaci-tor to ground on the DELAY pin as described in 2.5 above. The POK pin, on the other hand will go high immediately after the OFF pin is open circuited or pulled high, giving the system warn-ing of the impending shutdown. The DELAY pin provides a 1 µA current source to charge the cap, and when the cap charges above 2.5 V, the FAULT pin will go high.3.2 AC Warning Prior to Primary Drop-out In systems where the input line voltage is switched, the AC pin threshold should be set so that it causes POK to go low before the primary bulk voltage reaches drop-out and the primary PWM shuts off. The output of the AC comparator also causes the UVB pin to pull low, so that the undervoltage sensing does not trip the FAULT latch as the outputs fall below spec. Recall that the AC pin senses a divided down and filtered representation of the secondary side switching waveform, which will provide a proportional rep-resentation of the primary voltage via the turns ratio of the transformer.ASTEC reserves the right to make changes without further notice to any products described herein to improve reliability, function, or design. ASTEC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights or the rights of others. ASTEC products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify ASTEC of any such intended end use whereupon ASTEC will determine availability and suitability of its products for the intended use. ASTEC and the ASTEC logo are trademarks of ASTEC (BSR) PLC.ASTEC SEMICONDUCTOR255 Sinclair Frontage Road • Milpitas, California 95035 • Tel. (408) 263-8300 • FAX (408) 263-8340。

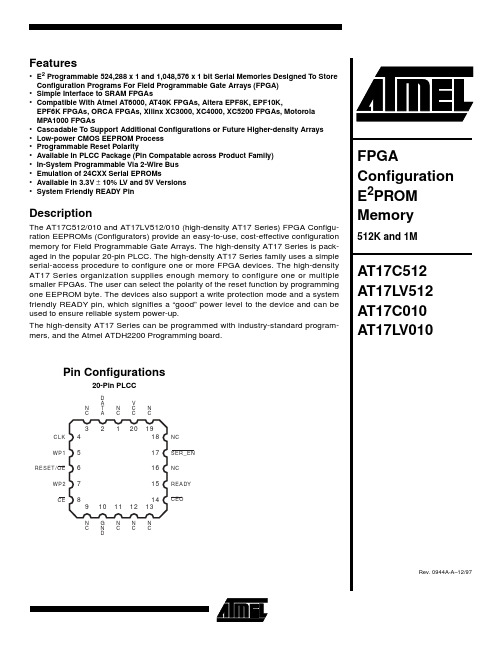

AT17C512-10JC资料

Features•E 2 Programmable 524,288 x 1 and 1,048,576 x 1 bit Serial Memories Designed To Store Configuration Programs For Field Programmable Gate Arrays (FPGA)•Simple Interface to SRAM FPGAs•Compatible With Atmel AT6000, AT40K FPGAs, Altera EPF8K, EPF10K,EPF6K FPGAs, ORCA FPGAs, Xilinx XC3000, XC4000, XC5200 FPGAs, Motorola MP A1000 FPGAs•Cascadable To Support Additional Configurations or Future Higher-density Arrays •Low-power CMOS EEPROM Process •Programmable Reset Polarity•Available In PLCC Package (Pin Compatable across Product Family)•In-System Programmable Via 2-Wire Bus •Emulation of 24CXX Serial EPROMs•Available in 3.3V ± 10% L V and 5V Versions •System Friendly READY PinDescriptionThe AT17C512/010 and AT17LV512/010 (high-density AT17 Series) FPGA Configu-ration EEPROMs (Configurators) provide an easy-to-use, cost-effective configuration memory for Field Programmable Gate Arrays. The high-density AT17 Series is pack-aged in the popular 20-pin PLCC. The high-density AT17 Series family uses a simple serial-access procedure to configure one or more FPGA devices. The high-density AT17 Series organization supplies enough memory to configure one or multiple smaller FPGAs. The user can select the polarity of the reset function by programming one EEPROM byte. The devices also support a write protection mode and a system friendly READY pin, which signifies a “good” power level to the device and can be used to ensure reliable system power-up.The high-density AT17 Series can be programmed with industry-standard program-mers, and the Atmel ATDH2200 Programming board.Pin Configurations20-Pin PLCCControlling The High-Density AT17 Series Serial EEPROMsMost connections between the FPGA device and the Serial EEPROM are simple and self-explanatory:•The DA T A output of the high-density A T17 Series drives DIN of the FPGA devices.•The master FPGA CCLK output drives the CLK input of the high-density A T17 Series.•The CEO output of any A T17C/L V512/010 drives the CE input of the next A T17C/L V512/010 in a cascade chain of PROMs.•SER_EN must be connected to V CC, (except during ISP).READY is available as an open-collector indicator of the device’s RESET status; it is driven Low while the device is in its POWER-ON RESET cycle and released (tri-stated) when the cycle is complete.There are two different ways to use the inputs CE and OE, as shown in the AC Characteristics waveforms. Condition 1The simplest connection is to have the FPGA D/P output drive both CE and RESET/OE in parallel (Figure 1). Due to its simplicity, however, this method will fail if the FPGA receives an external reset condition during the configura-tion cycle. If a system reset is applied to the FPGA, it will abort the original configuration and then reset itself for a new configuration, as intended. Of course, the high-density AT17 Series does not see the external reset signal and will not reset its internal address counters and, consequently, will remain out of sync with the FPGA for the remainder of the configuration cycle.Condition 2The FPGA D/P output drives only the CE input of the high-inversion of the input to the FPGA RESET input pin. This connection works under all normal circumstances, even High. A High level on the RESET/OE input to the AT17C/LVxxx – during FPGA reset – clears the Configura-tor’s internal address pointer, so that the reconfiguration starts at the beginning. The high-density AT17 Series does not require an inverter since the RESET polarity is pro-grammable.Block DiagramAT17C/LV512/010Pin Configurations20 PLCC Name I/O Description2DA T A I/O Three-state DA T A output for reading. Input/Output pin for programming.4CLK I Clock input. Used to increment the internal address and bit counter for reading and programming.5WP1I WRITE PROTECT (1). Used to protect portions of memory during programming. See programming guide for details.6RESET/OEIRESET/Output Enable input (when SER_EN is High). A Low level on both the CE andRESET/OE inputs enables the data output driver. A High level on RESET/OE resets both the address and bit counters. The logic polarity of this input is programmable as either RESET/OE or RESET/OE. This document describes the pin as RESET/OE.7WP2I WRITE PROTECT (2). Used to protect portions of memory during programming. See programming guide for details.8CEIChip Enable input. Used for device selection. A Low level on both CE and OE enables the data output driver. A High level on CE disables both the address and bit counters and forces the device into a low power mode. Note this pin will not enable/disable the device in 2-wire Serial Programming mode (i.e., when SER_EN is Low).10GND Ground pin.14CEOOChip Enable Out output. This signal is asserted Low on the clock cycle following the last bit read from the memory. It will stay Low as long as CE and OE are both Low. It will then follow CE until OE goes High. Thereafter, CEO will stay High until the entire PROM is read again and senses the status of RESET polarity.A2I Device selection input, A2. This is used to enable (or select) the device during programming, when SER_EN is Low (see Programming Guide for more details)15READY O Open collector reset state indicator. Driven Low during power-up reset, released when power-up is complete. (Recommend a 4.7K Ω Pull-up on this pin if used).17SER_EN ISerial enable is normally high during FPGA loading operations. Bringing SER_EN Low, enables the two wire serial interface mode for programming.20V CC+3.3V/+5V power supply pin.Absolute Maximum Ratings*Operating T emperature..................................-55°C to +125°C *NOTICE:Stresses beyond those listed under Absolute Maxi-mum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other condi-tions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Rat-ings conditions for extended periods of time may affect device reliability.Storage T emperature.....................................-65°C to +150°C Voltage on Any Pinwith Respect to Ground............................-0.1V to V CC + 0.5V Supply Voltage (V CC ).........................................-0.5V to +7.0V Maximum Soldering T emp. (10 s @ 1/16 in.)..................260°C ESD (R ZAP = 1.5K, C ZAP = 100 pF)...............................2000V元器件交易网FPGA Master Serial Mode SummaryThe I/O and logic functions of the FPGA and their associ-ated interconnections are established by a configuration program. The program is loaded either automatically upon power up, or on command, depending on the state of the three FPGA mode pins. In Master Mode, the FPGA auto-matically loads the configuration program from an external memory. The Serial Configuration EEPROM has been designed for compatibility with the Master Serial Mode. Cascading Serial Configuration EEPROMsFor multiple FPGAs configured as a daisy-chain, or for future FPGAs requiring larger configuration memories, cas-caded Configurators provide additional memory.As the last bit from the first Configurator is read, the clock disables its DATA line. The second Configurator recog-nizes the Low level on its CE input and enables its DATA output.Figure 1. Condition 1 Connection After configuration is complete, the address counters of all cascaded Configurators are reset if the reset signal drives the RESET/OE on each Configurator to its active (High) level.If the address counters are not to be reset upon comple-more details, please reference the AT17C Series Program-ming Guide.Programming ModeThe programming mode is entered by bringing SER_EN Low. In this mode the chip can be programmed by the 2-wire interface. The programming is done at V CC supply only. Programming super voltages are generated inside the chip. See the Programming Specification for Atmel's Con-figuration Memories Application Note for further informa-tion. The AT17C Series parts are read/write at 5V nominal. The AT17LV parts are read/write at 3.3V nominal.AT17C/L VXXX Reset PolarityThe AT17C/LVXXX lets the user choose the reset polarityStandby ModeThe AT17C/LVXXX enters a low-power standby mode whenever CE is asserted High. In this mode, the Configura-tor consumes less than 0.5mA at 5.0 volts. The output remains in a high impedance state regardless of the stateof the OE input. Operating ConditionsSymbol Description AT17CXXX AT17L VXXXUnits Min/Max Min/MaxV CC CommercialSupply voltage relative to GND-0°C to +70°C4.75 /5.25 3.0 / 3.6V IndustrialSupply voltage relative to GND-40°C to +85°C4.5 /5.5 3.0 / 3.6V MilitarySupply voltage relative to GND-55°C to +125°C4.5 /5.5 3.0 / 3.6V元器件交易网AT17C/LV512/010DC CharacteristicsV CC = 5V ± 5% Commercial / 5V ± 10% Ind./Mil.Symbol Description Min Max UnitsV IH High-level input voltage 2.0V CC VV IL Low-level input voltage00.8VV OH High-level output voltage (I OH = -4 mA)Commercial 3.86VV OL Low-level output voltage (I OL = +4 mA)0.32VV OH High-level output voltage (I OH = -4 mA)Industrial 3.76VV OL Low-level output voltage (I OL = +4 mA)0.37VV OH High-level output voltage (I OH = -4 mA)Military 3.7VV OL Low-level output voltage (I OL = +4 mA)0.4V I CCA Supply current, active mode (at FMAX)10mA I L Input or output leakage current (V IN = V CC or GND)-1010µAI CCS Supply current, standby modeCommercial0.5mA Industrial/Military0.5mADC CharacteristicsV CC = 3.3V ± 10%Symbol Description Min Max Units V IH High-level input voltage 2.0V CC V V IL Low-level input voltage00.8VV OH High-level output voltage (I OH = -2.5 mA)Commercial 2.4VV OL Low-level output voltage (I OL = +3 mA)0.4VV OH High-level output voltage (I OH = -2 mA)Industrial 2.4VV OL Low-level output voltage (I OL = +3 mA)0.4VV OH High-level output voltage (I OH = -2 mA)Military 2.4VV OL Low-level output voltage (I OL = +2.5 mA)0.4V I CCA Supply current, active mode5mA I L Input or output leakage current (V IN = V CC or GND)-1010µAI CCS Supply current, standby modeCommercial100µA Industrial/Military100µA元器件交易网AC CharacteristicsAC Characteristics When Cascading元器件交易网AT17C/LV512/010.2.AC test load = 50 pF .3.Float delays are measured with 5 pF AC loads. Transition is measured ± 200 mV from steady state active levels.AC Characteristics for AT17C512/010V CC = 5V ± 5% Commercial / V CC = 5V ± 10% Ind./MilSymbol Description Commercial/IndustrialMilitaryUnits MinMax MinMax T OE (2)OE to Data Delay 3035ns T CE (2)CE to Data Delay 4545ns T CAC (2)CLK to Data Delay5050ns T OH (2)Data Hold From CE, OE, or CLK 0ns T DF (3)CE or OE to Data Float Delay 5050ns T LC CLK Low Time 2020ns T HC CLK High Time2020ns T SCE CE Setup Time to CLK (to guarantee proper counting)2025ns T HCE CE Hold Time to CLK (to guarantee proper counting)00ns T HOE OE High Time (Guarantees Counter Is Reset)2020ns F MAX MAX Input Clock Frequency 1515MHz V RDYReady Pin Open Collector Voltage1.22.21.22.2VAC Characteristics for AT17C512/010 When CascadingV CC = 5V ± 5% Commercial / V CC = 5V ± 10% Ind./Mil.Symbol DescriptionCommercial/IndustrialMilitaryUnits MinMax MinMax T CDF (3)CLK to Data Float Delay 5050ns T OCK (2)CLK to CEO Delay 3540ns T OCE (2)CE to CEO Delay3535ns T OOE (2)RESET/OE to CEO Delay3030ns元器件交易网2.AC test load = 50 pF .3.Float delays are measured with 5 pF AC loads. T ransition is measured ± 200 mV from steady state active levels.4.During cascade F MAX = 12.5 MHz.AC Characteristics for AT17LV512/010V CC = 3.3V ± 10%Symbol Description Commercial/IndustrialMilitaryUnits Min MaxMin MaxT OE (2)OE to Data Delay 5055ns T CE (2)CE to Data Delay 5560ns T CAC (2)CLK to Data Delay5560ns T OH Data Hold From CE, OE, or CLK 0nsT DF (3)CE or OE to Data Float Delay 5050ns T LC CLK Low Time 2525ns T HC CLK High Time2525ns T SCE CE Setup Time to CLK (to guarantee proper counting)3035ns T HCE CE Hold Time to CLK (to guarantee proper counting)00ns T HOE OE High Time (Guarantees Counter Is Reset)2525ns F MAX (4)MAX Input Clock Frequency1510MHz V RDY Ready Pin Open Collector Voltage1.22.21.22.2VAC Characteristics for AT17LV512/010 When CascadingV CC = 3.3V ± 10%Symbol DescriptionCommercial/IndustrialMilitaryUnits MinMax MinMax T CDF (3)CLK to Data Float Delay 5050ns T OCK (2)CLK to CEO Delay 5055ns T OCE (2)CE to CEO Delay 3540ns T OOE (2)RESET/OE to CEO Delay3535ns元器件交易网元器件交易网AT17C/LV512/010Ordering Information - 5V DevicesMemory Size Ordering Code Package Operation Range 512K A T17C512-10JC20J Commercial(0°C to 70°C)A T17C512-10JI20J Industrial(-40°C to 85°C) 1M A T17C010-10JC20J Commercial(0°C to 70°C)A T17C010-10JI20J Industrial(-40°C to 85°C) Ordering Information - 3.3V DevicesMemory Size Ordering Code Package Operation Range 512K A T17L V512-10JC20J Commercial(0°C to 70°C)A T17L V512-10JI20J Industrial(-40°C to 85°C) 1M A T17L V010-10JC20J Commercial(0°C to 70°C)A T17L V010-10JI20J Industrial(-40°C to 85°C)Package Type20J20 Lead, Plastic J-Leaded Chip Carrier (PLCC)。

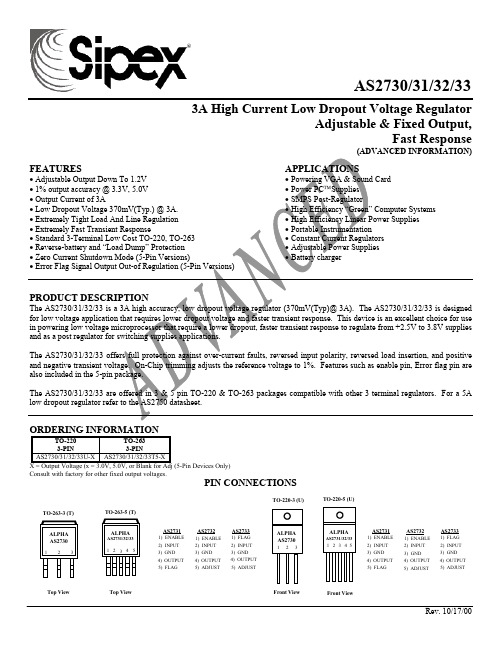

AS2730资料

AS2730/31/32/333A High Current Low Dropout Voltage RegulatorAdjustable & Fixed Output,Fast Response(ADVANCED INFORMATION)ORDERING INFORMATIONTO-220 3-PIN TO-263 3-PINAS2730/31/32/33U-X AS2730/31/32/33T5-XConsult with factory for other fixed output voltages.PIN CONNECTIONSTop ViewTO-263-3 (T)TO-263-5 (T)Top ViewFront ViewTO-220-3 (U)TO-220-5 (U)Front ViewAS2731AS2732AS27331) ENABLE 2) INPUT 3) GND 4) OUTPUT 5) FLAG1) ENABLE 2) INPUT 3) GND 4) OUTPUT 5) ADJUST1) FLAG 2) INPUT 3) GND 4) OUTPUT 5) ADJUSTAS2731AS2732AS27331) ENABLE 2) INPUT 3) GND 4) OUTPUT 5) FLAG1) ENABLE 2) INPUT 3) GND 4) OUTPUT 5) ADJUST1) FLAG 2) INPUT 3) GND 4) OUTPUT 5) ADJUSTABSOLUTE MAXIMUM RATINGSLead Temp. (Soldering, 5 Seconds)................................260°CMaximum Input Voltage (16V)Storage Temperature Range......................................................-65° to +150°COperating Junction Temperature RangeAS2730/31/32/33 Control Section.................................. -45°C +125°C AS2730/31/32/33 Power Transistor.................................-45°C +150°CELECTRICAL CHARACTERISTICS (NOTE 1) at I OUT = 10mA, T a =25°C, unless otherwise specified.PARAMETER CONDITIONS TypAS2730/31/32/33 Min MaxUnits3.3V VersionOutput Voltage (Note 2)I OUT = 10mA10mA ≤I OUT ≤ 3A, 4.75V ≤V IN ≤16V 3.3 3.3 3.270 3.240 3.3303.360 V5.0V VersionOutput Voltage (Note 2)I OUT = 10mA10mA ≤I OUT ≤ 3A, 5.5V ≤V IN ≤16V5.0 5.04.95 4.905.05 5.10VAll Voltage OptionsReference Voltage 1.240 1.228 1.215 1.252 1.265VReference Voltage (Note 8)` 1.203 1.277 VLine Regulation I O = 10mA, (V OUT + 1V) ≤ V IN ≤ 16V0.06 0.5 % Load Regulation V IN = V OUT + 5V, 10mA ≤ I OUT ≤ I FULLLOAD(Note 2, 6)0.2 1 % ∆V 20 100 ppm/°C ∆TOutput Voltage (Note 6) Temperature Coef.I O = 100mA 80 175 I O = 1.5A 250 Dropout VoltageI O = 3A370 600 mVGround CurrentI O = 1.5A, V IN = V OUT , +1V I O = 3A1037 35 mA I GNDDO Ground Pin Current at DropoutV IN = 0.5V less than specified V OUT I OUT = 10mA 0.9 mA Current LimitV OUT = 0V (Note 4) 4.5 3.0AOutput Noise Voltage (10Hz to 100kHz) I L = 100mA C L = 10µFC L = 33µF400 260V RMSAdjust Pin Bias Current40 80 120nAReference Voltage Temperature Coefficient(Note 7) 20 ppm/°CAdjust Pin Bias Current Temperature Coefficient 0.1 nA/°CFlag Output (Error Comparator) AS2731/AS2733Output Leakage CurrentV OH = 16V0.011.002.00µA Output Low VoltageDevice set for 5V. V IN = 4.5V I OL = 250µA220 300 400mV(Cont.)Upper Threshold Voltage Device set for 5V (Note 9) 60 4025mVLower Threshold Voltage Device set for 5V (Note 9) 75 95140mVHysteresis Device set for 5V (Note 9) 15 mV ENABLE Input AS2731/AS2732Input Logic VoltageLow (OFF)High (ON) 2.40.8 VV EN = 16V 100 600750 VEnable PinInput CurrentV EN = 0.8V 12µARegulator Output Current in Shutdown (Note 10) 10500µANotes:The Bold specifications apply to the full operating temperature range.Note 1: Maximum positive supply voltage of 60V must be of limited duration (<100msec) and duty cycle.) The maximum continuous supply voltage is 16V.Note 2: Full load current (I FL) is defined as 1.5A for theNote 3: Dropout voltage is defined as the input-to output differential when the output voltage drops to 99% of its nominal value with V OUT + 1V applied to V IN.Note 4: V IN = V OUT(NOMINAL) +1V. For example, use V IN= 4.3V for a3.3V regulator. Employ pulse-testing procedures to minimize temperature rise.Note 5: Ground pin current is the regulator quiescent current. The total current drawn from the source is the sum of the load current to the ground current.Note 6: Output voltage temperature coefficient is defined as the worst case voltage changed divided by the total temperature range.Note 7: Thermal regulation is defined as the change in the output voltage at a time T after a change in power dissipation is applied, excluding load or line regulation effects. Specifications are for a 200mA load pulse as V IN = 20V (a 4W pulse) for T = 10ms.Note 8: V REF≤ V OUT≤ (V IN – 1), 2.3V ≤ V IN≤ 16V, 10mA < IL ≤ I FL, TJ ≤ T JMAXNote 9: Comparator threshold is expressed in terms of a voltage differential at the Adjust terminal below the nominal reference voltage measured a 6V input. To express these thresholds in terms of output voltage change, multiply the error amplifier gain = V OUT/V REF = (R1 + R2)R2. For example, at a programmable output voltage of 5V, the Error output is guaranteed to go low when the output drops by 95mVx 5V/ 1.240V = 38mV. Threshold remain constant as a percent of V OUT as V OUT is varied, with the dropout warning occurring at typically 5% below nominal, 7.7% guaranteed.Note 10: V EN≤ 0.8V and V IN ≤ 16V, V OUT = 0.APPLICATION HINTSThe AS2730/31/32/33 incorporates protection against over-current faults, reversed load insertion, over temperature operation, and positive and negative transient voltage. However, the use of an output capacitor is required in order to insure the stability and the performances.Thermal ConsiderationAlthough the AS2730/31/32/33 offers limiting circuitry for overload conditions, it is necessary not to exceed the maximum junction temperature, and therefore to be careful about thermal resistance. The heat flow will follow the lowest resistance path, which is the Junction-to-case thermal resistance. In order to insure the best thermal flow of the component, a proper mounting is required. Note that the case of the device is electrically connected to the output. Thecase has to be electrically isolated, a thermally conductive spacer can be used. However do not forget to consider its contribution to thermal resistance.Assuming:V IN = 10V, V OUT = 5V, I OUT = 1.5A, T A = 50°C/W,θHeatsink Case= 6°C/W, θHeatsink Case = 0.5°C/W, θJC = 3°C/W Power dissipation under this conditionP D = (V IN – V OUT) * I OUT = 7.5WJunction TemperatureT J = T A + P D * (θCase – HS + θHS θJC)For the Control SectionT J = 50 + 7.5*(0.5 + 6=3) = 121.25°C121.25°C < T J (max) for the Control & Power Sections.In both case reliable operation is insured by adequate junction temperature.Capacitor RequirementsThe output capacitor is needed for stability and to minimize the output noise. The required value of the capacitor varies with the load. However, a minimum value of 10µF Aluminum will guarantee stability over load. A tantalum capacitor is recommended for a fast load transient responseIf the power source has high AC impedance, a 0.1µF capacitor between input & ground is recommended. This capacitor should have good characteristics up to 250 kHz.Minimum Load CurrentTo ensure a proper behavior of the regulator at light load, a minimum load of 10mA for AS2730/31/32/33 is required. Adjustable Regulator DesignAS2730/31are adjustable regulators and maybe programmed for any value between 1.25V and 16V using two resistors. The relation between the resistors is given by:R1=R2 (V OUT/1.240 –1)Resistors have a large value up to 1mΩ in order to reduce the current consumption. This might be interesting in the case of widely varying load currents.Error FlagAS2731/33 features an error indicating either an over current fault or a low input voltage. This flag pulls low when such a problem occurs and may sink 10mA. It is inoperative during thermal shutdown.Enable InputAS2731/32 features enable input allowing turning ON & OFF the device. EN has been designed to be compatible with TTL/CMOS logic. When the regulator is ON, the current flowing through this pin is approximately 20µA.Fig.1 Basic Fixed Output RegulatorV OUT VINFig. 2 Adjustable Output Voltage RegulatorV OUT VIN1AS2730/31/32/33 PACKAGE DRAWINGTO-263-3L (T)(4.4700.127)±(1.2700.051)±TO-263-5L (T)(4.4700.127)±(1.2700.051)±TO-220-3L (U)0.151D ± 0.002 (3.835 D ± 0.051)0.180 ± 0.005 (4.572 ± 0.127)0.032 ± 0.005 (0.813 ± 0.127)TO-220-5L (U)0.150 D +-0.005(3.81D +-0.13)0.175+-0.005(4.45+-0.13)-。

日本SHINKO神港温控器JC系列 中文选型说明书

日本神港JC□-33A系列数显调节仪

一、产品描述

JC□-33A系列控制器是日本神港(Shinko)生产的一款高精度、低价格的数字显示控制器/调节器。

二、广泛应用

橡塑、纺织、食品加工、电线电缆、汽车和金属热处理、石化、造纸、电厂、冶金、轻工、科研等领域等行业的温度、湿度、压力、液位等参数的调节控制;

可以热电偶K、热电阻pt100、电流DC4-20mA、电压DC1-5V等多种方式输入。

三、产品特点

1、多功能,低价位;

2、采用先进的加热冷却控制;控制方式灵活;自整定PID、PI、PD、P、ON/OFF;

3、2组报警,可设定多种不同的报警方式;

4、可以热电偶、热电阻、DC4-20mA、DC1-5V等多种方式输入;

5、精度高,优于0.2%;采样周期短,0.25s;

6、自带两组设定值,可通过外部给定信号进行切换;

7、可追加功能多:可提供24V直流电源,可设定加热器断线报警和回路异常,可设定串行数字通信功能等。

四、日本shinko神港温控器JC系列简易选型表

注:更多相关产品、各行业温度控制系统解决方案详情、资料下载>>>>>>>>请进入普旭官网:

>>>>>>>>咨询热线:400-000-3990。

三荣大板商品说明书

0304企业简介产品系列产品优势应用空间重点工程010302Company profile Product series Product advantages Application space Key projects p01-02p07-42施工说明Technical details p77-78p03-04工艺性能Process performance p05-06p43-67p68产品总览Product overview p69-76技术参数Technical parameters p79-80 4.5mm0506纯色 (釉面)Solid color(glazed)bSp05bbSp08a bSp03a bSp01bSp07abSp06a bSp05c bSp09bSp05e bSp10a 1000×2000mm / 1000×2400mm / 1000×3000mm 4.5mm every detail is coordinated, delicate design, make the whole space concise,bright, furniture and decoration layout, create such a delicate beautiful, warm andcomfortable space.每一处细节都协调统一,细腻的设计,使得整个空间简练、明亮,家具和装饰品布置其中,营造出如此精致美观、温馨舒适的空间。

Solid Color(GlAzed) / BSP09 / 1000×3000mmSolid Color(GlAzed) / BSP10A / 1000×3000mm 0708纯色(通体)pure color (full body)Pure Color (full Body) / BSf19+BSf29 /1000×3000mm bSf25bSf28bSf15bSf18bSf19bSf04bSf29bSf071000×2000mm / 1000×2400mm / 1000×3000mm 4.5mm 0910布纹wall paper WAll PAPer / BSz10 / 1000×3000mmWAll PAPer / BSz08 /1000×3000mm bSz08bSz09bSz10bSz051000×2000mm / 1000×2400mm / 1000×3000mm The excellent appearance of ceramic tiles with special materials to use, so thatthe texture of the space is very rich, but also reflects a variety of combined lifeexperience, adding special vitality to the space.外观效果出众的瓷砖搭配特别的材质来运用,使空间的质感非常丰富,也反映出多样结合的生活体验,为空间增添了特别的活力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。