Altium Designer设计教程 18

Altium Designer 18 课件第4章

4.3 使用自上而下的层次电路设计方法优化绘制

5.编辑Power图表符的端口。Power图表符代表电源电路,在电源电 路中有4脚连接端子,用于输入从外界稳压电源来的电压,因此Power子 电路块需放置3个输入端口;并需在Power子电路块中放置3个输出端口。 单击【布线】工具栏中的【放置图纸入口】工具。设置相关端口参数。

内容提要

本章主要目的:掌握电路图优化方法,熟练使用各绘图工具。前 几章中虽然完成了电路原理图的绘制,但电路图的线路连接不清晰, 使读者很难理清电路的结构,另外电路的功能不能很直观地表达。因 此,在本章中要对绘制好的电路原理图进行优化,以增强电路的可读 性。

图4.1 待优化电路图

4.1 使用网络标号进行电路原理图绘制的优化

4.1 使用网络标号进行电路原理图绘制的优化

1 .复制电路原理图到新建的原理图文件

执行【编辑】→【选择】→【全部】菜单命令或执行快捷键 “CTRL+A”。

执行【编辑】→【复制】菜单命令,或单击鼠标右键在弹出的菜单 命令中执行【复制】命令。

将界面切换到新建的原理图文件,执行菜单命令【编辑】→【粘 贴】。此时鼠标下将出现已绘制好的电路原理图。

4.6 在电路中标注元件其他相关参数优化绘制

双击电路中的电容C1,此时系统将弹出【Properties】编辑对话框, 在【Parameters】标签页中的Value的文本框中编辑电容C1的耐压值为50V。

编辑完成后,点击【OK】按钮,完成设置。 按照上述方式标注电路,结果如图4-9所示。

4.6 在电路中标注元件其他相关参数优化绘制

4.6 在电路中标注元件其他相关参数优化绘制

在图例电路中包含电阻元件,当电阻体内有电流流过时要发热,温 度太高容易烧毁,为了使电路正常工作,在选用电阻时用户需要考虑选 择何种功率的电阻;电路中还用到电容,电容的耐压值的合理选取是保 证电路正常工作的重要参数;此外,电路中用到二极管,二极管的最大 反向工作电压值的选取是关系电路正常工作的重要参数,如果反向电压 选取不当,可能会造成二极管被击穿。因此在电路中标注元件参数便于 阅读电路。

Altium Designer 18 课件第10章

10.3 创建钻孔文件

图10-11 【层】标签页

10.2 创建Gerber文件

该标签页的左侧列表用于选择设定需要生成Gerber文件的工作层面, 在【画线】列选取Gerber报表内需要记录的板层,如果需要板层翻转后 再记录,则需点选【反射】列中的对应选项。右侧列表则用于选择要加 载到各个Gerber层的机械层。

点击对话框下方的【绘制层】按钮或【镜像层】按钮。 单击【选择使用的】选项,系统将自动选中用户用到的板层。此处 勾选要生成一些相关文件,本例全部勾选。 此对话框中还包含有一个复选框,【包括未连接的中间层焊盘】复 选框。选中该复选框,表示在Gerber文件中将绘出未连接的中间层的焊 盘。

状,点击要测量的两点。系统会弹出这两点之间距离的信息提示框。

图10-9 距离信息提示框

10.2 创建Gerber文件

光绘数据格式是以向量式光绘机的数据格式Gerber数据为基础发展 起来的,并对向量式光绘机的数据格式进行了扩展,兼容了HPGL(惠普 绘图仪格式),Autocad DXF和TIFF等专用和通用图形数据格式。一些CAD 和CAM开发厂商还对Gerber数据作了扩展。

Gerber数据的正式名称为Gerber RS-274格式。向量式光绘机码盘上 的每一种符号,在Gerber数据中,均有一相应的D码(D-CODE)。这样, 光绘机就能够通过D码来控制、选择码盘,绘制出相应的图形。

10.2 创建Gerber文件

AltiumDesigner18中新建PCB文件的方法

AltiumDesigner18中新建PCB文件的方法

1. 打开Altium Designer 18软件,从主菜单选择“文件”->“新建”->“项目”。

2.在“新项目”对话框中,选择“PCB工程”作为项目类型,并为项目指定一个名称,然后单击“下一步”按钮。

3.在“新PCB工程选项”对话框中,选择一个PCB的电器文件模板,这将是新PCB文件的起点。

可以选择一个预设模板,也可以创建自定义模板。

选择完成后,单击“完成”按钮。

4. Altium Designer 18将创建一个新的项目文件夹,并在文件夹中创建一个与项目名称相同的文件夹。

打开新项目文件夹,可以看到创建了一个具有项目名称的PCB文件夹。

5.双击打开PCB文件夹,在文件夹中将找到一个与项目名称相同的PCB文件,双击打开它。

9. 使用“设计”->“规则检查”命令可以检查PCB设计是否符合设计规则和约束。

如果发现错误或警告,可以通过PCB Inspector面板和错误报告对其进行修复。

12.在布局完成后,可以使用“针孔”命令和“生成针孔报告”命令检查PCB来进行针孔检查和修复。

13.完成PCB设计后,可以使用“文件”->“保存”命令保存文件。

建议定期保存PCB文件,以防止数据丢失。

14. 可以使用“文件”->“导出”命令将PCB文件导出为不同的文件格式,如Gerber文件、DXF文件等,以备将来的制造和展示。

15.使用“文件”->“打印”命令可以打印PCB设计,并选择打印选项,如大小、方向、比例等。

Altium Designer 18 课件第1章

1.3 PCB 设计的工作流程

1、方案分析 2、电路仿真 3、设计原理图组件 4、绘制原理图 5、设计器件封装 6、设计PCB 7、文档整理

图1-1 PCB成品

1.4 Altium Designer的启动

启动界面:

图1-2 Altium Designer18 启动界面

1.4 Altium Designer的启动

1.2 Altium Designer的优势及特点

4、 增强的电路分析功能 为了提高设计板的成功率,Altium Designer中的PSPICE模型、功能和变量支持以及灵活的新 配置选项,增强了混合信号模拟。在完成电路设计后,可对其进行必要的电路仿真,观察 观测点信号是否符合设计要求。从而提高的设计的成功率,并大大降低了开发周期。 5、统一的光标捕获系统 Altium Designer 的 PCB 编辑器提供了很好的栅格定义系统–通过可视栅格,捕获栅格,元件 栅格和电气栅格等都可以有效地放置设计对象到PCB文档。

首先来看看菜单命令【File】→【New】中所包含的子菜单命令, 如图1-3所示:

图1-3 【File】→【New】中包含子菜单命令

1.4 Altium Designer的启动

【Schematic】:该命令可用来创建一个新的原理图编辑文件。 【PCB】:该命令可用来创建一个新的印制电路板编辑文件。 【Project】:在项目菜单的子菜单,该命令可用来创建一个项目文件。 【Library】:该命令是用来创建一个新的器件库文件。

1.2 Altium Designer的优势及特点

6、增强的多边形铺铜管理器 Altium Designer 的多边形铺铜管理器对话框提供了更强大的功能,提供了关于管理PCB板中 所有多边形铺铜的附加功能。附加功能包括创建新的多边形铺铜,访问对话框的相关属性 和多边形铺铜删除等,全面地丰富了多边形铺铜管理器对话框的内容,并将多边形铺铜管 理整体功能带到新的高度。 7、 强大的数据共享功能 Altium Desginer完全兼容Protel系列以前版本的设计文件,并提供对Protel 99 SE下创建的DDB 和库文件的导入功能,同时它还增加了P-CSD、OrCAD等软件的设计文件和库文件的导入功 能。它的智能PDF向导则可以帮助用户把整个项目或所选定的设计文件打包成可移植的PDF 文档,这样增强了团队之间的灵活合作。

Altium Designer 18 课件第2章

__________

RESET

)则设置时应

在每个字母后面加反斜杠,表示形式“R\E\S\E\T\”,设置效果如图2-22所示。

图2-22设置带有取反符号的管脚

2.1 创建原理图元件库

2.1.3 新建法制作元器件

其它管脚按照上述方法进行设置。完成“AT89S52”所有R_3__E8__引S__E__脚T_ (未表示出 电源引脚)设置后,2.1.2 工具栏应用介绍

1.绘制原理图工具箱 在实用工具栏中包含有两个重要的工具箱,如图2-7所示。 其各个按钮功能与【放置】下拉菜单中的各项命令有相对应的关系,【放置】下 拉菜单如图2-8所示。 该工具箱包括放置直线、放置曲线、放置文本框和产生器件等功能。 2.IEEE符号工具箱 单击实用工具栏中的图标,则会弹出相应的IEEE符号工具箱,如图2-9所示,这都 是符合IEEE标准的一些图形符号。

执行【文件】→【新建】→【库】→【原理图库】命令,打开原理图库文件 编辑环境。在切换成英文输入法状态下,单击右侧工作区域,再执行快捷键【O】 →【D】命令,打开【库编辑器工作台】对话框,如图2-10所示。

该对话框与原理图编辑环境中的【文档选项】对话框的内容基本上一致,下 一章节会进行详细介绍。因此在这里只对它的个别选项的含义进行介绍。

2.1.1原理图库文件编辑环境

1.主菜单栏 通过对比可以看出,原理图库文件编辑环境中的主菜单栏与原理图编辑环境中的 主菜单栏是不同的。在原理图库文件编辑环境中,主菜单栏如图2-3所示。 2.标准工具栏 它与原理图编辑环境中的标准工具栏一样,也可以使用户完成对文件的操作,如 打印、复制、粘贴和查找等。标准工具栏如图2-4所示。

重复上述过程,放完所有的引脚,单击鼠标右键或按键盘上的【ESC】键, 就可以退出绘制状态了,绘制好的器件模型如图2-14所示。

ad18操作笔记

AD18(Altium Designer 18)是一款强大的电子设计自动化(EDA)工具,广泛应用于电路板设计、原理图绘制、FPGA设计等领域。

以下是一些AD18的操作笔记,供您参考:启动与界面熟悉:启动AD18后,您会看到一个整洁的界面。

界面主要由菜单栏、工具栏、设计窗口、属性窗口等部分组成。

您可以通过菜单栏访问各种功能,工具栏提供常用功能的快捷按钮,设计窗口用于显示和编辑设计内容,属性窗口用于查看和修改元件属性。

新建工程:选择“File” > “New” > “Project”来新建一个工程。

您需要为工程选择一个保存位置,并命名。

原理图绘制:选择元件:在右下角的“panels”中选择“components”来找到您需要的元件。

调整原理图大小:双击原理图的边缘,然后在“sheet size”中调整大小。

复制粘贴元件:您可以框选中要复制的元件,然后使用Ctrl+C和Ctrl+V进行复制粘贴。

调整元件方向:选中元件后按X键进行水平翻转,按Y键进行垂直翻转。

PCB设计:在设计完原理图后,您可以转到PCB设计阶段。

在这里,您可以布置电路板上的元件,走线,以及进行各种规则检查。

编译与生成输出文件:完成设计后,选择“Project” > “Compile”来编译工程。

如果没有错误,您可以生成输出文件,如GERBER文件,用于板厂制板。

其他实用技巧:格点调整:视图中的栅格可以帮助您对齐元件。

您可以通过“View” > “Grids”来调整格点大小。

添加辅助线:在放置元件或走线时,可以使用辅助线来帮助对齐。

通过“放置” > “绘图工具” > “线”来添加辅助线。

使用Shift+空格可以改变辅助线的角度。

使用快捷键:AD18支持大量的快捷键,熟练掌握这些快捷键可以大大提高您的设计效率。

例如,P+N可以放置网络标签,T+A+A可以启动位号编辑器。

请注意,以上只是一些基础的AD18操作笔记。

Altium Designer 18 课件第7章

画出矩形。 此时元件自动布局,如图7-18所示。 调节Room区域,使所有元件都在Room区域内,完成矩形区域内布局。

7.1自动布局

7.1.2 元器件自动布局 按照Room区域也可实现元件的自动布局,首先调节Room区域,然后

该规则的【约束】区域内,提供了两个工作层选项允许放置元器件 封装,即【顶层】和【底层】。一般过孔式元器件封装都放置在PCB的顶 层,而贴片式元器件封装即可以放置在顶层也可以放置在底层。若要求 某一面不能放置元器件封装,则可以通过该设置实现这一要求。

7.1自动布局

7.1.1 布局规则设置

图7-5 【Permitted Layers】子规则设置窗

7.1.1 布局规则设置 在窗口的左列表框中,列出了系统所提供的10类设计规则,分别是

【Electrical】(电气规则)、【Routing】(布线规则)、【SMT】(贴片 式元器件规则)、【Mask】(屏蔽层规则)、【Plane】(内层规则)、 【Testpoint】(测试点规则)、【Manufacturing】(制板规则)、【High Speed】(高频电路规则)、【Placement】(布局规则)、【Signal Integrity】(信号分析规则)

7.2手动布局

7.2.1 元器件的排列 执行【编辑】→【对齐】命令,系

统会弹出【对齐】命令菜单,如图7-9 所示。系统还提供了排列工具栏,在应 用工具栏的第二个图标。

图7-9 【对齐】命令菜单

7.2手动布局

7.2.1 元器件的排列 执行【编辑】→【对齐】→【定位

器件文本】,系统则打开如图7-10所示 的【器件文本位置】对话框。

Altium Designer18教程步骤方法

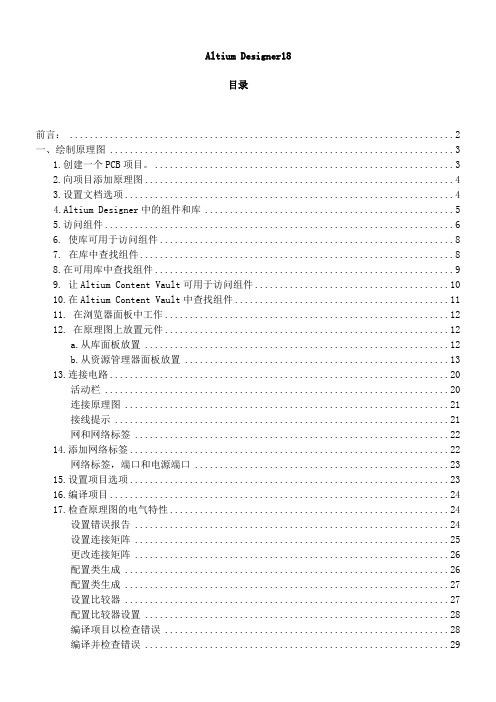

Altium Designer18目录前言: (2)一、绘制原理图 (3)1.创建一个PCB项目。

(3)2.向项目添加原理图 (4)3.设置文档选项 (4)4.Altium Designer中的组件和库 (5)5.访问组件 (6)6. 使库可用于访问组件 (8)7. 在库中查找组件 (8)8.在可用库中查找组件 (9)9. 让Altium Content Vault可用于访问组件 (10)10.在Altium Content Vault中查找组件 (11)11. 在浏览器面板中工作 (12)12. 在原理图上放置元件 (12)a.从库面板放置 (12)b.从资源管理器面板放置 (13)13.连接电路 (20)活动栏 (20)连接原理图 (21)接线提示 (21)网和网络标签 (22)14.添加网络标签 (22)网络标签,端口和电源端口 (23)15.设置项目选项 (23)16.编译项目 (24)17.检查原理图的电气特性 (24)设置错误报告 (24)设置连接矩阵 (25)更改连接矩阵 (26)配置类生成 (26)配置类生成 (27)设置比较器 (27)配置比较器设置 (28)编译项目以检查错误 (28)编译并检查错误 (29)二、创建一个新的PCB (30)添加新PCB到项目 (31)配置板的形状和位置 (31)设置原点和网格 (32)重新定义板的形状 (33)转移设计 (35)将设计从原理图捕获转移到PCB布局 (36)设置PCB工作区 (36)配置图层的显示 (37)图层提示 (39)配置图层可见性 (39)物理层和层堆栈管理器 (39)配置板层堆栈 (40)合适的网格设置 (41)设置设计规则 (44)交互布线电路板 (56)准备交互式走线 (56)验证您的电路板设计 (67)配置显示规则违规 (67)准备运行设计规则检查(DRC) (69)配置规则检查器 (69)•如果电路板上有任何孔,则还必须使用相同的单位、分辨率和film(菲林、胶片)设置的位置生成NC钻孔文件。

AltiumDesigner18教程步骤方法

AltiumDesigner18教程步骤方法Altium Designer18目录前言: (2)一、绘制原理图 (3)1.创建一个PCB项目。

(3)2.向项目添加原理图 (4)3.设置文档选项 (4)4.Altium Designer中的组件和库 (5)5.访问组件 (6)6. 使库可用于访问组件 (8)7. 在库中查找组件 (8)8.在可用库中查找组件 (9)9. 让Altium Content Vault可用于访问组件 (10)10.在Altium Content Vault中查找组件 (11)11. 在浏览器面板中工作 (12)12. 在原理图上放置元件 (12)a.从库面板放置 (12)b.从资源管理器面板放置 (13)13.连接电路 (20)活动栏 (20)连接原理图 (21)接线提示 (21)网和网络标签 (22)14.添加网络标签 (22)网络标签,端口和电源端口 (23)15.设置项目选项 (23)16.编译项目 (24)17.检查原理图的电气特性 (24)设置错误报告 (24)设置连接矩阵 (25)更改连接矩阵 (26)配置类生成 (26)配置类生成 (27)设置比较器 (27)配置比较器设置 (28)编译项目以检查错误 (28)编译并检查错误 (29)二、创建一个新的PCB (30)添加新PCB到项目 (31)配置板的形状和位置 (31)设置原点和网格 (32)重新定义板的形状 (33)转移设计 (35)将设计从原理图捕获转移到PCB布局 (36) 设置PCB工作区 (36)配置图层的显示 (37)图层提示 (39)配置图层可见性 (39)物理层和层堆栈管理器 (39)配置板层堆栈 (40)合适的网格设置 (41)设置设计规则 (44)交互布线电路板 (56)准备交互式走线 (56)验证您的电路板设计 (67)配置显示规则违规 (67)准备运行设计规则检查(DRC) (69)配置规则检查器 (69)如果电路板上有任何孔,则还必须使用相同的单位、分辨率和film(菲林、胶片)设置的位置生成NC钻孔文件。

《Altium Designer 18 印制电路板设计实用教程》教学课件(全)

1060、Radeon RX 470 分辨率为2560x1440(或更好)的双显示器

二、软件运行

单击Windows的【开始】按钮,显示开始菜单,运行Altium Designer 18

2. 放置引脚 执行Place→Pin菜单,并按<Tab> 修改属性。注 意:元件引脚只有一端有电连接性,即带有小“+”标志的 一端,该端必须朝向元器件的外面。

注意:元器件从坐标原点开始做起,一般放在第四象限上。

第5章 封装方式库的制作

本章要点

封装方式库的制作与维护 手工制作封装方式的过程 利用向导制作封装方式的过程 焊盘的属性设置

经为用户准备好大量的元器件,但是这些 库文件存放在硬盘上,是不能直接使用的, 用户需要哪个库,必须先加载它,也就是 将它调入内存中,成为“活”的库。

成品库的路径为:软件安装时指定的共 享文件文件夹下的Library文件夹内 。

集成库的安装与使用

二、成品库的加载

1、将光标移动到图纸右侧Libraries面板标签上,弹出 Libraies面板。 2、单击面板顶部的【Libraries...】按钮,显示库安装对话 框,单击Installed选项卡,再单击对话框右下角的 【Install...】按钮,打开库文件选择对话框,安装所需要的 库。

印制电路板的种类很多,按其结构可分为单面印制电路板、双面印制电路 板、多层印制电路板和软性印制电路板。

3、元器件实物、元器件符号和元器件封装方式识别 如图

PCB编辑器主界面

PCB 编辑器界面 和Schematic编辑 器界面结构基本 相似,但是细节 却不一样,切换 到不同的编辑器, 相应的菜单,工 具条等都会相应 的改变。

Altium Designer 18 课件第5章

5.1 印刷电路板的构成及其基本功能

5.1.2 印刷电路板的功能——提供机械支撑 电路板为集成电路等各种电子元器件固定、装配提供了机械支撑。

图5-2 印刷电路板为元器件提供机械支撑

5.1 印刷电路板的构成及其基本功能

5.1.3 印刷电路板的功能——实现电气连接或电绝缘 电路板实现了集成电路等各种电子元器件之间的布线和电气连接。 印刷电路板也实现了集成电路等各种电子元器件之间的电绝缘。

内容提要

印制电路的基板是由绝缘隔热、并不易弯曲的材质制作而成。在 表面可以看到的细小线路是铜箔,原本铜箔是覆盖在整个板子上的, 而在制造过程中部分被蚀刻处理掉,留下来的部分就变成网状的细小 线路了,这些线路被称作导线或称布线,并用来提供PCB上零件的电 路连接。

印制电路板几乎应用到各种电子设备中,如电子玩具、手机、计 算机等,只要有集成电路等电子元器件,都会使用印制板。

5.4 PCB板层

5.4.1 PCB分类 2. 双面板(Double-Sided Boards) 这种电路板的两面都有布线。不过要用上两面的导线,必须要在两

面间有适当的电路连接才行。这种电路间的“桥梁”叫做导孔(via)。 导孔是在PCB上,充满或涂上金属的小洞,它可以与两面的导线相连接。 因为双面板的面积比单面板大了一倍,而且因为布线可以互相交错(可 以绕到另一面),它更适合用在比单面板更复杂的电路上。双面板实例 如图5-8所示。

5.3 PCB中的名称定义

5.3.3 边接头(俗称金手指) 如果要将两块PCB相互连结,一般都会用到俗称「金手指」的边接头

(edge connector)。金手指上包含了许多裸露的铜垫,这些铜垫事实上 也是PCB布线的一部份。通常连接时,我们将其中一片PCB上的金手指插 进另一片PCB上合适的插槽上(一般叫做扩充槽Slot)。在计算机中,像 是显示卡,声卡或是其它类似的界面卡,都是借着金手指来与主机板连 接的。边接头如图5-7所示。

Altium Designer 18 课件第6章

6.6 载入网络表

6.6.1 准备设计转换 (1)对项目中所绘制的电路原理图进行编译检查,验证设计,确保

电气连接的正确性和元器件封装的正确性。 (2)确认与电路原理图和PCB文件相关联的所有元器件库均已加载,

保证原理图文件中所指定的封装形式在可用库文件中都能找到并可以使 用。PCB元器件库的加载和原理图元器件库的加载方法完全相同。

6.6 载入网络表

6.6.2 网络与元器件封装的装入 c.在原理图编辑环境中,执行【设计】→【Update PCB Document

PCB1.PcbDoc】命令。打开【工程更改顺序】对话框。 d.单击【验证变更】按钮,在【状态】区域中的【检测】栏中将会

显示检查的结果,出现绿色的对号标志,表明对网络及元器件封装的检 查是正确的,变化有效。当出现红色的叉号标志,表明对网络及元器件 封装检查是错误的,变化无效。

(a)焊盘1的封装数值

(b)焊盘2的封住数值

图6-12 DO-41封装具体数据值

6.4 规划电路板及参数设置

对于要设计的电子产品,设计人员首先需要确定其电路板的尺寸。 因此,电路板的规划也成为PCB制板中需要首先解决的问题。

电路板规划也就是确定电路板的板边,并且确定电路板的电气边界。 规划PCB板有两种方法:一种是手动规划电路板,另一种是利用Altium Designer的向导,这种方法前面已经介绍过了就不再重复介绍。

实现Altium Designer系统中所打开的窗口之间的相互切换。导航工具栏, 如图6-6所示。

图6-6 导航工具栏

6.2 PCB设计环境

6、PCB编辑窗口 编辑窗口即进行PCB设计的工作平台,用于进行元器件的布局、布线

有关的操作。PCB设计主要在这里完成。 7、板层标签 用于切换PCB工作的层面,所选中的板层的颜色将显示在最前端,如

Altium Designer 18 课件第8章

8.1布线的基本规则

PCB板尽量使用45°折线,而不用90°折线布线,以减小高频信号对外 的发射与耦合。

作为电路的输入及输出用的印制导线应尽量避免相邻平行,以免发 生回流,在这些导线之间最好加接地线。

当板面布线疏密差别大时,应以网状铜箔填充,网格大于8mil (0.2mm)。

贴片焊盘上不能有通孔,以免焊膏流失造成元件虚焊。 重要信号线不准从插座间穿过。 卧装电阻、电感(插件)、电解电容等元件的下方避免布过孔,以

Altium Designer软件中【Clearance】子规则规定了板上不同网络的走 线、焊盘和过孔等之间必须保持的距离。在单面板和双面板的设计中, 首选值为10-12mil;4层及以上的PCB首选值为7-8mil;最大安全间距一般 没有限制。

8.2布线前规则的设置

8.2.1 电气规则(Electrical)设置

图8-5【Modified Polygon】子规则设置窗口

8.2布线前规则的设置

8.2.2 布线规则(Routing)设置 执行【设计】→【规则】命令,打开【PCB规则及约束编辑器】对话

框,在该对话框左边的规则列表栏中,单击【Routing】前面的加号,可 以看到需要设置的电气子规则有8项。

这8项子规则分别是【Width】(布线宽度)子规则、【Routing Topology】(布线拓扑逻辑)子规则、【Routing Priority】(布线优先级) 子规则、【Routing Layerners】(布 线拐角)子规则、【Routing Via Style】(布线过孔)子规则、【Fanout Control】(扇出布线)子规则、【Differential Pairs Routing】(差分对布 线)子规则。

8.2布线前规则的设置

Altium Designer 18 课件第8章

说明 在布线时连接所有节点的连线最短。 连接所有节点后,在水平方向连线最短。 连接所有节点后,在垂直方向连线最短。

使用链式连通法则,从一点到另一点连通所有的节点, 并使连线最短。

选择一个Source(源点),以它为中心向左右连通所有 的节点,并使连线最短。

选择一个源点,将所有的中间节点数目平均分成组,所 有的组都连接在源点上,并使连线最短。

Altium Designer软件中【Clearance】子规则规定了板上不同网络的走 线、焊盘和过孔等之间必须保持的距离。在单面板和双面板的设计中, 首选值为10-12mil;4层及以上的PCB首选值为7-8mil;最大安全间距一般 没有限制。

8.2布线前规则的设置

8.2.1 电气规则(Electrical)设置

免波峰焊后孔与元件壳体短路。

8.1布线的基本规则

手工布线时,先布电源线,再布地线,且电源线应尽量在同一层面。 信号线不能出现回环走线,如果不得不出现环路,要尽量让环路小。 走线通过两个焊盘之间而不与它们连通的时候,应该与它们保持最

大而相等的间距。 走线与导线之间的距离也应当均匀、相等并且保持最大。 导线与焊盘连接处的过渡要圆滑,避免出现小尖角。 当焊盘之间的中心间距小于一个焊盘的外径时,焊盘之间的连接导

8.2布线前规则的设置

8.2.1 电气规则(Electrical)设置 电气规则的设置是针对具有电气特性的对象,用于系统的DRC电气校

验。当布线过程中违反电气特性规则时,DRC校验器将自动报警,提示用 户修改布线。执行【设计】→【规则】命令,打开【PCB规则及约束编辑 器】对话框,在该对话框左边的规则列表栏中,单击【Electrical】前面的 加号,可以看到需要设置的电气子规则有5项。

Altium Designer 18 课件第9章

9.4 铺铜

图9-12 电路以圆角形式铺铜

图9-13 八角形铺铜

9.4 铺铜

9.4.2 删除铺铜 在PCB编辑界面中的板层标签栏中,选择层面为【Top Layer】,在铺

铜区域单击鼠标,选中铺在顶层敷铜。然后拖动鼠标,将顶层铺铜拖到 电路之外。

然后单击【剪切】工具或按下【Delete】键将顶层铺铜删除Biblioteka 同理, 按照上述操作也可删除底层铺铜。

(1)【Net】:用于设定铺铜所要连接的网络,可以在下拉菜单中 进行选择。

(2)【Properties】区域:用于设定敷铜所在工作层面、铺铜区域的 命名等设置。

(3)【Fill Mode】:用于设置敷铜模式等设置,有三个标签页用来 设置填充模式。

9.4 铺铜

【Solid(Copper Regions)】:选中该单选按钮,表示铺铜区域内为 全铜铺设。

Altium Designer 18 课件

第九章 PCB后续操作

CONTENTS

1 添加测试点 2 补泪滴 3 包地 4 铺铜

5 添加过孔 6 PCB的其他功能 7 3D环境下精确测量

9.1 添加测试点

9.1.1 设置测试点设计规则 为了便于仪器测试电路板,用户可在电路中设置测试点。执行【设计】

9.1 添加测试点

9.1.1 设置测试点设计规则 2、【Testpoint Usage】(测试点使用)子规则 【Testpoint Usage】包括【Fabrication Testpoint Usage】(制造测试点

使用)子规则和【Assembly Testpoint Usage】(装配测试点使用)子规则, 用于设置测试点的有效性。包含三个选项,其意义如下所述。 【必需的】选项:表示适用范围内的必须生成测试点。 【禁止的】选项:表示适用范围内的每一条网络走线都不可以生成 测试点; 【无所谓】选项:表示适用范围内的网络走线可以生成测试点,也 可以不生成测试点。

Altium Designer 18 课件第7章

7.1自动布局

7.1.1 布局规则设置

图7-5 【Permitted Layers】子规则设置窗

Altium Designer 18 课件

第七章 元件布局

CONTENTS

1 自动布局 2 手动布局 3 PCB布局注意事项

内容提要

装入网络表和元件封装后,用户需要将元件封装放入工作区,这 就是对元件封装进行布局。在PCB设计中,布局是一个重要的环节。 布局的好坏将直接影响布线的效果,因此可以认为,合理的布局是 PCB设计成功的第一步。

7.1自动布局

7.1.1 布局规则设置 5.【Nets To Ignore】(忽略网络)子规则 【Nets To Ignore】子规则用于设置在采用【成群的放置项】方式执

行元件自动布局时可以忽略的一些网络,在一定程度上提高了自动布局 的质量和效率。执行菜单命令【新规则】,新建一个【Permitted Layers】 子规则,单击新建的规则,打开设置窗口。

布局的方式分为2种,即自动布局和手动布局。

内容提要

自动布局,是指设计人员布局前先设定好设计规则,系统自动在 PCB上进行元器件的布局,这种方法效率较高,布局结构比较优化, 但缺乏一定的布局合理性,所以在自动布局完成后,需要进行一定的 手工调整。以达到设计的要求。

手动布局,是指设计者手工在PCB上进行元器件的布局,包括移动 、排列元器件。这种布局结果一般比较合理和实用,但效率比较低, 完成一块PCB板布局的时间比较长。所以一般采用这两种方法相结合 的方式进行PCB的设计。

Altium Designer 18 课件第3章

3.2 对原理图的操作

3.2.3原理图纸的设置

为了更好地完成电路原理图的绘制,并符合绘制的要求,要对原理图纸进 行相应的设置,包括图纸参数设置和图纸设计信息设置。

1.图纸参数设置 进入了电路原理图编辑环境后,系统会给出一个默认的图纸相关参数,但 在多数情况下,这些默认的参数不适合用户的要求,如图纸的尺寸大小。用户应 当根据所设计的电路复杂度来对图纸的相关参数进行重新的设置,为设计创造最 优的环境。 下面就给出如何改变新建原理图图纸的大小、方向、标题栏、颜色和栅格 大小等参数的方法。 在新建的原理图文件中,执行“快捷键O”→【文档选项】菜单命令。

Altium Designer 18 课件

第三章 绘制电路原理图

CONTENTS

1 Altium Designer电路 原理图绘制预备知识

2 对原理图的操作 3 对元器件库的操作 4 对元器件的操作

5 绘制电路原理图

6 电路原理图绘制的相关技巧

7 编译项目及查错 8 生成原理图网络表文件 9 生成和输出各种报表和文件

3.2 对原理图的操作

3.2.1创建原理图文件

图3-2 PCB项目创建

图3-3 原理图文件的添加

3.2 对原理图的操作

3.2.2原理图编辑环境

原理图编辑环境主要由:主菜单栏、标准工具栏、配线工具栏、实用工具 栏、原理图编辑窗口、【元器件库】面板、仿真工具栏和面板控制中心几大部分 组成。了解这些部分的用途,可以更有效的完成原理图的绘制。第一次使用 AD18软件进行原理图绘制时,上述各工具栏是默认隐藏的,为了做图快速方便, 在绘图前需要将这些工具栏显示在编辑环境中。执行【视图】→【Toolbars】, 将需要的“布线”、“应用工具”、“原理图标准”勾选。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LED2_SL GREEN

LED1_SL RED

GND

第4页

共 17 页

DB_MotherBoardConnectors

HARD JTAG SOFT TCK TDI TDO TMS TCK TDI TDO TMS FPGA_TCK FPGA_TDI FPGA_TDO FPGA_TMS NEXUS_TCK NEXUS_TDI NEXUS_TDO NEXUS_TMS ONE_WIRE_DB_PB ONE_WIRE_PIO1 ONE_WIRE_DBID BUZZER DAU_RESET_SW SLEEP_N SW5 MH2 SW SW8 DIP IO36 USERIO LED8 USER_LED PBIO EXT_A PBIO EXT_B PBIO EXT_C D[49..0] EXTEND_C[49..0] D[49..0] EXTEND_B[49..0] D[49..0] EXTEND_A[49..0] L[7..0] USER_LED[7..0] IO[35..0] IO[35..0] GND EXTEND_A0 EXTEND_A1 EXTEND_A2 EXTEND_A3 EXTEND_A4 EXTEND_A5 EXTEND_A6 EXTEND_A7 EXTEND_A8 EXTEND_A9 EXTEND_A10 EXTEND_A11 EXTEND_A12 EXTEND_A13 EXTEND_A14 EXTEND_A15 EXTEND_A16 EXTEND_A17 EXTEND_A18 EXTEND_A19 EXTEND_A20 EXTEND_A21 EXTEND_A22 EXTEND_A23 EXTEND_A24 EXTEND_A25 EXTEND_A26 EXTEND_A27 EXTEND_A28 EXTEND_A29 EXTEND_A30 EXTEND_A31 EXTEND_A32 EXTEND_A33 EXTEND_A34 EXTEND_A35 EXTEND_A36 EXTEND_A37 EXTEND_A38 EXTEND_A39 EXTEND_A40 EXTEND_A41 EXTEND_A42 EXTEND_A43 EXTEND_A44 EXTEND_A45 EXTEND_A46 EXTEND_A47 EXTEND_A48 EXTEND_A49 GND MH1 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79 81 83 85 87 89 91 93 95 97 99 MH3 D[7..0] DIP[7..0] H DR_L D[4..0] SW[4..0] ONE_WIRE_DB_PB ONE_WIRE_PIO1 ONE_WIRE_DBID BUZZER DAU_RESET_SW SLEEP_N GND

第2页

共 17 页

DB_Common

Top Level Schematic For Daughter Board Design Both FPGA-Only and FPGA + MCU This Device Sheet is the same for all designs. It relies on being instantiated in a project that contains a device-specific sheet named DEVICES.SchDoc .

MEM

BUS

U_CommonM emory_Termination NB2_CommonMemory_Termination MEM

DIP USER_LED USERIO JTAG I2C

U_SRAM 6R4016V1D-TC10T_256K _K x16 SRAM_256Kx16_TSOP44 SRAM SRAM1

SPI_CLK SPI_DIN SPI_DOUT SPI_MODE SPI_SEL DAU_TFT_RED[4..0] DAU_TFT_GREEN[5..0] DAU_TFT_BLUE[4..0] DAU_TFT_M DAU_TFT_POL DAU_TFT_CL[3..1] DAU_TFT_STV DAU_TFT_STH DAU_TFT_DISP_ON DAU_TFT_BLIGHT DAU_TFT_IRQ DAU_TFT_MUX

KEYBOARD MOUSE RS232 SPI

U_SRAM 6R4016V1D-TC10T_256K _K x16 SRAM_256Kx16_TSOP44 SRAM SRAM2

CLOCKS PROGRAM TFT EXT_A EXT_B EXT_C

U_DaughterBoard_LEDS DB_LEDS STATUS_LED STATUS_LED STATUS_LED

FPGA_CCLK FPGA_DIN FPGA_DONE FPGA_ID[3..0] FPGA_INIT FPGA_M[2..0] FPGA_PROG_CLK FPGA_PROG_PWR_ON FPGA_PROGRAM FPGA_CLK REF_CLK FPGA_CLK1 CAN_TXD CAN_RXD SCL SDA RS232_TX RS232_RTS RS232_RX RS232_CTS KBDATA KBCLOCK MOUSEDATA MOUSECLOCK

MH2

CLOCKS

MH4

GND

CAN

MOLEX - 54075-1009

RS232

Red Connections are locked for NB1 compatibility. They are hardwired on the NB1 and therefore can NOT be changed. Green connections are I/O pins connected to NB1 compatible PCB resources on the mother board. These can be changed. Blue connections are connected to the New NB2 compatible resources on the motherboard. These can be changed.

TFT

PROGRAM

FPGA_CLK REF_CLK USER_LED0 USER_LED1 USER_LED2 USER_LED3 USER_LED4 USER_LED5 USER_LED6 USER_LED7 DIP0 DIP1 DIP2 DIP3 DIP4 DIP5 DIP6 DIP7 DAU_RESET_SW BUZZER SW0 SW1 SW2 SW3 SW4 DAU_TFT_RED0 DAU_TFT_RED1 DAU_TFT_RED2 DAU_TFT_RED3 DAU_TFT_RED4 DAU_TFT_BLUE0 DAU_TFT_BLUE1 DAU_TFT_BLUE2 DAU_TFT_BLUE3 DAU_TFT_BLUE4 DAU_TFT_GREEN0 DAU_TFT_GREEN1 DAU_TFT_GREEN2 DAU_TFT_GREEN3 DAU_TFT_GREEN4 DAU_TFT_GREEN5 DAU_TFT_STV DAU_TFT_STH DAU_TFT_CL1 DAU_TFT_CL2 DAU_TFT_CL3

ONE_WIRE_DB_PB ONE_WIRE_DBID ONE_WIRE_PIO1

第3页

共 17 页

DB_LEDS

STATUS LED

3V3 C1_SL 0.1uF 16V GND R2_SL 270R 1% 3V3

POWER LED

3V3

R1_SL 270R 1% LED_PWR

U1_SL SN74LVC1G04DBV STATUS_LED 1 2 3 GND NC A GND VCC Y 5 4 LED_PGM

GND

KEYBOARD

MOUSE

第5页

1 SDA 3 SCL 5 IO0 7 9 IO1 IO2 11 IO3 13 IO4 15 IO5 17 IO6 19 21 IO7 23 IO8 25 IO9 27 IO10 29 IO11 31 IO12 33 IO13 35 IO14 37 IO15 39 IO16 41 IO17 43 IO18 45 IO19 47 IO20 49 IO21 51 IO22 53 IO23 55 IO24 57 IO25 59 IO26 61 IO27 63 IO28 65 IO29 67 IO30 69 IO31 71 IO32 73 IO33 IO34 75 IO35 77 ONE_WIRE_DB_PB79 DAU_TFT_IRQ 81 83 DAU_TFT_POL DAU_TFT_MUX 85 87 DAU_TFT_M DAU_TFT_DISP_ON 89 DAU_TFT_BLIGHT91 93 95 97 99

U_M emory_CommonBus_DaughterBoard NB2_CommonMemory

U_DEVICES DEVICES.SchDoc DAU_RESET_SW SLEEP_N SW BUZZER CAN

U_M otherBoardConnectors DB_MotherBoardConnectors DAU_RESET_SW SLEEP_N SW BUZZER CAN DIP USER_LED USERIO JTAG I2C KEYBOARD MOUSE RS232 SPI CLOCKS PROGRAM TFT EXT_A EXT_B EXT_C ONE_WIRE_DB_PB ONE_WIRE_DBID ONE_WIRE_PIO1

DB30 Xilinx Spartan-3 FGG6766

第一部分