两类DSP芯片的引导过程分析

用DSP软件编程实现的引导装载系统分析

用DSP软件编程实现的引导装载系统分析引导装载系统(Bootloader)是计算机系统启动过程中的一个重要组成部分,负责加载操作系统或其他应用程序到内存,并进行初始化和启动。

DSP(Digital Signal Processor,数字信号处理器)是专门用于高速数值计算和信号处理的微处理器。

本文将介绍使用DSP软件编程实现的引导装载系统分析。

引导装载系统主要由两个部分组成:引导程序和加载程序。

引导程序是计算机系统启动时最先执行的程序,其大小通常较小,位于系统的ROM或Flash存储器中,并负责初始化硬件设备和加载加载程序。

加载程序的主要功能是将操作系统或其他应用程序从外部存储器(如硬盘、光盘或网络)加载到内存中,并跳转到相应程序的入口点。

1. 硬件初始化:引导程序需要初始化DSP芯片及其外设,包括中断控制器、时钟控制器、UART通信接口等。

这些初始化操作通常通过特定的寄存器操作完成。

2. 外部存储器访问:加载程序需要能够从外部存储器读取数据。

在DSP上,可以通过SPI(Serial Peripheral Interface)或其他通信接口与外部存储器进行数据交互。

通过编程实现这些接口的读取和写入操作,就可以实现外部存储器的访问。

3. 文件系统支持:加载程序需要支持特定的文件系统格式,如FAT32或NTFS等。

通过解析文件系统的目录结构和文件分配表,加载程序可以找到操作系统或应用程序的存储位置,并读取相应数据。

4. 加载和运行应用程序:加载程序需要将操作系统或应用程序的可执行文件从外部存储器加载到内存中。

具体操作包括读取文件数据、解析文件头信息、分配内存空间,并将文件数据拷贝到相应内存地址。

5. 跳转至应用程序入口点:加载程序将应用程序加载到内存后,需要跳转到应用程序的入口点,使其开始执行。

通过以上步骤,可以实现DSP软件编程中的引导装载系统。

在实际应用中,还需要考虑异常处理、错误检测和恢复等方面的设计。

dsp芯片的原理与应用

DSP芯片的原理与应用1. DSP芯片的概述DSP芯片(Digital Signal Processor,数字信号处理器)是一种专门用于数字信号处理的芯片。

它通过对数字信号的处理来实现各种信号处理算法,如音频信号处理、图像处理、视频编解码等。

DSP芯片具有高速计算和高效能耗比的特点,在许多领域都得到了广泛的应用。

2. DSP芯片的原理DSP芯片的核心部分是一组高性能的数学运算单元,主要包括算术逻辑单元(ALU)、寄存器文件和累加器等。

这些数学运算单元可以对数字信号进行加法、减法、乘法、除法等复杂的数学运算,并实现快速的乘积累加(MAC)操作。

此外,DSP芯片还配备了高速的存储器,用于存储待处理的数据和运算结果。

3. DSP芯片的应用领域3.1 音频信号处理DSP芯片在音频信号处理方面应用广泛。

它可以通过数字滤波器对音频信号进行滤波处理,实现均衡器、消噪器、混响器等音效效果。

另外,DSP芯片还可以对音频信号进行编解码,实现音频压缩和解压缩。

3.2 图像处理DSP芯片在图像处理方面也有很多应用。

它可以对图像进行数字滤波、边缘检测和图像增强等处理,用于医学图像的分析、工业检测和图像识别等领域。

3.3 视频编解码在视频处理领域,DSP芯片可以实现视频的压缩和解压缩。

它可以对视频信号进行编码,降低视频数据的传输带宽和存储空间,提高视频传输的效率。

同时,DSP芯片还可以对编码后的视频进行解码,恢复原始的视频信号。

3.4 通信系统DSP芯片广泛应用于各种通信系统中。

它可以实现数字调制解调、误码纠正、信道均衡和信号编码等功能,用于提高通信系统的性能和效率。

此外,DSP芯片还可以实现语音信号的压缩和解压缩,用于语音通信系统和语音识别系统等领域。

3.5 控制系统在控制系统中,DSP芯片可以实现数字控制、数字滤波和模拟信号的转换等功能。

它可以对控制信号进行数字化处理,提高控制系统的精度和稳定性。

此外,DSP芯片还可以与传感器和执行器进行接口,实现实时的控制和反馈。

TMS320C641X 系列DSP引导方法研究

TMS320C641X 系列DSP引导方法研究摘要:在进行DSP 产品化设计时, Bo otLOAder 是一项关键技术。

为了更好地解决数字信号处理器应用程序的加载问题,以TI 公司641X 系列DSP 为例,详细论述了DSP 的两种引导方法:ROM 引导和主机H PI 引导,包括二次代码编写、存储器空间分配、引导表生成和. hex 文件的烧写。

经某星载接收机系统实测验证,所述方法同时适用于BIOS 和NoBIOS 两种系统,具有可靠性高、可行性强的优点。

0 引言近年来,以数字信号处理器( DSP) 为基础的通用信号处理模块的研制受到人们的重视,它的研制成功满足了信号处理系统实时性和通用性的要求,被广泛应用于雷达、通信、电子测量和图像等领域。

进行DSP 开发,最终的目标产品要脱离仿真器运行,在上电后可自行启动程序代码,这就需要一个能在断电后保存程序的存储器。

对于C641X 系列的DSP,内部没有供用户使用的非易失性存储器,只能将程序代码存放在外部的非易失性存储器中。

因此,通常需要在上电复位时,将存储在外部速度较慢的存储器的程序代码搬移到片内高速RAM 中,这个过程被称为Bo otLo ader 。

因此,在设计通用信号处理模块前,有必要研究DSP 的多种引导方式。

1 C641X BootLoader 方式和过程C641X 有三种Boot 模式:不引导、ROM 引导和主机引导。

第一种方式只能用于仿真运行; 第二种方式利用片内固化的Boo tLoader 程序通过EDMA 通道,从EMIF 的CE1 空间拷贝1 KB 数据到地址0 处,然后从地址0 处开始执行。

这种方式只需一片非易失性存储器,实现较为简单; 第三种方式是在DSP 内核处于复位时,由外部主机通过主机接口实现程序引导。

这种方法虽然复杂度较前者高,但也被广泛应用于一些具有抗空间辐射效应的星载平台中。

2 ROM BOOT 实现前面提到这种方式是在DSP 上电复位后,由片内固化的Bo otLo ader 代码采用EDMA 方式从CE1 空间复制1 KB 代码到地址0 处。

干货 DSP技术芯片C2000上电引导模式解析

干货DSP技术芯片C2000上电引导模式解析

DSP技术目前已经被广泛的应用在了集成芯片研发过程中,这一类新产品的出现,为工程师的电路设计工作带来了极大的革新和帮助。

C2000作为一种比较常见的DSP技术集成芯片产品,应用范围广泛,但在使用过程中却常常会出现仿真运行正常但单机程序跑不起来的情况,今天我们将会就这种问题进行详细解析。

其实就DSP集成芯片C2000而言,之所以会在调试时出现单机程序无法运行的情况,其根本原因还是因为工程师没有正确的完成C2000的引导模式设置。

以C2000Piccolo系列的引导模式为例,尽管这一系列的芯片与delfino稍微有点区别,而concerto系列的芯片在引导模式设置方面更复杂。

但是Piccolo系列是最基础的DSP集成芯片类型,理解了Piccolo的引导原理对我们在日后工作中使用其余两个系列的芯片有非常大的帮助。

首先我们需要了解的,是C2000DSP技术集成芯片的代码执行程序运行问题。

下图中,图1是C2000的芯片复位流程图,从图中我们可以看到,当芯片在接收到一个复位信号后,会到0x3FFFC0去复位向量,该复位向量跳到BootROM0x3FF75C中去执行bootloader的程序,这里主要有进入引导和选择启动模式,以及一些外设引导的函数。

选择启动模式根据芯片的硬件或软件设置来判断芯片该去哪里寻找程序入口,其直接目的是如何找到main,然后执行应用程序。

图1 DSP技术芯片C2000的复位流程图

在了解了这种C2000集成芯片的复位流程之后,接下来我们再来看一下这。

TMS320VC5402DSP的并行引导加载

摘要在54’x 系列DSP 的应用设计中,DSP 的运行速度是衡量系统性能的一项重要指标.要达到预期的运行速度,就要给DSP系统的程序空间设计一个高速程序存储空间.引导是将程序存储在低速但停电数据不丢失的器件中,运行时使用存取速度快的RAM作为程序运行存储体,这样既可保证停电时数据不丢失又可进行高速数据存取.本文介绍TMS320VC5402并行引导方案的设计关键词:TMS320VC5402 FLASH BootLoader目录1、主要芯片介绍 (2)1.1 TMS320VC5402简介 (2)1.2 闪存SST39VF400A简介 (3)2、C5402片内Bootloader的引导原理 (3)2.1 C5402并行引导模式 (4)2.2 Bootloader的引导原理 (4)3、系统硬件电路的设计 (6)4、系统软件设计 (7)4.1测试程序设计 (7)4.2 用户初始化程序设计 (7)4.3 引导表的建立及引导装载过程 (9)5、课程设计心得 (12)参考文献 (14)1、主要芯片介绍1.1 TMS320VC5402简介TMS320VC5402(以下简称C5402)是德州仪器公司(TI)1999年10月推出的性价比极高(目标价格仅为5美元)的定点数字信号处理器(DSP)。

C5402主要特点如下[1]:·操作速率达100MIPS;·具有先进的多总线结构,三条16位数据存储器总线和一条程序存储器总线;·40位算术逻辑单元(ALU),包括一个40位桶形移位器和两个40位累加器;·一个17×17乘法器和一个40位专用加法器,允许16位带/不带符号的乘法;·整合维特比加速器,用于提高维特比编译码的速度;·单周期正规化及指数译码;·8个辅助寄存器及一个软件栈,允许使用业界最先进的定点DSP C 语言编译器;·数据/程序寻址空间1M×16bit,内置4K×16bit ROM和16K×16bit RAM;·内置可编程等待状态发生器、锁相环(PLL)时钟产生器、两个多通道缓冲串行口、一个8位并行与外部处理器通信的HPI口、2个16位定时器以及6通道DMA控制器;·低功耗,工作电源有3V和1.8V(内核),特别适合电池供电设备。

最新-两类DSP芯片的引导过程分析 精品

两类DSP芯片的引导过程分析摘要详细分析了公司32040和3205402两类芯片的系统引导特点。

在了解机理的基础上,叙述了工程设计中创建系统引导表的具体步骤,给出了创建步骤中所需的键接文件范例,并进行了说明。

关键词320403205402系统引导引导表目前,芯片正逐渐应用到电子设计中,其中应用最广泛的是公司生产的系列产品。

笔者在工程项目的开发中,对32040和3205402以下简称40和5402进行了系统的研究,并成功的实现了的脱机运行。

本文希望通过对40和5402两种芯片系统引导的描述使大家了解设计系列引导的步骤,能够利用设计自己的设备。

140和5402的系统引导机理公司的每一种产品,都为用户设计了多种系统的引导方式,如串口、并行加载、加载等。

40和5402的引导方式如表1所示。

表140和5402的引导方式405402程序执行地址32101003000001101口引导模式由2引脚识别2400000001011串行8位引导模式33600000001001并行引导模式4800000000111标准8位串行口1500000000101标准16位串行口2600000000011口引导模式70001口引导模式由入口点进行识别8通讯口引导方式1111在工程中,使用最广泛的并行加载方式。

它又分为8位数据宽度和16位数据宽度两种,笔者采用的是8位数据宽度的并行加载方式。

需要注意的是40的数据总线宽度是32位,引导表中数据存放的原则是低字节在低地址。

5402的数据宽度是16位,引导表中数据的存放原则是高字节在低地址。

1140的并行引导模式40加电时,芯片塞满到引脚为高电平,进入微处理器模式。

再检测3~0引脚电平,决定系统的引导方式和选择并行引导的始地址。

执行程序引导程序时,程序和数据存取等时间可以设置为最长7个等待周期。

若软件延时不够用,则需要辅助硬件延时等待。

双核DSP片TMS320VC5421的并行引导方案

双核DSP片TMS320VC5421的并行引导方案摘要:介绍了利用双核DSP芯片TMS320VC5421的片内Bootloader程序实现并行引导的设计方案,给出了其软件及硬件的具体实现方法。

关键词:TMS320VC5421;Bootloader;并行引导;Boot表;FLASH;CPLD1引言TMS320VC5421 1、2 (以下简称VC5421)是TI公司推出的一款双核定点DSP芯片,它拥有两个DSP子系统,每个子系统都有一个DSP核,并且均有独立的数据和程序存储空间,可以进行两核之间的通信,并且两个子系统共享一套片外总线。

此外,每个子系统各自拥有2k16bit字的片内ROM,并存储有Bootloader程序。

当DSP芯片上电或复位时,两个DSP核可分别启动自身独立的Bootloader程序,以实现用户程序的上电自举。

双核DSP自启动和单核DSP自启动的实现方法有较大的差别,这一点在DSP系统设计中需要特别注意。

本文对双核DSP芯片VC5421的引导模式进行了深入的分析和研究,给出了使用16位并行引导模式进行双核DSP引导的实现方案。

2TMS320VC5421的Boot模式VC5421可提供16位并行引导、8位并行引导和串行EEPROM引导等三种Boot模式来实现用户程序的上电自举。

其中16位并行引导模式是通过片外存储器接口(EMIF)以DMA方式将代码从16-bit字宽的片外数据存储器搬移到片内程序存储空间;8位并行引导模式则是通过片外存储器接口(EMIF)以DMA方式将代码从8-bit字宽的片外数据存储器搬移到片内的程序存储空间;而串行EEPROM引导模式主要是通过多通道缓冲串口2(McBSP2)从主设备中搬移代码并实现上电自举。

和54系列中其它芯片不同的是,VC5421片内ROM中的Bootloader程序并不支持HPI、并行I/O和标准串口模式的自启动方式。

在其所支持的三种boot模式中,16位并行引导模式是最常用的。

dsp芯片的原理与开发应用

DSP芯片的原理与开发应用1. 什么是DSP芯片?DSP芯片(Digital Signal Processor)是一种专用的数字信号处理器芯片,用于加速数字信号的处理和计算。

它通常由高速运算单元、数据存储器和输入输出接口等组成,具备高速、高效的信号处理能力。

DSP芯片广泛应用于音频、视频、通信、雷达、医疗等领域,是实现实时信号处理的重要工具。

2. DSP芯片的工作原理DSP芯片的工作原理可以简单概括为以下几个步骤:2.1 信号采样DSP芯片首先对输入信号进行采样,将连续的模拟信号转换为离散的数字信号。

常用的采样方式有周期采样和非周期采样,通过选择合适的采样频率和采样精度,可以有效地保留原始信号的特征。

2.2 数字信号处理采样后的信号经过ADC(Analog-to-Digital Converter)转换为数字信号后,DSP芯片开始进行数字信号处理。

这个过程包括滤波、变换、编码、解码、增益控制等一系列算法和操作。

DSP芯片通常集成了多种数学运算单元,如乘法器、加法器、移位器等,可以高速、高效地执行各种信号处理算法。

2.3 数据存储DSP芯片在处理过程中需要对输入、输出数据进行存储,通常包括程序存储、数据存储和寄存器等。

程序存储用于存放DSP芯片的软件程序,数据存储用于存放输入、输出数据以及中间计算结果,而寄存器则用于存放计算过程中的临时数据和控制信息。

2.4 输出重构在数字信号处理算法执行完毕后,DSP芯片将输出数据转换为模拟信号,经过DAC(Digital-to-Analog Converter)转换为连续的模拟信号。

输出重构的过程可以根据需求进行滤波、放大等处理,以获取高质量的模拟输出信号。

3. DSP芯片的开发应用DSP芯片具备高速、高效的信号处理能力,广泛应用于以下领域:3.1 通信领域DSP芯片在通信系统中广泛应用,如无线通信、移动通信和光纤通信等。

它可以处理无线信号的调频解调、调制解调、信号压缩和解码,实现高质量的音频和视频通信。

两类DSP芯片的引导过程分析(精)

两类DSP芯片的引导过程分析摘要:详细分析了TI公司TMS320C40和TMS320VC5402两类DSP芯片的系统引导特点。

在了解机理的基础上,叙述了工程设计中创建系统引导表的具体步骤,给出了创建步骤中所需的键接文件范例,并进行了说明。

关键词:TMS320C40 TMS320VC5402 系统引导引导表目前,DSP芯片正逐渐应用到电子设计中,其中应用最广泛的是TI公司生产的DSP 系列产品。

笔者在工程项目的开发中,对TMS320C40和TMS320VC5402(以下简称C40和C5402)进行了系统的研究,并成功的实现了DSP的脱机运行。

本文希望通过对C40和C5402两种芯片系统引导的描述使大家了解设计DSP系列引导的步骤,能够利用DSP设计自己的设备。

1 C40和C5402的系统引导机理TI公司的每一种DSP产品,都为用户设计了多种系统的引导方式,如串口、并行加载、HPI加载等。

C40和C5402的引导方式如表1所示。

表1 C40和C5402的引导方式C40C5402 程序执行地址IIOF3 IIOF2 IIOF1 IIOF01 0030 0000H 1 1 0 1 HPI口引导模式(由INT2引脚识别)2 4000 0000H 1 0 1 1 串行8位EEPROM引导模式(INT3)3 6000 0000H 1 0 0 1 并行引导模式4 8000 0000H 0 1 1 1 标准8位串行口McBPSP15 A000 0000H 0 1 0 1 标准16位串行口McBPSP26 C000 0000H 0 0 1 1 I/O口引导模式7 RESERVE 0 0 0 1 HPI口引导模式(由入口点进行识别)8 通讯口引导方式1 1 1 1在工程中,使用最广泛的EEPROM并行加载方式。

它又分为8位数据宽度和16位数据宽度两种,笔者采用的是8位数据宽度的并行加载方式。

需要注意的是C40的数据总线宽度是32位,引导表中数据存放的原则是低字节在低地址。

dsp芯片的原理及开发应用

DSP芯片的原理及开发应用1. DSP芯片的概述DSP(Digital Signal Processor,数字信号处理器)芯片是一种专门用于数字信号处理的集成电路。

它具备高效、快速的处理能力和专门的指令集,可以实现数字信号的采集、处理和输出。

DSP芯片在音频、视频、通信和图像处理等领域都有广泛的应用。

2. DSP芯片的原理DSP芯片相比于通用微处理器,其主要原理在于以下几个方面:2.1 架构DSP芯片的架构通常采用多重并行处理单元的结构,以支持复杂的数字信号处理算法。

典型的DSP芯片包含三个主要部分:控制单元、数据单元和外设控制器。

其中,控制单元负责协调整个系统的运行,数据单元主要用于执行算法运算,而外设控制器则管理芯片与外部设备的通信。

2.2 计算能力DSP芯片具备较强的计算能力,这得益于其专门的硬件加速器和指令集。

通常,DSP芯片具备高效的乘法累加器(MAC)和并行数据路径,可以在一个时钟周期内同时进行多个操作,从而加快信号处理速度。

2.3 特殊指令集DSP芯片的指令集通常优化了常见的数字信号处理算法,如滤波、变换和编码等。

这些指令可以直接操作数据和执行复杂的运算,减少了编程的复杂性和运算的时间。

2.4 存储器结构DSP芯片通常具备专门的高速存储器,包括数据存储器和程序存储器。

数据存储器用于存放输入和输出数据,而程序存储器则用于存放程序指令。

这样的存储器结构可以提高访问速度和运算效率。

3. DSP芯片的开发应用3.1 音频处理DSP芯片在音频处理中有广泛的应用,例如音频编解码、音频增强、音频滤波和音频效果处理等。

通过使用DSP芯片,可以提高音频处理的速度和质量,为音频设备和应用带来更好的用户体验。

3.2 视频处理DSP芯片在视频处理中也起到重要的作用。

例如,在视频编解码中,DSP芯片可以提供高效的压缩和解压缩算法,实现图像的高质量传输和存储。

此外,DSP芯片还可用于视频增强、图像处理和实时视频分析等领域。

DSP上电引导过程

}

SECTIONS

{

……….

Codestart:> Start page 0

……….

}

上面的代码执行后跳到_c_int00处执行,我对_c_int00的形成及具体情况不清楚,请知道的补充,_c_int00执行结束时调用用户的主程序main,则后续就是你自己的程序的执行了。

以上一些粗浅的说明,希望大家修正说的不正确的地方和补充未提及的地方,欢迎大家来讨论。

2812上电引导过程讨论!请踊跃发言

从上电到我们的主函数运行之间这段时间里2812到底做了些什么?2812是怎样引导程序运行的?下面叙述其启动过程。

在2812中引脚XMP/~MC,当该引脚的为高电平时表示是微处理器模式(microprocessor),为低电平时表示微机算计模式(microcomputer),当为微处理器模式时,2812内部的bootrom背禁止,通过zone7从外部调引导程序启动。2812复位以后,其复位向量是固定的0x3FFFC0,如果为为处理器模式,那么复位后的复位向量指向的外部的地址,即0x3FFFC0是zone7处的地址,若为微机算计模式,那么0x3FFFC0指向的是2812的片内FLASH的地址。下面就以微机算计模式加以说明其过程。

以跳转到你要去的地方,比如是boot loader或应用代码。在0x3F7FF6处放置跳转指令的方法如下:

.sect "codestart"

code_start:

.if WD_DISABLE == 1

LBwd_disable;Branch to watchdog disable code

.else

LB _c_int00 ;Branch to start ofboot.asmin RTS library

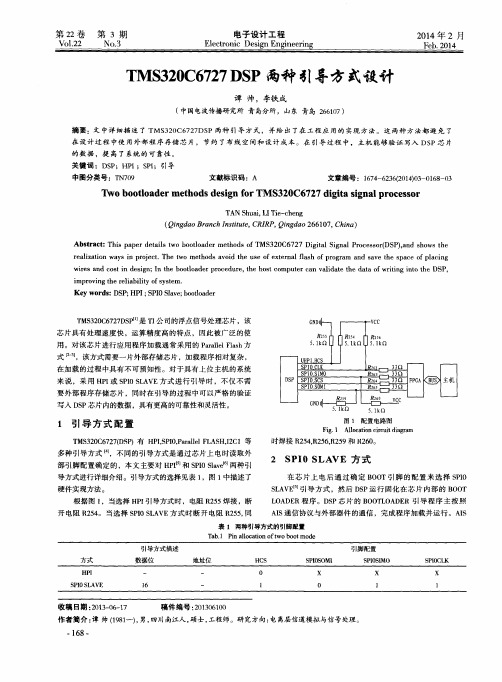

TMS320C6727DSP两种引导方式设计

式[ 2 - 3 1 ,该方式需要一片外部存储芯片,加载程序相对复杂, 在加载的过程中具有不可预知性 。对于具有上位主机的系统

来 说 ,采 用 H P I 或S P I O S L A V E方 式 进 行 引 导 时 ,不 仅 不 需 要 外 部 程 序 存储 芯 片 ,同 时在 引 导 的 过程 中可 以严 格 的 验证 写入 D S P芯 片 内的数 据 ,具 有更 高 的可 靠性 和灵 活性 。

时焊 接 R 2 5 4 , R 2 5 6 , R 2 5 9和 R 2 6 0 。

多种引导方式 【 4 】 ,不同的引导方式是通过 芯片上 电时读取外 部引脚配置确定 的,本文主要对 H P I t 和 S P 1 0 s l a v e 嘲两种引

导 方式 进行 详 细介 绍 。引导 方 式 的选择 见 表 1 ,图 1 中描 述 了 硬 件实 现方 法 。 根据图 1 ,当选 择 H P I 引导 方式 时 ,电阻 R 2 5 5焊接 ,断 开 电阻 R 2 5 4 。 当选 择 S P I O S L A V E方 式 时 断 开 电 阻 R 2 5 5 , 同

第2 2卷 第 3期

Vo 1 . 2 2 No . 3

电子设计 工程

E l e c t r o n i c De s i a n E n z i n e e

2 0 1 4年 2月

F e b. 2 01 4

S 3 2 0 C 6 7 2 7 D S P两种 引导方 式设计

wi r e s a n d c o s t i n d e s i g n ; I n t h e b o o t l o a d e r p r o c e d u r e , t h e h o s t c o mp u t e r c a n v a l i d a t e t h e d a t a o f w r i t i n g i n t o t h e DS P , i mp r o v i n g t h e r e l i a b i l i t y o f s y s t e m. Ke y wo r d s : DS P; HP I; S PI O S l a v e ; b o o t l o a d e r

DSP启动详解

DSP2812 启动详解1. 从0X3F FFC0处复位→执行0X3F FC00地址处的初始化引导函数(Initboot) →根据GPIO选择引导模式→确定用户程序入口地址→从入口处开始执行用户程序。

输入外部引脚为/XRS, 当/XRS为低电平时,DSP终止执行,PC指向地址:0x3FFFC0,当/xRS变成高电平时,DSP开始执行0x3FFFC0中存放的指令。

这条指令是条跳转指令或者说是复位中断向量,这个中断向量指向地址0X3F FC00处的初始化引导函数(Initboot),即将地址0x3FFC00(函数initboot的首地址)发给PC,值得注意的是:地址0X3F FFC0也有片内、片外两种,具体的选择情况是:当系统上电运行时,根据XMP/MC引脚的状态决定是从片外的3fffc0处读取复位向量或者时从片内的rom的3fffc0处读取复位向量。

低电平方式下从片内读取,高电平方式下从片外读取。

InitBoot 函数所做工作有:1.初始化状态寄存器;2.将堆栈指针设为0x400(0x400 - 0x44F作为启动过程中的堆栈);3.读CSM密码保护部分;如果是从片内读取的,则以上程序都是被固化在rom中的,无法更改,4.调用SelectBootMode;模式的选择是由四个引脚GPIOF4(SCITXDA), GPIOF12(MDXA), GPIOF3 (SPISTEA), GPIOF2(SPICLK5).的状态决定的,若为1xxx则跳转到FLASH地址0x3F7FF6, 0010为H0 SARAM地址为0x3F8000.调用ExitBoot以上是BootROM完成的工作。

从entrypoint开始,就进入用户程序区了。

对于汇编程序,可以在程序起点处写一条跳转到Start(如果程序起点是Start)的指令。

汇编情况比较简单,跳转到Start后,各项初始化代码工作都由自己完成。

对于C语言程序,通常的做法是在程序起点处放置一条跳转指令,转到_c_init0。

一种双DSP系统串行引导方案的实现(精)

一种双DSP系统串行引导方案的实现0引言在某型光电跟踪产品中,由于需要对抗各种人工干扰和背景干扰,使得导引系统需要处理的信息量成倍增加,对导引系统的实时处理性能提出了更高的要求。

针对这种情况,导引系统采用了双DSP系统的信息处理方案,DSP选用AD公司的ADSP218x和TI公司的TMS320C62x。

ADSP218x进行目标信号的采样和外围控制信号的输入、输出,TMS320C62x专门进行目标的鉴相、各种抗干扰算法的计算,这样TMS320C62x不受外设服务中断影响,可以更好地发挥计0 引言在某型光电跟踪产品中,由于需要对抗各种人工干扰和背景干扰,使得导引系统需要处理的信息量成倍增加,对导引系统的实时处理性能提出了更高的要求。

针对这种情况,导引系统采用了双DSP系统的信息处理方案,DSP选用AD公司的ADSP218x和TI公司的TMS320C62x。

ADSP218x进行目标信号的采样和外围控制信号的输入、输出,TMS320C62x专门进行目标的鉴相、各种抗干扰算法的计算,这样TMS320C62x不受外设服务中断影响,可以更好地发挥计算效率,提高了导引系统的实时处理性能。

本文针对ADSP218x系列和TMS320C62x系列组成的双DSP系统,提出了一种串行引导方案,同时给出了其硬件及软件的具体实现方法。

1 DSP引导模式1.1 TMS320C62x引导模式TMS320C62x系列DSP提供了三种引导方式:(1)无引导过程:DSP直接从地址0开始执行代码;(2)ROM方式引导:由DMA/EDMA控制器从外部CE1空间中的ROM中拷贝固定数量的代码到地址0,启动时也可选择ROM的宽度,拷贝结束后,CPU从地址0开始运行;(3)HPI方式引导:由外部主机通过HPI对芯片的存储器空间进行初始化,初始化结束后,外部主机通过HPI中断唤醒TMS320C62x,CPU开始从地址0运行。

所有这些设置项都是在芯片复位的时候才进行检查。

DSP引导功能的使用

中国冶金行业网 http://wwwห้องสมุดไป่ตู้

中国冶金行业网 } (5) 转换命令程序 convert.cmd 上面的工程文件经 CCS 系统编译、汇编后生成可执行 COFF 文件(.out),它需要转换为二进制文件,再写入 到 FLASH 中。CCS 开发系统带有转换程序: hex6x.exe 将可执行 COFF 文件(.out)转换为十六进制文件(.hex) hex2bin.exe 将十六进制文件(.hex)转换为二进制文件(.bin) 命令行的格式为: hex6x.exe convert.cmd hex2bin.exe mboot 其中 convert.cmd 内容如下: mboot.out ;输入文件名 .out 格式 -x -map mboot.map ;生成映射文件 -image -memwidth 8 ;内存的位宽 -o mboot.hex ;输出文件名 .hex 格式 ROMS { FLASH: org = 0, len = 0x10000, romwidth = 8 } 结束语 综上所述,实现 TMS320C6712的外部内存自引导并不复杂,关键是要理解芯片的自引导过程和程序汇编后各 部分的作用,配置好引导代码段和程序代码段的实际物理地址,并且正确地初始化相应的寄存器和变量。

中国冶金行业网

.global _boot ;定义全局函数 _boot: ;先设置控制寄存器,如 EMIF_GCR 等,(略) ;拷贝 FLASH 中的程序到 DSP 内部 RAM mvkl 0x00000400, A4 ;A4为 RAM 地址指针 mvkl 0x90000400, B4 ;B4为 FLASH 地址指针 mvkh 0x00000400, A4 mvkh 0x90000400, B4 zero A1 ;A1用作计数器 _boot_loop: ;DSP 开始读取 FLASH 中程序 ldb *B4++, B5 mvkl 0x0000F200, B6 ;B6为需要拷贝的字节数 add 1, A1, A1 mvkh 0x0000F200, B6 cmplt A1, B6, A0 nop stb B5, *A4++ [B0] b _boot_loop nop 5 mvkl .S2 _c_int00, B0 ;循环结束后,跳转到主函数 main 执行 mvkh .S2 _c_int00, B0 B .S2 B0 Nop 5 (3) 主程序 main.c 主程序是 DSP 要实现具体功能的主体,其定义的主函数 main()经编译后在函数_c_int00中调用,因此在上 中国冶金行业网

dsp芯片的原理的开发与应用

DSP芯片的原理的开发与应用1. DSP芯片的概述DSP(Digital Signal Processor)芯片是一种专门用于处理数字信号的芯片。

与通用微处理器相比,DSP芯片具有更强大的信号处理能力和更快的处理速度,因此在许多应用领域中得到了广泛的应用。

2. DSP芯片的原理DSP芯片的原理是基于数字信号处理技术,主要包括以下几个方面:2.1 数字信号的采样与量化对于模拟信号,首先需要进行采样,即将连续的模拟信号转化为离散的数字信号。

采样过程可以通过使用模数转换器(ADC)来实现。

而量化是指对采样后的信号进行离散化处理,将连续的数值转化为离散的数值表示。

2.2 数字信号的编码对于量化后的信号,需要进行编码以便在处理和传输过程中能够方便地表示。

常见的编码方式有PCM(脉冲编码调制)、DPCM(差分脉冲编码调制)等。

2.3 数字信号的处理算法DSP芯片的核心是处理算法,常见的算法有FFT(快速傅里叶变换)、滤波、解调等。

这些算法能够对数字信号进行各种复杂的处理和分析,实现音频、图像、视频等信号的处理和识别。

2.4 数字信号的输出与还原经过处理后的数字信号需要进行还原,即将数字信号转化为模拟信号以供人类感知。

这可以通过数模转换器(DAC)来实现,将数字信号转换为模拟信号。

3. DSP芯片的开发流程DSP芯片的开发过程可以分为以下几个步骤:3.1 项目需求分析在开始开发之前,首先需要对项目需求进行详细分析和定义,明确需要实现的功能和性能要求。

根据需求确定芯片的输入输出接口、处理算法等。

3.2 芯片设计根据需求分析的结果,进行芯片设计。

设计包括硬件设计和软件设计两个方面,硬件设计主要针对芯片的电路结构和布局,而软件设计主要是针对芯片的处理算法和程序设计。

3.3 芯片制造设计完成后,需要将设计图纸进行制造。

这个过程包括制造芯片的掩膜、制造电路板、组装芯片等。

3.4 芯片测试制造完成后,进行芯片的测试。

测试主要包括功能测试、性能测试等,确保芯片的功能和性能符合设计要求。

DSP工作原理

DSP工作原理1. 简介数字信号处理(Digital Signal Processing,DSP)是一种处理数字信号的技术,它涉及数字信号的获取、处理和分析。

DSP广泛应用于通信、音频、视频、雷达、医学成像等领域。

本文将详细介绍DSP的工作原理。

2. 数字信号处理流程DSP的工作原理可以分为以下几个步骤:2.1 信号采集DSP系统首先需要采集摹拟信号,并将其转换为数字信号。

这一步骤通常通过模数转换器(ADC)完成。

ADC将摹拟信号按照一定的采样频率进行采样,然后将采样后的信号转换为数字信号,以便后续的数字信号处理。

2.2 数字信号处理采集到的数字信号将被送入DSP芯片或者处理器进行数字信号处理。

DSP芯片通常包含一个或者多个数字信号处理器核心,用于执行各种算法和运算。

这些算法和运算可以包括滤波、变换、编码、解码、调制、解调等。

2.3 算法实现DSP芯片中的数字信号处理器核心将执行特定的算法来处理数字信号。

这些算法可以是基于时域的算法,如滤波器、卷积等;也可以是基于频域的算法,如傅里叶变换、小波变换等。

通过这些算法,DSP可以实现对信号的增强、去噪、压缩等处理。

2.4 结果输出处理后的数字信号可以通过数字信号处理器核心的输出端口送往其他设备或者系统。

输出可以是数字信号,也可以通过数模转换器(DAC)转换为摹拟信号,以供其他设备使用。

3. DSP的优势相比于传统的摹拟信号处理,DSP具有以下优势:3.1 灵便性DSP可以通过更改算法和参数来实现不同的信号处理功能,从而具有更高的灵便性。

这使得DSP在各种应用中具有广泛的适应性。

3.2 可编程性DSP芯片具有可编程性,可以根据具体需求进行编程和配置。

这使得DSP能够适应不同的信号处理算法和应用场景。

3.3 高性能DSP芯片通常采用并行处理架构,能够同时处理多个数据流。

这使得DSP具有较高的处理速度和运算能力,能够满足实时信号处理的需求。

3.4 低功耗相比于通用处理器,DSP芯片通常具有较低的功耗。

用DSP软件编程实现的引导装载系统分析

用DSP软件编程实现的引导装载系统分析

引导程序:引导程序主要负责加载应用程序并将控制权转交给应用程序。

引导程序的实现需要根据具体DSP的硬件特点进行设计,其中包括片上存储器和外部存储器的选择、存储器接口等。

引导程序的设计应该考虑到存储器使用的灵活性、性能和安全性。

同时,为了保证引导程序的可靠性,需要在设计时考虑到各种异常情况的处理,如存储器的读写异常、应用程序的异常退出等。

在实现过程中,还需要考虑到耗时问题,尽量减小引导程序的体积和执行时间,以便更快地启动应用程序。

引导程序和应用程序的实现需要满足以下要求:

1. 可靠性高:引导程序和应用程序需要具有高可靠性,能够在各种异常情况下保证系统的正常运行。

2. 体积小:为了能够快速加载应用程序,引导程序的体积应该尽量小,同时应用程序的体积也应该尽可能小,以便减小存储器的使用量。

3. 效率高:为了能够快速启动应用程序并完成任务,引导程序和应用程序的执行效率应该尽可能高,同时需要避免资源的浪费。

4. 可扩展性和可维护性:为了方便应用程序的调试和升级,应用程序应该具有良好的可扩展性和可维护性,能够方便地进行修改和更新。

总之,DSP软件编程实现的引导装载系统需要考虑到多方面的因素,包括硬件特点、系统需求、性能要求、错误处理等。

在实际应用中,需要根据具体情况进行设计和优化,以达到最佳的性能和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

两类DSP芯片的引导过程分析摘要: 详细分析了TI公司TMS320C40和TMS320VC5402两类DSP芯片的系统引导特点。

在了解机理的基础上,叙述了工程设计中创建系统引导表的具体步骤,给出了创建步骤中所需的链接文件范例,并进行了说明。

关键词: TMS320C40 TMS320VC5402 系统引导引导表目前,DSP芯片正逐渐应用到电子设计中,其中应用最广泛的是 TI 公司生产的DSP系列产品。

笔者在工程项目的开发中,对TMS320C40和TMS320VC5402(以下简称C40和C5402)进行了系统的研究,并成功的实现了DSP的脱机运行。

本文希望通过对C40和C5402两种芯片系统引导的描述使大家了解设计DSP系统引导的步骤,能够利用DSP设计自己的设备。

1 C40和C5402的系统引导机理TI公司的每一种DSP产品,都为用户设计了多种系统的引导方式,如串口、并行加载加载、HPI加载等。

C40和C5402的引导方式如表1所示。

在工程中,使用最广泛的是EEPROM并行加载方式。

它又分为8位数据宽度和16位数据宽度两种,笔者采用的是8位数据宽度的并行加载方式。

需要注意的是C40的数据总线宽度是32位,引导表中数据存放的原则是低字节在低地址。

C5402的数据宽度是16位,引导表中数据的存放原则是高字节在低地址。

1.1 C40的并行引导模式C40加电时,芯片检测到ROMAN引脚为高电平高电平,进入微处理器模式。

再检测IIOF3~IIOF0引脚电平,决定系统的引导方式和选择并行引导的始地址。

执行程序引导程序时,程序和数据存取等待时间可以设置为最长7个等待周期。

若软件延时不够用,则需要辅助硬件延时等待。

程序引导完毕后,会在IACK引脚产生脉冲,使引脚可以作为中断引脚使用并转入到程序的入口地址开始执行程序。

C40由中断引脚的电平决定系统引导后的程序执行地址,或决定是否由通讯口进行程序的加载。

采用 0030 0000H 作为主程序的入口地址,即将一片28C256地址设计为0030 0000H~0030 7FFFH。

在系统引导时,需维持IIOF3~IIOF0四个引脚电平为1101。

下面以IIOF2引脚和IIOF1引脚为例,叙述一下系统引导前后的中断引脚的处理过程。

图1电路是IIOF2引脚的外围处理电路。

在系统加电时,D31A的/PRE=0、/CLR=1,置位端有效,所以Q=1、/IIOF2=1。

加电完毕后,/PRE=1、/CLR=1,此时无/IACK信号,Q=1、/IIOF2=1,C40开始程序的加载工作。

当C40程序加载完毕时,IACK引脚会产生一个脉冲,Q=D=0,/IIOF2=/INT2。

C40会转入程序的入口地址执行程序,此时D触发器电路的工作已经完毕,C40此时可以处理中断信号。

图2电路是IIOF1引脚的外围处理电路。

系统引导时,要求/IIOF1引脚电平为低电平。

1.2 C5402并行引导模式C5402加电时,如果芯片检测到MP/MC引脚电平为低电平,系统从0FF80H开始执行代码。

此处有一个分支指令(厂家编程设置的),可以跳转到引导程序的开始地址(0F800H)。

这个程序可以在引导之前设置CPU状态寄存器的初始值。

中断被全局禁止,OVLY设置为1,程序和数据存取等待时间被设置为7个等待周期,外部内存块被设置为4K的WORDS(16BIT),然后开始程序的引导。

当C5402检测到INT2引脚为高电平、INT3引脚为高电平,即两个引脚都无效时,C5402会转到并行引导方式。

并行引导方式是通过扩展的内存接口从数据地址空间读取所需的引导表,再将代码传送到程序存储区。

并行引导既支持8位的数据宽度,也支持16位的数据宽度。

软件可编程等待寄存器(SWWSR)和块切换控制寄存器(BSCR)都可以在这两种模式中得到设置。

C5402数据存储区、程序存储区和I/O地址空间,用/DS、/PS和/IS三个引脚信号区分。

系统的引导表设在数据存储区,考虑到C5402内部只有16K×16的双存取RAM(DRAM),因此用于程序加载的EEPROM (EEPROM中存放的是系统的引导表)可考虑使用28LV256。

如果在设计中,使28LV256(+3.3V供电)占用系统的数据空间地址为8000H?觸0FFFFH,那么,C5402在系统引导时需从系统的数据地址0FFFEH和0FFFFH得到引导表的起始地址8000H。

在设计系统引导表时要注意这两个单元的内容。

如果设计EEPROM的首地址(系统引导表的首地址)为0C000H,那么数据地址0FFFEH和0FFFFH两个单元要存放C0和00H,也就是引导表的首地址。

在设计中也可以使用其它EEPROM或FLASH,如29LE010(128K×8BIT),但要正确配置它在系统中的地址。

引导表的首地址(即EEPROM的在系统中的首地址)是通过系统数据地址0FFFEH和0FFFFH 决定的,可以是08000H~0FFFDH之间的任意地址,但要保证能够存储系统引导表。

2 建立系统引导表的步骤程序经过仿真器仿真无误以后,就要建立引导表,使系统能够脱机运行。

下面介绍建立系统引导表的步骤:(1)编译文件。

编写完程序代码以后,对源程序进行编译,生成.obj 文件,对于C5402,编译时要采用-V548的编译描述符。

(2)链接文件,将.obj文件生成.out文件。

.out文件中应包括初始化的段落。

如.text,.const,.cinint等。

以上两步在仿真时,也需要执行,以便得到仿真用的.out文件。

(3)使用数制转换工具转换工具生成.HEX文件或.BIN文件,C40使用的数制转换工具为hex30.exe,C5402使用数制转换工具为hex500.exe。

根据所需的系统引导模式为数制转换工具编写命令文件,命令文件的编写很重要,下面分别例举了C40和C5402系统引导的两个CMD 命令文件。

例1:C40系统引导的CMD文件myfile.out /*要进行转化的COFF文件名*/-i /*建立INTEL十六进制文件的输出*/-image /*产生ROM所指示的内存映射*/-o n_t_fcom.hex /*输出的文件名*/-map n_t_hex.map /*输出的 MAP文件名*/-romwidth 8 /EEPROM 的数据宽度*/-cg 000000000H /*全局数据总线控制字*/-cl 3e3fbfd0H /*本地数据总线控制字*/-datawidth 32 /*数据宽度*/-memwidth 8 /*存储器的宽度*/-boot /*将所有的输入文件创建引导表*/-bootorg 0000H /*EPROM的0000H,系统的0030 0000H*/-ivtp 00700000H /*IVTP指针的初始值*/-tvtp 00000000H /*TVTP指针的初始值*/-iack 0300000H /*IACK指令的响应地址*/-e 00704000H /*程序的开始执行地址*/ROMS /*ROM的映射范围*/{EPROM: org = 00300000h,len = 8000H}例2:C5402系统引导CMD命令文件Myfile.out /*要进行转化的COFF文件名*/-e 0300H /*程序运行的入口点*/-i /*建立INTEL 十六进制文件的输出*/-boot /*将所有的输入文件创建引导表*/-bootorg 0000H /*EPROM中引导表的始地址*/-memwidth 8 /*EEPROM的数据宽度是8位*/-o myfile.hex /*输出的文件名*/下面给出操作符的几点说明:(1)-bootorg 指定引导表的地址,注意这里使用的是0000H,.HEX文件的始地址就是0000H。

在C40中,EEPROM28C256的0000H地址单元,在系统中地址是0030 0000H。

若改为-bootorg 0030 0000H,在用烧录烧录器打开.HEX文件时,可以看到起始地址是0030 0000H,若将.HEX文件烧到EEPROM中,需要修改烧录芯片的起始地址,比较麻烦。

但你可以将.HEX文件转化为.BIN文件,则地址就不必修改。

(2)输出文件的格式-a 输出ASCII码的十六进制文件-I 输出INTEL十六进制文件-m1 输出Motorola的S1数据格式文件-m2 输出Motorola的S2数据格式文件-m3 输出Motorola的S3数据格式文件-t 输出TI的数据格式文件-x 输出Tektronix 数据格式文件(3)检查.HEX文件正确与否,可以查看MAP映射文件,在.MAP文件里列出了.HEX文件中的一些具体配置。

如 32BIT数据位的排放顺序,即4个字节的排放顺序;系统引导表的参数:引导表的首地址、程序入口点、各个寄存器的初始值等;源程序中各段的起始地址、大小以及宽度等信息。

对照它,就可以确定内存资源是否得到了合理的配置和有无地址冲突。

以下是C40 MAP文件的举例:*********************************************TMS320C3x/4x Hex Converter Version 5.00*********************************************Fri Jun 8 09:47:33 2001INPUT FILE NAME:OUTPUT FORMAT: IntelPHYSICAL MEMORY PARAMETERSDefault data width: 32Default memory width: 8 (LS-->MS)Default output width: 8BOOT LOADER PARAMETERSTable Address: 00300000,PAGE 0Entry Point: 00704000Global Memory Configuration: 00000000Local Memory Configuration: 3e3fbfd0Interrupt Vector Table Pointer (IVTP): 00700000Trap Vector Table Pointer (TVTP): 00000000IACK Location: 00300000OUTPUT TRANSLATION MAP-------------------------------------00300000..00307fff Page=0 Memory Width=8 ROM Width=8 ″EPROM″-------------------------------------OUTPUT FILES: n_t_fcom.hex [b0..b7]CONTENTS: 00300000..003013ff BOOT TABLEintvect:dest=00700000 size=00000040 width=00000004.text:dest=00704000 size=0000048a width=00000004.data:dest=00705000 size=00000026 width=00000004003004f0..00307fff FILL = 00000000(4)烧录芯片。