IDT54FCT16374CTPV中文资料

FCT电子杰西特排序与检查机器说明书

Festo AG & Co.PostfachD-73726 EsslingenTelephone 07 11/34 67-5 36Telefax 07 11/34 67-6 16*******************Miniaturisation, i.e. more and more functions in a smaller and smaller space – this is the byword for companies which are operating in international competition in the electrical engineering/electronics sector. In conjunction with know-how and the entrepreneurial far-sightedness to foresee a relia-ble future in the global market,the ability to miniaturise is decisive.The company FCT electronic leipzig gmbh in Jesewitz manu-factures a broad range of plug connectors – small and minus-cule, high quality and highly versatile mass-produced com-Clear separation of small components with complex mixes!The Sortbox has produced its masterpieceponents used in the electrical engineering/electronics indu-stry.The requirementsIn the electrical engineering/electronics industry, the manu-facture of plug connectors requires the use of numerous individual, generally tiny, high quality parts. Depending on the end product being manufactur-ed, the combination changes constantly. It also includes plastic products with galvanis-ed surface finishing. To achieve optimum usage of galvanising capacity, different types of component are galvanised together and then separated again, fully sorted.Long live the fine difference With injection moulded parts which are frequently only a few millimetres in size and a few grams in weight, it is important to be able to identify compo-nents which are defective in shape and to remove them from the flow of components with accuracy and reliability.Foreign parts which do not belong to the current range of parts must also be identified and sorted out.Complex tasks require simple solutionsThe method used to separate the mixtures to ensure that the parts were fully sorted for deli-very used to involve meticu-lously precise and painstaking manual work.One may well imagine the expenditure required for this.In order to keep pace with the costs pressure coming from the market, FCT went looking for an automated solution with no ifs or buts: for 100% tested quality.A real money-boxThe Sortbox counteracted the costs pressure being exerted by the market as it could sepa-rate parts automatically both faster and more reliably.the system…the parts …the Sortbox …The result–The Sortbox can also be used as a stand-alone system for a wide variety of testing and separating tasks and can be put into operation with ease –Components can be taught for individual sorting posi-tions in seconds and on the machine directly–Automatic quality control ensures that the delivered components are of top quality –Foreign or defective parts are automatically sorted out –Once generated, the Teach-in data can be stored under the component number on a PC and then loaded into the Sortbox as required–Reverting to existing, tested Teach-in data leads to greater process reliability and saves time and refitting costs–Securing fully sorted compo-nents is always guaranteed even at high sorting speed and with a wide range of com-ponents–The tough, compact and robust system guarantees trouble-free operation。

IDT54FCT646A中文资料

MILITARY AND COMMERCIAL TEMPERATURE RANGESMAY 1992©1992 Integrated Device Technology, Inc.7.18DSC-4626/2The IDT logo is a registered trademark of Integrated Device Technology, Inc.FAST is a registered trademark of National Semiconductor Co.•IDT54/74FCT646 equivalent to FAST ™ speed;•IDT54/74FCT646A 30% faster than FAST •IDT54/74FCT646C 40% faster than FAST •Independent registers for A and B buses •Multiplexed real-time and stored data•I OL = 64mA (commercial) and 48mA (military)•CMOS power levels (1mW typical static)•TTL input and output level compatible •CMOS output level compatible•Available in 24-pin (300 mil) CERDIP, plastic DIP, SOIC,CERPACK and 28-pin LCC•Product available in Radiation Tolerant and Radiation Enhanced Versions•Military product compliant to MIL-STD-883, Class BThe IDT54/74FCT646/A/C consists of a bus transceiver with 3-state D-type flip-flops and control circuitry arranged for multiplexed transmission of data directly from the data bus or from the internal storage registers.The IDT54/74FCT646/A/C utilizes the enable control (G )and direction (DIR) pins to control the transceiver functions.SAB and SBA control pins are provided to select either real time or stored data transfer. The circuitry used for select control will eliminate the typical decoding glitch that occurs in a multiplexer during the transition between stored and real-time data. A LOW input level selects real-time data and a HIGH selects stored data.Data on the A or B data bus or both can be stored in the internal D flip flops by LOW-to-HIGH transitions at the appropriate clock pins (CPAB or CPBA) regardless of the select or enable control pins.FUNCTIONAL BLOCK DIAGRAM2536 drw 01B 1TO 7 OTHER CHANNELSSABCPBA CPAB SBA DIR G17.182FAST CMOS OCTAL TRANSCEIVER/REGISTERMILITARY AND COMMERCIAL TEMPERATURE RANGESPIN CONFIGURATIONSLCC TOP VIEWDIP/SOIC/CERPACKTOP VIEW(2)1.The data output functions may be enabled or disabled by various signals at the G or DIR inputs. Data input functions are always enabled, i.e., data atthe bus pins will be stored on every LOW-to-HIGH transition on the clock inputs.2.H = HIGH, L = LOW, X = Don’t Care, ↑ = LOW-to-HIGH Transition.2536 tbl 01LOGIC SYMBOLGNDA 1A 2A 3Vcc CPAB B 1A 4A 5A 6SAB DIR A 7A 8CPBA SBA B 2B 3B 4B 5B 6B 7B 82536 drw 062536 drw 02B 1B 2B 3B 4B 5NC c c P A B A B I R P B A B AC G ND A 7A 8B 8B 7B 6N CDIR L GLCPABXCPBAXSABXSBAL2536 drw 03DIRHGLCPABXCPBAXSABLSBAXDIRHLXGLLHCPBA SABXXXSBAXXX2536 drw 04DIRLHGLLCPABXH or LCPBAH or LXSABXHSBAHX(1)STORAGE FROMA AND/OR BREAL–TIME TRANSFERBUS B TO BUS AREAL–TIME TRANSFERBUS A TO BUS BTRANSFER STOREDDATA TO A AND/OR BNOTE:1.Cannot transfer data to A bus and B bus simultaneously.7.1837.184(1)2536 tbl 031.Stresses greater than those listed under ABSOLUTE MAXIMUMRATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability. No terminal voltage may exceed V CC by +0.5V unless otherwise noted.2.Inputs and V CC terminals only.3.Outputs and I/O terminals only.NOTE:2536 tbl 041.This parameter is measured at characterization but not tested.DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGEFollowing Conditions Apply Unless Otherwise Specified: V LC = 0.2V; V HC = V CC – 0.2VA CC A CC 2536 tbl 051.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at V CC = 5.0V, +25°C ambient and maximum loading.3.Not more than one output should be shorted at one time. Duration of the short circuit test should not exceed one second.4.This parameter is guaranteed but not tested.POWER SUPPLY CHARACTERISTICS1.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at V CC = 5.0V, +25°C ambient.3.Per TTL driven input (V IN = 3.4V); all other inputs at V CC or GND.4.This parameter is not directly testable, but is derived for use in Total Power Supply calculations.5.Values for these conditions are examples of the I CC formula. These limits are guaranteed but not tested.6.I C = I QUIESCENT + I INPUTS + I DYNAMICI C = I CC + ∆I CC D H N T + I CCD (f CP/2 + f i N i)I CC = Quiescent Current∆I CC = Power Supply Current for a TTL High Input (V IN = 3.4V)D H = Duty Cycle for TTL Inputs HighN T = Number of TTL Inputs at D HI CCD = Dynamic Current Caused by an Output Transition Pair (HLH or LHL)f CP = Clock Frequency for Register Devices (Zero for Non-Register Devices)f i = Input FrequencyN i = Number of Inputs at f iAll currents are in milliamps and all frequencies are in megahertz.7.1851.See test circuit and waveforms.2.Minimum limits are guaranteed but not tested on Propagation Delays.7.1867.187TEST CIRCUITS AND WAVEFORMS TEST CIRCUITS FOR ALL OUTPUTSENABLE AND DISABLE TIMESPROPAGATION DELAYSET-UP, HOLD AND RELEASE TIMESPULSE WIDTHDATA INPUTTIMING INPUTPRESET CLEAR ETC.PRESET CLEARCLOCK ENABLEETC.3V 1.5V 0V 3V 1.5V 0V 3V 1.5V 0V 3V 1.5V 0V7.0VSAME PHASE INPUT TRANSITION3V 1.5V0V 1.5V V OH V OL OUTPUTOPPOSITE PHASE INPUT TRANSITIONV OL V OH 3V 1.5V 0VENABLEDISABLENOTES 2536 drw 071.Diagram shown for input Control Enable-LOW and input ControlDisable-HIGH.2.Pulse Generator for All Pulses: Rate ≤ 1.0 MHz; Z O ≤ 50Ω; t F ≤ 2.5ns;t R ≤ 2.5ns.SWITCH POSITIONTest Switch Open Drain Disable Low Closed Enable Low All Other TestsOpenDEFINITIONS:2536 tbl 08C L =Load capacitance: includes jig and probe capacitance.R T =Termination resistance: should be equal to Z OUT of the PulseGenerator.7.188ORDERING INFORMATIONXX PackageX Process/Blank B CommercialMIL-STD-883, Class B P D SO L E Plastic DIP CERDIPSmall Outline ICLeadless Chip Carrier CERPACK646646A 646C Non-inverting Octal Transceiver/RegisterFast Non-inverting Octal Transceiver/RegisterSuper Fast Non-inverting Octal Transceiver/Register XXXX Device 2536 drw 055475–55°C to +125°C 0°C to +70°CFCTTemperature XX IDT。

德特威勒 产品手册

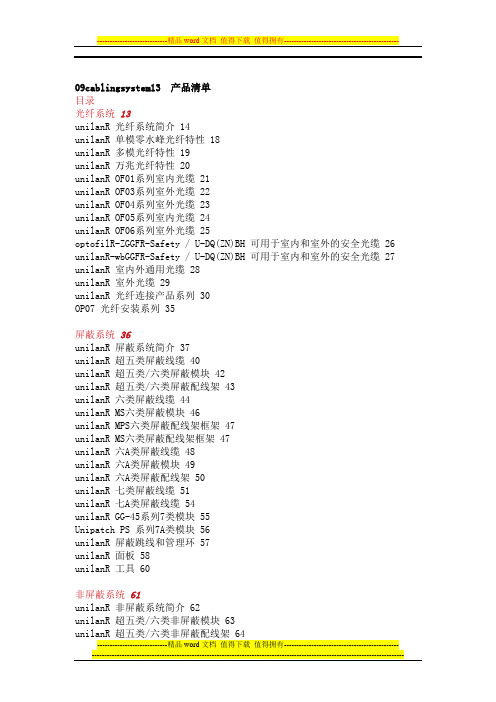

09cablingsystem13 产品清单目录光纤系统13unilanR 光纤系统简介 14unilanR 单模零水峰光纤特性 18unilanR 多模光纤特性 19unilanR 万兆光纤特性 20unilanR OF01系列室内光缆 21unilanR OF03系列室外光缆 22unilanR OF04系列室外光缆 23unilanR OF05系列室内光缆 24unilanR OF06系列室外光缆 25optofilR-ZGGFR-Safety / U-DQ(ZN)BH 可用于室内和室外的安全光缆 26 unilanR-wbGGFR-Safety / U-DQ(ZN)BH 可用于室内和室外的安全光缆 27 unilanR 室内外通用光缆 28unilanR 室外光缆 29unilanR 光纤连接产品系列 30OP07 光纤安装系列 35屏蔽系统36unilanR 屏蔽系统简介 37unilanR 超五类屏蔽线缆 40unilanR 超五类/六类屏蔽模块 42unilanR 超五类/六类屏蔽配线架 43unilanR 六类屏蔽线缆 44unilanR MS六类屏蔽模块 46unilanR MPS六类屏蔽配线架框架 47unilanR MS六类屏蔽配线架框架 47unilanR 六A类屏蔽线缆 48unilanR 六A类屏蔽模块 49unilanR 六A类屏蔽配线架 50unilanR 七类屏蔽线缆 51unilanR 七A类屏蔽线缆 54unilanR GG-45系列7类模块 55Unipatch PS 系列7A类模块 56unilanR 屏蔽跳线和管理环 57unilanR 面板 58unilanR 工具 60非屏蔽系统61unilanR 非屏蔽系统简介 62unilanR 超五类/六类非屏蔽模块 63unilanR 超五类/六类非屏蔽配线架 64unilanR 六类非屏蔽线缆 65unilanR 六类非屏蔽跳线 66unilanR 超五类非屏蔽线缆 67unilanR 超五类非屏蔽跳线 68e-lineR 非屏蔽超五类系列 69e-lineR 非屏蔽模块 70e-lineR 非屏蔽配线架 71e-lineR 非屏蔽线缆 72unilanR 110系列 73unilanR CU25/50三类语音配线架 74uninetR 三类语音大对数电缆线对 75uninetR 三类UTP 25对/50对/100对类室内大对数电缆 76 uninetR 三类UTP 25对/50对/100对类室外大对数电缆 77 unilanR 面板 78表面安装盒 80unilanR 管理环 81弹起式三口地面插座盒 81unilanR 系统附件 82德特威勒光纤系统解决方案unilan® 单模零水峰光纤特性德特威勒单模零水峰光纤特性;符合ITU-T Rec. G652D ;GB/T 9771.3-2000满足IEEE802.3ae 标准,支持10GBASE-L 万兆以太网达1000米以上距离及1000Base-LX 千兆以太网达5000米以上距离,向下兼容目前的100Mbps 及10Mbps 以太网应用Unilan®多模光纤特性符合IEC 60793-2-10、YD/T 1258.4-2005、GB 50311-2007、ISO/IEC 11802-2002、EN50173.1-2007、TIA-568C.3-2009标准,适用于中等传输距离的局域网,基于850nm和1300nm波长的中等传输速率。

半导体二极管参数符号

半导体二极管参数符号CT-势垒电容Cj-结(极间)电容,表示在二极管两端加规定偏压下,锗检波二极管的总电容Cjv-偏压结电容Co-零偏压电容Cjo-零偏压结电容Cjo/Cjn-结电容变化Cs-管壳电容或封装电容Ct-总电容CTV-电压温度系数。

在测试电流下,稳定电压的相对变化与环境温度的绝对变化之比CTC-电容温度系数Cvn-标称电容IF-正向直流电流(正向测试电流)。

锗检波二极管在规定的正向电压VF下,通过极间的电流;硅整流管、硅堆在规定的使用条件下,在正弦半波中允许连续通过的最大工作电流(平均值),硅开关二极管在额定功率下允许通过的最大正向直流电流;测稳压二极管正向电参数时给定的电流IF(AV)-正向平均电流IFM(IM)-正向峰值电流(正向最大电流)。

在额定功率下,允许通过二极管的最大正向脉冲电流。

发光二极管极限电流。

IH-恒定电流、维持电流。

Ii-发光二极管起辉电流IFRM-正向重复峰值电流IFSM-正向不重复峰值电流(浪涌电流)Io-整流电流。

在特定线路中规定频率和规定电压条件下所通过的工作电流IF(ov)-正向过载电流IL-光电流或稳流二极管极限电流ID-暗电流IB2-单结晶体管中的基极调制电流IEM-发射极峰值电流IEB10-双基极单结晶体管中发射极与第一基极间反向电流IEB20-双基极单结晶体管中发射极向电流ICM-最大输出平均电流IFMP-正向脉冲电流IP-峰点电流IV-谷点电流IGT-晶闸管控制极触发电流IGD-晶闸管控制极不触发电流IGFM-控制极正向峰值电流IR(AV)-反向平均电流IR(In)-反向直流电流(反向漏电流)。

在测反向特性时,给定的反向电流;硅堆在正弦半波电阻性负载电路中,加反向电压规定值时,所通过的电流;硅开关二极管两端加反向工作电压VR时所通过的电流;稳压二极管在反向电压下,产生的漏电流;整流管在正弦半波最高反向工作电压下的漏电流。

IRM-反向峰值电流IRR-晶闸管反向重复平均电流IDR-晶闸管断态平均重复电流IRRM-反向重复峰值电流IRSM-反向不重复峰值电流(反向浪涌电流)Irp-反向恢复电流Iz-稳定电压电流(反向测试电流)。

LD型单梁起重机使用说明书

LD型电动单梁桥式起重机使用说明书安徽江淮起重运输机械有限公司目录一、概述 (3)二、结构特征与工作原理 (3)三、设备性能指标 (5)四、设备的运输、安装、调整和试运行 (5)五、机械设备的维护和保养 (7)六、安全操作注意事项 (10)七、常见机械故障处理 (10)八、随机文件 (11)九、售后服务 (11)使用说明书一、概述电动单梁桥式起重机是以固式的电动葫芦安装在行车主梁上作为大车起升机构运行。

本产品为地面操纵。

该产品结构简单、重量轻、价格便宜,主要用于机械制造车间、仓库、装配及水电站检修等场所的一般吊重装卸作业。

本产品的工业环境温度为-25~40℃。

不适于用有爆炸危险、火灾危险的介质中和相对温度大于85%,充满腐蚀性气体的场所,也不适用于吊运溶化金属和有毒、易燃、易爆物品。

二、结构特征与工作原理本系列产品由桥架、起升机构、小车运行、大车运行和电气四个主要部分组成。

采用小车式的钢丝绳电动葫芦作为起升机构。

起重机装配试验应符合《GB/T3695-1994》之规定,安装起重机时,必须按附图的规定进行安装。

起重机在拆卸运输和产品安装时,端梁的连接必须按图纸规定拆装。

(一)、主梁本系列采用三梁结构,主梁与端梁用高强螺栓连接,为了防止运行机构行驶到极限位置时,主梁左右两侧设有缓冲块。

(二)、起升机构起升机构采用的电动葫芦为专业厂家联合设计生产的电动葫芦,其结构特点详见有关电动葫芦说明书。

(三)、大车大车运行机构采用四轮驱动,驱动电机为2台锥形制动电机,驱动轮的数量为总轮数量的一半。

(四)、电气系统1、概述起重机各个机构的运转,由地面控制按钮盒进行操作。

地面控制按钮盒与电控设备相配合,对各机构电动机实现启动、换向升降、制动。

电控系统保证大车运行机构操作的地面控制按钮盒无论是换向还是升降,都能够使运行电机平稳的启动、制动。

当地面控制按钮盒从运行换向转升降(升降转换向)时,应先停止运行。

从而改善了起重机操作性能和运行指标,减少了电气设备的启动次数,提高了起重机的电气寿命和可靠性。

LD型电动单梁桥式起重机资料

LD型电动单梁桥式起重机资料LD型电动单梁桥式起重机一、简单介绍LD型电动单梁桥式起重机(以下简称起重机)是按标准JB1306-2008设计制造的,与CDI、MDI等形式的电动葫芦配套使用,成为一种有轨运行的轻小型起重机,其适用起重量为1-10吨,适用跨度为7.5~22.5米,工作环境温度在-25~+40℃范围内。

为方便用户,设有地面和操纵室两种操纵形式,操纵室又设有端面及侧面开门两种形式,以供用户选择。

本产品为一般用途起重机,多用于机械制造、装配、仓库等场所,其结构特点如下:1、金属结构部分主梁采用钢板压延成形的U形槽钢,再与工字钢组焊成箱形实腹梁。

横梁也是用钢板压延成U形槽钢,再组焊成箱形横梁。

为贮存运输方便。

主横梁之用M20螺栓(45号钢)连接而成桥架。

2、电动葫芦电动葫芦可起升重物,并沿主梁横向移动,其结构特点详见有关电动葫芦说明书。

3、运行机构本产品是采用分别驱动形式,制动靠锥形制动电机来完成,传动是“一开二闭”式三级齿轮传动。

4、电气设备本产品所用运行电动机有单速锥形鼠笼电动机(用于运行速度20、30和45米/分)地操和锥形绕线电动机(用于运行速度45、60、75米/分)驾操二种形式,随操纵形式不同,设有两种电气控制。

电动葫芦及整个起重机均设有安全装置,如起升限位开关,终点限位开关等。

5、本产品规格表示方法如下(1)地面操纵例:起重量3吨,跨度10.5米,运行速度30米/分。

表示方法:LD3-10.5-30(2)操纵室操纵例:起重量5吨,跨度16.5米,运行60米/分。

表示方法:LDC5-16.5-60三、性能参数表1.技术规格:2.总重及轮压吨位操纵型式跨度(m)吨位(T)7.5810.51113.51416.51719.522.51 地操总重1.341.381.551.632.072.122.322.363.003.41最大轮压0.870.880.920.941.041.061.11.111.451.54 驾开操总重1.751.792.022.042.482.532.732.723.403.81最大轮压1.181.191.231.251.351.371.411.421.741.84 驾闭操总重1.771.812.022.002.482.532.732.773.403.81最大轮压1.191.201.241.262.471.371.411.421.741.842 地操总重1.601.651.901.952.262.392.642.693.854.60最大轮压1.461.471.541.551.621.681.741.752.182.38驾开操总重2.012.062.312.362.672.793.043.094.255.00 最大轮压1.771.781.851.861.931.972.042.052.482.68驾闭操总重2.032.082.332.382.672.793.043.094.255.00 最大轮压1.791.801.871.881.931.972.042.052.482.683 地操总重1.701.752.002.052.352.582.922.974.284.83最大轮压1.992.002.072.092.152.222.323.372.809.24 驾开操总重2.112.162.412.462.762.983.323.374.685.23最大轮压2.302.312.382.402.462.522.622.633.103.24 驾闭操总重2.132.182.432.482.762.983.323.374.085.23最大轮压2.322.332.402.422.462.522.622.633.103.245 地操总重2.002.052.302.482.882.943.243.304.575.65最大轮压3.093.123.203.243.343.353.443.463.854.20驾开操总重2.412.462.712.893.293.353.653.714.976.05 最大轮压3.403.433.513.553.653.663.753.774.234.58驾闭操总重2.432.482.732.913.293.353.653.714.976.05 最大轮压3.423.453.533.573.653.663.753.774.234.581 0 地操总重2.892.973.403.514.134.224.995.096.147.27最大轮压5.515.535.645.675.815.836.036.056.326.60 驾开操总重3.293.373.803.914.534.625.395.496.547.67最大轮压5.815.835.945.976.116.136.336.956.446.71 驾闭操总重3.393.373.803.914.534.625.395.496.547.67最大轮压5.815.835.945.976.116.136.336.956.446.71四、安装横梁主梁图2 主梁与横梁连接1、在用户现场上将起重机运行机构的驱动装置安装在横梁上。

IDT72T51546资料

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

1

2003 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice.

FEATURES:

•

• • • • • •

• • • • • • •

Choose from among the following memory density options: IDT72T51546 Total Available Memory = 1,179,648 bits IDT72T51556 Total Available Memory = 2,359,296 bits Configurable from 1 to 32 Queues Queues may be configured at master reset from the pool of Total Available Memory in blocks of 256 x 36 Independent Read and Write access per queue User programmable via serial port User selectable I/O: 2.5V LVTTL, 1.5V HSTL, 1.8V eHSTL Default multi-queue device configurations – IDT72T51546 : 1,024 x 36 x 32Q – IDT72T51556 : 2,048 x 36 x 32Q 100% Bus Utilization, Read and Write on every clock cycle 200 MHz High speed operation (5ns cycle time) 3.6ns access time Echo Read Enable & Echo Read Clock Outputs Individual, Active queue flags (OV, FF, PAE, PAF, PR) 8 bit parallel flag status on both read and write ports Shows PAE and PAF status of 8 Queues

IDT54FCT166H244CTE资料

1Y11Y21Y31Y41A11A21A31A42OE2A12A22A32A42Y12Y22Y32Y41OE33A13A23A33A43Y13Y23Y33Y444A14A24A34A44Y14Y24Y34Y4The IDT logo is a registered trademark of Integrated Device Technology, Inc.MILITARY AND COMMERCIAL TEMPERATURE RANGES OCTOBER 1996•Common features:–0.5 MICRON CMOS Technology–High-speed, low-power CMOS replacement forABT functions–Typical t SK(o) (Output Skew) < 250ps–Low input and output leakage ≤ 1µA (max.)–ESD > 2000V per MIL-STD-883, Method 3015;> 200V using machine model (C = 200pF, R = 0)–Packages include 25 mil pitch SSOP, 19.6 mil pitchTSSOP, 15.7 mil pitch TVSOP and 25 mil pitch Cerpack–Extended commercial range of -40°C to +85°C•Features for FCT16244T/AT/CT/ET:–High drive outputs (-32mA I OH, 64mA I OL)–Power off disable outputs permit “live insertion”–Typical V OLP (Output Ground Bounce) < 1.0V atV CC = 5V, T A = 25°C•Features for FCT162244T/AT/CT/ET:–Balanced Output Drivers:±24mA (commercial),±16mA (military)–Reduced system switching noise–Typical V OLP (Output Ground Bounce) < 0.6V atV CC = 5V,T A = 25°C•Features for FCT166244T/AT/CT:–Light Drive Balanced Output: ±8mA (commercial),±6mA (military)–Minimal system switching noise–Typical V OLP (Output Ground Bounce) < 0.25V atV CC = 5V,T A = 25°C•Features for FCT162H244T/AT/CT/ET:–Bus-Hold retains last active bus state during 3-state–Eliminates the need for external pull up resistorsThe 16-Bit Buffer/Line Driver is for bus interface or signal bufferingapplications requiring high speed and low power dissipation. Thesedevices have a flow through pin organization, and shrink packagingto simplify board layout. All inputs are designed with hysteresis forimproved noise margin. The three-state controls allow independent4-bit, 8-bit or combined 16-bit operation. These parts are plug inreplacements for 54/74ABT16244 where higher speed, lower noiseor lower power dissipation levels are desired.The FCT16244T/AT/CT/ET are ideally suited for drivinghigh capacitance loads (>200pF) and low impedancebackplanes. These "high drive" buffers are designed withpower off disable capability to allow "live insertion" of boardswhen used in a backplane interface.The FCT162244T/AT/CT/ET have balanced output currentlevels and current limiting resistors. These offer low groundbounce, minimal undershoot, and controlled output fall times,reducing the need for external series terminating resistorswhile still providing very high speed operation for loads of lessthan 200pF.The FCT166244T/AT/CT are suited for very low noise,point-to-point driving where there is a single receiver, or a verylight lumped load (<100pF). The buffers are designed to limitthe output current to levels which will avoid noise and ringingon the signal lines without using external series terminatingresistors.The FCT162H244T/AT/CT/ET have "Bus-Hold" which re-tains the input's last state whenever the input goes to highimpedance. This prevents "floating" inputs and eliminates theneed for pull-up/down resistors.PIN CONFIGURATIONS1Y 1GND1Y 3V CC1OE GND3Y 2GNDV CCGND1Y 21Y 42Y 12Y 22Y 32Y 43Y 13Y 33Y 44Y 14Y 34Y 44Y 24OE1A 11A 2GND1A 31A 4V CC2A 12A 22A 32A 43A 13A 23A 33A 4V CC4A 14A 34A 44A 2GNDGNDGND2OE 3OE2544 drw 04CERPACK TOP VIEW2544 tbl 011. On FCT16xH these pins have “Bus-hold”. All other pins are standard inputs, outputs or I/Os.1Y 1GND1Y 3V CCGND3Y 2GNDV CCGND1Y 21Y 42Y 12Y 22Y 32Y 43Y 13Y 33Y 44Y 14Y 34Y 44Y 24OE1A 11A 2GND1A 31A 4V CC2A 12A 22A 32A 43A 13A 23A 33A 4V CC4A 14A 34A 44A 2GNDGNDGND23OE2544 drw 03SSOP/TSSOP/TVSOP TOP VIEW1NOTE:1. This parameter is measured at characterization but not tested.(T A = +25°C, f = 1.0MHz)FUNCTION TABLE (1)1.H = HIGH Voltage Level X = Don’t CareL = LOW Voltage Level Z = High ImpedanceABSOLUTE MAXIMUM RATINGS (1)DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (STANDARD PARTS)Following Conditions Apply Unless Otherwise Specified:NOTES:1.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at Vcc = 5.0V, +25°C ambient.3.Not more than one output should be tested at one time. Duration of the test should not exceed one second.4.Duration of the condition can not exceed one second.5.The test limit for this parameter is ± 5µA at T A = –55°C.1.Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGSmay cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2.All device terminals except FCT162XXXT and FCT166XXXT output andI/O terminals.3.Output and I/O terminals for FCT162XXXT and FCT166XXXT.DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (BUS-HOLD)Following Conditions Apply Unless Otherwise Specified:NOTES:2544 lnk 061.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at Vcc = 5.0V, +25°C ambient.3.Not more than one output should be tested at one time. Duration of the test should not exceed one second.4.Pins with Bus-hold are identified in the pin description.5.The test limit for this parameter is ± 5µA at T A = –55°C.6.Does not include Bus-hold I/O pins.NOTES:1.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at Vcc = 5.0V, +25°C ambient.3.Not more than one output should be tested at one time. Duration of the test should not exceed one second.4.Duration of the condition can not exceed one second.5.The test limit for this parameter is ± 5µA at T A = –55°C.NOTES:1.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at V CC = 5.0V, +25°C ambient.3.Per TTL driven input (V IN = 3.4V). All other inputs at V CC or GND.4.This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.5.Values for these conditions are examples of the I CC formula. These limits are guaranteed but not tested.6.I C = I QUIESCENT + I INPUTS + I DYNAMICI C = I CC + ∆I CC D H N T + I CCD (f CP N CP/2 + f i N i)I CC = Quiescent Current (I CCL, I CCH and I CCZ)∆I CC = Power Supply Current for a TTL High Input (V IN = 3.4V)D H = Duty Cycle for TTL Inputs HighN T = Number of TTL Inputs at D HI CCD = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)f CP = Clock Frequency for Register Devices (Zero for Non-Register Devices)N CP = Number of Clock Inputs at f CPf i = Input FrequencyN i = Number of Inputs at f i2544 tbl 112544 tbl 12 NOTES:1.See test circuit and waveforms.2.Minimum limits are guaranteed but not tested on Propagation Delays.3.Skew between any two outputs of the same package switching in the same direction. This parameter is guaranteed by design.TEST CIRCUITS AND WAVEFORMS TEST CIRCUITS FOR ALL OUTPUTSC L =Load capacitance: includes jig and probe capacitance.R T =Termination resistance: should be equal to Z OUT of the PulseGenerator.7.0V3V 1.5V 0V3V 1.5V 0V 3V 1.5V 0V 3V 1.5V 0V DATA INPUTPRESET CLEAR ETC.1.5V1.5VSAME PHASE INPUT TRANSITION3V 1.5V 0V 1.5V V OH OUTPUTOPPOSITE PHASE INPUT TRANSITION3V 1.5V 0VV OL 3V 1.5V 0V 3.5V0V V OLENABLEDISABLEV OH PRESET CLEARCLOCK ENABLEETC.SET-UP, HOLD AND RELEASE TIMESPULSE WIDTHENABLE AND DISABLE TIMESPROPAGATION DELAY 2544 drw 072544 drw 06NOTES:1.Diagram shown for input Control Enable-LOW and input Control Disable-HIGH2.Pulse Generator for All Pulses: Rate ≤ 1.0MHz; t F ≤ 2.5ns; t R ≤ 2.5ns2544 drw 092544 drw 08ORDERING INFORMATIONIDT XXTemp. RangeXXXXDevice TypeXPackageXProcessBlankBPVPAPFE244T244AT244CT244ETCommercialMIL-STD-883, Class BShrink Small Outline Package (SO48-1)Thin Shrink Small Outline Package (SO48-2)Thin Very Small Outline Package (SO48-3)CERPACK (E48-1)Non-Inverting 16-Bit Buffer/Line Driver5474–55°C to +125°C–40°C to +85°CFCT2544 drw 10 XDriveBlankHStandardBus-holdXBus Hold1616216616-Bit High Drive16-Bit Balanced Drive16-Bit Light Drive。

BAT54CWT1G;BAT54CWT1;中文规格书,Datasheet资料

TA = 150C TA = 125C

TA = 85C

Figure 3. Leakage Current

14 CT, TOTAL CAPACITANCE (pF) 12 10 8 6 4 2 0 0 5 10 15 20 25 30

VR, REVERSE VOLTAGE (VOLTS)

Figure 4. Total Capacitance

Figure 1. Recovery Time uivalent Test Circuit

2

/

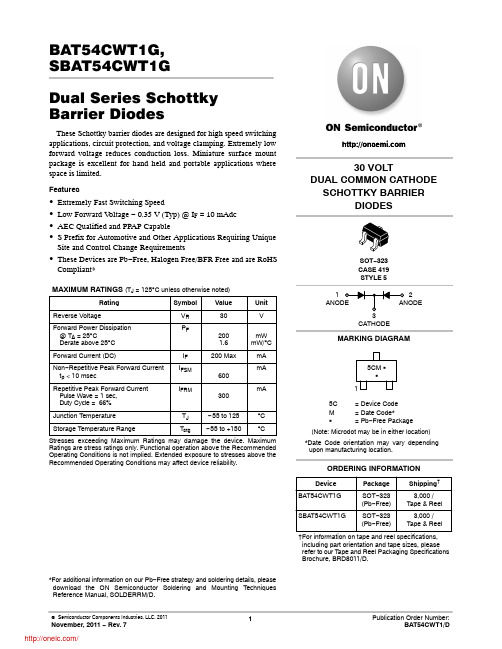

BAT54CWT1G, SBAT54CWT1G

100 1 25C IF, FORWARD CURRENT (mA) 85C 10 1 50C 1.0 25C 0.1 0.0 − 40C

e1

3

HE

1 2

E

b e

A 0.05 (0.002) A1

A2 L

c

STYLE 5: PIN 1. ANODE 2. ANODE 3. CATHODE

SOLDERING FOOTPRINT*

0.65 0.025 0.65 0.025

1.9 0.075 0.9 0.035 0.7 0.028

SCALE 10:1 mm Ǔ ǒinches

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

IDT72T54262L5BBI资料

FIFO 2 Data Out

Read Port Flag Outputs

Write Port Flag Outputs

FF0/IR0 PAF0 FF2/IR2 PAF2

EF0/OR0 PAE0 EF2/OR2 PAE2

6158 drw02

2

MARCH 22, 2005

元器件交易网

FIFO 3 Data Out

FF0/IR0 PAF0 FF1/IR1 PAF1 FF2/ IR2 PAF2 FF3/IR3 PAF3

Read Port Flag Outputs

IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. The TeraSync is a trademark of Integrated Device Technology, Inc.

Write Port Flag Outputs

6158 drw01

(See next page for Dual Mode)

MARCH 2005

DSC-6158/3

1

元器件交易网

IDT72T54242/72T54252/72T54262 2.5V QUAD/DUAL TeraSync™ DDR/SDR FIFO 32K x 10 x 4/16K x 20 x 2, 64K x 10 x 4/32K x 20 x 2 and 128K x 10 x 4/64K x 20 x 2

x10 or x20

WCLK0 WEN0 WCS0

32,768 x 10/16,384 x 20 65,536 x 10/32,768 x 20 131,072 x 10/65,536 x 20

IDT54FCT164245T中文资料

MILITARY AND COMMERCIAL TEMPERATURE RANGES

PIN DESCRIPTION

Pin Names xOE xDIR xAx xBx

Description Output Enable Input (Active LOW) Direction Control Input Side A Inputs or 3-State Outputs (3.3V Port) Side B Inputs or 3-State Outputs (5V Port)

or 5V circuits • ESD >2000V per MIL-STD-883, Method 3015;

>200V using machine model (C = 200pF, R = 0) • 25 MIL Center SSOP and Cerpack Packages • Extended commercial range of -40°C to +85°C • VCC1 = 5V ±10%, VCC2 = 2.7V to 3.6V • High drive outputs (-32mA IOH, 64mA IOL) on 5V port • Power-off disable on both ports permits "live insertion" • Typical VOLP (Output Ground Bounce) < 0.9V at

Z = High Impedance

2555 tbl 03

ABSOLUTE MAXIMUM RATINGS(1)

Symbol

Rating

VTERM(2) Terminal Voltage with Respect to GND

LVTH16374中文资料

48 1CLK 47 1D1 46 1D2 45 GND 44 1D3 43 1D4 42 VCC 41 1D5 40 1D6 39 GND 38 1D7 37 1D8 36 2D1 35 2D2 34 GND 33 2D3 32 2D4 31 VCC 30 2D5 29 2D6 28 GND 27 2D7 26 2D8 25 2CLK

OE does not affect internal operations of the flip-flop. Old data can be retained or new data can be entered while the outputs are in the high-impedance state.

• Ioff and Power-Up 3-State Support Hot Insertion

• Bus Hold on Data Inputs Eliminates the Need for External Pullup/Pulldown Resistors

• Distributed VCC and GND Pins Minimize High-Speed Switching Noise

– 200-V Machine Model (A115-A)

SN54LVTH16374 . . . WD PACKAGE SN74LVTH16374 . . . DGG OR DL PACKAGE

TLC549中文介绍与参考程序

TLC549中文介绍与参考程序TLC549使用单电源供电,工作电压范围为2.7V至5.5V。

它采用内部运算放大器和参考电压,具有高共模抑制比和低失调电压,提供准确的测量结果。

通过SPI接口,可以轻松地将数据传输到微控制器或其他数字设备。

以下是TLC549的主要特性:1.高精度:TLC549是一款12位的ADC,可以实现精确的模拟信号转换。

2.内部参考电压:TLC549已集成内部参考电压和运算放大器,可消除外部参考电压的需求,并提供更好的测量精度。

3.低功耗:TLC549在工作模式下的功耗非常低,适合各种低功率应用。

4.SPI接口:TLC549采用串行外围接口(SPI)进行数据传输,与微控制器和其他数字设备兼容。

5.可编程的采样率:TLC549的采样率可以通过控制输入引脚进行编程,以满足不同应用的要求。

下面是一个使用TLC549的参考程序,该程序可以读取模拟信号并将其转换为数字值:```#include <SPI.h>const int chipSelectPin = 10; // SPI芯片选择引脚int val = 0; // 储存读取到的模拟值void setuSerial.begin(9600);SPI.begin(;pinMode(chipSelectPin, OUTPUT);digitalWrite(chipSelectPin, HIGH); // 初始化SPI芯片选择引脚void loodigitalWrite(chipSelectPin, LOW); // 选中TLC549芯片delayMicroseconds(10);SPI.transfer(0x00); // 发送开始转换命令delayMicroseconds(10);val = SPI.transfer(0x00); // 读取转换结果的高8位val = (val << 8) + SPI.transfer(0x00); // 读取转换结果的低4位digitalWrite(chipSelectPin, HIGH); // 取消选中TLC549芯片Serial.println(val); // 打印转换结果delay(1000);```上述程序使用了SPI库,首先在`setup(`函数中初始化SPI通信,并设置芯片选择引脚为输出模式。

亚德客CT4S说明书

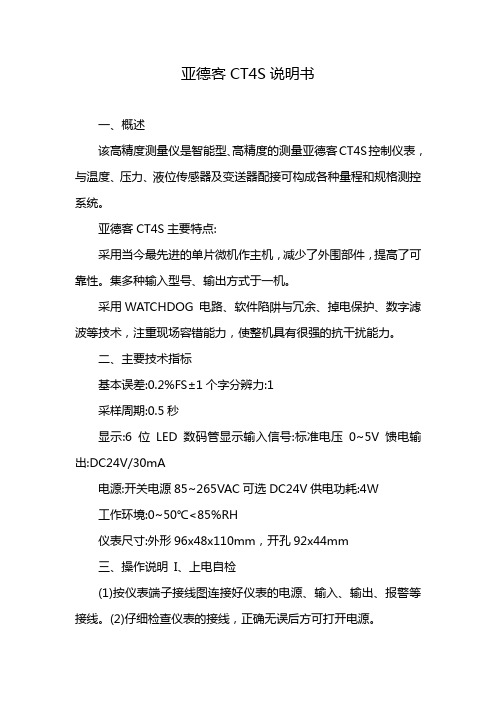

亚德客CT4S说明书一、概述该高精度测量仪是智能型、高精度的测量亚德客CT4S控制仪表,与温度、压力、液位传感器及变送器配接可构成各种量程和规格测控系统。

亚德客CT4S主要特点:采用当今最先进的单片微机作主机,减少了外围部件,提高了可靠性。

集多种输入型号、输出方式于一机。

采用WATCHDOG 电路、软件陷阱与冗余、掉电保护、数字滤波等技术,注重现场容错能力,使整机具有很强的抗干扰能力。

二、主要技术指标基本误差:0.2%FS±1个字分辨力:1采样周期:0.5秒显示:6位LED数码管显示输入信号:标准电压0~5V馈电输出:DC24V/30mA电源:开关电源85~265VAC可选DC24V供电功耗:4W工作环境:0~50℃<85%RH仪表尺寸:外形96x48x110mm,开孔92x44mm三、操作说明I、上电自检(1)按仪表端子接线图连接好仪表的电源、输入、输出、报警等接线。

(2)仔细检查仪表的接线,正确无误后方可打开电源。

(3)接通亚德客CT4S电源后仪表显示HELO字样表示仪表自检通过,如果显示HH-表示输入信号未接或超量程或断偶或热阻开路。

仪表采用人机对话形式来输入参数,用各种提示符来提示应轴入的数据。

I、按键功能在设定状态时,用于切换显示参数提示符和相应的设定值。

En-在设定状态时,用于存贮参数的新设定值并进入下一设定参数。

在设定状态时,用于增加设定值。

-在设定状态时,用于减少设定值。

Ⅲ、参数设定按住En键不动,超过2秒钟后仪表显示-Cd,按下键出现800,用键将800设成808后再按En键才进入参数设定状态,输入其他值无效,这主要是为了防止现场操作人员误修改参数。

(1)dot一小数点设定,范围0~3。

(2)inPL一线性输入下限对应显示值,即仪表量程下限,范围0-199999。

(3)inPH一线性输入上限对应显示值,即仪表量程上限,范围0~99999。

(4)oSEt一调零点校正系数范围-999~99.9,修正后显示值=修正前测量值+oSEt出厂值oSEt=0.0(5)FSEt一调满度校正系数范围0500~2.000,修正后显示值=FSEtx(修正前的测量值+oSEt),出厂值FSEt=1.000。

WIC1--中文简介

- 一段 定时限

WIC1 CT 范围

kVA 250 315 400 500 630 800 1000 1250 1600 2000 2500 3150 4000 6 kV 24 30 39 48 61 77 96 120 154 193 241 303 385 10 kV 14,4 18 23 29 36 46 58 72 92 116 144 182 231 15 kV 20 kV 15 19 24 31 39 48 62 77 96 121 154

WIC11 2 3 4

P

* E

* -W

跳牌指示器

Small type, front 34 x 23 mm, connection lead 1m

WIC1SZ4

Small type, front 34 x 23 mm, connection lead 1m with bi-stable signal contact 230V AC, 3A

内置断路器的环网柜

ABB SAFE柜

内置断路器的环网柜

欧玛嘉宝(珠海) LFF6柜

内置断路器的环网柜

伊顿公司 西瑞柜

内置断路器的环网柜

西门子 SIMOSEC柜

内置断路器的环网柜

GE Seco柜

WIC1保护特性

10000

•一般反时限 (Type A)

1000

•非常反时限 (Type B)

•极反时限 (Type C)

W2: 16 - 56 A W3 : 32 - 112 A W4: 64 - 224 A

WIC1-W2 WIC1-W3 WIC1-W4 WIC1-W5

14,4 18 23 29 36 46 58 72 91 116

ct4-42安全技术说明书

ct4-42安全技术说明书

1、TÜV 的安全认证,安全等级达到Type 4 Cat. 4 PL e

2、盲区小,节省安装空间

3、IP65/IP67 防护等级,高防护能力

4、通光面防撞设计,型材壁厚3mm,强力抗冲击碰撞

5、指示信息丰富,分路指示显示每光束状态,具备接线自检功能

6、内外减振设计,良好的抗振性能

7、高强度支架,多种安装方式

8、“安全”看的见,强力的MTTFD、MTTF数据支撑

产品组成

CT4 型安全光栅系统包括一个发射器、一个接收器和两根传输线。

系统采用DC24V工作,提供两路PNP输出、外部设备监控(EDM)功能和一路辅助输出(非安全),并配备状态指示功能。

检测距离有8m、15m两种规格,检测精度有14mm、30mm和46mm三种规格,检测高度232 mm~1672 mm,扩展精度120mm。

74ALVT16374资料

元器件交易网SSOP48:plastic shrink small outline package; 48 leads; body width 7.5 mm SOT370-1TSSOP48:plastic thin shrink small outline package; 48 leads; body width 6.1mm SOT362-1DefinitionsShort-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.DisclaimersLife support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.Philips Semiconductors811 East Arques AvenueP.O. Box 3409Sunnyvale, California 94088–3409Telephone 800-234-7381© Copyright Philips Electronics North America Corporation 1999All rights reserved. Printed in U.S.A.print code Date of release: 10-99。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

The FCT16374T/AT/CT/ET and FCT162374T/AT/CT/ET 16-bit edge-triggered D-type registers are built using ad-vanced dual metal CMOS technology. These high-speed,low-power registers are ideal for use as buffer registers for data synchronization and storage. The Output Enable (x OE )and clock (xCLK) controls are organized to operate each device as two 8-bit registers or one 16-bit register with common clock. Flow-through organization of signal pins sim-plifies layout. All inputs are designed with hysteresis for improved noise margin.The FCT16374T/AT/CT/ET are ideally suited for driving high-capacitance loads and low-impedance backplanes. The output buffers are designed with power off disable capability to allow "live insertion" of boards when used as backplane drivers.The FCT162374T/AT/CT/ET have balanced output drive with current limiting resistors. This offers low ground bounce,minimal undershoot, and controlled output fall times– reduc-ing the need for external series terminating resistors. The FCT162374T/AT/CT/ET are plug-in replacements for the FCT16374T/AT/CT/ET and ABT16374 for on-board bus inter-face applications.FUNCTIONAL BLOCK DIAGRAM1O 111CLK 1D 12542 drw 01O 122CLK2D 1TO 7 OTHER CHANNELS2542 drw 01The IDT logo is a registered trademark of Integrated Device Technology, Inc.MILITARY AND INDUSTRIAL TEMPERATURE RANGES FEBRUARY 1997•Common features:–0.5 MICRON CMOS Technology–High-speed, low-power CMOS replacement for ABT functions–Typical t SK (o) (Output Skew) < 250ps–Low input and output leakage ≤1µA (max.)–ESD > 2000V per MIL-STD-883, Method 3015;> 200V using machine model (C = 200pF, R = 0)–Packages include 25 mil pitch SSOP, 19.6 mil pitchTSSOP, 15.7 mil pitch TVSOP and 25 mil pitch Cerpack –Extended commercial range of -40°C to +85°C –V CC = 5V ±10%•Features for FCT16374T/AT/CT/ET:–High drive outputs (-32mA I OH , 64mA I OL )–Power off disable outputs permit “live insertion”–Typical V OLP (Output Ground Bounce) < 1.0V at V CC = 5V, T A = 25°C•Features for FCT162374T/AT/CT/ET:–Balanced Output Drivers:±24mA (commercial),±16mA (military)–Reduced system switching noise–Typical V OLP (Output Ground Bounce) < 0.6V at V CC = 5V,T A = 25°CPIN CONFIGURATIONS1O 1GND1O 3V CC1OE GND2O 2GNDV CCGND1O 21O 41O 51O 61O 71O 82O 12O 32O 42O 52O 72O 82O 62OE1CLK 1D 11D 2GND1D 31D 4V CC1D 51D 61D 71D 82D 12D 22D 32D 4V CC2D 52D 72D 82D 62CLKGNDGNDGND2542 drw 04CERPACK TOP VIEW1O 1GND1O 3V CC1OE GND2O 2GNDV CCGND1O 21O 41O 51O 61O 71O 82O 12O 32O 42O 52O 72O 82O 621CLK 1D 11D 2GND1D 31D 4V CC1D 51D 61D 71D 82D 12D 22D 32D 4V CC2D 52D 72D 82D 62CLKGNDGNDGND2542 drw 03SSOP/TSSOP/TVSOP TOP VIEWPIN DESCRIPTIONFUNCTION TABLE (1)(1)CAPACITANCE (T A = +25°C, f = 1.0MHz)2542 tbl 02NOTE:1. This parameter is measured at characterization but not tested.2542 lnk 041.H = HIGH Voltage Level L = LOW Voltage Level X = Don’t CareZ = High Impedance↑ = LOW-to-HIGH TransitionNOTES:1.Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2.All device terminals except FCT162XXXT Output and I/O terminals.3.Output and I/O terminals for FCT162XXXT.2542 lnk 03DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGEFollowing Conditions Apply Unless Otherwise Specified:NOTES:1.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at Vcc = 5.0V, +25°C ambient.3.Not more than one output should be tested at one time. Duration of the test should not exceed one second.4.Duration of the condition can not exceed one second.5.The test limit for this parameter is ± 5µA at T A = –55°C.NOTES:1.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at V CC = 5.0V, +25°C ambient.3.Per TTL driven input (V IN = 3.4V). All other inputs at V CC or GND.4.This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.5.Values for these conditions are examples of the I CC formula. These limits are guaranteed but not tested.6.I C = I QUIESCENT + I INPUTS + I DYNAMICI C = I CC + ∆I CC D H N T + I CCD (f CP N CP/2 + f i N i)I CC = Quiescent Current (I CCL, I CCH and I CCZ)∆I CC = Power Supply Current for a TTL High Input (V IN = 3.4V)D H = Duty Cycle for TTL Inputs HighN T = Number of TTL Inputs at D HI CCD = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)f CP = Clock Frequency for Register Devices (Zero for Non-Register Devices)N CP = Number of Clock Inputs at f CPf i = Input FrequencyN i = Number of Inputs at f iSWITCHING CHARACTERISTICS OVER OPERATING RANGE1.See test circuit and waveforms.2.Minimum limits are guaranteed but not tested on Propagation Delays.3.Skew between any two outputs of the same package switching in the same direction. This parameter is guaranteed by design.4.This limit is guaranteed but not tested.C L =Load capacitance: includes jig and probe capacitance.R T =Termination resistance: should be equal to Z OUT of the PulseGenerator.TEST CIRCUITS AND WAVEFORMS TEST CIRCUITS FOR ALL OUTPUTSENABLE AND DISABLE TIMESPROPAGATION DELAYSET-UP, HOLD AND RELEASE TIMES PULSE WIDTHSWITCH POSITIONNOTES:1.Diagram shown for input Control Enable-LOW and input Control Disable-HIGH2.Pulse Generator for All Pulses: Rate ≤ 1.0MHz; t F ≤ 2.5ns; t R ≤ 2.5ns2542 drw 097.0V3V 1.5V 0V3V 1.5V 0V 3V 1.5V 0V 3V 1.5V 0V DATA INPUTPRESET CLEAR ETC.1.5V1.5VSAME PHASE INPUT TRANSITION3V 1.5V 0V 1.5V V OH OUTPUTOPPOSITE PHASE INPUT TRANSITION3V 1.5V 0VV OL 3V 1.5V0V 3.5V 0VV OLENABLEDISABLEV OHPRESET CLEARCLOCK ENABLEETC.2542 drw 052542 drw 062542 drw 082542 drw 07ORDERING INFORMATIONIDT XX XXXX X XBlank BPV PA PFE CommercialMIL-STD-883, Class BShrink Small Outline Package (SO48-1) Thin Shrink Small Outline Package (SO48-2) Thin Very Small Outline Package (SO48-3) CERPACK (E48-1)Non-Inverting 16-Bit Register54 74–55°C to +125°C –40°C to +85°CFCT2542 drw 10。