芯片静电测试标准

静电测试标准

静电测试标准批准:审核:张闯编制:赵继勇2004年12月24日上传:开发部静电测试标准一般情况下,静电测试分为两种方式,一种为接触静电测试,另一种是非接触静电测试,通常电子元器件的接触防静电电压值要低于非接触防静电电压值。

工业防静电标准:接触防静电电压6 kV,非接触防静电电压8 kV。

静电测试前的准备工作:·连接好准备测试的设备,确保测试前的设备是正常运行的。

·连接好静电放电测试仪,确保测试仪的地线与设备的地线相互连接,形成放电回路。

1. 接触静电测试测试项目包括设备机箱外壳,电源接口,控制接口,以及通讯接口等。

测试电压标准,测试静电电压从2 kV开始增加,每次增加2 kV,直到20 kV为止,即测试静电电压分别为2 kV,4 kV,6 kV,8 kV,10 kV,12 kV,14 kV,16 kV,18 kV,20 kV。

测试频率标准,测试放电分为两种频率,但放电次数均为10次。

一种频率是1秒钟放电1次,连续放电10次,为低频静电放电测试;另一种频率是0.1秒钟放电1次,连续放电10次,为高频静电放电测试。

测试通过标准,硬件无任何损坏,通讯正常,数据无错误,丢失等情况。

测试停止标准,在测试某一项目时,如果硬件发生损坏,通讯异常或其他任何不正常的情况,测试将不向更高标准进行,而只统计当前测试结果。

测试转为下一项。

为提高测试精度,也可以在测试设备出现异常情况时,先调低静电电压1 kV进行测试,如果测试通过,则调高静电电压0.5 kV进行测试,如果测试不通过,则继续调低静电电压0.5 kV进行测试,依次类推,调节幅度不断减小为0.25 kV,0.125 kV等,直到精度达到要求为止,统计临界静电电压测试结果。

测试顺序标准,测试顺序为先确定电压,再确定频率。

电压由低到高,频率由慢到快。

即依次为2 kV低频测试,2 kV高频测试,4 kV低频测试,4 kV高频测试,直到20 kV低频测试,20 kV高频测试。

静电测试仪的测试标准

静电测试仪的测试标准静电测试仪是一种用于评估静电电荷的设备,广泛应用于电子工业、化工、纺织等行业中。

为了保证静电测试仪的可靠性和准确性,需要依据相关标准进行测试。

以下是一些常用的静电测试仪的测试标准。

1. 静电测试仪的基本指标测试静电测试仪的基本指标包括测试精度、测量范围、静电感应时间等,这些指标是评估静电测试仪性能的关键参数。

测试时需要使用一个标准静电电荷源,将其放置在一定距离内,然后记录静电测试仪的测量结果。

根据标准,测试结果应该与实际值相符合,并且测试仪应具备足够的测量范围和灵敏度。

2. 静电测试仪的稳定性测试静电测试仪的稳定性是指测试仪在长时间使用过程中的性能表现。

稳定性测试需要使用一个稳定的静电电荷源,将其放置在一定的距离内,然后连续进行多次测试,并记录每次测试的结果。

通过对比这些结果,评估静电测试仪的稳定性表现,确保其能够在长时间使用过程中保持准确性。

3. 静电测试仪的抗干扰能力测试静电测试仪在使用过程中可能会受到来自周围环境的干扰,如电磁场、静电场等。

为了评估静电测试仪的抗干扰能力,可以使用一个产生干扰的设备,将其放置在一定距离内,然后进行测试。

测试结果应该表明,静电测试仪在受到干扰时能够保持较高的准确性和稳定性。

4. 静电测试仪的可靠性测试静电测试仪的可靠性是指其在规定条件下能够保持性能的能力。

可靠性测试可以采用多种方法,如长时间连续测试、高温高湿环境测试等。

通过这些测试,评估静电测试仪在不同条件下的表现,并确保其能够长期、稳定地工作。

5. 静电测试仪的安全性测试静电测试仪在使用过程中需要与人体接触,因此其安全性也是一个重要的考虑因素。

安全性测试可以包括对测试仪外壳的绝缘性能、接地连接的稳定性等方面的测试。

测试结果应该表明,静电测试仪在使用过程中不会对人体造成伤害,并且具备良好的安全性能。

注:以上测试标准仅供参考,具体测试操作和要求应根据实际情况和相关行业标准进行制定。

在进行静电测试仪的测试时,应确保测试过程和测试设备的准确性,并严格按照测试标准进行操作,以保证测试结果的可靠性。

芯片可靠性测试标准

芯片可靠性测试标准芯片可靠性测试标准是指对芯片在特定条件下的可靠性进行测试的标准。

芯片作为电子产品的核心部件,其可靠性直接关系到产品的质量和稳定性。

因此,制定和执行严格的可靠性测试标准对于保证产品质量至关重要。

首先,芯片可靠性测试标准应包括环境适应性测试。

在不同的环境条件下,芯片的性能表现可能会有所不同。

因此,需要对芯片在高温、低温、潮湿、干燥等不同环境条件下的工作情况进行测试,以确保其在各种环境下都能正常工作。

其次,电气特性测试也是芯片可靠性测试标准中的重要内容。

包括对芯片的电压、电流、功耗等电气特性进行测试,以确保芯片在正常工作条件下不会出现电气性能不稳定的情况。

此外,还需要进行可靠性寿命测试。

通过对芯片在长时间工作情况下的稳定性进行测试,以评估其在长期使用过程中的可靠性表现。

这对于一些长寿命产品尤为重要,如航空航天、医疗器械等领域的电子产品。

另外,还需要进行可靠性退化测试。

随着芯片使用时间的增长,其性能可能会出现退化。

因此,需要对芯片在长时间使用后的性能进行测试,以评估其退化情况,并在设计阶段就考虑到这一点,以尽量延长产品的使用寿命。

最后,还需要进行可靠性故障模式测试。

通过对芯片可能出现的各种故障模式进行测试,以评估其在面对不同故障情况时的表现,从而为产品的故障分析和维修提供参考。

综上所述,芯片可靠性测试标准涵盖了环境适应性测试、电气特性测试、可靠性寿命测试、可靠性退化测试以及可靠性故障模式测试等内容。

通过严格执行这些测试标准,可以有效保证芯片产品的质量和可靠性,提高产品的市场竞争力,满足用户对产品质量和稳定性的需求。

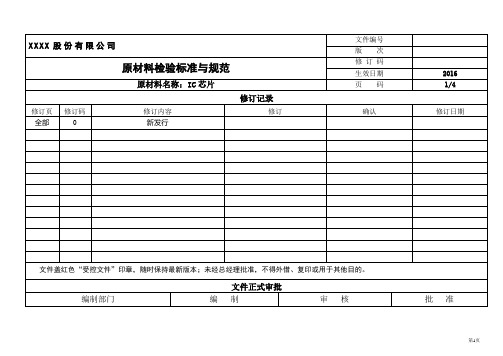

IC芯片检验标准与规范

文件编号

版 次

原材料检验标准与规范

修 订 码

生效日期

2016

原材料名称:IC芯片

页 码

2/4

1.引用标准

GB2828.1-2003《逐批检验计数抽样程序及抽样表(适用于连续批的检验)

2.合格质量充收水准

1. 抽样方案:根据GB2828.1-2003一般检验Ⅱ级水平(LEVEL)及正常检验一次抽样方案。

2 .合格质量水平(AQL):

A类不合格:严重缺点(CRI) AQL:0

B类不合格:主要缺点(MAJ) AQL:0.65

C类不合格:次要缺点(MIN) AQL:1.0

3.常规项目检验标准及检验方法

检验项目

抽样水平

检验方法

检验标准

不良描述

不良判定

检验工具

CR

MA

MI

外观

外包装

全数包装

目视全数外包装

封装形式正确,无混料,包装型号生产批号标识明确

5.检验环境

5.1在本标准中,除气候环境试验和可靠性试验外,其他试验均在下述正常大气条件下进行:

温度:10~35℃

相对湿度:35%~75%

大气压力:86~106kPB

5.2在本标准中,所有目视检验均在40W灯管下1.0米处,1.0以上视力距材料15cm检查10S.

6.相关表格

《进料检验报表》

《进料品质异常单》

√

1.0以上视力

静电环

印字清晰明确

印字模糊不清晰

√

XXXX股份有限公司

文件编号

版 次

原材料检验标准与规范

修 订 码

生效日期

2016

原材料名称:IC芯片

pcba的静电指标_解释说明

pcba的静电指标解释说明1. 引言1.1 概述在现代电子设备中,静电是一种常见的问题。

静电产生的原因是摩擦、分离和接触导致物体表面带电。

当静电不加控制地积聚在PCBA(Printed Circuit Board Assembly,印刷线路板组装)上时,可能会对PCBA造成严重的损坏。

为了保护PCBA免受静电损害,人们必须理解静电指标及其对PCBA的影响,并采取相应的防护措施。

本文将详细介绍PCBA的静电指标以及相关测试方法,并提供一些修复静电问题的方法和技巧。

1.2 文章结构本文共分为五个部分。

首先,概述了本文要讨论的话题以及引言部分内容。

接下来,第二部分将详细介绍PCBA的静电指标,包括静电产生原理、静电对PCBA 的影响以及常见的静电防护措施。

第三部分将介绍测试PCBA静电指标的方法,包括表面绝缘电阻测量方法、接地电阻测量方法以及表面放电测量方法。

第四部分将探讨修复静电问题的方法和技巧,包括静电清除技术介绍、静电包装技术介绍以及消除PCBA静电问题的实践经验总结。

最后,结论部分将对全文进行总结,并展望未来可能的研究方向。

1.3 目的本文的目的是提供关于PCBA的静电指标的详尽解释和说明。

通过深入了解静电产生原理、PCBA受到静电影响的情况以及常见的防护措施,读者将能够更好地了解如何测试和修复PCBA中出现的静电问题。

希望本文能为读者提供有价值的信息,并引起更多关于PCBA静电问题研究方面的注意和兴趣。

2. PCBA的静电指标2.1 静电产生原理静电是指在不同材料之间摩擦或分离时,电子从一个物体转移到另一个物体,使得物体带有正负电荷。

静电的产生主要是由于材料表面的电子在摩擦或分离过程中重新排列所致。

2.2 静电对PCBA的影响静电对PCBA产生的影响主要包括以下几个方面:首先,静电可能导致PCBA元件损坏。

当带有静电的人或物体接触到PCBA上的元件时,通过静电放电会导致元件内部结构被破坏,引起元件故障甚至损坏。

开关电源芯片通用测试要求和步骤-antonychen

开关电源芯片通用测试要求和步骤By Antony Chen开关电源必须通过一系列的测试,使其符合所有功能规格、保护特性、安规(如UL、CSA、VDE、DEMKO、SEMKO,长城等之耐压、抗燃、漏电流、接地等安全规格)、电磁兼容(如FCC、CE等之传导与幅射干扰)、可靠性(如老化寿命测试)、及其他特定要求等。

测试开关电源是否通过设计指标,需要各种精密的电子设备去模拟电源在各种环境下实际工作中的性能。

一、理论上的DCDC测试指标清单1.描述输入电压影响输出电压的几个指标形式(line)1.1绝对稳压系数:K=△Uo/△Ui1.2相对稳压系数:S=△Uo/Uo / △Ui/Ui1.3电网调整率(也称线性调整率):它表示输入电网电压由额定值变化+-10%时,稳压电源输出电压的相对变化量,有时也以绝对值表示。

line reg=△Uo/Uo*100%@ -10%<Ui<+10%1.4电压稳定度:负载电流保持为额定范围内的任何值,输入电压在规定的范围内变化所引起的输出电压相对变化△Uo/Uo(百分值),称为稳压器的电压稳定度。

STB=△Uo/Uo*100%@ 0<I load<max2.负载对输出电压影响的几种指标形式(load)2.1负载调整率(也称电流调整率)在额定电网电压下,负载电流从零变化到最大时,输出电压的最大相对变化量,常用百分数表示,有时也用绝对变化量表示。

2.2输出电阻(也称等效内阻或内阻)在额定电网电压下,由于负载电流变化△IL 引起输出电压变化△Uo,则输出电阻为Ro=|△Uo/△IL|Ω3.纹波电压的几个指标形式(ripple)3.1最大纹波电压在额定输出电压和负载电流下,输出电压的纹波(包括噪声)的绝对值的大小,通常以峰峰值或有效值表示。

V ripple=V MAX-V MIN3.2纹波系数Y(%)在额定负载电流下,输出纹波电压的有效值Urms 与输出直流电压Uo 之比,即Y=Umrs/Uo x100%3.3纹波电压抑制比(PSRR:Power Supply Rejection Ratio)在规定的纹波频率(例如50HZ)下,输入电压中的纹波电压Ui~与输出电压中的纹波电压Uo~之比,即:纹波电压抑制比=Ui~/Uo~ 。

芯片设计中的ESD保护设计要点有哪些

芯片设计中的ESD保护设计要点有哪些在当今高度数字化的时代,芯片作为电子设备的核心组件,其性能和可靠性至关重要。

静电放电(ESD)是导致芯片失效的常见原因之一,因此在芯片设计中,ESD 保护设计成为了不可或缺的环节。

本文将详细探讨芯片设计中 ESD 保护设计的要点。

首先,我们要了解 ESD 现象对芯片造成的危害。

ESD 是指静电荷在不同电位物体之间的快速转移,这种瞬间的高电流和高电压脉冲可能会损坏芯片内部的敏感电路,如晶体管的栅极氧化层、PN 结等,从而导致芯片功能失常甚至完全失效。

那么,在芯片设计中,有哪些关键的 ESD 保护设计要点呢?其一,合理的版图布局是基础。

在芯片版图设计中,应将 ESD 保护器件尽可能靠近芯片的输入输出引脚放置,以缩短 ESD 电流的泄放路径,减少其在芯片内部传播所造成的损害。

同时,要注意避免在敏感电路区域附近布置容易引发 ESD 问题的结构。

其二,选择合适的 ESD 保护器件至关重要。

常见的 ESD 保护器件包括二极管、MOS 管、可控硅(SCR)等。

二极管结构简单,但其能承受的 ESD 电流相对较小。

MOS 管具有较好的性能,但面积较大。

SCR 在承受高 ESD 电流方面表现出色,但触发电压的控制需要精心设计。

设计师需要根据芯片的具体应用场景和性能要求,综合考虑选择合适的保护器件。

其三,优化 ESD 保护电路的参数。

例如,确定保护器件的尺寸、栅极长度、掺杂浓度等,以确保在 ESD 事件发生时,能够快速、有效地泄放电流,同时又不会对正常的芯片工作造成过大的影响。

其四,考虑芯片的工作电压和速度要求。

不同的工作电压和速度会影响 ESD 保护电路的设计。

对于低电压、高速的芯片,需要采用特殊的 ESD 保护技术,以满足其性能要求。

其五,进行全面的仿真和验证。

通过仿真工具,模拟 ESD 事件发生时芯片内部的电流、电压分布情况,评估 ESD 保护设计的效果,并根据仿真结果进行优化调整。

a级防静电标准

a级防静电标准A级防静电标准A级防静电标准是指对电子设备和器件的防静电保护能力达到最高水平,称为A级防静电标准。

A级防静电标准是现代电子工业和微电子技术的必须技术条件之一,保障了电子设备和器件在生产、运输、储存、销售和使用环节中的安全性和可靠性。

A级防静电标准的主要内容包括以下三个方面:1. 静电检测标准静电检测标准是指A级防静电标准规定的静电电压阈值。

在A级防静电标准中,静电检测标准的电压范围为±20V,可用静电检测仪进行检测。

2. 防静电措施标准防静电措施标准是指A级防静电标准规定的针对电子设备和器件进行的各种防静电措施。

主要包括以下几个方面:(1)环境要求。

现代电子工业和微电子技术要求生产车间、储存库房和运输环节中必须保持相对湿度在40%~60%之间,并且温度不能过高,不能过低。

(2)静电散漫设备。

在防静电措施标准中,需要使用静电散漫设备,包括静电散漫妨碍器、静电散漫地板、静电散漫手环和静电散漫服装等。

(3)防静电包装。

在生产、运输和储存过程中,需要对电子设备和器件进行防静电包装,以避免静电的产生和电子设备和器件的损坏。

3. 静电防护设备标准静电防护设备标准是指在A级防静电标准中,规定的一些防静电设备的标准和要求。

主要包括以下几个方面:(1)防静电手腕带。

防静电手腕带是防止人体积累静电的一种防静电设备,必须符合A级防静电标准规定的静电电压阈值。

(2)防静电手套。

防静电手套可以防止手部接触电子设备和器件时产生的静电,必须符合A级防静电标准规定的防静电能力。

(3)静电电源。

静电电源是一种产生静电场的设备,必须符合A级防静电标准规定的静电电压阈值和防静电能力要求。

A级防静电标准是电子工业和微电子技术中必不可少的一项技术条件,它保障了电子设备和器件在生产、运输、储存、销售和使用环节中的安全性和可靠性。

在进行电子设备和器件的生产和使用时,必须全面落实A级防静电标准,并且建立相关的管理和监控机制,确保电子设备和器件的正常运行和长期稳定性。

ESD的原理和测试

ESD的原理和测试微波与电磁兼容轻松学习微波与电磁兼容的基础知识.静电放电(ESD: Electrostatic Discharge),应该是造成所有电⼦元器件或集成电路系统造成过度电应⼒(EOS: Electrical Over Stress)破坏的主要元凶。

因为静电通常瞬间电压⾮常⾼(>⼏千伏),所以这种损伤是毁灭性和永久性的,会造成电路直接烧毁。

所以预防静电损伤是所有IC设计和制造的头号难题。

静电,通常都是⼈为产⽣的,如⽣产、组装、测试、存放、搬运等过程中都有可能使得静电累积在⼈体、仪器或设备中,甚⾄元器件本⾝也会累积静电,当⼈们在不知情的情况下使这些带电的物体接触就会形成放电路径,瞬间使得电⼦元件或系统遭到静电放电的损坏(这就是为什么以前修电脑都必须要配戴静电环托在⼯作桌上,防⽌⼈体的静电损伤芯⽚),如同云层中储存的电荷瞬间击穿云层产⽣剧烈的闪电,会把⼤地劈开⼀样,⽽且通常都是在⾬天来临之际,因为空⽓湿度⼤易形成导电通到。

那么,如何防⽌静电放电损伤呢?⾸先当然改变坏境从源头减少静电(⽐如减少摩擦、少穿⽺⽑类⽑⾐、控制空⽓温湿度等),当然这不是我们今天讨论的重点。

我们今天要讨论的是如何在电路⾥⾯设计保护电路,当外界有静电的时候我们的电⼦元器件或系统能够⾃我保护避免被静电损坏(其实就是安装⼀个避雷针)。

这也是很多IC设计和制造业者的头号难题,很多公司有专门设计ESD的团队,今天我就和⼤家从最基本的理论讲起逐步讲解ESD保护的原理及注意点,你会发现前⾯讲的PN结/⼆极管、三极管、MOS管、全都⽤上了……以前的专题讲解PN结⼆极管理论的时候,就讲过⼆极管有⼀个特性:正向导通反向截⽌(不记得就去翻前⾯的课程),⽽且反偏电压继续增加会发⽣雪崩击穿(Avalanche Breakdown)⽽导通,我们称之为钳位⼆极管(Clamp)。

这正是我们设计静电保护所需要的理论基础,我们就是利⽤这个反向截⽌特性让这个旁路在正常⼯作时处于断开状态,⽽外界有静电的时候这个旁路⼆极管发⽣雪崩击穿⽽形成旁路通路保护了内部电路或者栅极(是不是类似家⾥⽔槽有个溢⽔⼝,防⽌⽔龙头忘关了导致整个卫⽣间⽔灾)。

芯片静电测试标准

芯片静电测试标准

芯片静电测试标准通常包括以下内容:

1. 静电放电感应(IEC 61000-4-2):该标准规定了测试应在不产生危险或无法修复的水平下进行。

在此标准下,小型设备皆可进行测试,测试时使用的脉冲电机最高电压为8kV。

2. 静电放电耐受性:可根据需求选择有关的标准进行测试,如ISO 10605、SAE J1812、MIL STD 883C 和1474B。

3. 静电放电发生的条件:是指放电源与模拟结果之间的误差,包括模拟条件(电压/电流源,阻值,引线长度和负载等)、芯片自身的电容等。

根据需求,可选择不同的标准进行测试。

芯片esd测试标准和方法(一)

芯片ESD测试标准和方法1. ESD测试标准- IEC 标准:这是国际电工委员会制定的ESD测试标准,用于评估设备的抗静电放电能力。

该标准规定了测试波形、测试级别和测试方法等内容,是ESD测试的国际通用标准。

- AEC-Q100标准:这是汽车电子领域常用的ESD测试标准,适用于评估汽车电子元器件的静电放电性能。

该标准对测试波形、测试级别和测试条件等进行了详细规定,以确保汽车电子设备在复杂的环境下具有良好的静电放电能力。

2. ESD测试方法- HBM测试方法:HBM(Human Body Model)是一种模拟人体静电放电的测试方法,通过模拟人体接地时的静电放电过程,评估芯片的抗静电放电能力。

该方法利用人体模型进行测试,可以快速评估芯片的静电放电性能,是一种常用的ESD测试方法。

- MM测试方法:MM(Machine Model)是一种模拟机器设备静电放电的测试方法,通过模拟机器间的静电放电过程,评估芯片的抗静电放电能力。

该方法利用机器模型进行测试,可以更真实地模拟实际工作环境中的静电放电情况,对芯片的静电放电性能进行全面评估。

- CDM测试方法:CDM(Charged Device Model)是一种模拟电荷器件静电放电的测试方法,通过模拟芯片和其它器件之间的静电放电过程,评估芯片的抗静电放电能力。

该方法利用充电器件模型进行测试,可以更精确地模拟芯片在实际应用中的静电放电情况,对芯片的静电放电性能进行准确评估。

3. ESD测试流程- 准备工作:进行ESD测试前,需要准备好测试设备、测试样品和测试环境等,确保测试的准确性和可靠性。

- 测试设置:根据不同的ESD测试方法和标准,设置合适的测试波形、测试级别和测试条件等,以确保测试的科学性和可比性。

- 进行测试:根据测试设置,进行HBM、MM或CDM等ESD测试,记录测试过程中芯片的静电放电情况和性能表现。

- 数据分析:对测试数据进行分析,评估芯片的抗静电放电能力,确定是否符合相关的ESD测试标准和要求。

芯片esd测试标准和方法

芯片ESD测试标准和方法如下:

1. 标准:根据静电的产生方式以及对电路的损伤模式不同,通常分为四种测试方式,包括人体放电模式(HBM)、机器放电模式(Machine Model)、元件充电模式(CDM)、电场感应模式(FIM)。

业界通常使用前两种模式来测试,即HBM和MM。

对于HBM,等效人体电容为100pF,等效人体电阻为 1.5KΩ。

规定小于2kV的则为Class-1,在2kV~4kV的为class-2,4kV~16kV的为class-3。

2. 方法:

* 接触放电:放电对象包括金属端子(如AUX端子、VIDEO端子、FM端子外导体、所有的螺钉、裸露在外的金属板等)、可导电的表面(如喷有金属漆的JOG、面板等)、水平金属板、垂直金属板。

放电等级为±4KV。

判断标准是B级,即在测试过程中允许出现功能性、显示紊乱,但在暂停测试后短时间内可自行(在无人为的干预的情况下)恢复正常的工作状态。

* 放电方法:放电导线与枪头同时放在被测端子(表面)上,进行连续放电,放电间隔时间应不少于1秒。

先用枪头对被测端子(表面)放电,然后将枪头移开,再用放电导线对被测端子(表面)的电荷导入大地。

重复10次。

如两种测试方法的结果不同,应以恶劣的结果为准。

以上信息仅供参考,如需了解更多信息,建议咨询专业人士。

AEC-Q101中文标准规范

基于离散半导体元件应力测试认证的失效机理内容列表AEC-Q101 基于离散半导体元件应力测试认证的失效机理附录1: 认证家族的定义附录2: Q101 设计、构架及认证的证明附录3: 认证计划附录4: 数据表示格式附录5: 最小参数测试要求附录6: 邦线测试的塑封开启附录7: AEC-Q101与健壮性验证关系指南附件AEC-Q101-001: 人体模式静电放电测试AEC-Q101-002: 人体模式静电放电测试 (废止)AEC-Q101-003: 邦线切应力测试AEC-Q101-004: 同步性测试方法AEC-Q101-005: 静电放电试验–带电器件模型AEC-Q101-006: 12V系统灵敏功率设备的短路可靠性描述感谢任何涉及到复杂的技术文件都来自于各个方面的经验和技能。

为此汽车电子委员会由衷承认并感谢以下对该版文件有重大贡献的人:固定会员:Rick Forster Continental CorporationMark A. Kelly Delphi CorporationDrew Hoffman Gentex CorporationSteve Sibrel HarmanGary Fisher Johnson ControlsEric Honosowetz Lear Corporation技术成员:James Molyneaux Analog DevicesJoe Fazio Fairchild SemiconductorNick Lycoudes FreescaleWerner Kanert InfineonScott Daniels International RectifierMike Buzinski MicrochipBob Knoell NXP SemiconductorsZhongning Liang NXP SemiconductorsMark Gabrielle ON SemiconductorTom Siegel Renesas TechnologyTony Walsh Renesas TechnologyBassel Atallah STMicroelectronicsArthur Chiang VishayTed Krueger [Q101 Team Leader]Vishay其他支持者:John Schlais Continental CorporationJohn Timms Continental CorporationDennis L. Cerney International RectifierRene Rongen NXP SemiconductorsThomas Hough Renesas TechnologyThomas Stich Renesas Technology本文件是专门的纪念:Ted Krueger (1955-2013)Mark Gabrielle (1957-2013)注意事项AEC文件中的材料都是经过AEC技术委员会准备、评估和批准的。

静电放电模式(HBM、MM、IEC)电路及静电等级 及比较

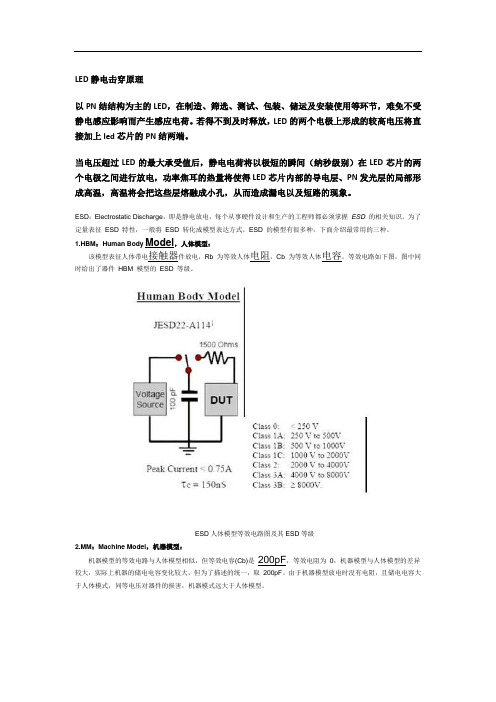

LED静电击穿原理以PN结结构为主的LED,在制造、筛选、测试、包装、储运及安装使用等环节,难免不受静电感应影响而产生感应电荷。

若得不到及时释放,LED的两个电极上形成的较高电压将直接加上led芯片的PN结两端。

当电压超过LED的最大承受值后,静电电荷将以极短的瞬间(纳秒级别)在LED芯片的两个电极之间进行放电,功率焦耳的热量将使得LED芯片内部的导电层、PN发光层的局部形成高温,高温将会把这些层熔融成小孔,从而造成漏电以及短路的现象。

ESD:Electrostatic Discharge,即是静电放电,每个从事硬件设计和生产的工程师都必须掌握ESD的相关知识。

为了定量表征ESD 特性,一般将ESD 转化成模型表达方式,ESD 的模型有很多种,下面介绍最常用的三种。

1.HBM:Human Body Model,人体模型:该模型表征人体带电接触器件放电,Rb 为等效人体电阻,Cb 为等效人体电容。

等效电路如下图。

图中同时给出了器件HBM 模型的ESD 等级。

ESD人体模型等效电路图及其ESD等级2.MM:Machine Model,机器模型:机器模型的等效电路与人体模型相似,但等效电容(Cb)是200pF,等效电阻为0,机器模型与人体模型的差异较大,实际上机器的储电电容变化较大,但为了描述的统一,取200pF。

由于机器模型放电时没有电阻,且储电电容大于人体模式,同等电压对器件的损害,机器模式远大于人体模型。

ESD机器模型等效电路图及其ESD等级3.CDM:Charged Device Model,充电器件模型:半导体器件主要采用三种封装型式(金属、陶瓷、塑料)。

它们在装配、传递、试验、测试、运输及存贮过程中,由于管壳与其它绝缘材料(如包装用的塑料袋、传递用的塑料容器等)相互磨擦,就会使管壳带电。

器件本身作为电容器的一个极板而存贮电荷。

CDM 模型就是基于已带电的器件通过管脚与地接触时,发生对地放电引起器件失效而建立的,器件带电模型如下:ESD充电器件模型等效电路图及其ESD等级器件的ESD 等级一般按以上三种模型测试,大部分ESD 敏感器件手册上都有器件的ESD数据,一般给出的是HBM 和MM。

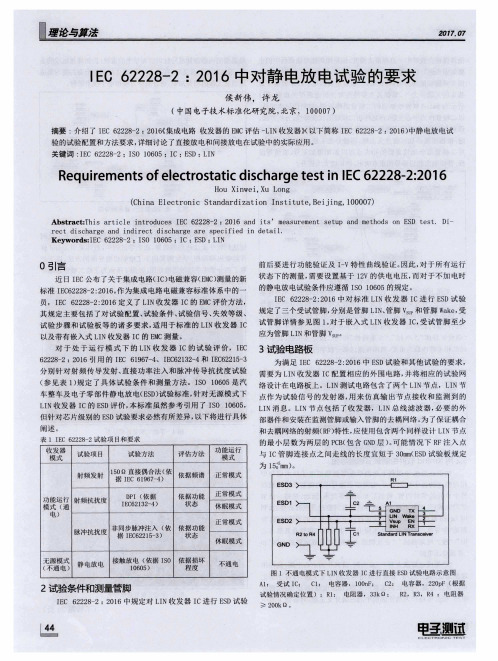

IEC 62228-2:2016中对静电放电试验的要求

以及带有嵌入式 L I N收发器 I c的 E M C测量 。 对于处于运行模式下的 L I N收 发 器 I c的试 验 评 价,I E C

6 2 2 2 8 — 2: 2 0 1 6引 用 的 I E C 6 1 9 6 7 - 4 、I E C 6 2 1 3 2 — 4和 I E C 6 2 2 1 5 - 3

Abs t r a c t : T hi S a r t i C l e i n t r o d u c e s I E C 6 2 2 2 8 — 2 :2 01 6 a n d i t s ’m e a s u r e m e n t

r ect di s c ha rg e an d i n di re ct di s ch ar ge a re s pe ci fl ed i n d et ai 1 .

H o u Xi n wei , X u L o n g

( C h i n a E l e c t r o n i C S t a n d a r d i z a t i o n I n s t i t u t e , B e i J i n g , 1 0 0 0 0 7 )

员,I E C 6 2 2 2 8 — 2 : 2 0 1 6定义了 L I N收发器 I c的 E M C评价方法 ,

I E C 6 2 2 2 8 — 2 : 2 0 1 6中对 标 准 L I N收 发器 I c进 行 E S D试 验

分别是管脚 L I N 、 管脚 V 和 管脚 W a k e , 受 其 规 定 主 要 包 括 了对 试 验 配 置 、 试验条件 、 试验 信号、 失效等级 、 规 定 了三 个 受 试 管 脚 , 试管脚 详情参 见 图 l 。 对 于嵌入 式 L I N收发器 I c , 受试管脚 至少 试 验步骤 和试验 板等 的诸 多要求 , 适用 于标准 的 L I N收 发 器 I C

AECQ相关

标签:AECQAECQ信息汇总最近在整理元器件方面的资料,涉及ROSH与AECQ的信息,下面整理了AE CQ的信息。

克莱斯勒、福特和通用汽车为建立一套通用的零件资质及质量系统标准而设立了汽车电子委员会(AEC),AEC 是“Automotive Electronics Council:汽车电子协会”之略,是主要汽车制造商与美国的主要部件制造商汇聚一起成立的、以车载电子部件的可靠性以及认定标准的规格化为目的的团体,AEC建立了质量控制的标准。

同时,由于符合AEC规范的零部件均可被上述三家车厂同时采用,促进了零部件制造商交换其产品特性数据的意愿,并推动了汽车零件通用性的实施,为汽车零部件市场的快速成长打下基础。

主要的汽车电子成员有:Autoliv, Co ntinental, Delphi, Johnson Controls 和Visteon。

AEC-Q100:主要用于预防产品可能发生各种状况或潜在的故障状态,引导零部件供货商在开发的过程中就能采用符合该规范的芯片。

AEC-Q100对每一个芯片个案进行严格的质量与可靠度确认,确认制造商所提出的产品数据表、使用目的、功能说明等是否符合最初需求的功能,以及在连续使用后个功能与性能是否能始终如一。

A EC-Q100标准的目标是提高产品的良品率,这对芯片供货商来说,不论是在产品的尺寸、合格率及成本控制上都面临很大的挑战。

AEC-Q100又分为不同的产品等级,其中第1级标准的工作温度范围在-40℃-1 25℃之间,最严格的第0级标准工作温度范围可达到-40℃-150℃。

0 等级:环境工作温度范围-40℃-150℃1 等级:环境工作温度范围-40℃-125℃2 等级:环境工作温度范围-40℃-105℃3 等级:环境工作温度范围-40℃-85℃4 等级:环境工作温度范围0℃-70℃AEC - Q100 Rev - G base: 集成电路的应力测试标准(不包含测试方法)AEC-Q100-001 邦线切应力测试AEC-Q100-002 人体模式静电放电测试AEC-Q100-003 机械模式静电放电测试AEC-Q100-004 集成电路闩锁效应测试AEC-Q100-005 可写可擦除的永久性记忆的耐久性、数据保持及工作寿命的测试AEC-Q100-006 热电效应引起的寄生闸极漏电流测试AEC-Q100-007 故障仿真和测试等级AEC-Q100-008 早期寿命失效率(ELFR)AEC-Q100-009 电分配的评估AEC-Q100-010 锡球剪切测试AEC-Q100-011 带电器件模式的静电放电测试AEC-Q100-012 12V 系统灵敏功率设备的短路可靠性描述AEC - Q101 Rev - C: 分立半导体元件的应力测试标准(包含测试方法)* AEC - Q101-001 - Rev-A: 人体模式静电放电测试* AEC - Q101-002 - Rev-A: 机械模式静电放电测试* AEC - Q101-003 - Rev-A: 邦线切应力测试* AEC - Q101-004 - Rev-: 同步性测试方法* AEC - Q101-005 - Rev-A: 带电器件模式的静电放电测试* AEC - Q101-006 - Rev-: 12V 系统灵敏功率设备的短路可靠性描述AEC - Q200 Rev - C: 半导体被动元件的应力测试标准(包含测试方法)* AEC - Q200-001 - Rev-A: 阻燃性能测试* AEC - Q200-002 - Rev-A: 人体模式静电放电测试* AEC - Q200-003 - Rev-A: 断裂强度测试* AEC - Q200-004 - Rev-: 自恢复保险丝测量程序* AEC - Q200-005 - Rev-: PCB板弯曲/端子邦线应力测试* AEC - Q200-006 - Rev-: 端子应力(贴片元件)/切应力测试* AEC - Q200-007 - Rev-: 电压浪涌测试AEC-Q001 零件平均测试指导原则提出了所谓的参数零件平均测试(PPAT)方法。

车规级电源管理芯片-2023标准

车规级电源管理芯片1范围本文件规定了车规级电源管理芯片的基本要求、技术要求、芯片测试、检验规则、标志、包装、运输及贮存等内容。

本文件适用于车规级电源管理芯片的生产制造。

2规范性引用文件下列文件中的内容通过文中的规范性引用而构成本文件必不可少的条款。

其中,注日期的引用文件,仅该日期对应的版本适用于本文件;不注日期的引用文件,其最新版本(包括所有的修改单)适用于本文件。

AEC-Q001部件平均测试指南AEC-Q002良率统计分析指南AEC-Q003集成电路特征化指南AEC-Q004零缺陷指南GB/T191包装储运图示标志GB/T2423.1电工电子产品环境试验第2部分:试验方法试验A:低温GB/T2423.2电工电子产品环境试验第2部分:试验方法试验B:高温GB/T2828.1计数抽样检验程序第1部分:按接收质量限(AQL)检案的逐批检验抽样计划GB/T7092半导体集成电路外形尺寸GB/T17626.2电磁兼容试验和测量技术静电放电抗扰度试验GB/T34590道路车辆功能安全GB/T42706.5电子元器件半导体器件长期贮存第5部分:芯片和晶圆3术语和定义下列术语和定义适用于本文件。

3.1芯片半导体元件产品的统称,是由独立半导体设备和被动组件,集成到衬底或线路板所构成的小型化电路。

3.2车规级电源管理芯片技术标准达到车规级,可应用于汽车电源控制管理的芯片。

3.3引脚从芯片内部电路引出与外围电路的接线,所有的引脚就构成了这块芯片的接口,可划分为脚跟、脚趾、脚侧等部分。

4基本要求4.1芯片属性4.1.1车规级芯片应具有高可靠性、高安全性、零缺陷率、批次一致性高的基本属性。

4.1.2高可靠性是指处理器芯片工作环境恶略,EMC要求苛刻等。

4.1.3高安全性是指处理器芯片电路设计要符合功能安全的要求,避免因系统失效带来的危险。

4.1.4零缺陷率是指汽车属于高危险性产品,其控制器在设计和生产环节要做到零缺陷。

芯片的故障分析与故障排除

芯片的故障分析与故障排除芯片故障是电子设备中常见的问题之一,它可能导致设备的不正常运行或完全失效。

本文将介绍芯片故障的分析方法和常见的故障排除技术。

一、芯片故障分析方法芯片故障分析是找出芯片故障原因的过程,可以采用以下几种方法来进行分析:1. 外部观察:通过肉眼观察芯片是否有物理损坏,如烧毁、破裂等。

2. 功能测试:通过对芯片进行功能测试,判断芯片是否能够正常工作。

3. 电气检测:使用测试仪器对芯片进行电气参数的测试,如电压、电流等,以确定芯片是否工作正常。

4. 静电放电检测:静电放电是芯片故障的一个常见原因,通过使用静电放电检测仪器,可以检测芯片是否存在静电放电问题。

二、芯片故障排除技术芯片故障排除是指在分析了芯片故障原因后,采取相应的措施修复故障。

下面介绍几种常见的芯片故障排除技术:1. 复位:对于一些临时性故障,通过软件或硬件复位芯片,可以使其重新启动,恢复正常工作。

2. 运行环境检查:芯片工作的环境对其性能有着重要影响,需要检查工作环境是否符合芯片的要求,如温度、湿度等。

3. 清洁处理:芯片表面或芯片引脚上的灰尘、污渍等可能导致接触不良,清洁处理可以解决这类问题。

4. 更换元器件:如果分析发现芯片内部的某个元器件损坏,需要将其更换为新的元器件,以修复故障。

5. 固件更新:芯片的固件可能存在版本问题,通过更新固件可以解决一些软件方面的故障。

三、芯片故障的预防除了分析和排除芯片故障外,预防芯片故障也是非常重要的。

以下是一些预防措施:1. 质量控制:在生产过程中,严格控制每个环节的质量,确保芯片的可靠性。

2. 适当的温度控制:芯片工作的温度范围是有限制的,需要保持在合适的温度范围内,避免过高或过低的温度对芯片产生影响。

3. 防静电措施:在芯片的运输、存储和使用过程中,需要采取适当的防静电措施,避免静电损坏芯片。

4. 适当的电源供应:芯片需要稳定的电源供应,确保供电电压和电流的稳定性,避免电源问题导致的故障。

考虑寄生参数影响的芯片RC-HBM静电测试模型

第50卷第4期电力系统保护与控制Vol.50 No.4 2022年2月16日 Power System Protection and Control Feb. 16, 2022 DOI: 10.19783/ki.pspc.210450考虑寄生参数影响的芯片RC-HBM静电测试模型熊素琴1,李求洋1,肖志强2(1.中国电力科学研究院有限公司,北京 100192;2.湖南大学电气与信息工程学院,湖南 长沙 410082)摘要:采用常规的人体模型(Human Body Model, HBM)进行静电释放(Electro-Static Discharge, ESD)测试时往往容易受到寄生参数的影响,使得电源芯片抗静电能力测量值与实际抗静电能力存在偏差,导致劣质产品通过HBM ESD 测试,影响电源芯片产品良品率的提升。

为此,提出了一种RC-HBM模型,通过引入RC并联支路,校正因寄生参数引起的静电放电电流的偏差,满足电源芯片静电可靠性测试的要求。

首先阐述了静电对电源芯片的损坏机理。

其次,分析了寄生参数对ESD电流的影响,阐述了常规HBM ESD测试的局限性。

并提出了一种新型的RC-HBM 模型,给出了RC并联支路参数的设计依据。

最后,通过批量实验验证了所提RC-HBM模型的准确性和合理性。

关键词:电源芯片;HBM模型;ESD;寄生参数;静电放电电流RC-HBM electrostatic test model of chip considering the influence of parasitic parametersXIONG Suqin1, LI Qiuyang1, XIAO Zhiqiang2(1. China Electric Power Research Institute Co., Ltd., Beijing 100192, China; 2. School of Electrical andInformation Engineering, Hunan University, Changsha 410082, China)Abstract: When the conventional human body model (HBM) is used for electro-static discharge (ESD) testing, the measured value of the power chip's antistatic ability deviates from the actual antistatic ability because of a parasitic effect, resulting in inferior products passing the HBM ESD test. This affects the improvement of the yield rate of power chip products. To this end, an improved HBM model is proposed, one which corrects the deviation of the electrostatic discharge current caused by parasitic parameters by introducing an RC parallel branch to meet the requirements of the electrostatic reliability test of the power chip. First, the mechanism of how static electricity causes damage to the power chip is described.Secondly, the influence of parasitic parameters on the ESD current is analyzed, and the limitations of the conventional HBM ESD test are elaborated. Then a new RC-HBM model is proposed, and the design basis of the RC parallel branch parameters is presented. Finally, batch experiments verify the accuracy and rationality of the HBM model proposed.This work is supported by the Science and Technology Project of State Grid Corporation of China (No.5100-201946434A-0-0-00).Key words: power chip; HBM model; ESD; parasitic parameters;electrostatic discharge current0 引言电源芯片是发电厂、变电站中众多电子设备中不可或缺的能量转换部分,尤其是控制、保护和自动化等装置,对电源芯片供电质量要求更高[1-5]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

芯片静电测试标准

引言

随着电子技术的快速发展,芯片已成为现代社会的关键组成部分。

然而,芯片在生产和使用过程中容易受到静电的损害。

为了确保芯片的质量和可靠性,制定芯片静电测试标准至关重要。

本文将对芯片静电测试标准进行全面、详细、完整和深入的探讨。

测试目的

芯片静电测试的主要目的是评估芯片在静电环境下的性能和可靠性。

通过测试,可以检测芯片是否容易受到静电损害,以及是否满足相关的测试标准。

测试结果将用于指导芯片的设计、生产和使用,以降低芯片的静电敏感性,提高芯片的品质。

测试方法

芯片静电测试一般包括以下几个方面的测试方法:

1. 静电放电测试

静电放电测试是评估芯片在静电放电事件下的性能的基本方法。

测试时,通过模拟静电放电事件,将芯片暴露在不同的放电电压和放电能量下,观察芯片的反应。

常用的测试方法包括人体模型(HBM)测试和机器模型(MM)测试。

1.1 人体模型(HBM)测试

人体模型(HBM)测试是模拟人体静电放电对芯片的影响。

测试时,将芯片连接到接地板上,然后将预定的放电电压施加在芯片的引脚上,观察芯片的输出和/或损坏情况。

1.2 机器模型(MM)测试

机器模型(MM)测试是模拟机器静电放电对芯片的影响。

测试时,将芯片连接到模拟电路上,通过一个预定的电容来模拟机器的静电放电,观察芯片的输出和/或损坏情况。

2. 静电放电保护测试

静电放电保护测试是评估芯片的静电放电保护性能的方法。

通过测试,可以确定芯片是否具有有效的静电放电保护电路,以防止静电放电损伤芯片。

2.1 静电放电保护电路设计

静电放电保护电路的设计是芯片静电测试中的关键环节。

设计时需要考虑芯片的特性和预期的静电放电情况,选择合适的保护元件和保护拓扑,以提高芯片的静电放电保护性能。

2.2 静电放电保护测试方法

静电放电保护测试主要包括放电幅值测试和放电速率测试。

通过这些测试方法,可以验证芯片的静电放电保护电路的性能,以及是否满足相关的测试标准。

3. 静电敏感性测试

静电敏感性测试是评估芯片在静电环境下的敏感性的方法。

通过测试,可以确定芯片对静电放电的敏感程度,以及是否满足相关的测试标准。

3.1 静电敏感性测试方法

常用的静电敏感性测试方法包括测量芯片的静电敏感等级和测量芯片的最大静电放电敏感性。

通过这些测试方法,可以确定芯片的静电敏感性,以及采取相应的措施降低芯片的静电敏感性。

测试标准

芯片静电测试标准通常由国际标准化组织(ISO)和行业标准组织制定。

常用的芯片静电测试标准包括:

1. ISO 10605

ISO 10605标准是用于评估电子设备对车辆静电放电(ESD)事件的抵抗能力的标准。

该标准规定了静电放电的测试方法和测试条件,以及测试结果的评估方法。

2. JEDEC JESD22-A114

JEDEC JESD22-A114标准是用于测试集成电路(IC)产品对人体模型(HBM)静电放电的敏感性的标准。

该标准定义了测试方法和测试条件,并规定了测试结果的评估方法。

3. IEC 61000-4-2

IEC 61000-4-2标准是用于评估电子设备对人体模型(HBM)和机器模型(MM)静电放电的抵抗能力的标准。

该标准规定了静电放电的测试方法和测试条件,以及测试结果的评估方法。

结论

芯片静电测试标准是确保芯片质量和可靠性的重要手段。

通过采用合适的测试方法和标准,可以评估芯片在静电环境下的性能和可靠性,以指导芯片的设计、生产和使用。

相关的国际和行业标准为芯片静电测试提供了科学的依据,促进了芯片行业的发展和进步。