TC1016中文资料

AOZ1016AI中文资料

Pin Function

Power ground. Electrically needs to be connected to AGND. Supply voltage input. When VIN rises above the UVLO threshold the device starts up. Reference connection for controller section. Also used as thermal connection for controller section. Electrically needs to be connected to PGND. The FB pin is used to determine the output voltage via a resistor divider between the output and GND. External loop compensation pin. The enable pin is active HIGH. Connect EN pin to VIN if not used. Do not leave the EN pin floating. PWM output connection to inductor. Thermal connection for output stage.

Applications

● ● ● ● ● ● ●

Point of load DC/DC conversion PCIe graphics cards Set top boxes DVD drives and HDD LCD panels Cable modems Telecom/networking/datacom equipment

CPC1016N中文资料

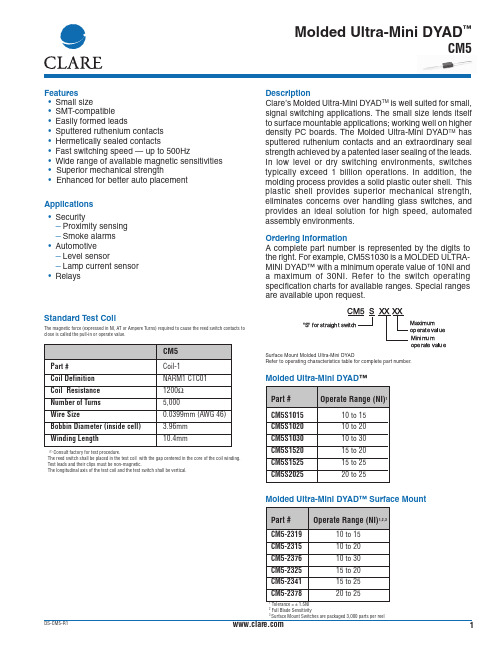

Applications Features DescriptionOrdering InformationClare’s Molded Ultra-Mini DYAD TM is well suited for small,signal switching applications. The small size lends itself to surface mountable applications; working well on higher density PC boards. The Molded Ultra-Mini DYAD TM has sputtered ruthenium contacts and an extraordinary seal strength achieved by a patented laser sealing of the leads.In low level or dry switching environments, switches typically exceed 1 billion operations. In addition, the molding process provides a solid plastic outer shell. This plastic shell provides superior mechanical strength,eliminates concerns over handling glass switches, and provides an ideal solution for high speed, automated assembly environments.Standard Test CoilA complete part number is represented by the digits to the right. For example, CM5S1030 is a MOLDED ULTRA-MINI DYAD™ with a minimum operate value of 10NI and a maximum of 30NI. Refer to the switch operating specification charts for available ranges. Special ranges are available upon request.Surface Mount Molded Ultra-Mini DYADRefer to operating characteristics table for complete part number.Molded Ultra-Mini DYAD ™Molded Ultra-Mini DYAD™ Surface Mount2Full Blade Sensitivity 3Surface Mount Switches are packaged 3,000 parts per reel1Molded Ultra-Mini DYAD ™CM5DS-CM5-R1•Small size•SMT-compatible •Easily formed leads•Sputtered ruthenium contacts •Hermetically sealed contacts•Fast switching speed — up to 500Hz•Wide range of available magnetic sensitivities • Superior mechanical strength• Enhanced for better auto placement •Security−Proximity sensing −Smoke alarms •Automotive −Level sensor−Lamp current sensor •RelaysThe magnetic force (expressed in NI, AT or Ampere Turns) required to cause the reed switch contacts to close is called the pull-in or operate value.(1) Consult factory for test procedure.The reed switch shall be placed in the test coil with the gap centered in the core of the coil winding.Test leads and their clips must be non-magnetic.The longitudinal axis of the test coil and the test switch shall be vertical.CM5S XX XXMaximum operate value Minimumoperate value"S"for straight switchCM5Rev. 1Absolute Maximum Ratings are stress ratings. Stressesin excess of these ratings can cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this data sheet is not implied.Exposure of the device to the absolute maximum ratings for extended period may degrade the device and effect its reliability.Molded Ultra-Mini DYAD ™2SpecificationsAll parameters are at 25°C unless otherwise stated.(1) Contact resistance measured with 4 terminal method, 1.1" between test leads (2)>1012 Ω is available upon request (3)A 24V zener in series with a diode across the coil (4)Use caution not to exceed vibration resistance limits while ultrasonically cleaning. Contact Clare, Inc.Engineering for more details/ recommendations (5)15 ampere turn minimumCM5Rev. 1Mechanical DimensionsDimensionsmm inchesMolded Ultra-Mini DYAD ™3CLARE LOCATIONSClare Headquarters78 Cherry Hill DriveBeverly, MA 01915Tel: 1-978-524-6700Fax: 1-978-524-4900Toll Free: 1-800-27-CLARE Clare Switch Division4315 Earth City Expresssway St. Louis, MO 63045Tel: 1-314-770-1832Fax: 1-314-770-1812Clare Micronix Division145 ColumbiaAliso Viejo, CA 92656-1490 Tel: 1-949-831-4622Fax: 1-949-831-4628SALES OFFICES AMERICASAmericas HeadquartersClare78 Cherry Hill DriveBeverly, MA 01915Tel: 1-978-524-6700Fax: 1-978-524-4900Toll Free: 1-800-27-CLARE Eastern RegionClareP.O. Box 856Mahwah, NJ 07430Tel: 1-201-236-0101Fax: 1-201-236-8685Toll Free: 1-800-27-CLARE Central RegionClare Canada Ltd.3425 Harvester Road, Suite 202 Burlington, Ontario L7N 3N1 Tel: 1-905-333-9066Fax: 1-905-333-1824Western RegionClare1852 West 11th Street, #348 Tracy, CA 95376Tel: 1-209-832-4367Fax: 1-209-832-4732Toll Free: 1-800-27-CLARE CanadaClare Canada Ltd.3425 Harvester Road, Suite 202 Burlington, Ontario L7N 3N1 Tel: 1-905-333-9066Fax: 1-905-333-1824EUROPEEuropean HeadquartersCP Clare nvBampslaan 17B-3500 Hasselt (Belgium)Tel: 32-11-300868Fax: 32-11-300890FranceClare France SalesLead Rep99 route de Versailles91160 ChamplanFranceTel: 33 1 69 79 93 50Fax: 33 1 69 79 93 59GermanyClare Germany SalesActiveComp Electronic GmbHMitterstrasse 1285077 ManchingGermanyTel: 49 8459 3214 10Fax: 49 8459 3214 29ItalyC.L.A.R.E.s.a.s.Via C. Colombo 10/AI-20066 Melzo (Milano)Tel: 39-02-95737160Fax: 39-02-95738829SwedenClare SalesComptronic ABBox 167S-16329 SpångaTel: 46-862-10370Fax: 46-862-10371United KingdomClare UK SalesMarco Polo HouseCook WayBindon RoadTauntonUK-Somerset TA2 6BGTel: 44-1-823 352541Fax: 44-1-823 352797ASIA PACIFICAsian HeadquartersClareRoom N1016, Chia-Hsin, Bldg II,10F, No. 96, Sec. 2Chung Shan North RoadTaipei, Taiwan R.O.C.Tel: 886-2-2523-6368Fax: 886-2-2523-6369Worldwide Sales OfficesSpecification: PB-CM5-R1©Copyright 2001, Clare, Inc.Molded Ultra-Mini DYAD™, Molded Mini DYAD™, andMolded DYAD® are trademarks of Clare, Inc.All rights reserved. Printed in USA.5/01/01Clare cannot assume responsibility for use of any circuitry otherthan circuitry entirely embodied in this Clare product. No circuitpatent licenses nor indemnity are expressed or implied. Clare re-serves the right to change the specification and circuitry, withoutnotice at any time. The products described in this document are notintended for use in medical implantation or other direct life supportapplications where malfunction may result in direct physical harm,injury or death to a person.。

GL610T中文资料

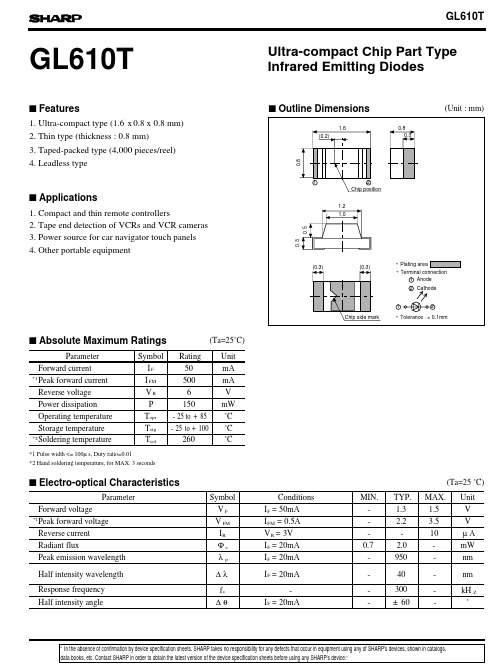

s Electro-optical Characteristics

Parameter Forward voltage *1 Peak forward voltage Reverse current Radiant flux Peak emission wavelength Half intensity wavelength Response frequency Half intensity angle Symbol VF V FM IR Φe λp ∆λ fc ∆θ Conditions I F = 50mA I FM = 0.5A V R = 3V I F = 20mA I F = 20mA I F = 20mA I F = 20mA MIN. 0.7 TYP. 1.3 2.2 2.0 950 40 300 ± 60 MAX. 1.5 3.5 10 -

GL610T

GL610T

s Features

1. Ultra-compact type (1.6 x 0.8 x 0.8 mm) 2. Thin type (thickness : 0.8 mm) 3. Taped-packed type (4,000 pieces/reel) 4. Leadless type

Ultra-compact Chip Part Type Infrared Emitting Diodes

s Outline Dimensions

1.6 (0.2) 0.8 0.3

(Unit : mm)

0.8

1

2 Chip position 1.2

s Applications

1. Compact and thin remote controllers 2. Tape end detection of VCRs and VCR cameras 3. Power source for car navigator touch panels 4. Other portable equipment

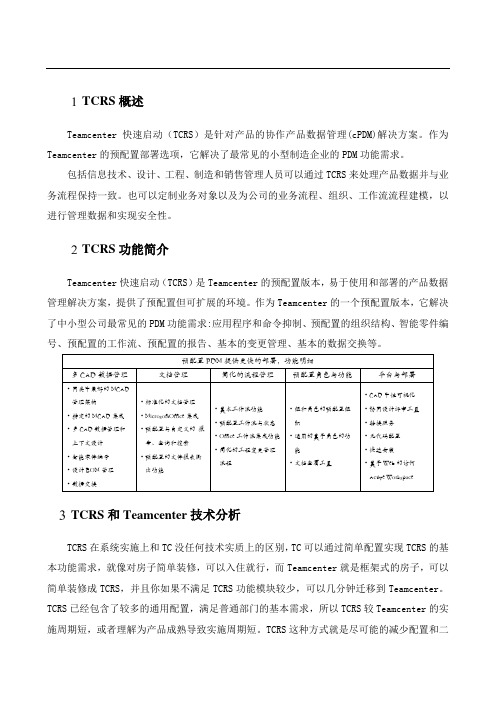

[工作规范]工作流联盟WfMC规范

![[工作规范]工作流联盟WfMC规范](https://img.taocdn.com/s3/m/5eb7745702d276a201292e5f.png)

(工作规范)工作流联盟WfMC规范工作流管理联盟规范工作流管理联盟工作流标准工作流过程定义接口――XML过程定义语言文档号:WFMC-TC-1025文档状态:草案1.0(β)2002.07.31Version1.0(β)版权©2002工作流管理联盟Allrightsreserved.Nopartofthispublicationmaybereproduced,storedinaretrievalsystem,o rtransmittedinanyformorbyanymeans,electronic,mechanical,photocopying,recordingor otherwise,withoutthepriorwrittenpermissionoftheWorkflowManagementCoalitionexce ptthatreproduction,storageortransmissionwithoutpermissionispermittedifallcopiesofth epublication(orportionsthereof)producedtherebycontainanoticethattheWorkflowMana gementCoalitionanditsmembersaretheownersofthecopyrighttherein.WorkflowManagementCoalition2436N.FederalHighway#374LighthousePoint,Fl33064USATel:+19547823376Fax:+19547826365Email:wfmc@WWW:http://)、Contributors:SethOsher(IntuitiveProductsInternationalCorp.)及RobertShapiro(CapeVisions).●从模式中去除InlineBlock和BlockName元素。

PANTONE服装纺织色卡-棉布版(TCX)系列新旧色号对照表

Pristine

11-0606 TCX

11-0609 TC

Ethereal Green

11-0609 TCX

11-0616 TC

Pastel Yellow

11-0616 TCX

11-0617 TC

Transparent Yellow

11-0617 TCX

11-0618 TC

Wax Yellow

Star White

11-4202 TCX

11-4300 TC

Marshmallow

11-4300 TCX

11-4301 TC

Lily White

11-4301 TCX

11-4303 TC

Mystic Blue

11-4303 TCX

11-4601 TC

Bit of Blue

11-4601 TCX

11-4604 TC

Silver Peony

12-1206 TCX

12-1207 TC

Pearl Blush

12-1207 TCX

12-1209 TC

Soft Pink

12-1209 TCX

12-1212 TC

Veiled Rose

12-1212 TCX

12-1304 TC

Pearl

12-1304 TCX

12-1305 TC

12-0813 TC

Autumn Blonde

12-0813 TCX

12-0815 TC

Vanilla Custard

12-0815 TCX

12-0817 TC

Apricot Gelato

12-0817 TCX

TC7106_06资料

TC7106/A/TC7107/AFeatures:•Internal Reference with Low Temperature Drift: -TC7106/7: 80ppm/°C Typical-TC7106A/7A: 20ppm/°C Typical•Drives LCD (TC7106) or LED (TC7107)Display Directly•Zero Reading with Zero Input•Low Noise for Stable Display•Auto-Zero Cycle Eliminates Need for Zero Adjustment•True Polarity Indication for Precision Null Applications•Convenient 9V Battery Operation (TC7106A)•High-Impedance CMOS Differential Inputs: 1012Ω•Differential Reference Inputs Simplify Ratiometric Measurements•Low-Power Operation: 10mW Applications:•Thermometry•Bridge Readouts: Strain Gauges, Load Cells, Null Detectors•Digital Meters: Voltage/Current/Ohms/Power, pH •Digital Scales, Process Monitors•Portable InstrumentationDevice Selection Table General Description:The TC7106A and TC7107A 3-1/2 digit direct displaydrive Analog-to-Digital Converters allow existing 7106/7107 based systems to be upgraded. Each device has a precision reference with a 20ppm/°C max tempera-ture coefficient. This represents a 4 to 7 times improve-ment over similar 3-1/2 digit converters. Existing 7106 and 7107 based systems may be upgraded withoutchanging external passive component values. TheTC7107A drives common anode light emitting diode (LED) displays directly with 8mA per segment. A lowcost, high resolution indicating meter requires only adisplay, four resistors, and four capacitors.The TC7106A low-power drain and 9V battery operationmake it suitable for portable applications.The TC7106A/TC7107A reduces linearity error to lessthan 1 count. Rollover error – the difference in readings for equal magnitude, but opposite polarity input signals,is below ±1 count. High-impedance differential inputsoffer 1pA leakage current and a 1012Ω input imped-ance. The differential reference input allows ratiometricmeasurements for ohms or bridge transducermeasurements. The 15μV P–P noise performance ensures a “rock solid” reading. The auto-zero cycle ensures a zero display reading with a zero volts input.Package Code Package Pin LayoutTemperatureRangeCPI40-Pin PDIP Normal0°C to +70°CIPL40-Pin PDIP Normal-25°C to +85°CIJL40-Pin CERDIP Normal-25°C to +85°CCKW44-Pin PQFP FormedLeads0°C to +70°CCLW44-Pin PLCC —0°C to +70°C3-1/2 Digit Analog-to-Digital Converters© 2006 Microchip Technology Inc.DS21455C-page 1TC7106/A/TC7107/APackage TypeDS21455C-page 2© 2006 Microchip Technology Inc.TC7106/A/TC7107/A Typical Application© 2006 Microchip Technology Inc.DS21455C-page 3TC7106/A/TC7107/ADS21455C-page 4© 2006 Microchip Technology Inc.1.0ELECTRICALCHARACTERISTICSAbsolute Maximum Ratings*TC7106ASupply Voltage (V+ to V-).......................................15V Analog Input Voltage (either Input) (Note 1)...V+ to V-Reference Input Voltage (either Input)............V+ to V-Clock Input...................................................Test to V+Package Power Dissipation (T A ≤ 70°C) (Note 2):40-Pin CERDIP.......................................2.29W 40-Pin PDIP ............................................1.23W 44-Pin PLCC...........................................1.23W 44-Pin PQFP...........................................1.00W Operating Temperature Range:C (Commercial) Devices..............0°C to +70°C I (Industrial) Devices ................-25°C to +85°C Storage Temperature Range..............-65°C to +150°CTC7107ASupply Voltage (V+)...............................................+6V Supply Voltage (V-)..................................................-9V Analog Input Voltage (either Input) (Note 1)...V+ to V-Reference Input Voltage (either Input)............V+ to V-Clock Input..................................................GND to V+Package Power Dissipation (T A ≤ 70°C) (Note 2):40-Pin CERDip........................................2.29W 40-Pin PDIP ............................................1.23W 44-Pin PLCC...........................................1.23W 44-Pin PQFP...........................................1.00W Operating Temperature Range:C (Commercial) Devices..............0°C to +70°C I (Industrial) Devices ................-25°C to +85°C Storage Temperature Range..............-65°C to +150°C*Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operation sections of the specifications is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.TC7106/A/TC7107/ATABLE 1-1:TC7106/A AND TC7107/A ELECTRICAL SPECIFICATIONSElectrical Characteristics: Unless otherwise noted, specifications apply to both the TC7106/A and TC7107/A at T A = 25°C,f CLOCK = 48kHz. Parts are tested in the circuit of the Typical Operating Circuit.Symbol Parameter Min Typ Max Unit Test ConditionsZ IR Zero Input Reading-000.0±000.0+000.0DigitalReading V IN = 0.0VFull Scale = 200.0mVRatiometric Reading999999/10001000DigitalReading V IN = V REFV REF = 100mVR/O Rollover Error (Difference in Reading forEqual Positive and NegativeReading Near Full Scale)-1±0.2+1Counts V IN- = + V IN+ ≅ 200mVLinearity (Max. Deviation from Best Straight Line Fit)-1±0.2+1Counts Full Scale = 200mV orFull Scale = 2.000VCMRR Common Mode Rejection Ratio (Note 3)—50—μV/V V CM = ±1V, V IN = 0V,Full Scale = 200.0mVe N Noise (Peak to Peak Value not Exceeded95% of Time)—15—μV V IN = 0VFull Scale - 200.0mVI L Leakage Current at Input—110pA V IN = 0VZero Reading Drift—0.21μV/°C V IN = 0V“C” Device = 0°C to +70°C— 1.02μV/°C V IN = 0V“I” Device = -25°C to +85°C TC SF Scale Factor Temperature Coefficient—15ppm/°C V IN = 199.0mV,“C” Device = 0°C to +70°C(Ext. Ref = 0ppm°C)——20ppm/°C V IN = 199.0mV“I” Device = -25°C to +85°C I DD Supply Current (Does not include LEDCurrent For TC7107/A)—0.8 1.8mA V IN = 0.8V C Analog Common Voltage(with Respect to Positive Supply)2.7 3.05 3.35V25kΩ Between Common andPositive SupplyV CTC Temperature Coefficient of AnalogCommon (with Respect to Positive Supply)————25kΩ Between Common andPositive Supply7106/7/A7106/7208050—ppm/°Cppm/°C0°C ≤ T A≤ +70°C(“C” Commercial TemperatureRange Devices)V CTC Temperature Coefficient of AnalogCommon (with Respect to Positive Supply)——75ppm/°C0°C ≤ T A≤ +70°C(“I” Industrial TemperatureRange Devices)V SD TC7106A ONLY Peak to Peak Segment Drive Voltage 456V V+ to V- = 9V(Note 4)V BD TC7106A ONLY Peak to Peak Backplane Drive Voltage 456V V+ to V- = 9V(Note 4)TC7107A ONLYSegment Sinking Current (Except Pin 19)58.0—mA V+ = 5.0VSegment Voltage = 3VTC7107A ONLYSegment Sinking Current (Pin 19)1016—mA V+ = 5.0VSegment Voltage = 3VNote1:Input voltages may exceed the supply voltages, provided the input current is limited to ±100μA.2:Dissipation rating assumes device is mounted with all leads soldered to printed circuit board.3:Refer to “Differential Input” discussion.4:Backplane drive is in phase with segment drive for “OFF” segment, 180° out of phase for “ON” segment.Frequency is 20 times conversion rate. Average DC component is less than 50mV.© 2006 Microchip Technology Inc.DS21455C-page 5TC7106/A/TC7107/ADS21455C-page 6© 2006 Microchip Technology Inc.2.0PIN DESCRIPTIONSThe descriptions of the pins are listed in Table 2-1.TABLE 2-1:PIN FUNCTION TABLEPin Number (40-Pin PDIP)NormalPin No.(40-Pin PDIP)(ReversedSymbol Description1(40)V+Positive supply voltage.2(39)D 1Activates the D section of the units display.3(38)C 1Activates the C section of the units display.4(37)B 1Activates the B section of the units display.5(36)A 1Activates the A section of the units display.6(35)F 1Activates the F section of the units display.7(34)G 1Activates the G section of the units display.8(33)E 1Activates the E section of the units display.9(32)D 2Activates the D section of the tens display.10(31)C 2Activates the C section of the tens display.11(30)B 2Activates the B section of the tens display.12(29)A 2Activates the A section of the tens display.13(28)F 2Activates the F section of the tens display.14(27)E 2Activates the E section of the tens display.15(26)D 3Activates the D section of the hundreds display.16(25)B 3Activates the B section of the hundreds display.17(24)F 3Activates the F section of the hundreds display.18(23)E 3Activates the E section of the hundreds display.19(22)AB 4Activates both halves of the 1 in the thousands display.20(21)POL Activates the negative polarity display.21(20)BP/GND LCD Backplane drive output (TC7106A). Digital Ground (TC7107A).22(19)G 3Activates the G section of the hundreds display.23(18)A 3Activates the A section of the hundreds display.24(17)C 3Activates the C section of the hundreds display.25(16)G 2Activates the G section of the tens display.26(15)V-Negative power supply voltage.27(14)V INT Integrator output. Connection point for integration capacitor. See INTEGRATING CAPACITOR section for more details.28(13)V BUFF Integration resistor connection. Use a 47k Ω resistor for a 200mV full scale range and a 47k Ω resistor for 2V full scale range.29(12)C AZThe size of the auto-zero capacitor influences system noise. Use a 0.47μF capacitor for 200mV full scale, and a 0.047μF capacitor for 2V full scale. See Section 7.1 “Auto-Zero Capacitor (CAZ)” on Auto-Zero Capacitor for more details.30(11)V IN -The analog LOW input is connected to this pin.31(10)V IN +The analog HIGH input signal is connected to this pin.32(9)ANALOG COMMON This pin is primarily used to set the Analog Common mode voltage for battery opera-tion or in systems where the input signal is referenced to the power supply. It alsoacts as a reference voltage source. See Section 8.3 “Analog Common (Pin 32)” on ANALOG COMMON for more details. 33(8)C REF -See Pin 34.34(7)C REF +A0.1μF capacitor is used in most applications. If a large Common mode voltage exists (for example, the V IN - pin is not at analog common), and a 200mV scale is used, a 1μF capacitor is recommended and will hold the rollover error to 0.5 count.35(6)V REF -See Pin 36.© 2006 Microchip Technology Inc.DS21455C-page 7TC7106/A/TC7107/A36(5)V REF +The analog input required to generate a full scale output (1999 counts). Place 100mV between Pins 35 and 36 for 199.9mV full scale. Place 1V between Pins 35 and 36 for 2V full scale. See paragraph on Reference Voltage.37(4)TESTLamp test. When pulled HIGH (to V+) all segments will be turned on and the display should read -1888. It may also be used as a negative supply for externally generated decimal points. See paragraph under TEST for additional information.38(3)OSC3See Pin 40. 39(2)OSC2See Pin 40.40(1)OSC1Pins 40, 39, 38 make up the oscillator section. For a 48kHz clock (3 readings per section), connect Pin 40 to the junction of a 100k Ω resistor and a 100pF capacitor. The 100k Ω resistor is tied to Pin 39 and the 100pF capacitor is tied to Pin 38.TABLE 2-1:PIN FUNCTION TABLE (CONTINUED)Pin Number (40-Pin PDIP)NormalPin No.(40-Pin PDIP)(ReversedSymbol DescriptionTC7106/A/TC7107/ADS21455C-page 8© 2006 Microchip Technology Inc.3.0DETAILED DESCRIPTION(All Pin designations refer to 40-Pin PDIP .)3.1Dual Slope Conversion PrinciplesThe TC7106A and TC7107A are dual slope, integrating Analog-to-Digital Converters. An understanding of the dual slope conversion technique will aid in following the detailed operation theory.The conventional dual slope converter measurement cycle has two distinct phases:•Input Signal Integration•Reference Voltage Integration (De-integration)The input signal being converted is integrated for a fixed time period (T SI ). Time is measured by counting clock pulses. An opposite polarity constant reference voltage is then integrated until the integrator output voltage returns to zero. The reference integration time is directly proportional to the input signal (T RI ). See Figure 3-1.FIGURE 3-1:Basic Dual Slope ConverterIn a simple dual slope converter, a complete conver-sion requires the integrator output to “ramp-up” and “ramp-down.” A simple mathematical equation relates the input signal, reference voltage and integration time.EQUATION 3-1:For a constant V IN :EQUATION 3-2:The dual slope converter accuracy is unrelated to the integrating resistor and capacitor values as long as they are stable during a measurement cycle. An inher-ent benefit is noise immunity. Noise spikes are integrated or averaged to zero during the integration periods. Integrating ADCs are immune to the large conversion errors that plague successive approxima-tion converters in high noise environments. Interfering signals with frequency components at multiples of the averaging period will be attenuated. Integrating ADCs commonly operate with the signal integration period set to a multiple of the 50/60Hz power line period (see Figure 3-2).FIGURE 3-2:Normal Mode Rejection of Dual Slope Converter1RCV R T RI RCT SIV IN (t)dt =∫Where:V R =Reference voltageT SI =Signal integration time (fixed)T RI =Reference voltage integration time (variable).V IN = V RT RI T SITC7106/A/TC7107/A4.0ANALOG SECTIONIn addition to the basic signal integrate and de-integrate cycles discussed, the circuit incorporates an auto-zero cycle. This cycle removes buffer amplifier, integrator, and comparator offset voltage error terms from the conversion. A true digital zero reading results without adjusting external potentiometers. A complete conversion consists of three cycles: an auto-zero, signal integrate and reference integrate cycle.4.1Auto-Zero CycleDuring the auto-zero cycle, the differential input signal is disconnected from the circuit by opening internal analog gates. The internal nodes are shorted to analog common (ground) to establish a zero input condition. Additional analog gates close a feedback loop around the integrator and comparator. This loop permits comparator offset voltage error compensation. The voltage level established on C AZ compensates for device offset voltages. The offset error referred to the input is less than 10μV.The auto-zero cycle length is 1000 to 3000 counts. 4.2Signal Integrate CycleThe auto-zero loop is entered and the internal differen-tial inputs connect to V IN+ and V IN-. The differential input signal is integrated for a fixed time period. The TC7136/A signal integration period is 1000 clock periods or counts. The externally set clock frequency is divided by four before clocking the internal counters. The integration time period is:EQUATION 4-1:The differential input voltage must be within the device Common mode range when the converter and mea-sured system share the same power supply common (ground). If the converter and measured system do not share the same power supply common, V IN-should be tied to analog common.Polarity is determined at the end of signal integrate phase. The sign bit is a true polarity indication, in that signals less than 1LSB are correctly determined. This allows precision null detection limited only by device noise and auto-zero residual offsets.4.3Reference Integrate PhaseThe third phase is reference integrate or de-integrate. V IN- is internally connected to analog common and V IN+is connected across the previously charged reference capacitor. Circuitry within the chip ensures that the capacitor will be connected with the correct polarity to cause the integrator output to return to zero. The time required for the output to return to zero is proportional to the input signal and is between 0 and 2000 counts.The digital reading displayed is:EQUATION 4-2:5.0DIGITAL SECTION (TC7106A) The TC7106A (Figure5-2) contains all the segment drivers necessary to directly drive a 3-1/2 digit liquid crystal display (LCD). An LCD backplane driver is included. The backplane frequency is the external clock frequency divided by 800. For three conversions/ second, the backplane frequency is 60Hz with a 5V nominal amplitude. When a segment driver is in phase with the backplane signal, the segment is “OFF.” An out of phase segment drive signal causes the segment to be “ON” or visible. This AC drive configuration results in negligible DC voltage across each LCD segment. This insures long LCD display life. The polarity segment driver is “ON” for negative analog inputs. If V IN+ and V IN-are reversed, this indicator will reverse. When the TEST pin on the TC7106A is pulled to V+, all segments are turned “ON.” The display reads -1888. During this mode, the LCD segments have a constant DC voltage impressed. DO NOT LEAVE THE DIS-PLAY IN THIS MODE FOR MORE THAN SEVERAL MINUTES! LCD displays may be destroyed if operated with DC levels for extended periods.The display font and the segment drive assignment are shown in Figure5-1.FIGURE 5-1:Display Font and Segment AssignmentIn the TC7106A, an internal digital ground is generated from a 6-volt zener diode and a large P channel source follower. This supply is made stiff to absorb the large capacitive currents when the backplane voltage is switched.T SI =4F OSCx 1000Where: F OSC = external clock frequency.1000 =V INV REF© 2006 Microchip Technology Inc.DS21455C-page 9TC7106/A/TC7107/AFIGURE 5-2:TC7106A Block DiagramDS21455C-page 10© 2006 Microchip Technology Inc.6.0DIGITAL SECTION (TC7107A) Figure6-2 shows a TC7107A block diagram. It is designed to drive common anode LEDs. It is identical to the TC7106A, except that the regulated supply and backplane drive have been eliminated and the segment drive is typically 8mA. The 1000’s output (Pin 19) sinks current from two LED segments, and has a 16mA drive capability.In both devices, the polarity indication is “ON” for negative analog inputs. If V IN- and V IN+ are reversed, this indication can be reversed also, if desired.The display font is the same as the TC7106A.6.1System TimingThe oscillator frequency is divided by 4 prior to clocking the internal decade counters. The four-phase measurement cycle takes a total of 4000 counts, or 16,000 clock pulses. The 4000-count cycle is indepen-dent of input signal magnitude.Each phase of the measurement cycle has the follow-ing length:1.Auto-zero phase: 1000 to 3000 counts (4000 to12000 clock pulses).For signals less than full scale, the auto-zero phase is assigned the unused reference integrate time period: 2.Signal integrate: 1000 counts (4000 clockpulses).This time period is fixed. The integration period is: EQUATION 6-1:3.Reference Integrate: 0 to 2000 counts (0 to 8000clock pulses).The TC7106A/7107A are drop-in replacements for the 7106/7107 parts. External component value changes are not required to benefit from the low drift internal reference.6.2Clock CircuitThree clocking methods may be used (see Figure6-1):1.An external oscillator connected to Pin 40.2. A crystal between Pins 39 and 40.3.An RC oscillator using all three pins.FIGURE 6-1:Clock CircuitsT SI = 40001F OSC ⎛⎝⎞⎠Where: F OSC is the externally set clock frequency.FIGURE 6-2:TC7107A Block Diagram7.0COMPONENT VALUESELECTION7.1Auto-Zero Capacitor (C AZ)The C AZ capacitor size has some influence on system noise. A 0.47μF capacitor is recommended for 200mV full scale applications where 1LSB is 100μV. A 0.047μF capacitor is adequate for 2.0V full scale applications. A mylar type dielectric capacitor is adequate.7.2Reference Voltage Capacitor(C REF)The reference voltage used to ramp the integrator out-put voltage back to zero during the reference integrate cycle is stored on C REF. A 0.1μF capacitor is acceptable when V IN- is tied to analog common. If a large Common mode voltage exists (V REF- – analog common) and the application requires 200mV full scale, increase C REF to1.0μF. Rollover error will be held to less than 1/2 count.A mylar dielectric capacitor is adequate.7.3Integrating Capacitor (C INT)C INT should be selected to maximize the integrator out-put voltage swing without causing output saturation. Due to the TC7106A/7107A superior temperature coefficient specification, analog common will normally supply the differential voltage reference. For this case, a ±2V full scale integrator output swing is satisfactory. For 3 readings/second (F OSC = 48kHz), a 0.22μF value is suggested. If a different oscillator frequency is used, C INT must be changed in inverse proportion to maintain the nominal ±2V integrator swing.An exact expression for C INT is:EQUATION 7-1:C INT must have low dielectric absorption to minimize rollover error. A polypropylene capacitor is recommended.7.4Integrating Resistor(R INT)The input buffer amplifier and integrator are designed with class A output stages. The output stage idling current is 100μA. The integrator and buffer can supply 20μA drive currents with negligible linearity errors. R INT is chosen to remain in the output stage linear drive region, but not so large that printed circuit board leakage currents induce errors. For a 200mV full scale, R INT is 47kΩ. 2.0V full scale requires 470kΩ.Note:F OSC = 48kHz (3 readings per sec).7.5Oscillator ComponentsR OSC (Pin 40 to Pin 39) should be 100kΩ. C OSC is selected using the equation:EQUATION 7-2:For F OSC of 48kHz, C OSC is 100pF nominally.Note that F OSC is divided by four to generate the TC7106A internal control clock. The backplane drive signal is derived by dividing F OSC by 800.To achieve maximum rejection of 60Hz noise pickup, the signal integrate period should be a multiple of 60Hz. Oscillator frequencies of 240kHz, 120kHz, 80kHz, 60kHz, 48kHz, 40kHz, etc. should be selected. For 50Hz rejection, oscillator frequencies of 200kHz, 100kHz, 66-2/3kHz, 50kHz, 40kHz, etc. would be suitable. Note that 40kHz (2.5 readings/second) will reject both 50Hz and 60Hz.7.6Reference Voltage SelectionA full scale reading (2000 counts) requires the input signal be twice the reference voltage.*V FS = 2V REF.C INT =(4000)V INT1F OSCV FSR INT⎛⎝⎞⎠⎛⎝⎞⎠Where:F OSC=Clock Frequency at Pin 38V FS=Full Scale Input VoltageR INT=Integrating ResistorV INT=Desired Full Scale Integrator Output Swing ComponentValueNominal Full Scale Voltage200.0mV 2.000VC AZ0.47μF0.047μFR INT47kΩ470kΩC INT0.22μF0.22μFRequired Full Scale Voltage*V REF200.0mV100.0mV2.000V 1.000VF OSC =0.45RCIn some applications, a scale factor other than unity may exist between a transducer output voltage and the required digital reading. Assume, for example, a pres-sure transducer output is 400mV for 2000 lb/in2. Rather than dividing the input voltage by two, the reference voltage should be set to 200mV. This permits the trans-ducer input to be used directly.The differential reference can also be used when a digital zero reading is required when V IN is not equal to zero. This is common in temperature measuring instru-mentation. A compensating offset voltage can be applied between analog common and V IN-. The trans-ducer output is connected between V IN+ and analogcommon.The internal voltage reference potential available at analog common will normally be used to supply the converter’s reference. This potential is stable when-ever the supply potential is greater than approximately 7V. In applications where an externally generated reference voltage is desired, refer to Figure7-1.FIGURE 7-1:External Reference8.0DEVICE PIN FUNCTIONALDESCRIPTION8.1Differential Signal InputsV IN+ (Pin 31), V IN- (Pin 30)The TC7106A/7017A is designed with true differential inputs and accepts input signals within the input stage common mode voltage range (V CM). The typical range is V+ – 1.0 to V+ + 1V. Common mode voltages are removed from the system when the TC7106A/ TC7107A operates from a battery or floating power source (isolated from measured system) and V IN- is connected to analog common (V COM) (see Figure8-2). In systems where Common mode voltages exist, the 86dB Common mode rejection ratio minimizes error. Common mode voltages do, however, affect the inte-grator output level. Integrator output saturation must be prevented. A worst-case condition exists if a large positive V CM exists in conjunction with a full scale negative differential signal. The negative signal drives the integrator output positive along with V CM (see Figure). For such applications the integrator output swing can be reduced below the recommended 2.0V full scale swing. The integrator output will swing within 0.3V of V+ or V-without increasing linearity errors.FIGURE 8-1:Common Mode VoltageReduces Available Integrator Swing (VCOM ≠ VIN)8.2Differential ReferenceV REF+ (Pin 36), V REF- (Pin 35)The reference voltage can be generated anywherewithin the V+ to V-power supply range.To prevent rollover type errors being induced by largeCommon mode voltages, C REF should be largecompared to stray node capacitance.The TC7106A/TC7107A circuits have a significantlylower analog common temperature coefficient. Thisgives a very stable voltage suitable for use as areference. The temperature coefficient of analogcommon is 20ppm/°C typically.8.3Analog Common (Pin 32)The analog common pin is set at a voltage potentialapproximately 3.0V below V+. The potential is between2.7V and3.35V below V+. Analog common is tied inter-nally to the N channel FET capable of sinking 20mA.This FET will hold the common line at 3.0V should anexternal load attempt to pull the common line towardV+. Analog common source current is limited to 10μA.Analog common is, therefore, easily pulled to a morenegative voltage (i.e., below V+ – 3.0V).The TC7106A connects the internal V IN+ and V IN-inputs to analog common during the auto-zero cycle.During the reference integrate phase, V IN- is con-nected to analog common. If V IN- is not externally con-nected to analog common, a Common mode voltageexists. This is rejected by the converter’s 86dB Com-mon mode rejection ratio. In battery operation, analogcommon and V IN- are usually connected, removingCommon mode voltage concerns. In systems where V-is connected to the power supply ground, or to a givenvoltage, analog common should be connected to V IN-. [INThe analog common pin serves to set the analog section reference or common point. The TC7106A is specifically designed to operate from a battery, or in any measure-ment system where input signals are not referenced (float), with respect to the TC7106A power source. The analog common potential of V+ – 3.0V gives a 6V end of battery life voltage. The common potential has a 0.001% voltage coefficient and a 15Ω output impedance.With sufficiently high total supply voltage (V+ – V- > 7.0V), analog common is a very stable potential with excellent temperature stability, typically 20ppm/°C. This potential can be used to generate the reference voltage. An external voltage reference will be unneces-sary in most cases because of the 50ppm/°C maximum temperature coefficient. See Internal Voltage Reference discussion.8.4TEST (Pin 37)The TEST pin potential is 5V less than V+. TEST may be used as the negative power supply connection for external CMOS logic. The TEST pin is tied to the inter-nally generated negative logic supply (Internal Logic Ground) through a 500Ω resistor in the TC7106A. The TEST pin load should be no more than 1mA.If TEST is pulled to V+ all segments plus the minus sign will be activated. Do not operate in this mode for more than several minutes with the TC7106A. With TEST=V+, the LCD segments are impressed with a DC voltage which will destroy the LCD.The TEST pin will sink about 10mA when pulled to V+.8.5Internal Voltage ReferenceThe analog common voltage temperature stability has been significantly improved (Figure8-3). The “A”version of the industry standard circuits allow users to upgrade old systems and design new systems without external voltage references. External R and C values do not need to be changed. Figure8-4 shows analog common supplying the necessary voltage reference for the TC7106A/TC7107A.FIGURE 8-3:Analog Common Temperature CoefficientFIGURE 8-4:Internal Voltage ReferenceConnection。

微芯片技术有限公司产品设计指南说明书

Battery Power Function Pack Design Guide Powering Y our Portable DesignMicrocontrollers PIC16C781MOSFET Drivers TC1411NBattery Chargers MCP73828Charge Pump DC/DC Converters MCP1252-ADJLow Dropout Linear Regulators TC55, TC1016Design ideas in this guide are based on many of the devices featured in Microchip Technology's Battery Management Function Pack, or “Fun Pack.” A complete device list and corresponding data sheets for these products can be found at /funpack Design ideas in this guide use the following devices:Operational Amplifiers MCP6041, MCP602Switching Regulators MCP1601, TC1102Closed loop control with linear regulators.Often the voltage source is “incompatible” with the load. A buffer needs to be placed between the source and load to regulate or control the voltage and/or current.Linear regulators provide closed loop control to “regulate”the voltage at the load. A basic linear regulator has three main components: an operational amplifier, a voltage reference, and a pass transistor . The main purpose of a linear regulator is to produce a constant, accurate outputvoltage at a lower magnitude than the input voltage.TC1016 Linear Regulator Features:n Space-Saving 5-Pin SC-70 Packagen Extremely Low Operating Current for Longer n Battery Life: 53 µA (typ.)n Very Low Dropout Voltage n Rated 80 mA Output CurrentnRequires only 1 µF Ceramic Output Capacitancen High Output Voltage Accuracy: ±0.5% (typ.)n 10 µsec (typ.) Wake-Up Time from SHDN n Power-Saving Shutdown Mode: 0.05 µA(typ.)n Over-Current and Over-Temperature Protection nPin Compatible Upgrade for Bipolar RegulatorsBeyond the basics, linear regulators often offer additional features: over-current protection, thermal protection, and reversed polarity protection to name a few.Microchip offers a line of CMOS, low dropout linear regulators. A low dropout regulator is a type of linearregulator designed to minimize the saturation of the output transistor and to minimize the drive requirements. LDOs can operate with a very small input to output differential.Specifications: Selected Linear RegulatorsTypical Typical Dropout Device Max. Input Output Output Active Voltage @ Max. Name Voltage Voltage Current (mA)Current (µA)I OUT (mV)FeaturesPackages TC1016 6.0 1.8, 2.7, 2.8, 3.08050150Shutdown5-pin SC-70TC5510 1.8, 2.5, 3.0, 3.3, 5.0250 1.13803-pin SOT-23A/SOT-89,3-pin TO-92TC2014 6.0 1.8, 2.5, 3.0, 3.3505545Shutdown, Reference bypass input 5-pin SOT-23A TC2015 6.0 1.8, 2.7, 2.8, 3.0, 3.31005590Shutdown, Reference bypass input 5-pin SOT-23A TC2185 6.0 1.8, 2.7, 2.8, 3.0, 3.315055140Shutdown, Reference bypass input 5-pin SOT-23A TC2116 6.0 1.8, 2.7, 2.8, 3.0, 3.315055140Shutdown, Error output5-pin SOT-23A TC21176.01.8,2.5,3.0, 3.3800806003-pin SOT-223, 3-pin DDPAKSpecifications: Selected Linear Regulator Combination Products:TC1300 6.0 2.5, 2.7, 2.8, 2.85, 30080210Shutdown Reference bypass input,8-pin MSOPLDO plus RESET output TC1301A/B*6.01.5 - 3.3 @ 100 mV300 / 150116104 / 150Dual LDO with RESET & 8-pin MSOP , 8-pin DFNincrementShutdown; TC1301B has individual shutdown*available summer 2003names: voltage step-down converter, DC-to-DC converter,chopper converter, etc. No matter what the name, inductor based, buck derived, switch-mode converters account for 80% to 90% of all converters sold.Microchip offers inductor based buck regulators and controllers. The distinction is whether or not the switch (MOSFET) is internal to the device (regulator) or controlled externally (controller). The schematic represented here depicts a MCP1601 buck regulator with its associatedexternal components.MCP1601 Synchronous Buck Regulator Features:n Input Range of 2.7V to 5.5V n PWM, PFM and LDO Operation n Integrated Switchesn 750 kHz Fixed Switching Frequencyn Oscillator Synchronization to 1 MHz PWM Mode n Auto-Switching from PWM/PFMn100% Duty Cycle Capable for Low Input Voltagen 500 mA Continuous Output Current n Under-Voltage Lock-Out Protection n Over-Temperature Protection n Integrated Soft Start Circuitry n Output Voltage Capability to 0.9Vn Wide Operating Temperature Range: -40°C to +85ºC nSmall MSOP8 PackageEmploying a switch-mode power converter.Anotherapproach to transferring the battery energy to the system load is to employ a switch-mode power converter . The primary advantage of a switch-mode power converter is that it can, ideally, accomplish power conversion and regulation at 100% efficiency. All power loss is due to non-ideal components and power loss in the control circuit.The buck converter is an inductor based switch-mode power converter used to step-down an input source to a lower magnitude output. The buck converter goes by manySpecifications: Selected Switching RegulatorsInput Voltage Output Switching Device OutputBuck/BoostRange (V)Voltage (V)Frequency FeaturesPackages MCP1601 Adjustable Step-Down 2.7 to 5.50.9 to V IN PWM/PFM/UVLO, Auto Switching, LDO 8-pin MSOP LDO TC105 Fixed Step-Down 2.2 to 10 3.0, 3.3, 5.0PFM/PWM Low-power shutdown mode5-pin SOT-23A TC110 Fixed Step-Up 2.0 to 10 3.0, 3.3, 5.0PFM/PWM Soft-start, Low-power shutdown mode 5-pin SOT-23A TC115 Fixed Step-Up 0.9 to 10 3.0, 3.3, 5.0PFM/PWM Feedback voltage sensing, Low-power shutdown mode5-pin SOT-89TC120 Fixed Step-Down 1.8 to 10 3.0, 3.3, 5.0PFM/PWM Soft-start, Low-power shutdown mode 8-pin SOP TC125 Fixed Step-Up 0.9 to 10 3.0, 3.3, 5.0PFM Low-power shutdown mode 5-pin SOT-23A TC126FixedStep-Up0.9 to 103.0, 3.3, 5.0PFMFeedback voltage sensing5-pin SOT-23A34Specifications: Battery Charger FamilyDevice Vcc Typical Supply Name Mode Cell Type Range (V)Current (µA)Features Packages MCP73826Linear Single Cell Lithium Ion 4.5 to 5.5260Small size6-pin SOT-23A MCP73827Linear Single Cell Lithium Ion 4.5 to 5.5250Mode indicator, charge current monitor 8-pin MSOP MCP73828LinearSingle Cell Lithium Ion4.5 to5.5265Charge complete indicator, temperature monitor8-pin MSOPMCP73828 Battery Charger Features:n High Accuracy Preset Voltage Regulation n Programmable Charge Current n Charge Complete IndicatornContinuous Temperature MonitoringUsing the MCP73828 charge management controller.The MCP73828 is a linear charge management controller for use in space-limited, cost sensitive applications. The MCP73828 combines high accuracy constant voltage,controlled current regulation, cell preconditioning, celltemperature monitoring, and charge complete indication in a space saving 8-pin MSOP package. The MCP73828provides a stand-alone charge management solution.n Automatic Power-Down when Input Power Removed n Shutdown Input for Charge Termination Control n Small 8-pin MSOP PackageSpecifications: PIC16C781/782Device OTP/Flash RAM I/O 8-Bit ADCComp-Timers/Max.Name Bytes Words Bytes Pins Packages Channels arators WDT Speed MHz.Other FeaturesPIC16C78117921024x141281620P , 20SO, 20SS, 821-16 bit, 1-8 bit,20Precision Vref, Op Amp, PSMC,PIC16C78235842048x1420JW1-WDT4MHz internal oscillator, DAC TC55 Low Dropout Positive Voltage Regulator Features:n Very Low Operating Current (1µA)n Very Low Dropout Voltage: 120mV typ at 100mA, 380mV typ at200mAn High Output Current: 250mA (V OUT = 5.0V)TC1411N Power MOSFET Driver Features:n Single, Non-inverting, Low-Side Driver, 1A Peak Output Current n Latch-Up Protected: Will Withstand 500mA Reverse Current n Input Will Withstand Negative Inputs Up to 5V nESD Protected: 4kVSwitch-mode, multi-chemistry charge management controller.The PIC16C781/782 are mixed analog/digital microcontrollers that combine the popular PIC®architecture with new mixed signal peripherals. The resulting devices change many of the old conventions of embedded design, and open up new application possibilities for the microcontroller .One of the applications that can take advantage of the PIC16C781/782’s unique peripheral set is a switch-mode,PIC16C781/782 Microcontroller Features:n Complete programmability n Enormous flexibilityn Stand-alone operation or in conjunction with a Smart Battery Pack nSix peripherals including 8x8-bit A/D, 8-bit D/A, V REF , Op Amp, 2x comparators, programmable switch mode controllerMCP602 Op Amp Features:n Specifications rated from 2.7V to 5.5V supplies n 2.8MHz GBWP , Unity gain stable n Low power I DD = 325mA maxnDual (MCP601 sinlge, MCP604 quad, MCP603 w/Chip Select)multi-chemistry charge management controller . This solution provides an enormous amount of design flexibility. The PIC16C781/782 can be used in a variety of switch-mode architectures allowing for diverse input and output voltages, control over charge current, charge voltage, or both. In addition, charge termination and multiple safety features can be incorporated.Specifications: MCP601/2/3/4Device# per package GBWP I Q Typ. (µA)V OS Max (mV)Operating VoltagePackagesMCP601/2/3/41/2/1 with CS/4 2.8 MHz23022.7 to 5.58-pin PDIP , 8-pin SOIC, 8-pin MSOP , 5-pin SOTSpecifications: TC55 Low Dropout Positive Voltage RegulatorDevice Max. Input VoltageOutput Voltage (V)Typ. Dropout Voltage @ 200mVTyp. Output Volt. Accuracy (%)PackagesTC55101.8,2.5,3.0,3.3,5.0380mV±0.53-pin SOT-23A, 3-pin SOT-89, 3-pin TO-92Specifications: TC1411N Power MOSFET DriverDevice Configuration Peak Output Current (A)Output Resistance (RH/RL) (Max. Ω@ 25°C)Max. Supply Voltage (V)PackagesTC1411NSingle, non-inverting111/11168-pin PDIP , 8-pin SOIC56Biasing the backlighting. The MCP1252-ADJ is an inductorless, positive-regulated charge pump DC/DC converter. The device generates an adjustable output voltage. It is specifically designed for applications requiring low noise and high efficiency and is able to deliver up to 120 mA output current. The device allows the input voltage to be lower or higher than the output voltage, by automatically switching between buck/ boostoperation.MCP1252 Charge Pump Features:n Inductorless, Buck/Boost, DC/DC Converter n Low Power: 80 µA (Typical)n 120 mA Output Currentn Wide Operating Temperature Range: -40°C to +85°C n Thermal Shutdown and Short-Circuit Protection nUses Small Ceramic Capacitorsn Low Power Shutdown Mode: 0.1 µA (Typical)n Shutdown Input Compatible with 1.8V Logic n V IN Range: 2.0V to 5.5V n Adjustable Output Voltage n Space-saving, 8-Lead MSOPnSoft-Start Circuitry to Minimize In-Rush CurrentToday's new color displays require a pure white light for back lighting. White light emitting diodes have become the component of choice. The MCP1252-ADJ is an excellent choice for biasing the back lighting. Light intensity is controlled uniformly through the use of ballast resistors.The peak intensity is set by the feedback to theMCP1252-ADJ. Dimming is accomplished by pulse-width modulating the shutdown pin of the device.Selected Regulated Charge Pump DC/DC Converters Specifications:Typical ActiveDevice Input Voltage Output Max. Input Output NameRange (V)VoltageCurrent (µA)Current (mA)FeaturesPackages MCP1252-33X50 2.7 to 5.5Selectable 3.3 or 5.0V 120 120mA for V IN >3.0V Power-Good output, 650 kHz oscillator 8-pin MSOP MCP1252-ADJ 2.0 to 5.5 Adjustable 1.5V to 5.5V 120 120mA for V IN >3.0V Power-Good output, 650 kHz oscillator 8-pin MSOP MCP1253-33X50 2.7 to 5.5 Selectable 3.3 or 5.0V120 120mA for V IN >3.0V Power-Good output, 1 MHz oscillator 8-pin MSOP MCP1253-ADJ 2.0 to 5.5 Adjustable 1.5V to 5.5V120 120mA for V IN >3.0VPower-Good output, 1 MHz oscillator8-pin MSOPTC11422.5 to 5.5-3V to -5V40020Regulated GaAs FET Supply, Internal 200 kHz oscillator, External clock 3 kHzto 500 kHz, Low-power shutdown mode 8-pin MSOPMicrochip also offers Inverting or Doubling Charge Pumps, Multi-Function Charge Pumps and Inverting and Doubling Charge Pumps. See the Microchip website for complete specifications .Driving white light emitting diodes in series. Analternative to the MCP1252 back lighting approach is to drive the white light emitting diodes in series. The series connection provides improved brightness matchingbetween the diodes since they all operate with the sameTC110 Step-Up DC/DC Controller Features:n Assured Start-up at 0.9Vn 50uA (Typ) Supply Current (f OSC = 100kHz)n 300mA Output Current @ V IN > 2.7V n 0.5uA Shutdown Moden 100kHz and 300kHz Switching Frequency Options n Programmable Soft-Start n 84% Typical EfficiencynSmall Package: 5-Pin SOT-23ASelected Switching Regulators Specifications:Input Voltage Output SwitchingDevice Output Buck/Boost Range (V)Voltage (V)Frequency FeaturesPackages TC110 Fixed Step-Up 2.0 to 10 3.0, 3.3, 5.0PFM/PWM Soft-start, Low-power shutdown mode 5-pin SOT-23A TC120FixedStep-Down1.8 to 103.0, 3.3, 5.0PFM/PWMSoft-start, Low-power shutdown mode8-pin SOPcurrent. Light intensity is adjusted by controlling the current through the diodes.The TC110 is a boost controller that can be used to bias the diodes in series as depicted.MCP6041/2/3/4 Operational Amplifier Features:n Low Quiescent Current: 600 nA/Amplifier (typ)n Rail-to-Rail Input: -0.3 V to V DD +0.3 V (max)n Rail-to-Rail Output: V SS +10 mV to V DD -10 mV (max)n Gain Bandwidth Product: 14 kHz (typ)n Wide Supply Voltage Range: 1.4 V to 5.5 V (max)n Unity Gain Stablen Available in Single, Dual and Quad n Chip Select (CS) with MCP6043n5-lead SOT-23 package (MCP6041 only)Selected Op Amp Specifications:Device# per packageGBWP IQ Typ. (µA)V OS Max (mV)Operating VoltageFeatures Packages MCP6041114 kHz 0.63 1.4 to 5.5Rail-to-rail I/O, 8-pin PDIP/SOIC/MSOP MCP61411100 kHz 0.63 1.4 to 5.5Rail-to-rail I/O, G>10 stable 8-pin PDIP/SOIC/MSOP MCP61422100 kHz 0.63 1.4 to 5.5Rail-to-rail I/O, G>10 stable 8-pin PDIP/SOIC/MSOP MCP61431100 kHz 0.63 1.4 to 5.5Rail-to-rail I/O, G>10 stable, CS 8-pin PDIP/SOIC/MSOP MCP61444100 kHz0.631.4 to 5.5Rail-to-rail I/O, G>10 stable14-pin PDIP/SOIC/MSOP7-The following Application Notes and Technical Briefs are available on the Microchip website: Application Notes:AN246:Driving the Analog Inputs of a SAR A/D Converter AN667:Smart Battery Charger with SMBus InterfaceAN693:Understanding A/D Converter Performance Specifications AN779:Using the Microchip TC54 Voltage DetectorAN786:Considerations for Driving Power MOSFETs in High Current, Switch-mode Regulators AN792: A Method to Determine How Much Power a SOT23 Can Dissipate in an ApplicationAN793:Power Management in Portable Applications: Understanding the Buck Switch-mode Power Converter AN799:Matching MOSFET Drivers to MOSFETsTechnical Briefs:TB065:Linear Circuit Devices for Applications in Battery Powered Wireless SystemsEvaluation Boards:Microchip offers a number of boards to help you evaluate device families. Contact your local Microchip sales office for a demonstration.Evaluation boards are available for the following devices featured in this guide.MCP1252/3MCP73826/7/8MCP1601MCP1301Information subject to change. The Microchip name and logo, PIC, PICmicro, are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other coun-tries. All other trademarks mentioned herein are the property of their respective companies. © 2003, Microchip Technology Inc. All rights reserved. DS39610A 5/2003Microchip Technology Inc. • 2355 W. Chandler Blvd. • Chandler, AZ 85224-6199 • (480) 792-7200 • Fax (480) 792-9210Microchip Technology’s Analog & Interface Product Families。

常见材料牌号对照

合金结构 钢

42SiMn

合金结构 20SiMn2

钢

MoV

合金结构 25SiMn2

钢

MoV

合金结构 37SiMn2

钢

MoV

合金结构 钢

40B

合金结构 钢

45B

合金结构 钢

50B

合金结构 钢

40MnB

合金结构 钢

45MnB

合金结构 钢

20Mn2B

合金结构 20MnMo

钢

B

合金结构

钢

15MnVB

合金结构

ML40

CE40E4

40

冷镦 钢

ML45

CE45E4

45 Cq45

冷镦 钢

ML25Mn CE28E4

冷镦 钢

ML30Mn CE28E4

冷镦 钢

ML35Mn CE35E4

Cq35

冷镦 钢

ML40Mn CE40E4 40г

冷镦 钢

ML45Mn CE45E4 45г

Cq45

冷镦 钢

ML15Cr

15X

17Cr3

合金结构 钢

40Cr

合金结构 钢

45Cr

合金结构 钢

50Cr

合金结构 钢

38CrSi

41Cr

40X 45X 50X 38XC

41Cr4

合金结构 钢

12CrMo

12XM

12CrMo4 4

合金结构 钢

15CrMo

15XM

合金结构 钢

20CrMo

18CrMo4 20XM

合金结构 钢

30CrMo

30XM

合金结构 钢

SPFC590

STKT540 STKT540 STKT540

TC中文文档

公告至A4大小的纸张用户:此文件格式提供了在8.5x11美国信。

它可以被打印在A4纸,但将有广泛的底部边缘。

重新格式化为A4纸只需要几个简单的步骤。

一是在Word中打开文件| a4的布局,并选择选项卡的大小。

二,进入第二页(目录中的任意位置),然后按F9键更新。

三,到最后一页指数(任何地方),然后按F9键再次重新索引。

四,保存在一个方便的新名称。

此文件PDF版本可在/downloads/tc.asp。

* Windows和Windows徽标是公司的商标群体的Microsoft。

目录引入自动化测试和TESTCOMPLETE---------------------------------------------------------------- --3自动化测试-----------------------------------------------------------------------------------------------------3测试类型--------------------------------------------------------------------------------------------------------3TestComplete项目和项目项--------------------------------------------------------------------------------4TestComplete用户界面---------------------------------------------------------------------------------------5TestComplete测试对象模型---------------------------------------------------------------------------------6检查和存储器----------------------------------------------------------------------------------------------------8创建您的第一个测试-------------------------------------------------------------------------------------------91创建一个测试项目------------------------------------------------------------------------------------------102。

天地伟业网络存储产品计算工具

码流大小 (Mbps)

1路1小时存储容量 (MB)

512

225

2

900

3

1350

6

2700

8ห้องสมุดไป่ตู้

3600

10

4500

监控路数

540 200 150

0 100 100

方案配置

方案可选产品型 号

方案需求容量 (TB)

硬盘净需求(块,无 方案需求硬盘(块,

RAID和热备)

RAID+热备)

1 TC-RS1012L

1.39

12.36 13.90 0.00 24.72 30.90

方案主盘阵数量 方案扩展柜设 方案剩余槽位数

(台)

备数量(台) (块)

275

--

0

197

--

8

20

--

0

60

--

10

138

137

0

50

147

8

2 2

主柜数量>>>

单套硬盘数

12 16 16 48 12 12 1 16 16 1

校验盘数量

1 1 1 1 1 1 扩展柜数量>>> 1 1 扩展柜数量>>>

摄像头编 号

视频格式

1 CIF(Kbps)

2 D1格式 3 720P 4 1080P(压缩) 5 1080P(标准) 6 1080P(无压缩)

24

1

存储净容量 >>>

1

32

18.19 36.38 25.47

1

32

3

存储净容量 >>>

枪支(弹药)库室风险等级划分与安全防范要求GA1016-2012

ICS?13.310A 91GA中华人民共和国公共安全行业标准GA 1016—2012枪支(弹药)库室风险等级划分与安全防范要求Level of risk and security requirementsfor guns (ammunition) depot/ storage room2012 - 12 - 26发布2012 - 12 - 26实施发布中华人民共和国公安部前言本标准的全部技术内容为强制性。

本标准按照GB/T1.1-2009给出的规则起草。

本标准由公安部治安管理局提出。

本标准由全国安全防范报警系统标准化技术委员会(SAC/TC 100)归口。

本标准起草单位:公安部治安管理局、北京市公安局治安管理总队。

本标准起草人:钱熊飞、何力、董传华、郭怡林、唐克敏、冯志强。

枪支(弹药)库室风险等级划分与安全防范要求1 范围本标准规定了枪支(弹药)库室风险等级划分标准和安全防范的基本要求,是枪支(弹药)库室安全防范工程设计、施工、验收和安全检查等工作的基本依据。

本标准适用于《中华人民共和国枪支管理法》规定的枪支(弹药)制造、配售、配备、配置单位和配置科研、展览、道具枪支(弹药)单位的库室建设和安全防范工作。

2 规范性引用文件下列文件对于本文件的应用是必不可少的。

凡是注明日期的引用文件,仅注日期的版本适用于本文件。

凡是不注日期的引用文件,其最新版本(包括所有的修改单)适用于本文件。

GB 17565-2007 防盗安全门通用技术条件GB 50003-2001 砌体结构设计规范GB 50010-2010混凝土结构设计规范GB 50068-2001 建筑结构可靠度设计统一标准GB 50348-2004 安全防范工程技术规范GB 50394-2007 入侵报警系统工程设计规范GB 50395-2007 视频安防监控系统工程设计规范GA/T 73-1994 机械防盗锁GA 374-2001 电子防盗锁3 术语和定义GB 50348-2004 中确立的以及下列术语和定义适用于本文件。

TC-RS1016L-J网络存储扩展柜使用说明书

网络存储扩展柜使用说明书TC-RS1016L-J网络存储扩展柜使用说明书声 明在您正式使用本存储系统之前,请您先阅读以下声明。

只有您阅读了以下声明并且同意以下各条款后,方可正式开始使用本存储系统;如果您对以下条款有任何疑问,请和您的供货商联系或直接与我们联系。

如您未向我们就以下条款提出疑问并开始使用本系统,则是默认您已经同意了以下各条款。

1、我们提醒您特别注意:在任何时候,除了我们提示您可以修改的参数以外,您不要修改本存储系统主板BIOS中的任何其他参数。

2、在您使用的存储系统出现任何硬件故障或您希望对硬件进行任何升级时,请您将机器的详细硬件配置反映给我们的客户服务中心;您不要自行拆卸存储系统机箱及机箱内任何硬件设备。

3、本存储系统的内存、CPU、CPU散热片、风扇、硬盘托架、硬盘等都是特殊规格的,请您不要将它们和任何其他型号机器的相应设备混用。

4、您在使用存储系统过程中遇到的任何软件问题,我们希望您首先和相应软件的提供商联系,由他和我们联系,以方便我们沟通、共同解决您碰到的问题。

对于如数据库、网络管理软件或其他网络产品等的安装、运行问题,我们尤其希望您能够这样处理。

5、如果上架安装本存储系统,请先仔细阅读本手册中的快速安装指南。

天地伟业致力于产品功能和性能的持续提升,这可能导致部分功能及操作与手册描述有所差异,但不会影响使用,如果您有任何使用疑难问题,请与我们的技术保障中心联系。

6、我们特别提醒您:在使用过程中,注意对您的数据进行必要的备份。

7、此为A级产品,在生活环境中,该产品可能会造成无线电干扰。

在这种情况下,可能需要用户对其干扰采取切实可行的措施。

8、请仔细阅读并遵守本手册的安全细则。

9、本手册中涉及的各软、硬件产品的标识、名称版权归产品的相应公司拥有。

安全细则1、本系统中的电源设备可能会产生高电压和危险电能,从而导致人身伤害。

请勿自行卸下主机盖并拆装、更换系统内部的任何组件,除非另外得到天地伟业的通知,否则只有经过天地伟业培训的维修技术人员才有权拆开主机盖及拆装、更换内部组件。

IEEEStd1016_SDD