电路板电镀部分IST孔壁及内层线路品质介绍

PCB质量接收标准

注意:1.当生产指示中有与以下项目相冲突时,需以生产指示为准。

2.当生产指示及以下项目未列举时,需以《质量检验规范》标准为准。

3.以下所提到的SMT包括BGA。

一.线路图形1.板面残铜:每面<=1处。

最大尺寸 <=0.5mm,离最近导体>=0.2mm.2.焊盘与SMT要求:1)焊盘无缩锡现象。

2)SMT和插装焊盘未有锡凸、划伤或缺损现象,针孔造成SMD的长或宽减少<=10%.3.孔:1)孔壁上出现的镀铜层破洞,不可超过1个,且破孔数不超过孔总数的5%,横向<=90度,纵向<=板厚的5%。

2)孔壁上出现的附着层(如锡层)破洞,不可超过3个,破孔面积未超过孔面积的10%,且破孔数不超过孔总数的5%。

3)A:对于阻焊塞孔或阻焊盖孔的孔,孔内或孔口残留的铅锡应满足:过电孔残留锡珠直径不大于0.1mm,含锡珠的过电孔不可超过板上过电孔总数的 1%;*但无SMT板的过电孔和单面SMT板的过孔焊接面可不受此限制。

B:对于非阻焊塞孔的孔,孔内或孔口残留的铅锡应满足:孔径<=0.35mm的过孔,且在焊接中无铅锡露出孔口或流到板面,允许铅锡塞孔;对于孔径>0.35mm的过孔,如铅锡塞孔或焊接中有铅锡露出孔口或流到板面则不接受。

4)金属化孔的孔电阻应小于1 mΩ5)孔壁粗糙度不超过30um,玻璃纤维突出不超过20 um.4.导体间锡拉间:缺陷在组件面不超过50% ,SS面小于30%。

5.大焊盘上的聚锡:缺陷在CS面不超过整个焊盘面积的50%,SS面小于30%,同时聚锡处锡高须小于0.051 mm.6.SMT之间及SMT到线的蚀刻间距要求仅需要大于或等于4 mil即可。

二、修补1.补线要求:a)导线拐弯处不允许补线;b)内层不允许补线;c)特性阻抗控制的线、差分线不允许补线。

d)过孔不允许补线;e)相邻平行导线不允许同时补线;f)断线长度大于2mm的不允许补线;g)焊盘周围不允许补线,补线点距离焊盘边缘大于3mm;h)同一导体补线最多1处;每板补线<=5处;每面<=3处;补线板的比例<=8%;三、阻焊1.阻焊膜(绿油)1)绿油圈到开窗的有孔PAD间距>=0.051mm;2)过电孔绿油盖焊环有锡圈或过孔开窗的板,允许绿油入孔数目<=过孔总数的5% ,不允许塞孔。

PCB各层介绍(讲得比较详细)

PCB各层介绍(讲得⽐较详细)信号层(SignalLayers):信号层包括TopLayer、Bottom Layer、Mid Layer 1…30。

这些层都是具有电⽓连接的层,也就是实际的铜层。

中间层是指⽤于布线的中间板层,该层中布的是导线。

内层(Internal Plane):Internal Plane 1…16,该类型的层仅⽤于多层板,这些层⼀般连接到地和电源上,成为电源层和地层,也具有电⽓连接作⽤,也是实际的铜层,但该层⼀般情况下不布线,是由整⽚铜膜构成。

丝印层(SilkscreenOverlay):包括顶层丝印层(Top overlay)和底层丝印层(Bottom overlay)。

定义顶层和底层的丝印字符,就是⼀般在阻焊层之上印的⼀些⽂字符号,⽐如元件名称、元件符号、元件管脚和版权等,⽅便以后的电路焊接和查错等。

锡膏层(PasteMask):或称助焊层,包括顶层锡膏层(Top paste)和底层锡膏层(Bottom paste),指我们可以看到的露在外⾯的表⾯贴装焊盘,也就是在焊接前需要涂焊膏的部分。

所以,这⼀层在焊盘进⾏热风整平和制作焊接钢⽹时也有⽤。

阻焊层(SolderMask):包括顶层阻焊层(Top solder)和底层阻焊层(Bottom solder),其作⽤与锡膏层相反,指的是要盖绿油的层。

该层不粘焊锡,防⽌在焊接时相邻焊接点的多余焊锡短路。

阻焊层将铜膜导线覆盖住,防铜膜过快在空⽓中氧化,但是在焊点处留出位置,并不覆盖焊点。

阻焊层⽤于在设计过程中匹配焊盘,是⾃动产⽣的。

机械层(MechanicalLayers):最多可选择16层机械加⼯层。

设计双⾯板只需要使⽤默认选项Mechanical Layer 1。

机械层是定义整个PCB板的外观的,它⼀般⽤于设置电路板的外形尺⼨,数据标记,对齐标记,装配说明以及其它的机械信息。

设计为PCB 机械外形,默认LAYER1为外形层。

其它LAYER2/3/4等可作为机械尺⼨标注或者特殊⽤途,如某些板⼦需要制作导电碳油时可以使⽤LAYER2/3/4等,但是必须在同层标识清楚该层的⽤途。

IST测试相关技术说明

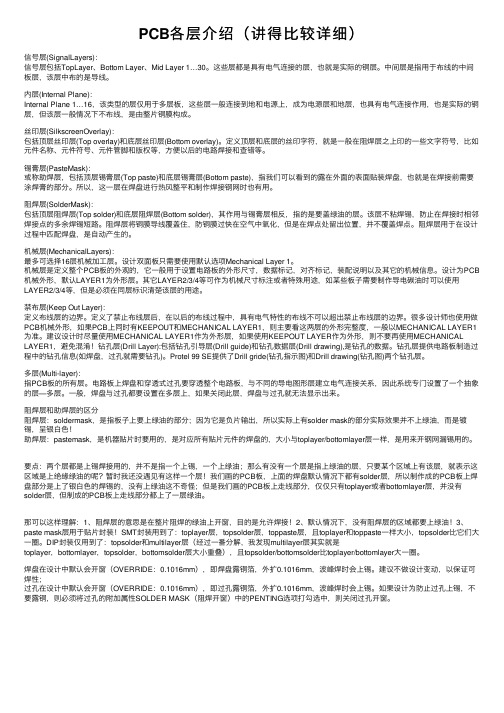

导通孔互联内应力测试(IST)在未来电路板线路互连质量评估的各种测试方法中已愈显重要,现在的测试或评价方式存在问题有:1测试速度慢;2再现性/重复性差;3很难做特性评估及无法仿真reflow制程中的组装环境;4测试结果很难分析及解释。

而最新的IST技术能够有效/快速的检测多层板层间贯穿孔(PTH)完整性及辨认接线柱与线路分离程度。

IST在基材之间产生均匀应力,分布于互联机路上,一直反复施加于PTH孔及内层结合处直到产生损坏为止。

另外IPC协会已经认证IST为评估PTH孔优先测试方法,且IST技术被发表于IPC-650测试手册内(IPC-TM-650 2.6.26)。

IST特色如下:1.使用电子式加热法可在3min内达到指定的测试温度到260℃;2.实时监控孔壁或内层链接断裂失效因子,在测试后可快速从试片上定位出正确的孔破位置并进行切片分析原因;3.IST工作周期约为250CYCLE/日,已建立IST数据库可对比产品的信赖度及等级;互联接应力参考测试标准为IPC-TM-650 2.6.26,规范名称为直流电诱导热循环测试(DC Current Induced Thermal Cycling Test)。

IST测试主要是量测孔与内层线路间的电阻值变化,因为孔铜是面对热循环的主要标的物。

热循环的产生主要是因为测试了高的电流,这些电流通过了特定的孔与内链接的线路而产生了热。

一般的设计会连贯约200个孔,同时连接的结构会通过两层的相邻线路,这样的线路设计被称为电源线路(Power Circuit)。

启动线路电源约3min加热至较高温度,之后停止以强对流方式冷却,2-3min完成冷却。

另外一个群组的连接点有两个不同的独立回路设计连接约500个分布在各个不同两层线路间的孔,这些在进行测试的线路,被称为感应线路(Sense Circuits)。

IST测试过程中常见分层问题分析办法及参考:测试完成后,将测试COUPON取下,放置在分层爆板量测装置中(Delamination Testing),仪器会计算两层间的电容值,若容值超过初始容值4%,则判断有分层现场。

浅析PCB两种重要可靠性测试方法

浅析PCB两种重要可靠性测试方法黄世清;张利华【摘要】PCB reliability testing is the most frequent subject the manufacturers and costumers devoted into. Intercenect stress test(IST)and thermal cycle test(TCT)are two of the most polular and effective test methods for evaluating the reliability of PCB in long term application within shot testing time. This paper introduce the test method and standard of IST and TCT, and presentate how to analysis test failures by introducing some study cases the auther have devoted into, and also recommend some improve dicection for IST and TCT failures.%电路板可靠性评估是每个制造厂家、客户研究得最多的课题,互联应力测试及冷热循环测试是现有的在短时间内评估电路板的长期可靠性的有效测试方法。

文章对互联应力测试及冷热循环测试方法及标准进行了详细介绍,并通过简单的实际测试研究案例来介绍如何分析失效并找出失效原因,并提出一些失效原因的改善方向。

【期刊名称】《印制电路信息》【年(卷),期】2014(000)004【总页数】7页(P88-94)【关键词】可靠性;互联应力测试;冷热循环测试【作者】黄世清;张利华【作者单位】深南电路有限公司,广东深圳 518053;深南电路有限公司,广东深圳 518053【正文语种】中文【中图分类】TN411 前言随着电子行业的不断发展,PCB行业对产品的长期可靠性要求越来越重视。

PCB电镀制程详细讲解

PCB电镀制程详细讲解PCB(Printed Circuit Board)电路板是现代电子产品中不可或缺的一部分,而电镀制程是制造高质量PCB的重要步骤之一。

本文将详细讲解PCB电镀制程的流程和技术。

1. 什么是PCB电镀制程PCB电镀制程是将一层金属(通常是铜)沉积在PCB的表面进行加固和保护的过程。

这种金属沉积的过程被称为电镀,通过电解反应控制金属离子的还原,使金属沉积在PCB的导线和孔内,增强导电性能和耐腐蚀性。

2. PCB电镀制程的流程2.1 表面处理在进行电镀之前,PCB的表面需要进行处理以确保金属沉积的质量和附着力。

常见的表面处理方法包括清洗、去脂、蚀刻和活化等步骤。

2.1.1 清洗清洗是去除表面污垢的过程,通常使用溶剂或清洗剂进行。

清洗的目的是去除表面的油污、灰尘和其他杂质,以确保金属沉积的质量。

2.1.2 去脂去脂是去除表面油脂的过程,常用的去脂方法包括化学去脂和物理去脂。

化学去脂使用化学剂将油脂分解,而物理去脂则使用高温或喷射方法将油脂从表面去除。

2.1.3 蚀刻蚀刻是用来去除PCB表面不需要的金属部分的过程,常见的蚀刻方法包括湿蚀刻和干蚀刻。

湿蚀刻使用化学液体(如氯化铁)将金属蚀刻去除,而干蚀刻使用气体(如氟化氢)进行。

2.1.4 活化活化是为了增强金属沉积的附着力而进行的表面处理步骤。

常见的活化方法包括化学活化和物理活化,其中化学活化使用活化液体进行,物理活化则通过物理处理(如高温、冲击等)来实现。

2.2 电镀完成表面处理后,就可以进行电镀了。

电镀通常使用铜或其他金属进行,流程如下:1.基底金属化:首先,在表面处理后,PCB上涂覆一层导电层,通常使用导电感应剂来实现。

2.挡板镀铜:将PCB放入电镀槽中,通过电解反应将铜离子还原到PCB表面的孔内和导线上,形成一层薄的铜镀层。

3.粗镀铜:在挡板镀铜之后,继续进行粗镀铜的步骤。

这一步用于增加铜层的厚度,在PCB的导线和孔内形成均匀的金属沉积。

浅谈电路板维修孔壁镀层空洞的成因及对策

浅谈电路板维修孔壁镀层空洞的成因及对策1、电路板PTH造成的孔壁镀层空洞PTH造成的孔壁镀层空洞主要是点状的或环状的空洞,具体产生的原因如下:浅谈电路板孔壁镀层空洞的成因及对策- 飛隆侠客- 飛隆侠客欢迎您的到来!其筋骨苦其心智诚(1)电路板沉铜缸铜含量、氢氧化钠与甲醛的浓度铜缸的溶液浓度是首先要考虑的。

一般来说,铜含量、氢氧化钠与甲醛的浓度是成比例的,当其中的任何一种含量低于标准数值的10%时都会破坏化学反应的平衡,造成化学铜沉积不良,出现点状的空洞。

所以优先考虑调整铜缸的各药水参数。

(2)电路板槽液的温度槽液的温度对溶液的活性也存在着重要的影响。

在各溶液中一般都会有温度的要求,其中有些是要严格控制的。

所以对槽液的温度也要随时关注。

(3)电路板活化液的控制二价锡离子偏低会造成胶体钯的分解,影响钯的吸附,但只要对活化液定时的进行添加补充,不会造成大的问题。

活化液控制的重点是不能用空气搅拌,空气中的氧会氧化二价锡离子,同时也不能有水进入,会造成SnCl2的水解。

(4)电路板清洗的温度清洗的温度常常被人忽视,清洗的最佳温度是在20℃以上,若低于15℃就会影响清洗的效果。

在冬季的时候,水温会变的很低,尤其是在北方。

由于水洗的温度低,板子在清洗后的温度也会变的很低,在进入铜缸后板子的温度不能立刻升上来,会因为错过了铜沉积的黄金时间而影响沉积的效果。

所以在环境温度较低的地方,也要注意清洗水的温度。

(5)电路板整孔剂的使用温度、浓度与时间药液的温度有着较严格的要求,过高的温度会造成整孔剂的分解,使整孔剂的浓度变低,影响整孔的效果,其明显的特征是在孔内的玻璃纤维布处出现点状空洞。

只有药液的温度、浓度与时间妥善的配合,才能得到良好的整孔效果,同时又能节约成本。

药液中不断累积的铜离子浓度,也必须严格控制。

(6)电路板还原剂的使用温度、浓度与时间还原的作用是去除去钻污后残留的锰酸钾和高锰酸钾,药液相关参数的失控都会影响其作用,其明显的特征是在孔内的树脂处出现点状空洞。

简述印制电路板的组成

简述印制电路板的组成印制电路板(Printed Circuit Board,简称PCB)是电子产品中必不可少的核心组成部分。

它是一种由导电材料制成的板状基板,上面布有一层或多层的电路线路。

PCB的组成可以分为以下几个方面。

1. 基板材料:PCB的基板通常采用绝缘性能较好的材料制成,如玻璃纤维增强塑料(FR-4)和多层薄板材料。

这些材料具有良好的绝缘性能和机械强度,能够承受电子元器件的安装和使用过程中的各种力学应力。

2. 导电层:PCB的导电层是由金属箔制成,通常使用铜箔。

铜箔具有良好的导电性能和可加工性,可以通过化学腐蚀、电镀等工艺将导电层形成所需的线路图案。

导电层的厚度通常为几十微米至几百微米,根据电路的需求可以选择不同厚度的铜箔。

3. 线路图案:线路图案是PCB上最核心的部分,它决定了电子元器件之间的连接方式。

线路图案的制作通常采用光刻或者电镀的方法。

在制作线路图案之前,需要将导电层表面涂覆一层光刻胶,然后通过光刻技术将需要形成的线路图案暴露出来。

接下来,通过化学腐蚀或者电镀的方法将导电层除去或者增加,最终形成所需的线路图案。

4. 焊盘和过孔:PCB上的焊盘和过孔是用于连接电子元器件的重要部分。

焊盘是导电层上的圆形金属区域,用于安装电子元器件的引脚。

过孔是连接不同层次的导电层的通孔,通过过孔可以实现不同层次之间的电气连接。

焊盘和过孔的制作通常是在线路图案制作完成后进行的,通过电镀的方法在导电层上形成。

5. 阻焊层和喷锡层:阻焊层和喷锡层是用于保护PCB线路和焊点的重要层。

阻焊层可以减少线路之间的串扰和短路,同时还可以防止PCB表面的金属部分氧化。

喷锡层是一层薄薄的锡层,用于保护焊盘和过孔,防止其氧化和腐蚀。

6. 标识层:标识层是用于标记PCB上元器件的位置、数值和方向的层。

标识层通常采用丝印或者喷墨的方式进行印刷。

7. 其他组成部分:除了以上几个主要组成部分外,PCB还可以包括其他辅助组件,如电容、电感、电阻等。

PCB水平电镀技术介绍

化学镀铜对人的危害关于化学镀铜对人体的危害有什么,相信在PCB制造业的朋友都相当之关心,为此,我们PCB资源网特别准备了这些篇文章,献给为PCB业贡献血汗的朋友,希望各位朋友保护好自己,将化学镀铜的危害减到最少化学镀铜,在几乎在每一间PCB制造企业都存在,在这一道工艺上,相传有很多危害,但是,并不是每一个工人,都完全了解在PCB制造当中,化学镀铜对人体的危害究竟到什么地步,在这里,为了我们广大同行的健康,我们PCB资源网(),特别准备了这一篇文章,比这方面的朋友了解一下,化学镀铜对人体的危害,究竟到什么程度了。

一、化学镀铜的了解化学镀铜(Eletcroless Plating Copper)通常也叫沉铜或孔化(PTH)是一种自身催化性氧化还原反应。

首先用活化剂处理,使绝缘基材表面吸附上一层活性的粒子通常用的是金属钯粒子(钯是一种十分昂贵的金属,价格高且一直在上升,为降低成本现在国外有实用胶体铜工艺在运行),铜离子首先在这些活性的金属钯粒子上被还原,而这些被还原的金属铜晶核本身又成为铜离子的催化层,使铜的还原反应继续在这些新的铜晶核表面上进行。

化学镀铜在我们PCB制造业中得到了广泛的应用,目前最多的是用化学镀铜进行PCB的孔金属化。

二、化学镀铜对人的危害的表现虽然很多朋友说,长期接触化学镀铜,会有有致癌的可能性,因为化学沉铜主要主份甲醛是致癌物质来,长期的接触,当然危险系统就会多很多了。

现在的情况看来,还没有非常直接的证据说明化学镀铜会致癌,但是,相信很多朋友都看到这一种情况吧,从事化学铜工序的朋友,很多头发都是掉了非当之多的,很多朋友头发都掉禿,这是什么原因,我们也暂时没有什么说明,有这些资料的朋友,请将相关的资料通过PCB资源网()发给我们,我们会在这里公布,先谢谢了。

三、化学镀铜对人的危害无论哪一种化学物质,长期过多的接触电,都人体都带来影响,在PCB镀铜工艺工种的朋友,由于长期接触电这方面的化学原素,所以,危害就特别大了。

线路板经典知识介绍

教

程

日

月 興

外层菲林

電

子

興 将外层线路菲林上的图象转移到板面上

業 股 份

显影 将板面未爆光部位的干膜用药水除 露出需加厚的铜

去,

有 图形电镀 把露出的铜加厚,再镀上纯锡做

限 为防蚀刻用

公 褪膜/蚀刻 褪去干膜后,把未被锡盖住的铜蚀

司 刻掉

培 訓 教

褪锡

把蚀刻后的板面上的锡褪掉,就得到

所要的线路

程

日

限 (4)一旦增层中之微盲孔恰好落在核心板通孔之正中央,或孔与环

公

之地盘领域时,则该核板通孔必须先要塞满填平,才能续做「孔 上垫」等板之面积之再生。

司 • 现行双面线路板要求绿漆塞孔,以达电测时之抽紧贴牢,防止喷

培 锡过程中掉进锡渣、助焊剂腐蚀过孔、抗氧化等。

訓

教

程

日

月 興

阻焊制程能力

電

子

興

業

股

份

有 正常工作。

限 • 在接入点将数字地和模拟地分开,就是为了将数字地 公 和模拟地的共地电阻降到最小。

司

培

訓

教

程

日

月 興

数字模拟地的分割

電

子

興

業

股

份

有

限

公

司

培

訓

教

程

日

月 興

电源的分割

電

子

興

業

股

份

有

限

公

司

培

訓

教

程

日

月 興

讯号屏蔽地

電

子

興

業

股

份

有

限

电镀层及其质量

3

第一节概述

二、电接触表面覆盖金属的方法

• 电镀、镶嵌、熔焊、铆接、真空蒸发、离子溅射 和化学覆盖等,

• 其中电镀在接插件和开关件接触表面上的应用较 为广泛。

三、电镀

1. 定义:电镀就是在电场作用下溶液中的金属离子 还原的过程。对电接触处的电镀和其他部位不同, 有其特殊要求,它对电接触的可靠性有着重要的 意义。

三、银离子迁移

2. 例如: 有人做过实验,镀银导线之间相隔 0.38mm,直流电压30V,在45℃,90% 相对温度环境下只需14天,导线之间短 路了,增加导线之间距离,短路所需的 时间也就增长。

19

第四节 锡及其合金

一、锡及其合金的特点

一般用在可靠性要求较低的场合代替价格昂贵的金合 金。 – 优点:

22

四、锡须

1. 锡须的产生

– 纯锡容易产生锡须,即生长出很多细丝。

– 结果是使导体之间短路 – 这种现象是由于电镀过程产生内应力所致。

2. 避免锡须的办法

– 是加入少量的铅(<4%Pb),使之成为锡铅合金。 – 由于Sn-Pb合金的熔点低于纯锡,所以它们更容易

焊接。

– Sn-Pb合金镀层的厚度一般在2.5~5μm,其中间层 金属一般选用Ni或Cu;接触压力不小于100gm,因 为必须要破裂或除去表面的氧化剂而得到低的接触 电阻。

12

二、镀金层微孔问题

7. 微孔率的检测方法

① SEM观察:很小的微孔,较曲折的微孔难以发现, 有时陷坑易被误认为是微孔,比较费事。不常用。

② 电腐蚀法 ③ 硫在化显气微体镜下(H观2S,察S并O统2)加计速数腐目蚀;法常:用形的成方的法腐。蚀日物本

怎么样的电路板有镀金工艺

怎么样的电路板有镀金工艺

电路板的镀金工艺是一种常见的表面处理技术,它可以提高电路板的导电性、抗氧化性和焊接性能。

以下是几种常见的电路板镀金工艺:

1. 电镀金:电镀金通常是指电路板表面先镀一层镍,然后再镀上一层金。

这种工艺可以增强电路板的导电性和抗氧化性,使其适用于高频、高速和高精度的应用。

2. 软金线焊盘:软金线焊盘是指在电路板表面覆盖一层软金(通常是银和金的合金),然后在焊盘上加热,使金属熔化并形成可焊接的焊盘。

软金线焊盘可以提高焊接质量和可靠性。

3. 化学镀金:化学镀金是一种利用化学反应在电路板表面形成金属镀层的工艺。

它通常使用化学物质和外加电流来实现金属的沉积。

化学镀金可以控制金属的厚度和均匀性,适用于小尺寸和高密度的电路板。

4. 金刚石点状镀金:金刚石点状镀金是一种在电路板上点状涂覆金刚石涂层的工艺。

金刚石涂层可以增加电路板的硬度和耐磨性,提高其使用寿命和可靠性。

总之,电路板的镀金工艺可以根据具体的需求和应用选择适合的工艺方法,以提高电路板的性能和可靠性。

线路板的组成及部分主要功能

线路板的组成及部分主要功能PCB由不同的元器件和多种复杂的⼯艺技术处理等制作⽽成,其中 PCB线路板的结构有单层、双层、多层结构,不同的层次结构其制作⽅式是不同的。

本⽂将详细介绍: PCB线路板组成的元件名称及对应⽤途,和PCB线路板单层、双层、多层结构的制作及多种类型⼯作层⾯的主要功能。

第⼀、印刷电路板主要由焊盘、过孔、安装孔、导线、元器件、接插件、填充、电⽓边界等组成,各组成部分的主要功能如下:焊盘:⽤于焊接元器件引脚的⾦属孔。

过孔:⽤于连接各层之间元器件引脚的⾦属孔。

安装孔:⽤于固定印刷电路板。

导线:⽤于连接元器件引脚的电⽓⽹络铜膜。

接插件:⽤于电路板之间连接的元器件。

填充:⽤于地线⽹络的敷铜,可以有效的减⼩阻抗。

电⽓边界:⽤于确定电路板的尺⼨,所有电路板上的元器件都不能超过该边界。

第⼆、印刷电路板常见的板层结构包括单层板(Single Layer PCB)、双层板(Double Layer PCB)和多层板(Multi Layer PCB)三种,这三种板层结构的简要说明如下:(1)单层板:即只有⼀⾯敷铜⽽另⼀⾯没有敷铜的电路板。

通常元器件放置在没有敷铜的⼀⾯,敷铜的⼀⾯主要⽤于布线和焊接。

(2) 双层板:即两个⾯都敷铜的电路板,通常称⼀⾯为顶层(Top Layer),另⼀⾯为底层(Bottom Layer)。

⼀般将顶层作为放置元器件⾯,底层作为元器件焊接⾯。

(3)多层板:即包含多个⼯作层⾯的电路板,除了顶层和底层外还包含若⼲个中间层,通常中间层可作为导线层、信号层、电源层、接地层等。

层与层之间相互绝缘,层与层的连接通常通过过孔来实现。

第三、印刷电路板(凡亿PCB打样⽣产)包括许多类型的⼯作层⾯,如信号层、防护层、丝印层、内部层等,各种层⾯的作⽤简要介绍如下:(1)信号层:主要⽤来放置元器件或布线。

Protel DXP通常包含30个中间层,即Mid Layer1~Mid Layer30,中间层⽤来布置信号线,顶层和底层⽤来放置元器件或敷铜。

线路板直接电镀介绍

线路板直接电镀

DMS-E 工艺介绍

直接电镀是替代化学镀铜的环保工艺,人工成本降低近一半。

不涉及甲醛等有毒致癌化学成分,而且化学原料大幅度减少,工艺简单、高效。

t e 1 l365 720 1470

作为代替化学镀铜的直接电镀技术必须满足以下条件:(q q 380 685 509)

(1)在非导体包括环氧玻璃布、聚酰亚胺、聚四氟乙烯等孔壁基材上,通过特殊处理形成一层导电层,以实现金属电镀。

同时还必须保证镀层与基体具有良好的结合力。

(2)形成导电层所用的化学药水对环境污染小,易于进行“三废”处理,不会再造成严重污染。

(3)形成导电层的工艺流程越短越好,而且要求操作范围应较宽,便于操作与维护。

(4)能适应各种印制板的制作。

如高板厚/孔径比的印制板,盲孔印制板,特殊基材的印制板等。

目前世界上直接电镀技术的材料来分类可以归纳为三大类型:第一类是以胶体钯工艺在非导体表面产生Pd导电金属薄层的技术,第二类是以导电高分子材料为导电层的所谓MnO2接枝技术;第三类是以碳或石墨悬浮液涂布薄膜为基础的直接电镀技术。

直接电镀工艺如下:

水平直接电镀(DMSE)工艺

新设备清洗及开缸

一、缸体清洗方法:。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PWB VB 机台系统作业流程

测量体积电阻 决定电阻 计算热电阻系数

选择/应用直流电流

监视内层互连情形

要求PTH达到150℃

热应力周期测试

Elevated resistance = ([TCR x Rm x Tn] + Rm) / 1.1 TCR = Thermal coefficient of resistance Rm = Resistance of coupon at room temp (25C) Tn = Specified temperature to be achieved.

-10

后制程分离导至内层互连接点断裂

"GROSS" POST RESISTANCE DEG RADATION 160 140 120 100 80 60 POST INTER CONNECT 40 20 0 1 6 11 16 21 26 31 36 41 46 51 56 61 66 71 76 81 86 91 96 101 106 IST CYCLES PTH INTER CONNECT

为什麼要使用新的热应力测试方法?

传统冷热冲击/漂锡等试验方法已使用将近十 年之久,其结果如下说明:

无法发现内层连接点的故障 过慢 不易得到良好的再现性及可靠性的结果 不同的量测方式不易得到相同的试验数据 不易模拟出产品在制造或组装时的真正制程环境 资料不易分析 & 说明

I.S.T.与传统热应力循环特性比较

FINE LINE GROSS

GOOD

对於不同孔距的品质分析

VA RIOUS GRID S IZES W IT H FINE LINE S EP ARAT IONS

50 45 RESISTA NCE CHANGE IN M ILLIOHM S 40 35

RESISTANCE CHANGE IN MILLIOHMS 50 45 40 35 30 25 20 15 10 5

vvvvvvvvvvvvvvvvvvvvvvvvvvv vvvvvvvvvvvvvvvvvvvvvvvvvvv vvvvvvvvvvvvvvvvvvvvvvvvvvv vvvvvvvvvvvvvvvvvvvvvvvvvvv

IST V.S 内层互连接点故障(1)

IST V.S 盲孔 内层互连接点故障(2)

vvvvvvvvvvvvvvvvvvvvvvvvvvv

Gross Separations

vvvvvvvvvvvvvvvvvvvvvvvvvvvv

Difficult to detect

Easy to detect

vvvvvvvvvvvvvvvvvv

vvvvvvvvvvvvvvvvvvvvvvvvvvv

Performance Variability Between .062" and .093" PWB's

250

200 Quantity of Coupons Te sted

150

100

50

0 100 150 200 250 300 350 400 450 500 550 600 650 700 750 800 850 900 950 50 1000 1050 1100

I.S.T. 技术应用/运用范围

制程 / 产品的特性比较, 依据参考线(Base Line). 化学电镀 / 直接电镀制程的评估. 制程的故障排除. 电(线)路板供应商的资格评鉴. 电(线)路板在组装或重工时所承受的热冲击影响. 客户产品的品质保证. 产品寿命周期预览. 减少或降低来自人为的微切片误差, 费用.

同步监测

记录/分析资料

IST 测试画面说明(1)

IST测试画面说明(2)

IST测试画面说明(3)

试片结构,孔破定位测试

菊瓣设计画面 (Daisy Chained)

黑点即表示PTH孔的孔破位置

IR测试画面

ห้องสมุดไป่ตู้层互连接点故障检测

vvvvvvvvvvvvvvvvvv

Fine line Separations

150

100

50

0 100 125 150 175 200 225 250 275 300 325 350 375 400 425 450 475 500 525 550 575 600 625 650 675 700 25 50 75

IST cycles @ 150C

不同厚度时品质分布表上的变化

现今客户的要求

板 材 中/高 Tg 的 FR4, Teflon, RCC .003" 微盲孔. .100"~ .300"或以上. 盲/ 埋孔, 导热孔, 插件孔. 机械, 雷射, 感光, 电浆钻孔等. 镀后,完工逐次压合式制程. 垫内孔(Via in pad), 复线板. 导通孔直径 电路板厚度 通孔种类 通孔构造 层间/ 叠层 互连方式

一般最常用的测试要求

材 板 导通孔直径 电路板厚度 纵 横 比 导通孔种类 数 层 电镀 方式 电镀 厚度 测试 温度 … FR4… .010" - .030" " " .062" - .093" 5:1 导通孔/埋孔/盲孔 6-25 层 化学电镀/直接电镀 " " .0005" - .002" 150C

.100 "

VARIOUS GRID SIZES WITH FINE LINE SEPARATIONS .100" .075" .050"

.075 "

.050 "

30 25 20 15 10 5 0

.035 "

.035" 58 77 96 115 134 153 172 191 210 229 248 267 286 305 324 343 362 381 400 419 438 457 476 495

20 39 58 77 96 115 134 153 172 191 210 229 248 267 286 305 324 343 362 381 400 419 438 457 476 495 IST CYCLES

1

20 39

0 1

IST CY CLE S

0.062" 板厚品质分布表

Performance demonstrated on .062" / 6+ layer / FR4 / .013" - .021" vias

20 CRACK PROPAGATION 10 ANNEALING 0 1 PTH CRACK INITIATION FATIGUE POST INTERCONNECT 16 31 46 61 76 91 106 121 136 151 166 181 196 211 226 241 256 271 286 301 316 331 346 361 376 391 STRAIN RELIEF IST CYCLES

藉由导入稳定的直流电流至内层的加热端使各层能稳 ( 150C ). 定平均受热(例 150C +/- 2C 在 3 分钟之内). X,Y,Z 受热端 / 加热端将有X,Y,Z X,Y,Z轴热膨胀的情形产生直到故 障的情形被检测出来, 就此故障情形将会是内层连接点 断裂或孔壁环状破裂等情形产生. 连续性的冷热循环直到达到微电阻变化量测试上限.

THERMAL PROFILES

160 150 140 130 120 110 100 90 80 70 60 50 40 30 20 10 0 -10 -20 -30 -40 -50 -60 -70

0 7 9 1 4 2 1 2 8

DEG REES CELSIUS

TIME IN MINUTES

I.S.T. 受热端及加热端测试方法

I.S.T. 技术可适用及推展的范围

将 IST建立成为品质验收标准 IST建立成为品质验收标准 及作为印刷电路板制程除错/可靠性工具 及作为印刷电路板制程除错/

材料供应商 供 应 商 汽车业 航空业 药水供应商 IST 军事方面 商业 电子业 通讯业 消 费 者

设备

设备制造商

实绩表 I.S.T. Technology/Services

不完全分离 完全的分离

内层电阻值衰减分布图

RESISTANCE DEGRADATION OF T HE PT H INTERCONNECT 50 PTH INTERCONNECT FAI LI NG 40 ACCELERATION RESISTANCE DEGRADATION IN IN MILLIOHMS 30

孔壁品质及内层线路品质测试 依据I.P.C 2.6.26

/html/2-6_2-6-26.pdf

I.S.T. 互连应力量测技术说明

IST 测试机台与试片

I.S.T. 系统发展过程

理论研发完成(Nortel, Dec) 测试机的诞生 专利的申请 测试机正市引进市场 IST取得专利权 IST系统北美客户推展 EPA/IPC 认同测试方法(2.6.26) 系统推展到欧洲 系统推展到亚洲 86~91 93 94 95 96 96~97 97 98 99

IST cycles @ 150C

0.093" 板厚品质分布表

Performance demonstrated on .093" / 6+ layer / FR4 / .013" - .021" vias

250

200 Quantity of Coupons Te sted

Sample size = 1500+ coupons

RESIS TANCE DEGRADATION IN MILLIOHMS

内层互连接点品质分界图

QUANTIFYING DEGREES OF POST SEPARATION (.050" GRID)