design_entry_cis初学(cadence)

(完整版)cadence PCB 画图(傻瓜教程快速入门)

cadence 画 PCB 板傻瓜教程(转帖)复制于某网站,谢谢。

拿出来分享吧,希望对初学者能有帮助,可以很快了解 Cadence 的使用,谢谢共享者。

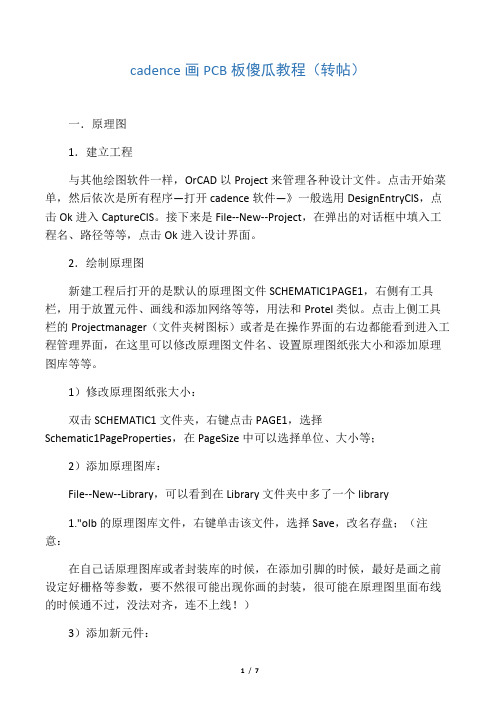

一.原理图1.建立工程与其他绘图软件一样,OrCAD 以Project 来管理各种设计文件。

点击开始菜单,然后依次是所有程序—打开 cadence 软件—》一般选用 Design Entry CIS,点击Ok 进入Capture CIS。

接下来是 File--New--Project,在弹出的对话框中填入工程名、路径等等,点击 Ok 进入设计界面。

2.绘制原理图新建工程后打开的是默认的原理图文件 SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和 Protel 类似。

点击上侧工具栏的Project manager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1)修改原理图纸张大小:双击 SCHEMATIC1 文件夹,右键点击 PAGE1,选择Schematic1 Page Properties,在 Page Size 中可以选择单位、大小等; 2)添加原理图库:File--New--Library,可以看到在 Library 文件夹中多了一个 library1.olb 的原理图库文件,右键单击该文件,选择 Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!)3)添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的 olb 库文件,选 New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片 Datasheet 中的引脚描述表格中直接拷贝、粘贴即可(pdf 格式的 Datasheet 按住Alt 键可以按列选择),可以批量添加管脚,方便快捷。

(完整版)CadenceDesignentryHDL教程

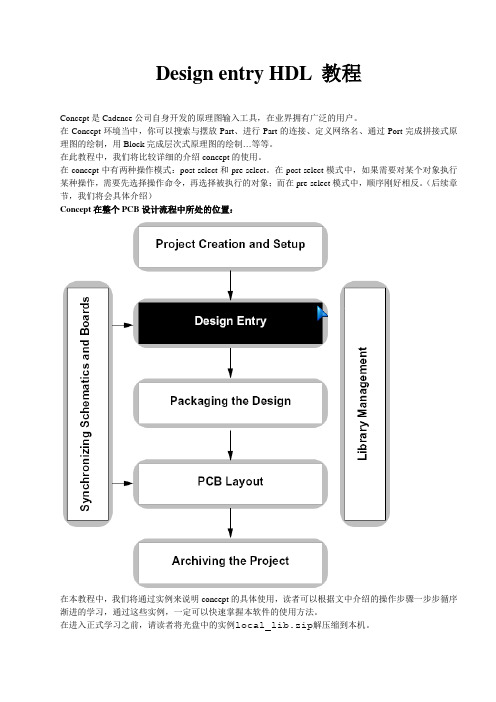

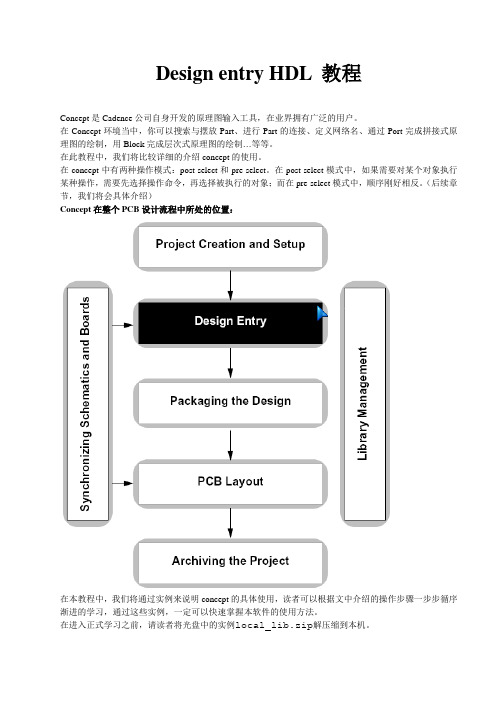

Design entry HDL 教程Concept是Cadence公司自身开发的原理图输入工具,在业界拥有广泛的用户。

在Concept环境当中,你可以搜索与摆放Part、进行Part的连接、定义网络名、通过Port完成拼接式原理图的绘制,用Block完成层次式原理图的绘制…等等。

在此教程中,我们将比较详细的介绍concept的使用。

在concept中有两种操作模式:post-select和pre-select。

在post-select模式中,如果需要对某个对象执行某种操作,需要先选择操作命令,再选择被执行的对象;而在pre-select模式中,顺序刚好相反。

(后续章节,我们将会具体介绍)Concept在整个PCB设计流程中所处的位置:在本教程中,我们将通过实例来说明concept的具体使用,读者可以根据文中介绍的操作步骤一步步循序渐进的学习,通过这些实例,一定可以快速掌握本软件的使用方法。

在进入正式学习之前,请读者将光盘中的实例local_lib.zip解压缩到本机。

本教程包含三大章节:第一章:创建一个项目在本章节中,将具体介绍项目的概念,库,cds_lib,project file以及如何创建项目。

第二章:原理图的绘制:在本章中将具体介绍多页原理图的绘制,内容涉及如何添加part,绘制连接线,绘制bus,检查整个设计等等。

第三章:原理图绘制的高级应用:在本章中将具体介绍层次式原理图的绘制,原理图网络表的产生,使用global find的功能来寻找整个设计中的某个元件以及对元件的属性进行编辑等等。

第一章:创建项目内容概要:●第一节概念1、什么是库2、什么是cds.lib file3、什么是project file●第二节创建一个项目(project)●第三节用project setup 来增加库第一节概念在cadence中,一个project包含如下的对象:1、涉及到的库;2、本地库(design libraries)3、Cds.lib 文件4、Project file(.cpm)接下来,将详细介绍什么是库?从设计原理图、PCB Layout直到进行真正的制造,不同的阶段,需要用到的元件的表现形式是不一样的。

cadence入门教程_修改版

Introduction to Cadence Customer IC Design Environment熊三星徐太龙编写安徽大学电子信息工程学院微电子学系目录1. Linux 常用命令 (3)2. 软件的启动 (5)3. 建立工程 (7)4. 画原理图 (9)5. 原理图仿真 (17)6. 生成symbol (25)7. 版图 (30)8. DRC检查 (50)9. LVS检查 (54)10. PEX参数提取 (58)11. 后仿真 (61)1.Linux 常用命令目前,电子设计自动化(Electronic Design Automation, EDA)工具多数都基于Linux操作系统,因此在学习使用EDA之前,有必要掌握一些Linux操作系统的基本命令。

1.mkdirmkdir命令让用户在有写权限的文件夹(目录)下建立一个或多个文件夹(目录)。

其基本格式如下:mkdir dirname1 dirname2 ... (dirname 为文件夹或者目录的名字)2.cdcd命令让用户进入一个有权限的文件夹(目录)。

其基本格式如下:cd Filename (Filename为文件夹或者目录的名字)cd .. (.. 表示上一层文件夹或者目录)3.lsls命令用以显示一个文件夹(目录)中包含的文件夹(目录)或者文件。

其基本格式如下:ls Filename (Filename为文件夹或者目录的名字)如果ls命令后没有跟文件夹(目录)名字,显示当前文件夹(目录)的内容。

ls 命令可以带一些参数,给予用户更多相关的信息:-a : 在UNIX/Linux中若一个文件夹(目录)或文件名字的第一个字元为"." ,该文件为隐藏文件,使用ls 将不会显示出这个文件夹(目录)或文件的名字。

如cshell 的初始化文件.cshrc,如果我们要察看这类文件,则必须加上参数-a。

格式如下:ls –a Filename-l : 这个参数代表使用ls 的长(long)格式,可以显示更多的信息,如文件存取权,文件拥有者(owner),文件大小,文件更新日期,或者文件链接到的文件、文件夹。

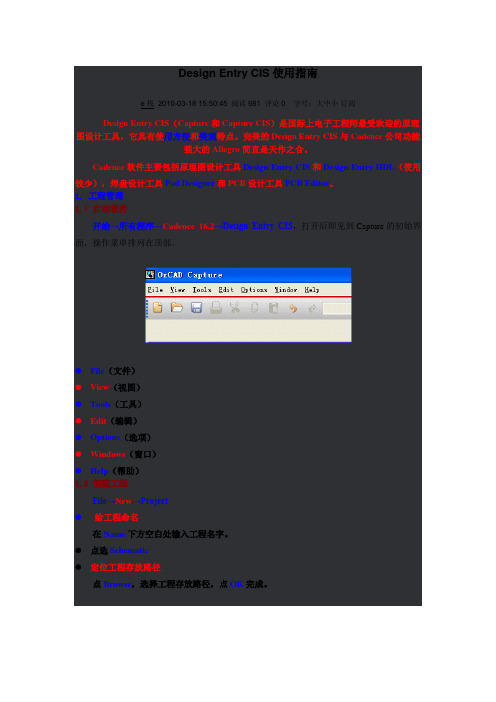

Design Entry CIS使用指南

Design Entry CIS使用指南e栈2010-03-18 15:50:45 阅读981 评论0 字号:大中小订阅Design Entry CIS(Capture和Capture CIS)是国际上电子工程师最受欢迎的原理图设计工具,它具有使用方便和美观特点。

完美的Design Entry CIS与Cadence公司功能强大的Allegro简直是天作之合。

Cadence软件主要包括原理图设计工具Design Entry CIS和Design Entry HDL(使用较少),焊盘设计工具Pad Designer和PCB设计工具PCB Editor。

1. 工程管理1.1 启动软件开始→所有程序→Cadence 16.2→Design Entry CIS,打开后即见到Capture的初始界面,操作菜单排列在顶部。

● File(文件)● View(视图)● Tools(工具)● Edit(编辑)● Options(选项)● Windows(窗口)● Help(帮助)1.2 创建工程File→New→Project● 给工程命名在Name下方空白处输入工程名字。

● 点选Schematic● 定位工程存放路径点Browse,选择工程存放路径,点OK完成。

1.3 打开工程File→Open→Project,选择工程存放路径和工程名,点打开。

1.4 工程子项打开工程后,工程包含以下选项,Design Resources(设计资源),Output(输出)和Referenced Projects(参考工程)。

1.4.1 设计资源✍ dsn(设计)● SCHEMATIC● Design Cache✍ Library(原理图库)1.4.2 输出● Drc(规则检查输出,只有规则检查后才会有)● Bom(材料表单,只有生成材料表单后才有)● NetList(网络表,只有生成网络表后才有)1.4.3 参考工程2. 原理图参数设置2.1图纸版面设置Options→Design template→Page Size2.1.1 页面单位● Inches(英制)● Millimeters(公制)2.1.2 页面尺寸● Inches版面A/B/C/D/E/Custom● Millimeters版面A4/A3/A2/A1/A0/Custom2.2 栅格设置Options→Design template→Grid Reference2.2.1 水平栅格设置水平方向栅格设置如果设置为millimeter的A4,则Width中输入2,否则打印出来的原理图四周的字母很大。

cadence PCB 画图(傻瓜教程快速入门)

cadence画PCB板傻瓜教程(转帖)一.原理图1.建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序—打开cadence软件—》一般选用DesignEntryCIS,点击Ok进入CaptureCIS。

接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2.绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。

点击上侧工具栏的Projectmanager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1)修改原理图纸张大小:双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1PageProperties,在PageSize中可以选择单位、大小等;2)添加原理图库:File--New--Library,可以看到在Library文件夹中多了一个library1."olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!)3)添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选NewPart,或是NewPartFromSpreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

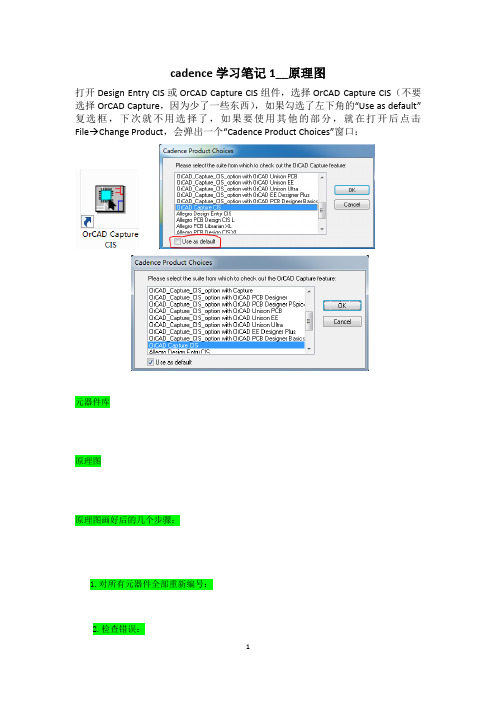

Cadence学习笔记1__原理图

新建元件时选择Heterogeneous,A部分和上面的一样画法,但是按键盘上的ctrl+N切换到B部分时,B部分是空白的,需要再画一次。

不管是Homogeneous还是Heterogeneous,点击工具栏ViewPakage,可以将A和B同时显示出来,如下图:

保存后,一个元件就画好了,画原理图时直接调用即可。

如果是由两部分组成的分裂元件,要在新建元件时在Parts per Pkg写2,这里分为Homogeneous和Heterogeneous两种。Homogeneous是只要画出A部分,B部分会默认的和A部分完全一样,Heterogeneous是画好A部分后,B部分仍然是空白的,需要再画。如果一个芯片包含了2个功能完全相同的部分,像下图中NE5532中的两个运放,就需要用到Homogeneous了,这里先选Homogeneous,点击ok。

元器件

FileNewLibrary新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是NewPart From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCBFootprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

点击左侧工具栏make图标 ,所有的横线和竖线都变成粉红色的,这就生成了一个表格,鼠标右击选择Tag Pin Name,在引脚名这一列点一下,会在这一列最上面出现“Name”,同样的,右击选择TagPin Number,在引脚编号这一列点一下,会在这一列最上面出现“Num”,如果放错了,比如说该放Name的地方放成了Num,可以在放Num之后再点一次,Num就消失了,产生的结果如上图右。

cadence 原理图学习笔记

Design Entry CIS :板基设计的原理图设计Design Entry HDL Rules Checker 芯片设计工具Design Entry HDL 芯片设计工具PCB Editor:PCB布局布线的软件PCB Router:自动布线的工具PCB SI:线路板的完整性分析SigXplorer:线路板的完整性分析平时画原理图工具:OrCAD Capture CIS原理图模板设置:创建原理图元件库新建的原理库存储到指定的位置新建元件库元件新建元件的属性,包括名称,索引号,封装,多元件共体,等信息元件库原理图编辑界面单个引脚放置:弹出引脚属性设置阵列引脚放置:单个引脚双击修改属性多个引脚选中后在spreadsheet一起修改。

放置填充多边形按住shift可以画任意角多边形双击调出多边形属性选择实体就好了放置元件方体画方框结束鼠标重复放置命令,右击End Mode 或者Esc元件属性,设置引脚管脚显示等。

元件封装属性修改,原理图与pcb封装的映射就在这里修改。

多元件共体浏览分裂元件浏览。

不规则元件第3讲:分裂元件制作创建Homogereous双运放元件,每个单元件都一摸一样,引脚编号不同,电源脚编号可以重复。

新建元件画好第一个单元件快捷键Ctrl+n 自动生成另一部分单元件。

需要全部重新定义引脚编号。

引脚名称隐藏快捷键Ctrl+b 可以返回查看A部分元件图形。

创建Heterogeneous元件,每部分图形可以不一致。

快捷键Ctrl+n 会完全留空,全部要重新画。

分裂元件整体浏览第4讲分裂元件的自动编号的问题解决。

分裂元件的组定义,在元件库中操作,使同组元件具备同一属性。

第一步:创建元件第二步:给元件创建一个可以区分“分组”的属性完成了单个元件的新属性的创建依次创建同组的其它元件的新属性。

要求同名同参数第三步:在原理图中双击元件使同组的元件都新属性参数相同即可。

配对时不能冲突,比如双运放就只能有两个运放,同一参数有三个运放相同的话就出错了。

Allegro Design Entry CIS和Allegro PCB Editor进行约束设计的方法

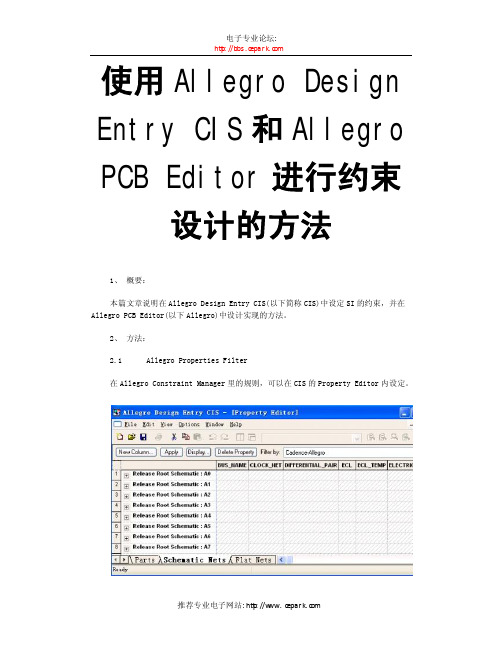

使用Allegro Design Entry CIS和Allegro PCB Editor进行约束设计的方法1、概要:本篇文章说明在Allegro Design Entry CIS(以下简称CIS)中设定SI的约束,并在Allegro PCB Editor(以下Allegro)中设计实现的方法。

2、方法:2.1 Allegro Properties Filter在Allegro Constraint Manager里的规则,可以在CIS的Property Editor内设定。

2.2 Class规则2.2.1 Net Spacing, Net Physical RulesSPACEING_CONSTRAINT_SET (15.7为NET_SPACING_TYPE),用于定义网络和其他要素之间的规则。

PHYSICAL_CONSTRAINT_SET (15.7为NET_PHYSICAL_TYPE),用于定义网络的物理的参数。

如:SPACING_CONSTRAINT_SET=10_mil_tracePHYSICAL_CONSTRAINT_SET=critical_clock_net操作步骤在CIS的设计界面选择网络。

在控制栏,选择Edit-properties。

变更Filter为Cadence_Allegro。

为SPACING_CONSTRAINT_SET和PHYSICAL_CONSTRAINT_SET添加属性值。

2.3 SI的规则设定2.3.1 Electrical Constraint Sets ECSETSElectrical Constraint Sets (ECSETS)包括预先设定的电气规则。

每个网络的规则可以直接定义。

可以通过设定Constraint,将其分配Allegro Constraint Manager的ECSETS 中。

譬如,差分信号通常带有phase tolerance、 secondary gap、 primary gap、 gather control等的参数,根据设定ECSETS规则,可以直接把它分配为这个网络的规则。

Cadence 16.5 Design Entry CIS层次化电路设计详解

1 orca 也会独2 (的对名复量式模块当前概述Allegro D orcad Captur 也会简化绘图Design E 独立的工程本文假定子电路设a )建立b )将默(见图1)的对象,不改c )d ) 对子○1在对话框名复位为待定点“确定○2 再次在对话框量式自动编号切换至对模块;(对当前图纸中无Cadenc (Cadeegro Design En apture 工具进化绘图工作sign Entry CIS 工程opj 文件和文假定大家对电路设计建立子电路工将默认的SCH ;Cadence 不改倒也无碍在PAGE1图纸对子电路进执行Tools->An 对话框的Pack 为待定;确定”执行标再次执行Too 对话框的Pack 动编号;换至对话框的对Renumber纸中无复用模块adence 16.5 D Cadence 软件gn Entry CIS 工具进行了多方;y CIS 的层次化文件和设计大家对Cadence 设计步骤电路工程、子电SCHEMATIC1ence 是用图纸倒也无碍,但图纸上设计子电路进行元件序>Annotate Packaging 设置执行标注任务Tools->Anno Packaging 设置话框的PCB Edito mber Design 复用模块,则不16.5 Design 软件子电路CIS 工具是Cad 了多方面演进层次化电路设计设计dsn dence 基子电路MATIC1夹来代将来出现 图设计子电路,元件序号标注ate (小细节置页下注任务,元Annotate (见图置页下B Editor Reuse ign ……项可酌选该项esign Entry C 电路复用实战笔Cadence SPB 演进;合理应路设计总体上分文件存在。

本的的平坦式图dsn 文件;图纸夹改名为电名来代表一份图会出现很1 子电路工程,外引接口标注(这步很关细节,需选到页面下选中Res 所有元件名即变见图2页面下选中Incr euse 页面,项可酌情考虑该项); ntry CIS 层次实战笔记之原ce SPB 16.5最新理的应验层次体上分为子电路坦式图纸设计;采用平坦式名为电路名(一份图纸的,多SCHEMAITC 路工程结构及接口点添加端步很关键)点选到要标注Reset part re 名即变成附有)Incremental ,选中Gener 考虑,该项对当层次化电路之原理最新推出的验层次化电路设子电路设计和纸设计已经掌握式设计的(如Blk_Tra ,这里MAITC1结构及端口添加端口名,要标注的图纸夹art referances 成附有”?”的待ental reference Generate Reus 项对当前图纸电路设计图篇 by 李雪推出的电路图设电路设计会图设计和主电路设经掌握,计的基开始k_Transceiver 改名主为貌似不是很爽口标注,定义好各元图纸夹或工程ances to “的待定rence update Reuse Module前图纸中的复用设计详解李雪雷)路图设计工具会让图纸条理电路设计两步若不懂可先初步本开始步骤;eiver ),PAGE1要是为了引用时很爽;好各元件封装工程,菜单才被?”选项,定状态;date ,设为对元odule ,允许生的复用模块重新工具,它纸条理更加清晰,子电路名不用时区(见图才被激活,设为将元件为对元件进行成可块编号,基于原加清晰,电路以学习; 不用管分引用1); 激活); 将元件进行增可复用,若F o l l o w M e !3 点“确定e )主电路设a )建立b )执行系统Refenen Implame ImplamePath and 确定”执行标最后,电路设计建立主电路工执行菜单Pla 会弹出fenence :输入plamenation Ty plamentation Nth and Filenem 执行标注任务存盘,关闭子电设计步骤 电路工程、主电Place->Hiera 模块设置对话输入模块在主ion Type :选择tion Name :eneme :输入子图注任务,元子电路工程主电路的Hierarchical B 对话框,各参块在主电路中的子电路输入子电路子电路在2 子电路元件所有元件名自路工程;路的dsn 文件cal Block 工各参数置如路中的元件名电路的方子电路中复用模所在的图3 子路元件标注对名即自动编号文件,正常绘制或工具栏设置如下:元件名,如”实现方式,选复用模块名,dsn 文件路径插入子电路示标注对话框动编号,成主电路 B?”;Schematic ,输入路名(注意浏电路示意图并生成该图纸的电路; 的图标子 matic View 图纸夹注意浏览时调图纸的复用模块插入子电路模块 名称(如Blk_Tra 览时调整文件类复用模块;路模块(见图lk_Transceiver 类型为见图3); eiver ); .dsn );F o l l o w M e !边界作多处名复refe Renu 图纸并选路块当前号动打电路3 3.1 件重对话框中框;画完结束;c )调整d )子引用(e )对主○1在对话框名复位为待定点“确定○2再次执在对话框reference upd 切换至对Renumber De 图纸中的复用中Selec 路块名(对已经是主点“确定号,且(开子电电路元件逻辑生成主电路生复、缺失话框中画完后系统调整边界把子电路(如图4对主电路进行执行Tools->An 对话框的Pack 为待定; 确定”执行标再次执行Tools 对话框的Pack update ,设为换至对话框的ber Design for U 的复用模块Select Module 对于Genera 经是主电路确定”执行对各个此时,在其子电路件有不的编号辑生电路生成成时无需缺失等错误完成设置后,系统即自动在界框形状及框中路符像元件一样);路进行元件序号>Annotate Packaging 设置执行标注任务Tools->Annota Packaging 设置设为对元件话框的PCB Ed n for Using Reu 模块重新编号odule to Mark enerate Reuse 电路啦,呵呵执行标注任务复用模块重新编如果在主电路中路查看,就会发同的编号) 成及调用 网络表特殊操作,等错误;系统边添及各的在主电图4 层次化件序号标注ate (需中置页下注任务,元nnotate (见图置页对元件进行量CB Editor Reu g Reused modu 编号,Action Mark for 中Reuse Module ); 注任务,元编号;电路中双击子电现,不 ,由于的鼠标光标框上添加子电路端口的位布在主电路中用层次化设计主标注(这步很关先选中图纸页面下选中Res 所有元件名即变见图5)面下选中Incre 行增量式自动编r Reuse 面 module ,on 选为Uncon 窗中自动dule 项可所有元件名 击子电路块不同 在标注时确变为虚十字状子电路的外引位置布局,使其中使用,参与主计主电路原理步很关键) 纸夹) Reset part re 名即变成附有 Incremental 自动编号;页面,选中请求对当前Unconditional 动出现的子电可不选,因为件名即自动编路块,系统自的引用处的子 已经确定了层次十字状态,需要外引端口及更主电路的绘路图art referances 成附有”?”的待ental ; 当前onal ,子电动编统 了层次需要接及显示美观;的绘制示例 ances to “的待定 图5 主电关系,所网接着在主电路中要素(见图,而且可拷贝?”选项,定状态; 主电路标注以在网络表中不电路中画出见图3);插入、,设为将元件标注中不会模块插入操粘贴,将元件出现元F o l l o w M e !执行Tools->Create Netlist…,系统即生成网表;应注意的是此前对子电路中元件封装属性等描述将被主电路引用时继承;3.2 网表调用在PCB Editor中执行import logic即可导入逻辑网表及元件封装(基本的PCB设置及生成操作此处不表),跟平坦时设计时相同;--------------------------------------------- The End,敬请关注PCB篇-----------------------------------!eMwolloF。

DesignEntryCIS简单设置

DesignEntryCIS简单设置Design Entry CIS(Capture和Capture CIS)是国际上电子工程师最受欢迎的原理图设计工具,它具有使用方便和美观特点。

完美的Design Entry CIS与Cadence公司功能强大的Allegro简直是天作之合。

Cadence软件主要包括原理图设计工具Design Entry CIS和Design Entry HDL(使用较少),焊盘设计工具Pad Designer和PCB设计工具PCB Editor。

1. 工程管理1.1 启动软件开始→所有程序→Cadence16.2→Design Entry CIS,打开后即见到Capture的初始界面,操作菜单排列在顶部。

l File(文件)l View(视图)l Tools(工具)l Edit(编辑)l Options(选项)l Windows(窗口)l Help(帮助)1.2 创建工程File→New→Projectl 给工程命名在Name下方空白处输入工程名字。

l 点选Schematicl 定位工程存放路径点Browse,选择工程存放路径,点OK完成。

1.3 打开工程File→Open→Project,选择工程存放路径和工程名,点打开。

1.4 工程子项打开工程后,工程包含以下选项,Design Resources(设计资源),Output(输出)和Referenced Projects(参考工程)。

1.4.1 设计资源dsn(设计)l SCHEMATICl Design CacheLibrary(原理图库)1.4.2 输出l Drc(规则检查输出,只有规则检查后才会有)l Bom(材料表单,只有生成材料表单后才有)l NetList(网络表,只有生成网络表后才有)1.4.3 参考工程2. 原理图参数设置2.1图纸版面设置Options→Design template→Page Size2.1.1 页面单位l Inches(英制)l Millimeters(公制)2.1.2 页面尺寸l Inches版面A/B/C/D/E/Customl Millimeters版面A4/A3/A2/A1/A0/Custom2.2 栅格设置Options→Design template→Grid Reference2.2.1 水平栅格设置水平方向栅格设置如果设置为millimeter的A4,则Width中输入2,否则打印出来的原理图四周的字母很大。

Cadence学习-基础篇-CIS

New PCEBG

EE-PD2-WH Anndy 2015/10/22

概述

• 一個設計項目在經過需求分析,確定產品功能和規格,并確定選用物料后,就要進入 硬件設計階段的原理圖和PCB 設計。原理圖設計是確定所有器件的電氣連接性能并保證 所有電氣連接正確。LAYOUT設計是將原理圖設計的電氣連接性能轉化成PCB 板上的物 理實現。 原理圖設計過程包含:

•

建立原理圖的器件封裝→進行原理圖設計(放置器件和連線)→輸入器件的特征參數 →自動生成位號→ DRC 檢查→導出網絡特性(用於LAYOUT) →導出BOM 清單。

• 因為時間限制,本文檔只介紹基本使用功能。

創建DSN 文件

• 新建或者打開一個Design 文件, FILE-NEW/OPEN。

添加庫文件 并新建一個原理圖封裝

其它常用功能介紹

• 標註

紅色區域為不具備電氣性能的 編輯功能選項,於對原理圖某 一區域進行標註,起強調或提 示作用。

•

查找

生成位號

Annotate : 生成位號。 Back Annotate: 將PCB 的位號回退導入到 原理圖中。

DRC 檢查 •

可以忽略Warn, 但是對於Error, 一定要修正原理圖,才能進入下一步。

•

器件原理圖封裝繪製 繪製可視的外形; 添加PIN; 編輯位號和器件名; 根據需要可能需要增加說明性的文字; 用到的選鍵如圖:

繪製后的封裝如圖: • 保存設計文件

Hale Waihona Puke 理圖繪製• 頁編輯 一般情況下,我們的產品都有參考原型,因此設計不需完全從零開始,只需對參 考原理圖進行刪減、增補和修改。 選定prototype,右擊添加 新頁、或刪除該頁、或改名;

Cadence Design entry HDL 教程

Design entry HDL 教程Concept是Cadence公司自身开发的原理图输入工具,在业界拥有广泛的用户。

在Concept环境当中,你可以搜索与摆放Part、进行Part的连接、定义网络名、通过Port完成拼接式原理图的绘制,用Block完成层次式原理图的绘制…等等。

在此教程中,我们将比较详细的介绍concept的使用。

在concept中有两种操作模式:post-select和pre-select。

在post-select模式中,如果需要对某个对象执行某种操作,需要先选择操作命令,再选择被执行的对象;而在pre-select模式中,顺序刚好相反。

(后续章节,我们将会具体介绍)Concept在整个PCB设计流程中所处的位置:在本教程中,我们将通过实例来说明concept的具体使用,读者可以根据文中介绍的操作步骤一步步循序渐进的学习,通过这些实例,一定可以快速掌握本软件的使用方法。

在进入正式学习之前,请读者将光盘中的实例local_lib.zip解压缩到本机。

本教程包含三大章节:第一章:创建一个项目在本章节中,将具体介绍项目的概念,库,cds_lib,project file以及如何创建项目。

第二章:原理图的绘制:在本章中将具体介绍多页原理图的绘制,内容涉及如何添加part,绘制连接线,绘制bus,检查整个设计等等。

第三章:原理图绘制的高级应用:在本章中将具体介绍层次式原理图的绘制,原理图网络表的产生,使用global find的功能来寻找整个设计中的某个元件以及对元件的属性进行编辑等等。

第一章:创建项目内容概要:●第一节概念1、什么是库2、什么是cds.lib file3、什么是project file●第二节创建一个项目(project)●第三节用project setup 来增加库第一节概念在cadence中,一个project包含如下的对象:1、涉及到的库;2、本地库(design libraries)3、Cds.lib 文件4、Project file(.cpm)接下来,将详细介绍什么是库?从设计原理图、PCB Layout直到进行真正的制造,不同的阶段,需要用到的元件的表现形式是不一样的。

Cadence新手简明教程

的孤岛。如果有没删除的孤岛或者没有将 shape更新到smooth,在光绘时就会报错。 3.如果删除过孤岛,在修线后相同区域又出 现孤岛,删除时会报cannot break shape to fragments。

74

在placement edit模式(右键 edit mode>placement edit)下圈中想要对齐的几个器 件,然后右键选择align component 即可对齐, 同时在右侧option选项卡中可以设置等间距 排列。

75

76

77

78

高亮 反高亮 显示飞线

隐藏飞线

79

1.按快捷键F3打开走线模式。 2.按下F3以后点击一个net,同名的net都会

8

9

10

11

需要填这两项

12

里面不需要 snap to grid

边框和引脚必须 snap to grid, 保证电气属性

13

14

15

如果需要更改原理图页大小,可以在工程文 件目录中选择相应的原理图页,右键选择 schematic page property

16

17

18

按p调出右侧的 place part窗口 从中选取需要的 元件,双击或 enter或点击面板 上的放置按钮摆 放该元件,可放 任意多个,放完 按ESC退出。

参数修改完成之后file->update to design可以 在symbol里更改属性。

注意这种方法没有修改焊盘库里的焊盘属性。 如果在pad designer中修改完参数选择save

to file则可以更改焊盘库里的属性。 如果是先更改了焊盘,想要更新到symbol中,

Cadence16.5DesignEntryCIS层次化电路设计详解

Cadence16.5DesignEntryCIS层次化电路设计详解1 orca 也会独2 (的对名复量式模块当前概述Allegro D orcad Captur 也会简化绘图Design E 独⽴的⼯程本⽂假定⼦电路设a )建⽴b )将默(见图1)的对象,不改c )d )对⼦○1在对话框名复位为待定点“确定○2 再次在对话框量式⾃动编号切换⾄对模块;(对当前图纸中⽆Cadenc (Cadeegro Design En apture ⼯具进化绘图⼯作sign Entry CIS ⼯程opj ⽂件和⽂假定⼤家对电路设计建⽴⼦电路⼯将默认的SCH ;Cadence 不改倒也⽆碍在PAGE1图纸对⼦电路进执⾏Tools->An 对话框的Pack 为待定;确定”执⾏标再次执⾏Too 对话框的Pack 动编号;换⾄对话框的对Renumber纸中⽆复⽤模块adence 16.5 D Cadence 软件gn Entry CIS ⼯具进⾏了多⽅;y CIS 的层次化⽂件和设计⼤家对Cadence 设计步骤电路⼯程、⼦电SCHEMATIC1ence 是⽤图纸倒也⽆碍,但图纸上设计⼦电路进⾏元件序>Annotate Packaging 设置执⾏标注任务Tools->Anno Packaging 设置话框的PCB Edito mber Design 复⽤模块,则不16.5 Design 软件⼦电路CIS ⼯具是Cad 了多⽅⾯演进层次化电路设计设计dsn dence 基⼦电路MATIC1夹来代将来出现图设计⼦电路,元件序号标注ate (⼩细节置页下注任务,元Annotate (见图置页下B Editor Reuse ign ……项可酌选该项esign Entry C 电路复⽤实战笔Cadence SPB 演进;合理应路设计总体上分⽂件存在。

本的的平坦式图dsn ⽂件;图纸夹改名为电名来代表⼀份图会出现很1 ⼦电路⼯程,外引接⼝标注(这步很关细节,需选到页⾯下选中Res 所有元件名即变见图2页⾯下选中Incr euse 页⾯,项可酌情考虑该项); ntry CIS 层次实战笔记之原ce SPB 16.5最新理的应验层次体上分为⼦电路坦式图纸设计;采⽤平坦式名为电路名(⼀份图纸的,多SCHEMAITC 路⼯程结构及接⼝点添加端步很关键)点选到要标注Reset part re 名即变成附有)Incremental ,选中Gener 考虑,该项对当层次化电路之原理最新推出的验层次化电路设⼦电路设计和纸设计已经掌握式设计的(如Blk_Tra ,这⾥MAITC1结构及端⼝添加端⼝名,要标注的图纸夹art referances 成附有”?”的待ental reference Generate Reus 项对当前图纸电路设计图篇 by 李雪推出的电路图设电路设计会图设计和主电路设经掌握,计的基开始k_Transceiver 改名主为貌似不是很爽⼝标注,定义好各元图纸夹或⼯程ances to “的待定rence update Reuse Module前图纸中的复⽤设计详解李雪雷)路图设计⼯具会让图纸条理电路设计两步若不懂可先初步本开始步骤;eiver ),PAGE1要是为了引⽤时很爽;好各元件封装⼯程,菜单才被?”选项,定状态;date ,设为对元odule ,允许⽣的复⽤模块重新⼯具,它纸条理更加清晰,⼦电路名不⽤时区(见图才被激活,设为将元件为对元件进⾏成可块编号,基于原加清晰,电路以学习;不⽤管分引⽤1);激活);将元件进⾏增可复⽤,若F o l l o w M e !3 点“确定e )主电路设a )建⽴b )执⾏系统Refenen Implame ImplamePath and 确定”执⾏标最后,电路设计建⽴主电路⼯执⾏菜单Pla 会弹出fenence :输⼊plamenation Ty plamentation Nth and Filenem 执⾏标注任务存盘,关闭⼦电设计步骤电路⼯程、主电Place->Hiera 模块设置对话输⼊模块在主ion Type :选择tion Name :eneme :输⼊⼦图注任务,元⼦电路⼯程主电路的Hierarchical B 对话框,各参块在主电路中的⼦电路输⼊⼦电路⼦电路在2 ⼦电路元件所有元件名⾃路⼯程;路的dsn ⽂件cal Block ⼯各参数置如路中的元件名电路的⽅⼦电路中复⽤模所在的图3 ⼦路元件标注对名即⾃动编号⽂件,正常绘制或⼯具栏设置如下:元件名,如”实现⽅式,选复⽤模块名,dsn ⽂件路径插⼊⼦电路⽰标注对话框动编号,成主电路 B?”;Schematic ,输⼊路名(注意浏电路⽰意图并⽣成该图纸的电路;的图标⼦ matic View 图纸夹注意浏览时调图纸的复⽤模块插⼊⼦电路模块名称(如Blk_Tra 览时调整⽂件类复⽤模块;路模块(见图lk_Transceiver 类型为见图3); eiver ); .dsn );F o l l o w M e !边界作多处名复refe Renu 图纸并选路块当前号动打电路3 3.1 件重对话框中框;画完结束;c )调整d )⼦引⽤(e )对主○1在对话框名复位为待定点“确定○2再次执在对话框reference upd 切换⾄对Renumber De 图纸中的复⽤中Selec 路块名(对已经是主点“确定号,且(开⼦电电路元件逻辑⽣成主电路⽣复、缺失话框中画完后系统调整边界把⼦电路(如图4对主电路进⾏执⾏Tools->An 对话框的Pack 为待定;确定”执⾏标再次执⾏Tools 对话框的Pack update ,设为换⾄对话框的ber Design for U 的复⽤模块Select Module 对于Genera 经是主电路确定”执⾏对各个此时,在其⼦电路件有不的编号辑⽣电路⽣成成时⽆需缺失等错误完成设置后,系统即⾃动在界框形状及框中路符像元件⼀样);路进⾏元件序号>Annotate Packaging 设置执⾏标注任务Tools->Annota Packaging 设置设为对元件话框的PCB Ed n for Using Reu 模块重新编号odule to Mark enerate Reuse 电路啦,呵呵执⾏标注任务复⽤模块重新编如果在主电路中路查看,就会发同的编号)成及调⽤⽹络表特殊操作,等错误;系统边添及各的在主电图4 层次化件序号标注ate (需中置页下注任务,元nnotate (见图置页对元件进⾏量CB Editor Reu g Reused modu 编号,Action Mark for 中Reuse Module );注任务,元编号;电路中双击⼦电现,不,由于的⿏标光标框上添加⼦电路端⼝的位布在主电路中⽤层次化设计主标注(这步很关先选中图纸页⾯下选中Res 所有元件名即变见图5)⾯下选中Incre ⾏增量式⾃动编r Reuse ⾯ module ,on 选为Uncon 窗中⾃动dule 项可所有元件名击⼦电路块不同在标注时确变为虚⼗字状⼦电路的外引位置布局,使其中使⽤,参与主计主电路原理步很关键)纸夹) Reset part re 名即变成附有 Incremental ⾃动编号;页⾯,选中请求对当前Unconditional 动出现的⼦电可不选,因为件名即⾃动编路块,系统⾃的引⽤处的⼦已经确定了层次⼗字状态,需要外引端⼝及更主电路的绘路图art referances 成附有”?”的待ental ;当前onal ,⼦电动编统了层次需要接及显⽰美观;的绘制⽰例 ances to “的待定图5 主电关系,所⽹接着在主电路中要素(见图,⽽且可拷贝”选项,定状态;主电路标注以在⽹络表中不电路中画出见图3);插⼊、,设为将元件标注中不会模块插⼊操粘贴,将元件出现元F o l l o w M e !执⾏Tools->Create Netlist…,系统即⽣成⽹表;应注意的是此前对⼦电路中元件封装属性等描述将被主电路引⽤时继承;3.2 ⽹表调⽤在PCB Editor中执⾏import logic即可导⼊逻辑⽹表及元件封装(基本的PCB设置及⽣成操作此处不表),跟平坦时设计时相同;--------------------------------------------- The End,敬请关注PCB篇-----------------------------------!eMwolloF。

第二章Cadence的原理图设计要点

第二章 Cadence的原理图设计2.1Design Entry CIS软件概述Cadence软件系统有两套电路原理图的设计工具,一套是Design Entry HDL,另一套就是我们马上要开始学习的Design Entry CIS。

其中Design Entry HDL 是Cadence公司原本的原理图设计软件,可以用于芯片电路和板级电路的设计,其长处在于可以把芯片的电路原理图和板级电路原理图结合在一起,进行综合设计;而Design Entry CIS主要用于常规的板级电路设计,Design Entry CIS原本是OrCAD公司的产品,OrCAD公司后来被Cadence公司收购,于是Design Entry CIS也就成了Cadence公司的另一套电路原理图设计软件。

Design Entry CIS原理图设计软件的特点是直观、易学、易用,在业界有很高的知名度,利用Design Entry CIS原理图设计软件可以进行简单的(只有单张图纸构成的)电路原理图设计,也可以进行(由多张图纸拼接而成的)平坦式电路原理图设计,还可以进行(多张图纸按一定层次关系构成的)层次式电路原理图设计。

在本章中,我们首先学习简单的电路原理图设计,然后再学习较为复杂的平坦式和层次式电路原理图设计。

我们将围绕一块非常简单的STC系列单片机下载电路板,学习简单电路原理图的设计,同时在此过程中,还将学习到USB转UART串行口、STC系列单片机下载电路等方面的知识。

接着,我们将围绕一块ARM-7核心实验板,进行平坦式和层次式电路原理图的设计,而该核心板是配套于ARM-7实验箱。

在此过程中我们还将学习到嵌入式技术等方面的知识。

2.2初识Design Entry CIS一.启动Design Entry CIS我们在电脑上点击“开始→所有程序→Cadence SPB 16.2→Design Entry CIS”,如下图所示:这时将弹出如下对话框:图2-2 选择工作内容在这里我们选择“OrCAD Capture CIS”一项,点击“OK”按钮后,就实际启动了Design Entry CIS,出现如下界面:图2-3 OrCAD Capture CIS软件界面与大多数软件一样,OrCAD Capture CIS软件也是以项目方式管理我们的设计文件的。