电子科技大学期末数字电子技术考试题a卷-参考答案教学内容

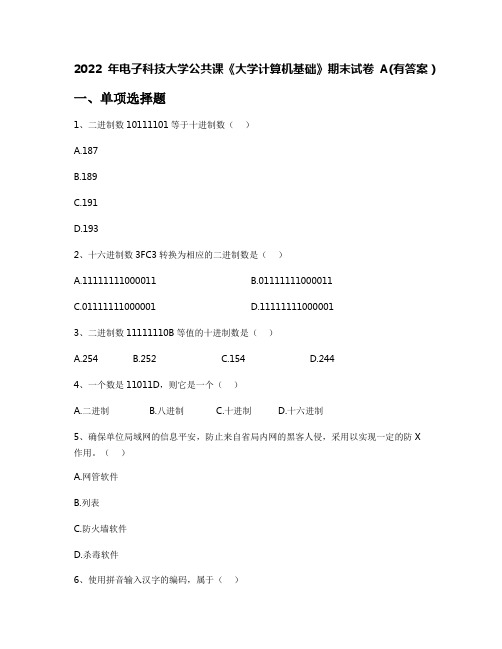

2022年电子科技大学公共课《大学计算机基础》期末试卷A(有答案)

2022年电子科技大学公共课《大学计算机基础》期末试卷A(有答案)一、单项选择题1、二进制数10111101等于十进制数()A.187B.189C.191D.1932、十六进制数3FC3转换为相应的二进制数是()A.11111111000011B.01111111000011C.01111111000001D.111111110000013、二进制数11111110B等值的十进制数是()A.254B.252C.154D.2444、一个数是11011D,则它是一个()A.二进制B.八进制C.十进制D.十六进制5、确保单位局域网的信息平安,防止来自省局内网的黑客人侵,采用以实现一定的防X作用。

()A.网管软件B.列表C.防火墙软件D.杀毒软件6、使用拼音输入汉字的编码,属于()A.外码B.机内码C.交换码D.字形码7、计算机由五大部件组成,它们是()A.控制器、运算器、存储器、输入设备、输出设备B.控制器、CPU、存储器、输入设备、输出设备C.运算器、控制器、外存储器、输入设备、输出设备D.CPU、运算器、外存储器、输入设备、输出设备8、在Windows 7的对话框中,选项前的“□”图标称为()A.单选按钮B.复选框C.命令按钮D.输入框9、下列有关快捷方式叙述正确的是()A.删除应用程序的快捷方式,并未删除对应的应用程序文件B.删除应用程序的快捷方式,也删除了对应的应用程序文件C.在桌面上只能建立应用程序快捷方式D.建立应用程序的快捷方式,就是将对应的应用程序文件复制到桌面上10、在Windows 7的资源管理器窗口中,可显示文件名、大小、类型和修改时间等内容的显示方式是()A.详细资料B.列表C.小图标D.大图标11、在Windows 7中,文件夹名称可以包含字符()A.*B.BC.ID.D.PS/212、剪贴板是个临时存储区,它属于什么的一部分()A.内存B.硬盘C.光盘D.BIOS13、下列不属于Windows 7中资源管理器的文件排序方式的是()A.按名称B.按类型C.按范围D.按日期14、在Word 2010文档中插入分节符,便于实现()A.修改文档B.创建文档目录C.阅读文档D.创建不同的页眉15、Word 中选定表格的某一行,再从“编辑”菜单中选择“清除”命令(或按Del健)将()A.副除这一行,即表格少一行B.副除该行各单元格中的内容C.副除该行中第一个单元格的内容D.删除该行的表格线16、下列有关Word2010叙述中,不正确的是()A、进行打印预览时必须开启打印机B、使用“文件”菜单的“打开”命令,可打开一个已存在的Doc文档C、可将正在编辑的文档另存为一个纯文本TXT文件D、允许同时打开多个文档17、在Word 2010编辑文档时,所见即所得的视图是()A.草稿视图B.页面视图C.大纲视图D.Web版式视图18、在Word中插入图片,其默认的环绕方式是()A.嵌入型B.四周型C.紧密型D.浮于文字下方19、下列关于Word文档分栏,叙述正确的是()A.各栏的宽度可以不同B.各栏的间距是固定的C.最多可以设4栏D.各栏之间不能添加分隔符20、在Excel 2010的数据清单中进行高级筛选时.下面不是必需的是()A.数据清单要有标题B.要指定数据区城C.要确定条件区域D.要确定结果的显示区域21、如果要在Excel 2010工作表区域C1:C15中输入起始值为3,公差为2的递增等差数列,在C2单元格中应输入公式()A.=C1-2B.=2-C1C.=C1+2D.=$C$1+222、在Excel 2010的数据库中,自动筛选是对各()A. 记录进行条件选择的筛选B. 字段进行条件选择的筛选C. 行号进行条件选择的筛选D. 列号进行条件选择的筛选23、在Excel 2010中.以下区域表示正确的是()A.A1-A5B.Al;A12C.(A1>A5)D.sheet1!A1.A1224、在对Excel 2010工作表中数据进行筛选时,没有的筛选方式是()A.手工筛选B.自动筛选C.用自定义筛选器筛选D.高级筛选25、已知Exce12010工作表包含示数据,B2单元的公式为:=B1+$A2,若将B2单元格的公式复制到D3单元格,则D3单元格中显示的结果为()Α. 5 B. 7 C. 10 D. 1526、在Access2010中允许使用多种数据类型,不包括()A.文本B.备注C.图片D.数字27、设置PowerPoint 2010动画时,若对动画出现的方向进行设置,单击()A.“效果”按钮B.“动画样式”按钮C.“预览”按钮D.“添加动画”按钮28、下列属于局域网的是()A.国家网B.校园网C.城市网D.因特网29、P/IP体系结构分为()A.7层B.4层021C.2层D.任意层30、实现局域网与广域网互联的主要设备是()A.网卡B.集线器C.路由器D.网桥二、填空题31、在Windows 7的“资源管理器”中,要选择连续4个文件,先用鼠标单击第1个文件,再按住_________键单击第4个文件。

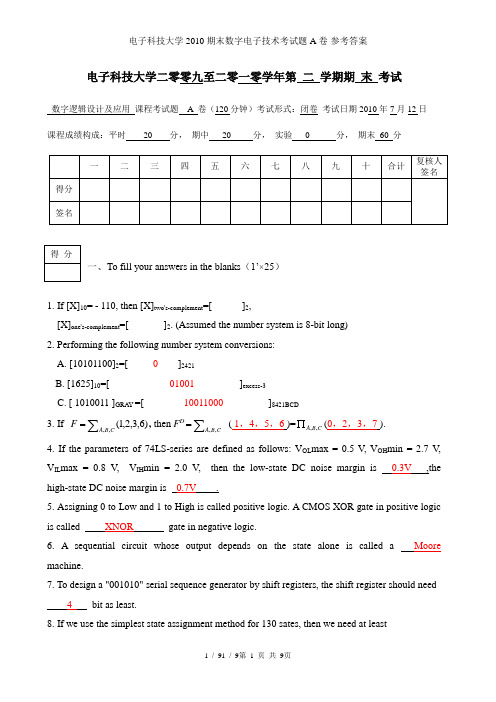

电子科技大学期末数字电子技术考试题a卷-参考答案

电子科技大学二零零九至二零一零学年第 二 学期期 末 考试数字逻辑设计及应用 课程考试题 A 卷(120分钟)考试形式:闭卷 考试日期2010年7月12日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末 60 分一、To fill your answers in the blanks (1’×25)1. If [X]10= - 110, then [X]two's-complement =[ ]2,[X]one's-complement =[ ]2. (Assumed the number system is 8-bit long) 2. Performing the following number system conversions: A. [10101100]2=[ 0 ]2421B. [1625]10=[01001 ]excess-3C. [ 1010011 ]GRAY =[10011000 ]8421BCD3. If ∑=C B A F ,,)6,3,2,1(, then F D ∑=C B A ,,( 1,4,5,6 )=C B A ,,∏(0,2,3,7 ).4. If the parameters of 74LS-series are defined as follows: V OL max = 0.5 V , V OH min = 2.7 V , V IL max = 0.8 V , V IH min = 2.0 V , then the low-state DC noise margin is 0.3V ,the high-state DC noise margin is 0.7V .5. Assigning 0 to Low and 1 to High is called positive logic. A CMOS XOR gate in positive logic is called XNOR gate in negative logic.6. A sequential circuit whose output depends on the state alone is called a Moore machine.7. To design a "001010" serial sequence generator by shift registers, the shift register should need 4 bit as least.8. If we use the simplest state assignment method for 130 sates, then we need at least8state variables.9. One state transition equation is Q*=JQ'+K'Q. If we use D flip-flop to complete the equation, the D input terminal of D flip-flop should be have the function D= JQ'+K'Q.10.Which state in Fig. 1 is ambiguous D11.A CMOS circuit is shown as Fig. 2, its logic function z= A’B’+ABFig. 1 Fig. 212.If number [A]two's-complement =01101010 and [B]one's-complement =1001, calculate [A-B]two's-complement and indicate whether or not overflow occurs.(Assumed the number system is 8-bit long)[A-B]two's-complement = 01110000, overflow no13. If a RAM’s capacity is 16K words × 8 bits, the address inputs should be 14bits; We need 8chips of 8K ⨯8 bits RAM to form a 16 K ⨯ 32 bits ROM..14. Which is the XOR gate of the following circuit A .15.There are 2n-n invalid states in an n-bit ring counter state diagram.16.An unused CMOS NOR input should be tied to logic Low level or 0 .17.The function of a DAC is translating the Digital inputs to the same value of analogoutputs.二、Complete the following truth table of taking a vote by A,B,C, when more than two of A,B,C approve a resolution, the resolution is passed; at the same time, the resolution can’t go through if A don’t agree.For A,B,C, assume 1 is indicated approval, 0 is indicated opposition. For the F,A B C F三、The circuit to the below realizes a combinational function F of four variables. Fill in the Karnaugh map of the logic function F realized by the multiplexer-based circuit. (6’)四、(A) Minimize the logic function expressionF = A·B + AC’ +B’·C+BC’+B’D+BD’+ADE(H+G) (5’)F = A·B + AC’ +B’·C+BC’+B’D+BD’ = A·(B ’C )’ +B’·C+BC’+B’D+BD’= A +B’·C+BC’+B’D+BD’+C ’D (或= A +B’·C+BC’+B’D+BD’+CD ’)= A +B’·C+BD’+C ’D (或= A + BC’+B’D +CD ’)(B) To find the minimum sum of product for F and use NAND-NAND gates to realize it (6’)),,,(Z Y X W F Π(1,3,4,6,9,11,12,14)------3分 F= X ’Z ’+XZ -----2分 =( X ’Z ’+XZ)’’=(( X ’Z ’)’(XZ)’)’ ------1分五、Realize the logic function using one chip of 74LS139 and two NAND gates.(8’)∑=)6,2(),,(C B A F ∑=)3,2,0(),,(E D C GF(A,B,C)=C’∑(1,3) ---- 3分 G(C,D,E)=C’∑(0,2,3) ----3分-六、Design a self-correcting modulo-6 counter with D flip-flops. Write out the excitation equations and output equation. Q2Q1Q0 denote the present states, Q2*Q1*Q0* denote the next states, Z denote the output. The state transition/output table is as following.(10’)Q2Q1Q0Q2*Q1*Q0*Z000 100 0100 110 0110 111 0111 011 0011 001 0001 000 1激励方程式:D2=Q0’(2分,错-2分)D1=Q2 (2分,错-2分)D0=Q1 (2分,错-2分)修改自启动:D2=Q0 +Q2Q1’(1分,错-1分)D1=Q2+Q1Q0’(1分,错-1分)D0=Q1+Q2Q0 (1分,错-1分)输出方程式:Z=Q1’Q0 (1分,错-1分)得分七、Construct a minimal state/output table for a moore sequential machine, that will detect the input sequences: x=101. If x=101 is detected, then Z=1.The input sequences DO NOT overlap one another. The states are denoted with S0~S3.(10’)For example:X:0 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 0 0 1 1 ……Z:0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 ……state/output table八、Please write out the state/output table and the transition/output table and theexcitation/output table of this state machine.(states Q2 Q1=00~11, use the state name A~D )(10’)Transition/output table State/output table Excitation/output table(4分) (3分) (3分)评分标准:转移/输出表正确,得4分;每错一处扣0.5分,扣完4分为止;由转移/输出表得到状态/输出表正确,得3分;每错一处扣0.5分,扣完3分为止;激励/输出表正确,得3分;每错一处扣0.5分,扣完3分为止。

数字电路2011期末考试题-参考解答

电子科技大学2010 -2011学年第二学期期末考试 A 卷课程名称:_数字逻辑设计及应用__ 考试形式:闭卷考试日期:20 11 年7 月7 日考试时长:_120___分钟课程成绩构成:平时30 %,期中30 %,实验0 %,期末40 %本试卷试题由__六___部分构成,共__6___页。

I. Fill your answers in the blanks(2’ X 10=20’)1. A parity circuit with N inputs need N-1XOR gate s. If the number of “1” in an N logic variables set, such as A、B、C、…W, is even number, then__________A B C W⊕⊕⊕⋅⋅⋅⋅⊕=0 .2. A circuit with 4 flip-flops can store 4bit binary numbers, that is, include 16 states at most.3. A modulo-20 counter circuit needs 5 D filp-flops at least. A modulo-288 counter circuit needs 3 4-bit counters of 74x163 at least.4. A 8-bit ring counter has 8 normal states. If we want to realize the same number normal states, we need a 4bit twisted-ring counter.5. If the input is 10000000 of an 8 bit DAC, the corresponding output is 5v. Then an input is 00000001 to the DAC, the corresponding output is 5/128 (0.0391) V; if an input is 10001000, the corresponding DAC output is 5.3125V.II. Please select the only one correct answer in the following questions.(2’ X 5=10)B ) chips of 4K ⨯4 bits RAM to form a 16 K ⨯ 8 bits RAM.A) 2 B) 8 C) 4 D) 162. To design a "01101100" serial sequence generator by shift registers, we need a( A)-bit shift register as least.A) 5 B) 4 C) 3 D) 63. For the following latches or flip-flops, ( B) can be used to form shift register.A) S-R latch B) master-slave flip-flop C) S-R latch with enable D) S’-R’ latch4. Which of the following statements is correct? ( C )A) The outputs of a Moore machine depend on inputs as well as the states.B) The outputs of a Mealy machine depend only on the states.C) The outputs of a Mealy machine depend on inputs as well as the states. D) A), B), C) are wrong.5. There is a state/output table of a sequential machine as the table 1, what the input sequences isdetected? ( D )A) 11110 B) 11010 C) 10010 D) 10110Table 1III.Analyze the sequential-circuit as shown in figure 1. [15’]1. Write out the excitation equations, transitionequations and output equation. [5’]2. Assume the initial state is Q 2Q 1=00, complete thetiming diagram for Q 2 ,Q 1 and Z.( Don ’t need consider propagation delay of each component)[10’]Figure-1解答:激励方程: D 1=Q 1⊕Q 2,D 2= Q /1+ Q /2转移方程:Q 1 *= D 1=Q 1⊕Q 2,Q 2 *=D 2= Q /1+ Q /2 输出方程:Z= Q 1•Q 2IV. Design a Mealy sequential detector with one input x and one output z. If and only if xdescribe the state meaning and finish the state/output table. [15] Example : x :0 1 0 1 1 1 1 0 0 1 1 0 0 1 1 1 1 1 z :0 0 0 0 0 0 1 0 0 1 0 0 0 1 0 0 1 1XState meaningS 0 1 Initial A A,0 B,0 Received 1 B C,0 D,0 Received 10 C E,0 B,0 Received 11 D C,0 F,0 Received 100 E A,0 B,1 Received 111 F C,0F,1S*,ZV. Analyze the circuit as shown below, which contains a 74x163 4-bit binary counter, a 74x138[15’] ’ output F. [5’]2. Write out the sequence of states for the 74x161 in the circuit. [7’]3. Describe the modulus(模) of the circuit. [3’]解答:F=D2=Y6/=(QDQCQBQA /)/ 状态序列:0,1,2,3,4,5,6,7,8,9,10,11,12,13,14,0,1,2,… M=15VI.the state transition sequence is 0→2→4→1→3→0→…with the binary code. 1. Fill out the transition/output table. [8’]2. Write out the excitation equations and output equation. [4’]3. List the complete transition/output table, and check the self-correct. [3’] transition/output table : 74X161的功能表输入 当前状态 下一状态 输出CLR_L LD_L ENT ENP QD QC QB QA QD* QC* QB* QA* RCO 0 X X X X X X X 0 0 0 0 1 0 X X X X X X D C B A 1 1 0 X X X X X QD QC QB QA 1 1 X 0 X X X X QD QC QB QA 1 1 1 1 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 1 0 0 1 0 1 1 1 1 0 0 1 0 0 0 1 1 1 1 1 1 0 0 1 1 0 1 0 0complete transition/output table:输出方程:Z=Q1Q0检查自启动:当Q2Q1Q0=101,可得下一状态为001;当Q2Q1Q0=110,可得下一状态为101;当Q2Q1Q0=111,可得下一状态为001。

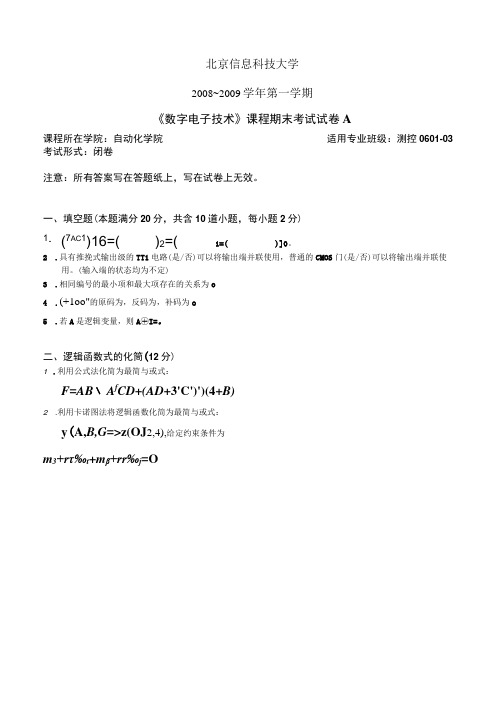

第一学期《数字电子技术》课程期末考试试卷A和答案数字电路与逻辑设计

北京信息科技大学2008~2009学年第一学期《数字电子技术》课程期末考试试卷A课程所在学院:自动化学院适用专业班级:测控0601-03考试形式:闭卷注意:所有答案写在答题纸上,写在试卷上无效。

一、填空题(本题满分20分,共含10道小题,每小题2分)1∙(7AC1)16=( )2=( 1=( )]0。

2.具有推挽式输出级的TT1电路(是/否)可以将输出端并联使用,普通的CMOS门(是/否)可以将输出端并联使用。

(输入端的状态均为不定)3.相同编号的最小项和最大项存在的关系为o4.(+1oo"的原码为,反码为,补码为o5.若A是逻辑变量,则A㊉I=。

二、逻辑函数式的化筒(12分)1 .利用公式法化简为最简与或式:F=AB∖A f CD+(AD+3'C')')(4+B)2 .利用卡诺图法将逻辑函数化简为最简与或式:y(A,B,G=>z(OJ2,4),给定约束条件为m3+rτ‰t+mβ+rr‰j=O下面电路图中,写出输出信号是什么状态(高电平、低电平或高阻态),已知乂为74系四、试用一片8选1数据选择器74HC151产生逻辑函数:Y=AB r CD÷48(C÷r>)+ABXCΦZ))÷ABC r 要求给出设计的全过程,并画出逻辑电路图。

(12分)s ,A2A4YO O O OO O O1O∣O O1O D1O O11O1O OO1O1/人O11O2O11151X X X高阻五、TT1主从JK触发器的输入波形如图所示,画出输出端Q的波形(12分)CP六、分析如图时序逻辑电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路的功能以及能否自启动。

(14分)CP七、 试用一片4位同步二进制计数器741S163接成十进制计数器(允许附加必要的门电路,采用清零法),并作简要说明。

741S163的引脚图如下所示。

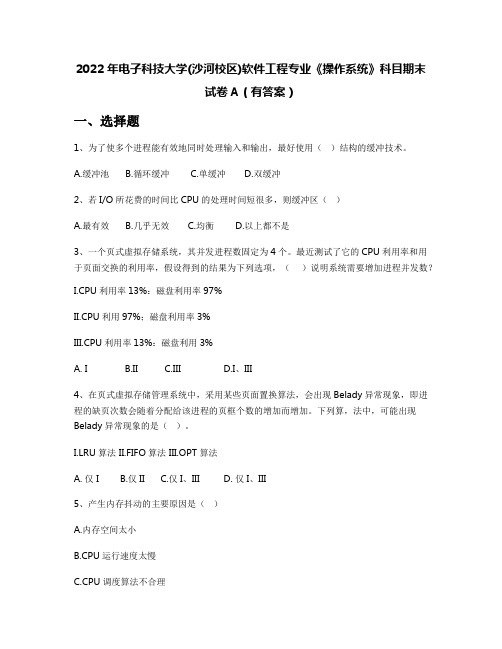

2022年电子科技大学(沙河校区)软件工程专业《操作系统》科目期末试卷A(有答案)

2022年电子科技大学(沙河校区)软件工程专业《操作系统》科目期末试卷A(有答案)一、选择题1、为了使多个进程能有效地同时处理输入和输出,最好使用()结构的缓冲技术。

A.缓冲池B.循环缓冲C.单缓冲D.双缓冲2、若I/O所花费的时间比CPU的处理时间短很多,则缓冲区()A.最有效B.几乎无效C.均衡D.以上都不是3、一个页式虚拟存储系统,其并发进程数固定为4个。

最近测试了它的CPU利用率和用于页面交换的利用率,假设得到的结果为下列选项,()说明系统需要增加进程并发数?I.CPU利用率13%:磁盘利用率97%II.CPU利用97%;磁盘利用率3%III.CPU利用率13%:磁盘利用3%A. IB.IIC.IIID.I、III4、在页式虚拟存储管理系统中,采用某些页面置换算法,会出现Belady异常现象,即进程的缺页次数会随着分配给该进程的页框个数的增加而增加。

下列算,法中,可能出现Belady异常现象的是()。

I.LRU算法 II.FIFO算法 III.OPT 算法A. 仅IB.仅IIC.仅I、IIID. 仅I、III5、产生内存抖动的主要原因是()A.内存空间太小B.CPU运行速度太慢C.CPU调度算法不合理D.页面置换算法不合理6、操作系统提供给编程人员的接口是()。

A.库函数B.高级语言C.系统调用D.子程序7、下列关于操作系统的论述中,正确的是()。

A.对于批处理作业,必须提供相应的作业控制信息B.对于分时系统,不一定全部提供人机交互功能C.从响应角度看,分时系统与实时系统的要求相似D.在采用分时操作系统的计算机系统中,用户可以独占计算机操作系统中的文件系统8、下面关于文件的叙述中,错误的是()。

I.打开文件的主要操作是把指定文件复制到内存指定的区域II.对一个文件的访问,常由用户访问权限和用户优先级共同限制III.文件系统采用树形片录结构后,对于不同用户的文件,其文件名应该不同IV.为防止系统故障造成系统内文件受损,常采用存取控制矩阵方法保护文件A.仅IB. 仅I、IIIC.仅I、III、IVD.I、II、III,IV9、下列关于打开文件open()操作和关闭文件close()操作的叙述,只有()是错误的。

数字电子技术试卷A及答案

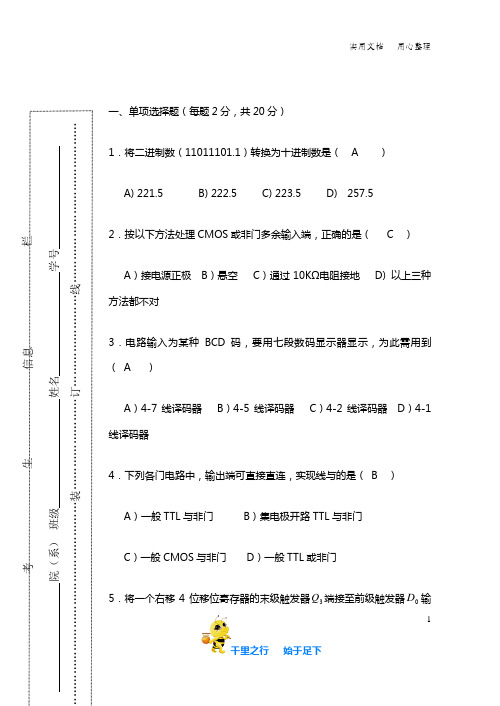

1一、单项选择题(每题2分,共20分)1.将二进制数(11011101.1)转换为十进制数是( A )A) 221.5 B) 222.5 C) 223.5 D) 257.52.按以下方法处理CMOS 或非门多余输入端,正确的是( C )A )接电源正极B )悬空C )通过10K Ω电阻接地 D) 以上三种方法都不对3.电路输入为某种BCD 码,要用七段数码显示器显示,为此需用到( A )A )4-7线译码器B )4-5线译码器C )4-2线译码器D )4-1线译码器4.下列各门电路中,输出端可直接直连,实现线与的是( B )A )一般TTL 与非门B )集电极开路TTL 与非门C )一般CMOS 与非门D )一般TTL 或非门5.将一个右移4位移位寄存器的末级触发器3Q 端接至前级触发器0D 输2入端。

设初态为3210Q Q Q Q =1101,以过5个CP 作用后的状态为( B )A )1101B )1110C )1011D )01116.用256×4位的RAM 扩展成2048×12位RAM ,每一条I/O 总线上并联了几条数据线?( C )A )24B )12C )8D )47.如下图中电路的名称是( D )A )单稳态电路B )JK 触发器C )施密特电路D )多谐振荡器8.已知函数D C B A Y ++=)(,则其反函数为( B )A )D CB DC A + B )D C B A ++ C )AC D AB + D )D B C A +9.可实现逻辑函数A Y =的是( D )A ) A A ⋅B ) A A +C )0⊕AD )1⊕A310.在倒T 形电阻网络D /A 转换器中,n n REFo D V V 2-=,设REF V =10V , D ="1000"0123=d d d d 时,则o V 为( B )伏。

A )3210-B ) 210-C ) 3210D ) 210 二、填空题:(24%)1.与十六进制(2D )16对应的二进制数是(101101)2 。

数字电子技术期末考试试题及答案(试卷一)

、 代入规则 对偶规则 反

演规则

、

。

5、为 了 实 现 高 的 频 率 稳 定 度 , 常 采 用 石英晶体

振荡

器 ; 单 稳 态 触 发 器 受 到 外 触 发 时 进 入 暂稳态 态

6、同步 RS 触发器中 R、S 为 高 电平有效,基本 R、S 触发器中 R、S

为低

电平有效

7、在进行 A/D 转换时,常按下面四个步骤进行, 采样 保持 量化 编

码、

、

、。Βιβλιοθήκη 二、选择题(每题 1 分,共 10 分)

1、有八个触发器的二进制计数器,它们最多有(

)种计数状态。

A、8; B、16; C、256; D、64

2、下列触发器中上升沿触发的是( )。

A、主从 RS 触发器;B、JK 触发器;C、T 触发器;D、D 触发器

3、下式中与非门表达式为( d ),或门表达式为(a )。

数字电子技术期末考试试题及答案(试卷一)

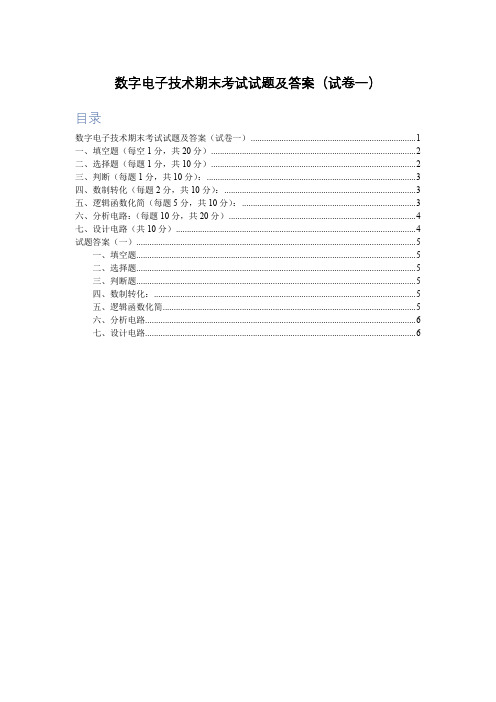

目录

数字电子技术期末考试试题及答案(试卷一) ........................................................................... 1 一、填空题(每空 1 分,共 20 分).............................................................................................2 二、选择题(每题 1 分,共 10 分).............................................................................................2 三、判断(每题 1 分,共 10 分):...............................................................................................3 四、数制转化(每题 2 分,共 10 分):.......................................................................................3 五、逻辑函数化简(每题 5 分,共 10 分):...............................................................................3 六、分析电路:(每题 10 分,共 20 分).....................................................................................4 七、设计电路(共 10 分).............................................................................................................4 试题答案(一)...............................................................................................................................5

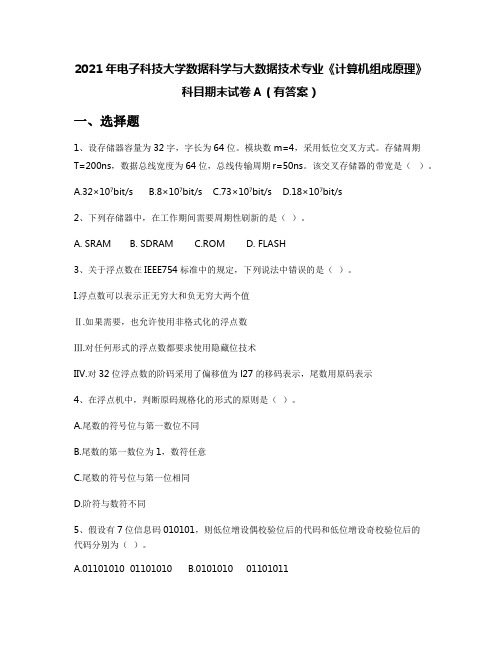

2021年电子科技大学数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)

2021年电子科技大学数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、设存储器容量为32字,字长为64位。

模块数m=4,采用低位交叉方式。

存储周期T=200ns,数据总线宽度为64位,总线传输周期r=50ns。

该交叉存储器的带宽是()。

A.32×107bit/sB.8×107bit/sC.73×107bit/sD.18×107bit/s2、下列存储器中,在工作期间需要周期性刷新的是()。

A. SRAMB. SDRAMC.ROMD. FLASH3、关于浮点数在IEEE754标准中的规定,下列说法中错误的是()。

I.浮点数可以表示正无穷大和负无穷大两个值Ⅱ.如果需要,也允许使用非格式化的浮点数Ⅲ.对任何形式的浮点数都要求使用隐藏位技术IⅣ.对32位浮点数的阶码采用了偏移值为l27的移码表示,尾数用原码表示4、在浮点机中,判断原码规格化的形式的原则是()。

A.尾数的符号位与第一数位不同B.尾数的第一数位为1,数符任意C.尾数的符号位与第一位相同D.阶符与数符不同5、假设有7位信息码010101,则低位增设偶校验位后的代码和低位增设奇校验位后的代码分别为()。

A.01101010 01101010B.0101010 01101011C.01101011 01101010D.01101011 011010116、总线的数据传输速率可按公式Q=Wf/N计算,其中Q为总线数据传输速率,W为总线数据宽度(总线位宽/8),f为总线时钟频率,N为完成一次数据传送所需的总线时钟周期个数。

若总线位宽为16位,总线时钟频率为8MHz,完成一次数据传送需2个总线时钟周期,则总线数据传输速率Q为()。

A.16Mbit/sB.8Mbit/sC.16MB/sD.8MB/s7、下列关于多总线结构的叙述中,错误的是()。

A.靠近CPU的总线速度较快B.存储器总线可支持突发传送方式C.总线之间需通过桥接器相连D.PCI-Expressx16采用并行传输方式8、下列描述中,正确的是()。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子科技大学二零零九至二零一零学年第 二 学期期 末 考试数字逻辑设计及应用 课程考试题 A 卷(120分钟)考试形式:闭卷 考试日期2010年7月12日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末 60 分一、To fill your answers in the blanks (1’×25)1. If [X]10= - 110, then [X]two's-complement =[ 10010010 ]2,[X]one's-complement =[ 10010001 ]2. (Assumed the number system is 8-bit long) 2. Performing the following number system conversions: A. [10101100]2=[ 000111010010 ]2421B. [1625]10=[0100100101011000 ]excess-3C. [ 1010011 ]GRAY =[10011000 ]8421BCD3. If ∑=C B A F ,,)6,3,2,1(, then F D ∑=C B A ,,( 1,4,5,6 )=C B A ,,∏(0,2,3,7 ).4. If the parameters of 74LS-series are defined as follows: V OL max = 0.5 V , V OH min = 2.7 V , V IL max = 0.8 V , V IH min = 2.0 V , then the low-state DC noise margin is 0.3V ,the high-state DC noise margin is 0.7V .5. Assigning 0 to Low and 1 to High is called positive logic. A CMOS XOR gate in positive logic is called XNOR gate in negative logic.6. A sequential circuit whose output depends on the state alone is called a Moore machine.7. To design a "001010" serial sequence generator by shift registers, the shift register should need 4 bit as least.8. If we use the simplest state assignment method for 130 sates, then we need at least8state variables.9. One state transition equation is Q*=JQ'+K'Q. If we use D flip-flop to complete the equation, the D input terminal of D flip-flop should be have the function D= JQ'+K'Q.10.Which state in Fig. 1 is ambiguous D11.A CMOS circuit is shown as Fig. 2, its logic function z= A’B’+ABFig. 1 Fig. 212.If number [A]two's-complement =01101010 and [B]one's-complement =1001, calculate [A-B]two's-complement and indicate whether or not overflow occurs.(Assumed the number system is 8-bit long)[A-B]two's-complement = 01110000, overflow no13. If a RAM’s capacity is 16K words × 8 bits, the address inputs should be 14bits; We need 8chips of 8K ⨯8 bits RAM to form a 16 K ⨯ 32 bits ROM..14. Which is the XOR gate of the following circuit A .15.There are 2n-n invalid states in an n-bit ring counter state diagram.16.An unused CMOS NOR input should be tied to logic Low level or 0 .17.The function of a DAC is translating the Digital inputs to the same value of analogoutputs.二、Complete the following truth table of taking a vote by A,B,C, when more than two of A,B,C approve a resolution, the resolution is passed; at the same time, the resolution can’t go thr ough if A don’t agree.For A,B,C, assume 1 is indicated approval, 0 is indicated opposition. For the F,A B C F三、The circuit to the below realizes a combinational function F of four variables. Fill in the Karnaugh map of the logic function F realized by the multiplexer-based circuit. (6’)四、(A) Minimize the logic function expressionF = A·B + AC’ +B’·C+BC’+B’D+BD’+ADE(H+G) (5’)F = A·B + AC’ +B’·C+BC’+B’D+BD’ = A·(B ’C )’ +B’·C+BC’+B’D+BD’= A +B’·C+BC’+B’D+BD’+C ’D (或= A +B’·C+BC’+B’D+BD’+CD ’)= A +B’·C+BD’+C ’D (或= A + BC’+B’D +CD ’)(B) To find the minimum sum of product for F and use NAND-NAND gates to realize it (6’)),,,(Z Y X W F Π(1,3,4,6,9,11,12,14)------3分 F= X ’Z ’+XZ -----2分 =( X ’Z ’+XZ)’’=(( X ’Z ’)’(XZ)’)’ ------1分五、Realize the logic function using one chip of 74LS139 and two NAND gates.(8’)∑=)6,2(),,(C B A F ∑=)3,2,0(),,(E D C GF(A,B,C)=C’∑(1,3) ---- 3分 G(C,D,E)=C’∑(0,2,3) ----3分-六、Design a self-correcting modulo-6 counter with D flip-flops. Write out the excitation equations and output equation. Q2Q1Q0 denote the present states, Q2*Q1*Q0* denote the next states, Z denote the output. The state transition/output table is as following.(10’)Q2Q1Q0Q2*Q1*Q0*Z000 100 0100 110 0110 111 0111 011 0011 001 0001 000 1激励方程式:D2=Q0’(2分,错-2分)D1=Q2 (2分,错-2分)D0=Q1 (2分,错-2分)修改自启动:D2=Q0 +Q2Q1’(1分,错-1分)D1=Q2+Q1Q0’(1分,错-1分)D0=Q1+Q2Q0 (1分,错-1分)输出方程式:Z=Q1’Q0 (1分,错-1分)得分七、Construct a minimal state/output table for a moore sequential machine, that will detect the input sequences: x=101. If x=101 is detected, then Z=1.The input sequences DO NOT overlap one another. The states are denoted with S0~S3.(10’)For example:X:0 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 0 0 1 1 ……Z:0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 ……state/output table八、Please write out the state/output table and the transition/output table and theexcitation/output table of this state machine.(states Q2 Q1=00~11, use the state name A~D )(10’)Transition/output table State/output table Excitation/output table(4分) (3分) (3分)评分标准:转移/输出表正确,得4分;每错一处扣0.5分,扣完4分为止;由转移/输出表得到状态/输出表正确,得3分;每错一处扣0.5分,扣完3分为止;激励/输出表正确,得3分;每错一处扣0.5分,扣完3分为止。