GS8322V72GC-225I中文资料

联通华盛3G系列产品介绍2010

特色推荐:1、超大屏幕,高清显示,高质量影像拍摄 2、强劲处理器高速运转,流畅协作 3、全新平台全新体验,支持谷歌移动服务 4、随时无缝高速互联,高速无线互联网接入 5、内置三大感应模式,人性化设计贴心细节 6、新一代MOTO智能指书,时时应手笔笔随心

签,还可以同步音乐铃声、应用程序等;

--电子邮箱:可以设置电子邮箱【公司邮箱】,支持邮件推送功 能,可以在线查看OFFICE附件;

-- 电子地图:使用GOOGLE地图,通过AGPS定位,可以查找线 路并实时查看路况;

其他功能:

指南针、 Safari上网、电话会议、实时天气预报、股市查询

销售话术: 一款革命性的移动电话、目前最好的 iPod 和开创性的 Internet 设备。

手机音乐,手机电视、手机报、USIM卡应用;

销售话术: 中兴X850机身造型典雅大方、小巧便携、结构紧凑,磨砂外壳手感极佳。

• 华为8100

上市时间: 待定

终端价格:

标准配置:待定

外观:滑盖、白色

操作系统: Android™ 2.1

尺寸:106mm(L)×57mm(W)×14mm(T) 电池容量: 1150mAh

终端价格:

标准配置:待定

外观:滑盖、白色

操作系统: Android™ 2.1

尺寸:106mm(L)×57mm(W)×14mm(T) 电池容量: 1150mAh

屏幕参数: 3.2’ HVGA ,26万色,电容触摸屏

网络频率:W-CDMA 2100MHz GSM 900/1800/1900 MHz

SL2.2S规格书,usb HUB大全,替换FE1.1S,GL850,GL852,PL2586

USB2.0 HUB控制器集成电路USB 2.0 HIGH SPEED 4-PORT HUB CONTROLLERSL2.2s数据手册Data Sheet内容目录第一章管脚分配 (3)1.1 SL2.2S管脚图 (3)1.2 SL2.2S管脚定义 (3)第二章 功能叙述 (5)2.1综述 (5)2.2指示灯 (5)2.2.1单灯方案 (5)2.2.2多灯方案 (6)2.2.3 LED指示定义 (6)2.3过流保护 (6)2.4充电支持 (6)2.5I2C接口 (7)2.6EEPROM设置 (7)第三章电气特性 (8)3.1极限工作条件 (8)3.2工作范围 (8)3.3直流电特性 (8)3.4HS/FS/LS电气特性 (8)3.5ESD特性 (8)附录一封装 (9)表格目录表格1: 端口LED定义 (6)表格 2 : ACTIVE LED定义 (6)表格3:EEPROM数据结构定义 (7)表格4: 最大额定值 (8)表格5: 工作范围 (8)表格6: 直流电特性 (8)插图目录图1:SSOP28 管脚图 (3)图2:单灯方案配置 (5)图3: 5灯方案配置 ............................................................................... (6)图 4:附录 封装图 ................................................................................... .9第一章管脚分配1.1SL2.2s管脚图图1:SSOP28 管脚图1.2SL2.2s管脚定义管脚名称28Die IO类型定义Pin#VSS 1 P 芯片地XOUT 2 O晶振PAD XIN 3 IDM4 4 B下行口4的USB信号DP4 5 BDM3 6 B下行口3的USB信号DP3 7 BDM2 8 B下行口2的USB信号DP2 9 BDM1 10 B下行口1的USB信号DP1 11 BVDD18 12 P 模拟1.8vVDD33 13 P 模拟3.3v - 14 NCUDM 15 B上行口的USB信号UDP 16 BRESET_N 17 I,Pu 芯片外部复位输入- 18 NCPSELF 19 I,Pu 高为自供电,低为总线供电VDD5 20 P 5v输入VDD33 21 P 3.3v输出DRV 22 B,Pu 点灯驱动信号LED1 23 B,Pu 点灯驱动信号LED2 24 B,Pu 点灯驱动信号PWRN 25 B,Pu 下行口电源输出控制,低有效OVCRN/SDA 26 B,PuI2C SDA数据线,内部上拉;芯片初始化完成后作为过流保护输入脚,低有效SCL 27 B,Pu I2C SCL时钟输出VDD18 28 P 数字1.8v注释:O,输出;I 输入;B 双向;P 电源/接地;Pu 上拉;Pd 下拉;NC 悬空;第二章 功能叙述2.1综述SL2.2s 是一颗高集成度,高性能,低功耗的USB2.0集线器主控芯片;该芯片采用STT 技术,单电源供电方式,芯片供电电压为5v , 内部集成5V 转3.3V,只需在外部电源添加滤波电容;芯片自带复位电路,低功耗技术让他更加出众。

WG-827型商务网关说明书

一.产品安装、使用安全说明(一)使用注意事项1.阅读、遵循并保留说明——操作设备之前,必须阅读并严格遵循安全说明及操作说明的所有要求。

请妥善保留本说明书,以备将来参考。

2.附件——请使用制造商推荐的附件或随产品提供的附件。

3.安装注意事项——请勿将此设备置于不稳定的台面、三脚架、支架或底座上。

防止设备由于掉落而造成的严重人身伤害及设备损坏。

请根据制造商的说明安装设备。

4.所有外接线禁止裸露,接线处和没用到的线头必须用绝缘胶布包扎,用于防止裸线意外的接触,导致设备的损坏。

5.维修——不要尝试自行维修设备。

打开或拆卸可能导致电击或其它危险。

所有维修事项均应交给专业的维修人员处理。

6.需要进行维修的损坏事项——发生以下情况时,请断开设备的交流或直流电源,然后通知专业的维修人员进行维修:-电源线或插头损坏。

-液体溅入设备或有异物落入设备。

-设备被水打湿或曝露在恶劣天气(雨、雪等)中。

-设备掉落或设备性能发生明显变化。

7.替换部件——如果需要替换部件,维修人员必须仅使用制造商指定的替换部件。

8.安全检查——维修设备之后,请让维修人员执行安全检查,确保设备能正常工作。

9.电源——仅使用标签上指明的电源类型操作设备。

如果不确定所用的电源类型请联系相关运营商(二)安装注意事项1.所有走线都必须套管,PVC管和镀锌管都可以,避免老鼠咬断线路引起故障。

虽然WG-827商务网关具备了良好的防静电、防雷击、防漏电设计,但请务必保证交流电地线连接完善,且交流电地线真实接地。

2.建议您不要经常带电拔插接线端子;请务必拔下接线端子,再进行相应的焊接工作。

3.对有强磁干扰的场所,应采用镀锌钢管或屏蔽线敷设并做接地处理。

4.WG-827商务网关出厂默认IP为192.168.9.243。

计算机在配置网关IP时,必须与网关在同一网段下,如计算机IP设置为:192.168.9.123。

5.在配置为出厂状态下的WG-827商务网关时,必须保证在局域网内只有一台出厂状态下的机器,以避免网络冲突。

毛斯(Moxa)UC-8200系列双核ARM Cortex-A7 1GHz IIoT网关产品说明书

UC-8200SeriesArm Cortex-A7dual-core1GHz IIoT gateways with built-in LTE Cat.4,1mini PCIe expansion slot for a Wi-Fi module,1CAN port,4DIs,4DOsFeatures and Benefits•Armv7Cortex-A7dual-core1GHz•ISASecure IEC62443-4-2Security Level2certified with Moxa IndustrialLinux3Secure•Moxa Industrial Linux with10-year superior long-term support•LTE-ready computer with Verizon/AT&T certification and industrial-grade CE/FCC/UL certifications•Dual-SIM slots•2auto-sensing10/100/1000Mbps Ethernet ports•Integrated LTE Cat.4module with US/EU/APAC band support•1CAN port supports CAN2.0A/B•microSD socket for storage expansion•-40to85°C wide temperature range and-40to70°C with LTE enabledCertificationsIntroductionThe UC-8200computing platform is designed for embedded data acquisition applications.The computer comes with dual RS-232/422/485serial ports,dual10/100/1000Mbps Ethernet ports,and one CAN port as well as dual Mini PCIe socket to support Wi-Fi/cellular modules.These versatile capabilities let users efficiently adapt the UC-8200to a variety of complex communications solutions.The UC-8200is built around a Cortex-A7dual core processor that has been optimized for use in energy monitoring systems,but is widely applicable to a variety of industrial solutions.With flexible interfacing options,this tiny embedded computer is a reliable and secure gateway for data acquisition and processing at field sites as well as a useful communications platform for many other large-scale deployments.Wide temperature LTE-enabled models are available for extended temperature applications.All units are thoroughly tested in a testing chamber, guaranteeing that the LTE-enabled computing platforms are suitable for wide-temperature applications.AppearanceUC-8210UC-8220SpecificationsComputerCPU Armv7Cortex-A7dual-core1GHzDRAM2GB DDR3LSupported OS Moxa Industrial Linux1(Debian9,kernel4.4),2027EOLMoxa Industrial Linux31(Debian11,kernel5.10),2031EOLSee /MILStorage Pre-installed8GB eMMCExpansion Slots MicroSD(SD3.0)socket x13OS is selectable via Moxa Computer Configuration System(CCS)for CTO models.For the model names,see the Ordering Information section of thedatasheet PDF file.Computer InterfaceEthernet Ports Auto-sensing10/100/1000Mbps ports(RJ45connector)x2 Serial Ports RS-232/422/485ports x2,software selectable(DB9male) CAN Ports CAN2.0A/B x1(DB9male)Digital Input DIs x4Digital Output DOs x4USB2.0USB2.0hosts x1,type-A connectorsWi-Fi Antenna Connector UC-8220Models:RP-SMA x2Cellular Antenna Connector UC-8220Models:SMA x2GPS Antenna Connector UC-8220Models:SMA x1Expansion Slots UC-8220-T-LX:mPCIe slot x2UC-8220-T-LX US/EU/AP Models:mPCIe slot x1SIM Format UC-8220Models:NanoNumber of SIMs UC-8220Models:2Buttons Programmable buttonTPM TPM v2.0Ethernet InterfaceMagnetic Isolation Protection 1.5kV(built-in)Security FunctionsHardware-based Security TPM2.0Hardware Root of Trust Secure BootIntrusion Detection Host-based Intrusion DetectionSecurity Tools Security Diagnostic ToolSecurity Event AuditingSecure UpdateDisk Protection LUKS Disk EncryptionRecovery One-step recovery to the last known secure stateDual-system design with automatic failbackReliability Network Keep AliveNetwork Failover and FailbackSerial InterfaceBaudrate300bps to921.6kbpsData Bits7,8Stop Bits1,2Parity None,Even,Odd,Space,MarkFlow Control RTS/CTS,XON/XOFFADDC(automatic data direction control)for RS-485RTS Toggle(RS-232only)Console Port1x4-pin header to DB9console portRS-232TxD,RxD,RTS,CTS,DTR,DSR,DCD,GNDRS-422Tx+,Tx-,Rx+,Rx-,GNDRS-485-2w Data+,Data-,GNDCAN InterfaceNo.of Ports1Connector DB9maleBaudrate10to1000kbpsIndustrial Protocols CAN2.0ACAN2.0BIsolation2kV(built-in)Signals CAN_H,CAN_L,CAN_GND,CAN_SHLD,CAN_V+,GNDDigital InputsConnector Screw-fastened Euroblock terminalDry Contact Off:openOn:short to GNDIsolation3K VDCSensor Type Wet contact(NPN)Dry contactWet Contact(DI to COM)On:10to30VDCOff:0to3VDCDigital OutputsConnector Screw-fastened Euroblock terminalCurrent Rating200mA per channelI/O Type SinkVoltage24VDC nominal,open collector to30VDCCellular InterfaceCellular Standards LTE Cat.4Band Options US Models:LTE Band2(1900MHz)/LTE Band4(1700MHz)/LTE Band5(850MHz)/LTE Band13(700MHz)/LTE Band17(700MHz)UMTS/HSPA850MHz/1900MHzCarrier Approval:Verizon,AT&TEU Models:LTE Band1(2100MHz)/LTE Band3(1800MHz)/LTE Band5(850MHz)/LTE Band7(2600MHz)/LTE Band8(900MHz)/LTE Band20(800MHz)UMTS/HSPA850MHz/900MHz/1900MHz/2100MHzAP Models:LTE Band1(2100MHz)/LTE Band3(1800MHz)/LTE Band5(850MHz)/LTE Band7(2600MHz)/LTE Band8(900MHz)/LTE Band28(700MHz)UMTS/HSPA850MHz/900MHz/1900MHz/2100MHzReceiver Types GPS/GLONASS/GalileoState-of-the-art GNSS solutionAccuracy Position:2.0m@CEP50Acquisition Hot starts:1.1secCold starts:29.94secSensitivity Cold starts:-145dBmTracking:-160dBmTime Pulse0.25Hz to10MHzLED IndicatorsSystem Power x2Programmable x1SIM card indicator x1Wireless Signal Strength Cellular/Wi-Fi x6Power ParametersNo.of Power Inputs Redundant dual inputsInput Voltage12to48VDCPower Consumption10WInput Current0.8A@12VDCReliabilityAlert Tools External RTC(real-time clock)Automatic Reboot Trigger External WDT(watchdog timer)Physical CharacteristicsDimensions UC-8220Models:141.5x120x39mm(5.7x4.72x1.54in)UC-8210Models:141.5x120x27mm(5.7x4.72x1.06in)141.5x120x27mm(5.7x4.72x1.06in)Weight UC-8210Models:560g(1.23lb)UC-8220Models:750g(1.65lb)Housing SECCMetalIP Rating IP30Installation DIN-rail mountingWall mounting(with optional kit)Environmental LimitsOperating Temperature-40to70°C(-40to158°F)Storage Temperature(package included)-40to85°C(-40to185°F)Ambient Relative Humidity5to95%(non-condensing)Shock IEC60068-2-27Vibration2Grms@IEC60068-2-64,random wave,5-500Hz,1hr per axis(without USB devicesattached)Standards and CertificationsEMC EN55032/35EN61000-6-2/-6-4EMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:4kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:10V/mIEC61000-4-4EFT:Power:2kV;Signal:1kVIEC61000-4-6CS:10VIEC61000-4-8PFMFIEC61000-4-5Surge:Power:0.5kV;Signal:1kV Industrial Cybersecurity IEC62443-4-1IEC62443-4-2Hazardous Locations Class I Division2ATEXIECExCarrier Approvals VerizonAT&TSafety UL62368-1EN62368-1Green Product RoHS,CRoHS,WEEEMTBFTime UC-8210-T-LX-S:708,581hrsUC-8220-T-LX:650,836hrsUC-8220-T-LX-US-S/EU-S/AP-S:528,574hrs Standards Telcordia(Bellcore)Standard TR/SRWarrantyWarranty Period5yearsDetails See /warrantyPackage ContentsDevice1x UC-8200Series computerDocumentation1x quick installation guide1x warranty cardInstallation Kit1x DIN-rail kit(preinstalled)1x power jack6x M2.5mounting screws for the cellular module Cable1x console cableDimensions UC-8210UC-8220Ordering Information12UC-8210-T-LX-SDefault:MIL1(-Debian9),2027EOLOrder WithModel UC-8210-T-LX-S(CTO):MIL3(Debian11)Secure/Standard,2031EOLWith MIL3Secure1GHzDual CoreBuilt in––-40to85°CUC-8220-T-LXDefault:MIL1(-Debian9),2027EOLOrder WithModel UC-8220-T-LX(CTO):MIL3(Debian11)Secure/Standard,2031EOLWith MIL3Secure1GHzDual CoreBuilt in Reserved Reserved-40to70°CUC-8220-T-LX-US-SDefault:MIL1(-Debian9),2027EOLOrder WithModel UC-8220-T-LX-US-S(CTO):MIL3(Debian11)Secure/Standard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inUS region LTEmodulepreinstalledReserved-40to70°CUC-8220-T-LX-EU-SDefault:MIL1(-Debian9),2027EOLOrder WithModel UC-8220-T-LX-EU-S(CTO):MIL3(Debian11)Secure/Standard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inEurope regionLTE modulepreinstalledReserved-40to70°CUC-8220-T-LX-AP-SDefault:MIL1(-Debian9),2027EOLOrder WithModel UC-8220-T-LX-AP-S(CTO):MIL3(Debian11)Secure/Standard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inAPAC regionLTE modulepreinstalledReserved-40to70°CUC-8210-T-LX-S(CTO)MIL3(Debian11)Secure orStandard,2031EOLWith MIL3Secure1GHzDual CoreBuilt in––-40to85°CUC-8220-T-LX(CTO)MIL3(Debian11)Secure orStandard,2031EOLWith MIL3Secure1GHzDual Core–Reserved Reserved-40to70°CUC-8220-T-LX-US-S (CTO)MIL3(Debian11)Secure orStandard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inUS region LTEmodulepreinstalledReserved-40to70°C12UC-8220-T-LX-EU-S (CTO)MIL3(Debian11)Secure orStandard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inEurope regionLTE modulepreinstalledReserved-40to70°CUC-8220-T-LX-AP-S (CTO)MIL3(Debian11)Secure orStandard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inAPAC regionLTE modulepreinstalledReserved-40to70°CAccessories(sold separately)Power AdaptersPWR-12150-EU-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,EU plug,-40to75°C operating temperature PWR-12150-UK-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,UK plug,-40to75°C operating temperature PWR-12150-USJP-SA-T Locking barrel plug,12VDC1.5A,100to240VAC,US/JP plug,-40to75°C operating temperature PWR-12150-AU-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,AU plug,-40to75°C operating temperature PWR-12150-CN-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,CN plug,-40to75°C operating temperature Power WiringCBL-PJTB-10Non-locking barrel plug to bare-wire cableCablesCBL-F9DPF1x4-BK-100Console cable with4-pin connector,1mWi-Fi Wireless ModulesUC-8200-WLAN22-AC Wireless package for UC-8200V2.0or later with Wi-Fi module,2screws,2spacers,1heat sink,1pad AntennasANT-LTEUS-ASM-01GSM/GPRS/EDGE/UMTS/HSPA/LTE,1dBi,omnidirectional rubber-duck antennaANT-LTE-ASM-04BK704to960/1710to2620MHz,LTE omnidirectional stick antenna,4.5dBiANT-LTE-OSM-03-3m BK700-2700MHz,multiband antenna,specifically designed for2G,3G,and4G applications,3m cable ANT-LTE-ASM-05BK704-960/1710-2620MHz,LTE stick antenna,5dBiANT-LTE-OSM-06-3m BK MIMO Multiband antenna with screw-fastened mounting option for700-2700/2400-2500/5150-5850MHzfrequenciesANT-WDB-ARM-02022dBi at2.4GHz or2dBi at5GHz,RP-SMA(male),dual-band,omnidirectional antennaDIN-Rail Mounting KitsUC-8210DIN-rail Mounting Kit DIN-rail mounting kit for UC-8210with4M3screwsUC-8220DIN-rail Mounting Kit DIN-rail mounting kit for UC-8220with4M3screwsWall-Mounting KitsUC-8200Wall-mounting Kit Wall-mounting kit for UC-8200with4M3screws©Moxa Inc.All rights reserved.Updated Jul18,2023.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

eterm自助培训-机型代码表

50-N/A 70-N/A 86-N/A 19-28 38-40 40-55 43-52 48-55 40-62 18-30 52-80 125-250 60-139 10--14

6--8 20-N/A 14-17 N/A-15 10--18 6--10 14-20 37-39 37-39

康纳戴尔区域喷气机 200 康纳戴尔区域喷气机 700 康纳戴尔区域喷气机 900 卡萨 C212/Nusantara NC-212 航空汽车 卡萨/Nusantara CN-235 康维尔 440/580/600/640 (货机) 康维尔 240/440/580 (客机) 康维尔 440 大都市(客机) 康维尔 580 客机 克提斯 C-46 突击机 波音公司(道格拉斯)DC-3 客机 波音公司(道格拉斯)DC-6B 客机 波音公司(道格拉斯)DC-8 客机 波音公司(道格拉斯)DC-9 客机 德夫康公司 德夫康公司 10/20/100/200/2000 德夫康公司 50/900 德.哈维兰公司 DHC-2 海狸/涡轮式海狸 德.哈维兰公司 DHC-4 驯鹿 英国宇航公司{德.哈维兰公司}飞鸽 英国宇航公司{德.哈维兰公司}苍鹭巢 德.哈维兰公司 DHC-3 涡轮式水獭 德.哈维兰公司 DHC-3 水猴/涡轮式水獭 德.哈维兰公司 DHC-2 海狸 德.哈维兰公司 DHC-3 水獭 德.哈维兰公司 DHC-6 双水獭 德.哈维兰公司 DHC-8 100 冲/BQ 德.哈维兰公司 DHC-8 200 冲/BQ

DH3 DH4 DH7 DH8 D1C D1F D1M D10 D11 D28 D3F D38 D6F D8F D8M D8X D8Y D9F D9S D91 D92 D93 D94 D96 EMB EMJ EM2 EQV

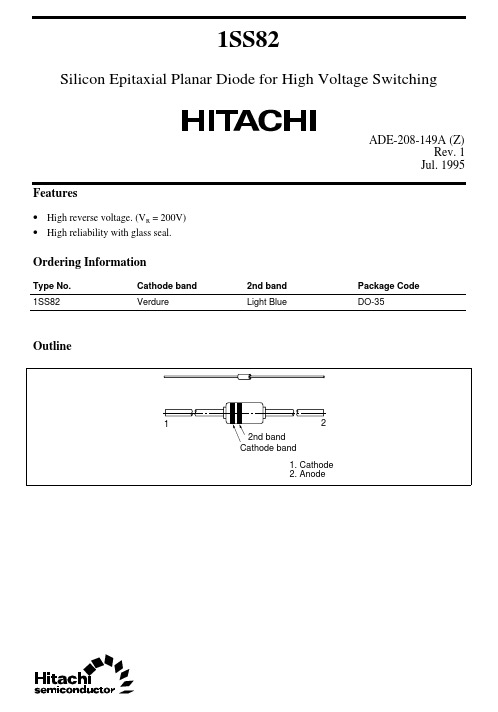

1SS82资料

1SS82Silicon Epitaxial Planar Diode for High Voltage SwitchingADE-208-149A (Z)Rev. 1Jul. 1995 Features• High reverse voltage. (V R = 200V)• High reliability with glass seal.Ordering InformationType No.Cathode band2nd band Package Code1SS82Verdure Light Blue DO-35Outline1SS822Absolute Maximum Ratings *2 (Ta = 25°C)ItemSymbol Value Unit Peak reverse voltage V RM *1250V Reverse voltage V R 200V Peak forward currentI FM 625mA Non-Repetitive peak forward surge current I FSM *21A Average forward current I O 200mA Power dissipation Pd 400mW Junction temperature Tj 175°C Storage temperatureTstg–65 to +175°CNotes: 1.Reverse voltage in excess of peak reverse voltage may deteriorate electrical characteristic.2.Within 1s forward surge current.Electrical Characteristics (Ta = 25°C)ItemSymbol Min Typ Max Unit Test Condition Forward voltage V F —— 1.0V I F = 100mA Reverse current I R1——0.2µAV R = 200V I R2——100V R = 250V CapacitanceC — 1.5—pF V R = 0V, f = 1MHzReverse recovery timet rr——100ns I F = I R = 30mA, Irr = 3mA, R L = 100Ω1SS82Fig.1 Forward current Vs. Forward voltageFig.2 Reverse current Vs. Reverse voltage31SS82Fig.3 Capacitance Vs. Reverse voltage 41SS82 Package Dimensions5Cautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.Hitachi Asia Pte. Ltd.16 Collyer Quay #20-00Hitachi TowerSingapore 049318Tel: 535-2100Fax: 535-1533URLNorthAmerica : http:/Europe : /hel/ecg Asia (Singapore): .sg/grp3/sicd/index.htm Asia (Taiwan): /E/Product/SICD_Frame.htm Asia (HongKong): /eng/bo/grp3/index.htm Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.Taipei Branch Office3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105)Tel: <886> (2) 2718-3666Fax: <886> (2) 2718-8180Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components)7/F., North Tower, World Finance Centre,Harbour City, Canton Road, Tsim Sha Tsui,Kowloon, Hong Kong Tel: <852> (2) 735 9218Fax: <852> (2) 730 0281 Telex: 40815 HITEC HXHitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 778322Hitachi Europe GmbHElectronic components Group Dornacher Stra§e 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:。

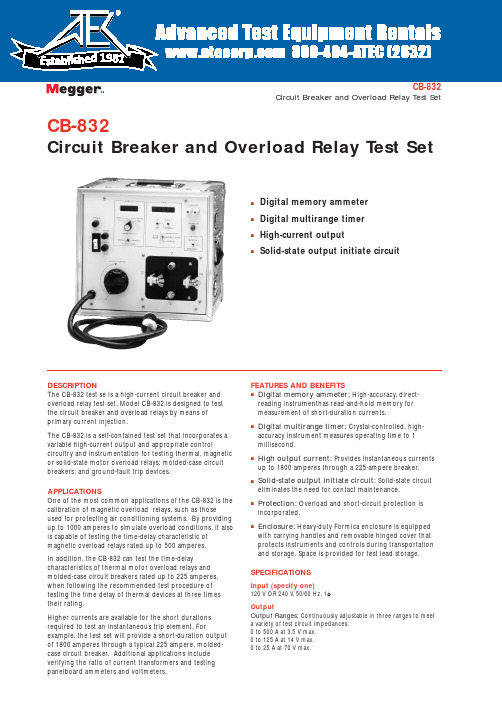

CB-832电路保护器和过载保护器测试装置I 数字内存电流表 I 数字多范围计时器 I 高电流输出

CB-832Circuit Breaker and Overload Relay Test SetsDigital memory ammeter sDigital multirange timer sHigh-current outputsSolid-state output initiate circuitCB-832Circuit Breaker and Overload Relay Test SetDESCRIPTIONThe CB-832 test se is a high-current circuit breaker and overload relay test set. Model CB-832 is designed to test the circuit breaker and overload relays by means of primary current injection.The CB-832 is a self-contained test set that incorporates a variable high-current output and appropriate controlcircuitry and instrumentation for testing thermal, magnetic or solid-state motor overload relays; molded-case circuit breakers; and ground-fault trip devices.APPLICATIONSOne of the most common applications of the CB-832 is the calibration of magnetic overload relays, such as thoseused for protecting air conditioning systems. By providing up to 1000 amperes to simulate overload conditions, it also is capable of testing the time-delay characteristic of magnetic overload relays rated up to 500 amperes.In addition, the CB-832 can test the time-delaycharacteristics of thermal motor overload relays and molded-case circuit breakers rated up to 225 amperes,when following the recommended test procedure of testing the time delay of thermal devices at three times their rating.Higher currents are available for the short durations required to test an instantaneous trip element. Forexample, the test set will provide a short-duration output of 1800 amperes through a typical 225 ampere, molded-case circuit breaker. Additional applications include verifying the ratio of current transformers and testing panelboard ammeters and voltmeters.FEATURES AND BENEFITSs Digital memory ammeter:High-accuracy, direct-reading instrumenthas read-and-hold memory for measurement of short-duration currents.sDigital multirange timer:Crystal-controlled, high-accuracy instrument measures operating time to 1millisecond.sHigh output current:Provides instantaneous currents up to 1800 amperes through a 225-ampere breaker.sSolid-state output initiate circuit:Solid-state circuit eliminates the need for contact maintenance.sProtection:Overload and short-circuit protection is incorporated.sEnclosure:Heavy-duty Formica enclosure is equipped with carrying handles and removable hinged cover that protects instruments and controls during transportation and storage. Space is provided for test lead storage.SPECIFICATIONSInput (specify one)120 V OR 240 V , 50/60 Hz, 1fOutputOutput Ranges:Continuously adjustable in three ranges to meet a variety of test circuit impedances:0 to 500 A at 3.5 V max.0 to 125 A at 14 V max.0 to 25 A at 70 V max.1981CB-832Circuit Breaker and Overload Relay Test SetOutput Capacity:The output circuit is designed to provide short-duration overloads.The output ranges will provide several times their current rating,provided the output voltage is sufficient to push the desired current through the impedance of the test circuit.The test set is capable of testing the time-delay characteristics of magnetic overload relays rated to 500 A using a test current of two times their rating (1000 A).avoid damage or overheating of the device under test while setting the test current.In the maintained mode, the output remains energized until manually turned off or, when performing timing tests, until the device under test operates—this both stops the timer and de-energizes the output.INSTRUMENTATIONAmmeterT o measure the output current, the test set incorporates a solid-state digital instrument with multiple ranges and a read-and-hold memory to measure short-duration currents.Operating Modes (switch-selected)Memory NormalDigital Display31/2digit, extra-bright LED display with 0.3-in. (7.62 mm) numerals Ranges (switch-selected)0 to 19.99/199.9/1999 A/3.00 kAContinuous Accuracy (overall ammeter system)±1% of reading, ±1 digit on three high ranges, ±1 digit on low range ±1% of rangeTimerA solid-state digital timer is incorporated to measure the elapsed time of the test in either seconds or cycles.It uses a crystal-controlled oscillator, therefore, its accuracy is independent of the line frequency.Display:5-digit, extra-bright LED display with 0.3 in. (7.62 mm)numeralsRanges (switch-selected)0 to 99.999 s 0 to 999.99 s 0 to 99999 cyclesAccuracy±0.005% of reading, ±1 digitTimer Control CircuitThis circuit automatically starts the timer when the output isenergized and automatically stops the timer and de-energizes the output when the device under test operates.This circuit accommodates the following test conditions by simple switch selection of the appropriate mode:Current Actuated:Used to test a device that has no auxiliary contacts to monitor, such as a single-pole circuit breaker. The timer stops when the output current is interrupted.Normally Closed:Used to test a device with normally closed contacts. The timer stops and the output is de-energized when the contacts open.Normally Open:Used to test a device with normally opencontacts. The timer stops and the output is de-energized when the contacts close.Dimensions14 H x 14.5 W x 13.4 D in.(356 H x 368 W x 343 D mm)Weight75 lb (34.1 kg)Overload CapabilityPercent Maximum Maximum Rated Time Time CurrentOnOff100 (1x)30 min 30 min 200 (2x) 3 min 8 min 300 (3x)30 s 4 min 400 (4x)7 s 2 minIt will test the time-delay characteristic of thermal devices rated up to 225 A using the recommended test current of three times their rating (675 A).Also, to perform an instantaneous trip test, it will provide 1800 A through a typical 225-ampere, molded-case circuit breaker.Overload Capability:T o increase use of the test set, it is designed so that the current ratings may be exceeded for short durations. Because the magnitude of the output current is determined by the impedance of the load circuit, the voltage rating must be sufficient to push the desired current through the device under test and the connecting test leads.Output Initiate Circuit:The test set uses a solid-state output initiating circuit. T o increase reliability and eliminate contact maintenance, this circuit uses a triac instead of a contactor to initiate the output.Output Initiate Control Circuit:The initiating control circuit provides momentary and maintained modes to control output duration.The momentary mode is used whenever the output is to be for a short duration. An example is an instantaneous trip test, or toUKArchcliffe Road Dover CT17 9EN EnglandT +44 (0) 1304 502101 F +44 (0) 1304 207342UNITED STATES 4271 Bronze WayDallas TX75237-1088 USA T 800 723 2861 (USA only) T +1 214 330 3203 F +1 214 337 3038OTHER TECHNICAL SALES OFFICES Valley Forge USA, Toronto CANADA,Mumbai INDIA, Trappes FRANCE,Sydney AUSTRALIA, Madrid SPAIN and the Kingdom of BAHRAIN.Registered to ISO 9001:2000 Reg no. Q 09290Registered to ISO 14001 Reg no. EMS 61597CB832_DS_en_V10Megger is a registered trademark。

飞龙 wi

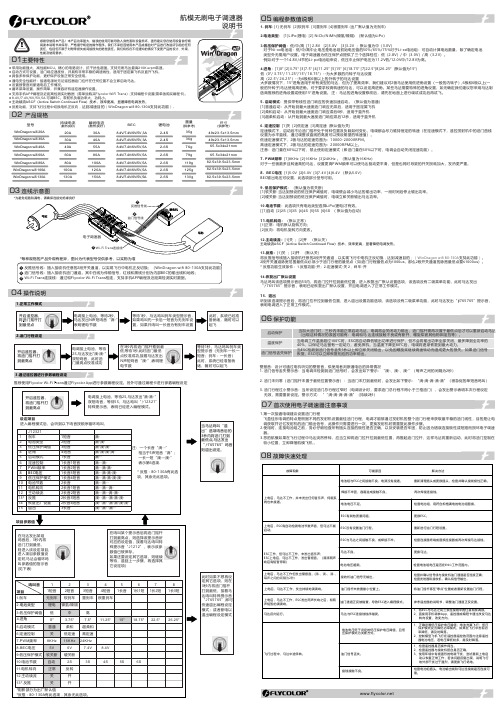

持续电流(散热良好)瞬间电流(散热良好)BEC尺寸(供参考)重量(供参考)20A 30A 40A 60A 30A 40A 55A 80A 锂电池型号79g 35g 36g 76g 49x23.5x13.5mm 65.5x34x21mm● 反推功能,支持飞行过程中切换电机正反向,达到减速目的(WinDragon wifi 80-130A 支持此功能)。

2-4S 2-4S 2-6S 2-6S 8.4V/7.4V/6V/5V ,5A 80A 100A 119g 2-6S 100A 120A 125g 2-6S 130A150A130g82.5x39.5x23.5mm2-6S航模无刷电子调速器WinDragon wifi 130AWinDragon wifi 100A WinDragon wifi 80A WinDragon wifi 60A WinDragon wifi 30A WinDragon wifi 40A WinDragon wifi 20A 8.4V/7.4V/6V/5V ,5A 8.4V/7.4V/6V/5V ,5A 8.4V/7.4V/6V/5V,5A8.4V/7.4V/6V/5V ,5A 82.5x39.5x23.5mm 82.5x39.5x23.5mm 65.5x34x21mm 49x23.5x13.5mm 02 产品规格04 操作说明1.正常工作模式2.油门行程设定3.通过遥控器进行参数编程设定推荐使用Flycolor Wi-Fi Trans 通过Flycolor App 进行参数编程设定。

另外可通过编程卡进行参数编程设定1. 刹车: [1] 无刹车 [2]软刹车 [3]重刹车 [4]很重刹车 (出厂默认值为无刹车)2.电池类型: [1]LiPo(锂电) [2] NiCb/NiMh(镍氢/镍隔) (默认值为Li Po )3.低压保护阈值:低/中/高 [1] 2.8V [2]3.0V [3]3.2V ;默认值为中(3.0V)对于Ni-xx电池组:低/中/高中止电压是电池组初始电压值的50%/65%/75%对于Li-xx电池组:可自动计算电池数量,除了确定电池 类型外无需用户设置。

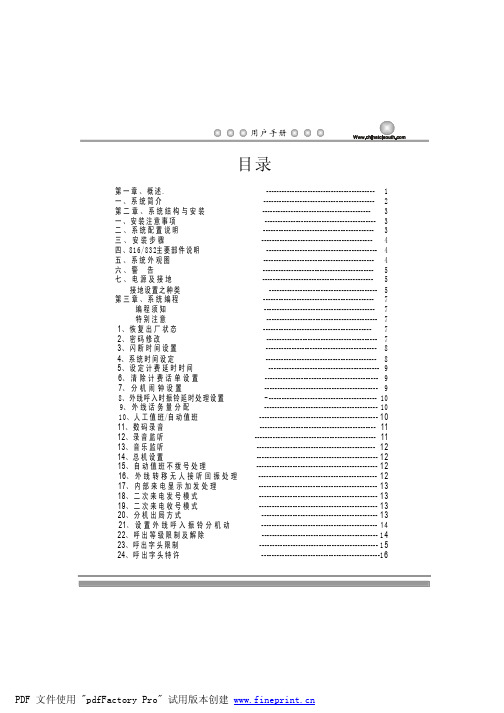

AF-832ID系列说明书内文090629

附录四、操作使用代码表

-------------------------------- 31

附录五、停电直通说明

-------------------------------- 32

附录六 、电话路 由选择 功能 --------------------------------- 32

附 录七 、P C计费 系 统 简 介

22

------------------------------- 22

--------------------------------- 22

------------------------------------- 22

---------------------------------- 22

-------------------------------- 23

----------------------------------------------- 12

----------------------------------------------- 12

---------------------------------------------- 12

---------------------------------------------- 13

-------------------------------- 23

-------------------------------- 24

--------------------------------- 24

------------------------------------------ 25

9、 外 线 话 务 量 分 配

卡特(Cat) PM820、PM822和PM825凝胶机械拉拔机说明文件

Cat® C18 ACERT™ EngineGross Power (ISO 14396)563 kW 755 hp Operating WeightPM820 36 130 kg 79,630 lb PM822 36 700 kg 80,887 lb PM825 37 500 kg 82,650 lb Cutting DimensionsWidth - PM820 2010 mm 79 in Width - PM822 2235 mm 88 in Width - PM825 2505 mm 98.8 in Maximum Cutting Depth 330 mm 13 inPM820, PM822 and PM825 Cold Planers2CONTENTSIntroduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2, 3Machine Feature Overview ....................4, 5Powertrain, Undercarriage ....................6, 7Operating Environment ........................8, 9Cutting System .............................10, 11Cat Grade Control Option ....................12, 13Material Collection System ..................14, 15Optional Equipment .........................16, 17Service and Reliability. . . . . . . . . . . . . . . . . . . . . . . 18, 19Cutting Bits ...................................20Cat Diamond Bits ..............................21Specifications ..............................22, 2323THE HIGH POWER HALF-LANE MILLING MACHINES YOU HAVE BEEN WAITING FORCat ® PM820, PM822 and PM825 cold planers are the product of years of study, tinkering, rethinking. Every system andcomponent has been examined, refined, optimized. The result is an advanced, world-class cold planer.The PM800 models are similar in design to their sister PM600 half lane cold planers...but they bring a lot more power, useful for the most demanding applications. The PM800 models deliver the same benefits as well: lowered operating costs and increased productivity, paired with Cat reliability and the legendary dealer support you expect from Caterpillar.The PM820, PM822 and PM825 are well equipped to deliver precision and efficient high production. Many options are available to enhance machine versatility and customize operations to suit the application, from milling highways to urban streets. Whether you are texturing the surface or milling an airport runway, there is a configuration that will meet your requirements and expectations.POWERFUL AND REFINEDPRECISION AND CONTROL WITH VERSATILITY TO SPARE.4938641011121413612457721. Cat C18 ACERT ™ Engine2. Ground Control Console3. Rear Water Fill Nozzle4. Remote Camera (option)5.Hydraulic Side Plates with Position Sensors6. Crawler Tracks with Bolt-on Pads7. Advanced Steering8. Dual Operating Consoles 9. Power Canopy (optional windscreens available, not shown)10. Dust Abatement System (option)11. High Pressure Water Spray Hose (option)12. Water Spray Control and Clean out Manifold13. LCD Touchscreen Display 14. Cat Diamond Bits (option)15. Cat Grade Control (option)515152744667891013142RUGGED POWERTRAIN SIMPLE DESIGN DELIVERS AMPLE POWER TO GROUND.C18 ACERT ENGINE– Meets regional emission standards as required:U.S. EPA Tier 4 Final / EU Stage IV– Provides a gross power of 563 kW (755 hp)– Automatic idle control function and multiple rotor speedsoptimizes output to the demand on the engine, keepingoperation smooth and efficient– High capacity cooling system keeps engine at idealtemperature for optimal fuel efficiency and lower emissions– Proven core engine design ensures reliability and quietoperation– Engine is iso-mounted to reduce noise and vibration6PROPEL SYSTEM– Robust propel system features two propel pumps and two propel circuits, diagonally opposed; each circuit drives the propel motors for two crawler tracks– Cross-flow traction control supplies dedicated hydraulic flowdiagonally across machine to the tracks that grip– Automatic Load Control senses load changes on the rotor system load and adjusts propel speed to prevent stalls and optimizeproduction7STABLE PLATFORM– Four leg posts with position sensors independently adjust and provide powered vertical movement to maintain desired height – Ride-control feature ensures smooth travel– Optional Cat Grade Control is integrated with the machine and works seamlessly to provide maximum cutting precision; system can be enhanced to full 3D milling capabilityWORRY-FREE TRACKS– Four crawler tracks based on proven Cat track design and components– Tracks automatically adjust to provide ideal tension – Track pads are easily replaceable with bolt-on designEXCELLENT MANEUVERABILITY– Four steering modes: front steer, rear steer, crab steer, coordinated steer– Advanced steering function adjusts track alignment to provide precise steering geometry and reduce pad wear – Minimum left cutting radius: 2 m (6.56 ft)– Minimum right cutting radius: PM820- 2 m (6.56 ft) PM822- 1.8 m (5.91 ft)PM825- 1.5 m (4.92 ft)The four post design offers excellent maneuverability and dependable operation to maximize versatility and production.8OPERATING ENVIRONMENT– Height-adjustable dual operating console is intuitive and comfortable– Optional power canopy can deploy or stow during machine operation; optional windscreen panels available– Touchscreen LCD display provides gauge cluster, operating information, remote camera feed, machine control anddiagnostics; optional second and third display available to provide additional gauge or machine operation/control information – Optional suspension seats reposition for optimal visibility and comfort– Lockable storage provides secure area to stow personal items – 12-volt power receptacleERGONOMIC CONTROLS– Controls comfortably positioned for easy use– Large, backlit keypads are visible in all light conditions – Durable design tested to 1 million cycles– Lockable covers provide protection from vandalismEQUIPPED FOR 24/7 OPERATION– Working areas and perimeter well lit with standard halogen lights – Displays and controls easy to see – Additional LED light options – Available balloon lighting optionsCOMFORT AND CONTROLOPERATE WITH CONFIDENCE.REAR910ROBUST ROTOR CHAMBER– Chamber optimizes material flow to promote thorough clean-out – Thicker steel in areas exposed to high abrasion enhances durability– Side plates are hydraulically adjustable with position-sensing cylinders, can be used as an averaging ski– Hydraulically adjustable moldboard applies optimal down-pressure to keep material contained for clean out and minimize required sweepingANTI-SLAB DEVICE– Helps to optimize sizing and gradation – Protects collecting conveyor– Prevents blockage in the discharge openingTHE VERSATILITY YOU NEED– Two available cutting widths; – Cutting depth to 330 mm (13 in)– Enhanced clearance for flush cutting– Three rotor speeds, electronically selectable during operation – High production and fine milling drums available – Optional Cat Grade Control keeps machine on targetCUTTING SYSTEMEFFICIENT AND DEPENDABLE, AS IT SHOULD BE.11ADVANCED AUTOMATED FEATURES– Automatic Load Control senses load changes on the rotor and adjusts propel speed to prevent stalls and optimize production– Automatic plunge-cut feature ensures precise, repeatable starting cuts and reduces wear on machine (requires Cat Grade Control option)– Ramp-in, Ramp-out cutting capability (requires Cat Grade Control option)– Jump hold feature assists to clear obstaclesROTOR DRIVE SYSTEM– Driven by two 6-rib high-tensile belts– Automatic belt tensioning to reduce slippage – Heavy-duty dry clutchHIGH PRODUCTION ROTORS– 2.0 m (79 in), 2.2 m (88 in) or 2.5 (98.6 in) cutting widths– Cutting bits held in exclusive conical quick-release tool holders and arranged in a triple-wrap flight pattern– Large, replaceable carbide-faced loading paddles effectively move milled material onto collecting conveyor– Standard 15 mm (0.6 in) tool tip spacing is optimal for high production and reduced wear– Triple tree tool arrangement on rotor ends reduces wear on rotor when maneuvering in the cut– Cat MasterGrade™ premium carbide bits available – Optional Cat Diamond Bits provide cutting life up to 80 times longer than conventional carbide bits, decreasing overall fuel consumption and reducing machine wear12INTEGRATED DESIGN– System communicates directly with position-sensing hydraulic cylinders, slope sensors and processors to ensure optimalprecisionCONTROL BOXES– LCD color touchscreen display with soft keys is durable andvisible in all light conditions– Intuitive interface is easy to understand and use– Supports multiple languages– Control boxes and sensors can be repositioned withoutreconfiguring settings– Full control over grade and slope can be attained from anycontrol boxCAT GRADE CONTROLEASY TO USE; HIGH PRECISION.BLUE: Averaged readings RED: Discarded readings1REFERENCE VERSATILITY1. Sonic Mounting Point2. Control Box Mounting Point3. Position-sensing Independently Controlled Side Plates4. Optional Position-sensing Hydraulically Controlled Inboard Ski2234SYSTEM VERSATILITY– System can utilize various references including sonics, contact sensors, position sensing hydraulic cylinders, wire rope sensors – Can be enhanced for full 3D operation– Sensors can be positioned in multiple inboard or external locations around the machineSONIC SENSORS– Sensor units feature five ceramic transducers– System discards the highest and lowest readings and averages remaining three for a true average– Each unit equipped with temperature sensor that compensates for fluctuations due to temperature change– Durable construction outlasts foil transducer design1113Each sensor has five transducers; the high and low readings are discarded and the remaining three are averaged for a true average reading.The high-capacity conveyors provide efficient removal of milled material and dust with outstanding discharge control.COLLECTING CONVEYOR– A wide opening and seamless 850 mm (33.5 in) wide belt efficiently clears rotor chamber– Reversible for easy clean out– Optional grease tensioner provides easy adjustment of belt alignment and tension WATER SPRAY SYSTEM– Water spray system provides lubrication and cools bits whilehelping to control dust– Spray system fed by 3400 L (898 gal) onboard tank; tank can be filled from top deck ports, rear fill valve, side fill valve or optional refill pump– Optional additional water spray system provides maximumlubrication, cooling and dust suppression– Onboard winterization system utilizes compressed air to purge water lines1415LOADING CONVEYOR– Aluminum covers and vinyl side panels reduce spillage and help control dust– Seamless 850 mm (33.5 in) wide belt provides heavy duty, high speed discharge– Variable belt speed optimizes speed to material type and production rate– Reversible for easy clean out– “Boost” feature provides a temporary surge in belt speed to help precisely place material– Loading conveyor folds to reduce length for transport– Loading conveyor swings 60 degrees from center position to the left or right60˚60˚OPTIONAL DUST ABATEMENT SYSTEM– Vacuum system ports to collecting conveyor housing and transition between collecting and loading conveyor to remove airborne particles– Augments dust suppression provided by water spray system – Discharges collected dust into the loading conveyor to facilitate removal from working area around machine – Maximizes dust removal capability when used with water spray system and optional additional water spray systemCAT GRADE AND SLOPE CONTROLSystem is integrated with the machine for maximum precision POWER SUN CANOPYDeploys or stows hydraulicallyWINDSCREENS FOR POWER SUN CANOPYCAT DIAMOND BITSLasts up to 80 times longer than conventional carbide bits ADDITIONAL LCD TOUCHSCREEN DISPLAYFor use to monitor machine functionsPRODUCT LINK, ADDITIONAL CONFIGURATIONSKeep track of your machine health, location or fleet use ADDITIONAL WATER SPRAY SYSTEMSecond system augments lubrication, bit cooling and dust suppression capabilities of the standard systemINBOARD AVERAGING SKIHydraulically controlled ski provides inboard reference for grade control systemROTOR TURNING DEVICEAssists with turning rotor during rotor serviceDUST ABATEMENT SYSTEMVacuum system ports to the transition area between the rotor chamber and the collecting conveyor as well as the transition between the collecting conveyor and the loading conveyor; dust is removed and expelled within the loading conveyor, where is it discharged with the milled materialREMOTE CAMERA, LOADING CONVEYORMounts to the discharge end of the loading conveyor; provides enhanced view of discharge loading REMOTE CAMERA, REARMounts to the rear of machine; provides enhanced view of area behind the machineREMOTE CAMERA, MAGNETIC MOUNTMounts magnetically to various locations; up to two magnetic cameras can be usedSUSPENSION SEATAdjustable seats installed on operator’s platformBIT BUCKET TRAYSTrays mount to rear crawlers and provide convenient storage for bit bucketsHIGH PRESSURE WASHDOWN SYSTEMHigh pressure hose and spray wand connect to onboard water tank to deliver high pressure water spray for convenient clean up WATER TANK TRANSFER PUMPWater pump provides additional options to fill onboard water tank FUEL TRANSFER PUMPFuel pump provides additional options to fill fuel tank WARNING BEACON, FIXEDAmber warning beacon mounts to one of two fixed locations on loading conveyor or rear of machineWARNING BEACON, MAGNETIC MOUNTAmber warning beacon can be magnetically mounted in multiple locations on the machineCOMMISSIONING SUPPORTCat technician provides machine introduction and training to key personnelOPTIONAL EQUIPMENT OPTIMIZE VERSATILITY, PRODUCTIVITY, COMFORT.161.Power Sun Canopy2. Inboard Averaging Ski3.Dust Abatement System4. Remote Camera, Loading Conveyor5.Remote Camera, Magnetic Mount6.Bit Bucket Trays7.High Pressure Washdown System8. Water Tank Transfer Pump3861245717EASY SERVICE DESIGNED RIGHT IN.Outstanding access to critical components and systems makes service and maintenance easier and faster. That keeps your machine where you need it: on the job.LARGE ACCESS DOORS AND PANELS– Designed to facilitate efficient service, reducing labor costs and service time– Quick and easy maintenance– Accessible pumps and components– Power hood opens to allow walk-in access– Visual indicators simplify routine service checks18HYDRAULIC SYSTEM– Manual overrides simplify troubleshooting by eliminatingfunctioning systems– Hydraulic hoses are cleanly routed and clamped for long-term reliability– Exposed hoses are wrapped in nylon sleeves for protectionagainst abrasion– Pressure test ports and oil sampling ports simplify hydraulicsystem diagnosisELECTRICAL SYSTEM– 24-volt system with 100 amp alternator– Color-coded and numbered electrical wiring simplifiestroubleshooting– Harnesses are wrapped in abrasion-resistant nylon braid ELECTRONIC CONTROL MODULES (ECM)– Monitors machine systems to ensure proper function andprecision– Provides warning indications via LCD touchscreen display when machine performance is substandard– Provides diagnostic information TELEMATICS: PRODUCT LINK™– Maximize up-time– Automatic machine location– Hour updates– Diagnostic codes– Schedule service at convenient times– Optional configurations availableLONG SERVICE INTERVALS– 500 hour engine oil service interval– 3,000 hour hydraulic oil service interval without oil sampling;6,000 hours with oil samplingACCESSORY DRIVE SYSTEM– Provides full operational control of auxiliary machine functions to enable assisted machine movement during maintenance or service– Facilitates assisted relocation of machine from live construction area to service area during emergency situations19Pallet ConcreteAsphalt or Asphalt off ConcreteAsphaltShallow 25 - 50 mm (1” - 2”)Moderate 75 - 125 mm (3” - 5”)Deep 150 mm (6” o r more)Puller Tool351-267844444292-510344444349-49464444316-23274444350-71994444Ø19.4Ø19.822182117217PROVEN BENEFITSMore efficiency, more productivity, lower fuel consumption and less wear on the machine. It all adds up to more profitability and growth for your company.– Last up to 80x longer than carbide tips, keeping crews more productive, month after month– Assure faster project completions– Provide you with a significant bidding advantage– Virtually eliminate labor costs for pick changes; eliminate unplanned, unproductive interruptions– Deliver proven fuel savings per ton of production– Enable faster milling speeds and increased productivity– Eliminate costly bit inventory, and the handling that goes with it– Require no rotation, crucial because half of carbide failures result when tools fail to turn– Create less vibration, increasing the life of planetaries, drive shafts, stub shafts, bearings and other parts and components– Increase track-pad life because the machine does not work as hard– Deliver a dramatically improved return on your mill investment through increased engagement– Extend life of moldboards through a consistent pattern; protect welded-on base blocks—and ultimately the drum Average life and exact tonnage is impacted by local aggregate and operating technique. Diamond Asphalt Bits last up to 45x the life of standard carbide bits and Diamond Extended Life Bits last up to 80x the life of standard carbide bits.STAY SHARP UP TO 80X CONVENTIONAL CARBIDE.2122SPECIFICATIONSHH23Weights shown are approximate and include:• Operating weights include coolants, lubricants, full fuel tank, full water tank and 75 kg (165 lb) operator.• Transport weights include coolants, lubricants, 50% full fuel tank and empty water tank.WeightPM820Operating weight 36 130 kg 79,630 lb Transport weight 32 230 kg71,035 lbPM822Operating weight 36 700 kg 80,887 lb Transport weight 32 800 kg 72,290 lbPM825Operating weight 37 500 kg 82,650 lb Transport weight33 600 kg 74,054 lbFuel Tank1108 L 288.1 gal Cooling System 104 L 27.5 gal Engine Oil 65 L 16.9 gal Hydraulic Oil 113 L 29.4 gal Water Tank3400 L898 galService Refill CapacitiesCat C18 ACERT Engine Gross power - ISO 14396 563 kW 755 hp Global emissions US EPA Tier 4 Final / EU Stage IVor Tier 3 / Stage IIIA / China Stage III equivalentOperating speed100 m/min 328 ft/min Maximum travel speed 5.9 km/h 3.7 mphPowertrainPM820 Milling Width2010 mm 79.1 in Number of Bits 170PM822 Milling Width 2235 mm 88 in Number of Bits 185PM825 Milling Width 2505 mm 98.6 in Number of Bits203Maximum Cutting Depth 330 mm 13 in Rotor Speeds100 / 109 / 118 rpmCutting SystemPower CanopyWindscreens for Power Canopy Inboard Averaging Ski CE CertificateAdditional Water Spray System Water Tank Transfer Pump Fuel Transfer Pump Dust Abatement System Cat Grade ControlRemote Camera (Front, Rear, or Magnet Mount)Product Link (optional configuration)Air-ride Operator’s Seats Drum Rotating Device Cat Diamond Bits Bit Bucket TraysMachine Commissioning SupportOptional EquipmentSPECIFICATIONSA Overall length, conveyor up14.52 m 47.62 ft B Maximum machine width - PM820, PM822 2.83 m 9.27 ft Maximum machine width - PM825 3.14 m 10.03 ft C Cutting width - PM820 2010 mm 79.1 in Cutting width - PM822 2235 mm 88 in Cutting width - PM8252505 mm 98.6 in D Maximum height, raised conveyor 5.23 m 17.17 ft E Height to optional canopy4.05 m 13.29 ft F Height, no canopy (canopy down) 3.00 m 9.84 ft G Maximum truck clearance 4.86 m 15.95 ft HConveyor swing± 60˚ from centerOperating DimensionsI Transport length12.43 m 40.79 ft J Transport width - PM820 2.50 m 8.2 ft Transport width - PM822 2.70 m 8.83 ft Transport width - PM825 3.01 m 9.88 ft K Length, track to track 6.69 m 21.95 ft L Length of base machine 8.33 m 27.33 ft FTransport height3.00 m 9.84 ftShipping DimensionsPM820, PM822 AND PM825 Cold Planers。

NUC微控制器产品系列说明书

M251 Feature

。 Arm® Cortex®-M23 。 运行速度可达 48 MHz

M252 Feature

。 USB 2.0 全速设备无需外 挂晶振

M253 Feature

。 USB 2.0 全速设备无需外 挂晶振

。 高达五路 UART 。 CAN FD x1

2

Low Power

TrustZone

AEC-Q100

Market Trend

随着电子应用对低功耗或电池供电的需 求日益增加,现今的应用必须尽量降低 能源消耗,甚至在极端情况下,可能需 要倚赖单颗电池来维持长达 15 至 20 年 运转

低功耗应用情景包含手持式设备、居家、 AIoT、IIoT (工业物联网) 等应用情景, 使用范围十分广泛

(Programmable Serial I/O) • USB 2.0 全速装置无需外挂晶振 • 独立的 RTC 电源 VBAT 管脚

Highlight

• 支持 1.8 V ~ 5.5 V 串行接口,可连接不同电压 装置

*USCI: Universal Serial Control Interface Controller

C

1.8 3.3 5 M253

CU

3.3 5 M071

1.8 3.3 5 M252

U

3.3 5 M051

1.8 3.3 5 M251

3.3 5 Mini51

3.3 5 3.3 5

1.8 3.3 Nano100

M480 M460 M471 M453 M452 M451

E CU E CU

U C

U

Arm9™

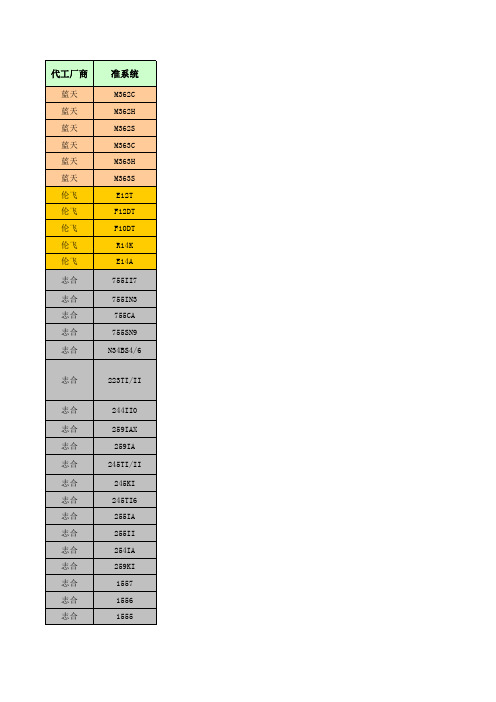

神舟准系统大全

蓝天 蓝天 蓝天 蓝天 蓝天 蓝天 伦飞 伦飞 伦飞 伦飞 伦飞 志合 志合 志合 志合 志合

准系统

M362C M362H M362S M363C M363H M363S E12T F12DT F10DT R14K E14A 755II7 755IN3 755CA 755,P182C,P240C,P210C,P210D 优雅Q300C、Q300P 优雅Q300S、Q300T、Q310S 优雅Q320N、Q320Y、Q320R、Q330R 承动L206T、L208E、L208T 承动F213E、F213T、F520E 天运F525R、 F237S 天运F525S、F525R、F237S 天运F420S、F430S、F440S、F520S、F225S、F205S、F206S、F208S、F506R 、Q420S、Q440S 天运L205S、L208R、L213R、L225R、L420S、L430S、L440R、L550S、L560R 优雅W220N、W220S、W220R、W225R、W420R、W430S、W440S 承运W280T、W300A、W280A 优雅HP510 优雅W230N、W230R、W230S 优雅HP260、HP280 、 W230N D5/D6 天运 Q530C、Q530S、Q540C、Q540X、Q540S、Q540C、Q550C、Q550S、F1400、Q1400、F5500、F233S、 F233R、F555S、F725S、F4000 天运F1500、F237S、F555R ; 天运F5600、F5700 承运F233T、F213T、F237T、F545T、F810T 承运F200T、F320T、F340T、F420T 天运 F4200 D2、F6400 D2 天运L1400、L1500、L1600、L3200、L5500、L4000 优雅 W240N、W240R、HP280 F3000 D6/D7 、 天运 F5800、F7300、F6400、F4200 承运F340T、F580T、F640T 优雅 Q120、Q130 承运B730G、B730S、B740G、B370S、B360S 承运W370T、W740T、W750T 优雅HP500、HP520、HP420、HP410 ;天运F5600、F5700 优雅HP500、HP520、HP800 优雅HP600、HP620、HP900、HP930 优雅 HP530、HP540、HP550、HP560、HP650、HP660、HP680 承运L420T、L840T、优雅HP740、HP760、HP840、HP860、HP870、HP880 优雅 U10R、U20R、U10T、U10V

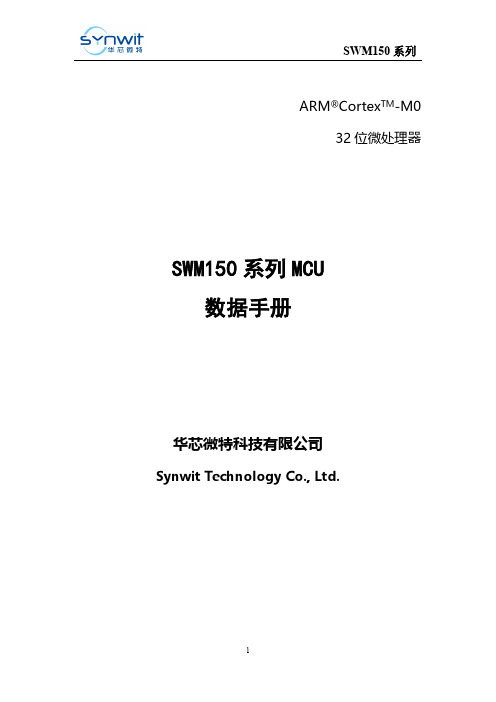

华芯微特科技有限公司 SWM150 系列 ARM Cortex-M0 32 位微处理器数据手册说明书

ARM®Cortex TM-M032位微处理器SWM150系列MCU数据手册华芯微特科技有限公司Synwit Technology Co., Ltd.目录1概述 (5)2特性 (5)3选型指南 (6)4功能方框图 (7)5管脚配置 (8)5.1TQFP48 (8)5.2LQFP64 (9)5.3管脚描述 (9)6功能描述 (13)6.1存储器映射 (13)6.2中断控制器 (15)6.3系统定时器 (20)6.4系统控制器 (21)6.5系统管理(SYSCON) (23)6.6通用I/O(GPIO) (49)6.7通用型定时器(TIMER) (55)6.8专用定时器(TIMERSE) (58)6.9看门狗定时器(WDT) (64)6.10UART接口控制器(UART) (67)6.11串行外设接口(SPI)控制器 (75)6.12脉冲宽度调制(PWM)发生器 (89)6.13模拟数字转换器(ADC) (101)6.14正交编码器(QEI) (110)6.15比较器/放大器(CMP) (119)6.16ISP及FLASH操作 (123)7典型应用电路 (125)8电气特性 (125)8.1绝对最大额定值 (125)8.2DC电气特性 (125)8.3AC电气特性 (126)8.4模拟器件特性 (127)9封装信息 (128)9.1TQFP48 (128)9.2LQFP64 (129)10版本记录 (130)图目录图4-1功能方框图 (7)图5-1 LQFP64封装管脚配置 (8)图5-2 LQFP64封装管脚配置 (9)图6-2 I/O引脚示意图 (26)图6-3 FLASH接口示意图 (27)图6-4 端口E滤波示意图 (50)图6-5 脉冲捕捉示意图 (59)图6-6 占空比捕捉示意图 (60)图6-7 UART结构图 (67)图6-8 串行数据格式 (68)图6-9 UART配置流程 (68)图6-10 SPI单个数据传输帧格式(SCPH=0) (77)图6-11 SPI连续数据传输帧格式(SCPH=0) (77)图6-12 SPI单个数据传输帧格式(SCPH=1) (78)图6-13 SPI连续数据传输帧格式(SCPH=1) (78)图6-14 Microwire不连续数据传输帧格式(不连续读数据) (79)图6-15 Microwire连续数据传输帧格式(连续读数据) (79)图6-16 Microwire单个数据传输帧格式(写数据) (80)图6-17 SSP单个数据传输帧格式 (80)图6-18 SSP多个数据连续传输帧格式 (80)图6-19 PWM结构示意图 (90)图6-20 死区发生示意图 (91)图6-21 PWM普通模式波形示意图 (91)图6-22 未开启死区的互补模式 (92)图6-23 开启死区的互补模式 (92)图6-24 中心对称模式 (93)图6-25 ADC结构示意图 (102)图6-26 ADC中断示意图 (104)图6-27 增量式正交编码盘示意图 (110)图6-28 三相信号正向/反向旋转时序关系 (111)图6-29 QEI结构示意图 (111)图6-30 x4计数模式 (112)图6-31 x2计数模式 (112)图6-32 可编程数字噪声滤波器结构框图 (113)图6-33 信号通过滤波器传播 (113)图6-34 索引复位模式 (113)图6-35 计数匹配复位模式 (114)图6-36 比较器/放大器结构示意图 (119)图7-1 典型应用电路图 (125)图9-1 TQFP48封装 (128)图9-2 LQFP64封装 (129)表格目录表格3-1 SWM240系列MCU选型表 (6)表格6-2 中断编号及对应外设 (15)表格8-1绝对最大额定值 (125)表格8-2 DC电气特性( Vdd-Vss = 3.3V, Tw =25℃) (125)表格8-3 内部振荡器特征值 (126)表格8-4 SAR ADC特征值 (127)表格8-5 比较器/放大器特性 (127)1概述SWM150系列MCU是基于ARM® Cortex TM-M0的32位微控制器。

832A中文资料

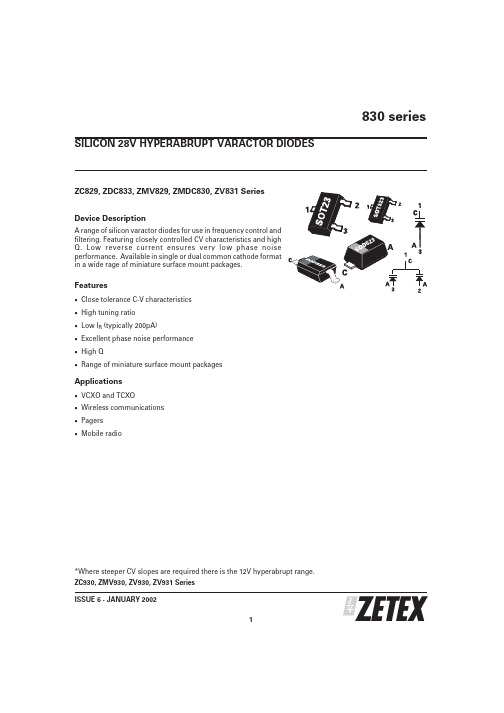

ZC829, ZDC833, ZMV829, ZMDC830, ZV831 Series Device DescriptionA range of silicon varactor diodes for use in frequency control and filtering.Featuring closely controlled CV characteristics and high Q.Low reverse current ensures very low phase noise performance.Available in single or dual common cathode format in a wide rage of miniature surface mount packages.Features·Close tolerance C-V characteristics ·High tuning ratio ·Low I R (typically 200pA)·Excellent phase noise performance ·High Q·Range of miniature surface mount packagesApplications·VCXO and TCXO·Wireless communications ·Pagers ·Mobile radio*Where steeper CV slopes are required there is the 12V hyperabrupt range.ZC930, ZMV930, ZV930, ZV931 Series 830 seriesISSUE 6 - JANUARY 20021SILICON 28V HYPERABRUPT VARACTOR DIODES830 seriesISSUE 6 - JANUARY 20022PARTCapacitance (pF)V R =2V,f=1MHzMin Q V R =3V f=50MHzCapacitance RatioC 2/C 20at f=1MHzMIN.NOM.MAX.MIN.MAX.829A 7.388.29.02250 4.3 5.8829B 7.798.28.61250 4.3 5.8830A 9.010.011.0300 4.5 6.0830B 9.510.010.5300 4.5 6.0831A 13.515.016.5300 4.5 6.0831B 14.2515.015.75300 4.5 6.0832A 19.822.024.2200 5.0 6.5832B 20.922.023.1200 5.0 6.5833A 29.733.036.3200 5.0 6.5833B 31.3533.034.65200 5.0 6.5834A 42.347.051.7200 5.0 6.5834B 44.6547.049.35200 5.0 6.5835A 61.268.074.8100 5.0 6.5835B 64.668.071.4100 5.0 6.5836A 90.0100.0110.0100 5.0 6.5836B95.0100.0105.0100 5.06.5TUNING CHARACTERISTICS at Tamb = 25°CPARAMETER SYMBOLMAX UNIT Forward currentI F 200mA Power dissipation at T amb =25ЊC SOT23P tot 330mW Power dissipation at T amb =25ЊC SOD323P tot 330mW Power dissipation at T amb =25ЊC SOD523P tot250mW Operating and storage temperature range-55to +150ЊCABSOLUTE MAXIMUM RATINGSPARAMETERCONDITIONS MIN.TYP.MAX.UNIT Reverse breakdown voltage I R =10uA 25V Reverse voltage leakageV R =20V 0.220nA Temperature coefficient of capacitanceV R =3V,f =1MHz300400ppCm/ЊCELECTRICAL CHARACTERISTICS at Tamb = 25°C830 seriesTYPICAL CHARACTERISTICSISSUE 6 - JANUARY 20023830 seriesISSUE 6 - JANUARY 20024O R D E R C O D E S A N D P A R T M A R K I N GR E E L C O D ER E E L S I Z ET A P E W I D T HQ U A N T I T Y P E R R E E LT A7i n c h (180m m )8m m3000T C13i n c h (330m m )8m m 10000T A P E A N D R E E L I N F O R M A T I O NT h e o r d e r c o d e s a r e s h o w n a s T A w h i c h i s f o r 7i n c h r e e l s .F o r 13i n c h r e e l s s u b s t i t u t e T C i n p l a c e o f T A i n t h e o r d e r c o d e .ISSUE 6 - JANUARY 20025830 seriesSOT23 PACKAGE DIMENSIONSSOD323 PACKAGE DIMENSIONSZetex plcFields New Road ChaddertonOldham, OL9 8NP United KingdomTelephone (44) 161 622 4422Fax: (44) 161 622 4420Zetex GmbHStreitfeldstraße 19D-81673 München GermanyTelefon: (49) 89 45 49 49 0Fax: (49) 89 45 49 49 49Zetex Inc700 Veterans Memorial Hwy Hauppauge, NY11788USATelephone: (631) 360 2222Fax: (631) 360 8222Zetex (Asia) Ltd3701-04Metroplaza, Tower 1Hing Fong Road Kwai Fong Hong KongTelephone: (852) 26100 611Fax: (852) 24250 494These offices are supported by agents and distributors in major countries world-wide.This publication is issued to provide outline information only which (unless agreed by the Company in writing)may not be used,applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned.The Company reserves the right to alter without notice the specification,design,price or conditions of supply of any product or service.For the latest product information,log on to©Zetex plc 2001830 series6ISSUE 6 - JANUARY 2002DIM MILLIMETRES MIN.MAX A ᎏ0.800A10.0000.100A20.6000.800b10.1600.300c 0.0800.220D 0.7000.900E 1.500 1.700E1 1.100 1.300L 0.2000.400L10.1700.230⍜1Њ4Њ10ЊSOD523 PACKAGE DIMENSIONSSOD323 PACKAGE DIMENSIONS。

GS832272C-250I资料

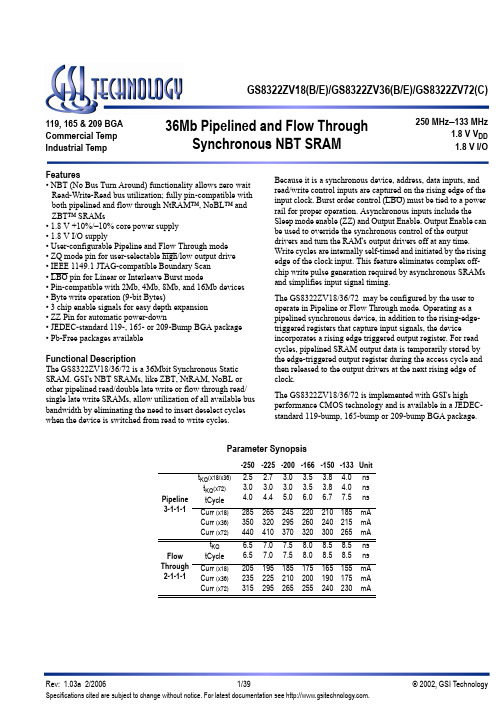

PreliminaryGS832218(B/E)/GS832236(B/E)/GS832272(C)2M x 18, 1M x 36, 512K x 7236Mb S/DCD Sync Burst SRAMs250 MHz –133 MHz 2.5 V or 3.3 V V DD 2.5 V or 3.3 V I/O119-, 165-, & 209-Pin BGA Commercial Temp Industrial Temp Features• FT pin for user-configurable flow through or pipeline operation • Single/Dual Cycle Deselect selectable• IEEE 1149.1 JTAG-compatible Boundary Scan• ZQ mode pin for user-selectable high/low output drive • 2.5 V +10%/–10% core power supply • 3.3 V +10%/–10% core power supply • 2.5 V or 3.3 V I/O supply• LBO pin for Linear or Interleaved Burst mode• Internal input resistors on mode pins allow floating mode pins • Default to SCD x18/x36 Interleaved Pipeline mode • Byte Write (BW) and/or Global Write (GW) operation • Internal self-timed write cycle• Automatic power-down for portable applications• JEDEC-standard 119-, 165-, and 209-bump BGA packageFunctional DescriptionApplicationsThe GS832218/36/72 is a 37,748,736-bit high performancesynchronous SRAM with a 2-bit burst address counter. Although of a type originally developed for Level 2 Cache applications supporting high performance CPUs, the device now finds application in synchronous SRAM applications, ranging from DSP main store to networking chip set support.ControlsAddresses, data I/Os, chip enable (E1), address burst control inputs (ADSP, ADSC, ADV), and write control inputs (Bx, BW, GW) are synchronous and are controlled by a positive-edge-triggered clock input (CK). Output enable (G) and power down control (ZZ) are asynchronous inputs. Burst cycles can be initiated with either ADSP or ADSC inputs. In Burst mode, subsequent burst addresses are generated internally and are controlled by ADV. The burst address counter may be configured to count in either linear or interleave order with the Linear Burst Order (LBO) input. The Burst function need not be used. New addresses can be loaded on every cycle with no degradation of chip performance.Flow Through/Pipeline ReadsThe function of the Data Output register can be controlled by the user via the FT mode . Holding the FT mode pin low places the RAM in Flow Through mode, causing output data to bypass the Data Output Register. Holding FT high places the RAM inPipeline mode, activating the rising-edge-triggered Data Output Register.SCD and DCD Pipelined ReadsThe GS832218/36/72 is a SCD (Single Cycle Deselect) and DCD (Dual Cycle Deselect) pipelined synchronous SRAM. DCD SRAMs pipeline disable commands to the same degree as read commands. SCD SRAMs pipeline deselect commands one stage less than read commands. SCD RAMs begin turning off their outputs immediately after the deselect command has been captured in the input registers. DCD RAMs hold the deselect command for one full cycle and then begin turning off their outputs just after the second rising edge of clock. The user may configure this SRAM for either mode of operation using the SCD mode input.Byte Write and Global WriteByte write operation is performed by using Byte Write enable (BW) input combined with one or more individual byte write signals (Bx). In addition, Global Write (GW) is available for writing all bytes at one time, regardless of the Byte Write control inputs.FLXDrive™The ZQ pin allows selection between high drive strength (ZQ low) for multi-drop bus applications and normal drive strength (ZQ floating or high) point-to-point applications. See the Output Driver Characteristics chart for details.Core and Interface VoltagesThe GS832218/36/72 operates on a 2.5 V or 3.3 V power supply. All input are 3.3 V and 2.5 V compatible. Separate output power (V DDQ ) pins are used to decouple output noise from the internal circuits and are 3.3 V and 2.5 V compatible.Parameter Synopsis-250-225-200-166-150-133UnitPipeline 3-1-1-1KQ t KQ (x72)tCycle 3.04.0 3.04.4 3.05.0 3.56.0 3.86.7 4.07.5ns ns Curr (x18)Curr (x36)Curr (x72)285350440265320410245295370220260320210240300185215265mA mA mA Flow Through 2-1-1-1t KQ tCycle 6.56.57.07.07.57.58.08.08.58.58.58.5ns ns Curr (x18)Curr (x36)Curr (x72)205235315195225295185210265175200255165190240155175230mA mA mA209-Bump BGA—x72 Common I/O—Top View (Package C)1234567891011A DQ G DQ G A E2ADSP ADSC ADV E3A DQB DQ B AB DQ G DQ G BC BG NC BW A BB BF DQ B DQ B BC DQ G DQ G BH BD NC E1NC BE BA DQ B DQ B CD DQ G DQ G V SS NC NC G GW NC V SS DQ B DQ B DE DQP G DQP C V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQPF DQP B EF DQ C DQ C V SS V SS V SS ZQ V SS V SS V SS DQ F DQ F FG DQ C DQ C V DDQ V DDQ V DD MCH V DD V DDQ V DDQ DQ F DQ F GH DQ C DQ C V SS V SS V SS MCL V SS V SS V SS DQ F DQ F H J DQ C DQ C V DDQ V DDQ V DD MCL V DD V DDQ V DDQ DQ F DQ F J K NC NC CK NC V SS MCL V SS NC NC NC NC K L DQ H DQ H V DDQ V DDQ V DD FT V DD V DDQ V DDQ DQ A DQ A L M DQ H DQ H V SS V SS V SS MCL V SS V SS V SS DQ A DQ A M N DQ H DQ H V DDQ V DDQ V DD SCD V DD V DDQ V DDQ DQ A DQ A N P DQ H DQ H V SS V SS V SS ZZ V SS V SS V SS DQ A DQ A P R DQP D DQP H V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQP A DQP E R T DQ D DQ D V SS NC NC LBO NC NC V SS DQ E DQ E T U DQ D DQ D NC A A A A A A DQ E DQ E U V DQ D DQ D A A A A1A A A DQ E DQ E V W DQ D DQ D TMS TDI A A0A TDO TCK DQ E DQ E W11 x 19 Bump BGA—14 x 22 mm2 Body—1 mm Bump PitchGS832272 209-Bump BGA Pin DescriptionSymbol Type DescriptionA0, A1I Address field LSBs and Address Counter Preset Inputs.An I Address InputsDQ ADQ BDQ CDQ DDQ EDQ FDQ GDQ HI/O Data Input and Output pinsB A, B B I Byte Write Enable for DQ A, DQ B I/Os; active lowB C,B D I Byte Write Enable for DQ C, DQ D I/Os; active lowB E, B F, B G,B H I Byte Write Enable for DQ E, DQ F, DQ G, DQ H I/Os; active lowNC—No ConnectCK I Clock Input Signal; active highGW I Global Write Enable—Writes all bytes; active lowE1I Chip Enable; active lowE3I Chip Enable; active lowE2I Chip Enable; active highG I Output Enable; active lowADV I Burst address counter advance enable; active low ADSP, ADSC I Address Strobe (Processor, Cache Controller); active low ZZ I Sleep Mode control; active highFT I Flow Through or Pipeline mode; active lowLBO I Linear Burst Order mode; active lowSCD I Single Cycle Deselect/Dual Cycle Deselect Mode Control MCH I Must Connect HighMCL Must Connect LowBW I Byte Enable; active lowZQ IFLXDrive Output Impedance Control(Low = Low Impedance [High Drive], High = High Impedance [Low Drive])TMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test ClockV DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS832272 209-Bump BGA Pin Description (Continued)SymbolTypeDescription165-Bump BGA—x18 Commom I/O—Top View (Package E)1234567891011A NC A E1BB NC E3BW ADSC ADV A A AB NC A E2NC BA CK GW G ADSP A NC BC NC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPA CD NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA DE NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA EF NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA FG NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA GH FT MCL NC V DD V SS V SS V SS V DD NC ZQ ZZ H J DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC J K DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC K L DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC L M DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC M N DQPB SCD V DDQ V SS NC A NC V SS V DDQ NC NC N P NC NC A A TDI A1TDO A A A A P R LBO A A A TMS A0TCK A A A A R11 x 15 Bump BGA—15 mm x 17 mm Body—1.0 mm Bump Pitch165-Bump BGA—x36 Common I/O—Top View (Package E)1234567891011A NC A E1BC BB E3BW ADSC ADV A NC AB NC A E2BD BA CK GW G ADSP A NC BC DQPC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPB CD DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB DE DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB EF DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB FG DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB GH FT MCL NC V DD V SS V SS V SS V DD NC ZQ ZZ H J DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA J K DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA K L DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA L M DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA M N DQPD SCD V DDQ V SS NC A NC V SS V DDQ NC DQPA N P NC NC A A TDI A1TDO A A A A P R LBO A A A TMS A0TCK A A A A R11 x 15 Bump BGA—15 mm x 17 mm Body—1.0 mm Bump PitchGS832218/36 165-Bump BGA Pin DescriptionSymbol Type DescriptionA0, A1I Address field LSBs and Address Counter Preset InputsAn I Address InputsDQ ADQ BDQ CDQ DI/O Data Input and Output pinsB A, B B, B C, B D I Byte Write Enable for DQ A, DQ B, DQ C, DQ D I/Os; active low (x36 Version)NC—No ConnectCK I Clock Input Signal; active highBW I Byte Write—Writes all enabled bytes; active lowGW I Global Write Enable—Writes all bytes; active lowE1I Chip Enable; active lowE3I Chip Enable; active lowE2I Chip Enable; active highG I Output Enable; active lowADV I Burst address counter advance enable; active l0w ADSC, ADSP I Address Strobe (Processor, Cache Controller); active low ZZ I Sleep mode control; active highFT I Flow Through or Pipeline mode; active lowLBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance Control (Low = Low Impedance [High Drive], High = High Impedance [LowDrive])TMS I Scan Test Mode SelectTDI I Scan Test Data InTDO O Scan Test Data OutTCK I Scan Test ClockMCL—Must Connect Low SCD—Single Cycle Deselect/Dual Cyle Deselect Mode Control V DD I Core power supplyV SS I I/O and Core GroundV DDQ I Output driver power supply119-Bump BGA—x36 Common I/O—Top View1234567A V DDQ A A ADSP A A V DDQ AB NC A A ADSC A A NC BC NC A A V DD A A NC CD DQ C DQP C V SS ZQ V SS DQP B DQ B DE DQ C DQ C V SS E1V SS DQ B DQ B EF V DDQ DQ C V SSG V SS DQ B V DDQ FG DQ C2DQ C BC ADV BB DQ B DQ B GH DQ C DQ C V SS GW V SS DQ B DQ B H J V DDQ V DD NC V DD NC V DD V DDQ J K DQ D DQ D V SS CK V SS DQ A DQ A K L DQ D DQ D BD SCD BA DQ A DQ A L M V DDQ DQ D V SS BW V SS DQ A V DDQ M N DQ D DQ D V SS A1V SS DQ A DQ A N P DQ D DQP D V SS A0V SS DQP A DQ A P R NC A LBO V DD FT A NC R T NC NC A A A A ZZ T U V DDQ TMS TDI TCK TDO NC V DDQ U7 x 17 Bump BGA—14 x 22 mm2 Body—1.27 mm Bump Pitch119-Bump BGA—x18 Common I/O—Top View1234567A V DDQ A A ADSP A A V DDQ AB NC A A ADSC A A NC BC NC A A V DD A A NC CD DQ B NC V SS ZQ V SS DQP A NC DE NC DQ B V SS E1V SS NC DQ A EF V DDQ NC V SSG V SS DQ A V DDQ FG NC DQ B BB ADV NC NC DQ A GH DQ B NC V SS GW V SS DQ A NC H J V DDQ V DD NC V DD NC V DD V DDQ J K NC DQ B V SS CK V SS NC DQ A K L DQ B NC NC SCD BA DQ A NC L M V DDQ DQ B V SS BW V SS NC V DDQ M N DQ B NC V SS A1V SS DQ A NC N P NC DQP B V SS A0V SS NC DQ A P R NC A LBO V DD FT A NC R T NC A A A A A ZZ T U V DDQ TMS TDI TCK TDO NC V DDQ U7 x 17 Bump BGA—14 x 22 mm2 Body—1.27 mm Bump PitchGS832218/36 119-Bump BGA Pin DescriptionSymbol Type DescriptionA0, A1I Address field LSBs and Address Counter Preset InputsAn I Address InputsDQ ADQ BDQ CDQ DI/O Data Input and Output pinsB A, B B, B C, B D I Byte Write Enable for DQ A, DQ B, DQ C, DQ D I/Os; active lowNC—No ConnectCK I Clock Input Signal; active highBW I Byte Write—Writes all enabled bytes; active lowGW I Global Write Enable—Writes all bytes; active lowE1I Chip Enable; active lowG I Output Enable; active lowADV I Burst address counter advance enable; active low ADSP, ADSC I Address Strobe (Processor, Cache Controller); active low ZZ I Sleep mode control; active highFT I Flow Through or Pipeline mode; active lowLBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance Control (Low = Low Impedance [High Drive], High = High Impedance [LowDrive])SCD I Single Cycle Deselect/Dual Cyle Deselect Mode Control TMS I Scan Test Mode SelectTDI I Scan Test Data InTDO O Scan Test Data OutTCK I Scan Test ClockV DD I Core power supplyV SS I I/O and Core GroundV SS I I/O and Core GroundV DDQ I Output driver power supplyGS832218/36 Block DiagramA1A0A0A1D0D1Q1Q0Counter LoadD QDQRegisterRegisterDQRegisterDQRegisterDQRegisterD QRegisterD QRegisterD QRegisterDQR e g i s t e rDQRegisterA0–An LBO ADV CK ADSC ADSP GW BW E 1FT GZZPower Down ControlMemory Array36364AQD DQx1–DQx93636Note: Only x36 version shown for simplicity.SCD3636B AB BB CB DNote:There are pull-up devices on the ZQ, SCD, and FT pins and a pull-down device on the ZZ pin, so those input pins can be unconnected and the chip will operate in the default states as specified in the above tables.Burst Counter SequencesBPR 1999.05.18Mode Pin FunctionsMode NamePin NameStateFunctionBurst Order Control LBO L Linear Burst H Interleaved Burst Output Register Control FT L Flow Through H or NC Pipeline Power Down Control ZZ L or NC Active H Standby, I DD = I SB Single/Dual Cycle Deselect Control SCD L Dual Cycle Deselect H or NC Single Cycle Deselect FLXDrive Output Impedance ControlZQL High Drive (Low Impedance)H or NCLow Drive (High Impedance)The burst counter wraps to initial state on the 5th clock.The burst counter wraps to initial state on the 5th clock.Linear Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 011011003rd address 101100014th address11000110I nterleaved Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 010011103rd address 101100014th address11100100Byte Write Truth TableFunction GW BW B A B B B C B D Notes Read H H X X X X1Read H L H H H H1 Write byte a H L L H H H2, 3 Write byte b H L H L H H2, 3 Write byte c H L H H L H2, 3, 4 Write byte d H L H H H L2, 3, 4 Write all bytes H L L L L L2,3,4 Write all bytes L X X X X X1.All byte outputs are active in read cycles regardless of the state of Byte Write Enable inputs.2.Byte Write Enable inputs B A, B B, B C, and/or B D may be used in any combination with BW to write single or multiple bytes.3.All byte I/Os remain High-Z during all write operations regardless of the state of Byte Write Enable inputs.4.Bytes “C” and “D” are only available on the x36 version.Synchronous Truth TableOperation Address UsedStateDiagramKey5E1ADSP ADSC ADV W3DQ4Deselect Cycle, Power Down None X H X L X X High-Z Read Cycle, Begin Burst External R L L X X X Q Read Cycle, Begin Burst External R L H L X F Q Write Cycle, Begin Burst External W L H L X T D Read Cycle, Continue Burst Next CR X H H L F Q Read Cycle, Continue Burst Next CR H X H L F Q Write Cycle, Continue Burst Next CW X H H L T D Write Cycle, Continue Burst Next CW H X H L T D Read Cycle, Suspend Burst Current X H H H F Q Read Cycle, Suspend Burst Current H X H H F Q Write Cycle, Suspend Burst Current X H H H T D Write Cycle, Suspend Burst Current H X H H T D Notes:1.X = Don’t Care, H = High, L = Low2.W = T (True) and F (False) is defined in the Byte Write Truth Table preceding3.G is an asynchronous input. G can be driven high at any time to disable active output drivers. G low can only enable active drivers (shownas “Q” in the Truth Table above).4.All input combinations shown above are tested and supported. Input combinations shown in gray boxes need not be used to accomplishbasic synchronous or synchronous burst operations and may be avoided for simplicity.5.Tying ADSP high and ADSC low allows simple non-burst synchronous operations. See BOLD items above.6.Tying ADSP high and ADV low while using ADSC to load new addresses allows simple burst operations. See ITALIC items above.Simplified State DiagramFirst WriteFirst ReadBurst WriteBurst ReadDeselect R WCRCWX XWRRWRXXX S i m p l e S y n c h r o n o u s O p e r a t i o nS i m p l e B u r s t S y n c h r o n o u s O p e r a t i o nCR RCWCRCRNotes:1.The diagram shows only supported (tested) synchronous state transitions. The diagram presumes G is tied low.2.The upper portion of the diagram assumes active use of only the Enable (E1) and Write (B A , B B , B C , B D , BW, and GW) control inputs, andthat ADSP is tied high and ADSC is tied low.3.The upper and lower portions of the diagram together assume active use of only the Enable, Write, and ADSC control inputs andassumes ADSP is tied high and ADV is tied low.Simplified State Diagram with GFirst WriteFirst ReadBurst WriteBurst ReadDeselect R WCRCWXXWRRWRXXX CRR CW CRCRW CWW CWNotes:1.The diagram shows supported (tested) synchronous state transitions plus supported transitions that depend upon the use of G.e of “Dummy Reads” (Read Cycles with G High) may be used to make the transition from read cycles to write cycles without passingthrough a Deselect cycle. Dummy Read cycles increment the address counter just like normal read cycles.3.Transitions shown in grey tone assume G has been pulsed high long enough to turn the RAM’s drivers off and for incoming data to meetData Input Set Up Time.Absolute Maximum Ratings(All voltages reference to V SS)Symbol Description Value UnitV DD Voltage on V DD Pins–0.5 to 4.6VV DDQ Voltage in V DDQ Pins–0.5 to 4.6VV I/O Voltage on I/O Pins–0.5 to V DDQ +0.5 (≤ 4.6 V max.)VV IN Voltage on Other Input Pins–0.5 to V DD +0.5 (≤ 4.6 V max.)VI IN Input Current on Any Pin+/–20mAI OUT Output Current on Any I/O Pin+/–20mAP D Package Power Dissipation 1.5WT STG Storage Temperature–55 to 125o CT BIAS Temperature Under Bias–55 to 125o C Note:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component.Power Supply Voltage RangesParameter Symbol Min.Typ.Max.Unit Notes3.3 V Supply Voltage V DD3 3.0 3.3 3.6V2.5 V Supply Voltage V DD2 2.3 2.5 2.7V3.3 V V DDQ I/O Supply Voltage V DDQ3 3.0 3.3 3.6V2.5 V V DDQ I/O Supply Voltage V DDQ2 2.3 2.5 2.7VNotes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.V DDQ3 Range Logic LevelsParameter Symbol Min.Typ.Max.Unit Notes V DD Input High Voltage V IH 2.0—V DD + 0.3V1V DD Input Low Voltage V IL–0.3—0.8V1V DDQ I/O Input High Voltage V IHQ 2.0—V DDQ + 0.3V1,3V DDQ I/O Input Low Voltage V ILQ–0.3—0.8V1,3 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.3.V IHQ (max) is voltage on V DDQ pins plus 0.3 V.V DDQ2 Range Logic LevelsParameter Symbol Min.Typ.Max.Unit Notes V DD Input High Voltage V IH0.6*V DD—V DD + 0.3V1V DD Input Low Voltage V IL–0.3—0.3*V DD V1V DDQ I/O Input High Voltage V IHQ0.6*V DD—V DDQ + 0.3V1,3V DDQ I/O Input Low Voltage V ILQ–0.3—0.3*V DD V1,3 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.3.V IHQ (max) is voltage on V DDQ pins plus 0.3 V.Recommended Operating TemperaturesParameter Symbol Min.Typ.Max.Unit Notes Ambient Temperature (Commercial Range Versions)T A02570°C2 Ambient Temperature (Industrial Range Versions)T A–402585°C2 Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.Note:These parameters are sample tested.Capacitance(T A = 25o C, f = 1 MH Z , V DD = 2.5 V)ParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Input/Output Capacitance C I/OV OUT = 0 V67pFAC Test ConditionsParameterConditionsInput high level V DD – 0.2 V Input low level 0.2 V Input slew rate 1 V/ns Input reference level V DDQ /2Output reference levelV DDQ /2Output loadFig. 1Notes:1.Include scope and jig capacitance.2.Test conditions as specified with output loading as shown in Fig. 1unless otherwise noted.3.Device is deselected as defined by the Truth Table. 20% tKCV SS – 2.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKCV DD + 2.0 V50%V DDV ILDQV DDQ/250Ω30pF *Output Load 1* Distributed Test Jig CapacitanceDC Electrical CharacteristicsParameter Symbol Test Conditions Min Max Input Leakage Current(except mode pins)I IL V IN = 0 to V DD–2 uA 2 uAZZ Input Current I IN1V DD≥V IN ≥V IH0 V≤ V IN ≤ V IH–1 uA–1 uA1 uA100 uAFT, SCD, ZQ Input Current I IN2V DD≥V IN ≥V IL0 V≤ V IN ≤ V IL–100 uA–1 uA1 uA1 uAOutput Leakage Current (x36/x72)I OL Output Disable, V OUT = 0 to V DD–1 uA 1 uA Output Leakage Current (x18)I OL Output Disable, V OUT = 0 to V DD–1 uA 1 uA Output High Voltage V OH2I OH = –8 mA, V DDQ = 2.375 V 1.7 V—Output High Voltage V OH3I OH = –8 mA, V DDQ = 3.135 V 2.4 V—Output Low Voltage V OL I OL = 8 mA—0.4 VN o t e s : 1.I D D a n d I D D Q a p p l y t o a n y c o m b i n a t i o n o f V D D 3, V D D 2, V D D Q 3, a n d V D D Q 2 o p e r a t i o n .2.A l l p a r a m e t e r s l i s t e d a r e w o r s t c a s e s c e n a r i o .O p e r a t i n g C u r r e n t sP a r a m e t e r T e s t C o n d i t i o n sM o d e S y m b o l -250-225-200-166-150-133U n i t0t o 70°C –40 t o 85°C0t o 70°C –40 t o 85°C 0t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C 0 t o 70°C –40t o 85°C O p e r a t i n g C u r r e n tD e v i c e S e l e c t e d ; A l l o t h e r i n p u t s ≥V I H o r ≤ V I LO u t p u t o p e n(x 72)P i p e l i n eI D DI D D Q 380604006035060370603205034050280403004026040280402353025530m AF l o w T h r o u g h I D D I D D Q275402854025540265402353024530225302353021030220302102022020m A(x 36)P i p e l i n eI D DI D D Q300503205027545295452554027540225352453521030230301902521025m AF l o w T h r o u g hI D DI D D Q210252202520025210251902020020180201902017020180201601517015m A(x 18)P i p e l i n eI D DI D D Q260252802524025260252252024520200202202019020210201701519015m AF l o w T h r o u g hI D DI D D Q190152001518015190151701518015160151701515015160151401515015m AS t a n d b y C u r r e n tZ Z ≥ V D D – 0.2 V—P i p e l i n e I S B608060806080608060806080m AF l o w T h r o u g hI S B608060806080608060806080m AD e s e l e c t C u r r e n tD e v i c e D e s e l e c t e d ; A l l o t h e r i n p u t s ≥ V I H o r ≤ V I L—P i p e l i n e I D D100115951109010585100851008095m AF l o w T h r o u g hI D D85100851008095809575907085m ANotes:1.These parameters are sampled and are not 100% tested.2.ZZ is an asynchronous signal. However, in order to be recognized on any given clock cycle, ZZ must meet the specified setup and holdtimes as specified above.AC Electrical CharacteristicsParameterSymbol-250-225-200-166-150-133UnitMinMaxMinMaxMinMaxMinMaxMinMaxMinMaxPipelineClock Cycle Time tKC 4.0— 4.4— 5.0— 6.0— 6.7—7.5—ns Clock to Output Valid (x18/x36)tKQ — 2.5— 2.7— 3.0— 3.5— 3.8— 4.0ns Clock to Output Valid (x72)tKQ — 3.0— 3.0— 3.0— 3.5— 3.8— 4.0ns Clock to Output Invalid tKQX 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Clock to Output in Low-ZtLZ 1 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Setup time tS 1.2— 1.3— 1.4— 1.5— 1.5— 1.5—ns Hold time tH 0.2—0.3—0.4—0.5—0.5—0.5—ns Flow ThroughClock Cycle Time tKC 6.5—7.0—7.5—8.0—8.5—8.5—ns Clock to Output ValidtKQ — 6.5—7.0—7.5—8.0—8.5—8.5ns Clock to Output Invalid tKQX 3.0— 3.0— 3.0— 3.0— 3.0— 3.0—ns Clock to Output in Low-ZtLZ 1 3.0— 3.0— 3.0— 3.0— 3.0— 3.0—ns Setup time tS 1.5— 1.5— 1.5— 1.5— 1.5— 1.5—ns Hold time tH 0.5—0.5—0.5—0.5—0.5—0.5—ns Clock HIGH Time tKH 1.3— 1.3— 1.3— 1.3— 1.5— 1.7—ns Clock LOW Time tKL 1.5—1.5—1.5—1.5— 1.7—2—ns Clock to Output in High-Z (x18/x36)tHZ 1 1.5 2.5 1.5 2.7 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0ns Clock to Output in High-Z (x72)tHZ 1 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0 1.5 3.0ns G to Output Valid (x18/x36)tOE — 2.5— 2.7— 3.0— 3.5— 3.8— 4.0ns G to Output Valid(x72)tOE — 3.0— 3.0— 3.0— 3.5— 3.8— 4.0ns G to output in Low-Z tOLZ 10—0—0—0—0—0—ns G to output in High-Z (x18/x36)tOHZ 1— 2.5— 2.7— 3.0— 3.0— 3.0— 3.0ns G to output in High-Z (x72)tOHZ 1— 3.0— 3.0— 3.0— 3.0— 3.0— 3.0ns ZZ setup time tZZS 25—5—5—5—5—5—ns ZZ hold time tZZH 21—1—1—1—1—1—ns ZZ recoverytZZR20—20—20—20—20—20—nsPipeline Mode Timing (SCD)Begin Read A Cont Cont Deselect Write B Read C Read C+1Read C+2Read C+3ContDeselecttHZtKQX tKQtLZtHtStOHZtOEtHtStHtStHtStHtStHtStStHtStHtStHtSBurst ReadtKCtKL Single Write tKH Single ReadQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)ABCDeselected with E1E1 masks ADSPE2 and E3 only sampled with ADSP and ADSCADSC initiated readCK ADSPADSCADVA0–AnGWBWBa–BdE1E2E3GDQa–DQdFlow Through Mode Timing (SCD)Begin Read A ContCont Write B Read C Read C+1Read C+2Read C+3Read C Cont DeselecttHZtKQXtKQ tLZtH tStOHZtOEtHtS tHtS tHtStHtS tHtS tHtStHtS tHtS tH tS tHtS tKCtKL tKHABCQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)Q(C)E2 and E3 only sampled with ADSCADSC initiated readDeselected with E1Fixed HighCK ADSPADSCADVA0–AnGWBWBa–BdE1E2E3GDQa–DQd。

GS8322ZV36GB-250资料