EDA设计(I)-5

EDA技术

1. 5、EDA软件工作平台 目前支持EDA技术软件工作平台非常丰富, 归类后一般有: 在模拟电路设计中,目前最好的EDA软件 应属于EWB(Elctrinic Work bench),具有界 面直观,操作方便、灵活,采用图形输入方式 (而不是文本输入方式)输入和创建电路。 在数字电路设计中, EDA软件的种类比较多 ,不同的器件制造商推出不同的EDA软件。

通往 I/O 模块

乘 积 项 选 择 矩 阵

时钟

清零 共 享

清零 选择

逻辑阵列

逻 辑 扩 展 项 通往 PIA 18

2)基于查找表的结构模块

• 一个N输入查找表 (LUT,Look Up Table)可以 实现N个输入变量的任何逻辑功能,如 N输入 “与”、 N输入“异或”等。 • 输入多于N个的函数、方程必须分开用几个查 找表( LUT)实现

波形输入

Synopsys, ViewLogic, Mentor Graphi 等厂商的EDIF文 .xnf

文本 文件

.gdf 图形 文件

.wdf

.tdf

.vhd

.sch 图形 文件

.edf 文本 文件

图形输入

波形 文件

文本 文本 文件 文件

Xilinx MAX+PLUS II 自身产生 从其他 EDA 工具输入

9

适配器功能是将由综合器产生的网表 文件配置于定的目标器件中,产生最终的 下载文件,如:JEDLC格式的文件。适配 所选定的目标器件(FPGA/CPLD芯片) 必须属于原综合指定的目标器件系列。适 配器则需由FPGA/CPLD供应商自己提供, 因为适配器的适配对象直接与器件结构相 对应。

10

FPGA/CPLD 开发流程图

EDA技术简介

实体说明

图5-3 mux21a实体 实体

ARCHITECTURE one OF mux21a IS BEGIN y <= a WHEN s = '0' ELSE b ; END ARCHITECTURE one ;

EDA技术 EDA技术

2、主流器件 、

◆ FPGA 现场可编程门阵列) (Field Programmable Gate Array现场可编程门阵列) 现场可编程门阵列 ◆ CPLD 复杂可编程逻辑器件) (Complex Programmable Logic Device复杂可编程逻辑器件) 复杂可编程逻辑器件

功能仿真

逻辑综合器

FPGA/CPLD

适配

结构综合器

时序与功能 门级仿真

1、功能仿真 、 2、时序仿真 、

FPGA/CPLD 编程下载

EDA技术 EDA技术

二、 FPGA最小系统 最小系统

EDA技术 EDA技术 1、EP1K100B+ 零售价:450元(含EPC2芯片 零售价: 元 芯片) 、 芯片

EDA技术 EDA技术

技术? 一、EDA技术? 技术

EDA( Automation电子设计自动化 电子设计自动化) ● EDA(Electronic Design Automation电子设计自动化) 是指利用计算机完成电子系统的设计。 是指利用计算机完成电子系统的设计。

EDA技术是以计算机和微电子技术为先导, 技术是以计算机和微电子技术为先导 ● EDA技术是以计算机和微电子技术为先导, 汇集了计算机图 形学、 拓扑、 逻辑学、 形学、 拓扑、 逻辑学、 微电子工艺与结构学和计算数学 等多种计算机应用学科最新成果的先进技术。 等多种计算机应用学科最新成果的先进技术。 EDA技术以计算机为工具, 技术以计算机为工具 ● EDA技术以计算机为工具, 代替人完成数字系统的逻辑综 合、布局布线和设计仿真等工作。 布局布线和设计仿真等工作。 等工作

EDA字符及数据类型

if (b=‘1’) then return a+1;

else return a;

end if;

end “+”;

第14页/共19页

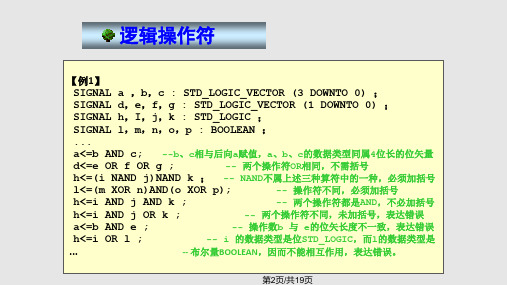

VHDL操作符的优先顺序

运算符 NOT,ABS,** *,/,MOD,REM +(正号),-(负号) +,-,& SLL,SLA,SRL,SRA,ROL,ROR =,/=,<,>,<=,>= AND,OR,NAND,NOR,XOR,XNOR

第13页/共19页

重载操作符

即用户自定义操作符,可以与预定义的操作符具有相同 的名称。对已存在的操作符重新定义,可进行不同类型操 作数之间的运算。

例:对一个整数和一个1位的二进制数进行加法运算

function “+” (a: integer; b: bit) return integer is

begin

除

整数和实数(包括浮点数)

取模

整数

乘方

整数

取绝对值

整数

取余

整数

正

整数

负

整数

逻辑左移

BIT 或布尔型一维数组

逻辑右移

BIT 或布尔型一维数组

算术左移

BIT 或布尔型一维数组

算术右移

BIT 或布尔型一维数组

逻辑循环左移 BIT 或布尔型一维数组

逻辑循环右移 BIT 或布尔型一维数组

用于对 SIGNAL 赋值

第8页/共19页

移位操作符

➢SLL(逻辑左移) ➢SRL(逻辑右移) ➢SLA(算术左移) ➢SRA(算术右移) ➢ROL(逻辑循环左移) ➢ROR(逻辑循环右移) 移位操作符的语句格式是: 标识符 移位操作符 移位位数 ;

eda课程设计5篇[修改版]

![eda课程设计5篇[修改版]](https://img.taocdn.com/s3/m/a1aef8d5dd36a32d72758100.png)

第一篇:eda课程设计数字钟一、设计要求设计一个数字钟,具体要求如下:1、具有时、分、秒计数显示功能,以24小时循环计时。

2、具有清零、校时、校分功能。

3、具有整点蜂鸣器报时以及LED花样显示功能。

二、设计方案根据设计要求,数字钟的结构如图8-3所示,包括:时hour、分minute、秒second计数模块,显示控制模块sel_clock,七段译码模块deled,报时模块alert。

三、VHDL程序library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; useIEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code. --library UNISIM;--use UNISIM.VComponents.all;entityddz is port(rst,clk: in std_logic; hour_h: out std_logic_vector( 6 downto 0); hour_l: outstd_logic_vector( 6 downto 0); min_h: out std_logic_vector( 6 downto 0);min_l: out std_logic_vector( 6 downto 0);sec_h: out std_logic_vector( 6 downto 0);sec_l: out std_logic_vector( 6 downto 0)); endddz;architecture Behavioral of ddz is signalcnt: std_logic_vector(15 downto 0); signalsec_h_in: std_logic_vector( 3 downto 0); signalsec_l_in: std_logic_vector( 3 downto 0); signalmin_h_in: std_logic_vector( 3 downto 0); signalmin_l_in: std_logic_vector( 3 downto 0); signalhour_h_in: std_logic_vector(3 downto 0); signalhour_l_in: std_logic_vector(3 downto 0);signalclk_s,clk_m,clk_h: std_logic; begin process(rst,clk) begin if rst='0' then sec_h_in'0');sec_l_in'0');clk_msec_l_inifsec_h_in=5 thensec_h_inclk_melsesec_h_inclk_mend if; else sec_l_inclk_mend if; end if; end process;process(rst,clk_m) begin if rst='0' then-- min_h_in'0');min_l_in'0'); -- clk_hmin_l_inmin_h_inclk_mend if; else min_l_inend if; end if; end process;process(rst,clk_n) begin if rst='0' then-- hour_h_in'0');hour_l_in'0'); -- clk_hhour_l_inhour_h_inclk_nend if; else hour_l_inend if; end if; end process;process(sec_l_in) begin casesec_l_in iswhen "0000" =>sec_lsec_lsec_lsec_lsec_lsec_lsec_lsec_lsec_lsec_lsec_lprocess(sec_h_in) begin casesec_h_in iswhen "0000" =>sec_hsec_hsec_hsec_hsec_hsec_hsec_hsec_hsec_hsec_hsec_hprocess(min_l_in) begin casemin_l_in iswhen "0000" =>min_lmin_lmin_lwhen "0011" =>min_lmin_lmin_lmin_lmin_lmin_lmin_lmin_lprocess(min_h_in) begin casemin_h_in iswhen "0000" =>min_hmin _h min _hmin _hmin _h min _hmin _hmin _hmin _hmin _hmin _hend case; end process;process(hour_l_in) begin casehour_l_in iswhen "0000" =>hour_lhour_lhour_lhour_lhour_lhour_lhour_lhour_lhour_lhour_lhour_lprocess(hour_h_in) begin casehour_h_in iswhen "0000" =>hour_hhour_hhour_hhour_h hour _h hour _h hour _h hour _h hour _hhour_h hour _h四、VHDL仿真结果五、课程设计心得通过这次课程设计,有效得巩固了课本所学的知识,而且通过上机仿真不断发现问题并及时改正,加深了我们对该课程设计的印象。

EDA电子设计自动化知识点总结

1、实体界面说明中端口的模式有四种端口模式为:1、IN相当于只可输入的引脚;2、OUT相当于只可输出的引脚;3、BUFFER相当于带输出缓冲器并可以回读的引脚;4、INOUT相当于双向引脚;2、嵌入式阵列块EAB能实现存储功能,每个EAB提供2048比特,可完成ROM,RAM,双口RAM或者FIFO功能。

3、VHDL程序设计中的两大基本描述语句是顺序语句,并行语句。

4、FLEX10K的结构提供了两条专用高速通道,即进位链和级联链。

5、常用的源程序输入方式有原理图输入方式、状态图输入方式、VHDL软件程序的文本方式。

6、FPGA的可编程互连线分为通用互连、直接互连、长线。

7、FPGA(现场可编程门阵列)结构可分为三部分:可编程逻辑单元、可编程输入/输出单元、可编程连线。

8、CPLD(复杂可编程逻辑器件)的结构可分为三部分:可编程逻辑宏单元、可编程输入/输出单元、可编程内部连线。

9、结构体的三种描述方式:行为级描述、数据流级描述、结构级描述。

10、EDA设计几个描述层次:行为级描述、寄存器传输级描述(RTL)、门级描述、版图级描述。

11、构成一个完整的VHDL语言程序的五大基本结构:实体(ENTITY)、结构体(ARCHITECURE)、配置(CONFIGURATION)、库(LIBRARY)、程序包(PACKAGE)。

12、VHDL的子程序有过程和函数两种类型,具有可重载性。

13、数字ASIC设计方法有两种:全定制法、半定制法(门阵列法、标准单元法、可编程逻辑器件法)。

14、数字系统的模型:数据处理子系统和控制子系统。

15、数字系统设计方法:模块设计法、自顶向下设计法、自底向上设计法。

16、EDA的工程设计流程:原理图/HDL文本输入→功能仿真→综合→适配→时序→仿真→编辑下载→硬件测试。

17、FPGA的配置流程:芯片初始化、芯片配置和起动。

18、转向控制语句共有五种:IF 语句、CASE 语句、LOOP 语句、NEXT 语句和EXIT 语句。

电子设计CAD基础

u=ATu

(2-6)

式(2-6)是用A矩阵表示的KVL的矩阵形式。

2.3.2 KVL 的矩阵形式

对于任一个连通图G,在支路排列顺序相同时,写出的矩阵 A、B、Q(上述例题就是如此) KCL 和KVL的矩阵形式见表1-1。

表中用 Q矩阵表示的KCL 和KVL的矩阵形式,可认为是 A矩 阵的推广,即结点推广到高斯面,其中u为树支电压列向量。用B 矩阵表示的KCL 和KVL的矩阵形式,可依对偶原理得之,即基本 回路与基本割集对偶,其中i为连支电流列向量,它与u树支电压 列向量对偶。

若把 Aa的任一行划去,比如将式中第3行划去,则得(n-1)×b阶 的(降阶的)关联矩阵,以A表示

2.2.2 (基本)回路矩阵

回路矩阵:设一个回路是由某些支路组成的,则称这 些支路与该回路相关联。支路与回路相关联的性质,可用 回路矩阵来描述。设有向图的独立回路数为l,支路数为b, 并对所有的独立回路与支路都进行编号。则该有向图的 (基本)回路矩阵为一个(l×b)阶的矩阵,用B表示。如果 它的行对应于一个基本回路Bf(我们多用这种基本回路, 习惯上简称为回路,形成的矩阵亦习惯上简称为回路矩 阵),列对应于支路,它的任一元素定义如下: 向一b致ij =(1以,连表支示的支方路向j与为基基本本回回路路i相i的关绕联行,方并向且);它们的方 向相b反ij =;-1,表示支路j与基本回路i相关联,但是它们的方

绪 论:二、CAD软件

3.EWB Multisim特点: (1)最突出的是软件中提供了各种虚拟仪

器 (2)软件带有丰富的电路元件库 (3)采用直观的电路图输入方式 (4)操作方便、易学易用,很适合电子类

课程的教学和实验

绪 论:二、CAD软件

其中的电路分析软件内核都是SPICE。

EDA技术与应用

EDA技术与应用电子设计技术的核心就是EDA技术,EDA是指以计算机为工作平台,融合应用电子技术、计算机技术、智能化技术最新成果而研制成的电子CAD通用软件包,主要能辅助进行三方面的设计工作,即IC设计、电子电路设计和PCB设计。

以下是关于EDA技术与应用,欢迎大家参考!EDA 技术已有30 年的发展历程,大致可分为三个阶段。

70 年代为计算机辅助设计(CAD阶段,人们开始用计算机辅助进行IC版图、PCB布局布线,取代了手工操作。

80年代为计算机辅助工程(CAE)阶段。

与CAD相比,CAE除了有纯粹的图形绘制功能外,又增加了电路功能设计和结构设计,并且通过电气连接网络表将两者结合在一起,实现了工程设计。

CAE的主要功能是:原理图输入,逻辑仿真,电路分析,自动布局布线,PCB后分析。

90年代为电子系统设计自动化(EDA)阶段。

一、EDA技术的基本特征EDA 代表了当今电子设计技术的最新发展方向,它的基本特征是:设计人员按照“自顶向下”的设计方法,对整个系统进行方案设计和功能划分,系统的关键电路用一片或几片专用集成电路(ASIC)实现,然后采用硬件描述语言(HDL)完成系统行为级设计,最后通过综合器和适配器生成最终的目标器件,这样的设计方法被称为高层次的电子设计方法。

下面介绍与EDA基本特征有关的几个概念。

1.“自顶向下”的设计方法10 年前,电子设计的基本思路还是选用标准集成电路“自底向上”地构造出一个新的系统,这样的设计方法就如同一砖一瓦建造金字塔,不仅效率低、成本高而且容易出错。

高层次设计是一种“自顶向下”的全新设计方法,这种设计方法首先从系统设计入手,在顶层进行功能方框图的划分和结构设计。

在方框图一级进行仿真、纠错,并用硬件描述语言对高层次的系统行为进行描述,在系统一级进行验证。

然后,用综合优化工具生成具体门电路的网络表,其对应的物理实现级可以是印刷电路板或专用集成电路。

由于设计的主要仿真和调试过程是在高层次上完成的,这既有利于早期发现结构设计上的错误,避免设计工作的浪费,又减少了逻辑功能仿真的工作量,提高了设计的一次成功率。

EDA技术及应用—基于FPGA的电子系统设计:基于Verilog hdl的数字电路设计

10100

1111

15

10101

8421BC 余三码 D码

0000

0011

0001

0100

0010

0101

0011

0110

0100

0111

0101

1000

0110

1001

0111

1010

1000

1011

1001

1100

-

-

-

-

-

-

-

-

-

-

-

-

4位格雷码

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000

4'b0011:a_to_g=7'b1111001; //显示3

4'b0100:a_to_g=7'b0110011; //显示4

4'b0101:a_to_g=7'b1011011; //显示5

4'b0110:a_to_g=7'b1011111; //显示6

4'b0111:a_to_g=7'b1110000; //显示7

4: y= {d[2:0],d[3]}; // rol

5: y= {d[3],d[3:1]}; // asr

6: y= {d[1:0],d[3:2]}; // ror2

7: y= d;

// noshift

default: y = d;

图6-2 基本门电路仿真结果

综合结果如图6-3所示。

图6-3 基本门电路综合结果

2、 三态逻辑电路

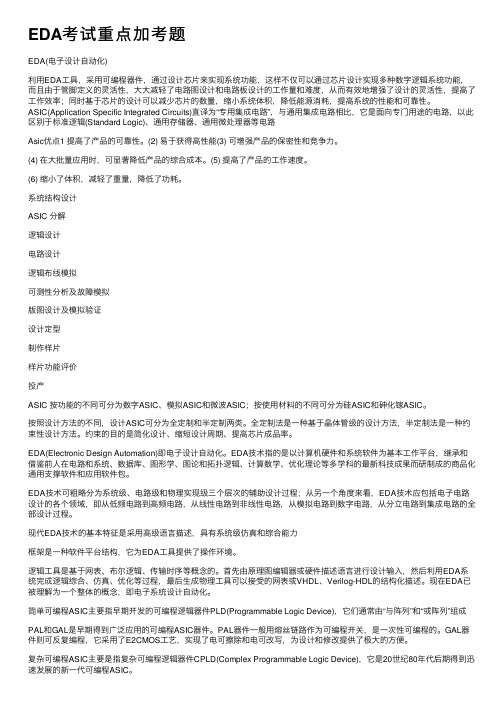

EDA考试重点加考题

EDA考试重点加考题EDA(电⼦设计⾃动化)利⽤EDA⼯具,采⽤可编程器件,通过设计芯⽚来实现系统功能,这样不仅可以通过芯⽚设计实现多种数字逻辑系统功能,⽽且由于管脚定义的灵活性,⼤⼤减轻了电路图设计和电路板设计的⼯作量和难度,从⽽有效地增强了设计的灵活性,提⾼了⼯作效率;同时基于芯⽚的设计可以减少芯⽚的数量,缩⼩系统体积,降低能源消耗,提⾼系统的性能和可靠性。

ASIC(Application Specific Integrated Circuits)直译为“专⽤集成电路”,与通⽤集成电路相⽐,它是⾯向专门⽤途的电路,以此区别于标准逻辑(Standard Logic)、通⽤存储器、通⽤微处理器等电路Asic优点1 提⾼了产品的可靠性。

(2) 易于获得⾼性能(3) 可增强产品的保密性和竞争⼒。

(4) 在⼤批量应⽤时,可显著降低产品的综合成本。

(5) 提⾼了产品的⼯作速度。

(6) 缩⼩了体积,减轻了重量,降低了功耗。

系统结构设计ASIC 分解逻辑设计电路设计逻辑布线模拟可测性分析及故障模拟版图设计及模拟验证设计定型制作样⽚样⽚功能评价投产ASIC 按功能的不同可分为数字ASIC、模拟ASIC和微波ASIC;按使⽤材料的不同可分为硅ASIC和砷化镓ASIC。

按照设计⽅法的不同,设计ASIC可分为全定制和半定制两类。

全定制法是⼀种基于晶体管级的设计⽅法,半定制法是⼀种约束性设计⽅法。

约束的⽬的是简化设计、缩短设计周期、提⾼芯⽚成品率。

EDA(Electronic Design Automation)即电⼦设计⾃动化。

EDA技术指的是以计算机硬件和系统软件为基本⼯作平台,继承和借鉴前⼈在电路和系统、数据库、图形学、图论和拓扑逻辑、计算数学、优化理论等多学科的最新科技成果⽽研制成的商品化通⽤⽀撑软件和应⽤软件包。

EDA技术可粗略分为系统级、电路级和物理实现级三个层次的辅助设计过程;从另⼀个⾓度来看,EDA技术应包括电⼦电路设计的各个领域,即从低频电路到⾼频电路,从线性电路到⾮线性电路,从模拟电路到数字电路,从分⽴电路到集成电路的全部设计过程。

eda原理图

1. 系统概述

MAX+plus II是Altera公司在 Windows 环 境下开发的可编程逻辑设计软件平台。该系 统将数字电路设计集成在一个环境内,支持 Altera公司的可编程器件,允许多种输入方式 的设计文件。经过系统编辑器的编译、综合 等操作,对设计进行功能模拟、逻辑分析、 自动布局布线、延时时间分析、下载编程, 最后将电路分配到一个或多个器件中。

六、EDA软件工具介绍

(一)EDA工具的基本功能(PLD-->ASIC) PLD:Programmable Logic Device

ASIC:Application Specific Integrated

Circuit (二) PLD器件的开发设计流程 (三) EDA工具的应用环境 (四) EDA工具的来源

3. 推荐的系统配置

500MHz以上奔腾PC机; Windows98或更高版本; 有效内存和物理存储空间与使用的器件有关。

器件系列 ACEX1K FLEX10K FLEX8000 FLEX6000 MAX9000 MAX7000

有效内存 256 256 64 64 64 48

物理RAM 128 128 32 32 32 16

特点

EDA课程的教学目标

了解可编程逻辑器件的基本原理,掌握一种

描述语言,掌握一种设计软件,具备有效地 完成数字系统设计的能力。

EDA课程的考核要求

EDA课程教材及参考资料 教材:专用集成电路与电子设计自动化 图书馆的参考书籍及相关期刊资料

实验指导书 —— 自编

相关网站:学院教学网站及国际著名公司网站

EDA软件工具 ---- MAX+plus II MAX+plus : Multiple Array Matrix and

EDA技术及发展趋势

EDA 技术及发展趋势EDA 技术的概念及范范畴:EDA 技术是在电子 CAD 技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

利用 EDA 工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出 IC 版图或者 PCB 版图的整个过程在计算机上自动处理完成。

现在对 EDA 的概念或者范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有 EDA 的应用。

目前 EDA 技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机创造过程中,从设计、性能测试及特性分析直到飞行摹拟,都可能涉及到 EDA 技术。

本文所指的 EDA 技术,主要针对电子电路设计、 PCB 设计和 IC 设计。

EDA 设计可分为系统级、电路级和物理实现级。

EDA 常用软件: EDA 工具层出不穷,目前进入我国并具有广泛影响的 EDA 软件有: EWB、PSPICE、OrCAD、PCAD、Protel、Viewlogic、Mentor、Graphics、Synopsys、LSIlogic、Cadence、MicroSim 等等。

这些工具都有较强的功能,一般可用于几个方面,例如不少软件都可以进行电路设计与仿真,同时以可以进行PCB 自动布局布线,可输出多种网表文件与第三方软件接口。

下面按主要功能或者主要应用场合,分为电路设计与仿真工具、 PCB 设计软件、 IC 设计软件、 PLD 设计工具及其它 EDA 软件,进行简单介绍。

1、电子电路设计与仿真工具电子电路设计与仿真工具包括 SPICE/PSPICE;EWB;Matlab;SystemView;MMICAD 等。

下面简单介绍前三个软件。

(1) SPICE (Simulation Program with Integrated Circuit Emphasis)是由美国加州大学推出的电路分析仿真软件,是 20 世纪 80 年代世界上应用最广的电路设计软件, 1998 年被定为美国国家标准。

EDA设计(I)-2

实单级放大电路的设计与仿真一.实验目的①掌握放大电路静态工作点的测试和调节方法。

②掌握放大电路的动态参数的测试方法。

③观察静态工作点的选择对输出波形及电压放大倍数的影二.实验要求:1.设计一个分压偏置的单管电压放大电路,要求信号源频率5kHz(峰值10mV) ,负载电阻5.1kΩ,电压增益大于50。

2.调节电路静态工作点(调节偏置电阻),观察电路出现饱和失真和截止失真的输出信号波形,并测试对应的静态工作点值。

3.调节电路静态工作点(调节偏置电阻),使电路输出信号不失真,并且幅度最大。

在此状态下测试:①电路静态工作点值;②三极管的输入、输出特性曲线和 、be r、ce r值;③电路的输入电阻、输出电阻和电压增益;④电路的频率响应曲线和f L、f H值。

三.实验步骤1.单级放大电路原理图。

图1-1 单级放大电路图1-2 静态工作点分析2.电路饱和失真和截止失真时输出电压的波形图以及两种状态下三极管的静态工作点值。

(1)当电位计调至50%时,输出波形如图 1-3所示,观察波形,此管出现了饱和失真,对应的静态工作点如图1-4所示。

图1-3 饱和失真时的波形图图1-4 饱和失真时各静态工作点值(2)当电位计调至0%时,输出波形如图1-5所示,观察波形,此管出现了截止失真,对应的静态工作点如图1-6所示:图1-5 截止失真时的波形图图1-6 截止失真时各静态工作点值3.测试三极管输入、输出特性曲线和 、r be、r ce值的实验图以及测试结果。

(1)测试三极管Q1的输入特性曲线图1-7 测试输入特性曲线的电路图图1-8 输入特性曲线be r dx dy =÷=2.25 Kohm(2)测试三极管Q1的输出特性曲线图1-9 测试输出特性曲线的电路图图1-8 输出特性曲线ce r dx dy =÷=39.39Kohm(3)β值的计算:c b I I β=÷=113.464. 电路工作在最大不失真状态下: (1) 三极管静态工作点的测量值;b I =13.83550e-6 A cI =1.56972e-3 A CEQ U =5.07424V(2) 输出波形图以及放大倍数,并与理论计算值进行比较图1-9 最大不失真时的波形图U O i A U U =÷=103.95|u A '|=|-β(4R //5R )÷be r |=95.25e=|uA '-UA | ÷ u A ' ⨯100%≈9.1%(3) 测量输入电阻、输出电阻和电压增益的实验图以及测试结果,并和理论计算值进行比较。

EDA技术及其应用

1.9 硬件测试技术

1.9.2 JTAG边界扫描测试

表1-1 边界扫描IO引脚功能

引脚

描述

功能

TDI 测试数据输入(Test Data Input) TDO 测试数据输出(Test Data Output)

测试指令和编程数据的串行输入引脚。数据在TCK的上升沿移 入。

测试指令和编程数据的串行输出引脚,数据在TCK的下降沿移 出。如果数据没有被移出时,该引脚处于高阻态。

适配器件

Timing Analyzer (时序分析器)

仿真

编程器

下载

图1-19 Quartus II设计流程

1.14 IP核

IP

软IP

固IP

硬IP

用HDL等硬件描述语 言描述的功能块,但 是并不涉及用什么具 体电路元件实现这些 功能。

完成了综合 的功能块

提供设计的 最终阶段产 品:掩膜

1.15 EDA的发展趋势

1.1 EDA技术

EDA (Electronic Design Automation)

EDA技术就是依赖功能强大的计算机,在EDA工具软件 平台上,对以硬件描述语言HDL (Hardware Description Language)为系统逻辑描述手段完成的设计文件,自动地完 成逻辑编译、化简、分割、综合、布局布线以及逻辑优化和 仿真测试,直至实现既定的电子线路系统功能。

随着市场需求的增长,集成工艺水平及计算机自动设 计技术的不断提高,促使单片系统,或称系统集成芯片成 为IC设计的发展方向

随着系统开发对EDA技术的目标器件各种性能要求的 提高,ASIC和FPGA将更大程度相互融合。

现在,传统ASIC和FPGA之间的界限正变得模糊。系 统级芯片不仅集成RAM和微处理器,也集成FPGA。整个 EDA和IC设计工业都朝这个方向发展,这并非是FPGA与 ASIC制造商竞争的产物,而对于用户来说,意味着有了更 多的选择。

EDA技术简介

高密度PLD(HDPLD): 高密度PLD(HDPLD): PLD EPLD:可擦除PLD EPLD:可擦除PLD

结构: GAL基本相同--大量增加了输出宏单元的数目 结构:和GAL基本相同--大量增加了输出宏单元的数目 基本相同-特点:集成密度大大提高,增加了设计的灵活性, 特点:集成密度大大提高,增加了设计的灵活性,内 部连线固定,时延很小, 部连线固定,时延很小,工作速度高

2、EDA工具的发展趋势 、 工具的发展趋势 (1)输入工具 以硬件描述语言(HDL)为主 以硬件描述语言(HDL)为主 (2)混合信号处理能力 数/模混合信号的处理 数字信号的描述:VHDL VeriogHDL 数字信号的描述:VHDL 模拟信号的描述:AHDL 模拟信号的描述:AHDL 微波信号的描述:MHDL 微波信号的描述:MHDL

(3)仿真工具 仿真分为: 功能仿真(前仿真、系统级仿真、行为仿真) 作用:验证系统的功能。 时序仿真(后仿真、电路级仿真) 作用:验证系统的时序特性、系统性能 仿真是系统验证的主要手段,是整个电 子设计过程中花费时间最多的环节。

时序仿真与功能仿真

是直接对VHDL、 是直接对VHDL、原理图描述或其他描 VHDL 述形式的逻辑功能进行测试模拟, 述形式的逻辑功能进行测试模拟,以了解 其实现的功能是否满足原设计的要求的过 程,仿真过程不涉及任何具体器件的硬件 特性。 特性。

复习回顾

1、什么是EDA技术? 、什么是EDA技术? 2、EDA技术与传统的电子设计 EDA技术与传统的电子设计 技术的差别? 3、EDA技术的发展趋势? EDA技术的发展趋势?

EDA技术与传统的电子设计技术的差别? EDA技术与传统的电子设计技术的差别? 技术与传统的电子设计技术的差别 1、(EDA)自上而下 、(EDA)自上而下 (基于芯片)

常用EDA软件简介

2006年3月第1期张水利等:常用EDA软件简介常用EDA软件简介张水利鲁冠华刘星(山东水利职业学院,山东日照276826)摘要:电子设计自动化(EDA)是近几年发展起来的设计方法,它为电子技术的发展提供了强劲的动力,有力地促进了电子技术的迅速进步。

作为以培养应用技术型人才为主的高职院校,电气类专业的老师和学生都应该了解并掌握常用的EDA软件,以便更好地为自己的工作和学习服务。

关键词:电子设计自动化;设计方法;高职学院;EDA软件EDA是ElectronicDesignAutomation的缩写,其含义为电子设计自动化,是20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术就是以计算机为工具,在EDA软件平台上,设计者用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

早期的EDA技术正如其定义,专门用于PLD(ProgrammableLogicDevice)、CPLD(ComplexPLD)、FPGA(FieldProgrammableGateArray)、ASIC(ApplicationSpecificIntegratedCircuit)器件的设计领域,只有专业人士才会接触。

后来,随着计算机技术和电子技术的进步,EDA技术逐渐深入到电子设计的各个领域。

在PCB设计、电路仿真等领域也开始大量应用计算机软件,所以又有人对EDA的定义进行了延伸,认为EDA技术是指以计算机为工作平台,融合了应用电子技术、计算机技术、智能化技术最新成果而研制的电子CAD通用软件包,主要能辅助进行IC设计、电子电路设计与仿真以及PCB设计等工作。

广义上的EDA软件包括哪些,这些问题各专业人士有不同的观点。

笔者认为,目前常用的EDA软件可分为以下几个方面:1电路仿真软件电路仿真软件主要应用于电路设计过程中。

【精品】用原理图输入法设计一个5人表决电路-参加表决者5人-同意为1-不同意为0-同剖析

用原理图输入法设计一个5人表决电路-参加表决者5人-同意为1-不同意为0-同剖析用原理图输入法设计一个5人表决电路,参加表决者5人,同意为1,不同意为0,同意者过半则表决通过,绿指示灯亮;表决不通过红指示灯亮。

内容提要:在电子设计与制造技术的发展中,核心就是电子设计自动化(EDA,Electronic Design Automation)技术。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

本次课程设计的目的是作出一个五人表决器,要求能实现五人表决器的基本功能,意义在于熟悉集成电路的引脚安排;掌握各芯片的逻辑功能及使用方法;了解五人表决器的组成及工作原理;掌握五人表决器的设计与制作方法。

采用了原理图输入法的设计方法,首先根据表决器的功能写出真值表,得出输出的表达式,再根据卡诺图,得到最简的表达式,然后根据学校的元件清单选择所需元件使用DXP2004程序画出原理图,仿真能得到正确的结果后画出PCB封装图,最后制版焊接做成成品。

我们做出来的成品最终能够实现五人表决器的基本功能。

关键词:五人表决器、EDA、VHDL、列写真值表⒈设计目的⑴设计一个五人表决器。

⑵掌握 QuartusII软件的使用方法⑶掌握各芯片的逻辑功能及控制方法。

⑷掌握原理图输入的设计方法和流程。

⑸了解和掌握五人表决器的功能。

⒉设计要求用原理图输入法设计一个5人表决电路,参加表决者5人,同意为1,不同意为0,同意者过半则表决通过,绿指示灯亮;表决不通过红指示灯亮。

⒊设计思路⑴设计表决工作电路。

⑵设计输出显示电路。

⑶用与或门设计原理图。

⒋实验条件⑴Win7操作系统⑵QuartusII EDA开发系统⑶输入信号x5、与门x10、或门x3、输出信号x1⒌实验过程⑴打开 QuartusII 软件,建立一个新的工程:①单击菜单 File\New Project Wizard②输入工程的路径、工程名以及顶层实体名。

EDA技术的基本概念

1 EDA技术的基本概念(什么是EDA技术,EDA做什么EDA即电子设计自动化,是Electronic Design Automa tion的英文缩写。

EDA技术是在电子CA D技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

具体讲就是:以大规模可编程逻辑器件为设计载体以硬件描述语言HDL(Hardwa re Descri ption Langua ge)为系统逻辑描述的主要表达方式以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具自动完成用软件的方式设计的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合、优化、逻辑布局布线、逻辑仿真直至完成对于特定目标芯片适配编译、逻辑映射、编程下载等工作最终形成集成电子系统或专用集成芯片。

2 EDA技术开发流程设计输入硬件描述语言文本输入这种方式与传统的计算机软件语言编辑输入基本一致,就是将使用了某种硬件描述语言(HDL)的电路设计文本,如VHDL或V eri l o g的源程序,进行编辑输入。

仿真让计算机根据一定的算法和一定的仿真库对ED A设计进行模拟,以验证设计排除错误。

分为功能仿真和时序仿真两种不同级别的仿真测试综合综合器不是机械的一对一翻译根据设计库、工艺库以及预先设置的各类约束条件选择最优的方式完成电路结构的形成。

是选择一种能充分满足各项约束条件且最低成本的实现方案。

适配适配器也称结构综合器,功能是将综合产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件,如JEDEC、Jam 格式的文件。

EDA常用术语及英文缩写

EDA常用术语及英文缩写电子设计自动化:EDA

片上系统:SOC

专用集成电路:ASIC

印制电路板:PCB

可编程逻辑器件:PLD

可编程模拟器件:PAC

在系统可编程模拟器件:ispPAC

复杂可编程逻辑器件:CPLD

现场可编辑门阵列:FPGA

硬件描述语言:HDL

可编程只读存储器:PROM

紫外线可擦除只读存储器:EPROM

电可擦除只读存储器:EEPROM

可编程阵列逻辑:PAL

通用阵列逻辑:GAL

可编程逻辑阵列:PLA

可编程逻辑阵列宏单元:LMC

输出逻辑宏单元:OLMC

可编程I/O单元:IOC

可编程内部连线:PIA

可编程逻辑块:CLB

输入/输出模块:IOB

可编程互连资源:PIR

数据选择器:MUX

在系统编程技术,在器件编程时,所用的无根信号线:(1):ispEN’:编程使能信号。

(2):SDO:数据输出线。

(3):SLCK:串行时钟线。

(4):SDI:向串行移位寄存器提供编程数据和其他命令。

(5):MODE:编程状态机的控制线。

全局布线区:GRP

输出布线区:ORP

逻辑阵列块:LAB

嵌入式阵列块:EAB

逻辑单元:LE

输入/输出单元:IOE

嵌入式系统块:ESB

边界扫描测试技术:BST

数字信号的硬件语言:VHDL Verilog HDL

模拟信号的硬件语言:AHDL

微波信号的硬件描述语言:MHDL。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一单级放大电路的设计与仿真一、实验目的1.掌握放大电路静态工作点的调整和测试。

2.掌握放大电路的动态参数的测试方法。

3.观察静态工作点的选择对输出波形及电压放大倍数的影响。

二、实验要求1. 设计一个分压偏置的单管电压放大电路,要求信号源频率5kHz,峰值10mV ,负载电阻5.1kΩ,电压增益大于50。

2. 调节电路静态工作点,观察电路出现饱和失真和截止失真的输出信号波形,并测试对应的静态工作点值。

3. 在正常放大状态下测试:①电路静态工作点值;②三极管的输入、输出特性曲线和 、R be 、R ce值;③电路的输入电阻、输出电阻和电压增益;④电路的频率响应曲线和f L、f H值。

三、实验步骤图1 单级放大电路图A u=1127÷7.007=160.84>50 ,满足实验要求。

1.饱和失真调节电位器的阻值改变静态工作点,当电位器为0%R w时,电路出现饱和失真,如下图图3饱和失真波形图4 饱和失真时的静态工作点此时由图可知静态工作Q点:I b=68.95170uA I c=7.63657mA U ce= U be-U bc 240.208mV2.截止失真调节电位器的阻值改变静态工作点,当电位器为80%R w时,电路出现截止失真图5 截止失真波形图6 截止失真时的静态工作点此时由图可知静态工作Q点:Ib=5.97098uA I c=774.55uA Uce=U be-U bc=21.5913V3.最大不失真调节电位器的阻值,当电位器为10%R w时,电路出现最大不失真图7 最大不失真时的波形图8 最大不失真静态工作点此时由图可知静态工作Q点:Ib=33.4421uA Ic=4.45028mA Uce= U be-U bc =10.234V 失真情况分析:对非线性失真,为观察到饱和失真,应将静态工作点设置的较高,处于三极管的饱和区,即调小电位器以增大基极电流。

为观察到截止失真,应将静态工作点设置的较低,处于三极管的截止区,即调大电位器以减小基极电流。

而只有找到合适的静态工作点,才可以获得最大不失真输出电压。

4.三极管输入、输出特性曲线和β、R be、R ce的值1)β求值β =Ic/Ib=133.072)三极管输入特性曲线及Rbe求值:图9 求三极管输入特性的电路图10 三极管输入特性曲线Rbe=dx/dy=1.08 kohm3)输出特性曲线及Rce求值:图11 求三极管输出特性的电路图12 输出特性曲线Rce=dx/dy=15.133 kohm4)电压增益已知测量值: Av=160.84 理论值:8.816608.1.1//15.1332//.15*07.133////'-=-=-=be C L v r Rce R R A β%6.3%100*88.1664.81608.8166|'|||'=-=-=v v v A A A E 在误差允许范围值内5. 输入电阻图13 求输入电阻的电路测量值 R i =7.007/7.665×1000=914.16ohm 理论值R i ‘=ohm 8.18661010//6.5//08.11b //)4//(Rbe 1=+=+)(R Rw R输出电阻:%.55%100*8.18666.19148.1866'=-=-=i i i R R R E6. 输出电阻图14 求输出电阻的电路测量值 Ro=7.071/3.604=1.962 kohm 理论值 Ro ‘≈ Rc = 2.1 kohm%7.6%100*1.26.91.12''=-=-=o oo R R R E 在误差允许范围内(7) 频率响应特性曲线根据上限频率和下限频率的定义,当放大倍数下降到中频的0.707倍对应的频率时,即将读数指针移到幅度为中频的0.707倍处,读出读数指针的示数(如上图所示),即下限频率KHz f L 609.61=,上限频率MHz f H 8637.34=四.实验小结本次实验对单级放大电路进行仿真,通过实验掌握了对放大电路的静态工作点分析,三极管输入输出特性曲线的绘制以及电路的幅频相频图等方法。

在实验中,由于对静态工作点的选择还是存在一些误差,使信号没有达到最大不失真,从而导致后面所测得的数据有误差;同时在选取数据的时候不时非常合理,从而造成一定的误差,所以实验结果与理论上有一点误差,但是都在误差允许范围内。

实验结论这是EDA 的第一个实验,由于比较陌生所以做的时候感觉比较困难,做的时间也比较长,实验过程中遇到不明白的地方及时向老师请教解决问题,如此反复加深了对实验的理解,同时对单级放大电路有了更深的理解。

实验二差动放大电路的设计与仿真一、实验目的1)掌握带有恒流源的差动放大电路的静态工作点的调试方法;2)掌握带有恒流源的差动放大电路的共模电压放大倍数以及差模放大倍数二、实验要求1.给出差动放大电路原理图。

2.给出电路每个三极管的静态工作点值和 、R be 、R ce值。

3.给出双端输入直流小信号时电路的A VD、A VD1、A VC、A VC1值,并和理论计算值作比较。

4.分析实验结果。

三、实验步骤1.实验电路图图1 实验电路空载时A VD=595.252/20=29.763>20满足实验要求2. 测试三极管静态工作点图2 三极管的静态工作点由图可知:Q1.Q2静态工作点:I b1=I b2=3.77312uA Ic1=Ic2=400.929uAU ce1= U ce2=8.612V 所以β1=β2=106.259 Q3的静态工作点:I b3=6.86388uA I c3=809.403uAU ce=7.147V 所以β3=117.922 (1)Q1Q2输入特性分析:图3 求Q1Q2输入特性电路图4 Q1Q2输入特性曲线可得:R be1= R be2 4.38kohm(2)Q1Q2输出特性分析:图5 Q1Q2输出特性曲线可得:R ce1= R ce2 d x/d y=113.27 kohm(3) Q3输入输出特性分析:图6 求Q3输入输出特性的电路图7 Q3输入输出特性曲线可得:R be3=d x/d y=3.5472 kohm(4) Q3输出特性分析:图8 Q3输出特性曲线可得Rce3=d x/d y=545.5 kohm3. 测试电路的A VD、A VD1、A VC、A VC1值(1)直流小信号双端输入双端差模输出:图9 直流小信号双端输入双端差模输出电路测量值:A VD=-1678/40=-41.95理论值:A VD′=-β1(R c // R ce)/[R b+R be+(1+β1)R W/2]=-44.15 E=( A VD′- A VD)÷ A VD′×100%=5.0% 在误差允许范围之内(2)直流小信号双端输入单端输出:测量差模单端输出的电压增益时,因为静态电流的影响,会造成较大的误差,所以可以采用两组信号,即两组结果来算,可以尽量的减小误差。

图10 直流小信号双端输入单端输出图11a 输入为40mv时的输出电压图11b 输入为20mv时的输出电压测量值:A VD1=(7152-7570)/(40-20)=20.9理论值:A VD1‵=1/2 A VD′=22.08E= ( A VD1‘-A VD1)/ A VD1‘=5.3%(3)直流小信号双端输入双端共模输出:图11 双端共模输入双端输出电路测量值:通过观察可知,A VC≈0理论值:因为输入电压为0,所以A VC‵=0所以测量值与理论值基本上相等。

(4)直流小信号双端输入单端共模输出:图12 有激励时节点2的电压图13无激励时节点2的电压Avc1 = (7.99072-7.99068)÷20×1000=0.002R o=R ce3(1+ )R6/(R be3+R6+R7//R8)=2439.03 kohm‵=R3/2/R o=0.00205理论值Avc1E=( Avc1‵- Avc1)÷Avc1‵×100%=2.4% 在误差允许范围内,满足实验要求。

四、实验小结实验结论差动电路具有放大差模信号,抑制共模信号的良好特性,差摸输入时,其输入电阻等于半边电路输入电阻的两倍。

而带恒流源的差动放大电路则有极高的共模抑制比,实验的结果也证明了这一点:当双端输入直流小信号时,无论是单端输出还是双端输出,共模输入时的输出均几乎零,而差模输入时的输出不为零。

小结:本次实验对差动放大电路进行仿真,通过实验掌握了差动放大电路在双端﹑单端输出下的差模﹑共模增益的求解,并与理论计算结果相比较,所得的实验值与理论值吻合的很好。

但是由于实验数据选取时的手动操作造成不可避免的误差,所以得到的实验结果还是存在一定的误差。

实验三负反馈放大电路的设计与仿真一、实验目的1、掌握阻容耦合放大电路的静态工作点的调试方法。

2、掌握多级放大电路的电压放大倍数,输入电阻,输出电阻的测试方法。

3、掌握阻容耦合多级放大电路的频率特性。

二、实验要求1.给出引入电压串联负反馈电路的实验接线图。

2.给出两级放大电路的电路原理图。

3.给出负反馈接入前后电路的放大倍数、输入电阻、输出电阻,并验证A F 1/F。

4.给出负反馈接入前后电路的频率特性和f L、f H值,以及输出开始出现失真时的输入信号幅度。

5.分析实验结果。

三、实验步骤1.阻容耦合两级放大电压串联负反馈电路原理图:图一阻容耦合两级放大电压串联负反馈电路原理图2.未接入反馈时的电路图图二未接入反馈时的电路图3.第一级放大电路的波形:图三第一级放大电路波形由示波器显示可知第一级输出不失真4. 第二级放大电路的波形:图四第二级放大电路波形由示波器显示可知第二级输出不失真6.无反馈时图五测量无负反馈时的电压放大倍数的电路图放大倍数为:197.233/0.707=278.972输入电阻为:707/0.131808=5.364 kohm图六测量无负反馈时的输出电阻的电路图输出电阻为:1000/0.260016=3.8459k0hm6.接入反馈后:图七测量有负反馈时的电压放大倍数的电路图放大倍数为:18.759/0.707=26.533输入电阻为:707/0.109248=6.899 kohm图八测量有负反馈时的输出电阻的电路图所以输出电阻为:1000/0.010172=0.9831kohm7. 验证A F 1/FF=Re1/(Re1+Rf)=200/5300=0.0377 A F=26.533 1/A F=1/26.533=0.03768可以看出A F≈1/F,两者的相对误差为E=(F-1/A F)/F=0.5%,所以A F≈1/F成立。