CLC018AJVJQ中文资料

常州市凯丽金电子有限公司 KELIKING ELECTRONIC 微型贴片电声元器件 KLJ-853

A.SCOPE 範疇This specification applies magnetic buzzer.KLJ-8530-3627此規格書適用於贴片電磁式蜂鳴器. KLJ-8530-3627B.SPECIFICATION 规格NO.ltemUnitSpecificationCondition1Rated Voltage 額定電壓Vo-p3.62Operating Volt 操作電壓Vo-p 2.5~4.53Mean Current 平均耗電流mA Max. 100Applying rated voltage. 2731HZ squar wave. 1/2duty 施以額定電壓.2731HZ.方波.50%負載4Coil Resistance 直流阻抗Ω16±35Sound Output輸出音壓dBA Min.85Distance at 10cm (A-weight). Applying rated voltage 2731HZ.square wave.1/2duty在10cm 處,施以額定電壓。

2731HZ.方波.50%負載6Rated Frequency 額定頻率HZ 27317Operating Temp 操作温度℃-30 ~+708Storage Temp 儲存温度℃-40 ~+809Dimension 尺寸mm L8.5×W/8.5×H3.0See attached drawing.請參照外觀尺寸圖10Weight 重量gram 0.611Material 材質L.C.P (Black)12Terminal 端子SMD type (鍍全錫/Plating Sn)See attached drawing.請參照外觀尺寸圖13EnvironmentalProtection Regulation环保法规RoHS14Storage life保存期限month66 months preservation at room temp.(25±3℃).Humidity30%在室溫下25±3℃.湿度30%以下可保存6個月C.TYPICAL FREQUENCY RESPONSE CURVE 頻率響應曲線D.APPEARANCE DRAWING 外觀尺寸图Tol:±0.3Unit:mmNO.ltem Test condition Evaluation standard1Solderability焊錫附著性Lead terminals are immersed in solder bath of +260±5℃for3±1Second.端子置於錫膏內.錫膏溫度:+260±5℃. 焊接時間:3±1秒95% surface of lead pads must be covered withfresh solder锡膏需覆盖端子上方95%2Soldering HeatResistance焊錫耐熱性The product is followed the reflow temperature curve to testIts reflow thermostability產品依照迴焊溫度曲線測試迴焊耐熱性No interference in operation操作上无任何不良3TerminalMechanicalStrength端子強度Lead pads shall be soldered on the pc board.and the force9.8N(1.0kg)shall be applied behind the part for 10 seconds將端子焊在PC板上后,對單體施以9.8N(1.0kg)拉力10秒No damage and cutting of端子不松动,不脱落4Vibration震動測試Buzzer shall be measured after being applied vibration of amplitudeof 1.5mm with 10 to 55hz band of vibration frequencyto each of 3per-pendicular directions for 6 hours震動週波數10~55HZ.全振幅1.5mm于X.Y.Z 3個方向.各6小時After the test the part shall meet specificationsWith-out any damage in appearance and the SPLShould be in±10dBA compared with initial one经测试后,单体除音壓外外觀及电气特性须符合规格,輸出音壓变化量须±10dBA内5Drop test落下測試The part only shall be dropped from a height of 75cm onto a 40mm thick wooden board 3 times in 3 axes(X.Y.Z).(a total of 9 times).單體從75公分高處.X.Y.Z. 3個方向.各3回.落于40mm厚木板上.H.ENVIRONMENT TEST 环境测试NO.ltem Test condition Evaluation standard1High temp test高温测试After being placed in a chamber at +80℃for 48 hours.置于+80℃环境中48小时After the test the part shall meetspecifications with-out anydegradation in appearance andperformance except SPL. After 4hours at +25℃.the SPL should bein±10dBA compared with initial one经测试后,静置于+25℃(室温)环境中4小时候,单体除音壓外,外觀及电气特性须符合规格,輸出音壓变化量需在±10dBA内2Low temp test低温测试After being placed in a chamber at -40℃for 48 hours.置于-40℃环境中48小时3Therman Shock热冲撃实验The part shall be subjected to 10 cycles.One cycle shall consist of:对单体施以热冲击实验10次循环.其循环内容如图示4Temp./HumidityCycle温度/湿度循环测试The part shall be subjected to 10 cycles. One cycle shall be 24 hoursand consist of单体承受温度/湿度循环测试10次.其循环内容如图示I.RELIABILITY TEST 信赖性测试No.ltem Test conditionEvaluation standard1Operating life test 寿命测试1. Ordinary temperature 室温寿命测试The part shall be subjected to 100 hours at room temperature with 3.0V.4000HZ applied(+25±10℃)下.输入3.0V.4000HZ 连续操作100小时2. High temperature 高温寿命测试The part shall be subjected to 50 hours at +55℃with 3.0V.4000HZ applied在+55℃环境下,输入3.0V.4000HZ 连续操作50小时3. Low temperature 低温寿命测试The part shall be subjected to 50 hours at -30℃with3.0V.4000HZ applied在-30℃环境下,输入3.0V.4000HZ 连续操作50小时After the test the part shall meet Specifications with-out any degradation in appearance and Performance except. SPL. after 4 hours at +25℃.the SPL.should be in +10dBA compared with initial one.经测试后,静置于+25℃(室温)环境中4小时后,单体除音壓外,外觀及电气特性须符合规格,輸出音壓变化量需在±10dBA 内TEST CONDITION.Standard Test Condition : a) Temperature:+5~+35℃ b)Humidity:45-85% c)Pressure:860-1060mbar一般测试条件 : a)温度:+5~+35℃ b)湿度:45-85% c)气压:860-1060mbar Judament Test Condition: a)Temperature:+25±2℃ b)Humidity:60-70% c)Pressure:860-1060mbar爭譩时测试条件 : a)温度:+25±2℃ b)温度:60-70% c)气压:860-1060mbarJ.Recommended Temperature Profile For Reflow Oven 建議回焊爐溫度曲线K.Recommended land pattern 建議基板設計尺寸圖L.PACKING STANDARD 包裝規格。

SMBJ18CA中文规格书

SMBJ5.0(C)A – SMBJ200ADocument number: DS19002 Rev. 20 - 2 1 of 6 May 2017© Diodes Incorporated Features∙600W Peak Pulse Power Dissipation ∙5.0V to 200V Standoff Voltages ∙Glass Passivated Die Construction ∙Uni- and Bi-Directional Versions Available ∙Excellent Clamping Capability ∙Lead-Free Finish; RoHS Compliant (Notes 1 & 2) ∙Halogen and Antimony Free. “Green” Device (Note 3)Mechanical Data ∙Case: SMB ∙Case Material: Molded Plastic.UL Flammability Classification Rating 94V-0∙Moisture Sensitivity: Level 1 per J-STD-020∙Terminals: Lead Free Plating (Matte Tin Finish).Solderable per MIL-STD-202, Method 208∙Weight: 0.1 grams (Approximate)Ordering Information (Note 4)*x = Device Voltage, e.g., SMBJ170A-13-F.Notes: 1.EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant. All applicable RoHS exemptions applied.2.See http:///quality/lead_free.html for more information about Diodes Incorporated’s definitions of Hal ogen- and Antimony-free, "Green" and Lead-free.3.Halogen- and Antimony-free "Green” products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.4.For packaging details, go to our website at /design/support/packaging/diodes-packaging/. Marking InformationBi-Directional Device Cathode Band for Uni-Directional DeviceTop View Bottom Viewxx = Product Type Marking Code (See Page 3) = Manufacturers’ Code MarkingYWW = Date Code MarkingY = Last Digit of Year (ex: 7 for 2017)WW = Week Code (01 to 53)YWWxx 找电子元器件上宇航军工SMBJ5.0(C)A – SMBJ200A Document number: DS19002 Rev. 20 - 22 of 6 May 2017© Diodes IncorporatedThermal CharacteristicsNotes: 5. Valid provided that terminals are kept at ambient temperature.6. Measured with 8.3ms single half sine-wave. Duty cycle = 4 pulses per minute maximum.7. Unidirectional units only.SMBJ5.0(C)A – SMBJ200A Document number: DS19002 Rev. 20 - 2 6 of 6 May 2017© Diodes IncorporatedSuggested Pad LayoutPlease see http:///package-outlines.html for the latest version.SMB。

JR劲锐佳芯片各型号使用明细

我司强势推出大电流电源IC\电源管理IC及大小功率的充电器IC,广泛应用在DVD, DVB(机顶盒),便携式DVD,车载DVD/VCD,液晶电视,液晶显示器,路由器,车载充电器,电瓶车控制电路板,车载冰箱,汽车音响,恒流串联LED灯驱动, VOIP,Audio,LCDM及各种小家电产品.XLSEMI产品应用领域1.DVB(机顶盒):XL1513,XL1580,XL1410(12V-1.8V/3.3V/5V/1A)2.Portable DVD:XL1410(12V-5V/3.3V/1.8V/1A),XL1580/XL1583(12 V-5V/1A)3.Video:XL1509-5.0S(12V-5V/1A)4.收音机电源:XL1509-ADJ,XL2576,XL2596组合DVD带音响/台式大收音机(带机芯):XL2576,XL2596,XL1509-ADJ5. LCD TV:XL1509-5.0/3.3、XL2596-5.0、6. LCDM:XL2596-5.0(12V-5V/3A),XL2596-3.3(15寸、17寸),XL15 07-5.0(12V-5V/1.5A)7. Audio:XL2596-5.0(12V-5V/3A)8. VOIP:XL1509-3.3(12V-3.3V/2A、12V-5V/1A),XL2596-3.39. 路由器:XL1509,XL1509-3.3,XL1410,XL151310. 液晶显示器:XL1501-3.3(12V-3.3V/3A)11.32寸以上液晶电视:XL4015(24V-12V/3A、24V-5V/5A)12.电梯控制板电源:XL2576,XL259613.锂电池包(多节锂电串联),移动电源,电池组,需恒压恒流充电:XL4001,XL4101,XL4015+358大功率锂电池包供电:XL6019,,XL6008,XL6007替代FP5138+MOS14.笔记本串联锂电池升压:XL6019,XL6008(12V~16V转19V/3A)15.车载MP3,MP4:XL1509,XL4001,XL1513(12V-5V/1 A)车载GPS:XL2596,XL150916.车载DVD:XL1507(12V-5V/1.5A,24V-5V/1.5A),XL1583(12V-5V/1.5A)17.公交车,出租车LED点阵显示屏:XL2576(24~36V转5V/1A)18.车载冰箱,汽车音响:XL4016(24V-12V/8A)19.车载充电器;XL1583,XL1410(12V~24V转5V/2A)XL4001,XL2001(12V~36V转5V/1.8A)XL4201,XL4101,XL2011,XL2012(12V~36V转5V/2.1A)XL4501,XL2013,(12V~36V转5V/3.1A~4.4A)XL1509(12V~36V转5V/1.5A),XL2576P(12V~36V转5V/1.5A),XL2576(12V~36V转5V/2A),XL2596(12V~36V转5V/2A),XL4013(12~24V转5V/3A),XL4015(12~24V转5V/4A),XL2001(12~24V转5V/1.8A),XL2011(12~24V转5V/2.1A),XL2012(12~24V转5V/2.4A),XL2013(12~24V转5V/3.2A),车充产品可以替代GL2576,GL2596,AX3007,AX3111,ACT4515,ACT4070,49 4+MOS,7500+MOS等方案20.上网本,笔记本车载充电器:60W以下的应用XL6009,XL6010,XL6011替代FP5138+MOS的方案,优点:线路简单,可靠性高升压方案(输入:10V~14V,输出:16V/19V,输出电流:2A,3A)升降压方案(输入:10V~30V,输出:12V/19V,输出电流:2A,3A)21.MR16射灯:XL30023*1W,4*1W ,5*1WLED模组驱动AC12V(DC10~16V)电子变压器升压供电:XL6003 5~7*1W,XL6005 10*1W车顶灯恒压输出,降压结构:XL1509车顶灯恒压输出,升压结构:XL6007,XL6008车顶灯恒压输出,升降压结构:XL6007,XL6008舞台灯XL2576,XL150922.电瓶车控制电路板:XL7001(60V转12V/5V/0.5A)23.安防产品:车载摄像头(小摄像头)供电:XL1509,XL1513小区,马路,建筑用的大摄像头,高速球供电:XL2596,XL1501摄像头里面用红外的LED灯驱动:XL1513,XL1530,XL1410市电和蓄电池混合供电:需要升降压应用XL6007,XL6008小区,大厦可视门铃对讲4寸,7寸屏供电:XL1509-ADJ,XL1410,XL1513,XL15 83(12V转5V/500mA)指示灯板:XL1513,XL141024.液晶电视数字屏,解码板电源驱动板:XL1513,XL153025.太阳能路灯,路标灯,庭院灯和5V~32V低压供电LED驱动,升降压应用领域:XL6003,XL6004,XL600526.大功率车载电源,降压,限流:XL4003+358,XL4005+358,XL4012+35827.降压型应用:XL4003,XL4005,XL4012可以替代PWM IC+MOS管等类似方案升压型应用:XL6007,XL6009,XL6010可以替代PWM IC+MOS管等类似方案升降压型应用:SEPIC BUCK-BOOST结构XL6007,XL6009,XL6010可以替代P WM IC+MOS管类似方案28.DVB:XL6007,XL6008马达天线供电(12V BOOST 19V/800mA)可以替代PWM IC+MOS管类似方案 CCD/CATVPMP/DSC/DSV/STB/VGA CardDPF(数码相框)PDALE D Panel背光LCD Panel背光移动电源应急充电器,可以替代FP5210+MOS,FP6210升压应用领域29.升压,恒压LED模组驱动:XL6007,XL6008,可以替代FP5210+MOS,FP621 0升压应用领域30.17寸以下LED背光驱动:XL6007,可以替代AMC3202的应用领域[1]XL14102APWM降压DC/DC,SOP8,输入3.6-18V,输出1.22V-16V转换效率高达90%,可替代BM1410A,TD1410,AP1512,AP1513,RM1410,GT1510,EC94 10,EC9410C,SD46520,ACT4060功能兼容AOZ1010AI,AOZ1015AI,EC9406[2]XL15833APWM降压DC/DC,SOP8,输入3.6-20V,输出1.23V-18V转换效率高达90%,可替代MP2355,ACT4060,MP1583,ZA3020,AOZ1014,MP1593[3]XL15132APWM降压DC/DC,SOP8,输入3.6-18V,输出0.8V-16V转换效率高达90%,可替代AP1513,OCP2020,BM1513/A,AX3101,RM2060,CX1513,EC9 413,AP1510,AP1520,AP1533,AP1534,AP5002功能兼容AOZ1010AI,AOZ1015AI,EC9406[4]XL15303APWM降压DC/DC,SOP8,输入3.6-18V,输出0.8V-16V转换效率高达90%,可替代AP1530,AP1538,AP1539,[5]XL25763APWM降压DC/DC,TO263/TO220,输入电压范围3.6-45V,可完全替换AE2576,BM2576,TD2576,AP1512/A,LM2576,LM2576,MIK2575,MIK2576A MC2576,OCP2006,HWD2575,EC942576[6]XL25963APWM降压DC/DC,TO263/TO220,输入电压范围3.6-45V,可完全替换AE2596,BM2596,TD2596,AP1501/A,AP1506,LM2596,AMC2596,MIK2596,OCP2011,OCP2016,GT1500,GT1504,AX2596,EC9401,CM2596S[7]XL15092APWM降压DC/DC,SOP8,输入3.6-36V,转换效率高达90%,功能替换LM2594,AE1509,TD1509,AP1509,OCP2019,HWD61410,EC9409,CM25 93.[8]XL4001,XL4101,XL4201,XL4501车载充电器,点烟器,恒流LED驱动,专用芯片150K2A/3A外部可调限流PWM降压DC/DC输入4.6V-40V可替代2576+431+324方案,34063+MOS+431+324方案[9]XL15073APWM降压DC/DC,TO252,输入3.6-36V,转换效率高达85%可完全替换AE1507,TD1507,AP1507,OCP2017,EC9407[10]XL4015大电流5APWM降压DC/DC,输入8-36V,输出0.8V-33V转换效率高达95%(功能兼容)---AOZ1014,LM2677,LM2678,LM2679[11]XL4012大电流12APWM降压DC/DC,TO220输入8-40V,输出0.8V-33V转换效率高达95%(功能兼容)---LM2677,LM2678,LM2679。

UPD178P018KK资料

device production, and early development and time-to-market. The µPD178P018 is a PROM version corresponding to the µPD178004, 178006, and 178016.

• HALT mode • STOP mode

Note When using the I2C bus mode (including when this mode is implemented by program without using the peripheral hardware), consult your local NEC sales representative when you place an order for mask.

Expansion RAM : 2048 bytes

Buffer RAM

: 32 bytes

8 bits × 32 registers (8 bits × 8 registers × 4 banks) With variable instruction execution time function 0.44 µs/0.88 µs/1.78 µs/3.56 µs/7.11 µs/14.22 µs (with 4.5-MHz crystal resonator)

Reference frequency Charge pump Phase comparator Frequency counter

15KW-8KW锂电充电机中英文说明书doc

高频PFC 1.5KW 锂电池充电机 1.5KW HF/PFC Lithium Battery Charger型号Models尺寸Size (mm):348(L) × 180(W) × 140(H)注:锂电池充电机的型号将根据锂电池组的实际最高电压来标注。

Note: Model of the Lithium battery charger will be marked in response to the actual maximum voltage for the Lithium battery pack.高频PFC 2KW 锂电池充电机 2KW HF/PFC Lithium Battery Charger型号Models尺寸Size (mm):349(L) × 198(W) × 139(H)注:锂电池充电机的型号将根据锂电池组的实际最高电压来标注。

Note: Model of the Lithium battery charger will be marked in response to the actual maximum voltage for the Lithium battery pack锂电池充电机Lithium Battery Charger输出电压最大值 Vout Max 输出电流最大值Iout Max TCCH-H35-40 34.6V 40A TCCH-H51-33 51.1V 33A TCCH-H65-25 65V 25A TCCH-H90-20 89.8V 20A TCCH-H104-16 104V 16A TCCH-H114-14 114V 14A TCCH-H130-12 130V 12A TCCH-H161-10161V 10A TCCH-H203-08203V 8A TCCH-H217-08217V 8A TCCH-H258-6A2 258V 6.2A TCCH-H320-05320V 5A锂电池充电机 Lithium Battery Charger 输出电压最大值 Vout Max输出电流最大值Iout Max TCCH-H66-35 66V 35A TCCH-H83-30 82.6V 30A TCCH-H96-25 96.2V 25A TCCH-H112-21 112V 21A TCCH-H130-18 130V 18A TCCH-H145-16 144.7V 16A TCCH-H168-15 168V 15A TCCH-H192-12 192V 12A TCCH-H208-11 208V 11A TCCH-H234-10 233.3V 10A TCCH-H243-09 243V 9A TCCH-H258-09 258V 9A TCCH-H290-08 289.5V 8A TCCH-H337-7A2 337V 7.2 TCCH-H389-06 389V 6A TCCH-H417-5A5 417V5.5A高频PFC 3KW 锂电池充电机 3KW HF/PFC Lithium Battery Charger型号Models尺寸size (mm):257(L) × 254(W) × 179(H)注:锂电池充电机的型号将根据锂电池组的实际最高电压来标注。

CLC001_DataSheet

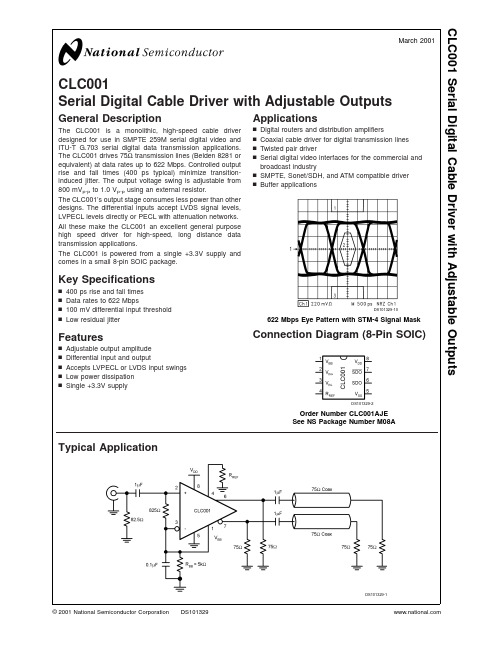

CLC001Serial Digital Cable Driver with Adjustable OutputsGeneral DescriptionThe CLC001is a monolithic,high-speed cable driver designed for use in SMPTE 259M serial digital video and ITU-T G.703serial digital data transmission applications.The CLC001drives 75Ωtransmission lines (Belden 8281or equivalent)at data rates up to 622Mbps.Controlled output rise and fall times (400ps typical)minimize transition-induced jitter.The output voltage swing is adjustable from 800mV p-p to 1.0V p-p using an external resistor.The CLC001’s output stage consumes less power than other designs.The differential inputs accept LVDS signal levels,LVPECL levels directly or PECL with attenuation networks.All these make the CLC001an excellent general purpose high speed driver for high-speed,long distance data transmission applications.The CLC001is powered from a single +3.3V supply and comes in a small 8-pin SOIC package.Key Specificationsn 400ps rise and fall times n Data rates to 622Mbpsn 100mV differential input threshold nLow residual jitterFeaturesn Adjustable output amplitude n Differential input and outputn Accepts LVPECL or LVDS input swings n Low power dissipation nSingle +3.3V supplyApplicationsn Digital routers and distribution amplifiersn Coaxial cable driver for digital transmission lines n Twisted pair drivernSerial digital video interfaces for the commercial and broadcast industryn SMPTE,Sonet/SDH,and ATM compatible driver n Buffer applicationsConnection Diagram (8-Pin SOIC)Typical ApplicationDS101329-10622Mbps Eye Pattern with STM-4Signal MaskDS101329-1March 2001CLC001Serial Digital Cable Driver with Adjustable Outputs©2001National Semiconductor Corporation Absolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Supply Voltage 4V Output Current27mA Maximum Junction Temperature +125˚CStorage Temperature Range −65˚C to +150˚CLead Temperature(Soldering 10seconds)+300˚CESD Rating (HBM)≥7kV ESD Rating (MM)≥500V Package Thermal Resistance θJA Surface Mount AJE 125˚C/W θJC Surface Mount AJE 105˚C/WReliability Information Transistor count291Recommended Operating ConditionsSupply Voltage Range (V DD -V SS )+3.0V to +3.6V Operating Free Air Temperature (T A )-40˚C to +85˚C R BB Range (applied to V BB input)(Note 6)1.3k Ωto 11.5k ΩElectrical CharacteristicsOver recommended operating supply and temperature ranges unless otherwise specified (Notes 2and 3)Symbol ParameterConditionsMin Typ Max Units OUTPUT DC SPECIFICATIONSV SDOSerial Driver Output VoltageR L =75Ω1%,R REF =1.91k Ω1%(for 800mV p-p ),Figure 1720800880mVR L =75Ω1%,R REF =1.5k Ω1%(for 1.0V p-p ),Figure 190010001100mVINPUT DC SPECIFICATIONS V TH Differential Input High Threshold V CM =+0.05V or +1.2V or +3.25V,0+100mV V TL Differential Input Low Threshold V DD =3.3V−1000mV V CMR Common Mode Voltage Range V ID =100mV,V DD =3.3V0.053.25V I IN Input Current V IN =0V or +3.0V,V DD =3.6V or 0V ±1±10µA I INBInput Current BalanceV IN =0V or +3.0V,V DD =3.6V or 0V,(Note 8)0.23µASUPPLY CURRENT I DDTotal Dynamic Power Supply Current (includes load current)R L =75Ω,R REF =1.91k Ω1%(V SDO =800mV p-p @270Mbps)70115mAR L =75Ω,R REF =1.5k Ω1%(V SDO =1.0V p-p @622Mbps)85130mAMISCELLANEOUS PARAMETERS L GEN Output Inductance 6nH R GEN Output Resistance 25k ΩI BBV BB CurrentR REF =1.91k Ω1%,(Note 6)250µA R REF =1.5k Ω1%,(Note 6)315µAC L C 001 2CLC001 AC Electrical CharacteristicsOver recommended operating supply and temperature ranges unless otherwise specified(Note3)Symbol Parameter Conditions Min Typ Max Unitst r,t f Rise time,Fall time20%–80%,(Notes4,5)400800pst os Output overshoot5%t jit Output jitter(Note7)25pst pd Propagation delay(Note5) 1.9nsNote1:“Absolute Maximum Ratings”are those values beyond which the safety of the device cannot be guaranteed.They are not meant to imply that the devicesshould be operated at these limits.The table of“Electrical Characteristics”specifies conditions of device operation.Note2:Current flow into device pins is defined as positive.Current flow out of device pins is defined as negative.All voltages are stated referenced to V SS=0V.Note3:Typical values are at25˚C and3.3V.Note4:This parameter is Guaranteed by Design.Note5:R L=75Ω,AC-coupled at270Mbps,R REF=1.91kΩ1%(for V SDO=800mV p-p±10%),C L not greater than5pF(See Figure1)Note6:The V BB output is intended as a bias supply pin for the inputs of this device only.It is not designed as a power supply output and should not be used topower other devices.Note7:R L=75Ω,AC-coupled at622Mbps,R REF=1.5kΩ1%(for V SDO=1.0V p-p±10%),clock pattern input.Note8:Input Current Balance(I INB)is the difference between the Input Current(I IN)on V IN+and V IN−for the same bias condition.Test Loads ArrayDS101329-4FIGURE1.Test Loads3Test Loads(Continued)Pin DescriptionsPin #Name Description1V BB Optional,bias voltage (may be used to bias inputs)-see device operation section for details.If unused leave as no connect (NC).2V IN+Positive input pin 3V IN-Negative input pin4R REF Output driver level control.Connect a resistor to ground to set output voltage swing.5V SS Negative power supply 6SDO Serial data true output 7SDO Serial data complement output 8V DDPositive power supplyDS101329-3FIGURE 2.Test CircuitC L C 001 4Device OperationINPUT INTERFACINGNumerous input configurations exist for applying PECL,LVPECL,and LVDS signals to the input of the CLC001.Inputs may be single-ended or differential,AC or DC coupled.The V BB pin may be used to provide a DC bias voltage to the inputs.Leave this pin as a no connect when no bias is needed.Note that DC-coupled inputs such as direct LVDS and LVPECL connections are self-biasing and do not require use of the V BB pin.I BB ,the current produced by the V BB pin,depends on R REF .For a given R REF ,the I BB current will remain constant,and the bias voltage is determined by the value of resistance,R BB ,between the V BB pin and ground.Figure 3and Figure 4show how R BB corresponds to some common V BB values with R REF held at 1.91k Ωand 1.5k Ω,respectively.Some common input configurations are shown in Figure 5through Figure 9.DS101329-11FIGURE 3.R BB vs.V BB for R REF =1.91k ΩDS101329-12FIGURE 4.R BB vs.V BB for R REF =1.5k ΩCLC0015Device Operation(Continued)Figure 5shows the CLC001with an AC-coupled,single ended input connection.The 82.5Ωresister in parallelwith 825Ωgives the equivalent termination resistance of 75Ω.R BB set at 5k Ωprovides 1.25V of DC bias to the input.A typical DC-coupled,twisted pair cable connection is shown in Figure 6.The CLC001is driven differentially.The line is terminated with a termination resistor equal to the impedance of the line being driven.The actual resistor value is media specific,but typically is between 100and120Ωdepending upon the cable.This resistor should be located close to the CLC001inputs pins to minimize the resulting stub length between the resistor and device pads.DS101329-5FIGURE 5.Single Ended 75ΩCoaxial Cable,AC-coupledDS101329-6FIGURE 6.Twisted Pair Cable,DC-coupledC L C 001 6Device Operation(Continued)Figure 7shows an AC-coupled,twisted pair cable application.It implements a center tap capacitancetermination used in conjunction with two 50Ωresistors to filter common mode noise.R BB set at 5k Ωprovides 1.25V of DC bias to each input.PECL or LVPECL drivers may be interfaced to the CLC001as shown in Figure 8.The voltage divider network will reduce the PECL output to the proper levels.For LVPECL,the 100Ωseries resistors should beremoved,since the common mode range inputs of the CLC001are wide enough to accept LVPECL levels directly.No external DC biasing is required for PECL/LVPECL connections.DS101329-7FIGURE 7.Twisted Pair Cable,AC-coupledDS101329-8FIGURE 8.PECL,DC-coupledCLC0017Device Operation(Continued)A typical LVDS input connection is shown in Figure 9.The media is driven differentially by an LVDS driver.The line is terminated with a termination resistor equal to the impedance of the line being driven.The actual resistor value is media specific,but typically is between 100and120Ω.This resistor should be located close to the CLC001inputs pins to minimize the resulting stub length between the resistor and device pads.The CLC001supports ±100mV thresholds across the entire LVDS common mode range of 0.1V to 2.3V for a 200mV differential signal.DS101329-9FIGURE 9.LVDS,DC-coupledC L C 001 8Device Operation(Continued)OUTPUT INTERFACINGThe CLC001has two complementary,ground referenced outputs designed to drive AC-coupled and terminated 75Ωcoaxial cables.The outputs are single ended; however,they could be treated as a single differential output as long as current paths from each output go to ground.The output of the CLC001is a high impedance current source.It expects to see a75Ωshunt resistor before driving cable to convert the current output to a voltage and provide proper back-matching.No series back-matching resistors should be used.Refer to Typical Application for an illustration.Output levels range from800mV p-p to1.0V p-p±10%into 75ΩAC-coupled,back-matched loads.Output level is controlled by the value of R REF connected to pin4.R REF is1.91kΩ±1%for800mV p-p,and1.5kΩ±1%for1.0 V p-p.Refer to Figure10for the output level’s sensitivity to R REF.The CLC001is designed as an AC-coupled75Ωcable driver.It is not intended to drive50Ωloads.The current source output does not provide enough current to allow for800mV across a50Ωdoubly terminated load.Evaluation BoardEvaluation boards are available for a nominal charge that demonstrate the basic operation of the SDI/SDV/SDH devices.The evaluation boards can be ordered through National’s Distributors.Supplies are limited,please check for current availability.The SD001EVK evaluation kit for the CLC001,Serial Digital Cable Driver with Adjustable Outputs,provides an operating environment in which the cable driver can be evaluated by system/hardware designers.The evaluation board has all the needed circuitry and connectors for easy connection and checkout of the device circuit options as discussed in the CLC001datasheet.A schematic,parts list and pictorial drawing are provided with the board.From the WWW,the following information may be viewed/ downloaded for most evaluation boards: /appinfo/interface•Device Datasheet and/or EVK User Manual•View a picture of the EVK•View the EVK Schematic•View the top assembly drawing and BOM•View the bottom assembly drawing and BOMPCB Layout RecommendationsPrinted circuit board layout affects the performance of the CLC001.The following guidelines will aid in achieving satisfactory device performance.•Use a ground plane or power/ground plane sandwich design for optimum performance.•Bypass device power with a0.01µF monolithic ceramic capacitor in parallel with a6.8µF tantalum electrolytic capacitor located no more than0.1″(2.5mm)from the device power pins.•Provide short,symmetrical ground return paths for:—inputs,—supply bypass capacitors and—the output load.•Provide short,grounded guard traces located —under the centerline of the package,—0.1″(2.5mm)from the package pins—on both top and bottom of the board with connecting vias.DS101329-13FIGURE10.Output level’s sensitivity to R REFCLC0019Physical Dimensionsinches (millimeters)unless otherwise notedLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:ap.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507Order Number CLC001AJE NS Package Number M08AC L C 001S e r i a lD i g i t a l C a b l e D r i v e r w i t h A d j u s t a b l e O u t p u t sNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

郎汉德PLC产品说明书

郎汉德PLC产品说明书LonHand-PLC文件版本:V1.0.2目录1.产品简介 (3)1.1产品概述 (3)1.2功能特点 (3)2.参数详情 (4)2.1电气参数 (4)2.2编程电缆参数 (5)2.3选型表 (6)2.4引脚定义 (8)2.4.1LH-M1410T(晶体管输出) (8)2.4.2LH-M1616T(晶体管输出) (9)2.4.3LH-M0808T(晶体管输出) (9)2.4.4LH-M1408R(继电器输出) (10)2.4.5LH-M0808R(继电器输出) (11)2.5PLC地址 (12)2.5.1PLC地址使用情况 (12)2.5.2特殊寄存器和位 (14)2.6模拟量转换 (18)2.7兼容三菱指令 (19)3.通信使用 (24)3.1串口通信配置 (24)3.2RS485通讯示例 (25)3.2.1PLC作为3U协议从站 (25)3.2.2PLC作为Modbus从站 (25)3.2.3PLC平时作为Modbus从站,临时切到3U下程序 (27)3.3自由通信协议ADPRW (28)3.3.1串口自由通信协议ADPRW指令使用 (28)3.3.2Modbus主站通信协议ADPRW指令使用 (30)4.售后 (32)5.更新历史 (32)1.产品简介1.1产品概述本PLC尺寸小巧,接口丰富,扩展性强,支持3U编程风格。

广泛应用于工业自动化领域。

1.2功能特点●极具有成本优势的高端PLC,支持3U编程风格;●外观紧凑,极省空间;可拔插压接端子,便于维护和调试;●直流供电,电源与外部隔离;●所有通讯口均隔离;●支持扩展,最大15个;●输出可支持NPN晶体管,继电器;●具有混合型主机以及混合型扩展模块,可有效节省模块数量;●最大编程步16K2.参数详情PLC 主机模块和PLC扩展模块的外观尺寸一致,如下图:2.1电气参数类别项目参数电气环境供电电源额定24V,12-32V 宽压输入范围;内部与外供电电气隔离工作温度-20~55°C湿度5%-95%RH (非结露)抗干扰性峰值:1500vp-p;幅度1uS;上升时间:30ms ;周期30-100HZ 抗震动符合IEC61121-2标准电气隔离性能通讯隔离性通讯口均与内部隔离电源隔离性内部5V、15V 之间隔离;与24V 输入隔离数字量量输入导通状态高于DC 15V,2.5mA 关断状态低于DC 7V,1mA晶体管输出响应时间ON->OFF20us以内OFF->ON50us以内输出电压范围DC5V~30V额定输出负载0.75A@DC24V继电器输出响应时间10ms以内输出电压范围DC5V-30或AC5V~250V 额定输出电压DC24V/2A或AC220V/2.0A 使用寿命机械1千万次电气10万次(额定负载)模拟量输出输出范围电压输出0~10V 电流输出0~20mA模拟量输入输入范围电流输入0-20mA或4-20mA 电压输入0-10V运动控制脉冲输出速度可达200KHZ 计数输入速度可200K以上2.2编程电缆参数本PLC对应的编程口为RS232通信。

LD-801原理图

Байду номын сангаасC1

C2

D

VCC C14 15P C15 15P D7 D6 D5 D4 D3 D2 GND D1 D0 MWRMRDCLE ALE GPIO_C1 VDD 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 D7 D6 D5 D4 D3 D2 GND D1 D0 MWR# MRD# CLE ALE GPIOC1 GPIOC0 VDD

Thursday, March 20, 2008 Sheet

1

Rev V1.0

1

of

3

5

4

3

2

PDF 文件使用 "pdfFactory Pro" 试用版本创建

5

4

3

2

1

U7

1

D

VSSD RCH VDDD RF_VDD VDDH RF_VSS VPLL MOD_OUT RF_OUT LC_OUT

R13 GPIO_B4

NC

C

RESET-

VCC 显示屏导光板 LED

R4 R6

47R 1K Q2 8050

C48 PAVCC

VRDA

D2

LED

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

VCC URES GND USBDP USBDM RESETPAVCC AOUTR AOUTL GND VRDA

R18 33K

1 2 3 4 5

A

1

J3

USB Port

精诚科技

Title

A

RF-AS6001

Size A4 Date:

L7805CV中文资料

August 2006Rev. 131/47L7800 seriesPositive voltage regulatorsFeature summary■Output current to 1.5A■Output voltages of 5; 5.2; 6; 8; 8.5; 9; 10; 12; 15; 18; 24V■Thermal overload protection ■Short circuit protection■Output transition SOA protectionDescriptionThe L7800 series of three-terminal positiveregulators is available in TO-220, TO-220FP , TO-3 and D 2PAK packages and several fixed output voltages, making it useful in a wide range of applications. These regulators can provide local on-card regulation, eliminating the distribution problems associated with single point regulation. Each type employs internal current limiting, thermal shut-down and safe area protection, making it essentially indestructible. If adequate heat sinking is provided, they can deliver over 1A output current. Although designedprimarily as fixed voltage regulators, thesedevices can be used with external components to obtain adjustable voltage and currents.Schematic diagramL7800 series2/47Contents1Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 2Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 3Test circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 4Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 5Typical performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 6Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 7Order code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 8Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47L7800 series Pin configuration 1 Pin configurationMaximum ratings L7800 series4/472 Maximum ratingsNote:Absolute Maximum Ratings are those values beyond which damage to the device mayoccur. Functional operation under these condition is not impliedTable 1.Absolute maximum ratingsSymbol ParameterValue Unit V I DC Input voltage for V O = 5 to 18V 35Vfor V O = 20, 24V40I O Output current Internally Limited P D Power dissipationInternally LimitedT STG Storage temperature range-65 to 150°C T OPOperating junction temperature rangefor L7800-55 to 150°C for L7800C0 to 150Table 2.Thermal DataSymbol ParameterD 2PAK TO-220TO-220FPTO-3Unit R thJC Thermal resistance junction-case 3554°C/W R thJAThermal resistance junction-ambient62.5506035°C/WL7800 series Test circuits 3 Test circuits5/47Electrical characteristics L7800 series6/474Electrical characteristicsTable 3.Electrical characteristics of L7805 (refer to the test circuits, T J = -55 to 150°C, V I = 10V, I O = 500 mA, C I = 0.33 µF , C O = 0.1 µF unless otherwise specified)Symbol ParameterTest conditionsMin.Typ.Max.Unit V O Output voltage T J = 25°C4.855.2V V O Output voltage I O = 5mA to 1A, P O ≤ 15W V I = 8 to 20V4.655 5.35V ∆V O (1)1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.Line regulationV I = 7 to 25V , T J = 25°C 350mVV I = 8 to 12V , T J = 25°C 125∆V O (1)Load regulation I O = 5 mA to 1.5A, T J = 25°C 100mV I O = 250 to 750mA, T J = 25°C 25I d Quiescent current T J = 25°C 6mA ∆I d Quiescent current change I O = 5mA to 1A 0.5mA V I = 8 to 25 V 0.8∆V O /∆T Output voltage drift I O = 5mA0.6mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C 40µV/V O SVR Supply voltage rejection V I = 8 to 18V , f = 120Hz 68dB V d Dropout voltage I O = 1A, T J = 25°C 2 2.5V R O Output resistance f = 1 KHz17m ΩI sc Short circuit current V I = 35V , T J = 25°C 0.75 1.2A I scpShort circuit peak currentT J = 25°C1.32.23.3AL7800 series Electrical characteristics7/47Table 4.Electrical characteristics of L7806 (refer to the test circuits, T J = -55 to 150°C, V I = 11V, I O = 500 mA, C I = 0.33 µF , C O = 0.1 µF unless otherwise specified)Symbol ParameterTest conditionsMin.Typ.Max.Unit V O Output voltage T J = 25°C5.7566.25V V O Output voltage I O = 5mA to 1A, P O ≤ 15W V I = 9 to 21V5.6566.35V ∆V O (1)Line regulationV I = 8 to 25V , T J = 25°C 60mVV I = 9 to 13V , T J = 25°C 30∆V O (1)Load regulation I O = 5 mA to 1.5A, T J = 25°C 100mV I O = 250 to 750mA, T J = 25°C 30I d Quiescent current T J = 25°C 6mA ∆I d Quiescent current change I O = 5mA to 1A 0.5mA V I = 9 to 25V 0.8∆V O /∆T Output voltage drift I O = 5mA0.7mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C 40µV/V O SVR Supply voltage rejection V I = 9 to 19V , f = 120Hz 65dB V d Dropout voltage I O = 1A, T J = 25°C 2 2.5V R O Output resistance f = 1 KHz19m ΩI sc Short circuit current V I = 35V , T J = 25°C 0.75 1.2A I scpShort circuit peak currentT J = 25°C1.32.23.3A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.Electrical characteristics L7800 series8/47Table 5.Electrical characteristics of L7808 (refer to the test circuits, T J = -55 to 150°C, V I = 14V, I O = 500 mA, C I = 0.33 µF , C O = 0.1 µF unless otherwise specified)Symbol ParameterTest conditionsMin.Typ.Max.Unit V O Output voltage T J = 25°C7.788.3V V O Output voltage I O = 5mA to 1A, P O ≤ 15W V I = 11.5 to 23V7.688.4V ∆V O (1)Line regulationV I = 10.5 to 25V , T J = 25°C 80mVV I = 11 to 17V , T J = 25°C 40∆V O (1)Load regulation I O = 5 mA to 1.5A, T J = 25°C 100mV I O = 250 to 750mA, T J = 25°C 40I d Quiescent current T J = 25°C 6mA ∆I d Quiescent current change I O = 5mA to 1A 0.5mA V I = 11.5 to 25V 0.8∆V O /∆T Output voltage drift I O = 5mA1mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C 40µV/V O SVR Supply voltage rejection V I = 11.5 to 21.5V , f = 120Hz 62dB V d Dropout voltage I O = 1A, T J = 25°C 2 2.5V R O Output resistance f = 1 KHz16m ΩI sc Short circuit current V I = 35V , T J = 25°C 0.75 1.2A I scpShort circuit peak currentT J = 25°C1.32.23.3A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.L7800 series Electrical characteristics9/47Table 6.Electrical characteristics of L7812 (refer to the test circuits, T J = -55 to 150°C, V I = 19V, I O = 500 mA, C I = 0.33 µF , C O = 0.1 µF unless otherwise specified)Symbol ParameterTest conditionsMin.Typ.Max.Unit V O Output voltage T J = 25°C11.51212.5V V O Output voltage I O = 5mA to 1A, P O ≤ 15W V I = 15.5 to 27V11.41212.6V ∆V O (1)Line regulationV I = 14.5 to 30V , T J = 25°C 120mVV I = 16 to 22V , T J = 25°C 60∆V O (1)Load regulation I O = 5 mA to 1.5A, T J = 25°C 100mV I O = 250 to 750mA, T J = 25°C 60I d Quiescent current T J = 25°C 6mA ∆I d Quiescent current change I O = 5mA to 1A 0.5mA V I = 15 to 30V 0.8∆V O /∆T Output voltage drift I O = 5mA1.5mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C 40µV/V O SVR Supply voltage rejection V I = 15 to 25V , f = 120Hz 61dB V d Dropout voltage I O = 1A, T J = 25°C 2 2.5V R O Output resistance f = 1 KHz18m ΩI sc Short circuit current V I = 35V , T J = 25°C 0.75 1.2A I scpShort circuit peak currentT J = 25°C1.32.23.3A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.Table 7.Electrical characteristics of L7815 (refer to the test circuits, T J = -55 to 150°C, V I = 23V, I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified)Symbol Parameter Test conditions Min.Typ.Max.Unit V O Output voltage T J = 25°C14.41515.6VV O Output voltage I O = 5mA to 1A, P O≤15WV I = 18.5 to 30V14.251515.75V∆V O(1)Line regulation V I = 17.5 to 30V, T J = 25°C150mV V I = 20 to 26V, T J = 25°C75∆V O(1)Load regulation I O = 5 mA to 1.5A, T J = 25°C150mV I O = 250 to 750mA, T J = 25°C75I d Quiescent current T J = 25°C6mA∆I d Quiescent current change I O = 5mA to 1A0.5mA V I = 18.5 to 30V0.8∆V O/∆T Output voltage drift I O = 5mA 1.8mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C40µV/V O SVR Supply voltage rejection V I = 18.5 to 28.5V, f = 120Hz60dB V d Dropout voltage I O = 1A, T J = 25°C2 2.5V R O Output resistance f = 1 KHz19mΩI sc Short circuit current V I = 35V, T J = 25°C0.75 1.2AI scp Short circuit peak current T J = 25°C 1.3 2.2 3.3A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.10/47Table 8.Electrical characteristics of L7818 (refer to the test circuits, T J = -55 to 150°C, V I = 26V, I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified)Symbol Parameter Test conditions Min.Typ.Max.Unit V O Output voltage T J = 25°C17.31818.7VV O Output voltage I O = 5mA to 1A, P O≤ 15WV I = 22 to 33V17.11818.9V∆V O(1)Line regulation V I = 21 to 33V, T J = 25°C180mV V I = 24 to 30V, T J = 25°C90∆V O(1)Load regulation I O = 5 mA to 1.5A, T J = 25°C180mV I O = 250 to 750mA, T J = 25°C90I d Quiescent current T J = 25°C6mA∆I d Quiescent current change I O = 5mA to 1A0.5mA V I = 22 to 33V0.8∆V O/∆T Output voltage drift I O = 5mA 2.3mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C40µV/V O SVR Supply voltage rejection V I = 22 to 32V, f = 120Hz59dB V d Dropout voltage I O = 1A, T J = 25°C2 2.5V R O Output resistance f = 1 KHz22mΩI sc Short circuit current V I = 35V, T J = 25°C0.75 1.2AI scp Short circuit peak current T J = 25°C 1.3 2.2 3.3A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.11/47Table 9.Electrical characteristics of L7820 (refer to the test circuits, T J = -55 to 150°C, V I = 28V, I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified)Symbol Parameter Test conditions Min.Typ.Max.Unit V O Output voltage T J = 25°C19.22020.8VV O Output voltage I O = 5mA to 1A, P O≤15WV I = 24 to 35V192021V∆V O(1)Line regulation V I = 22.5 to 35V, T J = 25°C200mV V I = 26 to 32V, T J = 25°C100∆V O(1)Load regulation I O = 5 mA to 1.5A, T J = 25°C200mV I O = 250 to 750mA, T J = 25°C100I d Quiescent current T J = 25°C6mA∆I d Quiescent current change I O = 5mA to 1A0.5mA V I = 24 to 35V0.8∆V O/∆T Output voltage drift I O = 5mA 2.5mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C40µV/V O SVR Supply voltage rejection V I = 24 to 35V, f = 120Hz58dB V d Dropout voltage I O = 1A, T J = 25°C2 2.5V R O Output resistance f = 1 KHz24mΩI sc Short circuit current V I = 35V, T J = 25°C0.75 1.2AI scp Short circuit peak current T J = 25°C 1.3 2.2 3.3A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.12/47Table 10.Electrical characteristics of L7824 (refer to the test circuits, T J = -55 to 150°C, V I = 33V, I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified)Symbol Parameter Test conditions Min.Typ.Max.Unit V O Output voltage T J = 25°C232425VV O Output voltage I O = 5mA to 1A, P O≤15WV I = 28 to 38V22.82425.2V∆V O(1)Line regulation V I = 27 to 38V, T J = 25°C240mV V I = 30 to 36V, T J = 25°C120∆V O(1)Load regulation I O = 5 mA to 1.5A, T J = 25°C240mV I O = 250 to 750mA, T J = 25°C120I d Quiescent current T J = 25°C6mA∆I d Quiescent current change I O = 5mA to 1A0.5mA V I = 28 to 38V0.8∆V O/∆T Output voltage drift I O = 5mA3mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C40µV/V O SVR Supply voltage rejection V I = 28 to 38V, f = 120Hz56dB V d Dropout voltage I O = 1A, T J = 25°C2 2.5V R O Output resistance f = 1 KHz28mΩI sc Short circuit current V I = 35V, T J = 25°C0.75 1.2AI scp Short circuit peak current T J = 25°C 1.3 2.2 3.3A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.13/47Table 11.Electrical characteristics of L7805C (refer to the test circuits, T J = -55 to 150°C, V I = 10V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified)Symbol Parameter Test conditions Min.Typ.Max.Unit V O Output voltage T J = 25°C 4.85 5.2VV O Output voltage I O = 5mA to 1A, P O≤15WV I = 7 to 20V4.7555.25V∆V O(1)Line regulation V I = 7 to 25V, T J = 25°C3100mV V I = 8 to 12V, T J = 25°C150∆V O(1)Load regulation I O = 5 mA to 1.5A, T J = 25°C100mV I O = 250 to 750mA, T J = 25°C50I d Quiescent current T J = 25°C8mA∆I d Quiescent current change I O = 5mA to 1A0.5mA V I = 7 to 25 V0.8∆V O/∆T Output voltage drift I O = 5mA-1.1mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C40µV/V O SVR Supply voltage rejection V I = 8 to 18V, f = 120Hz62dB V d Dropout voltage I O = 1A, T J = 25°C2V R O Output resistance f = 1 KHz17mΩI sc Short circuit current V I = 35V, T J = 25°C0.75AI scp Short circuit peak current T J = 25°C 2.2A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.14/47Table 12.Electrical characteristics of L7852C (refer to the test circuits, T J = -55 to 150°C, V I = 10V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified)Symbol Parameter Test conditions Min.Typ.Max.Unit V O Output voltage T J = 25°C 5.0 5.2 5.4VV O Output voltage I O = 5mA to 1A, P O≤15WV I = 8 to 20V4.955.2 5.45V∆V O(1)Line regulation V I = 7 to 25V, T J = 25°C3105mV V I = 8 to 12V, T J = 25°C152∆V O(1)Load regulation I O = 5 mA to 1.5A, T J = 25°C105mV I O = 250 to 750mA, T J = 25°C52I d Quiescent current T J = 25°C8mA∆I d Quiescent current change I O = 5mA to 1A0.5mA V I = 7 to 25 V 1.3∆V O/∆T Output voltage drift I O = 5mA-1mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C42µV/V O SVR Supply voltage rejection V I = 8 to 18V, f = 120Hz61dB V d Dropout voltage I O = 1A, T J = 25°C2V R O Output resistance f = 1 KHz17mΩI sc Short circuit current V I = 35V, T J = 25°C0.75AI scp Short circuit peak current T J = 25°C 2.2A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.15/47Table 13.Electrical characteristics of L7806C (refer to the test circuits, T J = -55 to 150°C, V I = 11V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified)Symbol Parameter Test conditions Min.Typ.Max.Unit V O Output voltage T J = 25°C 5.756 6.25VV O Output voltage I O = 5mA to 1A, P O≤15WV I = 8 to 21V5.766.3V∆V O(1)Line regulation V I = 8 to 25V, T J = 25°C120mV V I = 9 to 13V, T J = 25°C60∆V O(1)Load regulation I O = 5 mA to 1.5A, T J = 25°C120mV I O = 250 to 750mA, T J = 25°C60I d Quiescent current T J = 25°C8mA∆I d Quiescent current change I O = 5mA to 1A0.5mA V I = 8 to 25V 1.3∆V O/∆T Output voltage drift I O = 5mA-0.8mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C45µV/V O SVR Supply voltage rejection V I = 9 to 19V, f = 120Hz59dB V d Dropout voltage I O = 1A, T J = 25°C2V R O Output resistance f = 1 KHz19mΩI sc Short circuit current V I = 35V, T J = 25°C0.55AI scp Short circuit peak current T J = 25°C 2.2A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.16/47Table 14.Electrical characteristics of L7808C (refer to the test circuits, T J = -55 to 150°C, V I = 14V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified)Symbol Parameter Test conditions Min.Typ.Max.Unit V O Output voltage T J = 25°C7.788.3VV O Output voltage I O = 5mA to 1A, P O≤15WV I = 10.5 to 25V7.688.4V∆V O(1)Line regulation V I = 10.5 to 25V, T J = 25°C160mV V I = 11 to 17V, T J = 25°C80∆V O(1)Load regulation I O = 5 mA to 1.5A, T J = 25°C160mV I O = 250 to 750mA, T J = 25°C80I d Quiescent current T J = 25°C8mA∆I d Quiescent current change I O = 5mA to 1A0.5mA V I = 10.5 to 25V1∆V O/∆T Output voltage drift I O = 5mA-0.8mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C52µV/V O SVR Supply voltage rejection V I = 11.5 to 21.5V, f = 120Hz56dB V d Dropout voltage I O = 1A, T J = 25°C2V R O Output resistance f = 1 KHz16mΩI sc Short circuit current V I = 35V, T J = 25°C0.45AI scp Short circuit peak current T J = 25°C 2.2A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.17/47Table 15.Electrical characteristics of L7885C (refer to the test circuits, T J = -55 to 150°C, V I =14.5V, I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified)Symbol Parameter Test conditions Min.Typ.Max.Unit V O Output voltage T J = 25°C8.28.58.8VV O Output voltage I O = 5mA to 1A, P O≤15WV I = 11 to 26V8.18.58.9V∆V O(1)Line regulation V I = 11 to 27V, T J = 25°C160mV V I = 11.5 to 17.5V, T J = 25°C80∆V O(1)Load regulation I O = 5 mA to 1.5A, T J = 25°C160mV I O = 250 to 750mA, T J = 25°C80I d Quiescent current T J = 25°C8mA∆I d Quiescent current change I O = 5mA to 1A0.5mA V I = 11 to 27V1∆V O/∆T Output voltage drift I O = 5mA-0.8mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C55µV/V O SVR Supply voltage rejection V I = 12 to 22V, f = 120Hz56dB V d Dropout voltage I O = 1A, T J = 25°C2V R O Output resistance f = 1 KHz16mΩI sc Short circuit current V I = 35V, T J = 25°C0.45AI scp Short circuit peak current T J = 25°C 2.2A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.18/47Table 16.Electrical characteristics of L7809C (refer to the test circuits, T J = -55 to 150°C, V I = 15V,I O = 500 mA, C I = 0.33 µF, C O = 0.1 µF unless otherwise specified)Symbol Parameter Test conditions Min.Typ.Max.Unit V O Output voltage T J = 25°C8.6499.36VV O Output voltage I O = 5mA to 1A, P O≤ 15WV I = 11.5 to 26V8.5599.45V∆V O(1)Line regulation V I = 11.5 to 26V, T J = 25°C180mV V I = 12 to 18V, T J = 25°C90∆V O(1)Load regulation I O = 5 mA to 1.5A, T J = 25°C180mV I O = 250 to 750mA, T J = 25°C90I d Quiescent current T J = 25°C8mA∆I d Quiescent current change I O = 5mA to 1A0.5mA V I = 11.5 to 26V1∆V O/∆T Output voltage drift I O = 5mA-1mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C70µV/V O SVR Supply voltage rejection V I = 12 to 23V, f = 120Hz55dB V d Dropout voltage I O = 1A, T J = 25°C2V R O Output resistance f = 1 KHz17mΩI sc Short circuit current V I = 35V, T J = 25°C0.40AI scp Short circuit peak current T J = 25°C 2.2A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.19/47Electrical characteristics L7800 series20/47Table 17.Electrical characteristics of L7810C (refer to the test circuits, T J = -55 to 150°C, V I = 15V , I O = 500 mA, C I = 0.33 µF , C O = 0.1 µF unless otherwise specified)Symbol ParameterTest conditionsMin.Typ.Max.Unit V O Output voltage T J = 25°C9.61010.4V V O Output voltage I O = 5mA to 1A, P O ≤ 15W V I = 12.5 to 26V9.51010.5V ∆V O (1)Line regulationV I = 12.5 to 26V , T J = 25°C 200mVV I = 13.5 to 19V , T J = 25°C 100∆V O (1)Load regulation I O = 5 mA to 1.5A, T J = 25°C 200mV I O = 250 to 750mA, T J = 25°C 100I d Quiescent current T J = 25°C 8mA ∆I d Quiescent current change I O = 5mA to 1A 0.5mA V I = 12.5 to 26V 1∆V O /∆T Output voltage drift I O = 5mA-1mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C 70µV/V O SVR Supply voltage rejection V I = 13 to 23V , f = 120Hz 55dB V d Dropout voltage I O = 1A, T J = 25°C 2V R O Output resistance f = 1 KHz17m ΩI sc Short circuit current V I = 35V , T J = 25°C 0.40A I scpShort circuit peak currentT J = 25°C2.2A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.L7800 series Electrical characteristics21/47Table 18.Electrical characteristics of L7812C (refer to the test circuits, T J = -55 to 150°C, V I = 19V , I O = 500 mA, C I = 0.33 µF , C O = 0.1 µF unless otherwise specified)Symbol ParameterTest conditionsMin.Typ.Max.Unit V O Output voltage T J = 25°C11.51212.5V V O Output voltage I O = 5mA to 1A, P O ≤ 15W V I = 14.5 to 27V11.41212.6V ∆V O (1)Line regulationV I = 14.5 to 30V , T J = 25°C 240mVV I = 16 to 22V , T J = 25°C 120∆V O (1)Load regulation I O = 5 mA to 1.5A, T J = 25°C 240mV I O = 250 to 750mA, T J = 25°C 120I d Quiescent current T J = 25°C 8mA ∆I d Quiescent current change I O = 5mA to 1A 0.5mA V I = 14.5 to 30V 1∆V O /∆T Output voltage drift I O = 5mA-1mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C 75µV/V O SVR Supply voltage rejection V I = 15 to 25V , f = 120Hz 55dB V d Dropout voltage I O = 1A, T J = 25°C 2V R O Output resistance f = 1 KHz18m ΩI sc Short circuit current V I = 35V , T J = 25°C 0.35A I scpShort circuit peak currentT J = 25°C2.2A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.Electrical characteristics L7800 series22/47Table 19.Electrical characteristics of L7815C (refer to the test circuits, T J = -55 to 150°C, V I = 23V , I O = 500 mA, C I = 0.33 µF , C O = 0.1 µF unless otherwise specified)Symbol ParameterTest conditionsMin.Typ.Max.Unit V O Output voltage T J = 25°C14.51515.6V V O Output voltage I O = 5mA to 1A, P O ≤ 15W V I = 17.5 to 30V14.251515.75V ∆V O (1)Line regulationV I = 17.5 to 30V , T J = 25°C 300mVV I = 20 to 26V , T J = 25°C 150∆V O (1)Load regulation I O = 5 mA to 1.5A, T J = 25°C 300mV I O = 250 to 750mA, T J = 25°C 150I d Quiescent current T J = 25°C 8mA ∆I d Quiescent current change I O = 5mA to 1A 0.5mA V I = 17.5 to 30V 1∆V O /∆T Output voltage drift I O = 5mA-1mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C 90µV/V O SVR Supply voltage rejection V I = 18.5 to 28.5V , f = 120Hz 54dB V d Dropout voltage I O = 1A, T J = 25°C 2V R O Output resistance f = 1 KHz19m ΩI sc Short circuit current V I = 35V , T J = 25°C 0.23A I scpShort circuit peak currentT J = 25°C2.2A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.L7800 series Electrical characteristics23/47Table 20.Electrical characteristics of L7818C (refer to the test circuits, T J = -55 to 150°C, V I = 26V , I O = 500 mA, C I = 0.33 µF , C O = 0.1 µF unless otherwise specified)Symbol ParameterTest conditionsMin.Typ.Max.Unit V O Output voltage T J = 25°C17.31818.7V V O Output voltage I O = 5mA to 1A, P O ≤ 15W V I = 21 to 33V17.11818.9V ∆V O (1)Line regulationV I = 21 to 33V , T J = 25°C 360mVV I = 24 to 30V , T J = 25°C 180∆V O (1)Load regulation I O = 5 mA to 1.5A, T J = 25°C 360mV I O = 250 to 750mA, T J = 25°C 180I d Quiescent current T J = 25°C 8mA ∆I d Quiescent current change I O = 5mA to 1A 0.5mA V I = 21 to 33V 1∆V O /∆T Output voltage drift I O = 5mA-1mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C 110µV/V O SVR Supply voltage rejection V I = 22 to 32V , f = 120Hz 53dB V d Dropout voltage I O = 1A, T J = 25°C 2V R O Output resistance f = 1 KHz22m ΩI sc Short circuit current V I = 35V , T J = 25°C 0.20A I scpShort circuit peak currentT J = 25°C2.1A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.Electrical characteristics L7800 series24/47Table 21.Electrical characteristics of L7820C (refer to the test circuits, T J = -55 to 150°C, V I = 28V , I O = 500 mA, C I = 0.33 µF , C O = 0.1 µF unless otherwise specified)Symbol ParameterTest conditionsMin.Typ.Max.Unit V O Output voltage T J = 25°C19.22020.8V V O Output voltage I O = 5mA to 1A, P O ≤ 15W V I = 23 to 35V192021V ∆V O (1)Line regulationV I = 22.5 to 35V , T J = 25°C 400mVV I = 26 to 32V , T J = 25°C 200∆V O (1)Load regulation I O = 5 mA to 1.5A, T J = 25°C 400mV I O = 250 to 750mA, T J = 25°C 200I d Quiescent current T J = 25°C 8mA ∆I d Quiescent current change I O = 5mA to 1A 0.5mA V I = 23 to 35V 1∆V O /∆T Output voltage drift I O = 5mA-1mV/°C eN Output noise voltage B =10Hz to 100KHz, T J = 25°C 150µV/V O SVR Supply voltage rejection V I = 24 to 35V , f = 120Hz 52dB V d Dropout voltage I O = 1A, T J = 25°C 2V R O Output resistance f = 1 KHz24m ΩI sc Short circuit current V I = 35V , T J = 25°C 0.18A I scpShort circuit peak currentT J = 25°C2.1A1.Load and line regulation are specified at constant junction temperature. Changes in V O due to heating effects must betaken into account separately. Pulse testing with low duty cycle is used.。

CZ80PIO资料

CZ80PIOPeripheral DeviceMegafunctionGeneral DescriptionThe CZ80PIO, hereinafter referred to as PIO, is a dual-port device which can be programmed by the system software to function as a broad range of peripheral devices that are compatible with the Z80CPU such as most keyboards, printers etc.System design is simplified because the PIO connects directly to the Z80CPU with no additional logic. In larger systems, address decoders and buffers may be required.The CZ80PIO is a microcode-free design developed for reuse in ASIC and FPGA implementations. The design is strictly synchronous, with no internal tri-states and a synchronous reset.SymbolFeatures• Provides a direct interface between Z80 microprocessor systems and peripheraldevices• Two ports with interrupt-driven handshake for fast response• Four programmable operating modes:• Output Mode (both ports)• Input Mode (both ports)• Bi-directional (Port A only)• Bit Control Mode (both ports)• Programmable interrupts on peripheral status conditionsApplications• Programmable, dual - port device• Interface for a wide range of peripheral devices such as:• Keyboards• Printers• Paper table readers• PROM programmers etc.Pin DescriptionName Type DescriptionClockclk In System ClockInterface to Processordata_tri Out Tristate controller for buffer for databusdata_i In Data bus inputdata_o Out Data bus output:rd_n In Read Cycle Statusiorq_n In Input / Output Requestce_n In Chip Enablecdselect In Control / Data selectportselect In Port B / A selectm1_n InMachineCycleOneInterrupt Service Routineint_n InInterruptRequestiei In Interrupt Enable Inputieo Out Interrupt Enable OutputControlporta_tri In Tristate controller for buffer for databusporta_i In Port B bus inputporta_o Out Port B bus outputportb_tri In Tristate controller for buffer for databusportb_i In Port B bus inputportb_o Out Port B bus outputardy Out Register A readybrdy Out Register B readyastb_n In Port A strobe pulse from peripheraldevicebstb_n In Port B strobe pulse from peripheraldeviceFunctional DescriptionThe CZ80PIO megafunction is partitioned intomodules as shown in figure 1 and describedbelow.Port LogicEach port contains separate input and outputregisters, handshake control logic and thecontrol registers. All data transfers between the peripheral unit and the CPU use the data inputand output registers. The handshake logicassociated with each port controls the datatransfers through the input and the outputregisters. The mode control register (two bits)selects one of the four programmable operating modes. The Bit Control mode (mode 3) uses the remaining registers. The input/output controlregister specifies which of the eight data bits in the port are to be outputs and enables these bits; the remaining bits are inputs. The mask register specifies which of the bits in the port are masked.Control logicThe control logic consists of the CPU bus interface logic, interrupt control logic and internal control logic. The CPU bus interface logic interfaces the CZ80PIO directly to the CZ80CPU, so no external logic is necessary. For large systems, however, address decoders and/or buffers may be necessary. The interrupt control logic section handles all CPU interrupt protocol for nested-priority interrupt structures. Any device's physical location in a daisy-chain configuration determines its priority. Two lines (IEO and IEI) are provided in each PIO to form this daisy chain. The device closest to the CPU has the highest priority. Within a PIO, port A interrupts have higher priority then those of port B. In the byte input, byte output or bi-directional modes, an interrupt can be generated whenever the peripheral requests a new byte transfer. In the bit control mode, an interrupt can be generated when the peripheral status matches a programmed value.Block DiagramFigure 1. CZ80PIO Peripheral Device Block DiagramDevice Utilization & PerformanceSupported Device Utilization PerformanceFamily Tested LEs Memory (MHz)Flex EPF10KE30-1 733 - 67MHz Acex EP1K30-1 731 - 67MHz Apex EP20KE30-1 748 - 70MHz Apex2 EP2A15-7 763 - 95MHz Cyclone EP1C3-6 583 - 120MHz Stratix EP1S10-5 583 - 132MHz Stratix-II EP2S15-3 561 - 218MHzNotes:1. Optimized for speed2. Assumes all I/O is routed off-chipDeliverablesNetlist License• Post-synthesis EDIF netlist• Testbench (self checking)• Vectors for testing the functionality of the megafunction• Place & Route Script• Constraint file• Simulation script• Documentation HDL Source License• VHDL or Verilog RTL source code• Testbench (self checking)• Vectors for testing the functionality of the megafunction• Simulation scripts• Synthesis scripts• DocumentationVerification MethodsThe CZ80PIO megafunction’s functionality was verified by means of a proprietary hardware modeler. The same stimulus was applied to a hardware model that contained the original Zilog Z80PIO chip, and the results compared with the megafunction’s simulation outputs.Megafunction ModificationsThe CZ80PIO megafunction can be modified to include additional new ports. Please contact CAST, Inc. directly for any required modifications.Contact InformationCAST, Inc.11 Stonewall CourtWoodcliff Lake, New Jersey 07677 USAPhone: +1 201-391-8300Fax: +1201-391-8694E-Mail: info@URL: This megafunction developed by peripheralcontroller experts at Evatronix SACopyright © CAST, Inc. 2004, All Rights Reserved. Contents subject to change without notice。

CY7C1417AV18资料

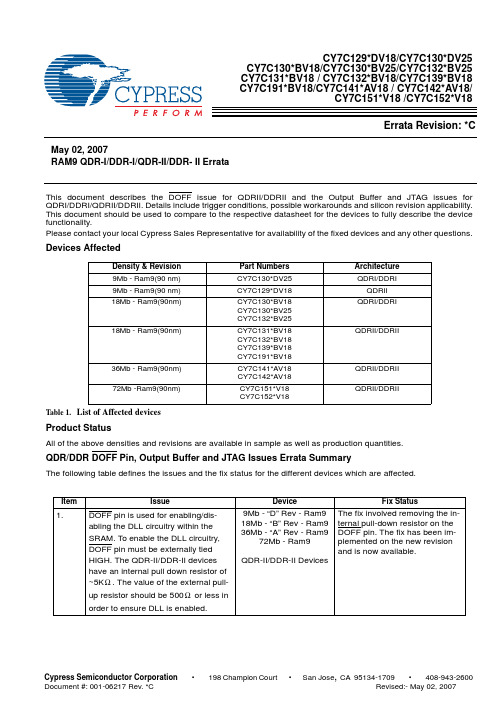

Errata Revision: *CMay 02, 2007RAM9 QDR-I/DDR-I/QDR-II/DDR- II ErrataCY7C129*DV18/CY7C130*DV25CY7C130*BV18/CY7C130*BV25/CY7C132*BV25CY7C131*BV18 / CY7C132*BV18/CY7C139*BV18CY7C191*BV18/CY7C141*AV18 / CY7C142*AV18/CY7C151*V18 /CY7C152*V18This document describes the DOFF issue for QDRII/DDRII and the Output Buffer and JTAG issues for QDRI/DDRI/QDRII/DDRII. Details include trigger conditions, possible workarounds and silicon revision applicability.This document should be used to compare to the respective datasheet for the devices to fully describe the device functionality.Please contact your local Cypress Sales Representative for availability of the fixed devices and any other questions.Devices AffectedTable 1. List of Affected devicesProduct StatusAll of the above densities and revisions are available in sample as well as production quantities.QDR/DDR DOFF Pin, Output Buffer and JTAG Issues Errata SummaryThe following table defines the issues and the fix status for the different devices which are affected.Density & Revision Part Numbers Architecture 9Mb - Ram9(90 nm)CY7C130*DV25QDRI/DDRI 9Mb - Ram9(90 nm)CY7C129*DV18QDRII 18Mb - Ram9(90nm)CY7C130*BV18CY7C130*BV25CY7C132*BV25QDRI/DDRI18Mb - Ram9(90nm)CY7C131*BV18CY7C132*BV18CY7C139*BV18CY7C191*BV18QDRII/DDRII36Mb - Ram9(90nm)CY7C141*AV18CY7C142*AV18QDRII/DDRII 72Mb -Ram9(90nm)CY7C151*V18CY7C152*V18QDRII/DDRIIItemIssueDeviceFix Status1.DOFF pin is used for enabling/dis-abling the DLL circuitry within the SRAM. To enable the DLL circuitry, DOFF pin must be externally tied HIGH. The QDR-II/DDR-II devices have an internal pull down resistor of ~5K . The value of the external pull-up resistor should be 500 or less in order to ensure DLL is enabled.9Mb - “D” Rev - Ram918Mb - “B” Rev - Ram936Mb - “A” Rev - Ram972Mb - Ram9QDR-II/DDR-II DevicesThe fix involved removing the in-ternal pull-down resistor on the DOFF pin. The fix has been im-plemented on the new revision and is now available.ΩΩTable 2.Issue Definition and fix status for different devices1. DOFF Pin Issue•ISSUE DEFINITIONThis issue involves the DLL not turning ON properly if a large resistor is used (eg:-10K ) as an external pullup resistor to enable the DLL. If a 10K or higher pullup resistor is used externally, the voltage on DOFF is not high enough to enable the DLL.•PARAMETERS AFFECTEDThe functionality of the device will be affected because of the DLL is not turning ON properly. When the DLL is enabled, all AC and DC parameters on the datasheet are met. •TRIGGER CONDITION(S)Having a 10K or higher external pullup resistor for disabling the DOFF pin.•SCOPE OF IMPACTThis issue will alter the normal functionality of the QDRII/DDRII devices when the DLL is disabled.•EXPLANATION OF ISSUEFigure 1 shows the DOFF pin circuit with an internal 5K internal resistor. The fix planned is to disable the internal 5K leaker.•WORKAROUND2.O/P Buffer enters a locked up unde-fined state after controls or clocks are left floating. No proper read/write access can be done on the device until a dummy read is performed.9Mb - “D” Rev - Ram918Mb - “B” Rev - Ram936Mb - “A” Rev - Ram972Mb - Ram9QDR-I/DDR-I/QDR-II/DDR-II Devices The fix has been implemented onthe new revision and is now avail-able.3.The EXTEST function in the JTAG test fails when input K clock is floating in the JTAG mode.9Mb - “D” Rev - Ram918Mb - “B” Rev - Ram936Mb - “A” Rev - Ram972Mb - Ram9QDR-I/DDR-I/QDR-II/DDR-II DevicesThe fix involved bypassing the ZQ circuitry in JTAG mode. This was done by overriding the ZQ circuit-ry by the JTAG signal. The fix has been implemented on the new re-vision and is now available.Figure 1.DOFF pin with the 5K internal resistorItemIssueDeviceFix StatusΩΩΩΩΩΩThe workaround is to have a low value of external pullup resistor for the DOFF pin (recommended value is <500). When DOFF pins from multiple QDR devices are connected through the same pull-up resistors on the board, it is recommended that this DOFF pin be directly connected to Vdd due to the lower effective resistance since the "leakers" are in parallel.Figure 2 shows the proposed workaround and the fix planned.•FIXSTATUSFix involved removing the internal pull-down resistor on the DOFF pin. The fix has been implemented on the new revision and is now available. The new revision is an increment of the existing revision. The following table lists the devices affected, current revision and the new revision after the fix.Table 3.List of Affected Devices and the new revison2.Output Buffer IssueFigure 2.Proposed workaround with the 500 external pullupCurrent Revision New Revision after the FixCY7C129*DV18CY7C129*EV18CY7C131*BV18CY7C131*CV18CY7C132*BV18CY7C132*CV18CY7C139*BV18CY7C139*CV18CY7C191*BV18CY7C191*CV18CY7C141*AV18CY7C141*BV18CY7C142*AV18CY7C142*BV18CY7C151*V18CY7C151*AV18CY7C152*V18CY7C152*AV18ΩΩ•ISSUE DEFINITIONThis issue involves the output buffer entering an unidentified state when the input signals (only Control signals or Clocks) are floating during reset or initialization of the memory controller after power up. •PARAMETERS AFFECTEDNo timing parameters are affected. The device may drive the outputs even though the read operation is not enabled. A dummy read is performed to clear this condition.•TRIGGER CONDITION(S)Input signals(namely RPS# for QDR-I/QDRII , WE# and LD# for DDR-I/DDRII) or Clocks (K/K# and/or C/C#) are floating during reset or initialization of the memory controller after power up.•SCOPE OF IMPACTThis issue will jeopardize any number of writes or reads which take place after the controls or clock are left floating. This can occur anywhere in the SRAM access ( all the way from power up of the memory device to transitions taking place for read/write accesses to the memory device) if the above trigger conditions are met.•EXPLANATION OF ISSUEFigure 3 shows the output register Reset circuit with an SR Latch circled. This latch has two inputs with one of them coming from some logic affected by the clock and RPS#(QDR) or WE# and LD#(DDR).The issue happens when clocks are glitching/toggling with controls floating. This will cause the SR latch to be taken into an unidentified state. The SR Latch will need to be reset by a dummy read operation if this happens. Array•WORKAROUNDThis is viable only if the customer has the trigger conditions met during reset or initialization of the memory controller after power up. In order for the workaround to perform properly, Cypress recommends the insertion of a minimum of 16 “dummy” READ operations to every SRAM device on the board prior to writing any meaningful data into the SRAM. After this one “dummy” READ operation, the device will perform properly.“Dummy” READ is defined as a read operation to the device that is not meant to retrieve required data. The “dummy” READ can be to any address location in the SRAM. Refer to Figure 4 for the dummy read implemen-tation.In systems where multiple SRAMs with multiple RPS# lines are used, a dummy read operation will have to be performed on every SRAM on the board. Below is an example sequence of events that can be performed before valid access can be performed on the SRAM.1) Initialize the Memory Controller2) Assert RPS# Low for each of the memory devicesNote:For all devices with x9 bus configuration, the following sequence needs to be performed:1) For the 72M / 36M / 18M x9 devices drive address pin A2 / A10 / A3 low respectively and perform dummyread.2) For the 72M / 36M / 18M x9 devices drive address pin A2 / A10 / A3 high respectively and perform dummyread.If the customer has the trigger conditions met during normal access to the memory then there is no workaround at this point.•FIX STATUSThe fix has been implemented on the new revision and is now available. The new revision is an increment of the existing revision. Please refer to Table 4 for the list of devices affected, current revision and the new revision after the fix.3. JTAG Mode Issue•ISSUE DEFINITIONIf the input clock (K Clock) is left floating when the device is in JTAG mode, spurious high frequency noise on this input can be interpreted by the device as valid clocks. This could cause the impedance matching circuitry (ZQ) on the QDR/DDR devices to periodically load itself with incorrect values. These incorrect values in the ZQ register could force the outputs into a High-Impedance state. The ZQ circuitry requires at least 1000 valid K clock cycles to drive the outputs from high impedance to low impedance levels.•PARAMETERS AFFECTEDThis issue only affects the EXTEST command when the device is in the JTAG mode. The normal functionality of the device will not be affected.•TRIGGER CONDITION(S)EXTEST command executed immediately after power-up without providing any K clock cycles.•SCOPE OF IMPACTThis issue only impacts the EXTEST command when device is tested in the JTAG mode. Normal functionality of the device is not affected. •EXPLANATION OF ISSUEImpedance matching circuitry (ZQ) is present on the QDR/DDR devices to set the desired impedance on the outputs. This ZQ circuitry is updated every 1000 clock cycles of K clock to ensure that the impedance of the O/P is set to valid state. However, when the device is operated in the JTAG mode immediately after power-up, high frequency noise on the input K clock can be treated by the ZQ circuitry as valid clocks thereby setting the outputs in to a high-impedance mode. If a minimum of 1000 valid K clocks are applied before performing the JTAG test, this should clear the ZQ circuitry and ensure that the outputs are driven to valid impedance levels.•WORKAROUNDElimination of the issue: After power-up, before any valid operations are performed on the device, insert a minimum of 1000 valid clocks on K input.•FIX STATUSThe fix involved bypassing the ZQ circuitry in JTAG mode. This was done by overriding the ZQ circuitry by the JTAG signal. The fix has been implemented on the new revision and is now available. The new revision is an increment of the existing revision. Please refer to Table 4 for the list of devices affected, current revision and the new revision after the fix..Table 4.List of Affected devices and the new revisionCurrent Revision New Revision after the FixCY7C129*DV18CY7C129*EV18CY7C130*DV25CY7C130*EV25CY7C130*BV18CY7C130*CV18CY7C130*BV25CY7C130*CV25CY7C132*BV25CY7C132*CV25CY7C131*BV18CY7C131*CV18CY7C132*BV18CY7C132*CV18CY7C139*BV18CY7C139*CV18CY7C191*BV18CY7C191*CV18CY7C141*AV18CY7C141*BV18CY7C142*AV18CY7C142*BV18CY7C151*V18CY7C151*AV18CY7C152*V18CY7C152*AV18ReferencesAll 90nm QDRI/DDRI/QDRII/DDRII datasheets:-Table 5.List of Datasheet spec# for the Affected devicesSpec#Part#DensityArchitecture38-05628CY7C1304DV259-MBIT QDR(TM) SRAM 4-WORD BURST 38-05632CY7C1308DV259-MBIT DDR-I SRAM 4-WORD BURST 001-00350CY7C1292DV18/1294DV189-MBIT QDR- II(TM) SRAM 2-WORD BURST 38-05621CY7C1316BV18/1916BV18/1318BV18/1320BV1818-MBIT DDR-II SRAM 2-WORD BURST 38-05622CY7C1317BV18/1917BV18/1319BV18/1321BV1818-MBIT DDR-II SRAM 4-WORD BURST 38-05623CY7C1392BV18/1393BV18/1394BV1818-MBIT DDR-II SIO SRAM 2-WORD BURST 38-05631CY7C1323BV2518-MBIT DDR-I SRAM 4-WORD BURST 38-05630CY7C1305BV25/1307BV2518-MBIT QDR(TM) SRAM 4-WORD BURST 38-05627CY7C1303BV25/1306BV2518-MBIT QDR(TM) SRAM 2-WORD BURST 38-05629CY7C1305BV18/1307BV1818-MBIT QDR(TM) SRAM 4-WORD BURST 38-05626CY7C1303BV18/1306BV1818-MBIT QDR(TM) SRAM 2-WORD BURST 38-05619CY7C1310BV18/1910BV18/1312BV18/1314BV1818-MBIT QDR - II (TM) SRAM 2-WORD BURST 38-05620CY7C1311BV18/1911BV18/1313BV18/1315BV1818-MBIT QDR - II SRAM 4-WORD BURST 38-05615CY7C1410AV18/1425AV18/1412AV18/1414AV1836-MBIT QDR-II(TM) SRAM 2-WORD BURST 38-05614CY7C1411AV18/1426AV18/1413AV18/1415AV1836-MBIT QDR(TM)-II SRAM 4-WORD BURST 38-05616CY7C1416AV18/1427AV18/1418AV18/1420AV1836-MBIT DDR-II SRAM 2-WORD BURST 38-05618CY7C1417AV18/1428AV18/1419AV18/1421AV1836-MBIT DDR-II SRAM 4-WORD BURST 38-05617CY7C1422AV18/1429AV18/1423AV18/1424AV1836-MBIT DDR-II SIO SRAM 2-WORD BURST 38-05489CY7C1510V18/1525V18/1512V18/1514V1872-MBIT QDR-II SRAM 2-WORD BURST 38-05363CY7C1511V18/1526V18/1513V18/1515V1872-MBIT QDR(TM)-II SRAM 4-WORD BURST 38-05563CY7C1516V18/1527V18/1518V18/1520V1872-MBIT DDR-II SRAM 2-WORD BURST 38-05565CY7C1517V18/1528V18/1519V18/1521V1872-MBIT DDR-II SRAM 4-WORD BURST 38-05564CY7C1522V18/1529V18/1523V18/1524V1872-MBITDDR-II SIO SRAM 2-WORD BURSTDocument History PageDocument Title: RAM9 QDR-I/DDR-I/QDR-II/DDR- II Errata Document #: 001-06217 Rev. *CREV.ECN NO.IssueDateOrig. ofChange Description of Change**419849See ECN REF New errata for Ram9 QDR2/DDR2 SRAMs.*A493936See ECN QKS Added Output buffer and JTAG mode issues, Item#2 and #3Added 9Mb QDR-II Burst of 2 and QDR-1/DDR-I part numbers.*B733176See ECN NJY Added missing part numbers in the title for Spec#’s 38-05615,38-05614,38-05363,38-05563 on Table 5 on page 7.*C1030020 See ECN TBE Updated the fix status of the three issues, and modified the description forthe Output Buffer workaround for x9 devices on page 5.。

飞利浦 CL81109SCN 2.4GHz 数字无绳电话用户手册.pdf用户手册说明书

用户手册CL81109SCNCL81209SCN2.4GHz 数字无绳电话欢迎欢迎购买 AT&T 产品。

在使用此 AT&T 产品前,请仔细阅读用户手册中第 42 至 43 页的重要安全信息。

为了更好地安装和使用您的电话,也请仔细阅读用户手册中所有操作说明和常见问题的帮助信息。

您也可以访问我们的网站:或者拨打我们的服务热线:400-022-9929产品型号: CL81109SCN(1 部子机)CL81209SCN(2 部子机)产品类别:2.4GHz 数字无绳电话序列号:购买日期:购买地点:产品型号和序列号标记在座机的底部。

© 2011 伟易达通讯设备有限公司保留所有权利。

此使用手冊上所载述的AT&T 商标及 AT&T 图标为 AT&T 拥有的商号,并在 AT&T 的品牌许可协议下授权予香港伟易达通讯设备有限公司使用。

中国印刷。

部件清单请保管好销货收据和原始包装,以便在享受质保服务时作为相关证明。

CL81109/CL81209 的包装盒中包括以下物品:子机(CL81109 包含 1 部)(CL81209 包含 2 部)座机电池仓盖(CL81109 包含 1 个)(CL81209 包含 2 个)带电源适配器的充电座(仅适用于 CL81209)用户手册专用镍氢电池包(CL81109 包含 1 个)(CL81209 包含 2 个)初始安装电话概览 – 子机 (1)电话概览 – 座机 (3)安装您的电话 (5)安装座机 (5)安装充电座(适用于CL81209) (6)安装电池并充电 (7)设置菜单结构 (8)铃声设置 (9)设置铃声旋律 (9)设置铃声音量 (9)设置静音模式 (9)设置提示音 (10)日期及时间设置 (11)设置日期格式 (11)设置时间格式 (11)设置日期及时间 (11)闹钟设置 (12)子机设置 (13)启用直拨电话 (13)停用直拨电话 (13)设置墙纸 (13)设置色彩主题 (14)设置屏保 (14)设置对比度 (14)重命名子机 (15)设置背光变暗 (15)设置语言 (16)设置自动接听 (16)子机重设 (16)座机设置 (17)设置拨号模式 (17)设置闪断时间 (17)关闭新语音信息提示 (18)设置 IP 号码 (18)更改系统 PIN 码 (19)座机重设 (19)电话操作拨打、接听电话和结束通话 (20)拨打外部电话 (20)通话时间 (20)接听电话 (20)结束通话 (20)用户手册CL81109SCNCL81209SCN2.4GHz 数字无绳电话目录通话状态下的操作 (21)调节耳机和免提通话声音音量 (21)麦克风静音 (21)电话操作 (22)开启/关闭子机 (22)开启/关闭铃声 (22)键盘锁定/解锁 (22)寻找子机 (22)重拨清单 (23)从重拨清单中重拨号码 (23)查看重拨记录 (23)将重拨记录存储到电话簿中 (24)删除一个重拨记录 (24)删除所有重拨记录 (24)进行内部呼叫 (25)进行内部呼叫 (25)转移外部通话 (25)进行三方通话 (26)切换外部通话与内部通话 (26)电话簿电话簿 (27)新增电话簿记录 (27)呼叫电话簿记录号码 (27)编辑电话簿记录 (28)查看电话簿记录 (28)删除一个电话簿记录 (28)删除所有电话簿记录 (29)查看电话簿容量 (29)设置或删除快速拨号 (29)来电显示来电显示 (31)查看来电记录 (31)将来电记录储存到电话簿中 (31)拨打来电显示清单中的号码 (32)删除一个来电记录 (32)删除所有来电记录 (32)开启或关闭新来电提示 (33)附录 A子机屏幕显示 (34)提示音与指示灯 (35)子机提示音 (35)指示灯 (35)附录 B增设子机 (36)登记子机 (36)解除已登记子机 (37)附录 C常见问题 (38)附录 D维护 (41)附录 E重要安全信息 (42)安全信息 (42)特别注意 (43)附录 F产品中有毒有害物质或元素的名称及含量表 (44)附录G产品技术参数 (45)附录H索引 (46)电话概览 – 子机菜单操作1. 按菜单功能键进入主菜单。

CY7C1515AV18资料

Page 2 of 31 [+] Feedback

元器件交易网

Logic Block Diagram (CY7C1513AV18)

CY7C1511AV18, CY7C1526AV18 CY7C1513AV18, CY7C1515AV18

18 D[17:0]

A(19:0) 20

■ Variable drive HSTL output buffers

■ JTAG 1149.1 compatible test access port

■ Delay Lock Loop (DLL) for accurate data placement

Configurations

CY7C1511AV18 – 8M x 8 CY7C1526AV18 – 8M x 9 CY7C1513AV18 – 4M x 18 CY7C1515AV18 – 2M x 36

Address Register

21

A(20:0)

2M x 8 Array 2M x 8 Array 2M x 8 Array 2M x 8 Array

Read Data Reg. 32 16

16

Control Logic

RPS

C C

Reg.

Reg. 8 8

Reg.

8

8

8

CQ CQ Q[7:0]

Logic Block Diagram (CY7C1526AV18)

Address Register

21

A(20:0)

2M x 9 Array 2M x 9 Array 2M x 9 Array 2M x 9 Array

Read Data Reg. 36 18

北斗车载终端系列产品介绍

培训总学时 培训总里程 双重身份验证 数据自动上传 实操培训记录 真人语音提示

IC卡识别 指纹识别 GPS定位监控 跨区培训报警 开机自检 教学评估

图片抓拍 远程升级 无线传输 教练信息 学员信息 彩屏显示

驾校计时计程一体机主要通过IC卡及指纹来验证学员,并且训练数据会通过GPSR 实时上传至数据库中,并将培训时间和训练公里数记录到IC卡中保存。 网址:

GPS定位 远程升级 震动报警 遇险自动开锁 熄火自动开锁 设防自动关窗

网址:

4S店车辆远程故障诊断

技术参数:

工作电压: 8V-36VDC 电源反接特性 : <1000V 工作电流: <90mA@12VDC 省电工作电流: <50mA@12VDC 终端尺寸: 97 X 58 X 26mm 工作温度: -35℃ ~ +75℃ 存储温度: -40℃ ~ +85℃ 工作湿度: 0~95% GPS定位精度: 道 GPS冷启动时间: 34秒 GPS温启动时间: 32秒 GPS热启动时间: 1.5秒 GSM频率: 900/1800MHz自适应 报警开关响应时间:持续按报警开关2秒以上

校车GPS监控管理

技术参数:

工作电压: 8V-36VDC 电源反接特性 : <1000V 工作电流: <90mA@12VDC @12VDC 省电工作电流: <50mA@12VDC 终端尺寸: 97 X 58 X 26mm 工作温度: -35℃ ~ +75℃ 存储温度: -40℃ ~ +85℃ 工作湿度: 0~95% GPS定位精度: 5.0m SEP,2.5m CEP GPS通道数: 16通道 GPS冷启动时间: 34秒 GPS温启动时间: 32秒 GPS热启动时间: 1.5秒 GSM频率: 900/1800MHz自适应 报警开关响应时间:持续按报警开关2秒以上

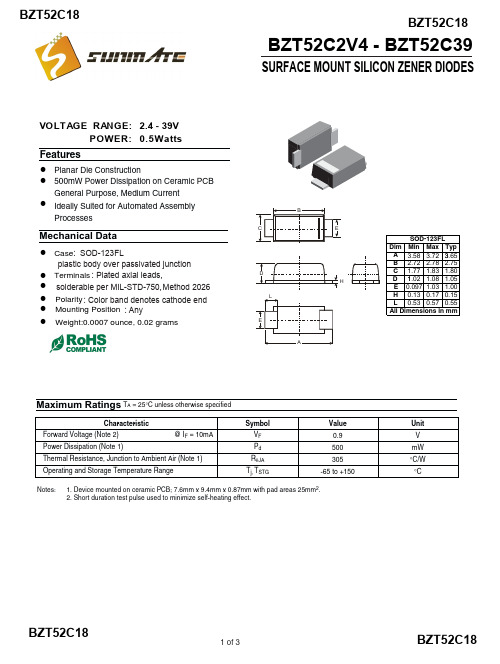

BZT52C18中文资料

VOLTAGE RANGE: 2.4 - 39 VPOWER: 0.5Wa t BZT52C2V4 - BZT52C39Planar Die Construction500mW Power Dissipation on Ceramic PCBGeneral Purpose, Medium Current Ideally Suited for Automated AssemblyProcessesFeaturesCharacteristicSymbolValue Unit Forward Voltage (Note 2)@ I F = 10mAV F 0.9V Power Dissipation (Note 1)Pd 500mW Thermal Resistance, Junction to Ambient Air (Note 1)R q JA 305°C/W Operating and Storage Temperature RangeT j,T STG-65 to +150°CNotes:1. Device mounted on ceramic PCB; 7.6mm x 9.4mm x 0.87mm with pad areas 25mm2.2. Short duration test pulse used to minimize self-heating effect.!!!SURFACE MOUNT SILICON ZENER DIODESMaximum Ratings T A = 25°C unless otherwise specified: SOD-123FLplastic body over passivated junction Method 2026: Color band denotes cathode end : AnyCase Terminals Polarity Mounting Position : Plated axial leads,solderable per MIL-STD-750,Mechanical Data!!!!!!Weight:0.0007 ounce, 0.02 grams3.58 3.72 0.55 0.57 0.530.15 0.17 0.13E D 1.00 1.03 0.097 1.05 1.08 1.021 1.80 1.83 1.77 2.75 2.78 2.72A 3.653 SOD-123FLDim Min Max Typ B C H LAll Dimensions in mmHType NumberZener Voltage Range(Note 2)Maximum Zener Impedance (Note 3)Maximum Reverse Current (Note 2)Typical TemperatureCoefficient @I ZTC mV/°C Test Current I ZTC V z @I ZTI ZT Z ZT@I ZTZ ZK @I ZK I ZK I R @ V R Nom (V)Min (V)Max (V)mA WmAuA V Min Max mA BZT52C2V4BZT52C2V7BZT52C3V0BZT52C3V3BZT52C3V6BZT52C3V9BZT52C4V3BZT52C4V7BZT52C5V1BZT52C5V6BZT52C6V2BZT52C6V8BZT52C7V5BZT52C8V2BZT52C9V1BZT52C10BZT52C11BZT52C12BZT52C13BZT52C15BZT52C16BZT52C18BZT52C20BZT52C22BZT52C24BZT52C27BZT52C30BZT52C33BZT52C36BZT52C39Electrical Characteristics@ T A = 25°C unless otherwise specifiedNotes:1. Device mounted on ceramic PCB; 7.6mm x 9.4mm x 0.87mm with pad areas 25mm2.2. Short duration test pulse used to minimize self-heating effect.3. f = 1kHz.2.4 2.2 2.65100600 1.050 1.0-3.5052.7 2.5 2.95100600 1.020 1.0-3.5053.0 2.8 3.2595600 1.010 1.0-3.5053.3 3.1 3.5595600 1.0 5.0 1.0-3.5053.6 3.4 3.8590600 1.0 5.0 1.0-3.5053.9 3.74.1590600 1.0 3.0 1.0-3.5054.3 4.0 4.6590600 1.0 3.0 1.0-3.5054.7 4.45.0580500 1.0 3.0 2.0-3.50.255.1 4.8 5.4560480 1.0 2.0 2.0-2.7 1.255.6 5.26.0540400 1.0 1.0 2.0-2 2.556.8 6.47.251580 1.0 2.0 4.0 1.2 4.556.2 5.8 6.6510150 1.0 3.0 4.00.4 3.757.57.07.951580 1.0 1.0 5.0 2.5 5.358.27.78.751580 1.00.7 5.0 3.2 6.259.18.59.6515100 1.00.5 6.0 3.87.05109.410.6520150 1.00.27.0 4.58.051110.411.6520150 1.00.18.0 5.49.051211.412.7525150 1.00.18.0 6.010.051312.414.1530170 1.00.18.07.011.051513.815.6530200 1.00.110.59.213.051615.317.1540200 1.00.111.210.414.051816.819.1545225 1.00.112.612.416.052018.821.2555225 1.00.114.014.418.052220.823.3555250 1.00.115.416.420.052422.825.6570250 1.00.116.818.422.052725.128.92803000.50.118.921.425.323028.032.02803000.50.121.024.429.423331.035.02803250.50.123.127.433.423634.038.02903500.50.125.230.437.423937.041.021303500.50.127.333.441.220.10.20.30.40.5255075100125150P ,P O W E R D I S S I P A T I O N (W )D T ,AMBIENT TEMPERATURE (C)Fig.1Power Dissipation vs Ambient TemperatureA °0.61020304050012345678910I ,Z E N E R C U R R E N T (m A )Z V ,ZENER VOLTAGE (V)Fig.2Zener Breakdown CharacteristicsZ0102030I ,Z E N E R C U R R E N T (m A )Z V ,ZENER VOLTAGE (V)Fig.3Zener Breakdown CharacteristicsZ 10203040246810102030405060708090100I ,Z E N ER C U R R E N T (m A )Z V ,ZENER VOLTAGE (V)Fig.4Zener Breakdown CharacteristicsZ C ,T O T A L C A P A C I T A N C E (p F )T 101001000V ,NOMINAL ZENER VOLTAGE (V)Fig.5Total Capacitance vs Nominal Zener VoltageZ。

中电力达ld80ai说明书

中电力达LD80AI说明书1. 简介中电力达LD80AI是一款高性能、高可靠性的工业级智能电力仪表。

本说明书将详细介绍该产品的功能特点、技术参数、安装使用方法以及注意事项。

2. 功能特点•高精度测量:中电力达LD80AI采用先进的测量技术,能够实现对电流、电压、功率因数等参数的高精度测量。

•多种通信接口:该设备支持RS485、Modbus等多种通信接口,方便与其他设备进行数据交互。

•多功能显示屏:配备大尺寸液晶显示屏,直观显示各项参数,并支持多种操作方式。

•报警功能:设备内置报警功能,可根据用户设置的阈值进行报警提示,确保安全运行。

•数据存储与传输:支持数据存储与传输功能,用户可以通过USB接口导出历史数据,并可以通过网络实时监控设备运行状态。

3. 技术参数以下是中电力达LD80AI的主要技术参数:参数值测量范围0~500A测量精度±0.5%电压输入范围AC100~380V频率范围45~65Hz通信接口RS485、Modbus工作温度范围-20℃~60℃防护等级IP544. 安装使用方法4.1 安装1.将中电力达LD80AI安装在合适的位置,确保通风良好且不易受到外界干扰。

2.将电流和电压传感器正确连接到设备的对应接口上。

3.根据实际需求,选择合适的通信接口进行连接。

4.2 使用1.接通电源后,中电力达LD80AI会自动进行初始化,并显示当前各项参数。

2.可通过操作面板上的按键或者远程控制软件对设备进行设置和操作。

3.如需导出历史数据,可将U盘插入USB接口,并按照菜单提示进行操作。

5. 注意事项•在安装和使用过程中,请务必遵守相关的安全操作规程,确保人身和设备安全。

•在设备运行过程中,如发现任何异常情况,请及时停止使用并联系售后服务人员进行维修。

•不得私自拆卸、修改设备内部结构,以免引起故障或安全事故。

•请定期对设备进行维护和检查,确保其正常运行。

以上是对中电力达LD80AI的详细说明。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。