ADS7868IDBVT;ADS7866IDBVT;ADS7867IDBVT;ADS7868IDBVR;ADS7868IDBVRG4;中文规格书,Datasheet资料

TFT触摸屏使用说明

2一、.4寸TFT 触摸屏使用说明要正确使用TFT 触摸屏,需要借助相应的单片机实验板,这里,以顶顶电子开发板DD-900实验开发板为例进行介绍,值得庆幸的是,DD-900上设有3V 电压输出端,因此,可以方便地为TFT 触摸屏供电。

TFT 触摸屏模块介绍随着TFT 触摸屏价格的不断下降,其应用也越来越广泛,学习TFT 触摸屏现已成为一种时尚,以前,很多人只有在ARM 单片机中才能看到TFT 触摸屏的风采,现在,随着51单片机性能的提高,51单片机也能玩TFT 触摸屏了,这里,我们介绍的是一款2.4寸TFT 触摸屏模块,其正面与反面外形如图所示:这款触摸屏模块主要具备如下特点:1.2.4寸320*240 ,65K/262K 色;2.屏带PCB 板, PCB 板设有2.4寸液晶屏、SD 卡座、触摸屏控制芯片ADS7843,通过40脚插针将屏、卡座和触摸芯片功能引脚,引脚间距为2.54mm ,采用杜邦线可十分方便地与单片机进行连接。

PCB 引出脚排列及功能如图所示:3.屏设置为8位,用户也可根据实际情况设置为16位。

4.控制IC 为ILI9325。

二、供电及连接说明DD-900实验开发板采用的是5V 供电,因此,单片机应采用5V 单片机,如STC89C516RD+、STC12C5A60S2等,晶振采用30M ,注意TFT 要采用3V 供电,否则有可能烧屏,TFT 与单片机连接时可加限流电阻,电阻大小为470欧左右,也可以不加,但单片机不可设置为推挽模式,各引脚连接如下: TFT 触摸屏 DD-900实验开发板 说明 GND GND 屏与背光供电VCC 3V LED+ 3V DB8~DB15 P00~P07 液晶屏部分DB0~DB7不连接(这里采用是8位方式,不用连接)RS P26 WR P25 RD P24 CS P27 RES P23 D_CLK P21 触摸控制部分D_CS P20 D_DIN P22 D_BUSY P34 D_DOUT P33 D_Penirq (中断) P35 SD_OUT 根据程序进行定义 SD 卡座部分(前两个实验,此部分未采用) SD_SCK 根据程序进行定义SD_DIN根据程序进行定义SD_CS 根据程序进行定义注意:在TFT 的PCB 板上标有TFT 的引脚功能,一定要认清管脚与标注的对应关系。

ADS7883SDBVT;ADS7883SBDBVT;ADS7883SDBVR;ADS7883SBDBVR;中文规格书,Datasheet资料

295.2°C/W 215°C 220°C

(1) Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

Copyright © 2008, Texas Instruments Incorporated

http://o

ADS7883

SLAS594 – JULY 2008 .......................................................................................................................................................................................................

http://o

ADS7883

....................................................................................................................................................................................................... SLAS594 – JULY 2008

武汉力源信息技术 ads7864 500khz 12 位六通道同时采样模数转换器 说明书

RESET

9

DB9

数据位 9

10

DB8

数据位 8

11

DB7

数据位 7

33

REFOUT

34

REFIN

35

AGND

12

DB6

数据位 6

13

DB5

数据位 5

36

+VA

37

CH A1+

14

DB4

数据位 4

38

CH A1—

15

DB3

数据位 3

39

CH B1+

16

DB2

数据位 2

40

CH B1—

17

DB1

数据位 1

4

武汉力源信息技术服务有限公司

免 费 电 话 :8 0 0 - 8 8 0 8 0 5 1

图 1 ADS7864 的单端输入与差分输入方法

注:共模电压(差分模式)=[(IN+)+(IN-)]/2。共模电压(单端模式)=IN-。 ADS7864 +IN和-IN之间的最大差分电压是VREF。对单端输入和差分输入共模电压范围的说明请参照图 3 与 图 4。

图 2 在单端与差分输入模式中使用 ADS7864

5

武汉力源信息技术服务有限公司

免 费 电 话 :8 0 0 - 8 8 0 8 0 5 1

图 3 单端输入:共模电压范围与VREF的关系

入信号的相对相位信息。每对通道都有一个保持信号( HOLDA 、 HOLDB 、 HOLDC )使 6 个通道上

的采样操作可以同时进行。该器件接受以内部+2.5V基准电压为中心在—VREF到+VREF范围内的模拟输入电 压。若在前端使用电平位移电路,该器件还授受双极性输入范围(见图 7)。

ads7886 芯片资料

2

Submit Documentation Feedback Product Folder Link(s): ADS7886

Copyright © 2005–2009, Texas Instruments Incorporated

ADS7886

SLAS492A – SEPTEMBER 2005 – REVISED NOVEMBER 2009

ABSOLUTE MAXIMUM RATINGS (1)

UNIT +IN to AGND +VDD to AGND Digital input voltage to GND Digital output to GND Operating temperature range Storage temperature range Junction temperature (TJ Max) Power dissipation, SOT23 and SC70 packages θJA Thermal impedance Lead temperature, soldering (1) SOT23 SC70 Vapor phase (60 sec) Infrared (15 sec) –0.3 V to +VDD +0.3 V –0.3 V to 7 V –0.3 V to (7 V) –0.3 V to (+VDD + 0.3 V) –40°C to 125°C –65°C to 150°C 150°C (TJ Max–TA)/θJA 295.2°C/W 351.3°C/W 215°C 220°C

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

tps78618kttt中文资料

元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. To minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third–party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Mailing Address:Texas InstrumentsPost Office Box 655303Dallas, Texas 75265Copyright 2003, Texas Instruments Incorporated。

AD7865中文介绍

FEATURESFast (2.4μs) 14-Bit ADCFour Simultaneously Sampled InputsFour Track/Hold Amplifiers0.35μs Track/Hold Acquisition Time2.4μs Conversion Time per ChannelHW/SW Select of Channel Sequence for ConversionSingle Supply OperationSelection of Input Ranges: ±10 V,±5 V and ±2.5 V,0 V to +5 V and 0 V to +2.5 VHigh Speed Parallel Interface Which Also AllowsInterfacing to 3 V ProcessorsLow Power, 115 mW TypPower Saving Mode, 15μW TypOvervoltage Protection on Analog InputsAPPLICATIONSAC Motor ControlUninterruptible Power SuppliesIndustrial Power Meters/MonitorsData Acquisition SystemsCommunicationsGENERAL DESCRIPTIONThe AD7865 is a fast, low power, four-channel simultaneous sampling 14-bit A/D converter that operates from a single +5V supply. The part contains a 2.4 μs successive approximation ADC, four track/hold amplifiers, 2.5 V reference, on-chip clock oscillator, signal conditioning circuitry and a high speed parallel interface. The input signals on four channels are sampled simultaneously thus preserving the relative phase information of the signals on the four analog inputs. The part accepts analog input ranges of ±10V, ±5V, ±2.5V, 0V to +2.5V and 0V to +5V. The part allows anysubset of the four channels to be converted in order to maximize the throughput rate on the selected sequence. The channels to be converted can be selected either via hardware (channel select input pins) or via software (programming the channel select register). A single conversion start signal (CONVST) simultaneously places all the track/holds into hold and initiates conversion sequence for the selected channels. The EOC signal indicates the end of each individual conversion in the selected conversion sequence. The BUSY signal indicates the end of the conversion sequence. Data is read from the part via a 14-bit parallel data bus using the standard CS and RD signals. Maximum throughput for a single channel is 350 kSPS. For all four channels the maximum throughput is 100 kSPS.PRODUCT HIGHLIGHTS1. The AD7865 features four Track/Hold amplifiers and a fast (2.4 μs) ADC allowing simultaneous sampling and then conversion of any subset of the four channels.2. The AD7865 operates from a single +5V supply and consumes only 115 mW typ, making it ideal for low power and portable applications.3. The part offers a high speed parallel interface for easy connectionto microprocessors, microcontrollers and digital signal processors.4. The part is offered in three versions with different analog input ranges. The AD7865-1 offers the standard industrial ranges of ±10V and ±5V; the AD7865-2 offers a unipolar range of 0V to +2.5V or 0V to +5V and the AD7865-3 offers the common signal processing input range of ±2.5V.5. The part features very tight aperture delay matching between the four input sample and hold amplifiers.PIN FUNCTION DESCRIPTIONS1 BUSY Busy Output. The busy output is triggered high by the rising edge of CONVST and remains high until conversion is completed on all selected channels.2 FRSTDATA First Data Output. FRSTDATA is a logic output which, when high, indicates that the Output Data Register Pointer is addressing Register 1—SeeAccessing the Output Data Registers. 3 CONVST Convert Start Input. Logic Input. A low-to-high transition on this input puts all track/holds into their hold mode and starts conversion on the selected channels. In addition, the state of the Channel Sequence Selection is also latched on the rising edge of CONVST . 4 CS Chip Select Input. Active low logic input. The device is selected when this input is active. 5 RD Read Input. Active low logic input which is used in conjunction with CS low to enable the data outputs. Ensure the WR pin is at logic high while performing a read operation. 6 WR Write Input. A rising edge on the WR input, with CS low and RD high, latches the logic state on DB0 to DB3 into the channel select register.7 CLK IN/SL1 Conversion Clock Input/Hardware Channel Select. The function of this pin depends upon the S H /SEL input. When the S H /SEL input is high (choosing software control of the channel selection sequence), this pin assumes its CLK IN function. CLK IN is an externally applied clock (that is only necessary when INT/EXT CLK is high) this allows the user to control the conversion rate of the AD7865. Each conversion needs 16 clock cycles in order for the conversion to be completed. The clock should have a duty cycle that is no greater than 60/40. See Using an External Clock. When the S H /SEL input is low (choosing hardware control of the channel conversion sequence), this pin assumes its Hardware Channel Select function. The SL1 input determines whether Channel 1 is included in the channel conversion sequence. The selection is latched on the rising edge of CONVST . See Selecting a Conversion Sequence. 8INT /EXT CLK/SL2 Internal/External Clock/Hardware Channel Select. The function of this pin depends upon the S H /SEL input. When the S H /SEL input ishigh (choosing software control of the channel selection sequence), this pin assumes its INT/EXT CLK function. When INT/EXT CLK is at a Logic 0, the AD7865 uses its internally generated master clock. When INT/EXT CLK is at Logic 1, the master clock is generated externally to the device and applied to CLK IN. When the SH/SEL input is low (choosing hardware control of the channel conversion sequence), this pin assumes its Hardware Channel Select function. The SL2 input determines whether Channel 2 is included in the channel conversion sequence. The selection is latchedon the rising edge of CONVST. When SH/is at Logic 1 these pins have no function and can be tied to Logic 1 or Logic 0. See Selecting a Conversion Sequence. 9–10 SL3–SL4 Hardware Channel Select. When the SH/SEL input is at Logic 1, the SL3 input determines whether Channel 3 is included in the channel conversion sequence while SL4 determines whether Channel 4 is included in the channel conversion sequence. When the pin is at Logic 1, the channel is included in the conversion sequence. When the pin is at Logic 0, the channel is excluded from the conversion sequence. The selection is latched on the rising edge of CONVST. See Selecting a Conversion Sequence.11SH/SEL Hardware/Software Select Input. When this pin is at a Logic 0, the AD7865 conversion sequence selection is controlled via the SL1–SL4 input pins and runs off an internal clock. When this pin is at Logic 1, the conversion sequence is controlled via the channel select registerand allows the ADC to run with an internal or external clock. See Selecting a Conversion Sequence.12 AGND Analog Ground. General Analog Ground. This AGNDÊpin should be connected to the system’s AGND plane.13–16 VIN4x, VIN3x Analog Inputs. See Analog Input section.17 AGND Analog Ground. Analog Ground reference for the attenuator circuitry. ThisAGNDÊpin should be connected to the system’s AGND plane.18–21 VIN2x, VIN1x Analog Inputs. See Analog Input section.22 STBY Standby Mode Input. This pin is used to put the device into the power save or standby mode. The STBY input is high for normal operation and low for standby operation.23 AGND Analog Ground. General Analog Ground. This AGND pin should be connected to the system’s AGND plane.24 VREF Reference Input/Output. This pin provides access to the internal reference (+2.5 V ±20 mV) and also allows the internal reference to be overdriven by an external reference source (+2.5 V±5%). A 0.1 mF decoupling capacitor should be connected between this pin and AGND.25 A VDD Analog Positive Supply V oltage, +5.0 V ±5%. A 0.1 mF decoupling capacitor should be connected between this pin and AGND.26 AGND Analog Ground. General Analog Ground. This AGND pin should be connected to the system’s AGND plane.27–34 DB13–DB6 Data Bit 13 is the MSB, followed by Data Bit 12 to Data Bit 6. Three-state TTL outputs. Output coding is twos complement for AD7865-1 and AD7865-3, and straight binary for AD7865-2.35 DVDD Positive Supply V oltage for Digital section, +5.0 V ±5%. A 0.1 mF decoupling capacitor should be connected between this pin and AGND. Both DVDD and A VDD should be externally tied together.36 VDRIVE This pin provides the positive supply voltage for the output drivers (DB0 to DB13), BUSY,EOC and FRSTDATA. It is normally tied to DVDD. VDRIVE should be decoupled with a 0.1 mF capacitor. It allows improved performance when reading during the conversion sequence. Also, the output data drivers may be powered by a 3 V ± 10% supply to facilitate interfacing to 3 V processors and DSPs.37 DGND Digital Ground. Ground reference for Digital circuitry. This DGND pin should be connected to the system’s DGND plane. The system’s DGND and AGND planes should be connected together at one point only, preferably at an AGND pin.38, 39 DB5, DB4 Data Bit 5 to Data Bit 4. Three-state TTL outputs.40–43 DB3–DB0 Data Bit 3 to Data Bit 0. Bidirectional data pins. When a read operation takes place, these pins are three-state TTL outputs. The channel select register is programmed with the data on the DB0–DB3 pins with standard CS and WR signals. DB0 represents Channel 1 and DB3 represents Channel 4.44 EOC End-of-Conversion. Active low logic output indicating conversion status. The end of each conversion in a conversion sequence is indicated by a low going pulse on this line.CONVERTER DETAILSThe AD7865 is a high speed, low power, four-channel simultaneous sampling 14-bit A/D converter that operates from a single +5ÊV supply. The part contains a 2.4Êms successive approximation ADC, four track/hold amplifiers, an internal +2.5ÊV reference and a high speed parallel interface. There are four analog inputs which can be sampled simultaneously, thus preserving the relative phase information of the signals on all four analog inputs. Thereafter, conversions will be completed on the selected subset of the four channels. The part accepts an analog input range of ±10 V or ±5 V (AD7865-1), 0 V to +2.5 V or0 V to +5 V (AD7865-2) and ±2.5 V (AD7865-3). Overvoltage protection on the analog inputs for the part allows the input voltage to go to ±18 V (AD7865-1 with ±10 V input range), ±9 V (AD7865-1 with ±5 V input range), –1 V to +18 V (AD7865-2) and –4 V to +18 V (AD7865-3) without causing damage or effecting the conversion result of another channel. The AD7865 has two operating modes Reading Between Conversions and Readingafter the Conversion Sequence. These modes are discussed in more detail in the Timing and Control section.A conversion is initiated on the AD7865 by pulsing the CONVST input. On the rising edge of CONVST, all four on-chip track/holds are simultaneously placed into hold and the conversion sequence is started on all the selected channels. Channel selectionis made via the SL1–SL4 pins if SH/SEL is logic zero, or via the channel select register if SH/SEL is logic one—see Selecting a Conversion Sequence. The channel select register isprogrammed via the bidirectional data lines DB0–DB3 and a standard write operation. The selected conversion sequence is latched on the rising edge of CONVST so changing a selection will only take effect once a new conversion sequence is initiated. The BUSY output signal is triggered high on the rising edge of CONVST and will remain high for the duration of the conversion sequence. The conversion clock for the part is generated internally using a laser-trimmed clock oscillator circuit. There is also the option of using an external clock, by tying the INT/EXT CLK pin logic high and applying an external clock to the CLKIN pin. However, the optimum throughput is obtained by using the internally generated clock— see Using an External Clock. The EOC signal indicates the end of each conversion in the conversion sequence. The BUSY signal indicates the end of the full conversion sequence and at this time all four Track and Holdsreturn to tracking mode. The conversion results can either be read at the end of the full conversion sequence (indicated by BUSY going low) or as each result becomes available (indicated by EOC going low). Data is read from the part via a 14-bit parallel data bus with standard CS and RD signals—see Timing and Control. Conversion time for each channel of the AD7865 is 2.4μs and the track/hold acquisition time is 0.35 μs. To obtain optimum performance from the part, the read operation should not occur during a channel conversion or during the 100 ns prior to the next CONVST rising edge. This allows the part to operate at throughput rates up to 100 kHz for all four channels and achieve data sheet specifications.。

ADS7881EVM, ADS7891EVM Evaluation Module User's Gu

User’s GuideADS7881EVM, ADS7891EVM Evaluation ModuleLijoy Philipose Data Acquisition ProductsABSTRACTThis user's guide describes the characteristics, operation, and use of the ADS78x1 (ADS7881 and ADS7891) 12-bit and 14-bit, parallel, analog-to-digital converter (ADC) evaluation module (EVM). Throughout this document, the terms evaluation board, evaluation module, and EVM are synonymous with the ADS78x1EVM.A complete circuit description, schematic diagram, layout, and bill of materials (BOM) are included in this document.Table of Contents1 Introduction (2)1.1 Features (2)1.2 Analog Interface (2)1.3 Digital Interface (4)1.4 Power Supplies (6)2 Using the EVM (7)3 ADS78x1EVM Bill of Materials (8)4 ADS78x1EVM Layout (10)5 ADS78x1EVM Schematics (14)6 Revision History (17)List of FiguresFigure 1-1. ADS7881 Input Buffer Circuit (3)Figure 2-1. Decoding Control Signals Using the Address Bus (7)Figure 4-1. Top Layer – Layer 1 (10)Figure 4-2. Ground Plane – Layer 2 (11)Figure 4-3. Power Plane – Layer 3 (12)Figure 4-4. Bottom Layer – Layer 4 (13)Figure 5-1. Schematic Page 1: Digital Buffer (14)Figure 5-2. Schematic Page 2: ADS7881, ADS7891 (15)Figure 5-3. Schematic Page 3: Digital Communication (16)List of TablesTable 1-1. Related Documentation from Texas Instruments (2)Table 1-2. Analog Input Connector (2)Table 1-3. Solder Short Jumper Setting (4)Table 1-4. Pin Out for Parallel Control Connector P2 (4)Table 1-5. Jumper Settings (5)Table 1-6. Data Bus Connector P3 (5)Table 1-7. Pin Out for Converter Control Connector J3 (6)Table 1-8. Power-Supply Test Points (6)Table 1-9. Power Connector, J1, Pin Out (6)Table 3-1. Bill of Materials (8)TrademarksAll trademarks are the property of their respective owners.Introduction 1 IntroductionThe ADS78x1EVM showcases the 12-bit, 4-MSPS (ADS7881) and 14-bit, 3-MSPS (ADS7891) ADCs. TheADS7881 and ADS7891 devices include a capacitor-based successive-approximation register (SAR) ADC with inherent sample and hold. These devices offer either a 12-bit or 14-bit parallel interface. Both devices offer byte mode operation that enables easy interface with 8-bit processors. They also have a pseudo-differential input stage and a 2.5-V internal reference.This evaluation module serves as a reference design and a low-cost method to test these converters in the end application. The following sections describe the pin outs of the various analog, power, and digital connectors and power requirements.Table 1-1 lists documents related to the ADS78x1EVM.1.1 FeaturesThe ADS78x1EVM includes the following features:•Full-featured evaluation board for the high-speed, SAR-type ADS7881(12-bit, 4-MSPS) or ADS7891(14-bit, 3-MSPS) single-channel, parallel interface ADCs•Onboard signal conditioning•Onboard reference•Input and output digital buffers•Onboard decoding for stacking multiple EVMs1.2 Analog InterfaceThe ADS7881 and ADS7891 ADCs have both a positive and negative analog input pin. The negative input pin, which has a range of –200 mV up to 200 mV is shorted on the board. A signal for the positive input pin can be applied at connector P1, pin 2 (as shown in Table 1-2) or at the center pin of the SMA connector J2.(1)All odd-numbered pins of P1 are tied to AGND.1.2.1 Signal ConditioningThe factory recommends the analog input to any SAR-type converter be buffered and low-pass filtered. The input buffer on the ADS78x1EVM uses the THS4031 (as shown in Figure 1-1) configured as an inverting gain of one. However, the amplifier is not stable at a gain of one, and is thus configured for inverting gain of one. The THS4031 was selected for its low noise, high slew rate, and fast settling time. The low-pass filter resistor and capacitor values were selected such that the ADS78x1EVM meets the 1-MHz AC performancespecifications listed in the data sheet. The series resistor works in conjunction with the capacitor to filter the input signal, but also isolates the amplifier from the capacitive load. The capacitor to ground at the input of the ADC works in conjunction with the series resistor to filter the input signal, and functions as a charge reservoir. This external filter capacitor works with the amplifier to charge the internal sampling capacitor during sampling mode. Resistors R1 and R12 were selected to reduce offset.The EVM has a provision to offset the input voltage by adjusting R25, a 10-kΩ potentiometer.130 pF(+)IN(−)INCCV IN10 k Figure 1-1. ADS7881 Input Buffer Circuit IntroductionIntroduction 1.2.2 ReferenceThe ADS78x1EVM provides an onboard 2.5-V reference circuit. The EVM also supplies a reference voltage via connecter P1 pin 20. This reference voltage can be filtered through amplifier U1. The converter itself has on-chip reference buffer, and therefore does not need to be buffered externally. The reference buffer circuit on the EVM is used to generate the offset voltage for the input amplifier, U2.The EVM allows selection from three reference sources. Set SJP1, SJP2, and SJP4 to select either an onboard reference voltage (REF1004-2.5), ADC internal reference, or a user-supplied reference voltage via P1 pin 20. Table 1-3 lists jumper settings and Section 5 provides full schematics.(1)Factory-set condition.1.3 Digital InterfaceThe ADS78x1EVM is designed for easy interfacing to multiple platforms. Samtec part numbers SSW-110-22-F-D-VS-K, TSM-110-01-T-DV-P, SSW-116-22-S-D-VS, and TSM-116-01-T-D-V-P provide a convenient dual row header and socket combination at P1, P2, P3, and J3. Consult Samtec at or 1-800-SAMTEC-9 for a variety of mating connector options.Connectors P1, P2, and P3 allows the user to plug the EVM into the 5-6k interface card to interface directly with the TMS320C5000 and TMS320C6000 series of DSP. Table 1-4 lists the connector pin out.(1)All even-numbered pins of P2 are tied to DGND.Read (RD), conversion start (CONVST) and reset (RESET) signals to the converter can be assigned to two different addresses in memory via jumper settings. The jumper settings allow up to two ADS78x1EVMs to be stacked into processor memory. See Table 1-5 for jumper settings. The evaluation module does not allow the Introduction chip-select (CS) line of the converter to be assigned to different memory locations. Instead, ground or wire the CS line to an appropriate signal of the user processor.(1)Factory-set condition.The data bus is available at connector P3. Table 1-6 lists the pin out information. This EVM supports two devices but the connector signals names are based on the ADS7981, which is the higher-resolution device. Depending on which device is being evaluated, care must be taken when connecting the EVM to a host processor.(1)All even-numbered pins of P3 are tied to DGND.As described in Table 1-7, this evaluation module provides direct access all the analog-to-digital converter control signals via connector J3.(1)All even-numbered pins of J3 are tied to DGND.1.4 Power SuppliesThe EVM accepts four power supplies.• A dual ±Vs DC supply for the dual-supply op amps. A ±12-V DC supply is recommended.• A single +5.0-V DC supply for the analog section of the board (ADC + reference).•A single +5.0-V or +3.3-V DC supply for the digital section of the board (ADC + address decoder + buffers).There are two ways to provide these voltages.1.Wire in voltages, as listed in Table 1-8, at test points on the EVM.e the power connector J1 and derive the voltages elsewhere.Table 1-9 lists the pin out connections forJ1. Set jumper W5 to short between pins 1-2 or pins 2-3 to short +3.3VD or +5VD, respectively, to be the buffer digital supply (+BVDD).Introduction Using the EVM2 Using the EVMThe ADS78x1EVM serves as a reference design, prototype board, and test platform for the software engineer to develop code.As a reference design, the ADS78x1EVM contains the essential circuitry to showcase the ADC. This essential circuitry includes the input amplifier, reference circuit, and buffers. The EVM analog input circuit is optimized for a 1-MHz sine wave, therefore users may need to adjust the resistor and capacitor values of the ADC input RC circuit. In AC-type applications where signal distortion is a concern, use polypropylene capacitors in the signal path. In applications where the input is multiplexed, either adjust or remove the ADC input resistor and capacitor, as needed.As a prototype board, the buffer circuit consists of a footprint in a standard 8-pin SOIC and resistor padsfor inverting and noninverting configurations. The ADS78x1EVM can be used to evaluate both dual- and single-supply amplifiers. The EVM comes installed with a dual-supply amplifier that allows the user to take advantage of the full input voltage range of the converter. For applications that require signal supply operation and smaller input voltage ranges, the THS4031 can be replaced with a single-supply amplifier, such as the OPA300. Short pad jumper SJP7 between pads 1 and 2, because SJP7 shorts the minus supply pin of the amplifier to ground. The positive supply voltage can be applied via test point TP12 or connector J1 pin 1.As a software test platform, connectors P1, P2, and P3 plug into the parallel interface connectors of the 5-6K interface card. The 5-6K interface card sits on the C5000 and C6000 digital signal processor starter kit (DSK). The ADS78x1EVM is then mapped into the processor memory space. This card also provides an area for signal conditioning. This area can be used to install application circuits for digitization by the ADS7881 or ADS7891 ADC. See the 5–6K Interface Board user's guide for more information.For the software engineer, the ADS78x1EVM provides a simple platform for interfacing to the converter. The EVM provides standard 0.1" headers and sockets to wire into prototype boards. The user must only provide three address lines (A2, A1, and A0) and one address valid line (DC_CS) to connector P2, as shown in Figure2-1. To choose which address combinations generate RD, CONVST, and RESET set jumpers as shown in Table 1-5. Recall that the chip select (CS) signal is not memory mapped or tied to P2, and therefore must be controlled via a general-purpose pin or shorted to ground at the J3 pin 1. If address decoding is not required, the EVM provides direct access to converter data bus via P3 and control via J3.A1A2DC_CSFigure 2-1. Decoding Control Signals Using the Address Bus4 ADS78x1EVM LayoutFigure 4-1 to Figure 4-4illustrate the silkscreens for the ADS78x1EVM.Figure 4-1. Top Layer – Layer 1ADS78x1EVM Layout Figure 4-2. Ground Plane – Layer 2 ADS78x1EVM LayoutFigure 4-3. Power Plane – Layer 3ADS78x1EVM Layout Figure 4-4. Bottom Layer – Layer 4 ADS78x1EVM Layout Revision History6 Revision HistoryChanges from Revision * (December 2004) to Revision A (October 2021)Page •Changed document title from ADS7881/ADS7891EVM to ADS7881EVM, ADS7891EVM Evaluation Module1•Changed ADS7881/ADS7891EVM to ADS78x1EVM throughout document (1)•Added Related Documentation from Texas Instruments table to Introduction section (2)•Changed paragraph preceding Data Bus Connector P3 (4)•Changed Data Bus Connector P3 table (4)IMPORTANT NOTICE AND DISCLAIMERTI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.TI’s products are provided subject to TI’s Terms of Sale or other applicable terms available either on or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products.TI objects to and rejects any additional or different terms you may have proposed.Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265Copyright © 2022, Texas Instruments Incorporated。

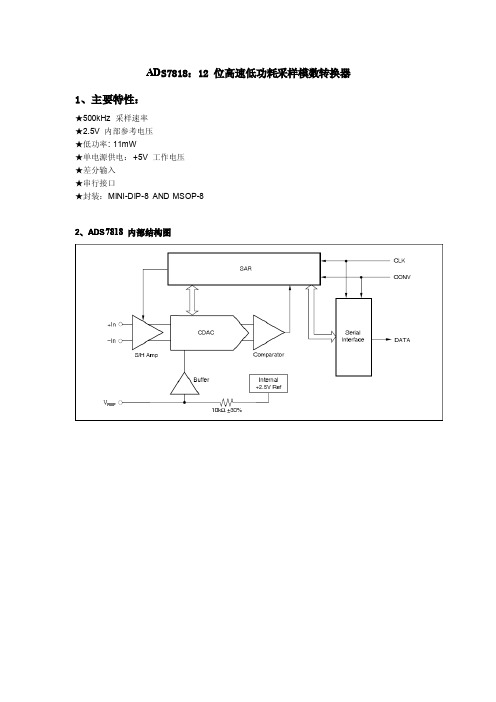

ADS7818与DAC7611资料

引脚 CONV 组成的串行接口直接与单片机的输入 /输出引脚连接。

ADS7818 应用电路

⑵、工作时序: 要使上述 ADS7818 的应用电路工作,单片机加到它的引脚上的信号必须满足如 下工作时序图:

串行时钟输入. 同步串行时钟决定了转换 速度。

8 +VCC 电源. 用0.1uF的瓷片电容和10uF的电解电容并联接地滤波。

4、对参考电压的说明:

★使用 内部 参考电 压时: 模拟输入电压范围: GND-200mV~VCC+ 200mV ★使用 外部 参考电 压时: FS (Full Scale)满刻度模拟输入电压=2VREF 如:外部参考电压的范围为 2.0V~ 2.55V, 模拟输入电压( +IN)的范围为 4.0V ~ 5.1V. 。 当VREF = 2.04 8V 时 ,模拟输入电压 +IN的范围为 0V to 4.095V (即 1mV/ LSB)

6、ADS7818 的一种应用电路: ⑴、电路结构: 在电源引脚 VCC 旁边通常应该连接两个容量分别为 10uF 和 0.1uF 滤波电容,

前者采用电解电容,后者采用瓷片电容,它们用来滤除电源中的干扰。 该电路使用内部参考电源以简化电路设计,在参考电源引脚 VREF 的接地线之间

并联电容分别为 0.1uF 和 2.2uF 两个电容以小除干扰。 待转换电压从引脚 +In 输入,引脚-In 直接接地。由于使用 2.5V 片内参考电 耗 ,

5、相关参数最大额定值

+VCC to GND ............................................................................ –0.3V to 6V Analog Inputs to GND .............................................. –0.3V to (VCC + 0.3V) Digital Inputs to GND ............................................... –0.3V to (VCC + 0.3V) 电源功耗 ......................... .............................................................. 325mW 节点最大温度 ................. .... ............. .......................................... +150°C 工作温度范围............................... ............... ........................ –40°C to +85°C 存储温度范围 .......... ............................................................ –65°C to +150°C 焊接温度 ............................. ......... ... .. ......... ...................................... +300°C

AD转换芯片介绍

l???????ADS7812?低功耗串行12位采样模数转换器

l???????ADS7810?12位800kHz采样CMOS模数转换器

l???????ADS7800?12位3us采样模数转换器

l???????ADS574??兼容微处理器的采样CMOSA/D转换器?

l???????THS1007?10位6MSPS同步采样四路通道ADC;包含并行DSP/uPI/F通道自动扫描?

l???????ADS901??10位20MSPSADC,具有单端/差动输入、外部参考和可调节全范围?

l???????ADS900??10位20MSPSADC,具有单端/差动输入、内部基准和可调节全范围?

l???????ADS822?10位40MSPSADC,具有单端/差动输入、内/外基准和断电、引脚符合ADS823/6/8?

l???????ADS821?10位40MSPSADC,单端/差动输入具有内部基准和9.3位ENOB?

l???????ADS820?10位20MSPSADC,单端/差动输入具有内部基准和9.5位ENOB?

l???????TLC3545?14位200KSPSADC,具有串行输出、自动断电和伪差动输入?

l???????TLC3544?14位、5V、200KSPS、4通道单级性ADC

l???????TLC3541?14位200KSPSADC系列输出、自动断电、单端输入?

l???????THS1403?14位、3MSPSADC单通道、差动输入、DSP/uPIF、可编程增益放大器、内部S&H?

l???????TLC4541?16位200KSPSADC,具有串行输出、自动断电和单端输入

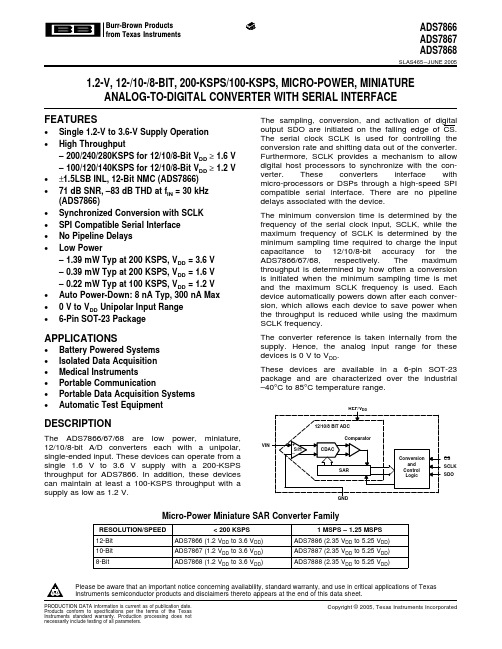

ADS7868资料

BurrĆBrown Products from TexasInstrumentsFEATURESAPPLICATIONSDESCRIPTIONVINCS SCLK SDOADS7866ADS7867ADS7868SLAS465–JUNE 20051.2-V,12-/10-/8-BIT,200-KSPS/100-KSPS,MICRO-POWER,MINIATURE ANALOG-TO-DIGITAL CONVERTER WITH SERIAL INTERFACEThe sampling,conversion,and activation of digital output SDO are initiated on the falling edge of CS.•Single 1.2-V to 3.6-V Supply Operation The serial clock SCLK is used for controlling the •High Throughputconversion rate and shifting data out of the converter.Furthermore,SCLK provides a mechanism to allow –200/240/280KSPS for 12/10/8-Bit V DD ≥1.6V digital host processors to synchronize with the con-–100/120/140KSPS for 12/10/8-Bit V DD ≥1.2V verter.These converters interface with •±1.5LSB INL,12-Bit NMC (ADS7866)micro-processors or DSPs through a high-speed SPI •71dB SNR,–83dB THD at f IN =30kHz compatible serial interface.There are no pipeline delays associated with the device.(ADS7866)•Synchronized Conversion with SCLK The minimum conversion time is determined by the frequency of the serial clock input,SCLK,while the •SPI Compatible Serial Interface maximum frequency of SCLK is determined by the •No Pipeline Delays minimum sampling time required to charge the input •Low Powercapacitance to 12/10/8-bit accuracy for the ADS7866/67/68,respectively.The maximum –1.39mW Typ at 200KSPS,V DD =3.6V throughput is determined by how often a conversion –0.39mW Typ at 200KSPS,V DD =1.6V is initiated when the minimum sampling time is met –0.22mW Typ at 100KSPS,V DD =1.2V and the maximum SCLK frequency is used.Each •Auto Power-Down:8nA Typ,300nA Max device automatically powers down after each conver-sion,which allows each device to save power when •0V to V DD Unipolar Input Range the throughput is reduced while using the maximum •6-Pin SOT-23PackageSCLK frequency.The converter reference is taken internally from the supply.Hence,the analog input range for these •Battery Powered Systems devices is 0V to V DD .•Isolated Data Acquisition These devices are available in a 6-pin SOT-23•Medical Instrumentspackage and are characterized over the industrial •Portable Communication–40°C to 85°C temperature range.•Portable Data Acquisition Systems •Automatic Test EquipmentThe ADS7866/67/68are low power,miniature,12/10/8-bit A/D converters each with a unipolar,single-ended input.These devices can operate from a single 1.6V to 3.6V supply with a 200-KSPS throughput for ADS7866.In addition,these devices can maintain at least a 100-KSPS throughput with a supply as low as 1.2V.Micro-Power Miniature SAR Converter FamilyRESOLUTION/SPEED <200KSPS1MSPS –1.25MSPS12-Bit ADS7866(1.2V DD to 3.6V DD )ADS7886(2.35V DD to 5.25V DD )10-Bit ADS7867(1.2V DD to 3.6V DD )ADS7887(2.35V DD to 5.25V DD )8-BitADS7868(1.2V DD to 3.6V DD )ADS7888(2.35V DD to 5.25V DD )Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright ©2005,Texas Instruments IncorporatedProducts conform to specifications per the terms of the Texas Instruments standard warranty.Production processing does not necessarily include testing of all parameters.元器件交易网ABSOLUTE MAXIMUM RATINGSADS7866ADS7867ADS7868SLAS465–JUNE 2005These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.ORDERING INFORMATION (1)MAXIMUM MAXIMUM NO MISSING PACKAGE SPECIFIED TRANSPORT INTEGRAL DIFFERENTIAL CODES PACKAGE PACKAGE ORDERING MODELMARKING TEMPERATUREMEDIA,LINEARITY LINEARITY RESOLULTIONTYPE DESIGNATORNUMBER (SYMBOL)RANGE QUANTITY (LSB)(LSB)(BIT)ADS7866I ±1.5–1/+1.512SOT23-6A66Y DBV –40°C to 85°C ADS7866IDBVT Small tape and reel,250ADS7866I ±1.5–1/+1.512SOT23-6A66Y DBV –40°C to 85°C ADS7866IDBVR Tape and reel,3000ADS7867I ±0.5±0.510SOT23-6A67Y DBV –40°C to 85°C ADS7867IDBVT Small tape and reel,250ADS7867I ±0.5±0.510SOT23-6A67Y DBV –40°C to 85°C ADS7867IDBVR Tape and reel,3000ADS7868I ±0.5±0.58SOT23-6A68Y DBV –40°C to 85°C ADS7868IDBVT Small tape and reel,250ADS7868I±0.5±0.58SOT23-6A68YDBV–40°C to 85°CADS7868IDBVRTape and reel,3000(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TI web site at .over operating free-air temperature range (unless otherwise noted)RATINGV DD to GND–0.3V to 4.0V Analog input voltage to GND –0.3V to V DD +0.3V Digital input voltage to GND –0.3V to 4.0V Digital output voltage to GND–0.3V to V DD +0.3VT AOperating free-air temperature range –40°C to 85°C T STORAGE Storage temperature range –65°C to 150°CT JJunction temperature 150°C θJA Thermal impedance 110.9°C/W SOT-23Package θJC Thermal impedance 22.31°C/W Vapor phase (10–40sec)250°C Lead temperature,soldering Infrared (10–30sec)260°C ESD3kV2元器件交易网 SPECIFICATIONS,ADS7866ADS7866ADS7867ADS7868 SLAS465–JUNE2005At–40°C to85°C,fSAMPLE =200KSPS and fSCLK=3.4MHz if1.6V≤VDD≤3.6V;f SAMPLE=100KSPS and f SCLK=1.7MHz if1.2V≤VDD<1.6V(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT SYSTEM PERFORMANCEResolution12BitsNo missing codes12BitsIntegral linearity–1.5 1.5LSB(1)Differential linearity–1 1.5LSB1.2V≤V DD<1.6V–22Offset error(2)LSB1.6V≤V DD≤3.6V–331.2V≤V DD<1.6V–22Gain error(3)LSB1.6V≤V DD≤3.6V–221.2V≤V DD<1.6V–2.5 2.5Total unadjusted error(4)LSB1.6V≤V DD≤3.6V–3.5 3.5SAMPLING DYNAMICS(See Timing Characteristics Section)t CONVERT Conversion time f SCLK=3.4MHz,13SCLK cycles 3.82µst SAMPLE Acquisition time f SCLK=3.4MHz,1.6V≤V DD≤3.6V0.64µsf SAMPLE Throughput rate f SCLK=3.4MHz,1.6V≤V DD≤3.6V200KSPSAperture delay10nsAperture jitter40ps DYNAMIC CHARACTERISTICSf IN=30kHz,1.2V≤V DD<1.6V68Signal-to-noiseSINAD dB and distortion fIN=30kHz,1.6V≤V DD≤3.6V6970f IN=30kHz,1.2V≤V DD<1.6V70SNR Signal-to-noise ratio dBf IN=30kHz,1.6V≤V DD≤3.6V7071f IN=30kHz,1.2V≤V DD<1.6V–70THD Total harmonic distortion(5)dBf IN=30kHz,1.6V≤V DD≤3.6V–83f IN=30kHz,1.2V≤V DD<1.6V75Spurious free dynamicSFDR dB range fIN=30kHz,1.6V≤V DD≤3.6V85At0.1dB,1.2V≤V DD<1.6V2At0.1dB,1.6V≤V DD≤3.6V4Full-power bandwidth(6)MHzAt3dB,1.2V≤V DD<1.6V3At3dB,1.6V≤V DD≤3.6V8 ANALOG INPUTFull-scale input span(7)VIN–GND0V DD VC S Input capacitance12pFInput leakage current–11µA DIGITAL INPUTLogic family,CMOS1.2V≤V DD<1.6V0.7×V DD 3.61.6V≤V DD<1.8V0.7×V DD 3.6V IH Input logic high level V1.8V≤V DD<2.5V0.7×V DD3.62.5V≤V DD≤3.6V2 3.6(1)LSB=Least Significant BIt(2)The difference in the first code transition000...000to000...001from the ideal value of GND+1LSB.(3)The difference in the last code transition011...111to111...111from the ideal value of V DD-1LSB with the offset error removed.(4)The absolute difference from the ideal transfer function of the converter.This specification is similar to INL error except the effects ofoffset error and gain error are included.(5)The2nd through10th harmonics are used to determine THD.(6)Input frequency where the amplitude of the digitized signal has decreased by0.1dB or3dB.(7)Ideal input span which does not include gain or offset errors.3元器件交易网ADS7866ADS7867ADS7868SLAS465–JUNE 2005SPECIFICATIONS,ADS7866(continued)At –40°C to 85°C,f SAMPLE =200KSPS and f SCLK =3.4MHz if 1.6V ≤V DD ≤3.6V;f SAMPLE =100KSPS and f SCLK =1.7MHz if 1.2V ≤V DD <1.6V (unless otherwise noted)PARAMETERTEST CONDITIONSMIN TYPMAX UNIT1.2V ≤V DD <1.6V–0.20.2×V DD 1.6V ≤V DD <1.8V –0.20.2×V DD V ILInput logic low levelV 1.8V ≤V DD <2.5V –0.20.3×V DD2.5V ≤V DD ≤3.6V–0.20.8I SCLK SCLK pin leakage current Digital input =0V or V DD–10.021µA I CS CS pin leakage current ±1µA C IN Digital input pin capacitance 10pF DIGITAL OUTPUTV OH Output logic high level I SOURCE =200µA V DD –0.2V DD V V OL Output logic low level I SINK =200µA 00.2V I SDO SDO pin leakage current Floating output –11µA Digital output pin C OUTFloating output10pF capacitanceData format,straight binaryPOWER SUPPLY REQUIREMENTS V DDSupply voltage1.23.6Vf SAMPLE =200KSPS,f SCLK =3.4MHz,V DD =3.6V 385500f SAMPLE =100KSPS,f SCLK =3.4MHz,V DD =3.6V 193µA f SAMPLE =50KSPS,f SCLK =3.4MHz,V DD =3.6V 97f SAMPLE =20KSPS,f SCLK =3.4MHz,V DD =3.6V 39f SAMPLE =200KSPS,f SCLK =3.4MHz,V DD =3V 340f SAMPLE =100KSPS,f SCLK =3.4MHz,V DD =3V 170µAf SAMPLE =50KSPS,f SCLK =3.4MHz,V DD =3V 85f SAMPLE =20KSPS,f SCLK =3.4MHz,V DD =3V 35f SAMPLE =200KSPS,f SCLK =3.4MHz,V DD =2.5V 305f SAMPLE =100KSPS,f SCLK =3.4MHz,V DD =2.5V153µA f SAMPLE =50KSPS,f SCLK =3.4MHz,V DD =2.5V 77Supply current,Digital inputs =0V I DDf SAMPLE =20KSPS,f SCLK =3.4MHz,V DD =2.5V 31normal operationor V DDf SAMPLE =200KSPS,f SCLK =3.4MHz,V DD =1.8V 256f SAMPLE =100KSPS,f SCLK =3.4MHz,V DD =1.8V 128µA f SAMPLE =50KSPS,f SCLK =3.4MHz,V DD =1.8V 65f SAMPLE =20KSPS,f SCLK =3.4MHz,V DD =1.8V 26f SAMPLE =200KSPS,f SCLK =3.4MHz,V DD =1.6V 241330f SAMPLE =100KSPS,f SCLK =3.4MHz,V DD =1.6V 121µA f SAMPLE =50KSPS,f SCLK =3.4MHz,V DD =1.6V 61f SAMPLE =20KSPS,f SCLK =3.4MHz,V DD =1.6V 25f SAMPLE =100KSPS,f SCLK =1.7MHz,V DD =1.2V 186250f SAMPLE =50KSPS,f SCLK =1.7MHz,V DD =1.2V 93µAf SAMPLE =20KSPS,f SCLK =1.7MHz,V DD =1.2V37I DDPower-down modeSCLK on or off0.0080.3µAPOWER DISSIPATIONf SAMPLE =200KSPS,f SCLK =3.4MHz,V DD =3.6V1.39 1.80Normal operation f SAMPLE =200KSPS,f SCLK =3.4MHz,V DD =1.6V 0.390.53mWf SAMPLE =100KSPS,f SCLK =1.7MHz,V DD =1.2V 0.220.3Power-down modeSCLK on or off,V DD =3.6V1.08µW TEMPERATURE RANGESpecified performance–4085°C4元器件交易网 SPECIFICATIONS,ADS7867ADS7866ADS7867ADS7868 SLAS465–JUNE2005At–40°C to85°C,fSAMPLE =240KSPS and fSCLK=3.4MHz if1.6V≤VDD≤3.6V;f SAMPLE=120KSPS and f SCLK=1.7MHz if1.2V≤VDD<1.6V(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT SYSTEM PERFORMANCEResolution10BitsNo missing codes10BitsIntegral linearity–0.50.5LSB(1)Differential linearity–0.50.5LSB1.2V≤V DD<1.6V–0.750.75Offset error(2)LSB1.6V≤V DD≤3.6V–111.2V≤V DD<1.6V–0.50.5Gain error(3)LSB1.6V≤V DD≤3.6V–0.50.51.2V≤V DD<1.6V–22Total unadjusted error(4)LSB1.6V≤V DD≤3.6V–22SAMPLING DYNAMICS(See Timing Characteristics Section)t CONVERT Conversion time f SCLK=3.4MHz,11SCLK cycles 3.235µst SAMPLE Acquisition time f SCLK=3.4MHz,1.6V≤V DD≤3.6V0.64µsf SAMPLE Throughput rate f SCLK=3.4MHz,1.6V≤V DD≤3.6V240KSPSAperture delay10nsAperture jitter40ps DYNAMIC CHARACTERISTICSf SAMPLE=100KSPS,f IN=30kHz,1.2V≤V DD<1.6V61Signal-to-noiseSINAD dB and distortion fSAMPLE=200KSPS,f IN=30kHz,1.6V≤V DD≤3.6V6161.7f SAMPLE=100KSPS,f IN=30kHz,1.2V≤V DD<1.6V61.5SNR Signal-to-noise ratio dBf SAMPLE=200KSPS,f IN=30kHz,1.6V≤V DD≤3.6V61.8f SAMPLE=100KSPS,f IN=30kHz,1.2V≤V DD<1.6V-68THD Total harmonic distortion(5)dBf SAMPLE=200KSPS,f IN=30kHz,1.6V≤V DD≤3.6V-78-72f SAMPLE=100KSPS,f IN=30kHz,1.2V≤V DD<1.6V73SFDR Spurious free dynamic range dBf SAMPLE=200KSPS,f IN=30kHz,1.6V≤V DD≤3.6V7480At0.1dB,1.2V≤V DD<1.6V2At0.1dB,1.6V≤V DD≤3.6V4Full-power bandwidth(6)MHzAt3dB,1.2V≤V DD<1.6V3At3dB,1.6V≤V DD≤3.6V8 ANALOG INPUTFull-scale input span(7)VIN–GND0V DD VC S Input capacitance12pFInput leakage current–11µA DIGITAL INPUTLogic family,CMOS1.2V≤V DD<1.6V0.7×V DD 3.61.6V≤V DD<1.8V0.7×V DD 3.6V IH Input logic high level V1.8V≤V DD<2.5V0.7×V DD3.62.5V≤V DD≤3.6V2 3.6(1)LSB=Least Significant BIt(2)The difference in the first code transition000...000to000...001from the ideal value of GND+1LSB.(3)The difference in the last code transition011...111to111...111from the ideal value of V DD-1LSB with the offset error removed.(4)The absolute difference from the ideal transfer function of the converter.This specification is similar to INL error except the effects ofoffset error and gain error are included.(5)The2nd through10th harmonics are used to determine THD.(6)Input frequency where the amplitude of the digitized signal has decreased by0.1dB or3dB.(7)Ideal input span which does not include gain or offset errors.5元器件交易网ADS7866ADS7867ADS7868SLAS465–JUNE 2005SPECIFICATIONS,ADS7867(continued)At –40°C to 85°C,f SAMPLE =240KSPS and f SCLK =3.4MHz if 1.6V ≤V DD ≤3.6V;f SAMPLE =120KSPS and f SCLK =1.7MHz if 1.2V ≤V DD <1.6V (unless otherwise noted)PARAMETERTEST CONDITIONSMIN TYPMAX UNIT1.2V ≤V DD <1.6V–0.20.2×V DD 1.6V ≤V DD <1.8V –0.20.2×V DD V ILInput logic low levelV 1.8V ≤V DD <2.5V –0.20.3×V DD2.5V ≤V DD ≤3.6V–0.20.8I SCLK SCLK pin leakage current Digital input =0V or V DD–10.021µA I CS CS pin leakage current ±1µA C IN Digital input pin capacitance 10pF DIGITAL OUTPUTV OH Output logic high level I SOURCE =200µA V DD –0.2V DD V V OL Output logic low level I SINK =200µA 00.2V I SDO SDO pin leakage current Floating output –11µA Digital output pin C OUTFloating output10pF capacitanceData format,straight binaryPOWER SUPPLY REQUIREMENTS V DDSupply voltage1.23.6V f SAMPLE =240KSPS,f SCLK =3.4MHz,V DD =3.6V 420500µA f SAMPLE =100KSPS,f SCLK =3.4MHz,V DD =3.6V172f SAMPLE =240KSPS,f SCLK =3.4MHz,V DD =1.6V 261330Supply current,Digital Inputs =0V I DDµA normal operationor V DD f SAMPLE =100KSPS,f SCLK =3.4MHz,V DD =1.6V107f SAMPLE =120KSPS,f SCLK =1.7MHz,V DD =1.2V 202250µA f SAMPLE =50KSPS,f SCLK =1.7MHz,V DD =1.2V83I DDPower-down modeSCLK on or off0.0080.3µAPOWER DISSIPATIONf SAMPLE =240KSPS,f SCLK =3.4MHz,V DD =3.6V1.51 1.80Normal operation f SAMPLE =240KSPS,f SCLK =3.4MHz,V DD =1.6V 0.420.53mWf SAMPLE =120KSPS,f SCLK =1.7MHz,V DD =1.2V 0.240.30Power-down modeSCLK on or off,V DD =3.6V1.08µW TEMPERATURE RANGESpecified performance–4085°C6元器件交易网 SPECIFICATIONS,ADS7868ADS7866ADS7867ADS7868 SLAS465–JUNE2005At–40°C to85°C,fSAMPLE =280KSPS and fSCLK=3.4MHz if1.6V≤VDD≤3.6V;f SAMPLE=140KSPS and f SCLK=1.7MHz if1.2V≤VDD<1.6V(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT SYSTEM PERFORMANCEResolution8BitsNo missing codes8BitsIntegral linearity–0.50.5LSB(1)Differential linearity–0.50.5LSB1.2V≤V DD<1.6V–0.50.5Offset error(2)LSB1.6V≤V DD≤3.6V–0.50.51.2V≤V DD<1.6V–0.50.5Gain error(3)LSB1.6V≤V DD≤3.6V–0.50.51.2V≤V DD<1.6V–11Total unadjusted error(4)LSB1.6V≤V DD≤3.6V–11SAMPLING DYNAMICS(See Timing Characteristics Section)t CONVERT Conversion time f SCLK=3.4MHz,9SCLK cycles 2.647µst SAMPLE Acquisition time f SCLK=3.4MHz,1.6V≤V DD≤3.6V0.64µsf SAMPLE Throughput rate f SCLK=3.4MHz,1.6V≤V DD≤3.6V280KSPSAperture delay10nsAperture jitter40ps DYNAMIC CHARACTERISTICSf SAMPLE=100KSPS,f IN=30kHz,1.2V≤V DD<1.6V49Signal-to-noiseSINAD dB and distortion fSAMPLE=200KSPS,f IN=30kHz,1.6V≤V DD≤3.6V4949.4f SAMPLE=100KSPS,f IN=30kHz,1.2V≤V DD<1.6V49.4SNR Signal-to-noise ratio dBf SAMPLE=200KSPS,f IN=30kHz,1.6V≤V DD≤3.6V49.8f SAMPLE=100KSPS,f IN=30kHz,1.2V≤V DD<1.6V–65Total harmonicTHD dB distortion(5)fSAMPLE=200KSPS,f IN=30kHz,1.6V≤V DD≤3.6V–72-66f SAMPLE=100KSPS,f IN=30kHz,1.2V≤V DD<1.6V67Spurious free dynamicSFDR dB range fSAMPLE=200KSPS,f IN=30kHz,1.6V≤V DD≤3.6V6667At0.1dB,1.2V≤V DD<1.6V2At0.1dB,1.6V≤V DD≤3.6V4Full-power bandwidth(6)MHzAt3dB,1.2V≤V DD<1.6V3At3dB,1.6V≤V DD≤3.6V8 ANALOG INPUTFull-scale input span(7)VIN–GND0V DD VC S Input capacitance12pFInput leakage current–11µA DIGITAL INPUTLogic family,CMOS1.2V≤V DD<1.6V0.7×V DD 3.61.6V≤V DD<1.8V0.7×V DD 3.6V IH Input logic high level V1.8V≤V DD<2.5V0.7×V DD3.62.5V≤V DD≤3.6V2 3.6(1)LSB=Least Significant BIt(2)The difference in the first code transition000...000to000...001from the ideal value of GND+1LSB.(3)The difference in the last code transition011...111to111...111from the ideal value of V DD-1LSB with the offset error removed.(4)The absolute difference from the ideal transfer function of the converter.This specification is similar to INL error except the effects ofoffset error and gain error are included.(5)The2nd through10th harmonics are used to determine THD.(6)Input frequency where the amplitude of the digitized signal has decreased by0.1dB or3dB.(7)Ideal input span which does not include gain or offset errors.7元器件交易网ADS7866ADS7867ADS7868SLAS465–JUNE 2005SPECIFICATIONS,ADS7868(continued)At –40°C to 85°C,f SAMPLE =280KSPS and f SCLK =3.4MHz if 1.6V ≤V DD ≤3.6V;f SAMPLE =140KSPS and f SCLK =1.7MHz if 1.2V ≤V DD <1.6V (unless otherwise noted)PARAMETERTEST CONDITIONSMIN TYPMAX UNIT1.2V ≤V DD <1.6V–0.20.2×V DD 1.6V ≤V DD <1.8V –0.20.2×V DD V ILInput logic low levelV 1.8V ≤V DD <2.5V –0.20.3×V DD2.5V ≤V DD ≤3.6V–0.20.8I SCLK SCLK pin leakage current Digital input =0V or V DD –10.021µA I CS CS pin leakage current ±1µA Digital input pin C IN10pF capacitanceDIGITAL OUTPUT V OH Output logic high level I SOURCE =200µA V DD –0.2V DD V V OL Output logic low level I SINK =200µA 00.2V I SDO SDO pin leakage current Floating output –11µA Digital output pin C OUTFloating output10pFcapacitance Data format,straight binaryPOWER SUPPLY REQUIREMENTS V DDSupply voltage1.23.6V f SAMPLE =280KSPS,f SCLK =3.4MHz,V DD =3.6V 439500µA f SAMPLE =100KSPS,f SCLK =3.4MHz,V DD =3.6V154f SAMPLE =280KSPS,f SCLK =3.4MHz,V DD =1.6V 264330Supply current,Digital Inputs =0V I DDµA normal operationor V DD f SAMPLE =100KSPS,f SCLK =3.4MHz,V DD =1.6V93f SAMPLE =140KSPS,f SCLK =1.7MHz,V DD =1.2V 201250µA f SAMPLE =50KSPS,f SCLK =1.7MHz,V DD =1.2V70I DDPower-down modeSCLK on or off0.0080.3µAPOWER DISSIPATIONf SAMPLE =280KSPS,f SCLK =3.4MHz,V DD =3.6V1.58 1.8Normal operation f SAMPLE =280KSPS,f SCLK =3.4MHz,V DD =1.6V 0.420.53mWf SAMPLE =140KSPS,f SCLK =1.7MHz,V DD =1.2V 0.240.3Power-down modeSCLK on or off,V DD =3.6V1.08µW TEMPERATURE RANGESpecified performance–4085°C8元器件交易网TIMING REQUIREMENTS (1)(2)ADS7866ADS7867ADS7868SLAS465–JUNE 2005At –40°C to 85°C,f SCLK =3.4MHz if 1.6V ≤V DD ≤3.6V;f SCLK =1.7MHz if 1.2V ≤V DD <1.6V,50-pF Load on SDO Pin,unless otherwise notedPARAMETERTEST CONDITIONS MIN TYPMAX UNIT t sample Sample timet SU(CSF-FSCLKF)+2×t C(SCLK)µs ADS786613×t C(SCLK)t convertConversion timeADS786711×t C(SCLK)µsADS78689×t C(SCLK)1.2V ≤V DD <1.6VSee (3)1001.6V ≤V DD <1.8V See (3)100t C(SCLK)Cycle timeµs1.8V ≤V DD <2.5V See (3)502.5V ≤V DD ≤3.6VSee(3)6.7t WH(SCLK)Pulse duration 0.4×t C(SCLK)0.6×t C(SCLK)ns t WL(SCLK)Pulse duration0.4×t C(SCLK)0.6×t C(SCLK)ns 1.2V ≤V DD <1.6V192t SU(CSF-FSCLKF)Setup time1.6V ≤V DD <1.8V 55ns1.8V ≤V DD ≤3.6V 551.2V ≤V DD <1.6V65t D(CSF-SDOVALID)Delay time1.6V ≤V DD <1.8V 55ns 1.8V ≤V DD ≤3.6V 551.2V ≤V DD <1.6V20t H(SCLKF-SDOVALID)Hold time1.6V ≤V DD <1.8V 10ns1.8V ≤V DD ≤3.6V 101.2V ≤V DD <1.6V140t D(SCLKF-SDOVALID)Delay time1.6V ≤V DD <1.8V 140ns 1.8V ≤V DD ≤3.6V 1401.2V ≤V DD <1.6V1080t DIS(EOC-SDOZ)Disable time1.6V ≤V DD <1.8V 760ns 1.8V ≤V DD ≤3.6V 7601.2V ≤V DD <1.6V20t WH(CS)Pulse duration1.6V ≤V DD <1.8V 10ns1.8V ≤V DD ≤3.6V 101.2V ≤V DD <1.6V20t SU(LSBZ-CSF)Setup time1.6V ≤V DD <1.8V 10ns 1.8V ≤V DD ≤3.6V10(1)All input signals are specified with t r =t f =5ns (10%to 90%of V DD )and timed from a voltage level of (V IL +V IH )/2.(2)See timing diagram in Figure 1.(3)Min t C(SCLK)is Min t SAMPLE of the specific resolution and supply voltage.See Acquisition Time,Conversion Time,and Total Cycle Time section for further details.Figure 1.Timing Diagram9元器件交易网PINCONFIGURATION(TOP VIEW)REF/V DDGND VINSCLKADS7866/67/68DBV PACKAGE CS SDO ADS7866ADS7867ADS7868SLAS465–JUNE 2005TERMINAL FUNCTIONSTERMINAL DESCRIPTIONNAME NO.REF/V DD 1External reference input and power supplyGND 2Ground for signal and power supply.All analog and digital signals are referred with respect to this pin.VIN 3Analog signal inputSCLK 4Serial clock input.This clock is used for clocking data out,and it is the source of conversion clock.This is the serial data output of the conversion result.The serial stream comes with MSB first.The MSB is clocked out (changed)on the falling edge one SCLK after the sampling period ends.This results in four leading zeros after CS SDO5becomes active.SDO is 3-stated once all the valid bits are clocked out (12for ADS7866,10for ADS7867,and 8for ADS7868).This is an active low input signal.It is used as a chip select to gate the SCLK input,to initiate a conversion,and to CS 6frame output data.10元器件交易网TYPICAL CHARACTERISTICS ADS7866f i − Input Frquency − kHzN o r m a l i z e d A m p l i t u d e − d B05101520253035404550f i − Input Frquency − kHzN o r m a l i z e d A m p l i t u d e − dBf i − Input Frequency − kHzT H D − T o t a l H a r m o n i c D i s t o r t i o n − d Bf i − Input Frequency − kHzS N R − S i g n a l -t o -N o i s e R a t i o − d Bf i − Input Frequency − kHzS I N A D − S i g n a l -t o -N o i s e a n d D i s t o r t i o n − d BFFT (8192Points)Figure 2.FFT (8192Points)Figure 3.SIGNAL-TO-NOISE RATIOSIGNAL-TO-NOISE TOTAL HARMONIC DISTORTIONvsAND DISTORTIONvsINPUT FREQUENCYvsINPUT FREQUENCYINPUT FREQUENCYFigure 4.Figure 5.Figure 6.f i − Input Frequency − kHzS F D R − S p u r i o u s F r e e D y n a m i c R a n g e − dBSCLK Frequency − MHzC C I S u p p l y C u r r e n t − −AµV DD − Supply Voltage − VC C I S u p p l y C u r r e n t − −AµThroughput − KSPSP o w e r C o n s u m p t i o n − m Wf i − Input Frequency − kHzT H D − T o t a l H a r m o n i c D i s t o r t i o n − dBCodeI N L − L S B s(Straight Binary in Decimal)SPURIOUS FREE DYNAMIC RANGESUPPLY CURRENTSUPPLY CURRENTvsvsvsINPUT FREQUENCYSCLK FREQUENCYSUPPLY VOLTAGEFigure 7.Figure 8.Figure 9.POWER CONSUMPTIONTOTAL HARMONIC DISTORTIONvsvsTHROUGHPUTINPUT FREQUENCYFigure 10.Figure 11.Figure 12.00.20.40.60.81CodeD N L − L S B s(Straight Binary in Decimal)−1−0.8−0.6−0.4−0.200.20.40.60.8105121024153620482560307235844096CodeI N L − L S B s(Straight Binary in Decimal)CodeD N L − L S B s(Straight Binary in Decimal)DNLFigure 13.INLFigure 14.DNLFigure 15.V DD − Supply Voltage − VC C I S u p p l y C u r r e n t − −AµV DD − Supply Voltage − VT h r o u g h p u t R a t e − K S P SV DD − Supply Voltage − VT h r o u g h p u t R a t e − K S P SMAX SUPPLY CURRENTTHROUGHPUT RATETHROUGHPUT RATEvsvsvsSUPPLY VOLTAGESUPPLY VOLTAGESUPPLY VOLTAGEFigure 16.Figure 17.Figure 18.f i − Input Frequency − kHzN o r m a l i z e d A m p l i t u d e − d BN o r m a l i z e d A m p l i t u d e − d Bf i− Input Frequency − kHzV DD − Supply Voltage − VT h r o u g h p u t R a t e − K S P S1.21.4 1.6 1.8V DD − Supply Voltage − VT h r o u g h p u t R a t e − K S P SFFT (8192Points)Figure 19.FFT (8192Points)Figure 20.THROUGHPUT RATETHROUGHPUT RATEvsvsSUPPLY VOLTAGESUPPLY VOLTAGEFigure 21.Figure 22.N o r m a l i z e d A m p l i t u d e − d Bf i− Input Frequency − kHzN o r m a l i z e d A m p l i t u d e − d Bf i − Input Frequency − kHzV DD − Supply Voltage − VT h r o u g h p u t R a t e − K S P SV DD − Supply Voltage − VT h r o u g h p u t R a t e − K S P SFFT (8192Points)Figure 23.FFT (8192Points)Figure 24.THROUGHPUT RATETHROUGHPUT RATEvsvsSUPPLY VOLTAGESUPPLY VOLTAGEFigure 25.Figure 26.THEORY OF OPERATIONThe ADS7866/67/68is a family of low supply voltage,low power,high-speed successive approximation register (SAR)analog-to-digital converters(ADCs).The devices can be operated from a supply range from1.2V to3.6 V.There is no need for an external reference.The reference is derived internally from the supply voltage,so the analog input range can be from0V to V DD.These ADCs use a charge redistribution architecture,which inherently includes a sample/hold function.START OF A CONVERSION CYCLEA conversion cycle is initiated by bringing the CS pin low and supplying the serial clock SCLK.The time between the falling edge of CS and the third falling edge of SCLK after CS falls is used to acquire the input signal.This must be greater than or equal to the minimum acquisition time(MIN t SAMPLE in Table1)specified for the desired resolution and supply voltage.On the third falling edge of SCLK after CS goes into hold mode and the process of digitizing the sampled input signal starts.Acquisition Time,Conversion Time,and Total Cycle TimeThe maximum SCLK frequency is determined by the minimum acquisition time(MIN t SAMPLE)specified for the specific resolution and supply voltage of the device.The conversion time is determined by the frequency of SCLK since this is a synchronous converter.The conversion time is13times the SCLK cycle time t C(SCLK)for the ADS7866,11times for the ADS7867,and9times for the ADS7868.The acquisition time,which is also the power up time,is the set-up time between the first falling edge of SCLK after CS falls(t SU(CSF-FSCLKF))plus2 times t C(SCLK).The total cycle time,t CYCLE,which is the inverse of the maximum sample rate,can be calculated as follows: t CYCLE=t SAMPLE+t CONVERT+0.5×t C(SCLK)if t DIS(EOC-SDOZ)+t SU(LSBZ-CSF)≤0.5×t C(SCLK)t CYCLE=t SAMPLE+t CONVERT+t DIS(EOC-SDOZ)+t SU(LSBZ-CSF)if t DIS(EOC-SDOZ)+t SU(LSBZ-CSF)>0.5×t C(SCLK)。

ads7846工作原理

ads7846工作原理ADS7846是一种触摸屏控制器,常用于嵌入式系统中。

它的工作原理是基于电阻式触摸屏的工作原理,通过检测电阻屏上两个坐标轴上的电压来确定用户的触摸位置。

下面将详细介绍ADS7846的工作原理。

电阻式触摸屏是一种常见的触摸屏技术,它由一层透明的电阻膜和一层玻璃面板组成。

电阻膜上涂有导电涂层,通常是用ITO(铟锡氧化物)材料制成。

当用户用手指或者触摸笔触摸屏幕时,手指或笔尖会与电阻膜上的导电涂层接触,形成一个电阻。

ADS7846通过在电阻屏上施加一对电压来检测触摸位置。

它会在X 轴和Y轴上分别施加一对电压,然后测量电阻屏上两个坐标轴上的电压。

通过测量电阻屏上两个坐标轴上的电压,ADS7846可以计算出用户触摸的具体位置。

为了实现这个过程,ADS7846内部有一个模数转换器(ADC),它可以将电阻屏上的电压转换为数字信号。

在测量过程中,ADS7846会将电阻屏上的电压与内部参考电压进行比较,然后将比较结果转换为数字信号。

为了提高测量的准确性,ADS7846还会进行一些校准操作。

校准操作可以消除电阻屏上的误差,确保测量结果的准确性。

通常,校准操作会在系统启动时进行,以校准电阻屏的坐标轴。

除了基本的触摸位置检测,ADS7846还可以检测多点触摸。

多点触摸是指用户同时使用多个手指或者多支触摸笔在屏幕上进行触摸操作。

ADS7846可以通过多个通道同时检测多个触摸点的位置,并将其转换为数字信号。

ADS7846是一种基于电阻式触摸屏的触摸屏控制器,通过测量电阻屏上两个坐标轴上的电压来确定用户的触摸位置。

它通过内部的模数转换器将电压转换为数字信号,并可以进行校准操作来提高测量的准确性。

除了基本的触摸位置检测,ADS7846还支持多点触摸功能。

ADS7846中文规格书-new

电压

内部基准 -

温漂

静态电流 -

外部基准输入

输入电压 -

范围

输入阻抗 内部基准电路停止

内部基准电路启用

电池电压监测

电压输入 -

范围

输入阻抗 采样电池电压

关闭电池电压监测

准确率

外部基准 2.5V

内部基准

温度检测

温度测量 -

范围

分辨率

差动模式(3)

准确率

TEMP0(4) 差动模式(3)

TEMP0(4)

数字输入/输出

电源电压在 2.7V 时功耗的典型值为 0.75mW (关闭内部基准), 转换速率为 125kHz,ADS7846芯片是电 池供电系统的理想选择,譬如 PDAs 与属于触摸屏、传呼器、手机和其它便携式的设备。ADS7846 有 TSSOP16、QFN16 和 VFBGA48 等封装形式,可在–40℃+85℃温度范围内工作。

-40

85

℃

注释:(1)LSB 是最低有效位,当 VREF=+2.5V 时 1LSB=610μV;(2)超过 50mA 的源电流将导致

器件性能降低;(3)差动模式下,测量 TEMP0 和 TEMP1 间的电压差;(4)TEMP0 模式下温漂为-2.1mV/℃;

(5)ADS7846 在 2.2V 的电源电压下,数字部分将停止工作。

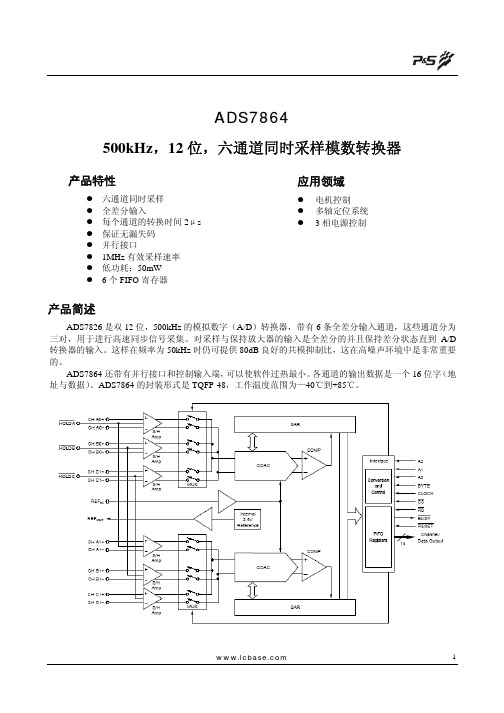

ADS7864

12位500KHz六通道同时采样的A/D转换器ADS7864及应用ADS7864是德州仪器(TI)公司Burr-Brown产品部最新推出的快速6通道全差分输入的双12位A/D转换器。

它能以500kHz的采样率同时进行六通道信号采样。

特别适用于马达控制和电力监控。

ADS7864的6路输入通道可分成3对,测量电机控制或电力监控应用的三相,并将模拟信号转换成DSP或微处理器所需的数字信号。

输入给片内6个采样-保持放大器的信号经全差分并在ADC输入期间内保持,使其在50kHz时仍能提供高达80dB的良好共模抑制比,对高噪声环境中的输入噪声抑制起到非常重要的作用。

ADS7864特有的并行接口能与六个FIFO寄存器连接,便于更快速地捕获数据。

各通道输出字(地址和数据)为16位。

* 6通道同时采样* 全差分输入* 每个通道转换时间2ms* 保证无失码* 并行接口* 低功耗:50mW* 6个FIFO寄存器芯片的工作原理ADS7864包含两个可以同时工作的12位A/D转换器。

其3个保持信号(HOLDA,HOLDB,HOLDC)选择输入的多路开关并且启动A/D转换。

这3个保持信号同时有效就可以同时保持6路输入信号,转换的数据分别存放在6个寄存器中。

模拟信号输入模拟信号输入一般有两种方法,即单端输入和差分输入。

单端输入时-IN输入端保持在共模电压,+IN输入模拟信号;差分输入时,输入信号的幅值为+IN和-IN输入的差。

双极性输入的信号,如±2.5V, ±5V, ±10V,可以通过如下的电路将其转换成0V~5V的输入范围。

启动A/D转换当保持信号HOLDX变为低电平时,对应的输入信号立即被保持,只要这时ADC是空闲的,即可进行A/D转换。

如果这时已有其它的通道处于保持态,则该通道将等待前面的通道完成转换后才能进行A/D转换。

如果在一个时钟周期各通道都处于保持态时,则通道A先转换,接着通道B,最后是通道C。

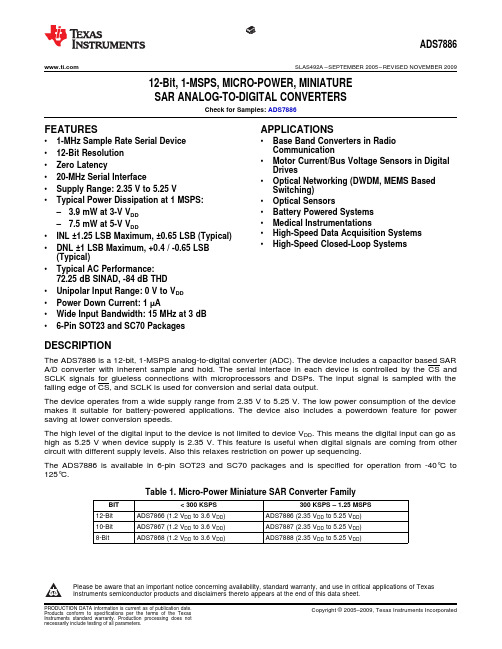

ADS7886 中文资料

ADS7886 12位1MSPS,微功率微SAR 模数转换器产品特征:1MHz采样频率串行装置12位分辨率零延迟20-MHz串行接口电源供电范围:2.55V~5.25V标准功耗在每秒百万次(转换速率单位):——3.9mW 在3V VDD——7.5mW 在5V VDDINL ±1.25 LSB Maximum, ±0.65 LSB (标准)DNL ±1 LSB Maximum, +0.4 / -0.65 LSB(标准){ INL 积分非线性(Integral nonlinearity,INL)积分非线性表示了ADC器件在所有的数值点上对应的模拟值和真实值之间误差最大的那一点的误差值,也就是输出数值偏离线性最大的距离。

单位是LSB。

例如,一个12bit的ADC,INL值为1LSB,那么,对应基准4.095V,测某电压得到的转换结果是1.000V,那么,真实电压值可能分布在0.999V到1.001V之间。

DNL(Differential Nonlinearity,差分非线性):理想刻度与实际刻度的偏差值。

对于一个理想ADC,其微分非线性为DNL = 0LSB,也就是说每个模拟量化台阶等于1LSB (1LSB = VFSR/N,其中VFSR为满量程电压,N是ADC的分辨率),跳变值之间的间隔为精确的1LSB。

若DNL误差指标≤ 1LSB,就意味着传输函数具有保证的单调性,没有丢码。

}标准交流性能:72.25 dB SINAD, -84 dB THD单极输入电压范围:0V~VDD电源休眠电流:1Μa输入带宽:15 MHz at 3 dB6引脚SOT23 and SC70 封装应用:广播通信中的基带转换器应用、电机电流/总线电压传感器在数字转换器中的应用光网络(基于DWDM,MEMS的开关)光学传感器电池供电系统医疗仪器高速数据采集系统高速闭环系统产品说明:ADS7886是12位,1-MSPS模拟-数字转换器(ADC)。

ADS7869:完整的模拟马达控制前端

可 能有 用 。

其它特有功能, 因此它非常适用于高

端 马 达 控 制 系 统 。A S 89 是 这 系 D 76

制 主 要 是 由A S 89的 内部 电容 器 D 76

列的最 新产 品 除了能以更低 的价 格提供 V C N 0 E A A 1具有的各种功能 以外 , 它还提供了几种 新的功能 , 像

在所有马达控制 应用 中, 都须对

流 向 马达 的 电流 进 行 监 测 ( 入 f 输 U、

世界 电子元器件 2 0 . 0 71 ww g c gc r w. e ma .o n

维普资讯

感 相位 电流

对 于 流 向马 达 的 电 流 ,它 们 的

就够 了 。电流 输 入 与 输 出 的典 型 配 在 此 仅 对 其 进 行 计 数 以 确 定 实 际 置 详 见 图 2 。

位置。

器在 内部与各 引脚相连 。 一旦 电流

改 变 方 向, B I T就 需切 换 这 是 由 G

符 号 比较器 X C m ( =U V或W) _ o pX 、

I V与 I 。更精确 的系统还 需要测 定 所 需 的速 度 或 位 置 。在 图 1 示 W) 的

模 S 8 9的 输入 量 马 达 的位 置 (1B)或 / 负 载 例 中 , 拟 输 入 与 AD 7 6 A、 1 和

的位置 (2 B ) A 、 2。机器通 常还包 含 A 2相 连 。 N

最 后 ,这 些 三 相 电流 的幅 度 通 产 生 正 弦 波 与 余 弦 波 。 过 多 路 模 数 转 换 器 进 行 同步 转 换 , A S 8 9内的 一 组 比较 器 将 正 D 76 模 数 转 换 器 通 过 输 入 多 路 复 用 器 与 弦 与 余 弦 数 字 化 。产 生 的 脉 冲 被

ads8866idgs的原理

ads8866idgs的原理

ads8866idgs是一种数字信号处理器芯片,其原理主要包括以下几点:

1. AD转换原理:ads8866idgs采用了高性能的模数转换技术,能够将模拟信号转换为数字信号。

通过内置的ADC(模数转换器)模块,将输入的模拟信号进行采样和量化,然后输出对应的数字信号。

2. 数字信号处理:ads8866idgs内部集成了多种数字信号处理算法和功能模块,可以对采集到的数字信号进行滤波、数学运算、数据处理等操作,从而实现对信号的处理和分析。

3. 数据存储与传输:ads8866idgs还具有数据存储与传输功能,可以将处理后的数据存储到内部存储器中,也可以通过各种接口将数据传输到外部设备进行进一步处理或显示。

ads8866idgs的原理是通过模数转换、数字信号处理和数据传输等技术,实现对模拟信号的采集、处理和传输,为数字信号处理领域提供了强大的功能和性能。

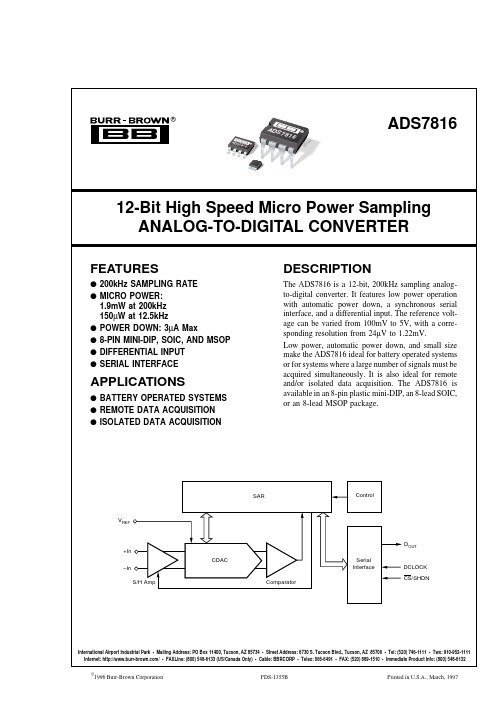

ADS7816

®

ADS7816

2

ABSOLUTE MAXIMUM RATINGS(1)

+VCC ..................................................................................................... +6V Analog Input ........................................................... –0.3V to (+VCC + 0.3V) Logic Input ............................................................. –0.3V to (+VCC + 0.3V) Case Temperature ......................................................................... +100°C Junction Temperature .................................................................... +150°C Storage Temperature ..................................................................... +125°C External Reference Voltage .............................................................. +5.5V NOTE: (1) Stresses above these ratings may permanently damage the device.

7848B DVB-T T2 T2 Lite DVB-S S2 S2X 数字测量仪 - 说明书

Touch screen, compact, robust and easy to useWith a panoramic 7 inches touch screen, you have full be-nefit of the touch screen technology: intuitive access to functions, menus and measurements. The new rugged housing with protective bumpers is designed for exten-sive field use and protection of sensitive parts of the ins-trumentAll digital measurements in DVB-T,DVB-T2/T2 Lite, DVB-S, DVB-S2, and DVB-S2X (option)The 7848B provides all measurements in DVB-T, DVB-T2/T2Lite, DVB-S,DVB-S2, and DVB-S2X (option). For each digital standard, we provide all measurements, including error rate, the constellation diagram and echoes analysis.All necessary functions and tools to save timeThe 7848B has a very simple and intuitive man-machine interface. Special functions have been added to save time and money.Checking the alignment of antennasThe 7848B includes a checksat mode for satellite and a special tool to align terrestrial antennas. User will have a graphical information combined with a beeper.USB InterfaceThe 7848B includes one USB interface for updating and getting the benefit of free firmware updates. The inter-face can be used to transfer measurements data, screens shots to a USB memory stick.* only for free-to-airA performing autosetAll measurements displayedon a single screenFast spectrum analysisEchoes display with guard intervalD V B -T 2D V B -T D V B -S D V B -S 2D V B -S 2X (o p t io n )W i d e ba n dM u l t i s tr e a mSun protector+rain protector+belt clip - P/N: 978489000AccessoriesRain protector - P/N: 978489500Carrying bag (supplied in standard) - P/N:978481000Carrying case - P/N:978483000Car cigar lighter adapter - P/N:978361000。

触摸屏控制芯片ADS7843中文资料

触摸屏控制芯片ADS7843中文资料当触笔触到屏上时,对应的位置就会产生相应大小的电压,输入到芯片,AD 转换后得到一个数据。

而触摸校准就是将接受到的原始模数转换值转换成屏幕像素坐标。

再就是了解触摸芯片,知道他的工作方式,以及跟STM32的连线。

触摸实验中,我的实验板是用SPI口来实现数据的传输的,即SPI与xpt2046相连。

触摸屏控制芯片ADS7843中文资料ADS7843是一个内置12位模数转换、低导通电阻模拟开关的串行接口芯片。

供电电压2.7~5 V,参考电压VREF为1 V~+VCC,转换电压的输入范围为0~ VREF,最高转换速率为125 kHz。

ADS7843引脚图及引脚功能说明了:ADS7843的引脚配置如图3所示。

表1为引脚功能说明,图4为典型应用。

ADS7843典型应用电路ADS7843之所以能实现对触摸屏的控制,是因为其内部结构很容易实现电极电压的切换,并能进行快速A/D转换。

图5所示为其内部结构,A2~A0和SER/为控制寄存器中的控制位,用来进行开关切换和参考电压的选择。

ADS7843之所以能实现对触摸屏的控制,是因为其内部结构很容易实现电极电压的切换,并能进行快速A/D转换。

图5所示为其内部结构,A2~A0和SER/为控制寄存器中的控制位,用来进行开关切换和参考电压的选择。

2.3 ADS7843的控制字及数据传输格式ADS7843的控制字如表4所列,其中S为数据传输起始标志位,该位必为"1"。

A2~A0进行通道选择(见表2和3)。

MODE用来选择A/D转换的精度,"1"选择8位,"0"选择12位。

SER/选择参考电压的输入模式(见表2和3)。

PD1、PD0选择省电模式:"00"省电模式允许,在两次A/D转换之间掉电,且中断允许;"01"同"00",只是不允许中断;"10"保留;"11"禁止省电模式。

12位500kHz六通道同时采样的A/D转换器ADS7864及其应用

12位500kHz六通道同时采样的A/D转换器ADS7864及

其应用

金鹰; 赵建洋; 等

【期刊名称】《《电子产品世界》》

【年(卷),期】2001(000)005

【摘要】本文介绍了可六路同时采样的高速A/D转换器ADS7864的性能、特点及工作原理,并介绍了该芯片在电网参数监测系统中的应用。

【总页数】2页(P46-47)

【作者】金鹰; 赵建洋; 等

【作者单位】淮阴工学院

【正文语种】中文

【中图分类】TP335.1

【相关文献】

1.12位A/D转换器ADS7864在电网谐波分析仪中的应用 [J], 孙光;梁长垠

2.AD9433 12位105/125MSPS射频采样A/D转换器 [J], 安德烈

3.8通道12位串行A/D转换器MAX1202及其应用 [J], 蒋双梅;高敦堂;都思丹

4.ADI 16通道12/16位数模转换器瞄准电信光模块控制应用 [J],

5.带嵌入式MCU的8通道12位A/D转换器ADuC812及其应用 [J], 谢卫华

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。