EDA_BOMHelper正式版 以BOM元件值反向修改Layout元件值 篇

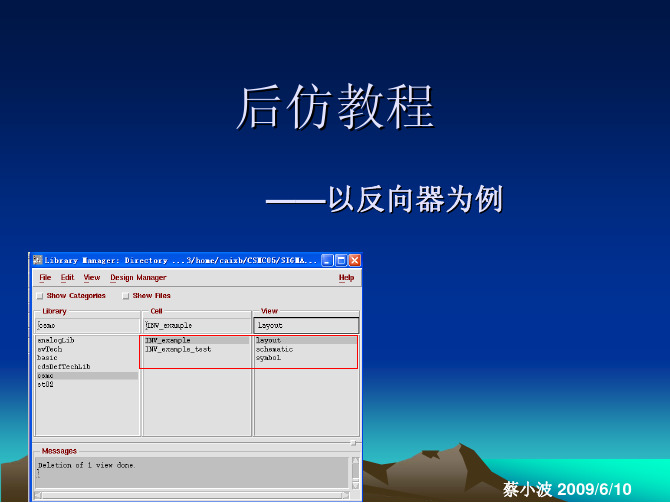

cadence后仿教程

默认第一项是 spectre,意味着 INV_example_tes t里调用的是 INV_example的 schmatic view来 进行仿真

如要进行后仿我们得 修改Switch View List, 把calibre加在spectre 前面,意味着仿真的时 候INV_example_test 调用INV_example的 calibre view来进行仿 真,这就是后仿!!!

<3>指定提取哪些节点的寄生参数: 默认是ALL Nets(提取所有节点) 也可以自定义(Specified Nets):可以提取除了指

定节点以外的所有节点(Exclude),也可以只提取指定的 节点(Include),在相应的文本框里写入节点的net名即 可,或者点击右侧的小箭头,然后在弹出的原理图里选择你 想输入的节点,按ESC键,你所选择的节点名就自动填在左 侧文本框中.

至此,我们仍未进行后仿,我们只是提取出 了寄生参数,并生成了带这些寄生参数的 calibre view,这都是为后仿做准备. 接下来介绍如何后仿.

方法一

1.打开测试平台,此 例是 INV_example_test. 2.打开ADE (仿真环 境)窗口 3.与仿真原理图不 同的是多出这一步: 点击Setup— >Environment 弹出一个配置窗口 (见下页)

6.Run PEX

弹出两个框:一个 是Calibre View配 置对话框(左 图),一个是寄生 参数文本(见下 页). 注意左边两个设 置,其他默认即 可.

6.Run PEX

第一次运行PEX会弹 出映射文件向导, 引导大家生成 MAP文件. 以后就不用设置了. 除了寄生电阻寄生电 容以外,所有器件 都用st02中的模型 来映射.

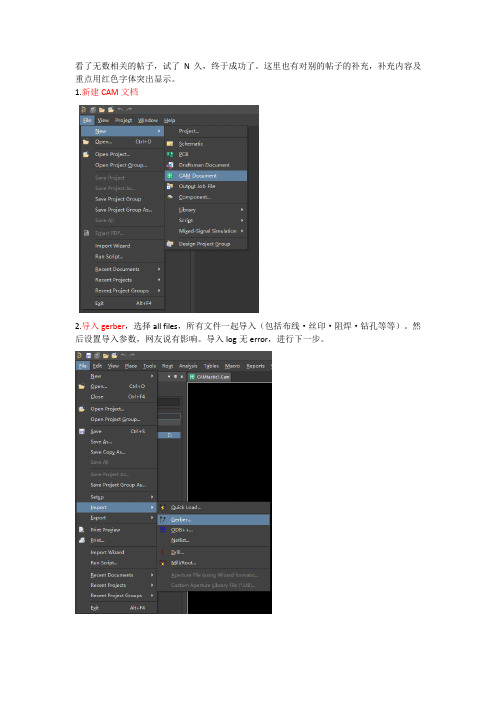

AD 19 gerber反转pcb

看了无数相关的帖子,试了N久,终于成功了。

这里也有对别的帖子的补充,补充内容及重点用红色字体突出显示。

1.新建CAM文档2.导入gerber,选择all files,所有文件一起导入(包括布线·丝印·阻焊·钻孔等等)。

然后设置导入参数,网友说有影响。

导入log无error,进行下一步。

3.导入drill。

问题来了,题主怎么都导入不成功,一直提示error:no recognized CAM files……导入的文件是后缀.drl的,理论上没问题。

拿别的.drl(钻孔文件)来试,导入成功。

说明该钻孔文件本身有问题,跳过此步,毕竟第一步导入gerber时,钻孔文件是有一起导入的,而且cam文档里,可以查看到drill层。

此图为别的导入成功的drill表。

导入时,可去设置units,多试试几个,直到不出现警告。

注意红色圈出来的部分,后面有大用。

4.抽取网络表,出现error。

出现error不要着急,神挡杀神,一个个去解决。

根据提示去设置层叠,也可提前设置。

主要是指定好TOP,Bottom。

接着设置PCB叠构,两层板:TOP为1,Bottom为2。

对于四层板:需要分别设置1层2层3层4层接着再抽取网络表,还是error根据提示去定义NC tools,到底怎么设定呢?灵机一动,想到上面导入成功导入时的提示,就下面第二张图So做如下设置。

后来反应过来,设置的是钻孔孔径:30mil的过孔然后就可以顺利的抽取网络表了5.导出到PCB,大功告成总结:导入钻孔表的目的是导入钻孔直径,钻孔层已经在导入gerber时导入了。

若是导入不成功,后面在NC tools自己设置。

题主试过另一个工程文件,drill导入成功,但是抽取网表时,还是error:no tools defined in NC tools table,还是得自己设置。

这是本人此次花费大量时间的罪魁祸首。

不知道是软件原因还是什么,反正宗旨是跟着步骤一步一步来,遇到什么问题就去解决,总会成功的。

AD20设计规则小结(DesignRules)

AD20设计规则⼩结(DesignRules)⼀.Electrical(电器规则)1.Clearence (线间距、铺铜间距设置规则)常规情况下,铺铜间距可设置为线间距的2-3倍;且铺铜间距和线间距应该分开制定规则。

2.Short-Circuit(短路提醒设置)此规则⽤来设计电路⽹络中的短路许可,系统默认规则是不允许短路。

3.Un-Routed Net(不完全连接检查规则)此规则⽤来检查电路⽹络中是否还存在未⾛线的⽹络,系统默认规则是不允许存在未⾛线的⽹络。

4.Un-Connected Pin(不完全连接Pin脚检查规则)此规则⽤来检查电路⽹络中是否存在未连接引脚,此规则⼀般不做设定,系统亦没有默认规则。

5.Modified Polygon(多边形铺铜规则)主要是⽤来防⽌铺铜时,当作出⼤铜⽪套⼩铜⽪的操作时,由于外部更改,重新铺铜后,会容易忽略⼩铜⽪⽽造成粘连。

Unpoured Polygen(未铺铜的多边形)→⑴Allow Shelved(允许隐藏显⽰):属于该规则范围内且当前已搁置的所有多边形将不会被标记违规;⑵Allow Modified(允许修改):属于该规则范围内且当前已修改但尚未铺铜的所有多边形将不会被标记违规;6.Creepage Distance(爬电距离)此规则是⽤来设置两个相邻导体(焊盘)或⼀个导体(焊盘)与相邻电机壳表⾯的沿绝缘层测量的最短距离。

爬电距离是沿绝缘表⾯测得的两个导电零部件之间或导电零部件与设备防护界⾯之间的最短路径。

即在不同的使⽤情况下,由于导体周围的绝缘材料被电极化,导致绝缘材料呈现带电现象。

(百度百科)⼆.Routing(⾛线规则)1.Width(线宽设置)2.Routing Topology(布线拓扑规则)⑴Short(布线最短规则) :在布线时连接所有节点的连线最短规则。

⑵Horizontal(⽔平最短规则):连接所有节点的⽔平连线最短规则。

⑶Vertical(垂直最短规则):连接所有节点的垂直⽅向连线最短规则。

EDABOMHelper电子工程师得力的好帮手

Bill of Materials是一简单而又繁琐的工作,特别是电子厂的Bill of Materials零件繁多,稍有不慎,造成的损失我也不用多说什么了。

哪个人做Bill of Materials多多少少都会让人诟病。

目前的现状是大部分公司内部没有统一的元器件库。

工程师各自建立自己常用的库,这样肯定无法保证每个工程师的元件信息的一致性。

主要表现为:1)器件命名规范不统一2)零器件建立规范不统一3)元器件参数不全.在设计过程中,电子工程师专注于元器件的电气参数。

到了生产采购过程,相关人员关注的又是其他信息,比如元器件厂商,供应商,厂商商型号等。

电路设计完成后输出简易的BOM,无法满足采购或者与ERP系统集成的要求。

需要手工输入以下信息:物料编号(Part Number)、零件说明(Description)、PCB包装(Footprint)、厂商信息(Vendor)…这些信息往往需要电子工程师去查询补全,形成大量的重复而且技术含量不高的工作,影响工作效率。

EDA_BOMHelper软件通过数据库接口链接到数据库中读取与元器件关键信息匹配的记录。

然后把这个元器件相关的其他信息(物料编码(Part Number)、零件说明(Description)、PCB包装(Footprint)、厂商信息(Vendor))等加载到Standard BOM列表中。

接下来就是(Export)导出到符合公司的Bill of Materials格式的模版文件中。

也为导入ERP系统做好了充分的前期准备。

最后还可以验证制作的Bill of Materials与设计文件是否正确。

如何自定义物料标准库?EDA_BOMHelper支持mdb;xls;et,3种格式的物料标准库文件。

Microsoft Office(Excel),Kingsoft Office(WPS),Microsoft Office(Access)。

现在我们来看看物料标准库的庐山真面目…正式数据从第三行开始(这个我相信大家都明白我就多作不解释了)。

eda技术实用教程-veriloghdl答案

eda技术实用教程-veriloghdl答案【篇一:eda技术与vhdl程序开发基础教程课后答案】eda的英文全称是electronic design automation2.eda系统设计自动化eda阶段三个发展阶段3. eda技术的应用可概括为4.目前比较流行的主流厂家的eda软件有、5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有7.逻辑综合后生成的网表文件为 edif8.布局布线主要完成9.10.常用的第三方eda工具软件有synplify/synplify pro、leonardo spectrum1.8.2选择1.eda技术发展历程的正确描述为(a)a cad-cae-edab eda-cad-caec eda-cae-cadd cae-cad-eda2.altera的第四代eda集成开发环境为(c)a modelsimb mux+plus iic quartus iid ise3.下列eda工具中,支持状态图输入方式的是(b)a quartus iib isec ispdesignexpertd syplify pro4.下列几种仿真中考虑了物理模型参数的仿真是(a)a 时序仿真b 功能仿真c 行为仿真d 逻辑仿真5.下列描述eda工程设计流程正确的是(c)a输入-综合-布线-下载-仿真b布线-仿真-下载-输入-综合c输入-综合-布线-仿真-下载d输入-仿真-综合-布线-下载6.下列编程语言中不属于硬件描述语言的是(d)a vhdlb verilogc abeld php1.8.3问答1.结合本章学习的知识,简述什么是eda技术?谈谈自己对eda技术的认识?答:eda(electronic design automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

2.简要介绍eda技术的发展历程?答:现代eda技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

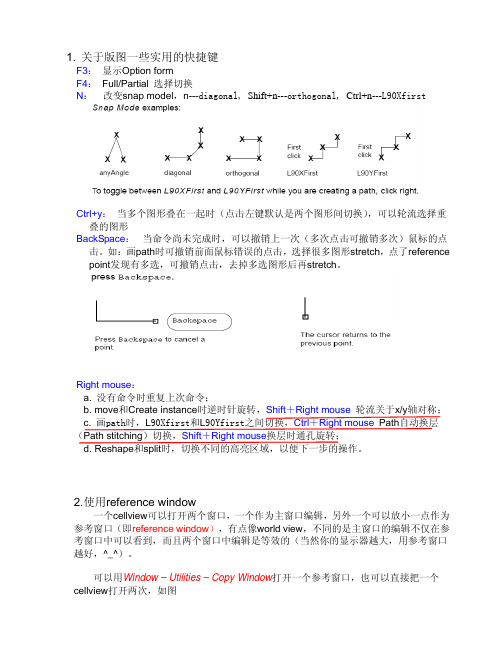

关于Cadence virtuoso Layout Editer的一些实用技巧

Right mouse: a. 没有命令时重复上次命令; b. move和Create instance时逆时针旋转,Shift+Right mouse 轮流关于x/y轴对称; c. 画path时,L90Xfirst和L90Yfirst之间切换,Ctrl+Right mouse Path自动换层

6. 关于Tap的使用

Tap是用来快速捕捉任意一个图形的相关属性,捕捉到的信息会自动赋给将要生成的 Object上包括Layer信息,Net的名字,其它属性(如path的width,endtype等等)

a. 用Tap来快速选择entry Layer

选择Edit – Tap [t],默认的是选择的Layer是边界最接近鼠标指针(或者边界与指针 重合)的图形的Layer,如果两层完全重合,则有一层可能一直也选不中。

②在Change To Layer 栏里选择你要换的layer,也可以通过Control+right mouse 键来选择需要换的层。

ห้องสมุดไป่ตู้

如果Change To Layer栏里没有层可选,那是因为在technology file 中没有关于这层 的contact(或者cdsVia的定义)定义,只有定义了之后才能使用path stitching功能。

因此可以设置环境变量 layerTapCycle为 t or nil, 可以改变捕捉的方法 在CIW敲入命令(只对这个icfb窗口适用): envSetVal("layout" "layerTapCycle" 'boolean t ) 或者在根目录下的.cdsenv文件中加入一行,每次启动icfb就会调用这个环境变量 layout layerTapCycle boolean t 设成 nil 时(默认值)选择的Layer是边界最接近鼠标指针(或者边界与指针重合) 的图形的Layer 设成 t 时,在重复的图形上连续点击,可以依次轮流的选择不同的Layer,直到选 到你想要的为止。

EDA_BOMHelper安装与说明

6.支持Logic(全部重编/选择重编[左上角/左下角方位开始])与Layout元件重新编号。

yout中显示可视工具条。

8.支持Layout PCB输出Bill of Materials。可以在工具中实时批量修改原理图的元件参数,封装,可以根据Bill of Materials反向修改pcb元件参数。可以输出元件用于SMT生产之用的元件中心坐标文件。还可以进行底层坐标镜像参数处理。支持同时导出元件两个以上元件参数(比如说:Value,Part ID,Decal)并且统计BOM。还可以分层(Layer)统计元件,分SMD统计元件,在分层(Layer)的基础上再分SMD统计元件。

30.通过相关设置EDA_BOMHelper支持按设计的电路模块输出Bill of Materials。

31.通过相关设置EDA_BOMHelper支持按设计的PCB板数输出Bill of Materials。

32.支持Logic/Layout/Protel99 /Orcad/P-CAD同值同封装元件连贯无间隔编号。

1MF=1000UF

225=2。2uf

226=22uf

224=0。22uf

105p=1uf

104p=100nf

152=1。5nf

472=4。7nf

103p=10nf

以上的意思是指元件参数(Value)的转换。"="前边的指是需要转换的元件参数,"="后边的指是转换之后的元件参数,这是一一对应的(例如:如果元件的参数等于103p,那么系统自动转换为10nf。)不能有重复项目,如果有只能匹配最末尾的那个。),用户可以不断完善,以达到后续的Bill of Materials在导出后尽量完美,以上只是EDA_BOMHelper默认的。如果需要用到此功能请在设置面板中>>User Setting 2:>>输入V-。

EDA-BOMHelper电子工程师最得力的好帮手

EDA-BOMHelper电子工程师最得力的好帮手BillofMaterial是一简单而又繁琐的工作,特别是电子厂的BillofMaterial零件繁多,稍有不慎,造成的损失我也不用多说什么了。

哪个人做BillofMaterial多多少少都会让人诟病。

目前的现状是大部分公司内部没有统一的元器件库。

工程师各自建立自己常用的库,这样肯定无法保证每个工程师的元件信息的一致性。

主要表现为:1)器件命名规范不统一2)零器件建立规范不统一3)元器件参数不全.在设计过程中,电子工程师专注于元器件的电气参数。

到了生产采购过程,相关人员关注的又是其他信息,比如元器件厂商,供应商,厂商商型号等。

EDA_BOMHelper软件通过数据库接口链接到数据库中读取与元器件关键信息匹配的记录。

然后把这个元器件相关的其他信息(物料编码(PartNumber)、零件说明(Decription)、PCB包装(Footprint)、厂商信息(Vendor))等加载到StandardBOM列表中。

接下来就是(E某port)导出到符合公司的BillofMaterial格式的模版文件中。

也为导入ERP系统做好了充分的前期准备。

最后还可以验证制作的BillofMaterial与设计文件是否正确。

如何自定义物料标准库?EDA_BOMHelper支持mdb;某l;et,3种格式的物料标准库文件。

MicrooftOffice(E某cel),KingoftOffice(WPS),MicrooftOffice(Acce)。

现在我们来看看物料标准库的庐山真面目正式数据从第三行开始(这个我相信大家都明白我就多作不解释了)。

EDA_BOMHelper获取数据以“序号”列为基准EDA_BOMHelper自动识别物料标准库文件中A列最后一个非空单元格行号并以此为基准,获取标准物料数据范围。

E某cel2003版本最大行号是是65536行,2007版本最大行号是1048576行,对于中小企业是肯定够用了。

立创eda操作手册(3篇)

第1篇目录1. 简介2. 系统安装与启动3. 界面介绍4. 基本操作5. 元件库管理6. 布局与布线7. 印制电路板设计8. 生成报表9. 设计文件输出10. 常见问题解答11. 总结1. 简介立创EDA是一款功能强大的电子设计自动化(EDA)软件,适用于电路设计、原理图绘制、PCB设计等领域。

本手册旨在帮助用户快速上手立创EDA,掌握其基本操作和设计流程。

2. 系统安装与启动2.1 系统要求- 操作系统:Windows 7/8/10- 处理器:Intel Core i3 或 AMD Athlon II 或更高- 内存:4GB RAM 或更高- 硬盘空间:1GB 或更高- 显卡:DirectX 9 或更高版本2.2 安装步骤1. 下载立创EDA安装包。

2. 双击安装包,按照提示完成安装。

3. 安装完成后,双击桌面上的立创EDA快捷方式启动软件。

3. 界面介绍立创EDA界面主要由以下部分组成:- 菜单栏:提供各种操作命令。

- 工具栏:提供常用的快捷工具。

- 设计区域:显示电路原理图或PCB布局。

- 元件库:提供各种元件供设计使用。

- 属性栏:显示当前选中元件或图形的属性。

4. 基本操作4.1 新建项目1. 点击“文件”菜单,选择“新建”。

2. 在弹出的对话框中,选择项目类型(原理图或PCB)。

3. 输入项目名称和保存路径,点击“确定”。

4.2 打开项目1. 点击“文件”菜单,选择“打开”。

2. 在弹出的对话框中,选择要打开的项目文件。

3. 点击“打开”按钮。

4.3 保存项目1. 点击“文件”菜单,选择“保存”或“另存为”。

2. 在弹出的对话框中,选择保存路径和文件名。

3. 点击“保存”按钮。

5. 元件库管理5.1 添加元件库1. 点击“元件”菜单,选择“添加元件库”。

2. 在弹出的对话框中,选择要添加的元件库。

3. 点击“确定”。

5.2 搜索元件1. 在元件库中,输入要搜索的元件名称。

2. 按下回车键或点击搜索按钮,搜索结果将显示在元件列表中。

立创eda 铺铜安全规则设置

立创eda 铺铜安全规则设置

在立创EDA中,铺铜安全规则设置主要涉及到电气规则中新建一个关于铺铜的规则(这里命名为ploy),具体步骤如下:

1. 在电气规则中新建一个关于铺铜的规则(这里命名为ploy)。

2. 选择最后一项。

3. 输入InPolygon 即可。

4. 修改具体的安全间距规则即可。

此外,还可以设置焊盘连接方式,在“设计->规则->Plane-

>PolygonConnect”中设置。

有全连接和部分连接两种方式,手焊建议部分连接。

部分连接方式可以设置为直连或发散,发散线宽可以设置,当设置线宽为0时,十字的宽度为系统自动生成的宽度;该线宽不能小于10mil,设置小于10mil时将只生成10mil线宽。

铺铜样式设置在“工具->铺铜管理器->属性”中设置,可以设置的内容包括网络、间距、焊盘连接方式等。

当网络和画布上的元素网络相同时,铺铜才可以和元素连接,并会显示出来,否则铺铜会被认为是孤岛被移除。

铺铜区距离其他同层电气元素的间隙。

当设计规则有间距设置时,铺铜间距会与设计规则比较,取大的值产生间隙。

以上内容仅供参考,建议咨询立创EDA官方客服,以获取最准确的信息。

klayout布尔运算

klayout布尔运算

KLayout是一款开源的EDA工具,提供了强大的布局编辑和分析功能。

其中布尔运算是KLayout中非常重要的一个功能,它可以对不同层次的布局数据进行逻辑计算,包括交集、并集、差集和异或等操作。

以下是关于KLayout布尔运算的一些详细解释:

1. 交集运算:交集运算可以将两个不同层次的布局数据进行相交操作,保留它们相交的部分,并将其它部分删除。

在KLayout中,可以使用交集运算将不同层次的布局数据进行合并,以达到更好的效果。

2. 并集运算:并集运算可以将两个不同层次的布局数据进行合并操作,将它们的所有部分都保留下来。

在KLayout中,可以使用并集运算将不同层次的布局数据进行合并,以便于后续的分析和处理。

3. 差集运算:差集运算可以将两个不同层次的布局数据进行相减操作,保留第一个数据的全部内容,并删除第二个数据中与第一个数据相交的部分。

在KLayout中,可以使用差集运算来删除与当前布局数据不符的一些数据,以达到更好的布局效果。

4. 异或运算:异或运算可以将两个不同层次的布局数据进行异或操作,将它们的不同部分保留下来,删除它们的相同部分。

在KLayout中,可以使用异或运

算将不同层次的布局数据进行合并,并保留它们的不同部分,以达到更好的布局效果。

总之,KLayout布尔运算是一款非常实用的布局编辑和分析工具,可以帮助工程师们更好地进行电路设计和分析。

qflowlayout 用法 -回复

qflowlayout 用法-回复qflowlayout是一个用于Qt框架的布局管理器,用于自动调整子组件的位置和大小,以适应窗口大小的变化。

它在Qt中提供了一种简单而灵活的方式来创建自适应的界面,使开发者能够更加方便地设计以屏幕大小为基准的用户界面。

首先,让我们来了解一下qflowlayout的基本用法。

1. 包含头文件要使用qflowlayout,我们首先需要在代码中包含相应的头文件。

在Qt 中,qflowlayout定义在QFlowLayout类中,因此我们需要添加以下代码:cpp#include <QFlowLayout>2. 创建qflowlayout对象在我们的界面中创建一个布局管理器之前,首先需要实例化一个qflowlayout对象。

这可以通过以下方式完成:cppQFlowLayout* layout = new QFlowLayout();3. 创建和添加子组件接下来,我们需要创建我们想要添加到qflowlayout中的子组件。

这些子组件可以是QWidget的任何派生类,例如QPushButton、QLineEdit 等。

创建子组件后,我们使用以下代码将它们添加到qflowlayout中:cpplayout->addWidget(widget);4. 设置间距和对齐方式qflowlayout允许我们设置子组件之间的间距和对齐方式。

间距可以通过以下代码设置:cpplayout->setSpacing(spacing);其中,spacing是一个整数,表示子组件之间的像素间隔。

默认值是0。

对齐方式可以通过以下代码设置:cpplayout->setAlignment(Qt::Alignment alignment);其中,alignment是Qt中定义的对齐方式之一,可以是Qt::AlignLeft、Qt::AlignRight、Qt::AlignCenter等。

EDA_BOMHelper安装与说明

10.独创在Layout PCB中飞线引导法布局工具,大大加大了PCB元件布局的工作效率。

12.优化Layout PCB导入Logo工具。

13.支持Layout中元件的序号与参数批量居中。支持Logic与Layout元件之间参数的同步,对比。

19.支持从Layout PCB元件重新编号反向同步Orcad文件。

20.支持P-CAD,Orcad输出Bill of Materials,以BOM反向修改PCB中元件参数(封装)。

21.支持由Protel99se/DXP/Altium Designer转换成的PADS文件的元件的参数移植,通常转换出来的元件在PADS中只有Comment参数而没有Value参数,EDA_BOMHelper可以将元件的Comment移植成Value属性。

*********************************************

ComponentModuleZ.txt

Power-/UP/RP/CP/

Audio-/UA/RA/CA/

Video-/UV/RV/CV/

Bluetooth-/UB/RB/CB/

Driver-/UD/RD/CD/

14.可以在EDA_BOMHelper工具中Bill of Materials视窗中实时点击元件时自动连接Logic/Layout在其中查找并缩放元件(Layout中可以设置自动换层单层查看模式),方便查看,特别适合工程技术员手工贴片做样,元件的查找。

15.支持Bill of Materials与Logic,Layout,Protel99se/DXP/Altium Designer,P-CAD,Orcad中元件的对比。(对比分三种颜色,位号-绿色;封装-红色;参数-橙色。)

模拟集成电路反向设计流程简介

如何进行集成电路反向设计?

• 与之相比较的超大规模集成电路(数字电 路)设镜或者专门的看图软件(如上海 圣景微电子公司的ChipsmithLite)

知识产权是一个笼统的称呼,具体到芯片中,其包含的 知识产权主要是布图(Layout)的著作权和专利独享权。在美 国司法实践中,通常认为布图的相同部分超过70%则视为侵 权。

芯片反向工程和软件反向工程的比较

一个经常被混淆的概念是:软件反向工程是违法的,类似的芯片反向工 程也是违法的。

的确,在大多数情况下,软件反向工程是违法的,这是因为大多数软件 的包装盒上都印有版权信息,其中通常都包括了不允许用各种形式对该软件 进行反向工程的条款,购买该软件则意味着接受所有条款。一旦购买软件就 形成了一种契约关系,受合同法保护。因此,对软件进行反向工程就违反了 购买软件时承诺的合同义务。

即使是从网络上下载的共享软件或者免费软件在安装前也会显示一些信息作为安装软件所必须接受的协议条款其中同样包括不允许进行反向工程的内容只有同意所有条款通常是选择accept或agree按钮才能够继续安装

集成电路 反向设计流程简介

什么是反向设计?

反向设计(reverse design)也叫反 向工程(reverse engineering),就是通 过对终端产品的拆卸、破解而得出它 的设计方案或者它的原料配方,以便 于投入大批量生产,这通常被认为是 取得他人商业秘密的一种方法。

• 使用的工具软件:

专用的EDA软件,如Cadence公司DFII 软 件包中的电路仿真器。

• 使用的工具软件:

立创eda设计规则设置

立创eda设计规则设置立创EDA是一种电子设计自动化工具,为电子设计师提供了快速、高效的设计、验证和生产流程。

设计规则设置是立创EDA中的一个重要环节,它决定了设计的可行性、可靠性和制造的可行性。

本文将详细介绍立创EDA设计规则设置的一些基本概念和具体步骤。

设计规则是指在设计电路时,所需要遵循的一系列规定,以满足电路功能和性能要求,并确保电路在制造和生产中能够正常工作。

设计规则设置是指将这些规则应用于电路设计中的过程。

在立创EDA中,设计规则设置包括以下几个方面。

1.尺寸规则设置:包括物理布局的尺寸规则、器件形状与间距的规则等。

在设置尺寸规则时,需要注意电路板的实际制造限制,如最小线宽线距、最小孔径等。

合理设置尺寸规则可以保证电路设计的可行性和可靠性。

2.电性规则设置:包括信号传输线的设计、电源和接地的布局、阻抗匹配等电性特性方面的规则。

合理设置电性规则可以优化电路性能,并减少电磁干扰和信号损耗。

3.材料规则设置:包括板材选择、焊盘尺寸、焊盘间距、焊盘控制等材料特性方面的规则。

在设置材料规则时,需要考虑材料的可靠性和可获得性,以确保电路设计符合制造和生产的要求。

4.DRC(设计规则检查)设置:DRC是立创EDA中的一个功能模块,用于检查设计是否符合所设定的规则。

在进行DRC设置时,需要根据具体的设计要求和制造要求,选择相应的检查规则。

通过合理设置DRC规则,可以提高设计的准确性和可靠性。

5.ERC(电器规则检查)设置:ERC是立创EDA中的另一个功能模块,用于检查设计中的电气问题。

在进行ERC设置时,需要关注电路的连通性、电压和电流的正常传输等电气特性。

通过合理设置ERC规则,可以降低电路设计中出现的电气问题。

基于以上几个方面,下面是立创EDA设计规则设置的一般步骤。

第一步是确定设计要求和制造要求。

在进行设计规则设置之前,首先需要明确设计的目标和要求,如电路的功能、性能、可靠性要求等,以及制造的要求,如最小线宽线距、最小孔径等。

PCB高级软件ProtelDXP应用技巧

PCB高级软件Protel DXP应用技巧将新的PCB添加到项目如果你想添加到项目的PCB是以自由文件打开的,在Projects 面板的Free Documents 单元右击PCB文件,选择Add to Project 。

这个PCB现在就列表在Projects 标签紧靠项目名称的PCBs 下面并连接到项目文件。

转换设计在将原理图信息转换到新的空白PCB之前,确认与原理图和PCB关联的所有库均可用。

由于在本教程中只用到默认安装的集成元件库,所有封装也已经包括在了。

只要项目已经编辑过并且在原理图中的任何错误均已修复,那么使用Update PCB 命令来启动ECO就能将原理图信息转换到目标PCB。

更新PCB将项目中的原理图信息发送到目标PCB:1、在原理图编辑器选择Design > Update PCB ( Multivibrator.PcbDoc ) 。

项目修改,Engineering Change Order 对话框出现。

2、点击Validate Changes 。

如果所有的改变均有效,检查将出现在状态列表中。

如果改变无效,关闭对话框,检查Messages 面板并清除所有错误。

3、点击Execute Changes 将改变发送到PCB。

完成后,状态变为完成(Done )4 、点击Close ,目标PCB打开,而元件也在板子上以准备放置。

如果你在当前视图不能看见元件,使用热键V、D(查看文档)。

设计PCB现在我们可以开始在PCB上放置元件并在板上布线。

设置PCB工作区在将元件定位在板子上之前,我们需要设置PCB工作区,如栅格、层和设计规则。

栅格(Grids )在开始定位元件之前,我们需要确认放置栅格设置正确。

放置在PCB工作区的所有对象均排列在称为捕获栅格(snap grid )上。

这个栅格需要设置得适合我们要使用的布线技术。

我们的教程电路用的是标准英制元件,其最小引脚间距为100mil。

我们将这个捕获栅格设定为100mil 的一个平均分数,50或25mil,这样所有的元件引脚在放置时均将落在栅格点一。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

打开Layout PCB文件,运行本工具生成BOM。

在BOM Report这个工作表中修改封装为R8.5的10K(数量为6个)改为20K

那么总共有33个元件与PCB的值不一样呢!下边操作如何以BOM反向修改Layout PCB 中元件的值。

首先我们要把工作表BOM Report置为当前工作,所以我们要切换过去、

现在可以运行工具了

程序运行完毕,会弹出信息框告诉用户修改了多少元件属性。

可以在PCB中看看是否更改Value属性成功?

R23由本来的10K现在因为BOM修改成20K,所以运行工具后PCB中也与BOM的值一致了!

******************************************************************************* Logic以BOM元件参数反向修改SCH元件参数的操作与Layout类似。

EDA_BOMHelper正式版QQ群:148707037。