KSP05中文资料

5mm圆头蓝光

MIL-STD-202:107D

MIL-STD-705:105E

5min 5min 5min

-35℃~25℃~85℃~-35℃

30min 5min 30min 5min

50Cycles

22

0

型號Model:

六、注意事項Note

(一)引腳成形方法LEDbracket forming method

耗散功率

Power Dissipation

Pm

50

mW

---

工作環境溫度Operation temperature

Tamb

-25至+80

℃

---

貯藏溫度

Storage temperature

Tstg

-35至+85

℃

---

焊接溫度

Solderingtemperature

Tsol

260

℃

波峰焊,離環氧體3mm處≤3S

Finishing the forming ofLEDbracket must be before soldering.

(4)支架成形需保證引腳和間距與線路板上一致。

Guarantee the gap between two pin ofLEDtallyswithLEDpadsin PCBwhen forming.

MIL-STD-750:2031

Ta=85℃±5℃

1000Hrs

22

0

低溫存儲

Low temperature store

JIS7021:B12

Ta=-35℃±5℃

1000Hrs

22

0

高溫高濕測試

High temperature/ humidity test

SMDA05C-4-2中文资料

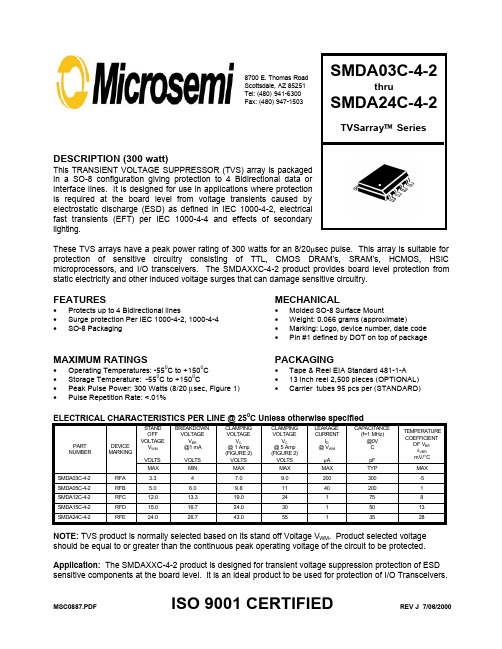

8700 E. Thomas Road Scottsdale, AZ 85251Tel: (480) 941-6300Fax: (480) 947-1503DESCRIPTION (300 watt)This TRANSIENT VOLTAGE SUPPRESSOR (TVS) array is packaged in a SO-8 configuration giving protection to 4 Bidirectional data or interface lines. It is designed for use in applications where protection is required at the board level from voltage transients caused by electrostatic discharge (ESD) as defined in IEC 1000-4-2, electrical fast transients (EFT) per IEC 1000-4-4 and effects of secondary lighting.These TVS arrays have a peak power rating of 300 watts for an 8/20µsec pulse. This array is suitable for protection of sensitive circuitry consisting of TTL, CMOS DRAM’s, SRAM’s, HCMOS, HSIC microprocessors, and I/O transceivers. The SMDAXXC-4-2 product provides board level protection from static electricity and other induced voltage surges that can damage sensitive circuitry.FEATURESMECHANICAL• Protects up to 4 Bidirectional lines•Molded SO-8 Surface Mount• Surge protection Per IEC 1000-4-2, 1000-4-4•Weight: 0.066 grams (approximate)•SO-8 Packaging•Marking: Logo, device number, date code •Pin #1 defined by DOT on top of packageMAXIMUM RATINGSPACKAGING• Operating Temperatures: -550C to +1500C •Tape & Reel EIA Standard 481-1-A • Storage Temperature: -550C to +1500C•13 inch reel 2,500 pieces (OPTIONAL)• Peak Pulse Power: 300 Watts (8/20 µsec, Figure 1)•Carrier tubes 95 pcs per (STANDARD)•Pulse Repetition Rate: <.01%ELECTRICAL CHARACTERISTICS PER LINE @ 250C Unless otherwise specifiedSTAND OFF VOLTAGE V WM VOLTS BREAKDOWN VOLTAGE V BR @1 mAVOLTS CLAMPING VOLTAGEV C@ 1 Amp (FIGURE 2)VOLTS CLAMPING VOLTAGEV C@ 5 Amp (FIGURE 2)VOLTS LEAKAGE CURRENTI D @ V WMµA CAPACITANCE (f=1 MHz)@0V CpF TEMPERATURE COEFFICIENTOF V BR áVBR mV/°CPART NUMBERDEVICE MARKINGMAXMIN MAXMAXMAX TYP MAX SMDA03C-4-2RFA 3.347.09.0200300-5SMDA05C-4-2RFB 5.0 6.09.811402001SMDA12C-4-2RFC 12.013.319.0241758SMDA15C-4-2RFD 15.016.724.03015013SMDA24C-4-2RFE24.026.743.05513528NOTE: TVS product is normally selected based on its stand off Voltage V WM . Product selected voltage should be equal to or greater than the continuous peak operating voltage of the circuit to be protected.Application: The SMDAXXC-4-2 product is designed for transient voltage suppression protection of ESD sensitive components at the board level. It is an ideal product to be used for protection of I/O Transceivers.SMDA03C-4-2 thru SMDA24C-4-2 WAVE FORMSPeak Pulse Power Vs Pulse Time Pulse Wave FormpINCHES MILLIMETERSMINMIN MAXMAX0.188 4.77 5.000.1970.150 3.81 4.010.1580.053 1.35 1.750.0690.0210.0110.280.530.0160.41 1.270.050。

ksp——精选推荐

ksp溶度积表化合物化学式温度K sp来源⽆⽔氢氧化铝Al(OH)320°C 1.9×10–33L⽆⽔氢氧化铝Al(OH)325°C 3×10–34w1三⽔合氢氧化Al(OH)320°C 4×10–13 C铝三⽔合氧化铝Al(OH)325°C 3.7×10–13 C 磷酸铝AlPO425°C 9.84×10–21w1溴酸钡Ba(BrO3)225°C 2.43×10–4w1碳酸钡BaCO316°C 7×10–9C, L 碳酸钡BaCO325°C 8.1×10–9C, L 铬酸钡BaCrO428°C 2.4×10–10C, L 氟化钡BaF225.8°C1.73×10–6C, L ⼆⽔合碘酸钡Ba(IO3)225°C 6.5×10–10C, L ⼆⽔合草酸钡BaC2O418°C 1.2×10–7C, L 硫酸钡BaSO418°C 0.87×10–10C, L 硫酸钡BaSO425°C 1.08×10–10C, L 硫酸钡BaSO450°C 1.98×10–10C, L 氢氧化铍Be(OH)225°C 6.92×10–22w1碳酸镉CdCO325°C 1.0×10–12w1氢氧化镉Cd(OH)225°C 7.2×10–15w1三⽔合草酸镉CdC2O418°C 1.53×10–8C, L 磷酸镉Cd3(PO4)2 25°C2.53×10–33w1硫化镉CdS 18°C3.6×10–29C, L碳酸钙(⽅解CaCO315°C 0.99×10–8C, L ⽯)碳酸钙(⽅解CaCO325°C 0.87×10–8C, L ⽯)碳酸钙(⽅解CaCO318-25°C 4.8×10–9P ⽯)铬酸钙CaCrO418°C 2.3×10–2L氟化钙CaF218°C 3.4×10–11C, L 氟化钙CaF225°C 3.95×10–11C, L 氢氧化钙Ca(OH)218°C-25°C 8×10–6P氢氧化钙Ca(OH)225°C 5.02×10–6w1六⽔合碘酸钙Ca(IO3)218°C 6.44×10–7L⼀⽔合草酸钙CaC2O4 18°C 1.78×10–9C, L ⼀⽔合草酸钙CaC2O4 25°C 2.57×10–9C, L 磷酸钙Ca3(PO4)225°C 2.07×10–33w1硫酸钙CaSO410°C 6.1×10–5C, L 硫酸钙CaSO425°C 4.93×10–5w1⼆⽔合酒⽯酸CaC4H4O618°C 7.7×10–7C, L 钙氢氧化亚铬Cr(OH)225°C 2×10–16w2氢氧化铬Cr(OH)325°C 6.3×10–31w2氢氧化钴Co(OH)225°C 1.6×10–15w2硫化钴CoS 18°C 3×10–26C, L 硫化钴CoS 18°C-25°C 10–21P碳酸铜CuCO325°C 1×10–10P氢氧化铜Cu(OH)218°C-25°C 6×10–20P氢氧化铜Cu(OH)225°C 4.8×10–20w1碘酸铜Cu(IO3)225°C 1.4×10–7C, L 草酸铜CuC2O425°C 2.87×10–8C, L 硫化铜CuS 18°C 8.5×10–45C, L 溴化亚铜CuBr 18°C-20°C 4.15×10–8 C氯化亚铜CuCl 18°C-20°C 1.02×10–6 C氢氧化亚铜Cu(OH) 25°C 2×10–15w1(与氧化亚铜平衡)碘化亚铜CuI 18°C-20°C 5.06×10–12 C硫化亚铜Cu2S 16°C-18°C 2×10–47C, L 硫氰化亚铜CuSCN 18°C 1.64×10–11C, L 氢氧化铁Fe(OH)318°C 1.1×10–36C, L 碳酸亚铁FeCO318°C-25°C 2×10–11P氢氧化亚铁Fe(OH)218°C 1.64×10–14C, L 氢氧化亚铁Fe(OH)225°C 1×10–15; 8.0×10–16P; w2草酸亚铁FeC2O425°C 2.1×10–7C, L 硫化亚铁FeS 18°C 3.7×10–19C, L溴化铅PbBr225°C 6.3×10–6; 6.60×10–6 P; w1碳酸铅PbCO318°C 3.3×10–14C, L 铬酸铅PbCrO418°C 1.77×10–14C, L 氯化铅PbCl225.2°C 1.0×10–4L氯化铅PbCl218°C-25°C 1.7×10–5P氟化铅PbF218°C 3.2×10–8C, L 氟化铅PbF226.6°C 3.7×10–8C, L 氢氧化铅Pb(OH)225°C 1×10–16; 1.43×10–20P; w1碘酸铅Pb(IO3)218°C 1.2×10–13C, L 碘酸铅Pb(IO3)225.8°C 2.6×10–13C, L 碘化铅PbI215°C 7.47×10–9 C碘化铅PbI225°C 1.39×10–8 C草酸铅PbC2O418°C 2.74×10–11C, L 硫酸铅PbSO418°C 1.6×10–8C, L 硫化铅PbS 18°C 3.4×10–28C, L 碳酸锂Li2CO325°C 1.7×10–3C, L 氟化锂LiF 25°C 1.84×10–3w1磷酸锂Li3PO425° 2.37×10–4w1磷酸铵镁MgNH4PO425°C 2.5×10–13C, L 碳酸镁MgCO312°C 2.6×10–5C, L 氟化镁MgF218°C 7.1×10–9C, L 氟化镁MgF225°C 6.4×10–9C, L 氢氧化镁Mg(OH)218°C 1.2×10–11C, L 草酸镁MgC2O4 18°C 8.57×10–5C, L 碳酸锰MnCO318°C-25°C 9×10–11P氢氧化锰Mn(OH)218°C 4×10–14C, L 硫化锰(粉⾊)MnS 18°C 1.4×10–15C, L 硫化锰(绿⾊)MnS 25°C 10–22P溴化汞HgBr225°C 8×10–20L氯化汞HgCl225°C 2.6×10–15L氢氧化汞Hg(OH)225°C 3.6×10–26w1(与氧化汞平衡)碘化汞HgI225°C 3.2×10–29L硫化汞HgS 18°C 4×10–53 to 2×10–49C, L 溴化亚汞HgBr 25°C 1.3×10–21C, L 氯化亚汞Hg2Cl225°C 2×10–18C, L 碘化亚汞HgI 25°C 1.2×10–28C, L 硫酸亚汞Hg2SO425°C 6×10–7; 6.5×10–7P; w1氢氧化镍Ni(OH)225°C 5.48×10–16w1硫化镍NiS 18°C 1.4×10–24C, L 硫化镍NiS 18°C-25°C 10–27P硫化镍NiS 18°C-25°C 10–21P酒⽯酸钾KHC4H4O618°C 3.8×10–4C, L ⾼氯酸钾KClO425°C 1.05×10–2w1⾼碘酸钾KIO425° 3.71×10–4w1⼄酸银AgC2H3O216°C 1.82×10–3L溴酸银AgBrO320°C 3.97×10–5C, L 溴酸银AgBrO325°C 5.77×10–5C, L 溴化银AgBr 18°C 4.1×10–13C, L 溴化银AgBr 25°C 7.7×10–13C, L 碳酸银Ag2CO325°C 6.15×10–12C, L 氯化银AgCl 4.7°C 0.21×10–10C, L 氯化银AgCl 9.7°C0.37×10–10L氯化银AgCl 25°C 1.56×10–10C, L 氯化银AgCl 50°C 13.2×10–10C, L 氯化银AgCl 100°C 21.5×10–10C, L 铬酸银Ag2CrO414.8°C 1.2×10–12C, L 铬酸银Ag2CrO425°C 9×10–12C, L 氰化银Ag2(CN)220°C 2.2×10–12C, L 重铬酸银Ag2Cr2O725°C 2×10–7L氢氧化银AgOH 20°C 1.52×10–8C, L 碘酸银AgIO39.4°C 0.92×10–8C, L 碘化银AgI 13°C 0.32×10–16C, L 碘化银AgI 25°C 1.5×10–16C, L 亚硝酸银AgNO225°C 5.86×10–4L草酸银Ag2C2O425°C 1.3×10–11L硫酸银Ag2SO418°C-25°C 1.2×10–5P硫化银Ag2S 18°C 1.6×10–49C, L 硫氰化银AgSCN 18°C 0.49×10–12C, L 硫氰化银AgSCN 25°C 1.16×10–12C, L 碳酸锶SrCO325°C 1.6×10–9C, L 铬酸锶SrCrO418°C-25°C 3.6×10–5P氟化锶SrF218°C 2.8×10–9C, L 草酸锶SrC2O418°C 5.61×10–8C, L 硫酸锶SrSO4 2.9°C 2.77×10–7C, L 硫酸锶SrSO417.4°C 2.81×10–7C, L 溴化铊TlBr 25°C 4×10–6L氯化铊TlCl 25°C 2.65×10–4L硫酸铊Tl2SO425°C 3.6×10–4L硫氰化铊TlSCN 25°C; 2.25×10–4L氢氧化锡Sn(OH)218°C-25°C 1×10–26P氢氧化锡Sn(OH)225°C 5.45×10–27;1.4×10–28w1;w2硫化锡SnS 25°C 10–28P氢氧化锌Zn(OH)218°C-20°C 1.8×10–14C, L ⼆⽔合草酸锌ZnC2O418°C 1.35×10–9C, L 硫化锌ZnS 18°C 1.2×10–23C, L 参考资料:L=Lange's 10th ed.; C=CRC 44th ed.; P=General Chemistry by Pauling, 1970 ed.; w1=⽹络来源1; w2=⽹络来源2。

MPC2005中文资料

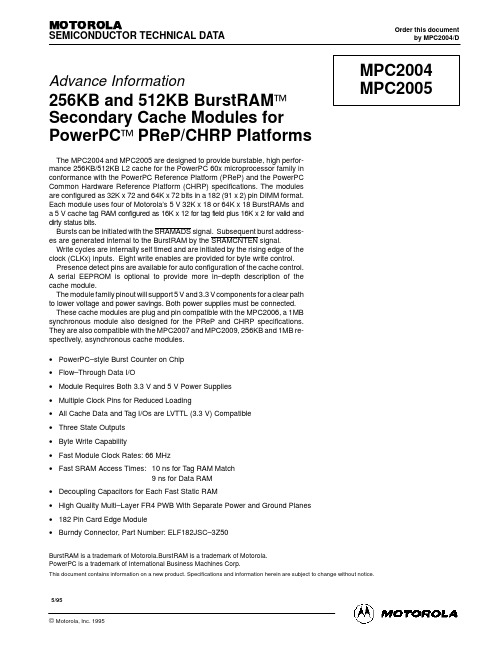

MPC2004•MPC20056–1Advance Information256KB and 512KB BurstRAM ™Secondary Cache Modules for PowerPC ™ PReP/CHRP PlatformsThe MPC2004 and MPC2005 are designed to provide burstable, high perfor-mance 256KB/512KB L2 cache for the PowerPC 60x microprocessor family in conformance with the PowerPC Reference Platform (PReP) and the PowerPC Common Hardware Reference Platform (CHRP) specifications. The modules are configured as 32K x 72 and 64K x 72 bits in a 182 (91 x 2) pin DIMM format.Each module uses four of Motorola’s 5 V 32K x 18 or 64K x 18 BurstRAMs and a 5 V cache tag RAM configured as 16K x 12 for tag field plus 16K x 2 for valid and dirty status bits.es are generated internal to the BurstRAM by the SRAMCNTEN signal.Write cycles are internally self timed and are initiated by the rising edge of the clock (CLKx) inputs. Eight write enables are provided for byte write control.Presence detect pins are available for auto configuration of the cache control.A serial EEPROM is optional to provide more in–depth description of the cache module.The module family pinout will support 5 V and 3.3 V components for a clear path to lower voltage and power savings. Both power supplies must be connected.These cache modules are plug and pin compatible with the MPC2006, a 1MB synchronous module also designed for the PReP and CHRP specifications.They are also compatible with the MPC2007 and MPC2009, 256KB and 1MB re-spectively, asynchronous cache modules.•PowerPC–style Burst Counter on Chip •Flow–Through Data I/O•Module Requires Both 3.3 V and 5 V Power Supplies •Multiple Clock Pins for Reduced Loading•All Cache Data and T ag I/Os are LVTTL (3.3 V) Compatible •Three State Outputs •Byte Write Capability•Fast Module Clock Rates: 66 MHz•Fast SRAM Access Times: 10 ns for Tag RAM Match9 ns for Data RAM •Decoupling Capacitors for Each Fast Static RAM•High Quality Multi–Layer FR4 PWB With Separate Power and Ground Planes •182 Pin Card Edge Module•Burndy Connector, Part Number: ELF182JSC–3Z50BurstRAM is a trademark of Motorola.BurstRAM is a trademark of Motorola.PowerPC is a trademark of International Business Machines Corp.This document contains information on a new product. Specifications and information herein are subject to change without notice.Order this documentby MPC2004/DMOTOROLASEMICONDUCTOR TECHNICAL DATAMPC2004MPC2005associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and。

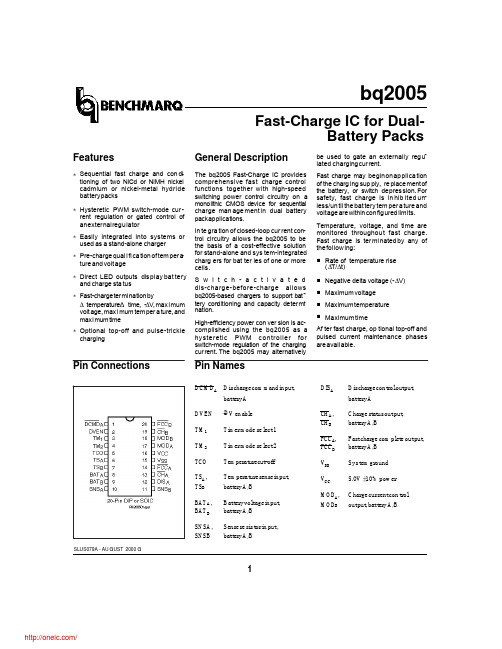

BQ2005S;BQ2005STRG4;BQ2005SG4;中文规格书,Datasheet资料

Features∗Se q uen t ial fast charge and con di -tion i ng of two NiCd or NiMH nickel cad m ium or nickel-metal hy d ride bat t ery p acks∗Hysteretic PWM switch-mode cur -rent reg u l a t ion or gated con t rol of an e x t er n al r eg u l a t or∗Easily in t e g rated into sys t ems or used as a stand-alone charger∗Pre-charge qual i fi ca tion of tem per a -ture a nd v olt a ge∗Di r ect LED out p uts dis play bat tery and charge sta tus∗Fast-charge t er m i n a t ion b y∆ tem p er a t ure/∆ time, -∆V, max i mum volt age, max i mum tem per a ture, and max i mum time∗Op t ional top-off and pulse-trickle charg i ng General DescriptionThe bq2005 Fast-Charge IC pro v idescom p re h en s ive fast charge con t rolfunc t ions to g ether with high-speedswitch i ng power con t rol cir c uitry on amono l ithic CMOS de v ice for se q uen t ialcharge man age ment in dual bat t erypack a p p li c a t ions.In te gra tion of closed-loop cur rent con -trol cir c uitry al l ows the bq2005 to bethe ba s is of a cost-effective so l u t ionfor stand-alone and sys tem-integratedcharg ers for bat ter ies of one or morecells.S w i t c h-a c t i v a t e ddis-charge-before-charge al l owsbq2005-based charg e rs to sup p ort bat -tery con ditioning and ca p ac i ty de t er m i -na t ion.High-efficiency power con ver sion is ac -com p lished us i ng the bq2005 as ahysteretic PWM con t rol l er forswitch-mode reg u l a t ion of the charg i ngcur rent. The bq2005 may al t er n a t ivelybe used to gate an ex t er n ally reg u -lated charging cur rent.Fast charge may be gin on ap pli ca tionof the charg ing sup ply, re place ment ofthe bat t ery, or switch de pres sion. Forsafety, fast charge is in hib ited un -less/un til the bat tery tem per a ture andvolt age are within con fig ured lim its.Tem p er a t ure, volt a ge, and time aremon i t ored through o ut fast charge.Fast charge is ter mi nated by any ofthe f ol l ow i ng:n Rate of temperature rise(∆T/∆t)n Negative delta voltage (-∆V)n Maximum v oltagen Maximum t emperaturen Maximum t imeAf ter fast charge, op tional top-off andpulsed cur r ent main t e n ance phasesare a vail a ble.1Fast- C harge IC for Dual-Bat tery Packsbq2005 Pin Connections Pin NamesSLUS079A - AU GUST 2000 G DCMD A Dis charge com mand in put,bat t ery ADVEN-D V en ableTM1Timer mode se lect 1TM2Timer mode se lect 2TCO Tem p era t ure c ut- o ffTS A,Tem pera ture sense in put, TS B bat t ery A/BBAT A, Bat t ery v olt a ge i n p ut, BAT B bat t ery A/BSNSA,Sense re sis tor in put , SNSB bat t ery A/B DIS A Dis charge con trol out put,bat t ery AC H A,Charge status out put,C H B bat t ery A/BFCC A,Fast charge com plete out put, FCC B bat t ery A/BV SS Sys tem groundV CC 5.0V ±10% powerMOD A,Charge cur rent con trol MOD B out put, bat tery A/BPin DescriptionsDCMD A Discharge-before-charge control input, battery ADCMD A controls the discharge-before-chargefunction of the bq2005.A negative-goingpulse on DCMD A initiates a discharge toEDV followed by a charge if conditions allow.By tying A to ground,automaticdischarge-before-charge is enabled on everynew charge cycle start.DVEN-∆V enable inputThis input enables/disables-∆V charge termi-nation.If DVEN is high,the-∆V test is en-abled.If DVEN is low,-∆V test is disabled.The state of DVEN may be changed at anytime.TM1–TM2Timer mode inputsTM1and TM2are three-state inputs that con-figure the fast charge safety timer,-∆V hold-off time,and that enhance/disable top-off.See Table2.TCO T emperature cutoff threshold inputInput to set maximum allowable batterytemperature.If the potential between TS Aand SNS A or TSB and SNS B is less than thevoltage at the TCO input,then fast charge ortop-off charge is terminated for the corre-sponding battery pack.TS A,TS BT emperature sense inputsInput,referenced to SNS A or SNS B,respec-tively,for an external thermistor monitoringbattery temperature.BAT A,BAT BV oltage inputsThe battery voltage sense input,referenced toSNS A,B,respectively.This is created by ahigh-impedance resistor divider network con-nected between the positive and the negativeterminals of the battery.SNS A,SNS BCharging current sense inputs,SNS A,B controls the switching of MOD A,Bbased on the voltage across an externalsense resistor in the current path of the bat-tery.SNS is the reference potential for theTS and BAT pins.If SNS is connected toV SS,MOD switches high at the beginning ofcharge and low at the end of charge.DIS A Discharge control outputPush-pull output used to control an externaltransistor to discharge battery A beforecharging.CH A,CH BCharge status outputsPush-pull outputs indicating charging statusfor batteries A and B,respectively.See Fig-ure1and Table2.FCC A,FCC BFast charge complete outputsOpen-drain outputs indicating fast chargecomplete for batteries A and B,respectively.See Figure1and Table2.MOD A,MOD BCharge current control outputsMOD A,B is a push-pull output that is used tocontrol the charging current to the battery.MOD A,B switches high to enable chargingcurrent to flow and low to inhibit chargingc u r r e n t flow to b a t t e r i e s A a nd B,respectively.V CC V CC supply input5.0V,±10%power input.Vss Ground2bq2005Functional DescriptionFigure3shows a block diagram and Figure4shows a state diagram of the bq2005.Battery Voltage and Temperature MeasurementsBattery voltage and temperature are monitored for maxi-mum allowable values.The voltage presented on the bat-tery sense input,BA T A,B,must be divided down to be-tween0.95∗V CC and0.475∗V CC for proper operation.A resistor-divider ratio of:RB1 RB2N2.375=−1is recommended to maintain the battery voltage within the valid range,where N is the number of cells,RB1is the resistor connected to the positive battery terminal, and RB2is the resistor connected to the negative bat-tery terminal.See Figure1.Note:This resistor-divider network input impedance to end-to-end should be at least200kΩand less than1MΩ.A ground-referenced negative temperature coefficient ther-mistor placed in proximity to the battery may be used as a low-cost temperature-to-voltage transducer.The tempera-ture sense voltage input at TS A,B is developed using a resistor-thermistor network between V CC and V SS.See Figure1.Both the BA T A,B and TS A,B inputs are refer-enced to SNS A,B,so the signals used inside the IC are:V BA T(A,B)-V SNS(A,B)=V CELL(A,B)andV TS(A,B)-V SNS(A,B)=V TEMP(A,B)Discharge-Before-ChargeThe DCMD A input is used to command discharge-before-charge via the DIS A output.Once activated, DIS A becomes active(high)until V CELL falls below V EDV where:V EDV=0.475∗V CC±30mVat which time DIS A goes low and a new fast charge cycle begins.The DCMD A input is internally pulled up to V CC(its in-active state).Leaving the input unconnected,therefore, results in disabling discharge-before-charge.A negative going pulse on DCMD A initiates discharge-before-charge at any time regardless of the current state of the bq2005.If DCMD A is tied to V SS,discharge-before-charge will be the first step in all newly started charge cycles.Starting A Charge CycleAnew charge cycle is started by(see Figure2):1.V CC rising above4.5V2.V CELL falling through the maximum cell voltage,V MCV where:V MCV=0.95∗V CC±30mVIf DCMD A is tied low,a discharge-before-charge will be executed as the first step of the new charge cycle.Oth-erwise,pre-charge qualification testing will be the first step.The battery must be within the configured temperature and voltage limits before fast charging begins.3bq2005Figure1.Voltage and Temperature MonitoringThe valid battery voltage range is V EDV<V BA T<V MCV. The valid temperature range is V HTF<V TEMP<V LTF, where:V LTF=0.4∗V CC±30mVV HTF=[(1/4∗V LTF)+(3/4∗V TCO)]±30mVV TCO is the voltage presented at the TCO input pin,and is configured by the user with a resistor divider between V CC and ground.The allowed range is0.2to0.4∗V CC.If the temperature of the battery is out of range,or the voltage is too low,the chip enters the charge pending state and waits for both conditions to fall within their al-lowed limits.The MOD A,B output is modulated to pro-vide the configured trickle charge rate in the charge pending state.There is no time limit on the chargepending state;the charger remains in this state as long as the voltage or temperature conditions are outside of the allowed limits.If the voltage is too high,the chip goes to the battery absent state and waits until a new charge cycle is started.Fast charge continues until termination by one or more of the five possible termination conditions:Delta temperature/delta time(∆T/∆t)Negative delta voltage(-∆V)Maximum voltageMaximum temperatureMaximum time4bq2005Figure2.Charge Cycle Phases-V TerminationIf the DVEN input is high,the bq2005samples the volt-age at the BAT pin once every 34s.If V CELL is lower than any previously measured value by 12mV ±4mV ,fast charge is terminated.The -∆V test is valid in the range V MCV -(0.2∗V CC )<V CELL <V MCV .Voltage SamplingEach sample is an average of 16voltage measurements t a k e n 57µs a p a r t.The resulting sample period (18.18ms)filters out harmonics around 55Hz.This tech-nique minimizes the effect of any AC line ripple that may feed through the power supply from either 50Hz or 60Hz AC sources.Tolerance on all timing is ±16%.Voltage Termination Hold-offA hold-off period occurs at the start of fast charging.During the hold-off period,-∆V termination is disabled.This avoids premature termination on the voltage spikes sometimes produced by older batteries when fast-charge current is first applied.∆T/∆t,maximum voltage and maximum temperature terminations are not affected by the hold-off period.T/t TerminationThe bq2005samples at the voltage at the TS pin every 34s,and compares it to the value measured two samples earlier.If V TEMP has fallen 16mV ±4mV or more,fast charge is terminated.The ∆T/∆t termination test is valid only when V TCO <V TEMP <V LTF .Temperature SamplingEach sample is an average of 16voltage measurements taken 57µs a p a r t.The resulting sample period (18.18ms)filters out harmonics around 55Hz.This tech-nique minimizes the effect of any AC line ripple that may feed through the power supply from either 50Hz or 60Hz AC sources.Tolerance on all timing is ±16%.Maximum Voltage,Temperature,and TimeAnytime V CELL rises above V MCV ,CHG goes high (the LED goes off)immediately .If the bq2005is not in the voltage hold-off period,fast charging also ceases immediately .If V CELL then falls back below V MCV before t MCV =1s (maximum),the chip transitions to the Charge Complete state (maximum voltage termination).If V CELL remains above V MCV at the expiration of t MCV ,the bq2005transi-tions to the Battery Absent state (battery removal).See Figure 4.Maximum temperature termination occurs anytime the voltage on the TS pin falls below the temperature cut-off threshold V TCO.Charge will also be terminated if V TEMP rises above the minimum temperature fault threshold,V LTF,after fast charge begins.Maximum charge time is configured using the TM pin.Time settings are available for corresponding charge rates of C/4,C/2,1C,and 2C.Maximum time-out termi-nation is enforced on the fast-charge phase,then reset,and enforced again on the top-off phase,if selected.There is no time limit on the trickle-charge phase.Top-off ChargeAn optional top-off charge phase may be selected to follow fast charge termination for the C/2through 4C rates.This phase may be necessary on NiMH or other5Corresponding Fast-Charge RateTM1TM2Typical Fast-Chargeand Top-Off Time LimitsTypical -∆V/MCVHold-Off Time (seconds)Top-Off Rate C/4Low Low 360137Disabled C/2Float Low 180820Disabled 1C High Low 90410Disabled 2C Low Float 45200Disabled 4C Float Float 23100Disabled C/2High Float 180820C/161C Low High 90410C/82C Float High 45200C/44C HighHigh23100C/2Note:Typical conditions =25°C,V CC =5.0V .Table 1.Fast Charge Safety Time/Hold-Off/Top-Off Tablebq2005battery chemistries that have a tendency to terminate charge prior to reaching full capacity.With top-off en-abled,charging continues at a r educed r ate after fast-charge termination for a period of time selected by the TM1and TM2input pins.(See Table2.)During top-off,the CC pin is modulated at a duty cycle of4s active for every30s inactive.This modulation results in an average rate1/8th that of the fast charge rate. Maximum voltage,time,and temperature are the only termination methods enabled during top-off.Pulse-Trickle ChargePulse-trickle charging follows the fast charge and op-tional top-off charge phases to compensate for self-discharge of the battery while it is idle in the charger. The configured pulse-trickle rate is also applied in the charge pending state to raise the voltage of an over-discharged battery up to the minimum required before fast charge can begin.In the pulse-trickle mode,MOD is active for260µs of a period specified by the settings of TM1and TM2.See Ta-ble1.The resulting trickle-charge rate is C/64when top-off is enabled and C/32when top-off is disabled. Both pulse trickle and top-off may be disabled by tying TM1and TM2to V SS.Charge Status IndicationCharge status is indicated by the CHG output.The state of the CHG output in the various charge cycle phases is shown in Figure4and illustrated in Figure2. Temperature status is indicated by the TEMP output. TEMP is in the high state whenever V TEMP is within the temperature window defined by the V LTF and V HTF tem-perature limits,and is low when the battery tempera-ture is outside these limits.In all cases,if V CELL exceeds the voltage at the MCV pin,both CHG and TEMP outputs are held high regard-less of other conditions.CHG and TEMP may both be used to directly drive an LED.Pack SequencingIf both batteries A and B are present when a new charge cycle is started,the charge cycle starts on battery B and B remains the active channel until fast charge termina-tion.Then battery A will be fast charged,followed by a top-off phase on B(if selected),a top-off phase on A(ifselected),and then maintenance charging on both.If only battery A is present,the charge cycle begins on A and continues until fast charge termination even if a battery is inserted in channel B in the meantime.A new battery insertion in channel B while A is in the top-off phase terminates top-off on A and begins a new charge cycle on B.If A is configured for or commanded to discharge-before-charge,the discharge may take place while channel B is the active charging channel.When the discharge is complete,if B is still the active channel battery A enters the Charge Pending state untilA becomes the active channel.Charge Current ControlThe bq2005controls charge current through the MOD A,B out-put pin.The current control circuitry is designed to sup-port implementation of a constant-current switching regu-lator or to gate an externally regulated current source.When used in switch mode configuration,the nominal regulated current is:I REG=0.225V/R SNSCharge current is monitored at the SNS A,B input by the voltage drop across a sense resistor,R SNS,between the low side of the battery pack and ground.R SNS is sized to provide the desired fast charge current.If the voltage at the SNS A,B pin is less than V SNSLO,the MOD A,B output is switched high to pass charge current to the battery.When the SNS A,B voltage is greater than V SNSHI,the MOD A,B output is switched low—shutting off charging current to the battery.V SNSLO=0.04∗V CC±25mVV SNSHI=0.05∗V CC±25mVWhen used to gate an externally regulated current source,the SNS A,B pin is connected to V SS,and no sense resistor is required.6bq2005bq2005Figure3.Block Diagram7bq2005Figure4.State Diagram8Absolute Maximum RatingsSymbol Parameter Minimum Maximum Unit NotesV CC V CC relative to V SS-0.3+7.0VV T DC voltage applied on any pin ex-cluding V CC relative to V SS-0.3+7.0VT OPR Operating ambient temperature-20+70°C CommercialT STG Storage temperature-55+125°CT SOLDER Soldering temperature-+260°C10s max.T BIAS Temperature under bias-40+85°CNote:Permanent device damage may occur if Absolute Maximum Ratings are exceeded.Functional opera-tion should be limited to the Recommended DC Operating Conditions detailed in this data sheet.Expo-sure to conditions beyond the operational limits for extended periods of time may affect device reliability. DC Thresholds(T A=T OPR;V CC±10%)Symbol Parameter Rating Tolerance Unit NotesV SNSHI High threshold at SNS A,Bresulting in MOD A,B=Low0.05*V CC±0.025VV SNSLO Low threshold at SNS A,B re-sulting in MOD A,B=High0.04*V CC±0.010VV LTF Low-temperature fault0.4*V CC±0.030V V TEMP≥V LTF inhibits/terminates chargeV HTF High-temperature fault(1/4*V LTF)+(3/4*V TCO)±0.030V V TEMP≤V HTF inhibitschargeV EDV End-of-discharge voltage0.475*V CC±0.030V V CELL<V EDV inhibitsfast chargeV MCV Maximum cell voltage0.95*V CC±0.030V V CELL>V MCV inhibits/terminates chargeV THERM TS input change for∆T/∆tdetection16±4mV-∆V BAT input change for-∆Vdetection12±4mVbq20059Recommended DC Operating Conditions(T A=0to+70°C)Symbol Parameter Minimum Typical Maximum Unit Notes V CC Supply voltage 4.5 5.0 5.5VV CELL BAT voltage potential0-V CC V V BA T-V SNSV BA T Battery input0-V CC VV TEMP TS voltage potential0-V CC V V TS-V SNSV TS Thermistor input0-V CC VV TCO Temperature cutoff0.2*V CC-0.4*V CC VV IH Logic input high 2.0--V DCMD A,DVEN Logic input high V CC-0.3--V TM1,TM2V IL Logic input low--0.8V DCMD A,DVEN Logic input low--0.3V TM1,TM2V OH Logic output high V CC-0.5--V DIS A,MOD A,B,I OH≤-5mA V OL Logic output low--0.5V DIS A,FCC A,B,CH A,B,MOD A,B,I OL≤5mAI CC Supply current- 1.0 3.0mA Outputs unloadedI OH DIS A,MOD A,B source-5.0--mA@V OH=V CC-0.5VI OL DIS A,FCC A,B,MOD A,B,CH A,B sink5.0--mA@V OL=V SS+0.5VI L Input leakage --±1µA DVEN,V=V SS to V CC ---400µA DCMD A,V=V SSI IL Logic input low source--70.0µA TM1,TM2,V=V SS to V SS+0.3VI IH Logic input high source-70.0--µA TM1,TM2,V=V CC-0.3V to V CCI IZ TM1,TM2tri-state opendetection -2.0- 2.0µATM1,TM2should be left dis-connected(floating)for Z logicinput state.I BA T Input current to BAT A,Bwhen battery is removed ---20µAV CC=5.0V;T A=25°C;inputshould be limited to this cur-rent when input exceeds V CC.Note:All voltages relative to V SS,except as noted. bq200510分销商库存信息:TIBQ2005S BQ2005STRG4BQ2005SG4。

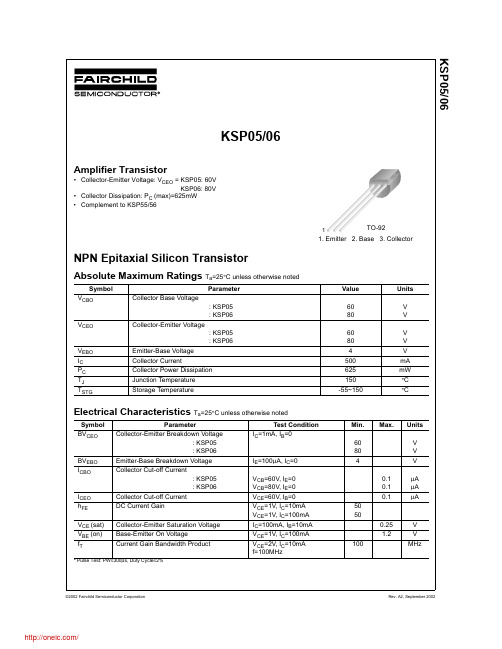

KSP05TA;KSP05BU;中文规格书,Datasheet资料

KSP05/06NPN Epitaxial Silicon TransistorAbsolute Maximum Ratings T a =25°C unless otherwise notedElectrical Characteristics T a =25°C unless otherwise noted* Pulse Test: PW ≤300µs, Duty Cycle ≤2%Symbol ParameterValueUnitsV CBO Collector Base Voltage: KSP05: KSP066080V VV CEOCollector-Emitter Voltage: KSP05: KSP066080V V V EBO Emitter-Base Voltage 4V I C Collector Current500mA P C Collector Power Dissipation 625mW T J Junction Temperature 150°C T STGStorage Temperature-55~150°CSymbol ParameterTest ConditionMin.Max.Units BV CEOCollector-Emitter Breakdown Voltage: KSP05: KSP06I C =1mA, I B =06080 V V BV EBO Emitter-Base Breakdown Voltage I E =100µA, I C =04VI CBOCollector Cut-off Current: KSP05: KSP06V CB =60V, I E =0V CB =80V, I E =00.10.1µA µA I CEO Collector Cut-off Current V CE =60V, I B =00.1µAh FE DC Current GainV CE =1V, I C =10mA V CE =1V, I C =100mA 5050V CE (sat)Collector-Emitter Saturation Voltage I C =100mA, I B =10mA 0.25V V BE (on)Base-Emitter On Voltage V CE =1V, I C =100mA 1.2Vf TCurrent Gain Bandwidth ProductV CE =2V, I C =10mA f=100MHz100 MHzKSP05/06Amplifier Transistor•Collector-Emitter Voltage: V CEO = KSP05: 60VKSP06: 80V•Collector Dissipation: P C (max)=625mW •Complement to KSP55/561. Emitter2. Base3. CollectorTO-921KSP05/06KSP05/06TRADEMARKSThe following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body,or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of TermsDatasheet Identification Product Status DefinitionAdvance InformationFormative or In Design This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.PreliminaryFirst ProductionThis datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.No Identification Needed Full ProductionThis datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.Obsolete Not In ProductionThis datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.FACT™FACT Quiet series™FAST ®FASTr™FRFET™GlobalOptoisolator™GTO™HiSeC™I 2C™ImpliedDisconnect™ISOPLANAR™LittleFET™MicroFET™MicroPak™MICROWIRE™MSX™MSXPro™OCX™OCXPro™OPTOLOGIC ®OPTOPLANAR™PACMAN™POP™Power247™PowerTrench ®QFET™QS™QT Optoelectronics™Quiet Series™RapidConfigure™RapidConnect™SILENT SWITCHER ®SMART START™SPM™Stealth™SuperSOT™-3SuperSOT™-6SuperSOT™-8SyncFET™TinyLogic™TruTranslation™UHC™UltraFET ®VCX™ACEx™ActiveArray™Bottomless™CoolFET™CROSSVOLT ™DOME™EcoSPARK™E 2CMOS™EnSigna™Across the board. Around the world.™The Power Franchise™Programmable Active Droop™分销商库存信息:FAIRCHILDKSP05TA KSP05BU。

EXC05HRXI资料

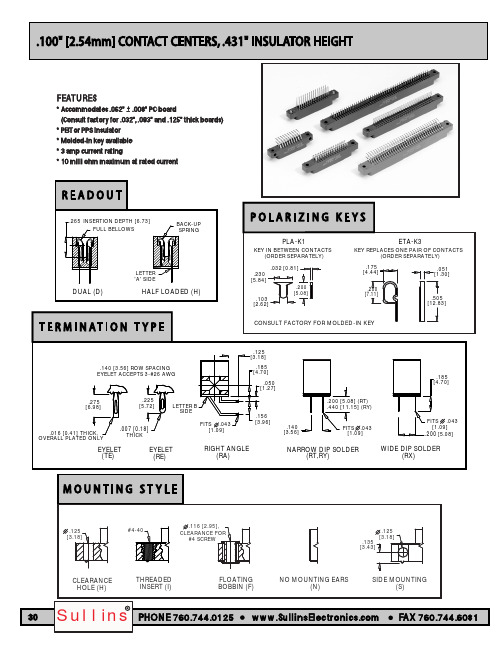

.265 INSERTION DEPTH [6.73] B A F D E REFER TO MOUNTING STYLE .025 [0.64] .100 TYP. [2.54]

INCHES C D +.015 +.010 _ _ 0.675 0.975 0.775 1.075 0.875 1.175 0.975 1.275 1.075 1.375 1.275 1.575 1.475 1.775 1.575 1.875 1.775 2.075 1.975 2.275 2.075 2.375 2.175 2.475 2.275 2.575 2.475 2.775 2.575 2.875 2.775 3.075 2.875 3.175 3.075 3.375 3.275 3.575 3.375 3.675 3.775 4.075 3.875 4.175 4.275 4.575 4.575 4.875 4.675 4.975 5.175 5.475 5.275 5.575 5.475 5.775 6.275 6.575

.016 [0.41] THICK, OVERALL PLATED ONLY

.007 [0.18]

THICK

EYELET (TE)

EYELET (RE)

RIGHT ANGLE (RA)

NARROW DIP SOLDER (RT,RY)

WIDE DIP SOLDER (RX)

.125 [3.18]

#4-40

.116 [2.95], CLEARANCE FOR #4 SCREW

.135 [3.43]

.125 [3.18]

CLEARANCE HOLE (H)

THREADED INSERT (I)

SCX05DNC资料

Microstructure Pressure SensorsCompensated 0 psi to 1psi up to 0 psi to 150 psiSCX SeriesFEATURES• Precision TemperatureCompensation• Calibrated Zero & Span • Small Size • Low Noise• Low Cost (SCX_NC) • High Accuracy (SCX_N) • High Impedance for Low Power ApplicationsTYPICAL APPLICATIONS• Medical Equipment The SCX series sensors provide a very cost-effective solution for pressure applications that require operation over wide temperature range. Theseinternally calibrated and temperature compensated sensors were specifically designed to provide an accurate and stable output over a 0 °C to 70 °C[32 °F to 158 °F] temperature range. This series is intended for use with non-corrosive, non-ionic working fluids such as air, dry gases and the like. • Barometry• Computer Peripherals • Pneumatic Controls • HVACELECTRICAL CONNECTIONDevices are available to measure absolute, differential and gage pressures from 1 psi (SCX01) up to 150 psi (SCX150). The Absolute (A in modelnumber) devices have an internal vacuum reference and an output voltage proportional to absolute pressure. The Differential (D in model number) devices allow application of pressure to either side of the pressure-sensingdiaphragm and can be used for gage or differential measurements.The SCX series devices feature an integrated circuit (IC) sensor element and laser trimmed thick film ceramic housed in a compact solvent resistant case. This package provides excellent corrosion resistance and provides isolation to external packaging stresses. The package has convenient mounting holes and pressure ports for ease of use with standard plastic tubing for pressure connection.PIN 1) TEMPERATURE OUTPUT (+) PIN 2) VsPIN 3) + OUTPUT PIN 4) GROUND If the application requires extended temperature range operation, beyond 0 °C to 70 °C [32 °F to 158 °F], two pins which provide an output voltage proportional to temperature are available for use with external circuitry. The 100 microsecond response time makes this series an excellent choice for computer peripherals and pneumatic control applications.PIN 5) - OUTPUTPIN 6) TEMPERATURE OUTPUT (-)Note: The polarity indicated is for pressure applied to port B. (Forabsolute devices pressure is applied to port A and the output polarity is reversed)The output of the bridge is ratio metric to the supply voltage. Operation from any dc supply voltage up to 20 Vdc is acceptable.WARNINGPERSONAL INJURY DO NOT USE these products as safety oremergency stop devices or in any other application where failure of the product could result in personal injury.Failure to comply with these instructions could result in death or serious injury.Contact your local honeywell representative, or go to Honeywell’s website at /sensing for additional details.WARNINGMISUSE OF DOCUMENTATION• The information presented in this product sheet is for reference only. Do not use this document as a product installation guide.• Complete installation, operation, and maintenance information is provided in the instructions supplied with each product.Failure to comply with these instructions could result in death or serious injury.Sensing and ControlMicrostructure Pressure SensorsCompensated 0 psi to 1psi up to 0 psi to 150 psiSCX SeriesPRESSURE RANGE SPECIFICATIONSFull-Scale Span (1)Model *Operating PressureProofPressure (2)Sensitivity Min. Typ.Max.SCX01DN17.82 mV 18.00 mV 18.18 mV SCX01DNC 0 psid to 1 psid 20 psid18 mV/psi 17.00 mV 18.00 mV 19.00 mV SCX05DN59.40 mV 60.00 mV 60.60 mV SCX05DNC 0 psid to 5 psid 20 psid12 mV/psi 57.50 mV 60.00 mV 62.50 mV SCX15AN89.10 mV 90.00 mV 90.90 mV SCX15ANC 0 psid to 15 psia 30 psia6.0 mV/psi 85.00 mV 90.00 mV 95.00 mV SCX15DN89.10 mV 90.00 mV 90.90 mV SCX15DNC 0 psid to 15 psid 30 psid6.0 mV/psi 85.00 mV 90.00 mV 95.00 mV SCX30AN89.10 mV 90.00 mV 90.90 mV SCX30ANC 0 psid to 30 psia 60 psia3.0 mV/psi 85.00 mV 90.00 mV 95.00 mV SCX30DN89.10 mV 90.00 mV 90.90 mV SCX30DNC 0 psid to 30 psid 60 psid3.0 mV/psi 85.00 mV 90.00 mV 95.00 mV SCX100AN99.00 mV 100.0 mV 101.0 mV SCX100ANC 0 psid to 100 psia 150 psia1.0 mV/psi 95.00 mV 100.0 mV 105.0 mV SCX100DN99.00 mV 100.0 mV 101.0 mV SCX100DNC 0 psid to 100 psid 150 psid1.0 mV/psi 95.00 mV 100.0 mV 105.0 mV SCX150AN89.00 mV 90.00 mV 91.00 mV SCX150ANC 0 psid to 150 psia 150 psia0.6 mV/psi 85.00 mV 90.00 mV 95.00 mV SCX150DN89.00 mV 90.00 mV 91.00 mV SCX150DNC0 psid to 150 psid 150 psid0.6 mV/psi85.00 mV90.00 mV 95.00 mV* Ordering information: Order model number.GENERAL SPECIFICATIONSCharacteristic Description (Maximum Ratings) All Devices Supply Voltage (V S) 20 Vdc Common Mode Pressure 50 psig Lead Soldering Temperature (2 seconds to 4 seconds)250 °C [482 °F]ENVIRONMENTAL SPECIFICATIONSCharacteristicDescription (Maximum Ratings) All DevicesCompensated Operating Temperature 0 °C to 70 °C [32 °F to 158 °F] Operating Temperature -40 °C to 85 °C [-40 °F to 185 °F] Storage Temperature -55 °C to 125 °C [-67 °F to 257 °F] Humidity Limits0 % RH to 100 % RHACCURACYModel Accuracy SCX01 through SCX150 Calibrated for span to within ±1 % (Highest accuracy) SCX01_C through SCX150_C Calibrated for span to within ±5 % (Fine adjustments of zeroand span can be provided in external circuitry)2 Honeywell • Sensing and ControlMicrostructure Pressure SensorsCompensated 0 psi to 1psi up to 0 psi to 150 psi SCX SeriesSCX PERFORMANCE CHARACTERISTICS (3)Characteristic Min.Typ.Max.Unit Zero Pressure Offset (4) -300 0.0 300 MicrovoltCombined Pressure Non-Linearity and Pressure Hysteresis (5) – ±0.1 ±0.5 %FSOTemperature Effect on Span 0 °C to 70 °C [32 °F to 158 °F] (6) – ±0.2 ±0.1 %FSOTemperature Effect on Offset 0 °C to 70 °C [32 °F to 158 °F] (6) – ±100 ±500 MicrovoltRepeatability (7) – ±0.2 ±0.5 %FSOInput Resistance (8) – 4.0 – kOhmOutput Resistance (9) – 4.0 – kOhmCommon Mode Voltage (10) 5.8 6.0 6.2 VdcResponse Time (11) – 100 – Microsec.Long Term Stability of Offset and Span (12) – ±0.1 – mVSCX_C SERIES PERFORMANCE CHARACTERISTICS (3)Characteristic Min.Typ.MaxUnit Zero Pressure Offset -1.0 0.0 ±1.0 mVCombined Pressure Non-Linearity and Pressure Hysteresis (5) Models: SCX05DNC, SCX15ANC, and SCX15DNC,Models: SCX01DNC, SCX30ANC, SCX30DNC, SCX100ANC, SCX100DNC, SCX150ANC, and SCX150DNC –– ±0.1±0.2±1.0±1.0% FSO% FSOTemperature Effect on Span 0 °C to 70 °C [32 °F to 158 °F] (6) –±0.4±2.0%FSO Temperature Effect on Offset 0 °C to 70 °C [32 °F to 158 °F] (6) – ±0.2 ±1.0 mVRepeatability (7) – ±0.2 ±0.5 %FSOInput Resistance (8) – 4.0 – kOhmOutput Resistance (9) – 4.0 – kOhmCommon Mode Voltage (10) 5.7 6.0 6.3 VdcResponse Time (11) – 100 – Microsec.Long Term Stability of Offset and Span (12) – ±0.1 – mV SPECIFICATION NOTESNote 1: Full-Scale Span is the algebraic difference between the output voltage at full-scale pressure and the output at zero pressure.Full-Scale Span is ratiometric to the supply voltage.Note 2: Maximum pressure above which causes permanent sensor failure.Note 3: Reference Conditions: (Unless otherwise noted)T A = 25°C, Supply VS= 12 Vdc, Common Mode Line pressure = 0 psig, Pressure applied to Port B. For absolute devices only,pressure is applied to Port A, and the output polarity is reversed.Note 4: For models SCX15AN, SCX30AN, SCX100AN, and SCX150AN,the Maximum zero pressure offset for absolute devices is 0 to ±500 Microvolt.Note 5: Pressure Hysteresis – the maximum output difference at any point within the operating pressure range for increasing and decreasing pressure.Note 6: Maximum error band of the offset voltage and the error band of the span, relative to the 25 °C [77 °F] reading.Note 7: Maximum difference in output at any pressure within the operating pressure range and the temperature within 0 °C to 70 °C[32 °F to 158 °F] after:a) 1,000 temperature cycles, 0 °C to 70 °C [32 °F to 158 °F]b) 1.5 million pressure cycles, 0 psi to Full-Scale Span.Note 8: Input resistance is the resistance between pins 2 and 4.Note 9: Output resistance is the resistance between pins 3 and 5.Note 10: Common Mode voltage of the output arms (Pins 3 and 5) for V S=12 Vdc.Note 11: Response time for a 0 psi to Full-Scale Span pressure step change, 10 % to 90 % rise time.Note 12: Long term stability over a one-year period.Honeywell • Sensing and Control 3Microstructure Pressure SensorsCompensated 0 psi to 1psi up to 0 psi to 150 psiSCX SeriesSensing and Control/sensingPHYSICAL DIMENSIONS for Reference Only (mm/in)WARRANTY/REMEDYHoneywell warrants goods of its manufacture as being free of defective materials and faulty workmanship.Contact your local sales office for warranty information. If warranted goods are returned to Honeywell during the period of coverage, Honeywell will repair or replace without charge those items it finds defective. Theforegoing is Buyer’s sole remedy and is in lieu of all other warranties, expressed or implied, including those of merchantability and fitness for a particular purpose.Specifications may change without notice. Theinformation we supply is believed to be accurate and reliable as of this printing. However, we assume no responsibility for its use.While we provide application assistance personally,through our literature and the Honeywell web site, it is up to the customer to determine the suitability of the product in the application.For application assistance, current specifications, or name of the nearest Authorized Distributor, contact a nearby sales office. Or call: 1-800-537-6945 USA/Canada 1-815-235-6847 International FAX1-815-235-6545 USA INTERNET/sensing info.sc@Honeywell11 West Spring Street Freeport, Illinois 61032008096-1-EN IL50 GLO 1203 Printed in USACopyright 2003 Honeywell International Inc. All Rights Reserved。

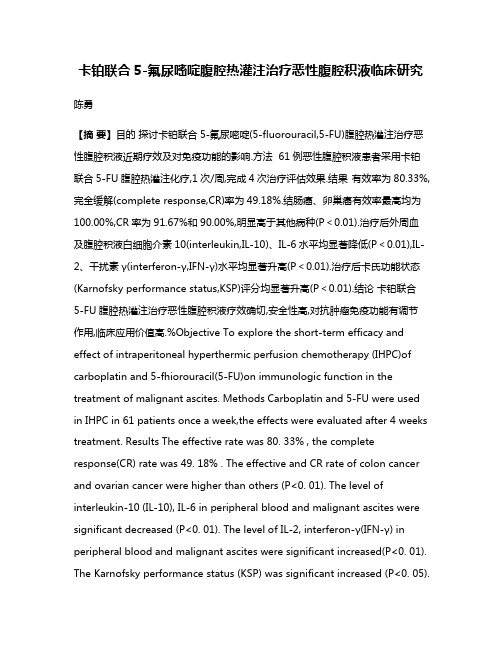

卡铂联合5-氟尿嘧啶腹腔热灌注治疗恶性腹腔积液临床研究

卡铂联合5-氟尿嘧啶腹腔热灌注治疗恶性腹腔积液临床研究陈勇【摘要】目的探讨卡铂联合5-氟尿嘧啶(5-fluorouracil,5-FU)腹腔热灌注治疗恶性腹腔积液近期疗效及对免疫功能的影响.方法 61例恶性腹腔积液患者采用卡铂联合5-FU腹腔热灌注化疗,1次/周,完成4次治疗评估效果.结果有效率为80.33%,完全缓解(complete response,CR)率为49.18%.结肠癌、卵巢癌有效率最高均为100.00%,CR率为91.67%和90.00%,明显高于其他病种(P<0.01).治疗后外周血及腹腔积液白细胞介素10(interleukin,IL-10)、IL-6水平均显著降低(P<0.01),IL-2、干扰素γ(interferon-γ,IFN-γ)水平均显著升高(P<0.01).治疗后卡氏功能状态(Karnofsky performance status,KSP)评分均显著升高(P<0.01).结论卡铂联合5-FU腹腔热灌注治疗恶性腹腔积液疗效确切,安全性高,对抗肿瘤免疫功能有调节作用,临床应用价值高.%Objective To explore the short-term efficacy and effect of intraperitoneal hyperthermic perfusion chemotherapy (IHPC)of carboplatin and 5-fhiorouracil(5-FU)on immunologic function in the treatment of malignant ascites. Methods Carboplatin and 5-FU were used in IHPC in 61 patients once a week,the effects were evaluated after 4 weeks treatment. Results The effective rate was 80. 33% , the complete response(CR) rate was 49. 18% . The effective and CR rate of colon cancer and ovarian cancer were higher than others (P<0. 01). The level of interleukin-10 (IL-10), IL-6 in peripheral blood and malignant ascites were significant decreased (P<0. 01). The level of IL-2, interferon-γ(IFN-γ) in peripheral blood and malignant ascites were significant increased(P<0. 01). The Karnofsky performance status (KSP) was significant increased (P<0. 05).Conclusion IHPC of carboplatin and 5 -FU in treatment of malignant ascites were effective and safe, and could regulate the antineoplastic immune function with a good clinical application value.【期刊名称】《河北医科大学学报》【年(卷),期】2013(034)003【总页数】3页(P270-272)【关键词】肿瘤;腹水;卡铂;氟尿嘧啶【作者】陈勇【作者单位】浙江省平湖市中医院肿瘤内科,浙江,平湖,314200【正文语种】中文【中图分类】R442.5恶性肿瘤腹腔积液是多种晚期肿瘤常见的并发症之一。

EPI6L2172KSP45L中文资料

TEL: (818) 892-0761 FAX: (818) 894-5791

---

54

---

40

---

34

---

35

---

40

42

---

38

---

34

---

37

---

37

---

37

---

40

---

Package B20

.330 (8.83)

PCA EPIXXXXXXB20

D.C.

.330 (8.38)

.060 (1.52)

.300 (7.62)

Suggested Pad Latout

元器件交易网

Surface Mount Power Inductor

ELECTRONICS INC.

EPI B30 Series

• Optimized for National’s LM259X Series • Low loss material ensures operation in high frequency switching

converters, such as Buck, Boost or as output averaging filter inductor • Also suitable for use in high quality filter applications • 150 KHz & 500 KHz Switching Frequency • Low Cost Inductor

DVPL0505S中文资料

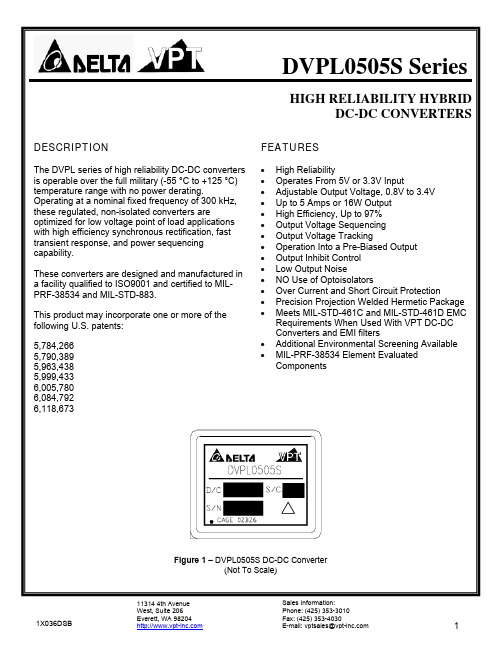

DVPL0505S Series

HIGH RELIABILITY HYBRID DC-DC CONVERTERS

DESCRIPTION

The DVPL series of high reliability DC-DC converters is operable over the full military (-55 °C to +125 °C) temperature range with no power derating. Operating at a nominal fixed frequency of 300 kHz, these regulated, non-isolated converters are optimized for low voltage point of load applications with high efficiency synchronous rectification, fast transient response, and power sequencing capability.

VOUT VOUT

VOUT VOUT VOUT

FAULT POWER DISSIPATION CAPACITIVE LOAD4

SWITCHING FREQUENCY

CASE ISOLATION

MTBF (MIL-HDBK-217F)

DYNAMIC

Load Step Output Transient5 Load Step Recovery2,5

3.3

3.30k

3.4

2.98k

R-TRIM

The output voltage is set with an external resistor connected from Trim pin to GND pin. This resistor must have a tolerance of 1% or less to achieve an accurate output voltage.

NC7SP05_04中文资料

TinyLogic is a registered trademark of Fairchild Semiconductor Corporation. Quiet Series, and MicroPak are trademarks of Fairchild Semiconductor Corporation.

Supply Voltage Input Voltage (VIN) Output Voltage (VOUT) HIGH or LOW State VCC = 0V Output Current in IOH/IOL VCC = 3.0V to 3.6V VCC = 2.3V to 2.7V VCC = 1.65V to 1.95V VCC = 1.40V to 1.60V VCC = 1.10V to 1.30V VCC = 0.9V Free Air Operating Temperature (TA) Minimum Input Edge Rate (∆t/∆V) VIN = 0.8V to 2.0V, VCC = 3.0V 10 ns/V

Ordering Code:

Order Number NC7SP05P5X NC7SP05L6X Package Number MAA05A MAC06A Product Code Top Mark P05 J7 Package Description 5-Lead SC70, EIAJ SC-88a, 1.25mm Wide 6-Lead MicroPak, 1.0mm Wide Supplied As 3k Units on Tape and Reel 5k Units on Tape and Reel

−0.5V to +4.6V −0.5V to +4.6V −0.5V to VCC +0.5V −0.5V to 4.6V ±50 mA −50 mA +50 mA ± 50 mA ± 50 mA −65°C to +150 °C

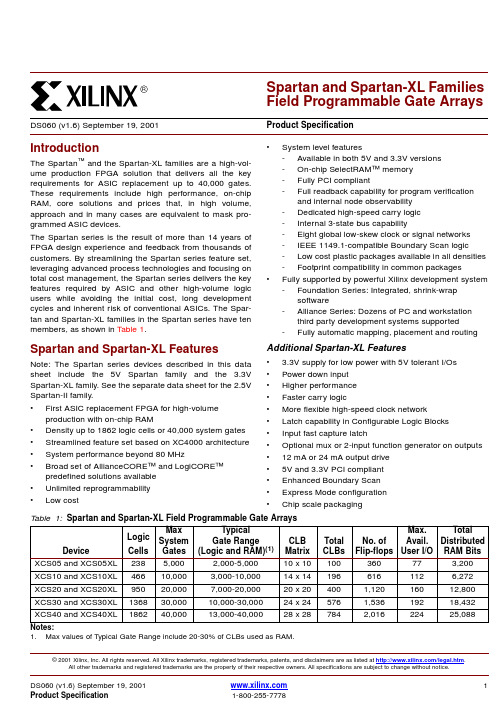

XCS05XL-4PC144I中文资料

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.IntroductionThe Spartan ™ and the Spartan-XL families are a high-vol-ume production FPGA solution that delivers all the key requirements for ASIC replacement up to 40,000 gates.These requirements include high performance, on-chip RAM, core solutions and prices that, in high volume,approach and in many cases are equivalent to mask pro-grammed ASIC devices.The Spartan series is the result of more than 14 years of FPGA design experience and feedback from thousands of customers. By streamlining the Spartan series feature set,leveraging advanced process technologies and focusing on total cost management, the Spartan series delivers the key features required by ASIC and other high-volume logic users while avoiding the initial cost, long development cycles and inherent risk of conventional ASICs. The Spar-tan and Spartan-XL families in the Spartan series have ten members, as shown in T able 1.Spartan and Spartan-XL FeaturesNote: The Spartan series devices described in this data sheet include the 5V Spartan family and the 3.3V Spartan-XL family. See the separate data sheet for the 2.5V Spartan-II family.•First ASIC replacement FPGA for high-volume production with on-chip RAM•Density up to 1862 logic cells or 40,000 system gates •Streamlined feature set based on XC4000 architecture •System performance beyond 80MHz•Broad set of AllianceCORE ™ and LogiCORE ™ predefined solutions available •Unlimited reprogrammability •Low cost•System level features-Available in both 5V and 3.3V versions -On-chip SelectRAM ™ memory -Fully PCI compliant-Full readback capability for program verificationand internal node observability -Dedicated high-speed carry logic -Internal 3-state bus capability-Eight global low-skew clock or signal networks -IEEE 1149.1-compatible Boundary Scan logic -Low cost plastic packages available in all densities -Footprint compatibility in common packages•Fully supported by powerful Xilinx development system -Foundation Series: Integrated, shrink-wrapsoftware-Alliance Series: Dozens of PC and workstationthird party development systems supported-Fully automatic mapping, placement and routing Additional Spartan-XL Features• 3.3V supply for low power with 5V tolerant I/Os •Power down input •Higher performance •Faster carry logic•More flexible high-speed clock network•Latch capability in Configurable Logic Blocks •Input fast capture latch•Optional mux or 2-input function generator on outputs •12 mA or 24 mA output drive •5V and 3.3V PCI compliant •Enhanced Boundary Scan •Express Mode configuration •Chip scale packagingSpartan and Spartan-XL Families Field Programmable Gate ArraysDS060 (v1.6) September 19, 2001Product Specification T able 1: Spartan and Spartan-XL Field Programmable Gate Arrays1.Max values of Typical Gate Range include 20-30% of CLBs used as RAM.2DS060 (v1.6) September 19, 2001General OverviewSpartan series FPGAs are implemented with a regular, flex-ible, programmable architecture of Configurable Logic Blocks (CLBs), interconnected by a powerful hierarchy of versatile routing resources (routing channels), and sur-rounded by a perimeter of programmable Input/Output Blocks (IOBs), as seen in Figure 1. They have generous routing resources to accommodate the most complex inter-connect patterns.The devices are customized by loading configuration data into internal static memory cells. Re-programming is possi-ble an unlimited number of times. The values stored in thesememory cells determine the logic functions and intercon-nections implemented in the FPGA. The FPGA can either actively read its configuration data from an external serial PROM (Master Serial mode), or the configuration data can be written into the FPGA from an external device (Slave Serial mode).Spartan series FPGAs can be used where hardware must be adapted to different user applications. FPGAs are ideal for shortening design and development cycles, and also offer a cost-effective solution for production rates well beyond 50,000 systems per month.Figure 1: Basic FPGA Block DiagramSpartan series devices achieve high-performance, low-cost operation through the use of an advanced architecture and semiconductor technology. Spartan and Spartan-XL devices provide system clock rates exceeding 80MHz and internal performance in excess of150MHz. In contrast to other FPGA devices, the Spartan series offers the most cost-effective solution while maintaining leading-edge per-formance. In addition to the conventional benefit of high vol-ume programmable logic solutions, Spartan series FPGAs also offer on-chip edge-triggered single-port and dual-port RAM, clock enables on all flip-flops, fast carry logic, and many other features.The Spartan/XL families leverage the highly successful XC4000 architecture with many of that family’s features and benefits. T echnology advancements have been derived from the XC4000XLA process developments.Logic Functional DescriptionThe Spartan series uses a standard FPGA structure as shown in Figure1, page2. The FPGA consists of an array of configurable logic blocks (CLBs) placed in a matrix of routing channels. The input and output of signals is achieved through a set of input/output blocks (IOBs) forming a ring around the CLBs and routing channels.•CLBs provide the functional elements for implementing the user’s logic.•IOBs provide the interface between the package pins and internal signal lines.•Routing channels provide paths to interconnect the inputs and outputs of the CLBs and IOBs.The functionality of each circuit block is customized during configuration by programming internal static memory cells. The values stored in these memory cells determine the logic functions and interconnections implemented in the FPGA.Configurable Logic Blocks (CLBs)The CLBs are used to implement most of the logic in an FPGA. The principal CLB elements are shown in the simpli-fied block diagram in Figure2. There are three look-up tables (LUT) which are used as logic function generators, two flip-flops and two groups of signal steering multiplexers. There are also some more advanced features provided by the CLB which will be covered in the Advanced Features Description, page13.Function GeneratorsTwo 16x1 memory look-up tables (F-LUT and G-LUT) are used to implement 4-input function generators, each offer-ing unrestricted logic implementation of any Boolean func-tion of up to four independent input signals (F1 to F4 or G1 to G4). Using memory look-up tables the propagation delay is independent of the function implemented.A third 3-input function generator (H-LUT) can implement any Boolean function of its three inputs. Two of these inputs are controlled by programmable multiplexers (see box "A" of Figure2). These inputs can come from the F-LUT or G-LUT outputs or from CLB inputs. The third input always comes from a CLB input. The CLB can, therefore, implement cer-tain functions of up to nine inputs, like parity checking. The three LUTs in the CLB can also be combined to do any arbi-trarily defined Boolean function of five inputs.4DS060 (v1.6) September 19, 2001A CLB can implement any of the following functions:•Any function of up to four variables, plus any second function of up to four unrelated variables, plus any third function of up to three unrelated variablesNote: When three separate functions are generated, one of the function outputs must be captured in a flip-flop internal to the CLB. Only two unregistered function generator outputs are available from the CLB.•Any single function of five variables•Any function of four variables together with some functions of six variables•Some functions of up to nine variables.Implementing wide functions in a single block reduces both the number of blocks required and the delay in the signal path, achieving both increased capacity and speed. The versatility of the CLB function generators significantly improves system speed. In addition, the design-software tools can deal with each function generator independently.This flexibility improves cell usage.Flip-FlopsEach CLB contains two flip-flops that can be used to regis-ter (store) the function generator outputs. The flip-flops and function generators can also be used independently (see Figure 2). The CLB input DIN can be used as a direct input to either of the two flip-flops. H1 can also drive either flip-flop via the H-LUT with a slight additional delay.The two flip-flops have common clock (CK), clock enable (EC) and set/reset (SR) inputs. Internally both flip-flops are also controlled by a global initialization signal (GSR) which is described in detail in Global Signals: GSR and GTS ,page 20.Latches (Spartan-XL only)The Spartan-XL CLB storage elements can also be config-ured as latches. The two latches have common clock (K)and clock enable (EC) inputs. Functionality of the storage element is described in Table 2.Figure 2: Spartan/XL Simplified CLB Logic Diagram (some features not shown)Clock InputEach flip-flop can be triggered on either the rising or falling clock edge. The CLB clock line is shared by both flip-flops.However, the clock is individually invertible for each flip-flop (see CK path in Figure 3). Any inverter placed on the clock line in the design is automatically absorbed into the CLB. Clock EnableThe clock enable line (EC) is active High. The EC line is shared by both flip-flops in a CLB. If either one is left discon-nected, the clock enable for that flip-flop defaults to the active state. EC is not invertible within the CLB. The clock enable is synchronous to the clock and must satisfy the setup and hold timing specified for the device.Set/ResetThe set/reset line (SR) is an asynchronous active High con-trol of the flip-flop. SR can be configured as either set or reset at each flip-flop. This configuration option determines the state in which each flip-flop becomes operational after configuration. It also determines the effect of a GSR pulse during normal operation, and the effect of a pulse on the SR line of the CLB. The SR line is shared by both flip-flops. If SR is not specified for a flip-flop the set/reset for that flip-flop defaults to the inactive state. SR is not invertible within the CLB.CLB Signal Flow ControlIn addition to the H-LUT input control multiplexers (shown in box "A" of Figure 2, page 4) there are signal flow control multiplexers (shown in box "B" of Figure 2) which select the signals which drive the flip-flop inputs and the combinatorial CLB outputs (X and Y).Each flip-flop input is driven from a 4:1 multiplexer which selects among the three LUT outputs and DIN as the data source.Each combinatorial output is driven from a 2:1 multiplexer which selects between two of the LUT outputs. The X output can be driven from the F-LUT or H-LUT, the Y output from G-LUT or H-LUT .Control SignalsThere are four signal control multiplexers on the input of the CLB. These multiplexers allow the internal CLB control sig-nals (H1, DIN, SR, and EC in Figure 2 and Figure 4) to be driven from any of the four general control inputs (C1-C4 in Figure 4) into the CLB. Any of these inputs can drive any of the four internal control signals.T able 2: CLB Storage Element FunctionalityLegend:XDon ’t careRising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Figure 3: CLB Flip-Flop Functional Block Diagram6DS060 (v1.6) September 19, 2001The four internal control signals are:•EC: Enable Clock•SR: Asynchronous Set/Reset or H function generator Input 0•DIN: Direct In or H function generator Input 2•H1: H function generator Input 1.Input/Output Blocks (IOBs)User-configurable input/output blocks (IOBs) provide the interface between external package pins and the internal logic. Each IOB controls one package pin and can be con-figured for input, output, or bidirectional signals. Figure 6shows a simplified functional block diagram of the Spar-tan/XL IOB.IOB Input Signal PathThe input signal to the IOB can be configured to either go directly to the routing channels (via I1 and I2 in Figure 6) or to the input register. The input register can be programmed as either an edge-triggered flip-flop or a level-sensitive latch. The functionality of this register is shown in Table 3,and a simplified block diagram of the register can be seen in Figure 5.Figure 4: CLB Control Signal InterfaceFigure 5: IOB Flip-Flop/Latch Functional BlockDiagramTable 3: Input Register FunctionalityX Don ’t care.Rising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)The register choice is made by placing the appropriate library symbol. For example, IFD is the basic input flip-flop (rising edge triggered), and ILD is the basic input latch (transparent-High). Variations with inverted clocks are also available. The clock signal inverter is also shown in Figure5 on the CK line.The Spartan IOB data input path has a one-tap delay ele-ment: either the delay is inserted (default), or it is not. The Spartan-XL IOB data input path has a two-tap delay ele-ment, with choices of a full delay, a partial delay, or no delay. The added delay guarantees a zero hold time with respect to clocks routed through the global clock buffers. (See Glo-bal Nets and Buffers, page12 for a description of the glo-bal clock buffers in the Spartan/XL families.) For a shorter input register setup time, with positive hold-time, attach a NODELAY attribute or property to the flip-flop.The output of the input register goes to the routing channels (via I1 and I2 in Figure6). The I1 and I2 signals that exit the IOB can each carry either the direct or registered input signal.The 5V Spartan input buffers can be globally configured for either TTL (1.2V) or CMOS (VCC/2) thresholds, using an option in the bitstream generation software. The Spartan output levels are also configurable; the two global adjust-ments of input threshold and output level are independent. The inputs of Spartan devices can be driven by the outputs of any 3.3V device, if the Spartan inputs are in TTL mode. Input and output thresholds are TTL on all configuration pins until the configuration has been loaded into the device and specifies how they are to be used. Spartan-XL inputs are TTL compatible and 3.3V CMOS compatible. Supported sources for Spartan/XL device inputs are shown in Table4.Spartan-XL I/Os are fully 5V tolerant even though the V CC is 3.3V. This allows 5V signals to directly connect to the Spar-tan-XL inputs without damage, as shown in Table4. In addi-tion, the 3.3V V CC can be applied before or after 5V signals are applied to the I/Os. This makes the Spartan-XL devices immune to power supply sequencing problems.Figure 6: Simplified Spartan/XL IOB Block Diagram8DS060 (v1.6) September 19, 2001Spartan-XL V CC ClampingSpartan-XL FPGAs have an optional clamping diode con-nected from each I/O to V CC . When enabled they clamp ringing transients back to the 3.3V supply rail. This clamping action is required in 3.3V PCI applications. V CC clamping is a global option affecting all I/O pins.Spartan-XL devices are fully 5V TTL I/O compatible if V CC clamping is not enabled. With V CC clamping enabled, the Spartan-XL devices will begin to clamp input voltages to one diode voltage drop above V CC . If enabled, TTL I/O com-patibility is maintained but full 5V I/O tolerance is sacrificed.The user may select either 5V tolerance (default) or 3.3V PCI compatibility. In both cases negative voltage is clamped to one diode voltage drop below ground.Spartan-XL devices are compatible with TTL, LVTTL, PCI 3V, PCI 5V and LVCMOS signalling. The various standards are illustrated in Table 5.Additional Fast Capture Input Latch (Spartan-XL only)The Spartan-XL IOB has an additional optional latch on the input. This latch is clocked by the clock used for the output flip-flop rather than the input clock. Therefore, two different clocks can be used to clock the two input storage elements.This additional latch allows the fast capture of input data,which is then synchronized to the internal clock by the IOB flip-flop or latch.T o place the Fast Capture latch in a design, use one of the special library symbols, ILFFX or ILFLX. ILFFX is a trans-parent-Low Fast Capture latch followed by an active High input flip-flop. ILFLX is a transparent Low Fast Capture latch followed by a transparent High input latch. Any of the clock inputs can be inverted before driving the library element,and the inverter is absorbed into the IOB.IOB Output Signal PathOutput signals can be optionally inverted within the IOB,and can pass directly to the output buffer or be stored in an edge-triggered flip-flop and then to the output buffer. The functionality of this flip-flop is shown in T able 6.T able 4: Supported Sources for Spartan/XL InputsT able 5: I/O Standards Supported by Spartan-XL FPGAsTable 6: Output Flip-Flop Functionality X Don ’t careRising edge (clock not inverted). SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Z3-stateOutput Multiplexer/2-Input Function Generator (Spartan-XL only)The output path in the Spartan-XL IOB contains an addi-tional multiplexer not available in the Spartan IOB. The mul-tiplexer can also be configured as a 2-input function generator, implementing a pass gate, AND gate, OR gate, or XOR gate, with 0, 1, or 2 inverted inputs.When configured as a multiplexer, this feature allows two output signals to time-share the same output pad, effec-tively doubling the number of device outputs without requir-ing a larger, more expensive package. The select input is the pin used for the output flip-flop clock, OK.When the multiplexer is configured as a 2-input function generator, logic can be implemented within the IOB itself. Combined with a Global buffer, this arrangement allows very high-speed gating of a single signal. For example, a wide decoder can be implemented in CLBs, and its output gated with a Read or Write Strobe driven by a global buffer. The user can specify that the IOB function generator be used by placing special library symbols beginning with the letter "O." For example, a 2-input AND gate in the IOB func-tion generator is called OAND2. Use the symbol input pin labeled "F" for the signal on the critical path. This signal is placed on the OK pin — the IOB input with the shortest delay to the function generator. Two examples are shown in Figure7.Output BufferAn active High 3-state signal can be used to place the out-put buffer in a high-impedance state, implementing 3-state outputs or bidirectional I/O. Under configuration control, the output (O) and output 3-state (T) signals can be inverted. The polarity of these signals is independently configured for each IOB (see Figure6, page7). An output can be config-ured as open-drain (open-collector) by tying the 3-state pin (T) to the output signal, and the input pin (I) to Ground.By default, a 5V Spartan device output buffer pull-up struc-ture is configured as a TTL-like totem-pole. The High driver is an n-channel pull-up transistor, pulling to a voltage one transistor threshold below V CC. Alternatively, the outputs can be globally configured as CMOS drivers, with additional p-channel pull-up transistors pulling to V CC. This option, applied using the bitstream generation software, applies to all outputs on the device. It is not individually programma-ble.All Spartan-XL device outputs are configured as CMOS drivers, therefore driving rail-to-rail. The Spartan-XL outputs are individually programmable for 12mA or 24mA output drive.Any 5V Spartan device with its outputs configured in TTL mode can drive the inputs of any typical 3.3V device. Sup-ported destinations for Spartan/XL device outputs are shown in Table7.Three-State Register (Spartan-XL Only)Spartan-XL devices incorporate an optional register control-ling the three-state enable in the IOBs. The use of the three-state control register can significantly improve output enable and disable time.Output Slew RateThe slew rate of each output buffer is, by default, reduced, to minimize power bus transients when switching non-criti-cal signals. For critical signals, attach a FAST attribute or property to the output buffer or flip-flop.Spartan/XL devices have a feature called "Soft Start-up," designed to reduce ground bounce when all outputs are turned on simultaneously at the end of configuration. When the configuration process is finished and the device starts up, the first activation of the outputs is automatically slew-rate limited. Immediately following the initial activation of the I/O, the slew rate of the individual outputs is deter-mined by the individual configuration option for each IOB. Pull-up and Pull-down NetworkProgrammable pull-up and pull-down resistors are used fortying unused pins to V CC or Ground to minimize power con-sumption and reduce noise sensitivity. The configurablepull-up resistor is a p-channel transistor that pulls to V CC.The configurable pull-down resistor is an n-channel transis-tor that pulls to Ground. The value of these resistors is typi-cally 20KΩ − 100KΩ (See "Spartan DC Characteristics Figure 7: AND and MUX Symbols in Spartan-XL IOB10DS060 (v1.6) September 19, 2001Over Operating Conditions" on page 43.). This high value makes them unsuitable as wired-AND pull-up resistors.After configuration, voltage levels of unused pads, bonded or unbonded, must be valid logic levels, to reduce noise sensitivity and avoid excess current. Therefore, by default,unused pads are configured with the internal pull-up resistor active. Alternatively, they can be individually configured with the pull-down resistor, or as a driven output, or to be driven by an external source. To activate the internal pull-up, attach the PULLUP library component to the net attached to the pad. To activate the internal pull-down, attach the PULL-DOWN library component to the net attached to the pad.Set/ResetAs with the CLB registers, the GSR signal can be used to set or clear the input and output registers, depending on the value of the INIT attribute or property. The two flip-flops can be individually configured to set or clear on reset and after configuration. Other than the global GSR net, no user-con-trolled set/reset signal is available to the I/O flip-flops (Figure 5). The choice of set or reset applies to both the ini-tial state of the flip-flop and the response to the GSR pulse.Independent ClocksSeparate clock signals are provided for the input (IK) and output (OK) flip-flops. The clock can be independently inverted for each flip-flop within the IOB, generating eitherfalling-edge or rising-edge triggered flip-flops. The clock inputs for each IOB are mon Clock EnablesThe input and output flip-flops in each IOB have a common clock enable input (see EC signal in Figure 5), which through configuration, can be activated individually for the input or output flip-flop, or both. This clock enable operates exactly like the EC signal on the Spartan/XL CLB. It cannot be inverted within the IOB.Routing Channel DescriptionAll internal routing channels are composed of metal seg-ments with programmable switching points and switching matrices to implement the desired routing. A structured,hierarchical matrix of routing channels is provided to achieve efficient automated routing.This section describes the routing channels available in Spartan/XL devices. Figure 8 shows a general block dia-gram of the CLB routing channels. The implementation soft-ware automatically assigns the appropriate resources based on the density and timing requirements of the design.The following description of the routing channels is for infor-mation only and is simplified with some minor details omit-ted. For an exact interconnect description the designer should open a design in the FPGA Editor and review the actual connections in this tool.The routing channels will be discussed as follows;•CLB routing channels which run along each row and column of the CLB array.•IOB routing channels which form a ring (called a VersaRing) around the outside of the CLB array. It connects the I/O with the CLB routing channels.•Global routing consists of dedicated networks primarily designed to distribute clocks throughout the device with minimum delay and skew. Global routing can also be used for other high-fanout signals.CLB Routing ChannelsThe routing channels around the CLB are derived from three types of interconnects; single-length, double-length,and longlines. At the intersection of each vertical and hori-zontal routing channel is a signal steering matrix called a Programmable Switch Matrix (PSM). Figure 8 shows the basic routing channel configuration showing single-length lines, double-length lines and longlines as well as the CLBs and PSMs. The CLB to routing channel interface is shown as well as how the PSMs interface at the channel intersec-tions.T able 7: Supported Destinations for Spartan/XL OutputsNotes:1.Only if destination device has 5V tolerant inputs.CLB InterfaceA block diagram of the CLB interface signals is shown in Figure9. The input signals to the CLB are distributed evenly on all four sides providing maximum routing flexibility. In general, the entire architecture is symmetrical and regular. It is well suited to established placement and routing algo-rithms. Inputs, outputs, and function generators can freely swap positions within a CLB to avoid routing congestion during the placement and routing operation. The exceptions are the clock (K) input and CIN/COUT signals. The K input is routed to dedicated global vertical lines as well as four single-length lines and is on the left side of the CLB. The CIN/COUT signals are routed through dedicated intercon-nects which do not interfere with the general routing struc-ture. The output signals from the CLB are available to drive both vertical and horizontal channels.Programmable Switch MatricesThe horizontal and vertical single- and double-length lines intersect at a box called a programmable switch matrix (PSM). Each PSM consists of programmable pass transis-tors used to establish connections between the lines (see Figure10).For example, a single-length signal entering on the right side of the switch matrix can be routed to a single-length line on the top, left, or bottom sides, or any combination thereof, if multiple branches are required. Similarly, a dou-ble-length signal can be routed to a double-length line on any or all of the other three edges of the programmable switch matrix.Single-Length LinesSingle-length lines provide the greatest interconnect flexibil-ity and offer fast routing between adjacent blocks. There are eight vertical and eight horizontal single-length lines associ-ated with each CLB. These lines connect the switching matrices that are located in every row and column of CLBs. Single-length lines are connected by way of the program-mable switch matrices, as shown in Figure10. Routing con-nectivity is shown in Figure8.Single-length lines incur a delay whenever they go through a PSM. Therefore, they are not suitable for routing signals for long distances. They are normally used to conduct sig-nals within a localized area and to provide the branching for nets with fanout greater than one.Figure 8: Spartan/XL CLB Routing Channels and Interface Block DiagramFigure 9: CLB Interconnect Signals。

KOYO DL05 系列可编程序控制器 说明书

Value & Technology可编程序控制器DL05系列用户手册[第二版]前言感谢你购买DL05系列PLC产品。

本手册向你详细介绍了DL05系列PLC的安装、设置及维护等内容;它也帮助你理解如何在一个系统中连接DL05系列PLC和其他的设备。

在首次使用DL05系列PLC前,务请先详细阅读本手册。

如果你在阅读本手册或使用DL05系列PLC时有什么疑难,或你需要另外的信息时,请与本公司或各地办事机构联系,以便尽快得到帮助。

由于产品的改进等原因,有时资料所刊内容会与实际的产品有些差别,请注意!在没有预先得到本公司书面许可的情况下,此手册的任何一部分都不得以任何方式被拷贝,复制或传播。

本公司保留对包括此文件在内的所有信息的专利权。

有关编程的内容,请参见《S系列编程手册》有关DL05上可使用扩充模块的资料,请参见《D0系列扩充模块资料》有关PID调节等功能,参见《DL05PID功能技术资料》手册版本如果有关此手册的情况你需与我们联系的话,应确认版本号。

题目:DL05 系列 用户手册刊号:KEW-M4111B版本日期变更说明原版2001/07 初版A版2004/02 第一版第二次印刷B版2010/08 第二版,增加对扩展模块支持的说明本手册中所用的提示标记当你看到左边的“感叹号”图标时,表明紧随其后的段落是一条警告信息。

此信息可以防止伤害、财产损失,甚至死亡。

左边的“记事本”图标表明紧随其后的段落将是一条特别的注意事项。

目录第1章开始 (1)DL05系列PLC (1)一般规格 (1)供电电源规格 (2)I/O选择 (2)输入接线图 (2)连接电源线 (4)连接编程设备 (4)第2章安装 (5)DL05前面板 (5)端子台拆卸 (5)安装尺寸 (6)导轨安装 (7)输入/输出回路保险丝 (7)源/汇的概念 (8)I/O公共端”C OMMON”的概念 (8)连接DC型I/O与晶体管现场设备(“S OLID S TATE”) (9)继电器输出接线方法 (12)DC输入接线方法 (14)DC输出接线方法 (15)AC输入/AC输出接线方法 (16)高速I/O接线方法 (17)DL05I/O电气性能规格 (18)第3章CPU性能和操作 (20)简介 (20)DL05特点 (20)CPU规格 (21)CPU硬件设置 (22)状态指示灯 (23)运行方式开关 (24)系统参数区 (24)停电保持区域 (24)DL05功能存储器 (25)DL05扩展I/O模块起始定义号 (25)DL05系统参数寄存器 (26)DL05特殊继电器 (28)DL05网络系统设置 (30)第4章高速计数和脉冲输出功能 (39)第一节简介 (39)第二节模式10:高速计数 (41)第三节模式20:A/B相计数 (51)第四节模式30:脉冲输出 (56)第五节模式40:外部中断 (74)第六节模式50:脉冲捕捉 (78)第七节模式60:滤波输入 (80)第5章系统维护 (82)硬件系统的维护 (82)诊断 (82)CPU显示 (85)通讯问题 (85)I/O点问题的解决 (85)电气干扰问题 (86)程序调试 (86)附录 (87)附录一DL05指令表 (87)附录二DL05系列无协议通讯 (93)第1章 开始DL05系列PLCDL05系列有8种型号,外观和CPU性能都相同。

R05H15资料

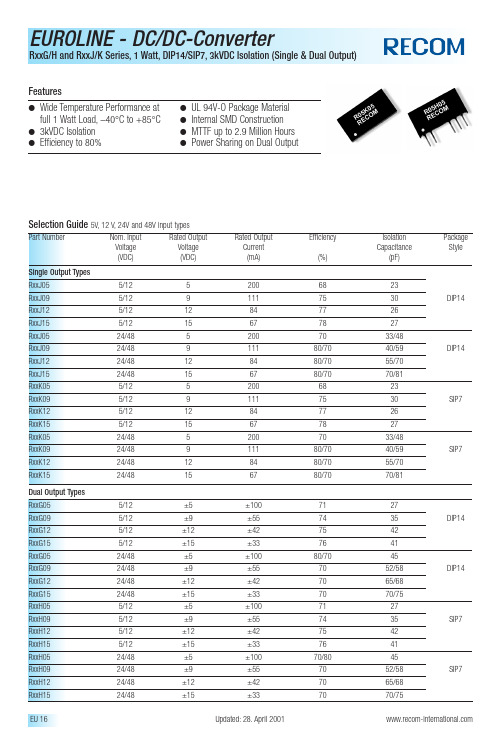

Dual Output TypesRxxG055/12±5±1007127RxxG095/12±9±557435DIP14 RxxG125/12±12±427542RxxG155/12±15±337641RxxG0524/48±5±10080/7045RxxG0924/48±9±557052/58DIP14 RxxG1224/48±12±427065/68RxxG1524/48±15±337070/75RxxH055/12±5±1007127RxxH095/12±9±557435SIP7 RxxH125/12±12±427542RxxH155/12±15±337641RxxH0524/48±5±10070/8045RxxH0924/48±9±557052/58SIP7 RxxH1224/48±12±427065/68RxxH1524/48±15±337070/75Absolute Maximum RatingsInput Voltage V IN5V types 7V typ.12V types 15V typ.24V types 24V typ.48V types48V typ.Short Circuit Duration 1)1s Internal Power Dissipation560mW Lead Temperature (1.5 mm from case for 10 seconds)300 °C1).Supply voltage must be discontinued at the end of the short circuit duration.Input Voltage Range V IN (continuous operation)5V input types 4.5VDC min./ 5.5VDC max.12V input types 10.8VDC min./ 13.2VDC max.24V input types 28VDC max.48V input types54VDC max.Reflected Ripple Current (depending on the type)20 mA p-p min.to 40 mA p-p max.Voltage Set Point Accuracy See Tolerance EnvelopeLine Regulation1.0% / 1.2% of V INLoad Voltage Regulation (10% load to 100% full load)single output types 6.7% min./ 15% max.dual output types 6.8% min./ 10% max.Ripple & Noise (20MHz band limited)single output types 32mVp-p min./ 80mVp-p max.dual output types24mVp-p min./ 40mVp-p max.Isolation Voltage (for 1 minute)3000VDC min.Test Voltage (50Hz,10 seconds)3000 Vpk min.Resistance (Viso = 1000V)10 G Ωtyp.Switching Frequency at Full Load (depending on the type)V IN 5V output types 120kHz min./ 135kHz max.V IN 12V output types 150kHz min./ 170kHz max.V IN 24V output types 150kHz max.V IN 48V output types150kHz max.Package Weight2.11 gOperating Temperature Range (all output types)–40°C min.to +85°C max.(see graph)Storage Temperature Range–50°C min.+125°C max.Case Temperature Above Ambient (depending on the type)5V output types+28°C max.all other output types +25°C max.MTTF 1) (depending on the type)–40°C,single output types 303kHrs min./ 2938kHrs max.+25°C,single output types 252kHrs min./ 2414kHrs max.+85°C,single output types 212kHrs min./ 1961kHrs max.–40°C,dual output types 185kHrs min./ 2068kHrs max.+25°C,dual output types 154kHrs min./ 1697kHrs max.+85°C,dual output types130kHrs min./ 1368kHrs max.1).Calculated using MIL-HDBK-217F with nominal input voltage at full load.Please contact us,if you need exact parameters for the converter you have selected.Electrical Specifications (measured at T A = 25°C,at nominal input voltage and rated output current unless otherwise specified)Package Style and Pinning (mm)。

JFQ.P-O.05

1 目的对公司所确定及所认定的重要环境及危险因素有关的运行与活动进行控制,以确保方针、目标和指标的有效实现。

2 适用范围本程序对公司所确定及所认定的重要环境及危险因素有关的运行与活动的管理和控制进行了说明。

3 职责3.1 管理者代表负责确定公司重要环境及危险因素。

3.2 管理者代表负责组织编制公司管理体系文件,确保重要环境及危险因素有关的运行和活动在受控状态下运行。

4 定义(略)5 运作流程5.1 管理者代表负责依据《环境因素控制程序》及〈危险源辨识和风险评价控制程序〉确定公司每一重要环境及危险因素。

5.2 公司重要环境及危险因素有关的运行和活动包括:a、物资储存、运输、运输车辆维护等;b、工艺实施、设备操作、维护、物料搬运等;c、设备购置、维修等;d、原材料选型、替代等;5.3 管理者代表组织策划对重要环境及危险因素涉及之运行与活动的管理和控制,若考虑在缺乏程序指导可能导致偏离方针、目标与指标的运行情况时,应建立并保持成文的程序及运行的标准。

5.4 有关文件的编制、审批及发布依据《文件控制程序》执行。