ModelSim 保存仿真文件过程

Modelsim工具的一般仿真流程

Mod elsim工具的使用一、仿真流程1.建立work库通常modelsim在使用的时候,和大多数开发软件一样,第一步先建立一个工程。

而modelsim在建立工程之前,一般都要建立一个工作库(library),命名为work,仿真的时候工程就运行在这个库里面。

通常modelsim在第一次运行的时候,并没有work这个库文件,所以没有work库的话,先建立一个work的library,再建立新的工程。

一般的工程路径设置如下:project放置FPGA的工程文件,source放置源代码(ipcore,建议放在工程的根目录下,有同事发现ipcore改变其路径,仿真的时候会出错,并且工程里面要手动添加IP核的文件),simulation放置modelsim的仿真工程。

新建一个work库。

File New-Library刚建立的work库是空的,因为里面什么东西都没有,但是当添加了相应的文件后,编译一次,work就会有内容了。

新建的Work,右键设置Edit一下他的属性,如图上所示,pathname这里指定到存放仿真工程的work的库文件夹即可。

2.建立新工程File—>New-Project然后就会弹出如下对话框,选择好工程的路径,命名好工程名字。

,如果之前就已经编写好了v或者vhd文件的话,直接选择add existing file,否则,选择Create New File。

接下来把所有的v或者vhd的文件都添加进来。

3.编写testbench……4.编译整个工程编写完testbench之后,编译整个工程,以后每当工程中其中一个文件修改后,只需单独编译修改的那个文件即可。

(参见文档最后部分的例子)编译完后,会发现在Project中,里面的文件都会打钩,并且在simulation文件夹里面的子文件夹work会多了一些东西出来。

返回到Library这里,会发现之前是空的wrok文件库里面,现在也多了一些东西。

ModelSim的前后仿真(Quartus)

利用Quartus5.0实现功能仿真1)打开一个工程文件。

2)打开Settings设置栏,选择Fitting Settings下的Simulator栏。

在右边出现的设置栏中将“Simulation Mode”的下拉菜单选择“Functional”,即可以实现软件下的功能仿真。

(下拉菜单中有“Functional”、“Timing”和“Timing using Fast Timing Model”,分别代表可以在Quartus软件下实现功能仿真,时序仿真和快速时序仿真。

最后一项一般不选,如果在Settings->Timing Requirement->More Settings下“Report Combined Fast/Slow Timing”选项设为“On”,就可以选择最后一项。

编译的报告里也会分别列出最快和最慢的时序报告。

)3)选择“Processing”菜单下的“Generate Functional Simulation Netlist”命令,否则将无法启动仿真。

4)新建一个波形仿真文件,文件后缀名为.vwf。

选择File菜单下的New->Other Files->VectorWaveform File。

如下图所示,左边空白栏处是节点名的列表区,右边空白栏处是仿真波形的显示区。

波形编辑窗口默认时间为1us,如果想改变仿真时间,可以选择Edit菜单下End Time,在弹出的对话框中选择需要的时间。

将新建的波形仿真文件保存下来。

5)将需要仿真的信号加入波形编辑窗口。

在列表区任一位置双击或者点击右键选择“InsertNode or Bus…”,弹出的对话框点击“Node Finder”按钮。

在“Node Finder”界面中点击“List”按钮,有关信号的列表会出现在界面的左边,双击需要观察的信号加入至界面右边。

如果工程中用到了很多信号,在左边列表中也会显示很多(Named编辑框默认的是*通配符),可以在Named编辑框中添加需要的信号名称实现模糊查找。

Modelsim使用说明

Modelsim 使用简明指南1 前言作为一种简单易用,功能强大的逻辑仿真工具,Modelsim 具有广泛的应用。

这里对ModelSim 作一个入门性的简单介绍。

首先介绍ModelSim 的代码仿真,然后介绍门级仿真和时序验证。

和时序验证。

2 代码仿真在完成一个设计的代码编写工作之后,可以直接对代码进行仿真,检测源代码是否符合功能要求。

这时,仿真的对象为HDL 代码,比较直观,速度比较快,可以进行与软件相类似的多种手段的调试(如单步执行等)。

在设计的最初阶段发现问题,在设计的最初阶段发现问题,可以节省大量的精力。

可以节省大量的精力。

2.1 代码仿真需要的文件1.设计HDL 源代码:源代码:新建一个“文本文档”文件,在记事本中输入HDL 源代码,使用V erilog 语言编程。

语言编程。

2.测试激励代码:.测试激励代码:在同一个文件中,根据设计要求输入/输出的激励程序,由于不需要进行综合,书写具有很大的灵活性。

有很大的灵活性。

3.保存该文件后退出,然后重命名该文件,.保存该文件后退出,然后重命名该文件,使该文件后缀名由使该文件后缀名由.txt 变为.v 。

如:t81.v 。

4. 该文件保存在你所建立的工作目录中,如:D\VLSItext\t1如果要修改该文件,仍然可以选择用仍然可以选择用记事本记事本打开编辑再保存,记事本相当于是一源代码输入软件。

输入软件。

注:所有的文件名及目录名均要求是英文,无中文字符。

2.2 代码仿真步骤1.建立工程:在ModelSim 中建立Project 。

如图2.1所示,点击File ðNew ðProject ,得到Creata Project 的弹出窗口,如图2.2所示。

在Project Name 栏中填写你的项目名字,建议和你的顶层文件名字一致,如t81。

Project Location 是你的项目目录,你可通过Brose 按钮来选择或改变,建议项目目录选择为你所保存源代码的目录,如:D\VLSItext\t1。

如何在ModelSim里仿真Altera的lpm_rom文件

如何在ModelSim里仿真Altera的lpm_rom文件

By ChinaLeo on July 1st, 2005

<这里我使用的是QuartusII5.0和ModelSim SE Plus 6.0>

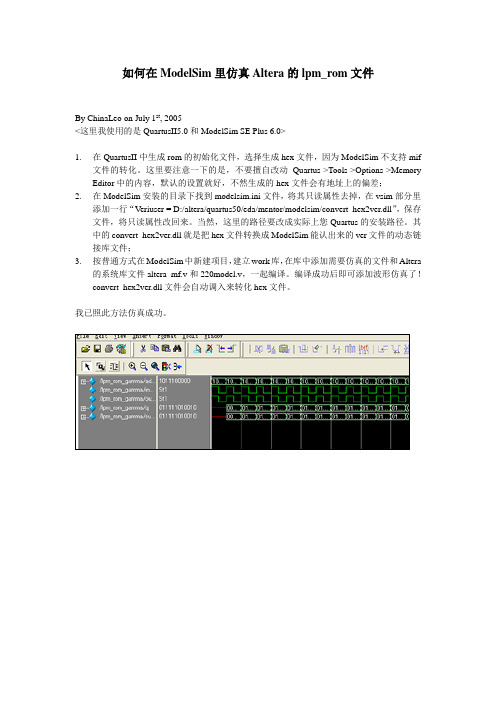

1.在QuartusII中生成rom的初始化文件,选择生成hex文件,因为ModelSim不支持mif

文件的转化。

这里要注意一下的是,不要擅自改动Quartus->Tools->Options->Memory Editor中的内容,默认的设置就好,不然生成的hex文件会有地址上的偏差;

2.在ModelSim安装的目录下找到modelsim.ini文件,将其只读属性去掉,在vsim部分里

添加一行“Veriuser = D:/altera/quartus50/eda/mentor/modelsim/convert_hex2ver.dll”,保存文件,将只读属性改回来。

当然,这里的路径要改成实际上您Quartus的安装路径。

其中的convert_hex2ver.dll就是把hex文件转换成ModelSim能认出来的ver文件的动态链接库文件;

3.按普通方式在ModelSim中新建项目,建立work库,在库中添加需要仿真的文件和Altera

的系统库文件altera_mf.v和220model.v,一起编译。

编译成功后即可添加波形仿真了!

convert_hex2ver.dll文件会自动调入来转化hex文件。

我已照此方法仿真成功。

modelsim+ISE后仿真流程

一、为modelsim 添加ISE的3 个仿真库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

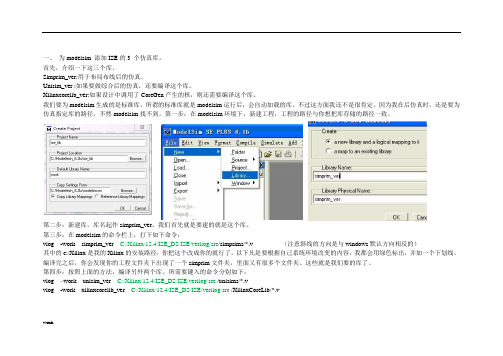

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src/simprims/*.v (注意斜线的方向是与windows默认方向相反的)其中的c:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

以下凡是要根据自己系统环境改变的内容,我都会用绿色标出,并加一个下划线。

编译完之后,你会发现你的工程文件夹下出现了一个simprim文件夹,里面又有很多个文件夹。

这些就是我们要的库了。

第四步:按照上面的方法,编译另外两个库。

所需要键入的命令分别如下:vlog –work unisim_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src /unisims/*.vvlog -work xilinxcorelib_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src /XilinxCoreLib/*.v第五步:把库建好后,接下来的事情就是使它成为modelsim的标准库。

这只要修改modelsim安装目录下的modelsim.ini文件就可以了。

EDK工程ModelSim仿真流程

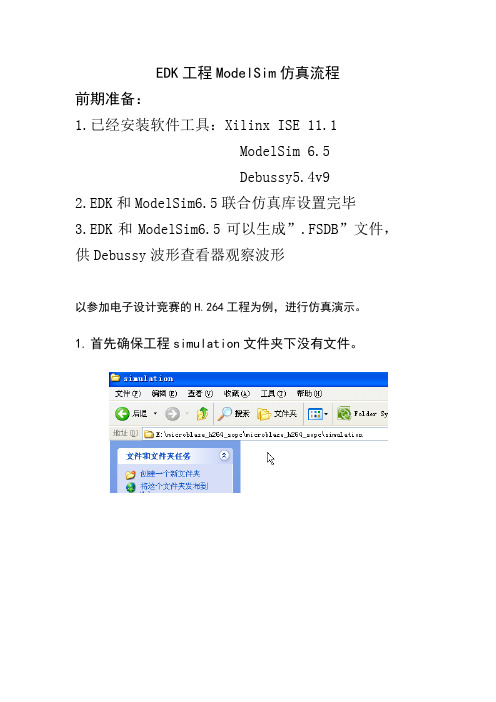

EDK工程ModelSim仿真流程前期准备:1.已经安装软件工具:Xilinx ISE 11.1ModelSim 6.5Debussy5.4v92.EDK和ModelSim6.5联合仿真库设置完毕3.EDK和ModelSim6.5可以生成”.FSDB”文件,供Debussy波形查看器观察波形以参加电子设计竞赛的H.264工程为例,进行仿真演示。

1.首先确保工程simulation文件夹下没有文件。

2.如果有文件,要通过如下方式清除,不能直接删除。

3.清除后,点击Simulation Generate Simulation HDLFiles,重新生成工程仿真的库文件。

Console控制台显示生成了Simulation ModelSimulation文件夹下生成了一堆文件。

4.在Simulation文件夹下,找到“system_tb.v”文件,打开,添加如下语句initial begin$dumpfile("aa.fsdb");$dumpvars;end以便仿真时,生成fsdb文件。

5.返回XPS界面,选择Simulation->Launch HDL Simulator,通过这种方式,打开了ModelSim6.5软件6.打开了ModelSim6.5软件,如下图所示7.打开Simulation文件夹中的system_setup.do文件,该文件中存放了系统生成的仿真脚本语句。

8.返回ModelSim6.5,在命令行下先输入“do system.do”命令。

9.输入如下命令“vsim -novopt -t ps D:/modeltech_6.5/win32/novas.dll -Lxilinxcorelib_ver -L secureip -L unisims_ver +notimingchecks system_tb glbl”理由(复制system_setup.do文件中第二条脚本语句”vsim -novopt -t ps -L xilinxcorelib_ver -L secureip -L unisims_ver +notimingchecks system_tb glbl”,注意到要仿真生成fsdb波形文件,所以在ps和-L前添加一条新的语句”D:/modeltech_6.5/win32/novas.dll”,要链接这个“novas.dll”动态链接文件。

modelsim使用教程

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

modelsim的详细使用方法

一、简介ModelSim是一款由美国Mentor Graphics公司推出的集成电路仿真软件,广泛应用于数字电路和系统设计领域。

它提供了强大的仿真和验证功能,能够帮助工程师快速高效地进行电路设计与验证工作。

本文将详细介绍ModelSim的使用方法,以帮助读者更好地掌握这一工具的操作技巧。

二、安装与配置1. 下载ModelSim安装包,并解压到指定目录2. 打开终端,进入ModelSim安装目录,执行安装命令3. 安装完成后,配置环境变量,以便在任何目录下都能够调用ModelSim程序4. 打开ModelSim,进行软件注册和授权,确保软件可以正常运行三、工程创建与管理1. 新建工程:在ModelSim主界面点击“File” -> “New” -> “Project”,输入工程名称和存储路径,选择工程类型和目标设备,点击“OK”完成工程创建2. 添加文件:在工程目录下右键点击“Add Existing”,选择要添加的源文件,点击“OK”完成文件添加3. 管理工程:在ModelSim中可以方便地对工程进行管理,包括文件的增删改查以及工程参数的设置等四、代码编写与编辑1. 在ModelSim中支持Verilog、VHDL等多种硬件描述语言的编写和编辑2. 在ModelSim主界面点击“File” -> “New” -> “File”,选择要新建的文件类型和存储位置,输入文件名称,点击“OK”完成文件创建3. 在编辑器中进行代码编写,支持代码高亮、自动缩进、语法检查等功能4. 保存代码并进行语法检查,确保代码符合规范,没有错误五、仿真与调试1. 编译工程:在ModelSim中进行代码编译,生成仿真所需的可执行文件2. 设置仿真参数:在“Simulation”菜单下选择“S tart Simulation”,设置仿真时钟周期、输入信号等参数3. 运行仿真:点击“Run”按钮,ModelSim将开始对设计进行仿真,同时显示波形图和仿真结果4. 调试设计:在仿真过程中,可以通过波形图和仿真控制面板对设计进行调试,查找并解决可能存在的逻辑错误六、波形查看与分析1. 查看波形:在仿真过程中,ModelSim会生成相应的波形文件,用户可以通过“Wave”菜单查看波形并进行波形分析2. 波形操作:支持波形的放大、缩小、平移、选中等操作,方便用户对波形进行分析和观察3. 波形保存:用户可以将波形结果保存为图片或文本文件,以便日后查阅和分析七、性能优化与验证1. 时序优化:在设计仿真过程中,可以通过观察波形和性能分析结果,对设计进行优化,提高设计的时序性能2. 逻辑验证:通过对仿真的结果进行逻辑验证,确保设计符合预期的逻辑功能3. 时序验证:对设计的时序性能进行验证,确保信号传输和时钟同步的正确性八、项目输出与文档整理1. 输出结果:在仿真和验证完成后,可以将仿真结果、波形图和性能分析结果输出为文本文件或图片,方便后续的文档整理和报告撰写2. 结果分析:对仿真结果和验证结果进行详细的分析,确定设计的性能和功能是否符合设计要求3. 文档整理:根据仿真和验证结果,进行文档整理和报告撰写,为后续的设计和优化工作提供参考九、总结与展望ModelSim作为一款专业的集成电路仿真软件,具有着强大的功能和丰富的特性,可以帮助工程师进行电路设计与验证工作。

使用ModelSim的仿真步骤

使用ModelSim的仿真步骤:

1.建立工程:选file/new/project菜单,打开Create Project窗口.

填Project Name栏,为你的工程启一个名子.

按Browse按纽,为你的工程指定一个盘上目录,作为以后工程文件的存放位置.

指定缺省库名为Work库.

2.在出现的ADD ITEMS TO THE PROJECT窗口中选Create New File为当前工程加入一个新建文件,或选Add existing File为当前工程加入一个已存在的文件.

3.选Compile/compile All对当前设计工程进行编译.

4.选Simulate/Star Simulation菜单项,打开仿真器.

5.在仿真器中选Design页,点击WORK页前的加号,打开WORK 库,选一个仿真文件,选好后,点击右下脚的OK按纽.

6.在出现的Object窗口中,会有芯片的引脚列表.选一个引脚,压鼠标右键,弹出一菜单,在其中选Add to wave/Selected Signal菜单项,可将引脚对象加入到Wave窗口中.重复上述过程,将全部引脚加入到Wave波形窗口中.

7.在WAVE中,选一个引脚,用WAVE窗口的工具画加在引脚上的波形.

8.画完输入引脚的波形后,输入RUN –ALL,回车,执行仿真.

注:上述仿真过程,可用命令:

vsim work.filename

启动仿真窗口.

view wave

打开波形窗口

add wave –dec *

加入所有波形信号,以十进制方式force

为每个引脚加入驱动信号

run –all

执行仿真任务。

Modelsim简单教程.

Modelsim入门技术文档单位:深圳大学EDA中心实验室指导老师:徐渊作者:陈战夫rshamozhihu@时间:2010-1-7说明:本文档作为EDA中心研究生modelsim入门用。

分三个章节阐述。

1.modelsim中库的编译1.自己新建一个文件夹,如D:\modelsimpro\counter,将counter.v与counter_tb.v文件拷贝到该文件夹下。

2.点击modelsim的图标,打开modelsim的界面窗口。

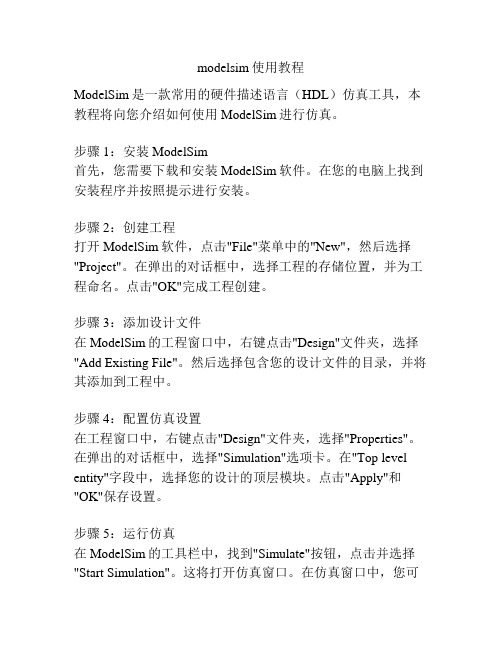

3.选择File > Change Directory,选择步骤1中的目录,点击OK。

4.选择File > New > Library。

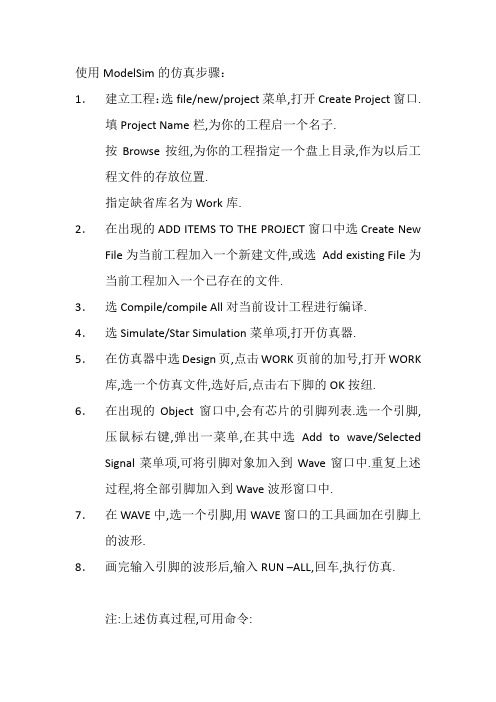

5.在library name与library physical name两栏中均填work.点击OK。

(在transcript窗口中可看到vlib workvmap work work)。

6.选择Compile > Compile,出现如下窗口。

同时选中counter.v与counter_tb.v两个文件。

7.点击compile.再点击done.8.在library标签点击work库前面的“+”号,可看到counter.v与counter_tb.v均在其目录下。

9.双击counter_tb.v可将该设计装载到本次工程库中。

10.选择View > Debug Windows >wave.将弹出波形窗口。

11.在workspace窗口下点击sim标签。

12.右击counter_tb.v,在出现的菜单中选择Add > Add to Wave。

13.在transcript窗口中VSIM>后敲入run 1000.则系统将仿真1000ns.我们可根据波形查看仿真结果。

14.在workspace窗口中点击files标签,鼠标左键双击counter.v,打开counter.v文件。

15.在第10行数字10旁鼠标左键点击一下,可出现一小红点,即断点。

(原创)在ModelSim里仿真Altera的lpm_rom文件的实践 (已经阅读)

在前面转载的《在ModelSim里仿真Altera的lpm_rom文件》一文广泛流传于网络。

经过本人最近时间的实践,对其中一些不正确或者说已经落伍了的地方进行修正。

1. 在QuartusII中生成rom的初始化文件,可以是hex,也可以是mif。

MIF 文件的格式很简单明了,所以我一向都是用MIF。

2.下载convert_hex2ver.dll文件,convert_hex2ver.dll就是把hex文件转换成ModelSim 能认出来的ver文件的动态链接库文件。

新版本的QuartusII中已经不带此文件了。

需要在网上找一份。

(老版本的软件里带了此文件(路径:quartusXX/eda/mentor/modelsim/),应当可以用。

)

3.将convert_hex2ver.dll文件放在modelsim安装路径的win32目录下;

4. 在ModelSim安装的目录下找到 modelsim.ini文件,将其只读属性去掉,在“; List of dynamically loaded objects for Verilog PLI applications,”后填入一行“Veriuser = convert_hex2ver.dll”。

保存文件,将只读属性改回来。

Over!祝你好运!

补丁:看到楼下网友留言不能仿真ROM,在这里再增加一条

5.需要将MIF文件复制到ModelSim仿真工程的文件夹下!你运行一次编译和仿真后,会看到自动生成的.ver文件,该文件名同你的MIF文件。

ModelSim的前后仿真(Quartus)

利用Quartus5.0实现功能仿真1)打开一个工程文件。

2)打开Settings设置栏,选择Fitting Settings下的Simulator栏。

在右边出现的设置栏中将“Simulation Mode”的下拉菜单选择“Functional”,即可以实现软件下的功能仿真。

(下拉菜单中有“Functional”、“Timing”和“Timing using Fast Timing Model”,分别代表可以在Quartus软件下实现功能仿真,时序仿真和快速时序仿真。

最后一项一般不选,如果在Settings->Timing Requirement->More Settings下“Report Combined Fast/Slow Timing”选项设为“On”,就可以选择最后一项。

编译的报告里也会分别列出最快和最慢的时序报告。

)3)选择“Processing”菜单下的“Generate Functional Simulation Netlist”命令,否则将无法启动仿真。

4)新建一个波形仿真文件,文件后缀名为.vwf。

选择File菜单下的New->Other Files->V ectorWaveform File。

如下图所示,左边空白栏处是节点名的列表区,右边空白栏处是仿真波形的显示区。

波形编辑窗口默认时间为1us,如果想改变仿真时间,可以选择Edit菜单下End Time,在弹出的对话框中选择需要的时间。

将新建的波形仿真文件保存下来。

5)将需要仿真的信号加入波形编辑窗口。

在列表区任一位置双击或者点击右键选择“InsertNode or Bus…”,弹出的对话框点击“Node Finder”按钮。

在“Node Finder”界面中点击“List”按钮,有关信号的列表会出现在界面的左边,双击需要观察的信号加入至界面右边。

如果工程中用到了很多信号,在左边列表中也会显示很多(Named编辑框默认的是*通配符),可以在Named编辑框中添加需要的信号名称实现模糊查找。

Modelsim6.5基本仿真步骤

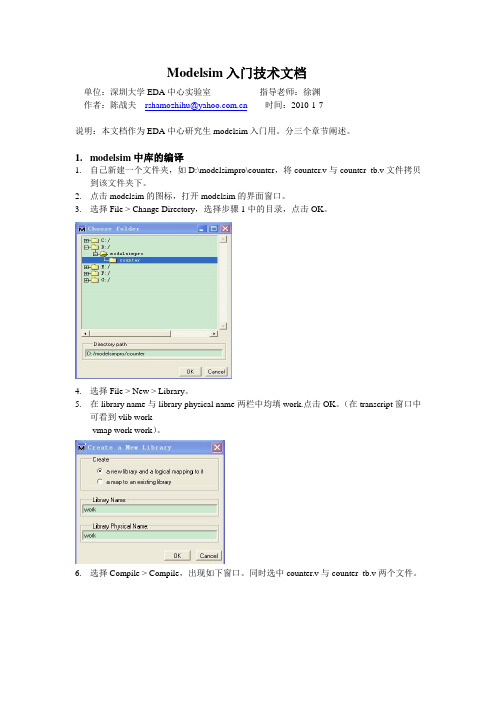

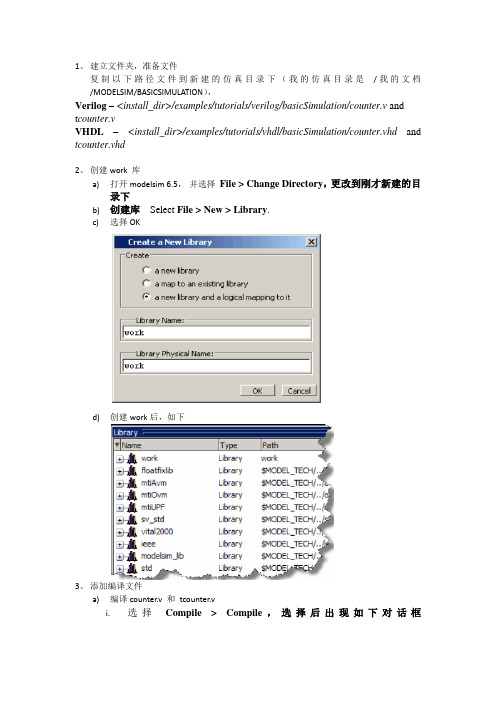

复制以下路径文件到新建的仿真目录下(我的仿真目录是/我的文档/MODELSIM/BASICSIMULATION),

Verilog–<install_dir>/examples/tutorials/verilog/basicSimulation/counter.vand tcounter.v

a)在主窗口中选择Simulate > End Simulation

b)输入命令vsim -novopt counter

14、打开之前生成的波形文件

a)输入view wave

b)选择File > Load

c)双击waveedit.do文件

15、导出刚才创建的波形

a)第一种是导出格式为HDL格式的test bench文件。

i.File > Export > Waveform

ii.选择Verilog Testbench(你用什么就选什么)

iii.如果必要的话输入1000for End Time

iv.在文件名中输入“export”然后点OK

v.

vi.通过以上步骤,modelsim就根据波形自动创建了一个名为export.v的test bench文件。

*/

for (i = 4'b0; ((carry == 4'b1) && (i <= 7)); i = i+ 4'b1)

begin

increment[i] = val[i] ^ carry;

carry = val[i] & carry;

end

end

endfunction

always @ (posedge clk or posedge reset)

Modelsim仿真流程-经验总结

Modelsim仿真流程-经验总结Modelsim仿真流程-经验总结1.Modelsim简介略。

2.modelsim仿真流程:modelsim基本的仿真流程包括建立库、建立工程并编译、仿真、调试、但在libero环境中运行modelsim时,软件自动映射库和生成工程文件。

其中功能仿真、综合仿真以及后仿真分别映射presynth、postsynth和postlayout库。

基本流程是:建立工作库→编译源代码→启动仿真→分析、调试。

2.1建立库并映射在modelsim中,任何使用VHDL、Verilog HDL、SystemC等语言实现的设计,都被编译到一个库中。

方法一:File>New>Library选择新建并映射到该库;方法二:在modelsim>提示符下运行命令vlib work2-建立库,vmap work work2-建立映射库;2.2建立工程Modelsim仿真需要建立自己的工程,同时modelsim还提供了文件夹管理工程的功能。

step1:File>New>project,并指定库文件名;step2:新建文件或导入文件;2.3编译文件建立好工程后,使用compile功能对源文件进行编译。

Libero环境启动modelsim时,系统执行run.do脚本文件自动编译源文件。

鼠标右击文件,选择compile All对所有的工程文件执行编译操作;?启动仿真,使用simulation>start simulation>选择design选项卡功能使modelsim进入仿真状态,之后可以运行仿真。

在libero 环境下,运行modelsim直接从运行仿真这一步骤开始。

运行仿真可以设置仿真时间或选择仿真全部tcl命令:do run.do –当设计修改后,使用此命令重新导入设计;Do wave.do-打开波形列表文件,或者向当前波形添加列表;Restart-复位当前仿真,从0时刻重新仿真;Run 1ms-运行仿真1ms时间;Run all-运行全部的仿真;在libero环境下,可以自己编写脚本文件代替run.do文件,在项目比较大的情况下可以大大简化仿真的操作。

modelsim后仿真过程

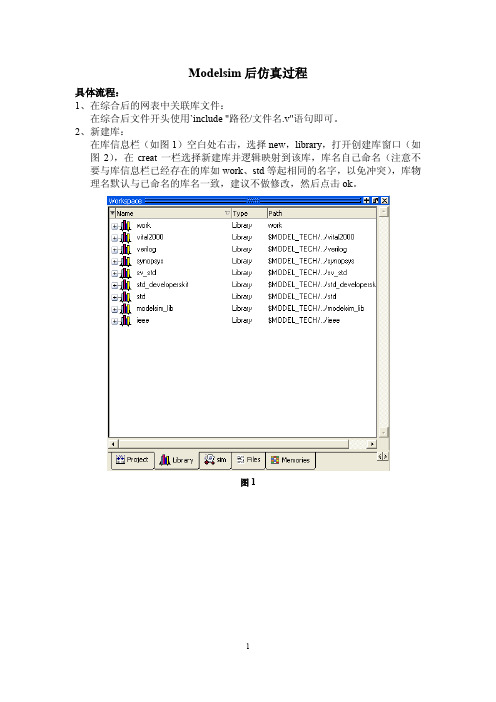

Modelsim后仿真过程具体流程:1、在综合后的网表中关联库文件:在综合后文件开头使用`include "路径/文件名.v"语句即可。

2、新建库:在库信息栏(如图1)空白处右击,选择new,library,打开创建库窗口(如图2),在creat一栏选择新建库并逻辑映射到该库,库名自己命名(注意不要与库信息栏已经存在的库如work、std等起相同的名字,以免冲突),库物理名默认与已命名的库名一致,建议不做修改,然后点击ok。

图1图23、设置文件编译到新建库:在project信息栏(如图3)空白处右击,选择properties,打开工程编译设置窗口(如图4),Do Not Compile不选;点击Compile to library旁边的倒三角,选择自己已新建的库;Place in Folder同样点击旁边的倒三角选择,一般都是默认顶层;然后点击ok。

图3图44、编译与仿真:编译步骤1中所得的综合后的网表文件,并进行仿真,其过程与前仿过程一样,这里不再赘述,但注意此时仿真时要在自己新建的库中找欲仿真模块,与前仿时在work中找欲仿真模块是同样的过程。

疑点回答:(1)`include "路径/文件名.v"中的路径可以是绝对路径,也可以是相对路径,若库文件(.v文件)与综合后的网表文件在同一路径下,则路径可以省略,即为`include "文件名.v"。

(2)在综合后的网表中添加库文件的目的是将他们“关联”成一个文件,这样编译时就可以识别综合后的网表中调用的库元件,也就是实现了库的调用。

(3)我们新建的库只是一个空的可存储编译信息的库类型文件包,并不是实际的引入了库,其目的就是用来存放已关联库文件的综合后的网表的编译信息,至于与实际库信息的关联是通过网表关联实现的;而其他自带的库(work库除外,其用于存放前仿编译信息,也是空的,不含任何库信息)比如std等都是实际存在的,若不新建,直接在这些库中编译会造成不必要的麻烦。

modelsim仿真详细过程(功能仿真与时序仿真)

序,这样比较方便些。软件自带的编辑环境不是很好,使用第三方的编辑工

具是推荐的方法。建议使用UltraEdit或Notepad++这些专业的代码编辑软

件。

UltraEdit偏重于功能的强大和丰富的用户可定制化特性,而

Notepad++更加注重易用性。两者在普通功能上差异不是特别大,根据自己的

喜好选择一款即可。

图5给工程中添加文件

在路径G:\FPGA_Project\ModelSim\counter8下新建两个文件,一个

是counter8.v,一个是test_counter8.v,前者是我们的原始的设计文件,后者

是其相应的仿真测试文件。在这个路径的Windows目录下,在空白处右键选

择新建一个文本文档.TXT格式,然后在这个文件上右键选择UltraEdit或Edit

modelsim仿真详细过程(功能仿真与时序仿真)

ModelSim仿真入门:功能仿真

本实验的目的就是在ModelSim环境下学习掌握该软件的一般仿真测

试流程和仿真测试方法,另外学习编写简单的Test Bench程序并在ModelSim

下进行调试。

实验步骤如下:

1.打开ModelSim软件,如图1所示:

withNotepad++就可以启动相应的代码编辑工具进行编辑了,保存的时候注意

存成.v或格式即可。

新建一个工程,在弹出的对话框中,给该工程命名并指定一个存放的路径,

如图4所示:

图4新建工程

在这里,工程名和你的顶层文件名保持一致是推荐的做法。路径的注

意事项已经说过,这里不再提及。默认的库名就是work,这个无需更改,点

ModelSim后仿真 详细流程介绍

目录

仿真的基本概念

后仿真前的基本准备工作

后仿真的基本操作步骤

后仿真的基本操作步骤

时序仿真的流程

所用例子:divider_module.v

1.新建一个project,建立divider_module工程,建立work工作库,把 quartus II综合后的simulation文件夹里的几个文件一起复制到当前工 程目录下,向工程添加三个文件——divider_module.v, divider_module_tb.v 和 divider_module.vo,如下图所示。

仿真的基本概念

布局布线后仿真(时序仿真)

功能仿真VS布局布线后仿真

仿真的基本概念

布局布线后仿真(时序仿真)

输入文件

1

设计源代码和 testbench激励 文件

2

从布局布线结 果中抽象出来 的门级网表 (.vo文件)

3

扩展名为 SDO 或 SDF 的标准时延 文件(一般用 Quartus生成 的.sdo文件)

后仿真前的基本准备工作

Altera仿真库建立步骤

4.同样的方法步骤编译altera_device器件库。在编译这个库时选择 的文件为一些器件文件如图所示。当然为了加快编译速度,也可以 选择只用到的器件库文件。

后仿真前的基本准备工作

Altera仿真库建立步骤

5.编译库结束后,为了在每次新建工程的时候不需要重新编译 Altera的仿真库,需要修改Modelsim的安装目录下的modelsim.ini文 件。

仿真验证是FPGA设计过程中非常重要的一个环节,大家不要忽略。

仿真验证工作占设计总工作量的70% “在这个设计规模达数百万门的ASIC、可复用的知识产权(IP)和系统芯片(SOC) 的时代,仿真验证占到了设计总工作量的70%左右。设计团队应该配备能够正确描述 仿真验证需求的工程师和专门进行验证的工程师。仿真验证工程师的数量甚至是RTL 设计人员的两倍。” ----《Writing Testbenches》 【美】Janick Bergeron