用CPLD制作的电子闹钟

基于CPLD的数字电子钟设计报告

目录引言 (3)一:VHDL的概述 (3)第一章各模块设计 (6)一设计要求及目的 (6)1.1 设计要求 (6)1.2 目的 (6)二各程序模块设计说明及仿真 (6)2.1 60进制计数器 (6)2.2 24进制计数器: (9)2.3 8进制计数器: (11)2.4 花样闹钟: (13)第二章设计过程及结论 (19)一设计过程: (19)二测试及结论: (20)三学习心得: (20)内容简要本次CPLD课程学习的主要任务是灵活地运用CPLD相关知识、基本的VHDL硬件描述语言编程得到我们想要的器件以实现我们所预期的功能,最终设计出产品——数字电子钟。

实现的基本功能是时、分、秒在数码管上的显示和分钟、小时的校准,扩展部分有以下几点:整点报时、定时闹钟、定时花样闹钟。

引言一:VHDL的概述硬件描述语言(hardware description language,HDL)是电子系统硬件行为描述、结构描述、数据流描述的语言。

目前,利用硬件描述语言可以进行数字电子系统的设计。

随着研究的深入,利用硬件描述语言进行模拟电子系统设计或混合电子系统设计也正在探索中。

国外硬件描述语言种类很多,有的从Pascal发展而来,也有一些从C语言发展而来。

有些HDL成为IEEE标准,但大部分是企业标准。

VHDL来源于美国军方,其他的硬件描述语言则多来源于民间公司。

可谓百家争鸣,百花齐放。

这些不同的语言传播到国内,同样也引起了不同的影响。

在我国比较有影响的有两种硬件描述语言:VHDL语言和Verilog HDL语言。

这两种语言已成为IEEE标准语言。

电子设计自动化(electronic design automation,EDA)技术的理论基础、设计工具、设计器件应是这样的关系:设计师用硬件描述语言HDL描绘出硬件的结构或硬件的行为,再用设计工具将这些描述综合映射成与半导体工艺有关的硬件配置文件,半导体器件FPGA则是这些硬件配置文件的载体。

基于CPLD的数字时钟设计

CPLD课程学习报告学生姓名:熊军同组者姓名:黄辉CPLD的全称是Complex Programmable Logic Device (即复杂可编程器件),但本次试验所使用的器件并不是CPLD而是FPGA,FPGA的全称是Field Programmable Gate Array (即现场可编程门阵列)。

FPGA与CPLD有很多相似点,它们都是可编程数字逻辑器件,都在时序逻辑电路和组合逻辑电路中有很强的优势。

它们的区别在于,FPGA的容量大、速度慢且不可预测、掉电信息丢失,二CPLD容量小、速度快且有很好的可预测性、掉电信息不丢失。

CAD 的全称是Computer Aided Design(即计算机辅助设计)。

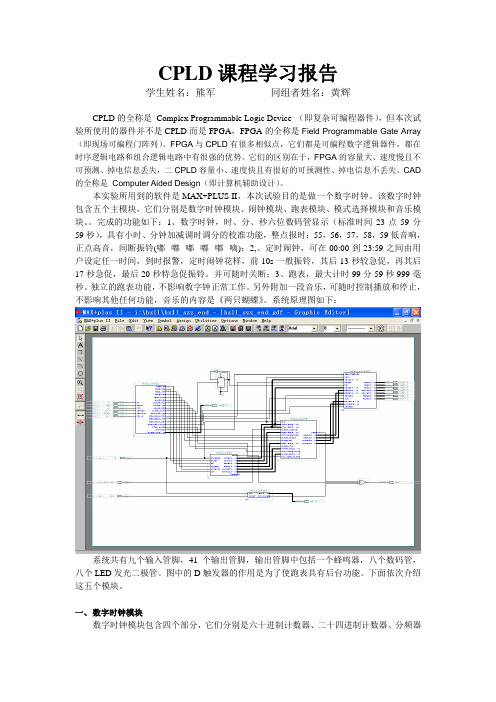

本实验所用到的软件是MAX+PLUS II,本次试验目的是做一个数字时钟。

该数字时钟包含五个主模块,它们分别是数字时钟模块、闹钟模块、跑表模块、模式选择模块和音乐模块。

完成的功能如下:1、数字时钟,时、分、秒六位数码管显示(标准时间23点59分59秒),具有小时、分钟加减调时调分的校准功能,整点报时:55,56,57,58,59低音响,正点高音,间断振铃(嘟--嘟--嘟--嘟--嘟--嘀);2,、定时闹钟,可在00:00到23:59之间由用户设定任一时间,到时报警,定时闹钟花样,前10s一般振铃,其后13秒较急促,再其后17秒急促,最后20秒特急促振铃。

并可随时关断;3、跑表,最大计时99分59秒999毫秒。

独立的跑表功能,不影响数字钟正常工作。

另外附加一段音乐,可随时控制播放和停止,不影响其他任何功能,音乐的内容是《两只蝴蝶》。

系统原理图如下:系统共有九个输入管脚,41个输出管脚,输出管脚中包括一个蜂鸣器,八个数码管,八个LED发光二极管。

图中的D触发器的作用是为了使跑表具有后台功能。

下面依次介绍这五个模块。

一、数字时钟模块数字时钟模块包含四个部分,它们分别是六十进制计数器、二十四进制计数器、分频器和整点报时控制器。

CPLD大作业--电子时钟43进制(两种实现方法)

CPLD大作业报告——电子时钟设计姓名:班级:控制专研-15学号:实验日期:2015年12月15日一、实验内容:1.使用CPLD设计电子钟电路框图,并对主要功能进行解释;2.设计小时、分、秒处理功能模块的VHDL程序;二、实验要求:1.编写小时、分、秒处理功能模块编程。

2.对仿真图形进行分析,对关键处的时序进行解释。

3.每个人的小时、分、秒数都不同。

根据任务布置,本设计的小时、分、秒数分别为24、43、43。

三、模块设计1. 一个模块实现的数字钟设计方案(1)时钟VHDL源程序LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY clk43 ISPORT(CLRN,LDN,EN,CLK : IN STD_LOGIC;Sa, Ma, Ha : IN INTEGER RANGE 0 TO 9;Sb, Mb : IN INTEGER RANGE 0 TO 4;Hb : IN INTEGER RANGE 0 TO 2;QSa,QMa,QHa : OUT INTEGER RANGE 0 TO 9;QSb,QMb : OUT INTEGER RANGE 0 TO 4;QHb : OUT INTEGER RANGE 0 TO 2);END clk43;ARCHITECTURE a OF clk43 ISBEGINPROCESS (CLK)V ARIABLE tmpsa,tmpma,tmpha : INTEGER RANGE 0 TO 9;V ARIABLE tmpsb, tmpmb : INTEGER RANGE 0 TO 4;V ARIABLE tmphb : INTEGER RANGE 0 TO 2;BEGINIF CLRN='0' THENtmpsb := 0; tmpsa := 0;tmpmb := 0; tmpma := 0;tmphb := 0; tmpha := 0;ELSEIF (CLK'event AND CLK='1') THENIF LDN='0' THENtmpsa:=Sa; tmpsb:=Sb; tmpma:=Ma; tmpmb:=Mb;tmpha:=Ha; tmphb:=Hb;ELSIF EN='1' THENIF (tmpsb=4 AND tmpsa=2 AND tmpmb=4 ANDtmpma=2) THENIF (tmphb=2 AND tmpha=3) THENtmpha:=0; tmphb:=0 ;ELSIF tmpha=9 THENtmpha:=0; tmphb:=tmphb+1;ELSE tmpha:=tmpha+1;END IF;END IF;IF (tmpsb=4 AND tmpsa=2) THENIF (tmpmb=4 AND tmpma=2) THENtmpmb:=0; tmpma:=0;ELSIF tmpma=9 THENtmpma:=0;tmpmb:=tmpmb+1;ELSE tmpma:=tmpma+1;END IF;END IF;IF (tmpsb=4 AND tmpsa=2) THENtmpsa:=0;tmpsb:=0;ELSIF tmpsa=9 THENtmpsa:=0;tmpsb:= tmpsb+1;ELSE tmpsa := tmpsa+1;END IF;END IF;END IF;END IF;QSa<=tmpsa; QSb<=tmpsb;QMa<=tmpma; QMb<=tmpmb;Qha<=tmpha; Qhb<=tmphb;END PROCESS ;END a;以上程序实现了,用统一化整体模块完成了对时钟的时、分、秒的相应的进制设计。

基于CPLD的多功能数字时钟

前言我们已经进入了数字化和信息化的时代,其特点是各种数字产品的广泛应用。

现代数字产品在性能提高、复杂度增大的同时,其更新换代的步伐也越来越快,实现这种进步的因素在于生产制造技术和电子设计技术的进步。

CPLD器件和EDA技术的出现,改变了这种传统的设计思路,使人们可以立足于CPLD芯片来实现各种不同的功能,新的设计方法能够由设计者自己定义器件内部逻辑和管脚,将原来由电路板设计完成的工作大部分放在芯片的设计中进行。

这样不仅可以通过芯片设计实现各种逻辑功能,而且由于管脚定义的灵活性,减轻了原理图和印制板设计的工作量和难度,增加了设计的自由度,提高了效率。

同时这种设计减少了所需芯片的种类和数量,缩小了体积,降低了功耗,提高了系统的可靠性。

目录前言 (1)一、设计内容和要求 (3)1. 设计一个数字钟,具有计时,校时,闹钟和整点报时的功能。

(3)二、实验环境 (4)1. 软件环境 (4)2. 硬件环境 (4)三、系统设计方案的确定 (5)1. 结构框图 (5)2. 总体思路 (5)1) 总体电路图 (6)2) 校时模块 (7)3) 时钟模块 (9)4) 闹钟模块 (11)5) 闹钟计数器模块 (14)6) 报时模块 (16)7) MODE按键模块 (16)四、仿真与引脚锁定 (18)1. 仿真 (18)2. 引脚锁定 (18)小结 (24)参考文献 (25)一、设计内容和要求1. 设计一个数字钟,具有计时,校时,闹钟和整点报时的功能。

基本要求:1)计时功能采用24小时方式,显示小时、分钟和秒;2)采用双键调整法,MODE和SET。

3)MODE按键用于模式选择,包括时钟数码管模块显示。

计时模块数码管显示,包括计时、秒校时、分校时和小时校时;闹钟模块数码管显示,包括闹钟校时和校分。

4)SET作为校时脉冲;5)结果用6个数码管显示和一个蜂咛器;6)用VHDL语言编程实现系统功能;7)在Quartus II环境中编译、仿真通过,并得到正确的波形;8)在实验系统上下载成功并有正确的结果;9)完成相应的实训报告。

cpld时钟

CPLD课程学习报告CPLD 课程是一门实践性非常强的课程,它要求我们运用基本的VHDL硬件描述语言编程得到我们想要的器件以实现我们所预期的功能。

这次CPLD课程学习的主要任务就是灵活地运用CPLD相关知识来设计一个数字电子钟,其基本要求是时、分、秒在数码管上的显示和小时、分钟的校准,扩展要求包括以下几点:1、整点报时:55,56,57,58,59低音响,正点高音,间断振铃(嘟--嘟--嘟--嘟--嘟--嘀)2、跑表:最大计时99分59秒999毫秒。

独立的跑表功能,不影响数字钟正常工作。

3、定时闹钟:可在00:00到23:59之间由用户设定任一时间,到时报警。

4、定时闹钟花样:前10s一般振铃,其后13秒较急促,再其后17秒急促,最后20秒特急促振铃。

并可随时关断。

5、其他(加减调时调分、音乐铃声等,越新奇越好)。

下面我就整个数字电子钟功能的实现过程做一一讲解。

首先,要完成一个最基本的时钟,首要任务就是编写两个计数器(24进制和60进制)。

60进制计数器的VHDL描述如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;ENTITY dl21_cnt60 isport(clk,reset,en:in bit;q0,q1:out std_logic_vector(3 downto 0); carry:out std_logic);end;architecture one of dl21_cnt60 issignal m0,m1:std_logic_vector(3 downto 0); beginprocess(clk,reset,en)beginif reset='1'then m0<="0000";m1<="0000"; elsif clk'event and clk='1' thenif en='0'thenif m0="1001" and m1="0101" thenm1<="0000";m0<="0000";carry<='1';elsif m0="1001" then m1<=m1+1;m0<="0000"; else m0<=m0+1;carry<='0';end if;end if;end if;end process;q0<=m0;q1<=m1;end;通过对程序的保存、创建项目、编译之后,我们可以得到下图所示的实体器件:60进制计数器到底我们做的这个60进制计数器对不对呢,它能不能达到我们想要的效果呢,下面让我们来用波形仿真试一试就知道了。

基于CPLD的VHDL语言数字钟(含秒表)

基于CPLD的VHDL语言数字钟(含秒表)设计利用一块芯片完成除时钟源、按键、扬声器和显示器(数码管)之外的所有数字电路功能。

所有数字逻辑功能都在CPLD器件上用VHDL语言实现。

这样设计具有体积小、设计周期短(设计过程中即可实现时序仿真)、调试方便、故障率低、修改升级容易等特点。

本设计采用自顶向下、混合输入方式(原理图输入—顶层文件连接和VHDL语言输入—各模块程序设计)实现数字钟的设计、下载和调试。

一、功能说明已完成功能1.完成秒/分/时的依次显示并正确计数;2.秒/分/时各段个位满10正确进位,秒/分能做到满60向前进位;3.定时闹钟:实现整点报时,又扬声器发出报时声音;4.时间设置,也就是手动调时功能:当认为时钟不准确时,可以分别对分/时钟进行调整;5.利用多余两位数码管完成秒表显示:A、精度达10ms;B、可以清零;C、完成暂停可以随时记时、暂停后记录数据。

待改进功能:1.闹钟只是整点报时,不能手动设置报时时间,遗憾之一;2.秒表不能向秒进位,也就是最多只能记时100ms;3.秒表暂停记录数据后不能在原有基础上继续计时,而是复位重新开始。

【注意】秒表为后来添加功能,所以有很多功能不成熟!二、设计方案1.数字钟顶层设计外部输入要求:输入信号有1kHz/1Hz时钟信号、低电平有效的秒/微秒清零信号CLR、低电平有效的调分信号SETmin、低电平有效的调时信号SEThour;外部输出要求:整点报时信号SOUND(59分51/3/5/7秒时未500Hz低频声,59分59秒时为1kHz高频声)、时十位显示信号h1(a,b,c,d,e,f,g)、时个位显示信号h0(a ,b,c,d,e,f,g)、分十位显示信号m1及分个位m0、秒十位s1及秒个位s0、微秒十位ms1及微秒个位ms0;数码管显示位选信号SEL0/1/2等三个信号。

2. 内部功能模块主要有:Fenp分频模块:主要是整点报时用的1kH与500Hz的脉冲信号,这里的输入信号是1KHz信号,所以只要一个二分频即可;时间基准采用1Hz输入信号直接提供(当然也可以分频取得,这里先用的是分频取得的信号,后考虑到精度问题而采用硬件频率信号。

CPLD数字钟实验报告

二、 实验目的

学会使用 Quartus Ⅱ这款 EDA 常用设计软件。 掌握在 Quartus Ⅱ中电路图的作法、仿真方法和作图技巧。 掌握 CPLD 实验箱的使用和电路的加载运行方法。 掌握动态扫描原理

三、 实验内容

(1)74LS160 的原理与功能 74LS160 为异步清零计数器,即 RD 端输入低电平,不受 CP 控制,输出端立

inst5

由于低位片可以自动清零,而高位片在 6 时则需要清零。因为清零时 6 的存 在非常短暂,故高位片的清零信号无法作为进位输出。

因此若需要进位信号则可以利用 QD 在清零前的高电平经过非门产生一个 上升沿输出。

下面是 74ls160 构成六十进制的波形图。

个位到 9 清零。

十位到 5 清零。

十位清零后产 生进位脉冲。

引出端符号:

TC

进位输出端

CEP

计数控制端

Q0-Q3

输出端

CET

计数控制

CP

时钟输入端(上升沿有效)

/MR 异步清除输入端(低电平有效)

/PE

同步并行置入控制端(低电 平有效)

功能表:

说明: H-高电平 L-低电平 X-任意

(2)下面是用 74LSl60 构成的六十进制计数器和模块功能示意图:

VCC

2qb inst7

ins t 6

(4)时、分、秒模块连接。

DigitalClock60

1clk

ins t 6

1qa 1qb 1qc 1qd 2qa 2qb 2qc 2qd 3clk

DigitalClock60

1clk

ins t 2

1qa 1qb 1qc 1qd 2qa 2qb 2qc 2qd 3clk

基于cpld的多功能数字钟的设计

第23卷 第3期2016年3月仪器仪表用户INSTRUMENTATIONEIC Vol.232016 No.3基于CPLD的多功能数字钟的设计车玮(西北师范大学 知行学院计算机与电子信息工程系,兰州 730070)摘 要:文中简述了一种基于CPLD的多功能数字钟的设计方案。

所有电路都固化在一片CPLD芯片中,电路结构简单、控制方便,资源利用率高,成本低,调试比较容易。

采用VHDL和原理图相结合的设计输入方式,在MAXPLUS II开发环境下完成设计、编译和仿真。

关键词:VHDL;可编程逻辑器件;MAXPLUS II中图分类号:TH 文献标识码:A 文章编号:1671-1041(2016)03-0016-04 Design of Multifuncton Digital Clock Based on CPLDChe Wei(Zhixing College, Northwest Normal University, Lanzhou, 730070, China)Abstract: This article briefly introuduces a design scheme of multifunctional digital clock based on CPLD. All circuits are cured in a CPLD chip. The circuit is simple in structure, easy to control, and has high resource utilization, low cost, which is easy to debug. The digital clock is designed,compiled as well as simulated under maxplus II development environment, applying the design input method of the scheme combining both VHDL and block diagram together.Key words: VHDL; CPLD; maxplus II0 前言复杂的可编程逻辑器件 (Complex Programmable Logic Divices,CPLD)是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。

基于CPLD和VHDL的数字钟的设计

基 于CP D和VHDL L 的数 字钟 的设 计

江 翠 云

( 武汉市交通学校 湖北 武汉 407 ) 304

[ 摘

要] 细介绍一 种基于C L 的数字 电子钟 的实现 。数字钟主 要部分 的片上 系统编程采 用V D 硬 件描述 语言实现 ;时 间显示采 用七位L D 详 PD HL E 数码 管显示 。该数

波 ,并持 续Z 秒 ,用于 驱动 外部 的 蜂呜器 。 O

C M O EN C U T I O PN T ON 5 S

字钟可直接 对时间 ‘ ’和 ‘ ’进 行修改校 正,还可实现 整点发声报 时。 分 秒

[ 关键 词 】 P D V D 数 字钟 C L H L

中图分类 号:T 4 文献标识码 :A 文章编 号:1 7 -7 9 2 1 )0 2 0 7 1 N 6 1 5 7( 0 0 1 0 1 —0

P R (,, : OT MN S

Y :

I SD L I : N T O C G

O T S D U T

—

LG C : O I )

2 38 制计 数器 (ON _ ) 进 O UT 8 8 制计 数器 用 于扫 描数 码 管 。Ck 引入 扫描 时钟 ,计数 器对 时钟 上 进 l脚 跳 沿 从 O 循 环计 数 。输 出值 为三 位 二进 制 码 ,接 入 8 数码 管 的 位选 端 ~7 位

2 4 多路 开关 (U 8 _4 . MX 4 1 ) 多 路 数据 选择 器 的作用 是 在 8 进制 计 数 器位 选 端输 入 信 号 的控 制下 , 从三 个 计数 器输 出 的6 路数 据 中选择 一路 送到 译码 器译 码 。 由于 每路 信号 都 由4 BD 位 C 码组 成 ,因 此该 选择 器 为 六 四选 一 四多 路选 择器 ,而 多余 的两 路 用 于输 出 间隔号 ‘ 一’ 。端 口配 置如 下 :

用CPLD制作的电子闹钟

电子闹钟设计----可编程ASIC设计作业选题电工九班殷平51050918根据要求:请设计具有“对表”功能的、能够显示“时”“分(LED),能够设置闹钟时间并于到达时刻准时闹铃10秒的全功能电子闹钟。

时基由有源晶振产生,频率为1MHZ,外部输入本设计。

设计过程如下:一、单元模块设计如下:(1)可用于分、秒的模60计数器模块TITLE"C60A";SUBDESIGN c60a(clr,clk,en :INPUT;en1,q[6..0],c :OUTPUT;)V ARIABLEc1 :DFF;flip[6..0]:DFF;start[1..0]:DFF;reset:NODE;mlip[6..0]:NODE;nlip[6..0]:NODE;BEGINDEFAULTSen1=GND;END DEFAULTS;mlip[]=flip[]&b"0001111";nlip[]=flip[]&b"1110000";start[].clk=clk;start0.d=clr;start1.d=start0.q;reset=start0.q&!start1.q;flip[].clrn=!reset;c1.clrn=!reset;c1.clk=clk;flip[].clk=clk;q[]=flip[];c=c1.q;IF !reset THENflip[].d=0;END IF;IF !en THENflip[].d=GND;ELSEIF flip[]==H"59" THEN flip[].d=GND;c1.d=VCC; ELSEIF mlip[]==9 THENflip[].d=flip[].q+7;ELSEflip[].d=flip[].q+1;c1.d=GND;END IF;IF nlip[]==b"1010000"THENen1=VCC;END IF;END;(2)可用于计时的模24计数器TITLE "C24"; SUBDESIGN c24(clr,clk,en :INPUT;q[5..0],c :OUTPUT;)V ARIABLEflip[5..0] :DFF;start[1..0] :DFF;reset :NODE;mlip[5..0] :NODE;BEGINmlip[]=flip[]&b"001111";start[].clk=clk;start0.d=clr;start1.d=start0.q;reset=start0.q&!start1.q;flip[].clrn=!reset;flip[].clk=clk;q[]=flip[];IF !reset THENflip[].d=0;END IF;IF !en THENflip[].d=GND;ELSEIF flip[]==H"23"THENflip[].d=GND;ELSEIF mlip[]==9 THENflip[].d=flip[].q+7;ELSEflip[].d=flip[].q+1;END IF;IF flip[]==0 THENc=VCC;ELSEc=GND;END IF;END;(3)用于校时的模块模1000计数器title"c1000";subdesign c1000(clk :input;cao :output;)variableflip[9..0] :dff;beginflip[].clk=clk;if flip[]==h"3e7" thenflip[].d=gnd;elseflip[].d=flip[].q+1;end if;if flip[]==0 thencao=vcc;elsecao=gnd;end if;end;(4)整点报时模块模2计数器在MAX+plusⅡ的文本编辑器中输入如下语句并将文件保存为c2.title"c2";subdesign c2(clk :input;cao :output;)variablecao1 :dff;begincao1.clk=clk;cao=cao1.q;cao1.d=!cao1.q;end;(5)显示模块显示模块程序如下:title"mulx";subdesign mulx(clk :input;h[5..0],m[6..0],s[6..0] :input;a,b,c,d,e,f,g :output;seg[6..1] :output;)variableflip[2..0] :dff;led[6..0] :node;out[3..0] :node;hh[3..0],hl[3..0] :node;mh[3..0],ml[3..0] :node;sh[3..0],sl[3..0] :node;begina=led6;b=led5;c=led4;d=led3;e=led2;f=led1;g=led0; hh[3..2]=gnd;hh[1..0]=h[5..4];hl[]=h[3..0];mh3=gnd;mh[2..0]=m[6..4];ml[]=m[3..0];sh3=gnd;sh[2..0]=s[6..4];sl[]=s[3..0];flip[].clk=clk;if flip[]==5 thenflip[].d=gnd;elseflip[].d=flip[].q+1;end if;case flip[] iswhen h"0"=>out[]=sh[];seg[]=b"111110";when h"1"=>out[]=sl[];seg[]=b"111101";when h"2"=>out[]=mh[];seg[]=b"111011";when h"3"=>out[]=ml[];seg[]=b"110111";when h"4"=>out[]=hh[];seg[]=b"101111";when h"5"=>out[]=hl[];seg[]=b"011111";end case;tableout[3..0] => led[6..0];h"0" => b"1111110";h"1" => b"0110000";h"2" => b"1101101";h"3" => b"1111001";h"4" => b"0110011";h"5" => b"1011011";h"6" => b"1011111";h"7" => b"1110000";h"8" => b"1111111";h"9" => b"1111011";end table;end;三将模块组合成数字电路数字闹钟的原理图如下图所示,其中COUNT为计时模块,CONTROL为校时模块,RING为整点报时模块,MULX为显示模块。

cpld多功能,数字钟时钟,电赛,电子大赛,电子设计,报告书

作品名称:多功能数字时钟申报者信息:作品类别:第四类电子测量装置类目录一、引言二、方案设计三、总体设计四、单元电路(或软件模块)设计五、单元电路测试六、整体测试七、结论八、附录九、参考文献一.引言本产品为多功能数字钟,其主要功能为显示时间与温度,通过开关手动切换,数字显示镶嵌在废旧木板上,突出环保与废物利用的特点,与构建节约型社会相符合。

二.方案设计1.方案选择为实现本题目要求可以采用如下几种方案:一、数字钟可选方案:(1)运用单片机进行数字钟设计,采用EMP240T100C5进行编程设计。

(2)运用单片机作为中央处理器,STC89C52RC进行编程控制。

二、温度测量电路可选方案:(1)采用集A/D转换、译码与驱动于一身的多功能芯片7106,利用它来进行A/D转换、译码驱动一个3位半的液晶显示器,用以显示当前温度值。

模拟信号经电阻R12由30、31管脚输入,由芯片内部的双斜积分电路进行A/D转换,0~199.9mV的电压可得到1~1999的数字,再经译码电路输出3位半的7段译码信号,并驱动3位半液晶显示器显示当前温度值。

1(2)利用MSP430来测量电阻,就可以通过斜率技术而不使用A/D转换电路,处理起来简单易行。

对于这种技术,可以使用MSP430系列芯片上的比较器和时钟来完成斜率的A/D转换。

本系统的具体温度测量是应用电容充放电把被测电阻值转换成时间,再利用MSP430内部的捕获比较寄存器准确捕捉时间,从而测量出热敏电阻的阻值,以间接获得温度值。

(3)利用AD590随温度变化产生不同输出电压特性进行测试温度值/℃AD590电流/μA 经10kΩ电压V/V 放大器输出V0/V0 237.2 2.732 010 283.2 2.832 0.49 20 293.2 2.932 0.98 30 303.2 3.032 1.47 40 313.2 3.132 1.96 50 323.2 3.232 2.45 60 333.2 3.332 2.94 70 343.2 3.432 3.43 80 353.2 3.532 3.92 90 363.2 3.632 4.41 100 373.2 3.732 4.902附图:各温度与电流电压参考关系表图8:温度对电压影响曲线(4)利用单片机STC89C52RC为处理器,通过DS18B20处理温度信号为电信号,从而测出温度值。

基于CPLD的单片多功能数字钟

% 安装与使用

该电路使用直流 #9 电源,系统组装于一块电路板上, 整个电路仅需 % 个轻触按键 开 关 。 只 要 程 序 编 写 无 误 , 则 无需更多调试。实际使用时 , 只 要 按 动 功 能 开 关 , 就 可 调 整其相关输出,操作简单, 运 行 精 确 、 可 靠 。 该 系 统 若 需 用于其它装置进行定时、报警等方面的控制时,只需编 写、修改其中程序即可。

Q"&&""""Q EK() Q""&&QR Q""&&""&Q EK() Q"&""QR Q""&""&"Q EK() Q"&"&QR Q"""""&"Q EK() Q"&&"QR

SS$ SS% SS# SS’

/$ 、 /" 为 高 电 平 , 即 为 #V 秒 时 , 将 !"%U5Z 的 信 号 送 往

SST SSU SSV SSW SSM SSA SSD SS6 SSX SS"

5678 +) 9:;<=>?@A<B6A:>C 4$ D2E)*2 "F G =6;8 2H* 9:;<=>?@A<B6A:>C 4’ D2E)*2 "F F G ()D -./G I3JK+*(J*H3( -./<I3JK 2L -./ +0 M(N+) E+*K 567 96=(J* =6;OP Q&&&&""&Q EK() Q"""&QR Q"&""&""Q EK() Q""&"QR

CPLD技术设计数字时钟 电子报告 精品

设计题目:数字电路1总体设计方案1.1 设计目的1. 熟悉并且了解集成电路的引脚安排。

2. 掌握每一块芯片的逻辑功能及使用方法。

4. 了解数字钟的组成及工作原理和分析方法。

5. 熟悉分·时·秒数字时钟的设计绘图与线路板的制作1.2设计指标数字时钟的时间以24小时为一个周期;或者以24进制和60进制的方法经过译码驱动部分来显示时、分、秒;用蜂鸣器来整点报时,而达到数字时钟的效果。

1.3设计要求2.1画出数字时钟电路原理图或画出仿真的电路图。

2.2电路元器件和各元件的参数选择。

2.3 用protus7.4仿真软件进行电路仿真以及调试。

2.4 protel的原理图绘画和pcb板的绘制生成。

3 制作要求自行装接和调试,焊点焊的饱满,尽量不要虚焊,遇到问题,不害怕,不紧张将其按老师的要求制作出来。

4制作设计报告写出设计与制作的全过程,附上相关资料,图纸和心得体会。

二电路设计2.1 计数器电路个位和十位计数器及时个位和时间计数电路由秒个位和秒十位计数器、分个时十位计数器电路构成,其中秒个位和秒十位计数器、分个位和分十位计数器为60进制计数器,而根据设计要求,时个位和时十位计数器为24进制计数器。

2.2 译码驱动电路译码驱动电路将计数器输出的BCD码转换为数码管需要的逻辑状态,并且为保证数码管正常工作提供足够的工作电流。

2.3数码管数码管通常有发光二极管(LED)数码管和液晶(LCD)数码管,我这次设计所用到的是最常见的7段LED数码管。

这种数码管是利用八个发光二极管,按一定顺序连接制作成的数字、字符显示元器件。

在使用时,只需在数码管的各个引脚上送入合适的高低电平,从而达到显示0~9一系列不同的数字。

LED数码管内部集结了八个条状发光二极管排列成“日”字图案,它有共阳极和共阴极之分,当8个发光二极管的负极接在一起时称之为共阴极数码管,正极接在一起时称之为共阳数码管,对于共阴极数码管,把阴极接低电平,其余8个输入端接高电平,数码管发光;对于共阳极数码管,将阳极接高电平,其余8个输入端接低电平,数码管发光。

基于CPLD的VHDL时钟设计

摘要:数字钟学习的目的是掌握各类计数器及它们相连的设计方法;掌握多个数码管显示的原理与方法;掌握模块化设计方式;掌握用VHDL语言的设计思想以及整个数字系统的设计。

此数字钟具有时,分,秒计数显示功能,以24小时为计数循环;能实现清零,调时,调分以及整点报时等功能。

本设计是一个显示时(2位)分(2位)秒(2位)共六个数字的多功能电子钟。

信号发生器输出的40Mhz作为系统频率(时钟),因此将其分频得1Hz的秒钟信号,秒计满60即得1分钟,分满60即得1小时信号,小时满24即得一天。

关键词:数字钟,计数器,数码管,模块化设计, VHDL。

一、设计分析1.1 设计要求1)具有时、分、秒计数显示功能,以24小时循环计时。

2)时钟计数显示时有LED灯的花样显示。

3)具有调节小时、分钟及清零的功能。

4)具有整点报时功能。

1.2 性能指标及功能设计1)时钟计数:完成时、分、秒的正确计时并且显示所计的数字;对秒、分60进制计数,即从0到59循环计数,时钟——24进制计数,即从0到23循环计数,并且在数码管上显示数值。

2)时间设置:手动调节分钟、小时,可以对所设计的时钟任意调时间,这样使数字钟真正具有使用功能。

我们可以通过实验板上的键7和键4进行任意的调整,因为我们用的时钟信号均是1HZ的,所以每LED灯变化一次就来一个脉冲,即计数一次。

3)清零功能:reset为复位键,低电平时实现清零功能,高电平时正常计数。

可以根据我们自己任意时间的复位。

4)蜂鸣器在整点时有报时信号产生,蜂鸣器报警。

产生“滴答.滴答”的报警声音。

5)LED灯在时钟显示时有花样显示信号产生。

即根据进位情况,LED不停的闪烁,从而产生“花样”信号。

1.3 系统方框图二、设计方案本设计采用自顶向下的设计方法和模块化设计方式,它由秒计数模块,分计数模块,小时计数模块,报警模块,秒分时设置模块和译码模块,程序包,entity模块(顶层模块)八部分组成。

优点:设计简单方便,层次清晰,工程的建立方便,无需单独设计各个组件模块产生原理图文件后再进行电路连接设计。

基于CPLD的多功能数字时钟实现

图1整体框图该时钟的晶振源由实验板自带的50MHz晶振源提供,对50MHz 分频得到1Hz的脉冲;然后对其计数,“秒钟”满60清0向分位进一,同样“分”满60进一到“时”,小时采用12小时制,故时满12清零。

接着,使用刷新电路对其进行动态刷新,并通过数码管显示出来。

对于校时部分,直接通过校时电路对分、时部分进行校时。

最后,关于对控制电路的设计,控制电路通过使用模二进制的循环状态机实现四种模式循环,不同模式的控制,对模式信号进行处理,从而使MUX进行不同的选择实现显示以及闪烁。

关于防抖部分,在每个按键输入处进行消抖处理即可。

2数字钟模块实现在确定整体思路基础后,进行模块化设计,采用模块化设计方便进行局部调整,以及模块的重用,便于开发,节省开发流程。

对于该系统划分为以下几个模块去实现:①分频电路②秒钟计时电路③时钟计时电路④动态刷新和译码显示电路⑤控制电路⑥防机械按键抖动电路⑦闪烁电路⑧校时电路⑨功能选择电路。

下面详细介绍控制电路、防机械按键抖动电路的实现。

2.1控制电路实现图2控制电路2.2防机械按键抖动电路实现及效果稳定可靠的信号输入是时钟系统能可靠工作的重要条件,我们不能将任何有毛刺的输入作为计时器的时钟信号,因此需要设计机械按键防抖动电路。

该系统涉及到两个外部机械按键,要使它们每一次按下时都要产生单脉冲信号,以此提高可靠的信号。

由于机械式开关的核心部件为弹性金属簧片,因而在开关切换的瞬问会在接触点出现来回弹跳的现象。

虽然只是进行了一次按键,但在按键信号稳定的前后出现了多个脉冲,如图3按键波形图所示。

为了确保按键识别的准确性,在按键信号抖动的情况下不能进入状态输入,为此就必须对按键进行消抖处理。

实验开发板机械按键module键和check键常态下为高电平。

如图4为去抖电路所示硬件消抖电路,当按键Y按下时产生抖动,此时若时钟脉冲CP的上升沿不来则两个D触发器的Q端不变,保持初始状态。

设初始状态为Q1=Q2=0,输出S=Q1*Q2=1。

基于CPLD的多功能数字时钟实现1

基于CPLD的多功能数字时钟实现何有为沈祖斌(江汉大学数计学院湖北,武汉 430056)摘要:基于CPLD的数字时钟,采用原理图方式设计,使用自上而下的思想和模块化思想设计时钟系统,形成一个结构明晰的带有防机械按键抖动的多功能数字时钟。

在quartusII 9.0平台上编译与仿真,得到正确结果;同时也在ALTERA 公司的CPLD芯片EPM240T100C5上验证通过,效果良好计时精准。

本文详细介绍该数字时钟系统通过原理图方式实现的全过程,重点介绍动态刷新、功能选择、校时闪烁、防机械按键抖动模块的功能实现。

采用原理图设计方式,加强了对数字逻辑器件的熟悉,能全方位锻炼学生能力。

关键词:数字钟防抖动原理图校时Abstract:Digital clock based on CPLD, the schematic design, using thetop-down thought and the idea of modularization design of the clock system, forming a structure clear with anti machinery jitter of keys of the multi-function digital clock. On the quartusII 9 platform to compile and simulation, get the right results, but also in the ALTERA company's CPLD chip EPM240T100C5 verification through, the effect of good time accurate. The whole process of the digital clock system is introduced in detail, and the function of dynamic refresh, function selection, flash, and anti mechanical key jitter module are introduced in detail. Using the principle diagram design method, strengthen the understanding of the digital logic device, can the full range of training students' ability.Key words:digital clock,Anti shake,Schematic diagram,School1.整体设计方案本系统采用最原始的原理图设计方案,采用原理图设计能最大限度的了解内部电路结构,了解其中的原理构造,清晰易懂,而且在一定程度上很好的强化与锻炼了“数字逻辑”知识。

利用CPLD设计可调时数字钟

数字电路课程设计 题目:利用CPLD 设计可调时数字钟学院电子信息工程学院专业学号姓名教师装 订线基于CPLD数字时钟设计摘要本次课程设计是用数字电路知识以及MaxplusⅡ软件进行的制作,首先理解电路原理图,然后进行了焊接,本次焊接增加自己的动手能力。

然后对数字电路书又进行了复习,最后应用MaxplusⅡ软件进行了编程。

电路通过使用数字元件,来构成完成二十四小时的数字钟设计,并且将译码器和数据选择器配合使用来完成动态的显示输出。

此外,外部控制开关用来控制电路,使得该电路可以完成保持、清零、快速校对时间等一系列的功能。

本系统的难点在于EDA系统作图及最后系统优化的应用。

尤其是小数点的显示控制,用一个或门,通过1Hz来控制第三个数码管的点显示,再通过一个与非门来控制第五个数码管的点显示,第五个数码管的点在整个脉冲阶段显示,而第三个数码管的点只有在低电平时显示,以达到结果是第五个数码显示管的点常亮,而第三个数码管的点以1Hz的频率闪烁。

制作中经常遇到各种问题,如第一次用的七段译码器显示六和九时,显示的不是很好,就重新自己做的译码器,让其显示的比较完美,而且也出现了制作的程序太大问题,最后不断的修改终于成功了。

关键词:数字电路MaxplusⅡ七段译码器目录1.1设计要求1.2设计原理1.2.1电源电路.......................................1.2.3显示电路 ...............................................................................二各模块说明2.1设计思路及步骤2.2总体框图2.3各模块说明2.3.1BCD-7段译码显示电路............................2.3.2时间计数器电路.................................2.3.3数据选择器电路.................................2.3.4译码器电路.....................................2.3.5比较器电路.....................................2.3.6按键消抖电路...................................2.4数字钟电路总图三课程总结3.1遇到的问题及其解决办法3.2收获与体会参考文献一总体设计方案1.1设计要求1、以数字形式显示时、分、秒的时间;2、要求手动校时、校分、校秒;3、调节时间时对应显示位以2Hz频率闪烁;4、时与分显示之间的小数点常亮;5、分与秒显示之间的小数点以1Hz频率闪烁;6、各单元模块设计即可采用原理图方式也可以用Verilog程序进行设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子闹钟设计

----可编程ASIC设计作业选题

电工九班殷平51050918

根据要求:请设计具有“对表”功能的、能够显示“时”“分(LED),能够设置闹钟时间并于到达时刻准时闹铃10秒的全功能电子闹钟。

时基由有源晶振产生,频率为1MHZ,外部输入本设计。

设计过程如下:

一、单元模块设计如下:

(1)可用于分、秒的模60计数器模块

TITLE"C60A";

SUBDESIGN c60a

(

clr,clk,en :INPUT;

en1,q[6..0],c :OUTPUT;

)

V ARIABLE

c1 :DFF;

flip[6..0]:DFF;

start[1..0]:DFF;

reset:NODE;

mlip[6..0]:NODE;

nlip[6..0]:NODE;

BEGIN

DEFAULTS

en1=GND;

END DEFAULTS;

mlip[]=flip[]&b"0001111";

nlip[]=flip[]&b"1110000";

start[].clk=clk;

start0.d=clr;

start1.d=start0.q;

reset=start0.q&!start1.q;

flip[].clrn=!reset;

c1.clrn=!reset;

c1.clk=clk;

flip[].clk=clk;

q[]=flip[];

c=c1.q;

IF !reset THEN

flip[].d=0;

END IF;

IF !en THEN

flip[].d=GND;

ELSEIF flip[]==H"59" THEN flip[].d=GND;c1.d=VCC; ELSEIF mlip[]==9 THEN

flip[].d=flip[].q+7;

ELSE

flip[].d=flip[].q+1;

c1.d=GND;

END IF;

IF nlip[]==b"1010000"THEN

en1=VCC;

END IF;

END;

(2)可用于计时的模24计数器TITLE "C24"; SUBDESIGN c24

(

clr,clk,en :INPUT;

q[5..0],c :OUTPUT;

)

V ARIABLE

flip[5..0] :DFF;

start[1..0] :DFF;

reset :NODE;

mlip[5..0] :NODE;

BEGIN

mlip[]=flip[]&b"001111";

start[].clk=clk;

start0.d=clr;

start1.d=start0.q;

reset=start0.q&!start1.q;

flip[].clrn=!reset;

flip[].clk=clk;

q[]=flip[];

IF !reset THEN

flip[].d=0;

END IF;

IF !en THEN

flip[].d=GND;

ELSEIF flip[]==H"23"THEN

flip[].d=GND;

ELSEIF mlip[]==9 THEN

flip[].d=flip[].q+7;

ELSE

flip[].d=flip[].q+1;

END IF;

IF flip[]==0 THEN

c=VCC;

ELSE

c=GND;

END IF;

END;

(3)用于校时的模块模1000计数器

title"c1000";

subdesign c1000

(

clk :input;

cao :output;

)

variable

flip[9..0] :dff;

begin

flip[].clk=clk;

if flip[]==h"3e7" then

flip[].d=gnd;

else

flip[].d=flip[].q+1;

end if;

if flip[]==0 then

cao=vcc;

else

cao=gnd;

end if;

end;

(4)整点报时模块

模2计数器

在MAX+plusⅡ的文本编辑器中输入如下语句并将文件保存为c2.

title"c2";

subdesign c2

(

clk :input;

cao :output;

)

variable

cao1 :dff;

begin

cao1.clk=clk;

cao=cao1.q;

cao1.d=!cao1.q;

end;

(5)显示模块

显示模块程序如下:

title"mulx";

subdesign mulx

(

clk :input;

h[5..0],m[6..0],s[6..0] :input;

a,b,c,d,e,f,g :output;

seg[6..1] :output;

)

variable

flip[2..0] :dff;

led[6..0] :node;

out[3..0] :node;

hh[3..0],hl[3..0] :node;

mh[3..0],ml[3..0] :node;

sh[3..0],sl[3..0] :node;

begin

a=led6;b=led5;c=led4;d=led3;e=led2;f=led1;g=led0; hh[3..2]=gnd;hh[1..0]=h[5..4];hl[]=h[3..0];

mh3=gnd;mh[2..0]=m[6..4];ml[]=m[3..0];

sh3=gnd;sh[2..0]=s[6..4];sl[]=s[3..0];

flip[].clk=clk;

if flip[]==5 then

flip[].d=gnd;

else

flip[].d=flip[].q+1;

end if;

case flip[] is

when h"0"=>

out[]=sh[];

seg[]=b"111110";

when h"1"=>

out[]=sl[];

seg[]=b"111101";

when h"2"=>

out[]=mh[];

seg[]=b"111011";

when h"3"=>

out[]=ml[];

seg[]=b"110111";

when h"4"=>

out[]=hh[];

seg[]=b"101111";

when h"5"=>

out[]=hl[];

seg[]=b"011111";

end case;

table

out[3..0] => led[6..0];

h"0" => b"1111110";

h"1" => b"0110000";

h"2" => b"1101101";

h"3" => b"1111001";

h"4" => b"0110011";

h"5" => b"1011011";

h"6" => b"1011111";

h"7" => b"1110000";

h"8" => b"1111111";

h"9" => b"1111011";

end table;

end;

三将模块组合成数字电路

数字闹钟的原理图如下图所示,其中COUNT为计时模块,CONTROL为校时模块,RING为整点报时模块,MULX为显示模块。

二、用编辑后截图如下:

按图形顺序依次为1.计时模块(COUNT)

2.整点报时模块(RING)

3.校时模块(COTROL)

4.电子闹钟的顶层原理图(CLOCK)

参考文献:<<ALTERA可编程逻辑器件>>于枫主编。