Allegro差分线走线规则

allegro差分规则设计

Allegro差分线的规则设置“读万卷书,不如行万里路,行万里路,不如阅人无数,阅人无数,不如名师点悟。

”技术交流群78321575 78321575 78321575 谢谢!1)pair 名称:Allegro菜单点击logic-->Assign differential pair,在net filter 中选择所要设的net1,net2, 或直接在board file 中点选net,在Rule Name 中key 入pair 名称﹐点右下方的Add 后会自动增加到上方的Rule Selection Area 中﹐可以点Modify或Delete 来修改或删除所设的pair.2)设置差分线规则类型给pair 定义一个net spacing type property(规则类型),如CLK-CLK:点Attach property, net...,注意find 窗口中选property 而非net,再点more...,从左边选取先前设的pair,如CK0R-CK0R,点apply﹐在弹出的对话框中点net_spacing_type﹐在右边的value 值中输入CLK-CLK。

3)设置差分线规则参数set net spacing constrains values , 设定走线线距规则参数值:点constraints 窗口的spacing rule set 下的set values,在出现的对话框中右边空格输入CLK-CLK, 点add 增加到constraint set name 栏。

然后按guideline 设定各项spacing.¯ line to line 指的是此对pair 和其它线的间距。

注1: Length Tolerance indicates the amount of tolerance allowed between the total length or delay of the two nets. (两net 之间的误差范围)注2:Primary Max Sep indicates the maximum edge to edge spacing between a differential pair. (指该pair 本身的间距)注3:Secondary Max Sep indicates an edge to edge spacing that is greater that the Primary Max Sep value. This allows an increase in thespacing between the differential pair when necessary. The total amount of etch/conductor on a net can not exceed this amount.(必要时允许增大该pair 本身的间距到此值)4)布线技巧route differential pair 时的技巧:routing 时发现本身的两根net 没有按规则挤线会弹的很开。

Allegro差分线走线规则

Allegro差分线走线规则SOFER TECHNICAL FILE Allegro 15.x 差分线布线规则设置Doc Scope : Cadence Allegro 15.xDoc Number : SFTCA06001Author :SOFERCreate Date :2005-5-30Rev : 1.00Allegro 15.x差分线布线规则设置文档内容介绍:1.文档背景 (3)2.Differential Pair信号介绍 (3)3.如何在Allegro中定义Differential Pair属性 (4)4.怎样设定Differential Pair在不同层面控制不同线宽与间距 (8)5.怎样设定Differential Pair对与对之间的间距 (11)1.文档背景a)差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,差分线大多为电路中最关键的信号,差分线布线的好坏直接影响到PCB 板子信号质量。

b)差分线一般都需要做阻抗控制,特别是要在多层板中做的各层的差分走线阻抗都一样,这个一点要在设计时计算控制,否则仅让PCB板厂进行调整是非常麻烦的事情,很多情况板厂都没有办法调整到所需的阻抗。

c)Allegro版本升级为15.x后,差分线的规则设定与之前版本有很大的改变。

虽然Allegro15.0版本已经发布很长时间了,但是还是有很多人对新版本的差分线规则设置不是很清楚。

2.Differential Pair信号介绍差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计,什么另它这么倍受青睐呢?在PCB设计中又如何能保证其良好的性能呢?带着这两个问题,我们进行下一部分的讨论。

何为差分信号?通俗地说,就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”。

Allegro设置差分线和等长的方法

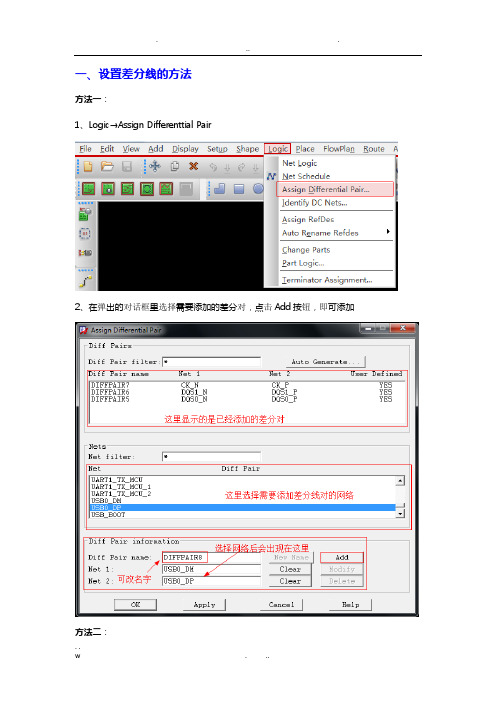

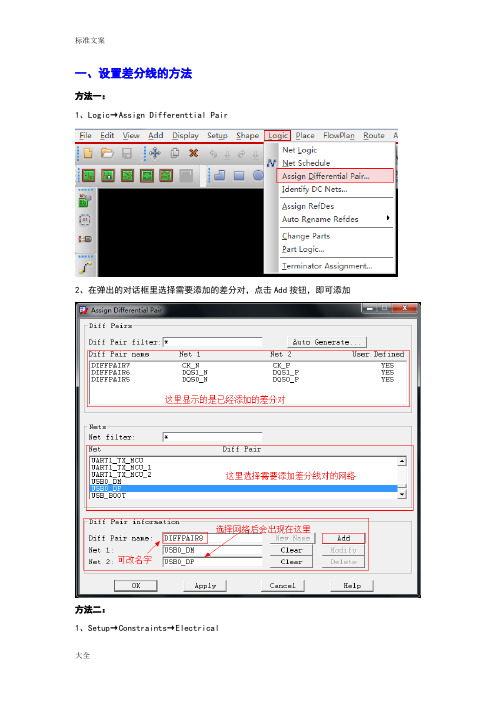

A l l e g r o设置差分线和等长的方法Revised by Petrel at 2021一、设置差分线的方法方法一:1、Logic→AssignDifferenttialPair2、在弹出的对话框里选择需要添加的差分对,点击Add按钮,即可添加方法二:1、Setup→Constraints→Electrical2、选择Net,然后在Objects→Create→DifferenttialPair3、在弹出的对话框里选择需要添加的差分对,点击Create按钮,即可添加设置完差分线对后,需要设置其约束规则,方法如下:1、初始默认的有一个DEFAULT规则,右击DEFAUlT,选择Create→PhysicalCSet2、弹出一下对话框,在PhysicalCSet栏写上规则名称,建议根据差分线的阻抗描写,点击OK,这里已经写好,规则名称为:DIFF100,就可以看到多了一行PCS3、设立好规则后就可以在这项规则里设置线宽间距等参数了4、在Net一栏看到有已经设好的差分线,在ReferencedphysicalCSet选项下选择刚刚设好的规则DIFF100*规则设置中各个项目的含义*LineWidth(设置基本走线宽度)Min:最小线宽Max:最大线宽,写0相当于无限大Neck(neck模式,一般在间距很小的时候用到)MinWidth:最小线宽MaxLength:最大线长DifferentialPair(差分线设置,单端线可不写)MinLineSpacing:差分对的最小线间距PrimaryGap:差分对理想线间距NeckGap:差分对最小允许线间距(+)Tolerance:差分线允许的误差+(-)Tolerance:差分线允许的误差-Vias(过孔选择)BBViaStagger(设置埋/盲孔的过孔间距)Min:最小间距Max:最大间距AllowPad-PadConnect:/Etch:/Ts:/示意图:二、设置等长1、进入规则设置页面Electrical→Net→Routing→RelativePropagationDelay2、选中需要设置等长的网络,右击,选择Create→MatchGroup3、更改组名称4、设置好后,会显示MGrp,如下图。

allegro建立差分线规则

allegro建立差分线规则

建立差分线规则是在使用Allegro软件进行PCB设计时非常重要的一步。

差分

线是一对相互衔接的信号线,用于传输高速数字信号,如USB、HDMI和以太网等。

通过建立差分线规则,可以确保差分线的质量和稳定性,减少干扰和串扰,从而提高整体电路性能。

首先,在Allegro软件中,打开设计文件并进入布局编辑器。

选择需要添加差

分线规则的信号线对,并右键单击选择“差分对属性”。

在弹出的对话框中,可以设置差分线的物理特性、约束条件和信号完整性要求。

物理特性方面,可以设置差分线的宽度、间距和层堆栈,以满足设计要求。

这

些参数会影响差分线的阻抗和信号传输速率,需要根据具体设计需求进行调整。

约束条件方面,可以设置差分线的最大长度、最小间距和最大串扰限制等。

这

些约束条件会在布线时自动检测和优化差分线,确保其满足电路的可靠性和性能要求。

信号完整性要求方面,可以设置差分线的最大延迟和最小延迟不平衡等。

这些

要求会在信号传输过程中考虑时延和时序要求,确保差分信号的同步性和稳定性。

在建立差分线规则之后,可以进行布线操作。

Allegro软件会根据所设定的差

分线规则自动分配和布线差分线,同时提供实时反馈和报告,以便进行优化和调整。

综上所述,建立差分线规则是使用Allegro软件进行PCB设计中至关重要的一步。

通过准确设置差分线的物理特性、约束条件和信号完整性要求,可以确保差分线的质量和稳定性,提高整体电路性能。

同时,在布线过程中,Allegro软件提供

了自动分配和布线差分线的功能,方便优化和调整设计。

allegro差分线设置规则

allegro差分线设置规则Allegro差分线设置规则引言:Allegro差分线是一种常用的信号传输方式,在电路设计中起到了重要的作用。

本文将探讨Allegro差分线设置规则,从理论和实践角度介绍如何正确地设置Allegro差分线以保证信号传输的准确性和稳定性。

一、什么是Allegro差分线?Allegro差分线是一种差分信号传输方式,通过同时传输正负两个信号来降低干扰和提高信号的抗噪声能力。

差分信号在信号线上的电压差被解读为二进制信号,从而实现数据传输。

Allegro差分线广泛应用于高速数据传输、音频信号传输等领域。

二、设置规则1. 差分线对称布局:为了减小差分信号间的电磁干扰,差分线应该尽量保持对称布局。

在PCB设计中,可以通过布局对称的方式将差分信号线放置在相邻的层上,并且保持相同的长度和宽度,以确保信号的平衡传输。

2. 差分线长度匹配:差分线的长度差异会导致信号的相位差,从而影响信号的准确性和稳定性。

因此,在布线过程中,应尽量使差分线的长度保持一致,以确保信号的同步传输。

3. 差分线与其他信号线的间隔:为了避免干扰,差分线应与其他信号线保持一定的间隔。

特别是与高频信号线、时钟线等应尽量保持一定的距离,以减小相互之间的电磁干扰。

4. 差分线与地线的间隔:差分线与地线之间的间隔也需要特别注意。

过大的间隔会增加信号线的阻抗,影响信号的传输质量;而过小的间隔则容易导致信号与地线之间的串扰干扰。

因此,在实际设计中,应根据具体情况合理设置差分线与地线的间隔。

5. 差分线的屏蔽与接地:为了进一步降低差分线的干扰,可以采用屏蔽措施。

常见的做法是在差分线周围设置屏蔽层,并将屏蔽层接地,以消除外部电磁干扰对信号的影响。

6. 差分线的阻抗匹配:差分线的阻抗匹配是保证信号传输质量的关键。

在设计中,应根据差分线的特性和设计要求,选择合适的阻抗值。

常见的阻抗匹配方式有微带线和差分对线,设计时需要注意保持差分线的阻抗匹配。

allegro差分线分组约束规则设置

allegro差分线分组约束规则设置摘要:1.Allegro差分线分组约束规则简介2.设置差分线分组约束规则的步骤3.约束规则的应用场景及优势4.总结与建议正文:1.Allegro差分线分组约束规则简介Allegro软件是一款专业的印刷电路板(PCB)设计软件,其差分线分组约束规则是其中一项重要的功能。

通过这项功能,用户可以实现自动化布局,确保PCB上各个元件的正确位置和连接关系,从而提高整体设计的稳定性和可靠性。

2.设置差分线分组约束规则的步骤在Allegro软件中设置差分线分组约束规则,主要可以分为以下几个步骤:步骤一:创建差分线。

首先,在Allegro中创建差分线,它们用于定义分组约束规则。

步骤二:定义约束规则。

在创建差分线后,设置相应的约束规则,如最小间距、最大间距等。

步骤三:应用约束规则。

将设置好的约束规则应用于需要布局的元件,以确保它们在PCB上的位置和连接关系满足设计要求。

步骤四:检查与修复。

在布局过程中,不断检查PCB设计是否符合约束规则,如有问题,及时进行修复。

3.约束规则的应用场景及优势差分线分组约束规则在以下场景中具有显著优势:- 提高设计效率:通过自动化布局,设计者可以更快地完成PCB设计,减少重复性工作。

- 保证连接可靠性:约束规则确保了元件之间的正确连接,降低了故障风险。

- 优化电路性能:合理的布局可以降低信号干扰,提高电路性能。

- 易于维护:约束规则使得设计更加规范,便于后期维护和升级。

4.总结与建议差分线分组约束规则在Allegro软件中发挥着重要作用,能够帮助设计者实现自动化布局,提高PCB设计的质量。

在使用过程中,建议设计者熟练掌握约束规则的设置方法,并根据实际需求进行调整。

allegro走线规则

allegro走线规则

Allegro是一款PCB设计软件,而走线规则是在PCB设计阶段用来定义和约束走线的规则和限制。

以下是一些常见的Allegro走线规则:

1. 面间间距规则(Plane to Plane Spacing Rules):指定不同电源层或平面之间的最小间距要求,以防止短路或电气干扰。

2. 几何限制规则(Geometry Rules):指定走线的最小宽度、最小间距和最大长度等几何约束,以确保设计满足制造和性能要求。

3. 差分走线规则(Differential Pair Rules):用于定义差分信号(如高速信号对)的走线规则,包括相位匹配、长度匹配和间距匹配等。

4. 信号完整性规则(Signal Integrity Rules):用于防止信号完整性问题,如信号串扰、时钟抖动和时钟延迟等。

可以设置信号的最大延时、最大串扰和最大抖动值等。

5. 电源和地规则(Power and Ground Rules):定义电源和地平面的走线规则,如电源走线的最小宽度、地平面的连接方式和分割规则等。

6. 约束规则(Constraint Rules):包括引脚约束、时序约束和布线约束等,用于确保设计满足电气和时序要求。

以上仅是一些常见的Allegro走线规则,具体的规则设置还取决于设计的需求、制造要求和性能目标等。

在使用Allegro进行PCB设计时,可以根据实际需求来设定相应的走线规则。

Allegro线宽、间距、等长、差分

A llegro 中的约束规则设置Allegrophan 刚好五个字w w w .pc b b b s .c o m修订记录日期版本描述作者2008-12V1.0初版,学完的总结。

适用于Cadence 15.5版本。

Allegrophan 2009-09-08V1.1小改,修改部分措辞Allegrophan 2009-10-14V1.2小改,更正、修改几个错漏之处。

添加一些说明性文字。

感谢群里的佳猪、梦姑娘等朋友的指正!Allegrophanw w w .p c b b b s .c o m目录一:Physical (Line/vias )rule 物理特性(线宽和过孔)约束设置:.............41)“Set values”设置约束特征值....................................................................52)“Attach property ”绑定约束.....................................................................63)“Assignment table ”约束规则分配........................................................8二“Spacing rule”间距约束设置...........................................................................91)“Set values ”设置约束特征值................................................................92)“Attach property ”绑定约束.................................................................103)“Assignment table ”约束规则分配......................................................11三Constraint areas 区域约束设置......................................................................12四Allegro 中走线长度的设置............................................................................131)差分线等长设置......................................................................................132)一组Net 等长..........................................................................................163)XNet 等长................................................................................................17w w w .p c b b b s .c o m线宽、线距、区域的约束主要在“Constraints Sys ”中设置,点击“Setup/Constraints ”或点击图标打开“Constraints Sys ”窗口,如下:“Constraints Sys ”窗口分两个级别,第一级别有两类:Standard design rules 和Exte Extended nded design rules 。

Allegro 教程之 基本规则设置 布线规则设置 线宽及线间距的设置

在PCB设计过程中,需要通过设置各种规则,以满足各种信号的阻抗。

比如,常用的高速差分线,我们常控的100欧姆,那么到底走多宽的线以及差分线之间的间距到底是多少,才能满足设计要求的100欧姆阻抗呢本文就对Allegro 种的基本规则设置做一个详细的讲解。

注:本文是基于Allegro 15 版本的。

对于16版本不适用。

首先需要打开规则管理器,可通过以下三种方式打开:一、点击工具栏上的图标。

二、点击菜单Setup->Constraints三、在命令栏内输入"cns" 并回车打开的规则管理器如下:在最上面一栏有一个On-line DRC,这是对画板过程中不停检测是否违反规则,并可产生DRC。

一般我们都默认开启。

可以实时查看产生的DRC 错误,并加以修正。

接下来的Spacing rule set 是对走线的线间距设置。

比如对于时钟线、复位线、及高速查分线。

我们可以再这里面加一规则,使其离其它信号线尽可能的远。

Physical(lines/vias)rule set 是针对各种物理规则设置,比如线宽,不同信号线的过孔等。

例如我们可通过电源网络的设置,使其默认线宽比普通信号走线更粗,已满足走线的载流能力。

现针对一个时钟及电源,分别设置间距规则和物理规则。

首先筛选网络,对于需要设置线间距规则的网络赋上Net_Spacing_Type 属性、而对于需要设置线宽规则的网络赋上Net_Physical_type 。

而对于即要线间距和线宽规则约束的网络,可将Net_Spacing_Type 及Net_Physical_type 属性同时赋上。

本例针对的时钟网络,只需要对其赋上Net_Spacing_Type ,方法如下:点击菜单Edit->Properties然后在右侧Find 一栏中选择Nets 。

如下图所示:如果你知道PCB上网络名,那么你可以直接在PCB上选择一个网络。

假如你并不知道到底哪个网络是时钟,那么你可以选择Find下面的More然后在弹出的对话框中筛选出时钟网络。

allegro差分线分组约束规则设置

allegro差分线分组约束规则设置摘要:I.简介- 什么是Allegro- 差分线分组约束规则的作用II.差分线分组约束规则设置- 设置规则概述- 具体设置步骤- 步骤1:定义分组- 步骤2:设置差分线属性- 步骤3:应用规则III.应用实例- 实例1:设置差分线分组约束规则- 步骤1:创建工程- 步骤2:添加元件- 步骤3:设置差分线分组约束规则- 实例2:使用差分线分组约束规则进行设计优化- 步骤1:发现问题- 步骤2:应用规则优化设计- 步骤3:验证优化结果IV.总结- 差分线分组约束规则的重要性- 在实际应用中的优势正文:I.简介Allegro 是一款广泛应用于PCB 设计领域的EDA 工具,可以帮助设计师快速、高效地完成电路板设计。

在Allegro 中,差分线分组约束规则设置是一项关键功能,它能够帮助设计师更好地管理差分线,提高设计效率和质量。

差分线分组约束规则主要用于对差分线进行分类和约束,以便在设计过程中更加方便地管理和调整。

通过设置差分线分组约束规则,可以确保差分线在设计中的正确性和一致性,避免因差分线问题导致的设计错误。

II.差分线分组约束规则设置在Allegro 中设置差分线分组约束规则主要包括以下几个步骤:1.定义分组:首先,设计师需要根据设计需求,定义差分线的分组。

分组可以根据差分线的功能、性能等特点进行划分,以便于后续的管理和调整。

2.设置差分线属性:在定义分组的基础上,设计师需要为每个分组设置差分线的属性。

这些属性包括差分线的宽度、间距、过孔等参数,可以根据设计规范和实际需求进行调整。

3.应用规则:设置好差分线属性后,设计师需要将规则应用到实际的设计中。

在Allegro 中,可以通过菜单命令或脚本语言等多种方式应用差分线分组约束规则,确保差分线在设计中的正确性和一致性。

III.应用实例以下是两个关于差分线分组约束规则设置的应用实例:实例1:设置差分线分组约束规则1.创建工程:首先,设计师创建一个新的Allegro 工程,并导入所需的元器件和设计文件。

allegro设置差分线和等长的方法

一、设置差分线的方法方法一:1、Logic→Assign Differenttial Pair2、在弹出的对话框里选择需要添加的差分对,点击Add按钮,即可添加方法二:1、Setup→Constraints→Electrical2、选择Net,然后在Objects→Create→Differenttial Pair3、在弹出的对话框里选择需要添加的差分对,点击Create按钮,即可添加设置完差分线对后,需要设置其约束规则,方法如下:1、初始默认的有一个DEFAULT规则,右击DEFAUlT,选择Create→Physical CSet2、弹出一下对话框,在Physical CSet栏写上规则名称,建议根据差分线的阻抗描写,点击OK,这里已经写好,规则名称为:DIFF100,就可以看到多了一行PCS3、设立好规则后就可以在这项规则里设置线宽间距等参数了4、在Net一栏看到有已经设好的差分线,在Referenced physical C Set选项下选择刚刚设好的规则DIFF100*规则设置中各个项目的含义*Line Width(设置基本走线宽度)Min:最小线宽Max:最大线宽,写0相当于无限大Neck(neck模式,一般在间距很小的时候用到)Min Width:最小线宽Max Length:最大线长Differential Pair(差分线设置,单端线可不写)Min Line Spacing:差分对的最小线间距Primary Gap:差分对理想线间距Neck Gap:差分对最小允许线间距(+)T olerance:差分线允许的误差+(-)Tolerance:差分线允许的误差-Vias(过孔选择)BB Via Stagger(设置埋/盲孔的过孔间距)Min:最小间距Max:最大间距AllowPad-Pad Connect:/ Etch:/Ts:/示意图:二、设置等长1、进入规则设置页面Electrical→Net→Routing→Relative Propagation Delay2、选中需要设置等长的网络,右击,选择Create→Match Group3、更改组名称4、设置好后,会显示MGrp,如下图。

Allegro设置差分线和等长地方法

一、设置差分线的方法方法一:1、Logic→Assign Differenttial Pair2、在弹出的对话框里选择需要添加的差分对,点击Add按钮,即可添加方法二:1、Setup→Constraints→Electrical2、选择Net,然后在Objects→Create→Differenttial Pair3、在弹出的对话框里选择需要添加的差分对,点击Create按钮,即可添加设置完差分线对后,需要设置其约束规则,方法如下:1、初始默认的有一个DEFAULT规则,右击DEFAUlT,选择Create→Physical CSet2、弹出一下对话框,在Physical CSet栏写上规则名称,建议根据差分线的阻抗描写,点击OK,这里已经写好,规则名称为:DIFF100,就可以看到多了一行PCS3、设立好规则后就可以在这项规则里设置线宽间距等参数了4、在Net一栏看到有已经设好的差分线,在Referenced physical C Set选项下选择刚刚设好的规则DIFF100*规则设置中各个项目的含义*Line Width(设置基本走线宽度)Min:最小线宽Max:最大线宽,写0相当于无限大Neck(neck模式,一般在间距很小的时候用到)Min Width:最小线宽Max Length:最大线长Differential Pair(差分线设置,单端线可不写)Min Line Spacing:差分对的最小线间距Primary Gap:差分对理想线间距Neck Gap:差分对最小允许线间距(+)Tolerance:差分线允许的误差+(-)Tolerance:差分线允许的误差-Vias(过孔选择)BB Via Stagger(设置埋/盲孔的过孔间距)Min:最小间距Max:最大间距AllowPad-Pad Connect:/Etch:/Ts:/示意图:二、设置等长1、进入规则设置页面Electrical→Net→Routing→Relative Propagation Delay2、选中需要设置等长的网络,右击,选择Create→Match Group3、更改组名称4、设置好后,会显示MGrp,如下图。

allegro差分对走线技巧

allegro差分对走线技巧

差分对走线技巧是一种用于设计高速数据传输电路的技术。

差分对走线是指将信号分成两个互为相反的差分信号,在PCB

设计中将两条差分信号线路作为一对对称的线路进行布线。

以下是几种常用的差分对走线技巧:

1. 避免走线长度不一致:差分信号走线两条线路的长度应保持一致,避免信号的相位差引起信号的失真。

2. 保持差分信号的相邻距离:两条差分信号线路之间的距离也要保持一致,用于减少信号的互相干扰。

3. 使用相同的线宽:差分信号的两条线路应该使用相同的线宽,确保两个信号的阻抗匹配。

4. 使用地平面: 在差分对走线的两条线路之间放置地平面,用

于减少信号之间的干扰。

5. 使用差分信号线路层叠: 在PCB设计中,将差分信号线路放置在相邻的层上,可以进一步减少信号之间的干扰。

以上是一些常见的差分对走线技巧,设计工程师可以根据具体的电路需求和信号特性,结合实际情况选择适合的技巧进行设计。

allegro差分对布线规则中的每个参数的意思

allegro差分对布线规则中的每个参数的意思Allegro是一款广泛应用于电子设计自动化(EDA)领域的PCB设计软件,其强大的差分对布线功能在高速信号设计中尤为突出。

在使用Allegro进行差分对布线时,需要遵循一定的规则,并设置多个参数以确保信号完整性。

本文将对这些参数进行详细解析,以帮助读者更好地理解其意义。

一、差分对布线规则参数概述在Allegro中,差分对布线规则主要包括以下参数:1.差分对名称(Diff Pair Name)2.差分对层(Diff Pair Layer)3.差分对间距(Diff Pair Spacing)4.差分对宽度(Diff Pair Width)5.差分对长度匹配(Diff Pair Length Match)6.差分对阻抗(Diff Pair Impedance)二、各参数意义解析1.差分对名称(Diff Pair Name)差分对名称用于标识差分对,方便在布线过程中对其进行识别和管理。

差分对名称应具有一定的意义,便于理解。

2.差分对层(Diff Pair Layer)差分对层用于指定差分对所在的布线层。

通常情况下,差分对应在同一层进行布线,以减小层间耦合对信号完整性的影响。

3.差分对间距(Diff Pair Spacing)差分对间距是指差分对两个信号线之间的距离。

合适的间距有助于减小信号线之间的相互干扰,提高信号完整性。

通常,差分对间距应大于等于两倍线宽。

4.差分对宽度(Diff Pair Width)差分对宽度是指差分对两个信号线的宽度。

在高速信号设计中,差分对宽度对信号完整性有很大影响。

通常,差分对宽度应保持一致,以减小信号线之间的阻抗差异。

5.差分对长度匹配(Diff Pair Length Match)差分对长度匹配是指差分对两个信号线的长度差异。

在高速信号设计中,长度匹配对信号完整性至关重要。

为了减小信号延迟和相位差,应尽量使差分对两个信号线的长度相等。

allegro16.6差分线线宽线距设计方法

Allegro16.6差分线线宽线距设计方法一、介绍1.1 Allegro16.6简介Allegro16.6是由Cadence Design Systems公司(卡登斯设计系统公司)推出的一款集成电路设计软件,主要用于PCB(Printed Circuit Board,印刷电路板)布局设计和信号完整性分析。

差分线是PCB设计中的重要元件,其线宽和线距的设计对于信号传输的稳定性和可靠性至关重要。

本文将从Allegro16.6软件的角度,共享差分线线宽线距的设计方法。

二、差分线的重要性2.1 信号完整性在PCB设计中,信号的完整性是一个非常重要的问题。

差分线作为传输高速信号的通道,其线宽和线距的设计直接影响到信号的传输速率、抗干扰能力和抗串扰能力等方面。

合理的差分线设计可以有效地提高信号的稳定性和可靠性。

2.2 电磁兼容差分线的设计不仅涉及到传输性能,还需要考虑电磁兼容性。

合理的线宽线距设计可以降低差分线之间的串扰和辐射,减少对周围电路的干扰,提高整个系统的电磁兼容性。

三、Allegro16.6差分线线宽线距设计方法3.1 设定设计规范在使用Allegro16.6软件进行差分线设计时,首先需要设定设计规范。

包括差分线的层设定、线宽线距的要求和信号完整性标准等方面。

根据实际的设计需求和规范要求,对差分线的设计参数进行合理的设定。

3.2 使用差分线工具Allegro16.6提供了丰富的差分线设计工具,包括差分线的创建、编辑和仿真等功能。

在设计过程中,可以使用这些工具快速高效地对差分线进行设计和验证。

通过仿真分析,可以及时发现设计中的问题,并进行调整优化。

3.3 考虑布局约束在进行差分线设计时,需要考虑到布局的约束条件。

包括与其他线路的交叉、与器件的连接以及整体布局的合理性等方面。

合理的布局约束可以有效地降低信号的串扰和辐射,提高整个系统的稳定性和可靠性。

3.4 仿真验证在完成差分线设计后,需要进行仿真验证。

allegro差分线分组约束规则设置

allegro差分线分组约束规则设置【最新版】目录1.Allegro 软件概述2.差分线分组约束规则的概念3.差分线分组约束规则的设置方法4.差分线分组约束规则的应用实例5.总结正文一、Allegro 软件概述Allegro 是一款专业的 EDA(电子设计自动化)软件,广泛应用于 PCB (印刷电路板)设计领域。

通过 Allegro 软件,设计人员可以轻松实现电路原理图的绘制、PCB 布局布线以及各种设计规则的检查等功能。

在PCB 设计过程中,设计规则的合理设置是保证电路板性能和可靠性的关键。

二、差分线分组约束规则的概念差分线分组约束规则是 Allegro 软件中一种用于控制差分线(Differential Pair)布局布线的设计规则。

差分线是指在高速信号传输过程中,通过两条走线进行数据传输,以降低外部干扰和信号衰减的影响。

在实际应用中,为了保证差分线的传输性能,需要对差分线的布局布线进行分组约束。

三、差分线分组约束规则的设置方法在 Allegro 软件中,设置差分线分组约束规则的方法如下:1.打开 Allegro 软件,载入需要设置差分线分组约束规则的 PCB 设计文件。

2.在顶部菜单栏中,依次点击“规则”(Rules)→“约束规则”(Constraints)→“新建”(New),打开“新建约束规则”对话框。

3.在“新建约束规则”对话框中,设置差分线分组约束规则的名称、描述等信息,然后点击“添加”(Add)按钮。

4.在弹出的“添加约束规则”对话框中,设置差分线分组约束规则的具体参数,包括差分线分组名称、走线宽度、间距等,点击“确定”(OK)按钮。

5.在“新建约束规则”对话框中,点击“确定”(OK)按钮,完成差分线分组约束规则的设置。

四、差分线分组约束规则的应用实例在实际的 PCB 设计过程中,我们可以通过以下实例应用差分线分组约束规则:假设某高速信号传输系统,需要设计两条差分线,分别为 A 和 B。

allegro建立差分线规则

allegro建立差分线规则

建立差分线规则的方法如下:

1. 确定差分线的标准:差分线指的是MACD指标中的DIF线

和DEA线之间的差值。

一般情况下,当DIF线由负值变为正

值时,表示买入信号;当DIF线由正值变为负值时,表示卖

出信号。

2. 设定阈值:根据市场经验和个人风险偏好,设定一个合适的阈值来判断买入和卖出信号。

比如,当DIF线大于等于阈值时,触发买入信号;当DIF线小于等于阈值的负值时,触发

卖出信号。

3. 确定持仓策略:根据买入和卖出信号,制定持仓策略。

比如,当触发买入信号时,可以全仓买入;当触发卖出信号时,可以全部卖出或者部分卖出。

4. 设置止损和止盈点:为了控制风险,可以设置一定的止损和止盈点。

比如,当买入后的价格下跌到设定的止损点时,自动卖出;当买入后的价格上涨到设定的止盈点时,自动卖出。

5. 定期回顾和调整规则:市场行情时刻变化,所以需要定期回顾和调整差分线规则。

可以根据历史回测结果和市场环境来优化规则,提高交易效果。

需要注意的是,差分线规则只是一种参考,投资者应根据个人

情况和市场情况综合考虑。

此外,差分线规则也具有一定的局限性,不能完全依赖于它进行投资决策。

allegro差分线分组约束规则设置

allegro差分线分组约束规则设置(最新版)目录1.allegro 差分线分组约束规则的概念2.allegro 差分线分组约束规则的设置方法3.allegro 差分线分组约束规则的应用实例4.allegro 差分线分组约束规则的优缺点正文一、allegro 差分线分组约束规则的概念Allegro 是一种用于印刷电路板(PCB)设计的专业软件,它能够帮助设计人员快速高效地完成电路板的布局和设计。

在 Allegro 中,差分线分组约束规则是一种用于控制差分线(differential pair)布局的规则,能够有效地提高电路板的信号完整性。

二、allegro 差分线分组约束规则的设置方法在 Allegro 中,设置差分线分组约束规则的方法如下:1.打开 Allegro 软件,点击菜单栏的“工具”选项,选择“约束管理器”。

2.在弹出的“约束管理器”窗口中,选择“新建”选项,创建一个新的约束。

3.在“新建约束”对话框中,选择“差分线分组”选项,然后输入差分线的名称和描述。

4.在“差分线分组”对话框中,设置差分线的属性,包括线宽、间距、层数等。

5.确认设置后,点击“确定”按钮,完成差分线分组约束规则的设置。

三、allegro 差分线分组约束规则的应用实例在实际的电路板设计中,差分线分组约束规则可以应用于各种需要差分线布局的场景,例如高速信号传输、模拟信号处理等。

下面是一个应用实例:假设我们需要设计一个用于高速数据传输的电路板,其中涉及到一对差分线。

我们可以通过设置差分线分组约束规则,控制这对差分线的布局,以确保信号的完整性。

四、allegro 差分线分组约束规则的优缺点差分线分组约束规则在提高电路板信号完整性方面具有显著的优势,但也存在一些不足之处:优点:1.有效提高信号完整性,减少信号干扰和噪声。

2.便于设计和修改,提高设计效率。

缺点:1.需要对差分线进行专门的设置和管理,增加了设计复杂度。

2.对于复杂的电路板设计,差分线分组约束规则的设置可能会变得繁琐。

allegro差分线线距设计

Allegro差分线线距设计介绍在高速信号传输中,差分线线距设计是确保信号完整性和数据可靠性的重要因素之一。

本文将介绍差分线线距的概念、设计原则以及常见的设计方法。

差分线线距的概念差分线指的是一对电路中的两根导线,它们具有相等且相反的信号,用于在电路中传输高速差分信号。

差分线的线线距是指这两根导线之间的距离。

合理的线线距设计可以最大限度地减少干扰和串扰,确保信号的完整性和可靠性。

设计原则1.保持恒定线线距在设计差分线时,应确保两根线之间的线线距保持恒定。

恒定的线线距可以提供均匀的电场分布,减少信号的不对称和非对称模式耦合。

2.控制垂直耦合垂直耦合是指差分线与相邻层或其他导线之间的耦合。

为了减少垂直耦合效应,应选择合适的板层厚度和介质常数,并避免差分线与其他信号线平行走向。

3.控制水平耦合水平耦合是指差分线与同一层内的其他导线之间的耦合。

为了减少水平耦合效应,可以采用差分线的屏蔽设计、行/列间距设计和地平交叉抑制等方法。

4.保持对称性对称性是指两根差分线之间的物理参数要尽量保持一致,包括线宽、线长等。

对称性设计可以减小插入损耗和相位不匹配,提高信号的传输质量。

设计方法1.选择合适的差分线宽度和间距差分线宽度和间距的选择应根据具体的应用需求和性能要求进行考量。

一般来说,较宽的差分线可以提供更低的电阻和损耗,而较窄的差分线可以提供更高的线线距。

根据设计规范和信号要求,选择合适的差分线尺寸。

2.使用差分线屏蔽为了减少垂直和水平耦合的影响,可以在差分线周围添加屏蔽层。

屏蔽层可以是金属层、地层或信号层。

屏蔽层的添加可以有效地降低信号的串扰和干扰。

3.控制差分线的行/列间距差分线的行/列间距是指差分线与相邻行/列之间的距离。

合理的行/列间距设计可以减少信号的水平耦合效应,提高信号的完整性和抗干扰能力。

结论差分线线距设计在高速信号传输中起着至关重要的作用。

通过恒定线线距、控制耦合效应、保持对称性等设计原则和方法,可以有效地提高信号的完整性和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SOFER TECHNICAL FILE Allegro 15.x 差分线布线规则设置

Doc Scope : Cadence Allegro 15.x

Doc Number : SFTCA06001

Author :SOFER

Create Date :2005-5-30

Rev : 1.00

Allegro 15.x差分线布线规则设置

文档内容介绍:

1.文档背景 (3)

2.Differential Pair信号介绍 (3)

3.如何在Allegro中定义Differential Pair属性 (4)

4.怎样设定Differential Pair在不同层面控制不同线宽与间距 (8)

5.怎样设定Differential Pair对与对之间的间距 (11)

1.文档背景

a)差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,差分线

大多为电路中最关键的信号,差分线布线的好坏直接影响到PCB板子信号质量。

b)差分线一般都需要做阻抗控制,特别是要在多层板中做的各层的差分走线阻抗都

一样,这个一点要在设计时计算控制,否则仅让PCB板厂进行调整是非常麻烦的

事情,很多情况板厂都没有办法调整到所需的阻抗。

c)Allegro版本升级为15.x后,差分线的规则设定与之前版本有很大的改变。

虽然

Allegro15.0版本已经发布很长时间了,但是还是有很多人对新版本的差分线规

则设置不是很清楚。

2.Differential Pair信号介绍

差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,电路中最关

键的信号往往都要采用差分结构设计,什么另它这么倍受青睐呢?在PCB设计中又如何能保证其良好的性能呢?带着这两个问题,我们进行下一部分的讨论。

何为差分信号?通俗地说,就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值

来判断逻辑状态“0”还是“1”。

而承载差分信号的那一对走线就称为差分走线。

差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面:

a.抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎

是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可

以被完全抵消。

b.能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场

可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

c.时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端

信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,

同时也更适合于低幅度信号的电路。

目前流行的LVDS(low voltage differential signaling)就是指这种小振幅差分信号技术。

……

由于篇幅问题,这里对差分信号不做深入介绍了。

3.如何在Allegro中定义Differential Pair属性

设定一对Net为Differential Pair的方式有两个:

方法一:. 菜单 Logic>Differential Pair…

已设定好的

Differential Pair

的名字和Net

板子上的所有

Net名称

1.输入Differential Pair名字

3.点击Add

添加完成设定

2.分别在上面Net列表或直接点击

板子上网络选择设定的Net

方法二: Constraint Manager

点击板子名称右

击鼠标出现菜单

选择Create。

点击Create

输入名字

完成设定选择两个Net

图示及参数设置

Primary gap

Primary line width

Neck gap

Neck width 靠一起的长度最大允许没有最小走线间距走线间距允许误差

长度误差

最大允许

最后需要Assign 分配,给设定differential pair属性的的网络具体遵循哪个设定值,

前面定义的值

把定义指定给具体设定

的differential pair

4.怎样设定Differential Pair在不同层面控制不同线宽与间距

由于需要控制差分阻抗, 表层为微带线,内层为带状线,这样如果表里层使用相同线宽线距这样就比较难控制阻抗一致,因此就带来了不同层面走不同线宽和间距的差分线,如表层走线宽6间距6, 内层线宽5间距8.

由于15版Allegro在DiffPair参数设置里不能设置不同层面的线宽线距,见下面图片:

所以我们需要使用其它方法来实现以上问题.具体见下面步骤.

步骤:

1.按照上面的方法,把需要定义差分线的net一对对地定义好.

2.使用Edit-Properties给需要定义的差分线指定Net_Physical_Type

Net_Physical_Type:名字可以随便取.

3.在Setup-Constraints的Physical rule set中添加一个Constraint Set Name,见下图:

4.选择不同Subclass设置不同的Min line width(差分线线宽)和Diff Pair primary gap(差

分对之间的间距).

5.重复步骤4把所有层面的线宽、间距都设好.

6.在Physical的Assignment Table中给Physical Property指派好Physical Constraint Set

值,见下图:

7.完成,见下图效果:

当通过Via换层是自动变化线宽和间距.

上海索服电子科技有限公司5.怎样设定Differential Pair对与对之间的间距

这个设定续上面设置,如果用户还需要设差分对与对之间的间距,那应该怎么办呢?

见下图:

这个和普通线间距设置方法是一样的,这里不详细介绍了,大致步骤:

1.使用Edit-Property给差分信号定义:Net_Spacing_Type

2.Setup–Constraint 设置Spacing rules set的Set value…值

3.Setup-Constraint设置Spacing rules set的Assignment table…

4.完成

――[全文完]――

以上技术文档由上海索服电子科技有限公司提供

更多EDA技术文档请访问:

P 11/ 11 Copyright @ 2005-2006 by Shanghai Sofer Electronics & Technology Co., Ltd.。