Cadence Allegro 16.2规则设置

cadence 16.2约束规则设置

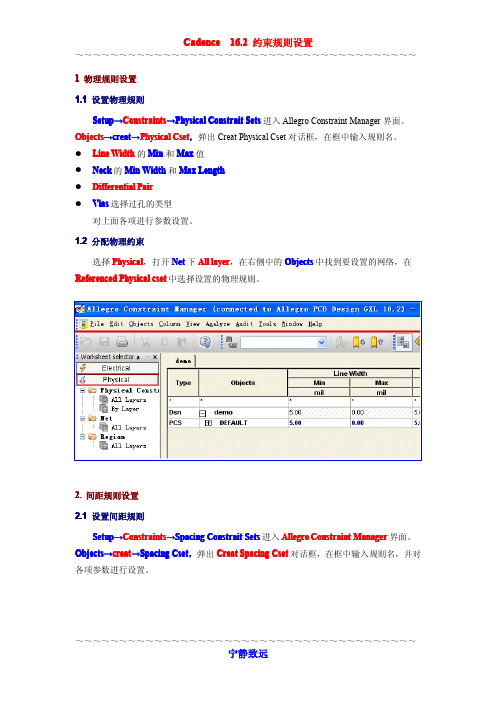

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ 1 物理规则设置 1.1 设置物理规则 →Constraints →Physical Constrait Sets 进入 Allegro Constraint Manager 界面。 Setup Setup→ Constraints→ →creat →Physical Cset,弹出 Creat Physical Cset 对话框,在框中输入规则名。 Objects Objects→ creat→ � � � � Line Width 的 Min 和 Max 值 Neck 的 Min Width 和 Max Length Differential Pair Vias 选择过孔的类型 对上面各项进行参数设置。 1.2 分配物理约束 选择 Physical,打开 Net 下 All layer,在右侧中的 Objects 中找到要设置的网络,在 Referenced Physical cset 中选择设置的物理规则。

3. 设置网络属性 →Constraints →Constrait manager 后,打开 Properties ,分别对 Net Properties 下 Setup Setup→ Constraints→ 的 Electrical Properties,General Properties 和 Ratsnest Properties 进行设置。 4. 元件属性设置 4.1 设置元件属性 →Constraints →Constrait manager 后 , 打 开 Properties , 分 别 对 Component Setup Setup→ Constraints→ Properties 下的 General,Thermal,Swapping 和 Reuse 属性进行设置。 4.2 设置管脚属性 Setup →Constraints →Constrait manager 后,打开 Properties ,分别对 Pin Properties Setup→ Constraints→ 下的 General,Shapes 和 Manufacturing 属性进行设置。

Allegro约束规则设置

约束规则的设置孙海峰在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。

在Allegro PCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。

首先,需要认识一下,Allegro PCB的约束管理器:在PCB设计界面中,执行Setup/Constraints/Constraint Manager命令,弹出Allegro Constraint Manager对话框,如下图。

在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。

约束规则可以按板层、网络或者区域进行设置。

约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。

工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。

在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。

约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。

一、电气规则设置在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/Electrical CSet命令可新建电气规则。

1、选择信号完整性仿真规则Signal Integrity属性,其中包括电气属性、反射属性、单调失真属性、初始串扰、仿真串扰以及同步开关噪声这六个规则设置。

Allegro基本规则设置指导书

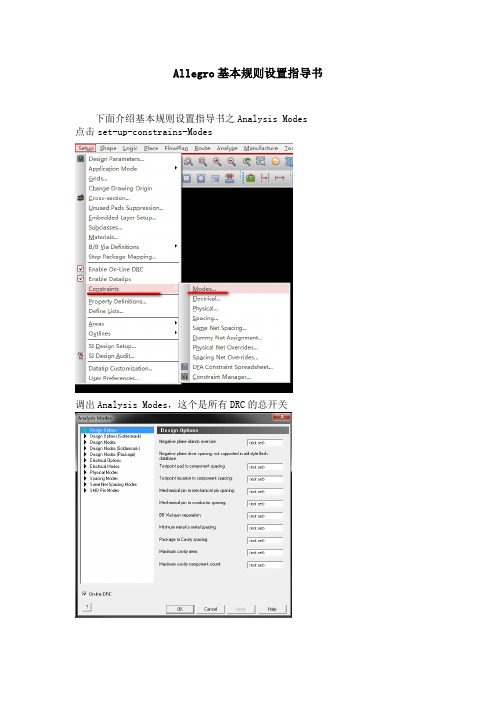

Allegro基本规则设置指导书下面介绍基本规则设置指导书之Analysis Modes 点击set-up-constrains-Modes调出Analysis Modes,这个是所有DRC的总开关下面介绍常用的一些开关设置1.Design Options (Soldermask)从上往下阻焊到阻焊的间距阻焊到pad和走线间距阻焊到shape1的间距钢网到钢网的间距2.Design Mode从上往下测试点Pad到器件DRC开关测试点到器件的DRC开关测试点在器件下方的DRC开关重孔开关3.Design Mode(soldermask)从上往下阻焊到阻焊的DRC开关阻焊到Pad和线的DRC开关阻焊到shape的DRC开关钢网到钢网的DRC开关4.Design Modes(Package)从上到下器件和器件的DRC开关器件超出package keepin的DRC开关器件在器件禁布的DRC开关5.Electric options从上往下开启最短长度延时开启相对长度延时开启pin delay开启Z轴延时6.Electric Modes从上往下绝对长度延时开关相对长度延时开关总长DRC开关差分检查DRC开关7.Physical Mode从上往下走线出现T分支DRC开关Pad和Pad连接的DRC开关过孔使用类型DRC开关8.Spacing Modes默认全部选择所有间距相关的DRC开关都要打开9.Same Net Spacing Modes同名网络DRC开关,默认全部打开10.SMD Pins Modes盘中孔DRC默认是关闭的,可以用来检查孔是否打在SMD的pin上的情况11.开启DRC总开关On-line DRC是需要开启的,否则所有DRC都不起作用Physical规则设置下面介绍规则设置指导书之Physical规则设置点击Set-up-constraints-Constraint Manager打开规则管理器1.设置Physical规则2.打开时默认有个Default规则从左往右Line Width最小线宽最大线宽Neck最小线宽Neck的走线长度3.如果是差分规则,需要额外设以下参数从左往右最小线间距差分对之间的间距Neck走线差分之间的间距正公差负公差4.Pad-Pad connect选择Not Allowed,不允许Pad和Pad直接连接简而言之,就是允许盘中孔Physical规则匹配下面介绍基本规则设置指导书之Physical规则匹配1.在这里给网络匹配上相应的规则2.可以给同一类型的网络建立一个Net Class,匹配规则更方便选中需要的net右击创建Class3.同时如果是差分对的话,需要创建差分对选择需要的两个net,Create Differential PairPhysical Region下面介绍基本规则设置指导书之Physical Region1.空白的地方创建一个Region2.给新建的Region匹配一个规则,所有区域里面的Physical相关的都按照Region的规则来3.当部分网络想按照本身的规则来匹配,可以创建region-Class4.然后匹配回它原来的规则5.后面这些规则一般按照Physical里面设置的规则不修改Spacing规则设置下面介绍基本规则设置指导书之Spacing规则设置1.设置Line到其它的间距规则从左往右线到线,通孔pin,表贴pin,测试pin,通孔Via,盲埋孔,测试孔,微孔,铜皮,Bond finger,hole之间的间距2.设置pin到其它的间距,通孔pin和表贴pin3.设置Via到其它的间距4.设置shape到其它的间距5.设置Bond Finger到其它的间距7.设置盲埋孔之间的间距Spacing规则匹配下面介绍基本规则设置指导书之Spacing规则匹配2.可以把同一类网络创建一个Net Class给Net Class匹配间距规则会更为方便Spacing规则Class to Class 下面介绍基本规则设置指导书之Spacing规则Class to Class1.当我们需要给组和组之间设置一个间距规则时候需要用到这个功能在需要的Net Class地方创建一个Class to Class2.Class to Class匹配一个规则Spacing Region 下面介绍基本规则设置指导书之Spacing Region1.空白的地方创建一个Region2.给创建好的Region 匹配一个规则3.当网络需要在Region中需要按照自身的规则匹配时,可以创建RegionClass来匹配4.Region也支持Class to Class规则,点击ok即可5.设置好的如下图Same Net Spacing规则设置下面介绍基本规则设置指导书之Same Net Spacing规则设置8.设置Line到其它的间距规则从左往右线到线,通孔pin,表贴pin,测试pin,通孔Via,盲埋孔,测试孔,微孔,铜皮,Bond finger,hole之间的间距9.设置pin到其它的间距,通孔pin和表贴pin10.设置Via到其它的间距11.设置shape到其它的间距12.设置Bond Finger到其它的间距13.设置Hole到其它的间距14.打开或者关闭同名网络开关Same Net Spacing规则匹配下面介绍基本规则设置指导书之Same Net Spacing规则匹配3.匹配设置好的Same Net间距规则Same Net Spacing Region下面介绍基本规则设置指导书之Same Net Spacing Region6.空白的地方创建一个Region7.给创建好的Region 匹配一个规则8.当网络需要在Region中需要按照自身的规则匹配时,可以创建RegionClass来匹配Electrical Min Max Propagation Delay下面介绍基本规则设置指导书之Electrical Min Max Propagation Delay在这里可以设置走线的最短和最长的长度,这个过孔和pin delay的长度也会计算进去Electrical Total Etch Length下面介绍Allegro基本规则设置指导书之Electrical Total Etch Length这里可以设置走线的最短和最长的值,这里的值只是走线长度,不包含过孔和pin delay的长度Electrical Differentail Pair下面介绍基本规则设置指导书之 Electrical Differentail Pair这里一般用来设置差分的对内等长,在tolerance这里设置Electrical Relative Propagation Delay下面介绍基本规则设置指导书之 Electrical Relative Propagation Delay1.这里用来设置等长规则2.在创建Match Group之前要创建pin pair3.创建好pin pair之后,选中需要做等长的网络,创建Match Group4.创建好Match Group之后,Scope选择Global, Tolerance 输入公差值5.选择一个网络作为基准。

Cadence_SPB16.2中文教程

2

图 1.3 表贴元件焊盘设置

如果是通孔焊盘,需要填写的参数有: BEGINLAYER 层的 Regular Pad,Thermal Relief,Anti Pad; DEFAULTINTERNAL 层的 Regular Pad,Thermal Relief,Anti Pad; ENDLAYER 层的 Regular Pad,Thermal Relief,Anti Pad; SOLDEMASK_TOP 层的 Regular Pad; PASTEMASK_TOP 层的 Regular Pad。 如图 1.4 所示。 在 BEGINLAYER、DEFAULTINTERNAL、ENDLAYER 三个层面中的 Thermal Relief 可以 选择系统提供的默认连接方式,即 Circle、Square、Oblong、Rectangle、Octagon 五种,在 PCB 中这几种连接方式为简单的‘+’形或者‘X’形。也可以选用自己画的热风焊盘连接 方式,即选择 Flash。这需要事先做好一个 Flash 文件(见第二节)。这些参数的设置见下面的 介绍。

第 2 章 建立封装 .......................................................................................................10

第 3 章 元器件布局 ...................................................................................................23

第 5 章 输出底片文件 ...............................................................................................70

Cadence快速入门视频教程的SPB_16.2版本一

2. 教程内容

3. 软件介绍 Design Entry CIS:板级原理图工具 Design Entry HDL:设计芯片的原理图工具,板级设计不用 Layout Plus:OrCAD 自带的 PCB 布线工具,功能不如 PCB Editor 强大 Layout Plus SmartRoute Calibrate:OrCAD 自带的 PCB 布线工具,功能不如 PCB Editor 强大 PCB Editor:Cadence 的 PCB 布线工具 PCB Librarian:Cadence 的 PCB 封装制作工具 PCB Router:Cadence 的自动布线器 PCB SI:Cadence 的 PCB 信号完整性信号仿真的工具 SigXplorer:Cadence 的 PCB 信号完整性信号仿真的工具

接下来,设置输入管脚的正负属性 :点击 Toolbar 的 Place Text,或者菜单 Place/Text,如下图:

输入-,点击 OK,再输入+,点击 OK, 如下图: 接下来放置管脚,如下图:

现在,完成了 NE5532 中两个运放中的一个,现在编辑另一个:

Ctrl+N,或者 View/Next Part,如下图:

4. 软件列表

5. 开始学习 Design Entry CIS 启动:Start/Cadence SPB 16.2/Design Entry CIS 启动后,显示下图:

里面有很多选项,应该是对应不同的 License

本教程使用:OrCAD Capture CIS 我个人认为:Allegro PCB Design CIS XL 是所有可选程序中,功能最强大的,但不知道,强在哪里;而且 本教程的原理图文件可以使用上表中不同的程序打开 6. 选择 OrCAD Capture CIS,启动后显示下图

Cadence_Allegro16.2常用操作方法

Cadence_Allegro16.2常用操作方法Orcad中图纸模版的设置1.Option—>Design Template—>Title Block,Symbol栏中输入Title Block所在的.OLB库文件位置(E:\cadence_design\schlib\DIDIDEV.OLB),Title Block中输入模版文件名“TitleBlock_SHU”,内有公司的logo。

2.Text栏内Title中输入正在设计的板的名称,Document Number中输入文件编号,Revision中输入版本号。

3.在添加新页时,模版图纸的上述信息会自动添加Orcad 中快速修改所有零件的Footprint方法一:一页一页修改,打开某页,按CTRL+A,选中当前页所有器件,再点右键,选Edit属性,在弹出对话框中选Parts栏,按要修改REF 排序,用左键拖拉要修改的为同种封装器件再点右键,然后击EDIT,填入封装就成批修改了方法二:选择顶层原理图(SCHEMATIC1),右键选Edit Object Properties,列出所有元件,找到PCB Footprint 那项,可以逐个填入,也可以相同封装填一个,然后拖动该黑框的右下角十字形复制。

Orcad BOM表中输出原件的PCBfootprint封装型号选中顶层项目设计.dsn标题,在tools菜单中选择bill of materials,在header栏追加填入“\tPCBFootPrint”,在Combined property string栏中追加填入“\t{PCB footprint}”,不选Open in Excel,生成.BOM文件后,用excel手工导入.BOM文件,在导入步骤三中选择“文本”方式。

然后在Excell 中修改BOM表的边框等格式。

Orcad还有一处地方可输出带有机械尺寸的BOM表,选中顶层项目设计.dsn标题,在report菜单中选择CIS bill of Materials,有standard和Crystal report两种形式输出。

CadenceSPB16.2入门教程——教你手动建立封装

Cadence_SPB16.2入门教程——手动建立封装建立封装2.1 新建封装文件用Allegro来演示做一个K4X51163内存芯片的封装。

打开程序->Cadence SPB 16.2->PCB Editor,选择File->New,弹出新建设计对话框,如图2.1所示。

图2.1 新建封装在Drawing Type列表框中选择Package symbol,然后点击Browse按钮,选择保存的路径并输入文件名,如图2.2所示。

图2.2 选择保存封装的路径点击打开回到New Drawing对话框,点击OK退出。

就会自动生成一个bga63.dra的封装文件。

点击保存文件。

2.2 设置库路径在画封装之前需要在Allegro设置正确的库路径,以便能正确调出做好的焊盘或者其它符号。

打开之前建立的封装文件bga63.dra,选择Setup->User Preferences,如图2.3所示。

图2.3 设置路径弹出User Preferences Editor对话框,如图2.4所示。

图2.4 User Preferences Editors对话框点击Paths前面的‘+’号展开来,再点击Library,现在只需要设置两个地方就可以了,padpath(焊盘路径)和psmpath(封装路径)。

点击padpath 右边Value列的按钮。

弹出padpath Items对话框,如图2.5所示。

图2.5 padpath 对话框点击图标按钮,在padpath Items对话框的列表框中新增了一个空项,点击右边的按钮弹出一个路径选择对话框,选择你存放焊盘的文件夹加入其中,点击OK。

如果想要加入多个路径,重复上述过程就即可。

还可以点击padpath Items 对话框右上角的下个上移下移箭头来移动列表框中的项目,越靠上的优先权越高,如果不同路径中的焊盘或封装出现相同名字的时候allegro会优先选用最上面的路径中的焊盘和封装。

allegro16.2 元器件布局 免费下载

Cadence_SPB16.2入门教程——元器件布局元器件布局3.1 建立电路板(PCB)打开程序->Cadence SPB 16.2->PCB Editor,选择File->New,弹出新建设计对话框,如图3.1所示。

图3.1 新建设计对话框点击Browse按钮,弹出文件对话框,在图标列表内选择保存的路径,输入文件名,最好单独保存在一个文件夹里,如图3.2 所示。

图3.2 选择文件保存路径单击打开关闭文件对话框。

回到New Drawing对话框,单击OK退出。

如果想使用向导来建立电路板,则在New Drawing对话框中选择Board(wizard),如图3.3所示。

图3.3 使用向导方式生成电路板选择Board(wizard)点击OK后就会出来一个向导对话框,按照提示一步一步设置好直到完成即可。

3.2 导入网络表打开程序->Cadence SPB 16.2->PCB Editor,打开3.1节用手工建立好的电路板test.brd。

选择菜单File->Import->Logic,如图3.4所示。

图3.4 导入网络表弹出Import Logic对话框。

如图3.5所示。

在Import logic type组合框内选择网络表输出的类型,因为原理图是用Orcad Capture设计的,所以选择Design entry CIS(Capture)。

Place changed component组合框用来选择导入新的网络表后是否更新PCB中的元件封装。

·Always:总是更新;·Never:从不更新;·If same symbol:一样的时候不更新。

·Allow etch removal during ECO:新导入网络表后,allegro将网络关系改变了的管脚上的多余走线删除。

·Ignore FIXED property:当满足替换条件或者其它更改删除时是否忽略有FIXED属性的元件、走线、网络等等。

Cadence SPB 16.2 Guide

Cadence SPB 16.2安装指南将此处改为你的计算机名(1)用记事本打开Crack目录的license.lic文件,将Server后ID前的那段文字改成你的计算机名。

先选择安装License Manager(2)运行Setup程式,首先安装License Manager。

(4)此处保留5280的端口数即可,但程式本身会留一些空格,直接点Next会 报端口错误,鼠标点击此框,按Del删除所有内容和空格后再填入5280即可。

(6)启动LmTools工具来设定License Manager刚才修改过的计算机名(5)License Manager安装成功后可以看到我们在Lic文件中修改过的计算机名(7)启动LmTools后选择Using Service而不是License File(8)把修改好的license.lic文件复制到Cadence安装目录的License Manager目录下(9)Path to the license file,点击Browese选择刚刚复制到LicenseManager的目 录的那个lic文件。

(10)选择完成后点击Save Service,然后在如下对话框确认“是”。

(11)在此启动或停止License Manager服务,软件正常工作时要保证服务处于启动状态。

(12)以上完成后,选择Product Installation。

(13)安装过程中如果有提示要选择什么授权文件,一律掠过点Next,如果一般只使用公司的lib文件,建议就不要安装自带的lib了,因为安装的时间很漫长。

(14)这步很重要,在license path文本框中填入5280@hostname即可,这里的hostname 就是之前修改lic文件时用的那个计算机名。

(15)把crack目录下的crack.exe程式拷贝到Cadence的安装目录下,然后运行,直到黑色 命令提示符窗口自动关闭。

(16)最后,重新启动系统,安装完成。

Cadence.Allegro.SPB.v16.2破解及安装步骤(已验证可行)

Cadence.Allegro.SPB.v16.2破解及安装步骤(已验证可行)严正声明:该破解及安装方法仅用于交流学习该软件,请不要以任何形式用于商业目的,本人不承担任何由个人或企业将此软件用于商业目的而引发的一切法律纠纷所带来后果,如需用于商业目的,请向Cadence 公司购买授权;否则后果自负。

从上一年到现在,一共安装了Cadence.Allegro.SPB.v16.2四次,非常痛惜,由于种种原因,前三次都以失败而告终,通过网上的安装经验及自己的摸索,功夫不负有心人,终于在今天下午将Candence Allego SPB16.2安装成功。

现把安装经验及注意事项分享如下:1.简介Cadence? Allegro是 Cadence 推出的先进 PCB 设计布线工具。

Allegro 提供了良好且交互的工作接口和强大完善的功能,和它前端产品 Capture 的结合,为当前高速、高密度、多层的复杂 PCB 设计布线提供了最完美解决方案。

Allegro 拥有完善的 Constraint 设定,用户只须按要求设定好布线规则,在布线时不违反 DRC 就可以达到布线的设计要求,从而节约了烦琐的人工检查时间,提高了工作效率!更能够定义最小线宽或线长等参数以符合当今高速电路板布线的种种需求。

2. 安装及破解步骤步骤:一、下载好所需的安装光盘镜像文件,VeryCD网站上有有两个版本,一个是ISO 文件(共有3个ISO文件,占用空间1630MB左右);另个版本是两个BIN文件(占用空间1.10GB左右),本人所用的是第二个版本。

二、将上述文件(两个版本都可以)加载到虚拟光驱中,并打开,运行setup.exe 文件。

三、点击setup 进入安装界面,首先点击Licence Manger.如图所示:四、在首次安装LICENSE MANAGER的时候,安装程序会要求给出LICENSE FILE LOCATION,不要填任何东西,直接点击CANCLE结束这个对话框,如下图所示:五、将LICENSE.DAT复制到CADENCE文件夹中,然后用记事本打开它,将this_host改成你的计算机名称,并保存;六、查看计算机名称,如下图所示,我的计算机名称是 WWW-97F34E33509,而不是 WWW-97F34E33509. 就是说名称不包含末尾的句号!七、将cdslmd.exe复制到刚刚安装的LICENSE MANAGER文件夹中,覆盖原有的相同程序。

Allegro约束规则设置

Allegro约束规则设置约束规则的设置孙海峰在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。

在Allegro PCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。

首先,需要认识一下,Allegro PCB的约束管理器:在PCB设计界面中,执行Setup/Constraints/Constraint Manager命令,弹出Allegro Constraint Manager对话框,如下图。

在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。

约束规则可以按板层、网络或者区域进行设置。

约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。

工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。

在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。

约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。

一、电气规则设置在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/Electrical CSet命令可新建电气规则。

1、选择信号完整性仿真规则Signal Integrity属性,其中包括电气属性、反射属性、单调失真属性、初始串扰、仿真串扰以及同步开关噪声这六个规则设置。

ALLEGRO 约束规则设置步骤[图解]

![ALLEGRO 约束规则设置步骤[图解]](https://img.taocdn.com/s3/m/ec584a196bd97f192279e956.png)

ALLEGRO 约束规则设置步骤[图解]本文是我对约束规则设置方面的一些理解,希望对新手能有所帮助。

由于本人水平有限,错误之处难免,希望大家不吝赐教!在进行高速布线时,一般都需要进行线长匹配,这时我们就需要设置好constraint 规则,并将这些规则分配到各类 net group 上。

下面以 ddr为例,具体说明这些约束设置的具体步骤。

1.布线要求DDR 时钟:线宽 10mil,内部间距 5mil,外部间距30mil,要求差分布线,必需精确匹配差分对走线误差,允许在+20mil 以内DDR 地址、片选及其他控制线:线宽 5mil,内部间距 15mil,外部间距 20mil,应走成菊花链状拓扑,可比 ddrclk 线长 1000-2500mil,绝对不能短DDR 数据线,ddrdqs,ddrdm线:线宽 5mil,内部间距 15mil,外部间距 20mil,最好在同一层布线。

数据线与时钟线的线长差控制在 50mil 内。

2.根据上述要求,我们在 allegro 中设置不同的约束针对线宽(physical),我们只需要设置 3 个约束:DDR_CLK, DDR_ADDR, DDR_DATA设置好了上述约束之后,我们就可以将这些约束添加到 net上了。

点击 physical rule set 中的 attac h……,再点击右边控制面板中的more,弹出对话框如上图所示,找到 ckn0和 ckp0,点击 apply,则弹出选中左边列表中的NET_PHYSICAL_TYPE, 在右边空格内输入DDR_CLK, 点击apply,弹出即这两个 net已经添加上了 NET_PHYSICAL_TYPE 属性,且值为 DDR_CLK.类似的,可以将 DDR 数据线,数据选通线和数据屏蔽线的 NET_PHYSICAL_TYPE 设为DDR_DATA, DDR 地址线,片选线,和其他控制线的 NET_PHYSICAL_TYPE 设为DDR_ADDR. 上述步骤完成后,我们就要将已经设好的约束分配到这些 net group 上。

ALLEGRO16.2的区域规则设置

终于知道区域规则怎么用了,还不会的看过来(16.2)

1.在physical或者spacing工作表下新建一个区域(Region)约束,如下图。

下载 (89.01 KB)

2009-4-1 11:24

名字可以随便命名,比如我这里命名为CPU_BGA,如图。

2.分别在physical和spacing工作表里设定好刚才设定的区域规则参数,我是这样设的,不对别砸砖头啊。

Physical:

Spacing

好了,规则都设好了,下面回到pcb edit。

3.在pcb edit里画一个区域(当然要先打开你的板子PCB了),选择shape/regtanglar,你也可以用别的命令,这步主要是

画一个区域。

如图。

4.右边的options窗口中,active class subclass选择constrait region,在assign to region里选择刚刚建好的好个区域规则

(cpu_bga)将这个规则指定到这个区域中。

如图

5.在PCB中画出一个区域,比如我这里是把BGA芯片圈住。

如图。

6.完成,现在你在这个BGA里面的所有线宽、间距都是按cpu_bga这个规则了,出了外面就是另外的规则了,你可以

另外指定了。

看到没有,出了这个区域线宽变了。

8.jpg (60.12 KB)。

Cadence_SPB16.2入门教程——PCB布线精品文档14页

Cadence_SPB16.2入门教程——PCB布线(一)PCB布线4.1 PCB层叠结构层叠结构是一个非常重要的问题,不可忽视,一般选择层叠结构考虑以下原则:·元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;·所有信号层尽可能与地平面相邻;·尽量避免两信号层直接相邻;·主电源尽可能与其对应地相邻;·兼顾层压结构对称。

对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在 50MHZ以上的(50MHZ以下的情况可参照,适当放宽),建议排布原则:·元件面、焊接面为完整的地平面(屏蔽);·无相邻平行布线层;·所有信号层尽可能与地平面相邻;·关键信号与地层相邻,不跨分割区。

基于以上原则,对于一个四层板,优先考虑的层叠结构应该是:·S ←信号·G ←地平面·P ←电源层·S ←信号对于一个六层板,最优的层叠结构是:·S1 ←信号·G1 ←地平面·S2 ←信号·G2 ←地平面·P ←电源层·S4 ←信号对于一个八层板,有两种方案:方案 1:方案2:·S1 ←信号S1 ←信号·G1 ←地平面G1 ←地平面·S2 ←信号S2 ←信号·G2 ←地平面P1 ←电源层·P ←电源层G2 ←地平面·S3 ←信号S3 ←信号·G3 ←地平面P2 ←电源层·S4 ←信号S4 ←信号方案2主要是比方案1多了一个电源层,在电源比较多的情况下可以选择方案2。

对于更多层的结构也是按照上面的原则来定,可以参考其它的资料。

下面以SMDK6410核心板(设计为八层板)来设置层叠结构,包括规则设置,PCB布线等。

打开程序->Cadence SPB 16.2->PCB Editor,然后打开在第3 章布局好的PCB文件。

allegro 16.3等长规则设置

1、点击CM

2、在左边选择Electrical—>Net—>Routing—>Reห้องสมุดไป่ตู้ative Propagation Delay

3、选中工程名,点右键选择creat—>match group

4、这个“0”和上图的“flash_b0”是一样的。选中之后点右键如下图所示:

5、之后选择你要做等长的那组数据线。

6、选择pinpair

7、然后再选中工程名,点击右键,

选中工程名,点右键选择creat—>match group

这步同步骤3操作是一样的,但是不要命同样的名字。(我命的名字是B0)

8、

最后就是这个样子,箭头指向的地方就是这组数据线的误差范围。

Allegro16.2新功能教程

Allegro PCB Editor What's New in Release 16.0.Date : 2007/07/16.Author : Jonathan Lee.Revision : 1.0.Version : 16.0.備註:Allegro V16.0 新版本擁有全新的操作介面,使用者在人性化的介面上更能有效率地工作,以下為V16.0新增功能及新介面的介紹。

PCB Editor User Interface變更的部份為:.ToolbarIcon的更新、及工具群組的變更.Fold-Away Windows使工具視窗最大化,平時不使用時,Control Panel會自動收縮.Cadence Branding在SPB系列產品的左上角多了Cadence 商標.Context-sensitive Editing新的pre-selection編輯模式可依被點選物件相關參數設定或可執行之命令,可節省滑鼠遊標在工具列、control panel和物件間移動的時間,此模式可切換下列兩種模式。

A . General Edit Application Mode一般編輯模式,點選物件後會有該物件可執行的相關指令B . Etch Edit Application ModeEtch 相關應用編輯模式,點選物件後,就會自動依物件執行如列表之相關指令.Central Location for Design Parameters常用的設計參數集中在同一個控制界面,新的參數設定界面包含 Display、Design、Text、Etch Edit、Shape and Manufacturing .Color and Visibility EnhancementsAllegro Products Now Support OpenGL Standard支援Open GL顯示,若要最佳效能,基本配備為獨立顯示卡128MB,系統1GB以上的RAMModernization of Color/Visibility User Interface新的顏色層面顯示界面Color Support Extended to 192顏色可支援192色,二個調色盤,每個調色盤為6x16的矩陣,一個調色盤共96色Transparent Graphics Improve Visibility Through the PCB 可設定物件的透明度,使物件透明化,讓重疊的物件更易顯示Quick Access to Commonly Used Subclasses可以將常用的層面設定為我的最愛,自設常用的層面可在同一個畫面作層面控制,而這個新的設定會在local pcbenv內存一個 myfavorites.txt 儲存相關的層面設定。

allegro16.2 PCB布线2

4.2 布线规则设置布线约束规则是PCB布线中很重要的一步工作,规则设置和好坏直接影响到PCB信号的好坏和工作效率。

布线规则主要设置的是差分线,线宽线距,等长匹配,过孔等等。

下面一步一步设置这些规则。

约束规则在约束管理器中设置。

选择菜单 Setup->Constraints->Constraint Manager。

或者直接点击工具栏上的图标按钮打开约束管理器,如图4.5所示。

图4.5 打开约束管理器打开约束管理器后的界面如图4.6所示。

图4.6 约束管理器可以看到界面包含了两个工作区,左边是工作簿/工作表选择区,用来选择进行约束的类型;右边是工作表区,是对应左边类型的具体约束设置值。

在左边共有6个工作表,而一般只需要设置前面四个工作表的约束就可以了,分别是Eelctrical、Physical、Spacing、Same Net Spacing。

分别对应的是电气规则的约束、物理规则的约束,如线宽、间距规则的约束(不同网络)、同一个网络之间的间距规则。

为了能更好的使用约束管理器,先做一点基本概念的解释。

4.2.1 对象(object)对象是约束所要设置的目标,是具有优先级的,顶层指定的约束会被底层的对象继承,底层对象指定的同样约束优先级高于从顶层继承下来的约束,一般尽量在顶层指定约束。

最顶层的对象是系统system,最底层的对象是管脚对pin–pair。

对象的层次关系依次为:系统(system)-> 设计(Designe)-> 总线(bus)->网络类(net class)->总线(bus)-> 差分对(differential pair)-> 扩展网络/网络(Xnet)-> 相对或匹配群组(Match group)-> 管脚对(Pin pair)(1)系统(system)系统是最高等级的对象,除了包括设计(比如单板)之外,还包括连接器这些设计的扩展网络、互连电缆和连接器。

cadence规则设置介绍

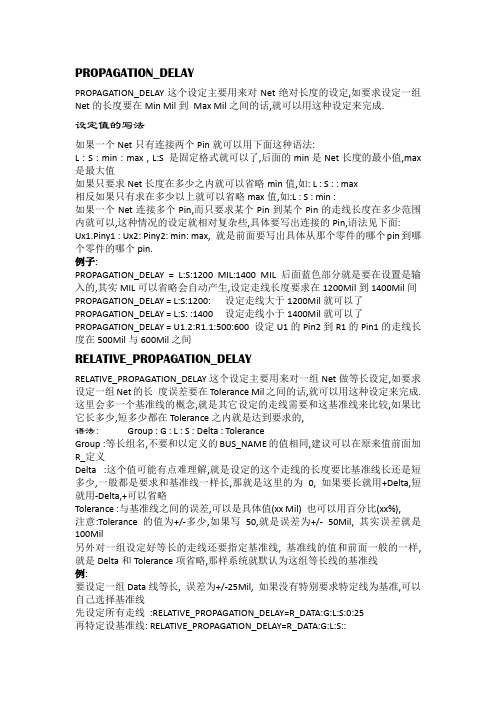

PROPAGATION_DELAYPROPAGATION_DELAY这个设定主要用来对Net绝对长度的设定,如要求设定一组Net的长度要在Min Mil到Max Mil之间的话,就可以用这种设定来完成.设定值的写法如果一个Net只有连接两个Pin就可以用下面这种语法:L : S : min : max , L:S 是固定格式就可以了,后面的min是Net长度的最小值,max 是最大值如果只要求Net长度在多少之内就可以省略min值,如: L : S : : max相反如果只有求在多少以上就可以省略max值,如:L : S : min :如果一个Net连接多个Pin,而只要求某个Pin到某个Pin的走线长度在多少范围内就可以,这种情况的设定就相对复杂些,具体要写出连接的Pin,语法见下面:Ux1.Piny1 : Ux2: Piny2: min: max, 就是前面要写出具体从那个零件的哪个pin到哪个零件的哪个pin.例子:PROPAGATION_DELAY = L:S:1200 MIL:1400 MIL 后面蓝色部分就是要在设置是输入的,其实MIL可以省略会自动产生,设定走线长度要求在1200Mil到1400Mil间PROPAGATION_DELAY = L:S:1200: 设定走线大于1200Mil就可以了PROPAGATION_DELAY = L:S: :1400 设定走线小于1400Mil就可以了PROPAGATION_DELAY = U1.2:R1.1:500:600 设定U1的Pin2到R1的Pin1的走线长度在500Mil与600Mil之间RELATIVE_PROPAGATION_DELAYRELATIVE_PROPAGATION_DELAY这个设定主要用来对一组Net做等长设定,如要求设定一组Net的长度误差要在Tolerance Mil之间的话,就可以用这种设定来完成. 这里会多一个基准线的概念,就是其它设定的走线需要和这基准线来比较,如果比它长多少,短多少都在Tolerance之内就是达到要求的,语法:Group : G : L : S : Delta : ToleranceGroup :等长组名,不要和以定义的BUS_NAME的值相同,建议可以在原来值前面加R_定义Delta :这个值可能有点难理解,就是设定的这个走线的长度要比基准线长还是短多少,一般都是要求和基准线一样长,那就是这里的为0, 如果要长就用+Delta,短就用-Delta,+可以省略Tolerance :与基准线之间的误差,可以是具体值(xx Mil) 也可以用百分比(xx%),注意:Tolerance的值为+/-多少,如果写50,就是误差为+/- 50Mil, 其实误差就是100Mil另外对一组设定好等长的走线还要指定基准线, 基准线的值和前面一般的一样,就是Delta和Tolerance项省略,那样系统就默认为这组等长线的基准线例:要设定一组Data线等长, 误差为+/-25Mil, 如果没有特别要求特定线为基准,可以自己选择基准线先设定所有走线:RELATIVE_PROPAGATION_DELAY=R_DATA:G:L:S:0:25再特定设基准线: RELATIVE_PROPAGATION_DELAY=R_DATA:G:L:S::如果有根线要比基准线长50Mil则设定为:RELATIVE_PROPAGATION_DELAY=R_DATA:G:L:S:50:25IMPEDANCE_RULEIMPEDANCE_RULE=A:B:C:DA:起点PINB:终点PINC:阻抗的数值大小D:阻抗的误差大小例如:(1).IMPEDANCE_RULE=ALL:ALL:50ohm:10ohm设定走线的阻抗是50ohm,误差值是正负10ohm(2).IMPEDANCE_RULE=U1.1:R1.1:50ohm:20%设定走线在U1.1 到R1.1 之间的阻抗是50ohm,误差是正负20%SWITCH/SETTLE_DELAY在约束管理器界面的“NET”栏部分打开timing,点击switch/settle delay, 在min 和max栏分别设置网络的信号上升沿和下降沿,输入方法为min:“0.25:0.26”,max:“3.25 3.25”即表示网络的信号上升沿和下降沿分别为0.25ns和0.26ns。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Spacing规则(约束)

Rex

dlutarm@

2009-07-02 Allegro 16.0以后版本的约束规则设置较之前有很大改变,对于用惯了15.x的人

来说,很多不习惯新的约束管理器。

和在对待女人的态度上,恰相反。

80后说90后脑残,15.7说16.2脑残,Xp说Vista脑残。

Vista确实很脑残。

新事物取代旧事物是自然界发展的客观规律。

说明:

1本文只介绍了Spacing约束的设置,因为Physical规则通常来说都设置的非常简单。

掌握了Spacing规则Physical规则对你来说一定是小Case。

另外,Physical 规则的设置也写的话,一定显得都是在重复Spacing的设置;

2文中所有的规则(约束),如不特殊说明默认情况下均指Spacing规则(约束);3对于Electrical的约束,是另一种约束,本文不作讨论。

约束的设置方式:

1直接的:Net中写数值,

2 间接的:创建Constraint Set,然后Assign给Net;

这两种都很常用,后者管理方便。

在Physical和Spacing设置中用后者比较好,但是在Electrical中,我看到很多很多的人会混合使用。

使用第二种约束设置方式的约束设置步骤:

1约束的对象

2约束的内容

3给对象分配内容

1

这3个步骤默默的引导着所有间接约束的设置。

基本约束

预备

先理解:

Net class

2

Net class-class

Region

Region-class

Region-class-class

Bus

……

现在不理解,想跳过去。

没关系,你早晚都要理解的。

最简单和稍微复杂一点的约束:

最简单的就是default的约束,稍微复杂一点的就是修改了一点默认的约束。

再复杂一些的约束:

你可能会想让不断变化的CLK(我们不考虑是不是差分)和其他的线离的远一些。

在Constraint Set中Create规则并设置规则的内容:

Creat & Set之后

3

给Net分配规则:

更高级的约束:

What Can U Think?

有了一根线的约束,贪婪的本性会使你你很快上升到两根线(通常是Diff)和更多线的约束。

两根线(Diff)的约束是不敢称更高级约束的,顶多算一种特殊的约束。

这里我们讨论更多线的约束。

你会想到一组BUS。

接下来,你会Create一组Bus,并且很自然你会在Referenced Spacing CSet里给这组Bus加上约束。

那么,我问你,这个Spacing究竟是什么呢?是BUS内部的Space吗?还是BUS和其他线的Space?恐怕你自己也说不清楚。

你可能会说是所有的线的Space,包括内部和外部。

你似乎觉得自己是对的。

那么我再问你:如果BUS_A的Space为Spac_XMIL,BUS_B的Space为Spac_YMIL(X!=Y),BUS_A和BUS_B之间的Space会是多少呢?X?Y?应该都不是。

(X+Y)/2?亏你想的出来。

其实你一开始就错了,问题不是这么Easy(当然也不复杂),否则怎么敢叫更高级的约束?

Create Net Class:

很多人不明白Net中Bus和Class的区别。

相同:都是一组线,

不同:一种是按照功能划分,一种按照规则划分。

有人会说Bus和Class也可以是一根线,我懒得理朝左右而不是前方,钻牛角尖的人。

这两种化划分是不是有点多此一举?NO,功能相同就规则相同吗?

Net Class是按照功能划分,所以这里我们需要先创建Net Class。

4

Net Class-Class

在左侧的Folder区域你可能早就注意到这个神秘的东西了。

他将带给我们什么样的惊喜呢?毫无疑问它将成为化解我们之前疑问的有力工具。

如何使用呢?Net Class-Class:

BUS和其他线间距:

5

BUS内部线间距:

BUS与BUS之间

6

Region 约束

没错,如你所想,这个约束就是15.X 的Area 约束。

这是个很有意思,并且非常有用的约束。

创建Region :

7

Assign to Region:

Assign What to Region?

Region!

Assign Region to Region?

First Region is具体(即能看得到的)的Region,Second Region is抽象的Region~ 这是个很有意思的地方。

Allegro里面有Assign different pair,Assign Refdes,这里却是Assign()to Region。

这个命令放在Logic中是很合理的,但是Cadence 公司干脆一不做二不休把这个命令去掉,需要在绘制区域的时候,在control panel 中Assign。

这时候Assign你就不用说括号中的内容了,因为Assign的肯定是你正在画的东西。

Assign Area to Region也有点不妥当吧?

(本文所有操作除了这个绘制约束Region(即具体的Region)在AllegroPCB完成外,其他操作均在约束管理器中完成。

)

shape->Rectangular矩形,Control Panel 的option的active class 选Constraint Region, subclass选择all.

assgin to region刚刚在规则管理中建立的区域规则。

8

创建sapcing规则

按层叠设置间距:

9

Spacing规则分配:

最高级的约束:

听到“最高级”你一定很激动,仿佛感觉自己已经练到了九阳神功的第九层。

指的是什么?

不要着急,先听我给你罗嗦几句话,这几句话你在除了这篇文章的任何资料上都看不到。

规则可以分为Physical和Spacing规则,但是你有没有想过分成Line(这里的Line 包括Bus,Bus也是Line)规则和Region规则也是很舒服呢?首先,这两个集合可以包括所有的规则而又没有冲突(真的没有冲突吗?);其次,这两个规则的划分会对更高级的约束设置带来意想不到的效果。

Line和Region都是带规则的,Line的规则是流动的,Region的规则是固定的。

当携带规则长驱直入的Line进入Region将怎么办呢?Region会觉得很爽吗?Line呢?究竟谁会更爽呢?比如一组线内部的间距是10mil,与其它线的间距是20mil,进入特殊的Region之后将使用何种规则?其实你是导演,你想让谁爽谁就爽。

他俩要是都爽了,你也就爽了。

很河蟹。

那么作为导演,你该如何满足他们的需求呢?(说白了就是解决规则冲突,让大家相安无事,共建河蟹PCB。

)

当不同规则的Class与Class在同一个Region不期而遇,或100个Class在同一个Region不期而遇,后果将怎么样呢?面对如此错中复杂的局面,你将何去何从?

Create Net Class:

要是还不明白Class和Bus的区别,再琢磨琢磨。

10

Create Region-Class。

创建之后:

11

到这里我们就可以给Region-Class分配规则了,我们先不分。

Create Region-Class-Class

Class与Class在同一个Region不期而遇了。

创建之后:

12

局部放大,相信你能看明白这个是什么意思。

Spacing规则分配:

包括Region-Class,Region-Class-Class

13

短短的时间之内,你就学会了九阳神功,从“欲渡黄河冰塞川,将登太行雪满山”的彷徨失措,摇身一变,你已经到了华山之巅,俨然一副“拔剑四顾心茫然”的独孤求败。

完。

因为自己也是初学Allegro,说的不妥之处请大家拍砖。

参考资料:无。

任何问题:dlutarm@

转载请注明出处。

14。