基于AT91RM9200微控制器的以太网接口驱动程序设计

浅谈AT91RM9200的嵌入式网络摄像机的设计与实现

浅谈AT91RM9200的嵌入式网络摄像机的设计与实现1.引言随着通信技术和网络技术的迅猛进展,通过网络远程实时监控重要场所已倍受人们关注,网络摄像机在此背景下产生,并成为人们关注的焦点。

网络摄像机是一种结合传统摄像机与网络技术所产生的新一代摄像机,它可以将影像通过网络传至地球另一端,且远端的扫瞄者不需用任何专业软件,只要标准的网络扫瞄器(如"Microsoft IE或Netscape)即可监视其影像。

网络摄像机要将高清楚度的实时视频信息通过互联网传送到监控终端,因其信息量巨大,所以必需压缩。

通常人们采纳与MPEG-4算法相结合的计划来实现,不仅编程工作量大,而且产品的成本高。

本文所介绍的网络摄像机采纳专用的MPEG-4压缩芯片、以作为操作系统,不仅开发便捷、成本低廉,而且实时性好,适用范围广。

2.系统总体设计系统总体设计包括硬件设计和软件设计两部分。

这两部分工作是相互联系的,需要交错举行,系统设计是开发人员举行的工作,他们将系统设计阶段得到的目标系统的规律模型转换为目标系统的物理模型,该阶段得到工作成绩――系统设计解释书是下一个阶段系统实施的工作依据。

硬件设计模块主要包括微控制器模块、微控制器是将微型计算机的主要部分集成在一个芯片上的单芯片微型计算机。

微控制器出生于20世纪70年月中期,经过20多年的进展,其成本越来越低,而性能越来越强大,这使其应用已经无处不在,遍及各个领域。

例如电机控制、条码阅读器/扫描器、消费类、嬉戏设备、电话、HVAC、楼宇平安与门禁控制、工业控制与和白色家电(洗衣机、微波炉)等。

压缩编码模块、网络接口模块和相机控制模块四部分。

微控制器模块主要由主控芯片、DataFlash和SDRAM(1)组成。

其中,主控芯片是囫囵控制系统的核心,它负责囫囵系统的调度工作。

DataFlash里固化了嵌入式Linux内核、及其文件系统、应用软件和第1页共7页。

AT91RM9200(DKEK) VxWorks BSP

AT91RM9200(DK/EK) VxWorks BSP开发者指南AT91RM9200(DK/EK) VxWorks BSP (1)开发者指南 (1)1. 介绍: (1)2. 软件包安装: (2)3. BSP结构: (2)•逻辑结构 (2)•文件结构 (4)4. 编译与裁减BSP (5)5. 硬件配置 (7)6.程序流程 (8)7. 程序说明 (8)1) 基本 BSP (8)2) 中断控制器驱动(intrCtl) (12)3) 时钟驱动(timer) (13)4) Uart 驱动(sio) (14)5) 网络驱动(end) (14)6) usb Host驱动(usb) (16)7) usb slave驱动(usbslave) (16)8) Display驱动(display) (18)9) CompactFlash卡驱动(cf) (20)10) 声音codec驱动(audio) (23)11) DataFlash卡驱动(dataflash) (25)12) MMC 卡驱动(mmc) (28)1. 介绍:本软件是基于ATMEL AT91RM9200 评估板(AT91RM9200DK 和 AT91RM9200EK) 的VxWorks 操作系统的BSP.它包含以下功能.1) AT91RM9200 高级中断控制器(AIC)2) AT91RM9200 系统时钟3) 2 个UART .4) 1 个10/100M 以太网口5) USB host (OHCI)接口.6) USB Salve 接口7) 1个 CompactFlash 接口8) 1个 Atmel DataFlash/MMC 接口.9) 1个 DAC3550A 音频输出接口.10) Epson s1d13806 显示接口.2. 软件包安装:本软件包有两部分组成.一部分是BSP(at91rm9200bsp.zip), 另一部分是范例项目(at91rm9200proj.zip).把at91rm9200bsp.zip 直接解压到Vxworks操作系统安装目录下的target/config目录下. 解压后会出现at91rm9200目录.把at91rm9200proj.zip 直接解压到Vxworks操作系统安装目录下的target/proj目录下. 解压后会出现at91rm9200目录.3. BSP结构:• 逻辑结构本软件包有两部分组成.一部分是BSP, 另一部分是范例项目.BSP 位于Vxworks操作系统安装目录下的target/config/at91rm9200.范例项目位于Vxworks安装目录下的target/proj/at91rm9200.启动Tornado后,打开workspace, target/proj/at91rm9200/at91.wsp.在这个workspace中包含了项目 at91rm9200.wpj ,每个项目有三个视图(Files, Vxworks,Build).Files 视图列出了范例项目包含的文件,这些文件都是缺省的,基本上每一个项目都是一样的(参阅vxworks的手册)。

最新-SSD192019显示控制器与AT91RM9200的接口技术 精品

SSD1906显示控制器与AT91RM9200的接口技术摘要通过对1906显示控制器的介绍,分析其在基于919200微控制器的嵌入式系统中的应用;给出详细的硬件连接图及主要的寄存器配置。

关键词1906919200显示控制引言1906是公司推出的一款中小规模的显示控制芯片。

这款显示控制芯片集成了显存及时序电路,因而为手持设备和消费电子领域提供了一个低成本、低功耗的单芯片解决方案。

919200是公司推出的一款基于9的嵌入式处理器,时钟频率为180。

919200处理器内部没有集成控制器,因而需要通过专用的显示控制器,实现显示。

本文介绍1906显示控制器在基于919200微控制器的嵌入式系统中的具体应用。

11906显示控制器介绍1906显示控制芯片,内部集成了256的显存,可以支持单色和彩色,以及多种有源和无源面板。

1906还具有强大的总线兼容性,可与多种类型的连接。

此外,1906提供的功能还包括虚拟显示、浮动窗口窗口大小可变显示,并支持两个光标,可以减少软件的操作。

32位的内部数据通道,可以提供高带宽的显示内存,以实现现快速的屏幕刷新。

1906还个有单电压供电的优点。

1906显示控制器的另一个特点,是具有很短的访问延迟时间,因而可以支持无交互信号的微处理器。

此外,1906支持单时钟信号输入,即总线时钟、内存时钟和像素时钟都可以由时钟输入1得到。

这款显示控制器对的类型和操作系统没有具体要求,因而是实际应用中的一个理想的显示解决方案。

基于1906的显示控制系统结构如图1所示。

11总线兼容性1906显示控制器兼容多种类型的接口,特别是对现在常用的嵌入式处理器,基本上都可以实现无缝连接。

对于不同的总线接口,1906内部提供了多个时序控制寄存器,可以根据不同接口的时序要求,进行相应的配置。

1906支持的总线接口类型包括具有信号的通用#1型和通用#2型总线接口;;1龙珠;68;龙珠6832868328;日立3和4。

星光AT91RM9200开发板使用手册

中国电子开发网()星光AT91RM9200开发板使用手册用户手册CEDN2008‐4‐1在使用本文档的时候,如遇到问题请访问中国电子开发网的技术支持()目录星光AT91RM9200开发板使用手册 (3)0 结构示意图 (3)1 系统构成 (4)1.0 基本构成 (4)1.1 外部接口 (4)2 地址空间分配(系统reset之后) (4)3 外部中断分配 (5)4 跳线说明 (6)4.0 启动模式选择 (6)4.1 其他跳线(一般不必设置) (6)5 首次使用 (7)5.0 注意事项 (7)5.1 开发板板载启动代码 (7)5.2 开发板板载启动信息 (7)6 简单程序的调试 (8)6.0 调试工具 (8)6.1 AXD添加H‐JTAG支持 (8)6.2 调试过程 (9)7 将文件烧写到开发板 (12)7.0 将文件烧写到NOR FLASH (12)8 其他说明 (14)星光AT91RM9200开发板使用手册0 结构示意图图1、星光AT91RM9200开发板结构示意图1 系统构成1.0 基本构成1、处理器CPU: 型号AT91RM9200 封装272pin‐FBGA2、NOR FLASH: 型号SST39VF3201 封装48Pin‐TSOP 4M 总线宽带16bits3、NAND FLASH: 型号K9F1208U0C‐Y,P 封装48pin‐TSOP1 64M4、内存SDRAM: 型号HY57V281620 封装54pin‐TSOP 两片32M 总线宽带32bits 1.1 外部接口1、UART串口: 3个的串口(J3为4线,J4为2线(DEBUG),J15为485串口)。

2、USB接口: 1个USB Host接口。

1个USB Device接口。

3、IIC接口: 用于IIC总线EEPROM。

4、SD/MMC接口: 用于SD/MMC卡。

5、CF卡接口: 1个CF卡。

6、CAN总线: 通过SPI总线扩展,MCP2515 CAN控制器。

基于AT91RM9200与LINUX2.6.26内核的嵌入式平台开发全过程

基于AT91RM9200与LINUX2.6.26内核的嵌入式平台开发全过程收藏一、ARM9+LINUX开发历程使用了51系列和MOTOROLA单片机若干年,觉得自己已经跟不上嵌入式发展的时代了。

决定开发一种新的硬件平台,综合比较了一下,觉得ARM9+LINUX模式不错。

先从头捋一遍32位嵌入式开发平台的流程:芯片选型——使用DXP画原理图(如果有可能买块开发板可以极快加快进度)——使用DXP 画PCB图——芯片购买/PCB投板生产——芯片焊接——使用ADS编写简单硬件测试程序,调试硬件——搭建LINUX服务器,在服务器建立交叉编译环境——利用服务器和本机超级终端开发U-BOOT-1.3.4——利用U-BOOT-1.3.4的以太网FTP功能和服务器移植开发LINUX-2.6.26 内核——开发文件系统——开发驱动程序——应用程序开发,项目完基本成后回过头来想就是这个一个过程,中间走了不少弯路,在本博客中都有记载,很多问题有的也没有来得及记。

说干就干,时间安排如下:(1)5~7月硬件设计(芯片,型号,预测价格),已初步完成CPU:AT91RM9200,81SDRAM:MT48LC16M16A2TG-75IT(两片32MB*2)74*2FLASH:S29GL256N10TAI010(NOR型,32MB,存代码,写慢读快)57.52FLASH∶K9F2G08U0B(NAND256MB,预留存测试数据,写快读慢)41.1铁电存储器:FM24CL64(代替EEPROM24LC65,8KB)8.29以太网物理层控制器:DM9161E(100M/10M自适应)9.4从USB接口:用于与PC机通信主USB接口:用于后续移植LINUX时软件更新触摸屏驱动器:TSC2046(预留)液晶显示屏模块-TFT液晶显示接口(预留)(2)ADS+AXD+J-LINK调试过程目的是为了熟悉ARM开发流程,ADS开发环境,以便为将来U-BOOT的移植打下基础.由于网上资料不多,本步骤走了不少冤枉路,特总结在此,以便以后可以参考.容易步骤省略.安装ADS>>创建ADS工程>>添加所需要文件>>DEBUG SETTING,将程序的RO_Base设为0X200000则将程序导入A T91RM9200的片内16K的SRAM中运行,实践证明此时不需要管BMS引脚是高是低都能正常运行,也不需要进行REMAP;若将程序的RO_Base设为0X20000000则将程序导入片外64M的SDRAM中运行,此时程序导进SDRAM后需要SETMEM命令将SDRAM初始化,才能正常运行。

基于AT91RM9200微处理器的最小系统设计

研究Technology StudyI G I T C W 技术26DIGITCW2020.061 A RM 微处理器目前,在多个领域中都在使用ARM 微处理器,例如通信电子、智能工业、多媒体教育等。

根据相关数据统计,通用计算机的应用数据已经大大低于基于ARM 微处理器的设备应用数据。

故此,基于ARM 微处理器的开发应用已成为数字时代的应用技术潮流。

文章中主要介绍了基于AT91RM9200处理器的最小系统,其次介绍了ARM 芯片的外围接口的电路设计,并给出了相关器件选型。

2 硬件设计最小系统是最基本的电路,为了保证微处理器的工作可靠。

ARM 处理器最小系统的定义是确保ARM 处理器能够正常启动、运行的最小电路集合。

由微处理器AT91RM9200、电源电路、晶体振荡器电路、复位电路、NorFlash 、SDRAM 、RS232调试接口等电路组成最小嵌入式系统,其原理框图如图1所示。

图1 最小系统的框架图在本方案中,ARM 处理器选用ATMEL 公司AT91RM9200芯片,具有ARM920T 内核,带有MMU (Memory Management Unit ),工作时钟可达到180 MHz ,具有外部存储器扩展端口,具有外部中断控制器,支持以太网和USB 接口。

2.1 电源电路ARM 处理器I/O 电源3.3 V 推荐芯片LT1764AEQ-3.3#PBF V 推荐芯片,ARM 处理器内核电源1.8 V 推荐芯片TPS72518DCQ ,如图2所示。

2.2 复位电路低电平有效,300 ms 以上,模块正常运行时为高电平;本设计中的复位电路由FPGA提供。

图2 电源电路2.3 晶体振荡器电路存储系统运行所需的时钟和外设电路工作时所需的时钟由晶体振荡器电路提供。

本设计使用无源晶体作为时钟输入,即使掉电程序和数据都不会丢失;起振需要ARM 处理器内部PLL 锁相环电路配合,震荡起振。

设计中主时钟采用18.432 MHz 无源晶振,在ARM 芯片内部通过锁相环倍频至180 MHz 以上,作为ARM 处理器的工作时钟,慢速时钟采用32.768 kHz 无源晶振,为ARM 处理器的慢速外设提供时钟。

AT91RM9200DK U-Boot Flash Programming Solutions

AT91RM9200DK U-Boot Flash ProgrammingSolutionsIntroductionThe AT91RM9200DK Development Board is provided with a default boot program in its external Flash memory. This boot program, called U-Boot, is used by the AT91RM9200DK to boot after reset. The U-Boot performs initialization of the AT91RM9200DK, provides user interface via the Serial Debug Port and allows appli-cation download through the Serial Debug Port or Ethernet.This Application Note aims at providing solutions when the U-Boot program contained in the external Flash of AT91RM9200DK Development Board has been deleted. Two ways of reprogramming the Flash memory are described in this Application Note; the method selected depends on whether the user has a Slingshot™ JTAG/ICE interface. If this interface is not being used, then the external Flash is reprogrammed using the internal BootROM (embedded on the AT91RM9200 version 58A07F).AT91 ARM®Thumb®MicrocontrollersApplication Note6041A–ATARM–01/042AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04U-Boot SoftwareFeatures The main features of the U-Boot software embedded in the AT91RM9200DK Develop-ment Kit are:•Standalone primary bootstrap •Small footprint •OS-independent •Auto-boot and interactive modes •Command line interface •Non-volatile environment variables •Flash programming capability •DataFlash programming capability (only available in latest Open Source download)•Download through serial interface (Kermit protocol)•Download through Ethernet (tftp)•Integrated bootp •Scripting capabilityOrganization To optimize the use of resources, U-Boot is made up of three parts:•A primary bootstrap •A de-compression executable • A gzip-compressed binary executable called the U-Boot ImageThe primary bootstrap is concatenated to the de-compression executable into one sin-gle file called the boot image and must reside in the AT91RM9200DK Flash on NCS0 ataddress 0x1000_0000.The primary bootstrap is a simple assembly code routine that sets up the system andputs it into an operational state. More specifically, it starts the high-speed clocks of theCPU and programs the on-chip memory controller to define the memory layout. Whenthese steps are completed, the primary bootstrap gives control to the de-compressionexecutable.The de-compression executable is an optimized version of the gunzip program. It de-compresses the gzip-compressed image of U-Boot into RAM, and jumps to it. The loca-tion of the binary executable in RAM is defined at link time.3AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Figure 1. Flash Mapping0x1000_0000Boot Image24 KbytesEnvironment Variables 8 Kbytes0x1000_E0000x1000_60000x1001_0000Free32 KbytesU-BootgzippedImage64 Kbytes0x1002_00004AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Reprogramming the External Flash on the AT91RM9200DK Development Board For Users of SlingshotJTAG/ICE Interface andMULTI ®2000The procedure for reprogramming the Flash described here is applicable to users of the AT91RM9200DK Development Board who have the Green Hills ® Slingshot JTAG/ICE interface and MULTI2000.Hardware and SoftwareRequirements •UBootFlashProgramming.zip file provided with this Application Note •Green Hills Slingshot JTAG/ICE interface •Green Hills MULTI2000 (V3.6.1 or higher) running on your PC •A serial cable (null modem)•HyperTerminal running on your PC application (1115200, 8, N, 1)Connecting theAT91RM9200DK to the HostPC 1.Connect the AT91RM9200DK to the Host PC using the serial cable through the Serial Debug Port on the A T91RM9200DK and the serial COM port on the Host PC. Open a HyperT erminal session with the following configuration: 115200 bitrate, 8-bit data length, No parity bit, 1 stop bit and No flux control.2.Connect the Slingshot JT AG/ICE Interface to the A T91RM9200DK through theJTAG/ICE Interface connector and to the PC through the USB Port.Launching the MULTI2000 3.Extract the AT91RM9200 Getting Started Software Package file calledAT91RM9200-GettingStarted-GHS3_6-1_1.exe , available in the UBootFlash-Programming.zip file provided with this Application Note.unch the MULTI2000 Project Manager and open the project Getting-Started.bld. This is available in the software package, extracted to the followingdirectory path C:\UBootFlashProgramming\AT91RM9200-GettingStarted-GHS3_6-1_1\A T91RM9200-GettingStarted\compil.5.Select the project basic_flash.bld by double-clicking on it. Build it and check ifbuild was succesful.6.Power-up and reset the AT91RM9200DK Development Board.Configuring the Connection to the AT91RM9200DK This is one of the most important steps in the procedure. As the Flash has been com-pletely erased, a standard initialization that would normally configure the External BusInterface, the Remap and the PLLs is not performed on the AT91RM9200DK. To carryout the initialization correctly, a Target Setup Script file (extension .dbs) must be used.The file, named mpserv_dk9200_PLL.dbs, is provided with this Application Note. Youare strongly advised to use it.To proceed:7.Click on the Connect button to open the Connection Chooser window:5AT91RM9200DK U-Boot Application Note6041A–ATARM–01/048.In the Connection Chooser window, select the ARM ®9 Green Hills Probe ™ Con-nection (mpserv):9.Edit the selected Connection Method:10.In the Slingshot Connection Editor window, select the Target Setup Script file thatinitializes the AT91RM9200DK correctly. It is very important to use the filempserv_dk9200_PLL.dbs provided with this Application Note:6AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Launching the Debugger 11.Click on the Debug button to run the debugger:12.In the debugger environment, click on the Step button to download thebasic_flash project:13.In the debugger environment, switch to the command pane:Loading the LoaderApplication The next step is to download the loader.bin application. This application is used to download a binary file from a HyperTerminal session through the Serial Debug Portusing the Xmodem protocol. The loader.bin file to download is available in the the soft-ware package extracted at the beginning of the procedure and available in the directory C:\UBootFlashProgramming\AT91RM9200-GettingStarted-GHS3_6-1_1\AT91RM9200-GettingStarted\Flash. See “Launching the MULTI2000” on page 4.14.Download the loader.bin application in the internal RAM at address 0x200000 bywriting the following command in the command pane window (prompt MULTI>):MULTI> memload raw C:\UBootFlashProgramming\AT91RM9200-GettingStarted-GHS3_6-1_1\AT91RM9200-GettingStarted\Flash\loader.bin 0x20000015.Set the Program Counter (pc) at the beginning of the downloaded loader.binapplication and run from here:MULTI> target reg pc 0x200000MULTI> target runLoading U-Boot The loader application is now running on the AT91RM9200DK and is ready to downloada binary application file through the Serial Debug Port using the Xmodem protocol on a HyperTerminal session.16.Download the u_boot.bin binary file using the Xmodem protocol. This file isavailable in the UBootFlashProgramming.zip file provided with this ApplicationNote under the directory path C:\UBootFlashProgramming\binary.7AT91RM9200DK U-Boot Application Note 6041A–ATARM–01/04In the HyperTerminal session, send the file u_boot.bin using the Xmodem protocol.At the end of the Xmodem transfer, a new prompt is displayed in the HyperTerminal window:Uboot>The U-Boot is now running on the AT91RM9200DK.This Boot program can now be used to download files to the SDRAM through the Serial Debug Port using the Kermit protocol with a HyperTerminal session. It is then copied to the Flash.Downloading U-Boot BinaryFiles The last step is to download the primary bootstrap, boot.bin, and the gzip-compressed U-Boot image, u-boot.gz. These two files are available in the UBootFlashProgram-m i ng.z i p fi l e pr o v i d e d w i t h t hi s A p pl i c a t io n N o te in th e d i r e c to r y C:\UBootFlashProgramming\binary.17.The first file to load is the boot image “boot.bin ”.Uboot> loadb 20000000## Ready for binary (Kermit) download …## Start Addr =0x20000000The boot image is now loaded in SDRAM. The following command copies the SDRAM (0x20000000) to Flash(0x10000000):Uboot> protect off 10000000 10005fffUnprotect 3 sectorsUboot> erase 10000000 10005fffErase Flash from 0x10000000 to 0x10005fff...Erasing sector 0 ... ok.Erasing sector 1 ... ok.Erasing sector 2 ... ok.done.Erased 3 sectors.Uboot> cp.b 20000000 10000000 5FFFCopy to flash… done.Uboot> protect on 10000000 10005FFFProtected 3 sectorsUboot>18.Once the primary bootstrap has been loaded, the U-Boot gzipped image can becopied into Flash. The file to load is the uboot gzipped image “u-boot.gz ”:Uboot> loadb 20000000## Ready for binary (Kermit) download …## Start Addr =0x20000000Uboot> protect off 10010000 1001ffffUnprotect 1 sectorsUboot> erase 10010000 1001ffffErase Flash from 0x10010000 to 0x1001ffff...8AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Erasing sector 8 ... ok.done.Erased 1 sectors.Uboot> cp.b 20000000 10010000 FFFFCopy to flash… done.Uboot> protect on 10010000 1001FFFFProtected 1 sectorsUboot>19.The U-Boot has been upgraded. Reboot your board.9AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Using the InternalBootROM The procedure for reprogramming the Flash described here is applicable to users of theAT91RM9200DK Development Board who do not have a Green Hills Slingshot JTAG/ICE Interface. The solution presented here uses the Internal BootROM of the AT91RM9200.After reset, the AT91RM9200DK boots from the external Flash memory by default (BMS high during reset). To boot using the embedded Boot ROM program (on-chip boot mode with BMS low during reset), it is mandatory to remove the R159 resistor from the AT91RM9200DK development board temporarily.Hardware and SoftwareRequirements •UBootFlashProgramming.zip file available with this Application Note •A serial cable (Null modem)•HyperTerminal running on your PC application (1115200,8,N,1)Connecting theAT91RM9200DK to the HostPC 1.Connect the AT91RM9200DK to the Host PC using the serial cable through the Serial Debug Port on the A T91RM9200DK and the serial COM port on the Host PC. Open a HyperT erminal session with the following configuration, 115200 bitrate, 8-bit data length, No parity bit, 1 stop bit and No flux control.Loading the Loader Application2.Download the loader.bin application. This application is used to download abinary file from a HyperTerminal session through the Serial Debug Port using the Xmodem protocol.3.Extract the AT91RM9200 Getting Started Software Package file calledAT91RM9200-GettingStarted-GHS3_6-1_1.exe , available on the UBootFlash-Programming.zip file provided with this Application Note. The loader.bin file to download is available in the software package extracted to the following directory path C:\UBootFlashProgramming\AT91RM9200-GettingStarted-GHS3_6-1_1\A T91RM9200-GettingStarted\Flash.4.Power-up and reset the AT91RM9200DK Development Board.The Internal Boot Program runs and waits for downloading an application code into the internal SRAM via Xmodem protocol through the Serial Debug Port (DBGU). It then branches to the application entry point at the first address of the SRAM.5.On the HyperTerminal session, send the file loader.bin using Xmodem protocol.Loading U-Boot The loader application is now running on the AT91RM9200DK and is ready to downloada binary application file through the Serial Debug Port using the Xmodem protocol on a HyperTerminal session.6.Download the u_boot.bin binary file using the Xmodem protocol. This file isavailable available in the UBootFlashProgramming.zip file provided with this Application Note under the following directory path C:\UBootFlashProgramming\binary.In the HyperTerminal session, send the file u_boot.bin using Xmodem protocol. At the end of the Xmodem transfer, a new prompt is displayed in the HyperTerminal window:Uboot>The UBoot is now running on the AT91RM9200DK.This Boot program can be used to download files to the SDRAM through the Serial Debug Port using the Kermit protocol with a HyperTerminal session. It is then copied to the Flash.10AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Downloading U-Boot BinaryFiles The last step is to download the primary bootstrap, boot.bin, and the gzip-compressed U-Boot image, u-boot.gz. These two files are also available in the UBootFlashProgram-m i ng.z i p fi l e pr o v i d e d w i t h t hi s A p pl i c a t io n N o te in th e d i r e c to r y C:\UBootFlashProgramming\binary.7.The first file to load is the boot image “boot.bin ”.Uboot> loadb 20000000## Ready for binary (Kermit) download …## Start Addr =0x20000000The boot image is now loaded in SDRAM. The following command copies the SDRAM (0x20000000) to Flash(0x10000000).Uboot> protect off 10000000 10005fffUnprotect 3 sectorsUboot> erase 10000000 10005fffErase Flash from 0x10000000 to 0x10005fff...Erasing sector 0 ... ok.Erasing sector 1 ... ok.Erasing sector 2 ... ok.done.Erased 3 sectors.Uboot> cp.b 20000000 10000000 5FFFCopy to flash… done.Uboot> protect on 10000000 10005FFFProtected 3 sectorsUboot>8.Once the primary bootstrap has been loaded, the U-Boot gzipped image can becopied into Flash. The file to load is the uboot gzipped image “u-boot.gz ”:Uboot> loadb 20000000## Ready for binary (Kermit) download …## Start Addr =0x20000000Uboot> protect off 10010000 1001ffffUnprotect 1 sectorsUboot> erase 10010000 1001ffffErase Flash from 0x10010000 to 0x1001ffff...Erasing sector 8 ... ok.done.Erased 1 sectors.Uboot> cp.b 20000000 10010000 FFFFCopy to flash… done.Uboot> protect on 10010000 1001FFFFProtected 1 sectorsUboot>The U-Boot has been upgraded.11AT91RM9200DK U-Boot Application Note6041A–ATARM–01/049.Set the R159 resistor on the AT91RM9200DK to boot from the external Flashmemory. Reboot your board.Printed on recycled paper.Disclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard warranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel’s products are not authorized for use as critical components in life support devices or systems.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literature6041A–ATARM–01/04© Atmel Corporation 2004. All rights reserved. Atmel ® and combinations thereof are the registered trademarks of Atmel Corporation or its subsidiaries. Green Hills ® and MULTI ® are the registered trademarks, and Slingshot ™ and Green Hills Probe ™ are the trademarks of Green Hills Software, Inc. ARM ® is the registered trademark of ARM Ltd. Other terms and product names may be the trademarks of others.。

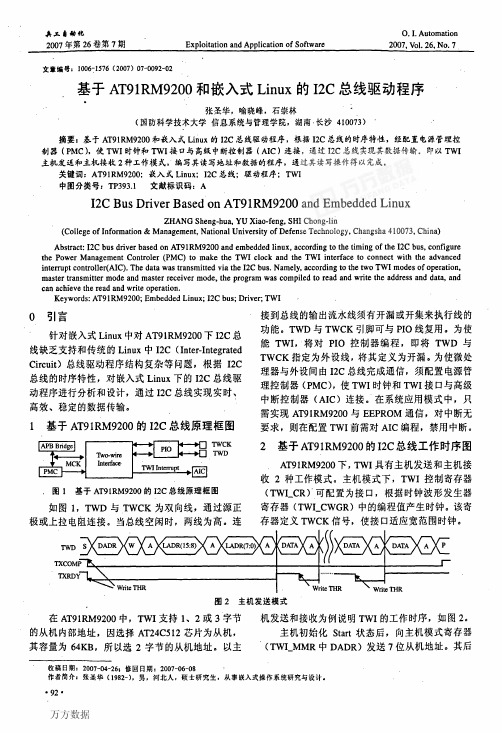

基于AT91RM9200和嵌入式Linux的I2C总线驱动程序

寄存器(TwI—CwGR)中的编程值产生时钟。该寄

◇)@@ @激 存器定义TwcK信号,使接口适应宽范围时钟。 ∈Ⅺ 广

R ~形 1tcn{R

k \w嘲 eTHR

图2主机发送模式

.

在AT9lRM9200中,Twl支持l、2或3字节 机发送和接收为例说明TwI的工作时序,如图2。

的从机内部地址,因选择AT24C512芯片为从机,

2 基于AT91RM9200的12C总线工作时序图

AT91RM9200下,TwI具有主机发送和主机接 收2种工作模式。主机模式下,TwI控制寄存器

(TWLCR)。可配置为接口,根据时钟波形发生器

如图1,TwD与TWCK为双向线,通过源正 极或上拉电阻连接。当总线空闲时,两线为高。连

K’

z’\\wHtcTHR

【5】周剑波。基于FPGA和嵌入式Linux的网络视频采集处

理系统研究【D】.北京:北京科技大学,2Q06.

·93·

万方数据

主机初始化Start状态后,向主机模式寄存器

其容量为64KB,所以选2字节的从机地址。以主 ‘(TwI—MMR中DADR)发送7位从机地址。其后

收稿日期}2007—04—26l修回日期:2007一06一08 作者简介:张圣华(1982一),男,河北人,硕士研究生,从事嵌入式操作系统研究与设计. ·92·

动程序进行分析和设计,通过12C总线实现实时、 高效、稳定的数据传输。

僦脍 1 基于AT91RM9200的12C总线原理框图

I坐呈璺!g!I

—忑二=,

TWCK TWD

陌n:者薪习h

McK。 -

图1 基于AT91RM9200的12C总线原理框图

接到总线的输出流水线须有开漏或开集来执行线的 功能。TWD与TwCK引脚可与PIO线复用。为使 能TWI,将对PIO控制器编程,即将TwD与 TwcK指定为外设线,将其定义为开漏。为使微处 理器与外设间由12C总线完成通信,须配置电源管 理控制器(PMC),使TwI时钟和TwI接口与高级 中断控制器(AIC)连接。在系统应用模式中,只 需实现AT9lRM9200与EEPROM通信,对中断无 要求,则在配置TWI前需对AIC编程,禁用中断。

AT91RM9200DK U-Boot Flash Programming Solutions

AT91RM9200DK U-Boot Flash ProgrammingSolutionsIntroductionThe AT91RM9200DK Development Board is provided with a default boot program in its external Flash memory. This boot program, called U-Boot, is used by the AT91RM9200DK to boot after reset. The U-Boot performs initialization of the AT91RM9200DK, provides user interface via the Serial Debug Port and allows appli-cation download through the Serial Debug Port or Ethernet.This Application Note aims at providing solutions when the U-Boot program contained in the external Flash of AT91RM9200DK Development Board has been deleted. Two ways of reprogramming the Flash memory are described in this Application Note; the method selected depends on whether the user has a Slingshot™ JTAG/ICE interface. If this interface is not being used, then the external Flash is reprogrammed using the internal BootROM (embedded on the AT91RM9200 version 58A07F).AT91 ARM®Thumb®MicrocontrollersApplication Note6041A–ATARM–01/042AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04U-Boot SoftwareFeatures The main features of the U-Boot software embedded in the AT91RM9200DK Develop-ment Kit are:•Standalone primary bootstrap •Small footprint •OS-independent •Auto-boot and interactive modes •Command line interface •Non-volatile environment variables •Flash programming capability •DataFlash programming capability (only available in latest Open Source download)•Download through serial interface (Kermit protocol)•Download through Ethernet (tftp)•Integrated bootp •Scripting capabilityOrganization To optimize the use of resources, U-Boot is made up of three parts:•A primary bootstrap •A de-compression executable • A gzip-compressed binary executable called the U-Boot ImageThe primary bootstrap is concatenated to the de-compression executable into one sin-gle file called the boot image and must reside in the AT91RM9200DK Flash on NCS0 ataddress 0x1000_0000.The primary bootstrap is a simple assembly code routine that sets up the system andputs it into an operational state. More specifically, it starts the high-speed clocks of theCPU and programs the on-chip memory controller to define the memory layout. Whenthese steps are completed, the primary bootstrap gives control to the de-compressionexecutable.The de-compression executable is an optimized version of the gunzip program. It de-compresses the gzip-compressed image of U-Boot into RAM, and jumps to it. The loca-tion of the binary executable in RAM is defined at link time.3AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Figure 1. Flash Mapping0x1000_0000Boot Image24 KbytesEnvironment Variables 8 Kbytes0x1000_E0000x1000_60000x1001_0000Free32 KbytesU-BootgzippedImage64 Kbytes0x1002_00004AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Reprogramming the External Flash on the AT91RM9200DK Development Board For Users of SlingshotJTAG/ICE Interface andMULTI ®2000The procedure for reprogramming the Flash described here is applicable to users of the AT91RM9200DK Development Board who have the Green Hills ® Slingshot JTAG/ICE interface and MULTI2000.Hardware and SoftwareRequirements •UBootFlashProgramming.zip file provided with this Application Note •Green Hills Slingshot JTAG/ICE interface •Green Hills MULTI2000 (V3.6.1 or higher) running on your PC •A serial cable (null modem)•HyperTerminal running on your PC application (1115200, 8, N, 1)Connecting theAT91RM9200DK to the HostPC 1.Connect the AT91RM9200DK to the Host PC using the serial cable through the Serial Debug Port on the A T91RM9200DK and the serial COM port on the Host PC. Open a HyperT erminal session with the following configuration: 115200 bitrate, 8-bit data length, No parity bit, 1 stop bit and No flux control.2.Connect the Slingshot JT AG/ICE Interface to the A T91RM9200DK through theJTAG/ICE Interface connector and to the PC through the USB Port.Launching the MULTI2000 3.Extract the AT91RM9200 Getting Started Software Package file calledAT91RM9200-GettingStarted-GHS3_6-1_1.exe , available in the UBootFlash-Programming.zip file provided with this Application Note.unch the MULTI2000 Project Manager and open the project Getting-Started.bld. This is available in the software package, extracted to the followingdirectory path C:\UBootFlashProgramming\AT91RM9200-GettingStarted-GHS3_6-1_1\A T91RM9200-GettingStarted\compil.5.Select the project basic_flash.bld by double-clicking on it. Build it and check ifbuild was succesful.6.Power-up and reset the AT91RM9200DK Development Board.Configuring the Connection to the AT91RM9200DK This is one of the most important steps in the procedure. As the Flash has been com-pletely erased, a standard initialization that would normally configure the External BusInterface, the Remap and the PLLs is not performed on the AT91RM9200DK. To carryout the initialization correctly, a Target Setup Script file (extension .dbs) must be used.The file, named mpserv_dk9200_PLL.dbs, is provided with this Application Note. Youare strongly advised to use it.To proceed:7.Click on the Connect button to open the Connection Chooser window:5AT91RM9200DK U-Boot Application Note6041A–ATARM–01/048.In the Connection Chooser window, select the ARM ®9 Green Hills Probe ™ Con-nection (mpserv):9.Edit the selected Connection Method:10.In the Slingshot Connection Editor window, select the Target Setup Script file thatinitializes the AT91RM9200DK correctly. It is very important to use the filempserv_dk9200_PLL.dbs provided with this Application Note:6AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Launching the Debugger 11.Click on the Debug button to run the debugger:12.In the debugger environment, click on the Step button to download thebasic_flash project:13.In the debugger environment, switch to the command pane:Loading the LoaderApplication The next step is to download the loader.bin application. This application is used to download a binary file from a HyperTerminal session through the Serial Debug Portusing the Xmodem protocol. The loader.bin file to download is available in the the soft-ware package extracted at the beginning of the procedure and available in the directory C:\UBootFlashProgramming\AT91RM9200-GettingStarted-GHS3_6-1_1\AT91RM9200-GettingStarted\Flash. See “Launching the MULTI2000” on page 4.14.Download the loader.bin application in the internal RAM at address 0x200000 bywriting the following command in the command pane window (prompt MULTI>):MULTI> memload raw C:\UBootFlashProgramming\AT91RM9200-GettingStarted-GHS3_6-1_1\AT91RM9200-GettingStarted\Flash\loader.bin 0x20000015.Set the Program Counter (pc) at the beginning of the downloaded loader.binapplication and run from here:MULTI> target reg pc 0x200000MULTI> target runLoading U-Boot The loader application is now running on the AT91RM9200DK and is ready to downloada binary application file through the Serial Debug Port using the Xmodem protocol on a HyperTerminal session.16.Download the u_boot.bin binary file using the Xmodem protocol. This file isavailable in the UBootFlashProgramming.zip file provided with this ApplicationNote under the directory path C:\UBootFlashProgramming\binary.7AT91RM9200DK U-Boot Application Note 6041A–ATARM–01/04In the HyperTerminal session, send the file u_boot.bin using the Xmodem protocol.At the end of the Xmodem transfer, a new prompt is displayed in the HyperTerminal window:Uboot>The U-Boot is now running on the AT91RM9200DK.This Boot program can now be used to download files to the SDRAM through the Serial Debug Port using the Kermit protocol with a HyperTerminal session. It is then copied to the Flash.Downloading U-Boot BinaryFiles The last step is to download the primary bootstrap, boot.bin, and the gzip-compressed U-Boot image, u-boot.gz. These two files are available in the UBootFlashProgram-m i ng.z i p fi l e pr o v i d e d w i t h t hi s A p pl i c a t io n N o te in th e d i r e c to r y C:\UBootFlashProgramming\binary.17.The first file to load is the boot image “boot.bin ”.Uboot> loadb 20000000## Ready for binary (Kermit) download …## Start Addr =0x20000000The boot image is now loaded in SDRAM. The following command copies the SDRAM (0x20000000) to Flash(0x10000000):Uboot> protect off 10000000 10005fffUnprotect 3 sectorsUboot> erase 10000000 10005fffErase Flash from 0x10000000 to 0x10005fff...Erasing sector 0 ... ok.Erasing sector 1 ... ok.Erasing sector 2 ... ok.done.Erased 3 sectors.Uboot> cp.b 20000000 10000000 5FFFCopy to flash… done.Uboot> protect on 10000000 10005FFFProtected 3 sectorsUboot>18.Once the primary bootstrap has been loaded, the U-Boot gzipped image can becopied into Flash. The file to load is the uboot gzipped image “u-boot.gz ”:Uboot> loadb 20000000## Ready for binary (Kermit) download …## Start Addr =0x20000000Uboot> protect off 10010000 1001ffffUnprotect 1 sectorsUboot> erase 10010000 1001ffffErase Flash from 0x10010000 to 0x1001ffff...8AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Erasing sector 8 ... ok.done.Erased 1 sectors.Uboot> cp.b 20000000 10010000 FFFFCopy to flash… done.Uboot> protect on 10010000 1001FFFFProtected 1 sectorsUboot>19.The U-Boot has been upgraded. Reboot your board.9AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Using the InternalBootROM The procedure for reprogramming the Flash described here is applicable to users of theAT91RM9200DK Development Board who do not have a Green Hills Slingshot JTAG/ICE Interface. The solution presented here uses the Internal BootROM of the AT91RM9200.After reset, the AT91RM9200DK boots from the external Flash memory by default (BMS high during reset). To boot using the embedded Boot ROM program (on-chip boot mode with BMS low during reset), it is mandatory to remove the R159 resistor from the AT91RM9200DK development board temporarily.Hardware and SoftwareRequirements •UBootFlashProgramming.zip file available with this Application Note •A serial cable (Null modem)•HyperTerminal running on your PC application (1115200,8,N,1)Connecting theAT91RM9200DK to the HostPC 1.Connect the AT91RM9200DK to the Host PC using the serial cable through the Serial Debug Port on the A T91RM9200DK and the serial COM port on the Host PC. Open a HyperT erminal session with the following configuration, 115200 bitrate, 8-bit data length, No parity bit, 1 stop bit and No flux control.Loading the Loader Application2.Download the loader.bin application. This application is used to download abinary file from a HyperTerminal session through the Serial Debug Port using the Xmodem protocol.3.Extract the AT91RM9200 Getting Started Software Package file calledAT91RM9200-GettingStarted-GHS3_6-1_1.exe , available on the UBootFlash-Programming.zip file provided with this Application Note. The loader.bin file to download is available in the software package extracted to the following directory path C:\UBootFlashProgramming\AT91RM9200-GettingStarted-GHS3_6-1_1\A T91RM9200-GettingStarted\Flash.4.Power-up and reset the AT91RM9200DK Development Board.The Internal Boot Program runs and waits for downloading an application code into the internal SRAM via Xmodem protocol through the Serial Debug Port (DBGU). It then branches to the application entry point at the first address of the SRAM.5.On the HyperTerminal session, send the file loader.bin using Xmodem protocol.Loading U-Boot The loader application is now running on the AT91RM9200DK and is ready to downloada binary application file through the Serial Debug Port using the Xmodem protocol on a HyperTerminal session.6.Download the u_boot.bin binary file using the Xmodem protocol. This file isavailable available in the UBootFlashProgramming.zip file provided with this Application Note under the following directory path C:\UBootFlashProgramming\binary.In the HyperTerminal session, send the file u_boot.bin using Xmodem protocol. At the end of the Xmodem transfer, a new prompt is displayed in the HyperTerminal window:Uboot>The UBoot is now running on the AT91RM9200DK.This Boot program can be used to download files to the SDRAM through the Serial Debug Port using the Kermit protocol with a HyperTerminal session. It is then copied to the Flash.10AT91RM9200DK U-Boot Application Note6041A–ATARM–01/04Downloading U-Boot BinaryFiles The last step is to download the primary bootstrap, boot.bin, and the gzip-compressed U-Boot image, u-boot.gz. These two files are also available in the UBootFlashProgram-m i ng.z i p fi l e pr o v i d e d w i t h t hi s A p pl i c a t io n N o te in th e d i r e c to r y C:\UBootFlashProgramming\binary.7.The first file to load is the boot image “boot.bin ”.Uboot> loadb 20000000## Ready for binary (Kermit) download …## Start Addr =0x20000000The boot image is now loaded in SDRAM. The following command copies the SDRAM (0x20000000) to Flash(0x10000000).Uboot> protect off 10000000 10005fffUnprotect 3 sectorsUboot> erase 10000000 10005fffErase Flash from 0x10000000 to 0x10005fff...Erasing sector 0 ... ok.Erasing sector 1 ... ok.Erasing sector 2 ... ok.done.Erased 3 sectors.Uboot> cp.b 20000000 10000000 5FFFCopy to flash… done.Uboot> protect on 10000000 10005FFFProtected 3 sectorsUboot>8.Once the primary bootstrap has been loaded, the U-Boot gzipped image can becopied into Flash. The file to load is the uboot gzipped image “u-boot.gz ”:Uboot> loadb 20000000## Ready for binary (Kermit) download …## Start Addr =0x20000000Uboot> protect off 10010000 1001ffffUnprotect 1 sectorsUboot> erase 10010000 1001ffffErase Flash from 0x10010000 to 0x1001ffff...Erasing sector 8 ... ok.done.Erased 1 sectors.Uboot> cp.b 20000000 10010000 FFFFCopy to flash… done.Uboot> protect on 10010000 1001FFFFProtected 1 sectorsUboot>The U-Boot has been upgraded.11AT91RM9200DK U-Boot Application Note6041A–ATARM–01/049.Set the R159 resistor on the AT91RM9200DK to boot from the external Flashmemory. Reboot your board.Printed on recycled paper.Disclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard warranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel’s products are not authorized for use as critical components in life support devices or systems.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literature6041A–ATARM–01/04© Atmel Corporation 2004. All rights reserved. Atmel ® and combinations thereof are the registered trademarks of Atmel Corporation or its subsidiaries. Green Hills ® and MULTI ® are the registered trademarks, and Slingshot ™ and Green Hills Probe ™ are the trademarks of Green Hills Software, Inc. ARM ® is the registered trademark of ARM Ltd. Other terms and product names may be the trademarks of others.。

AT91RM9200处理器引导程序及其启动方式

2 0 1 3年

图 1 引导程序流向 F i . 1 O v e r a l l f l o w o f t h e b o o t s t r a r o r a m g p p g

3. 1 B o o t L o a d e r 启动引导程序 U 系 b o o t主 要 包 括 系 统 初 始 化 、

收稿日期 : 2 0 1 3 0 2 1 9 - - , 作者简介 :梁志福 ( 男, 内蒙古丰镇人 , 高级工程师 , 从事火力发电厂自动控制技术的研究 。 1 9 6 6- ) : l E-m a i l i a n z h i f u 2 0 1 1@1 2 6. c o m g

1 4 2

ห้องสมุดไป่ตู้

热 力 发 电

: A b s t r a c t T h e o v e r a l l f l o w o f b o o t s t r a o f t h e AT 9 1 RM 9 2 0 0p r o c e s s o r w a s i n t r o d u c e d . r o r a m p p g , r o c e s s o rs T w o s t a r i n m e t h o d s o f t h i s t a r t i n f r o m t h e e x t e r n a l s t o r a e a n d f r o m t h e i n n e r s t o r - p g g g , a e w e r e s u mm a r i z e d . M o r e o v e r t h e f u n c t i o n s o f t h e B o o t L o a d e r a n d B o o t U l o a d e r w h i c h c o n - g p , s i s t s o f t h e i n n e r s t a r t i n r o r a m w e r e a n a l z e d . B e s i d e s t h e r e s t r i c t i o n s o f a b o v e f u n c t i o n s o n g p g y b o o t s t r a r o r a m w e r e a l s o d e s c r i b e d . t h e p p g : ; ; ; K e w o r d s AT 9 1 RM 9 2 0 0p r o c e s s o r b o o t s t r a r o r a m; s t a r t i n m e t h o d b o o t s t r a l o a d e r b o o t p p g g p y u l o a d e r p

AT91RM9200_0509资料

Features Array•Incorporates the ARM920T™ ARM® Thumb® Processor–200 MIPS at 180 MHz, Memory Management Unit–16-KByte Data Cache, 16-KByte Instruction Cache, Write Buffer–In-circuit Emulator including Debug Communication Channel–Mid-level Implementation Embedded Trace Macrocell (256-ball BGA Package Only)•Low Power: On VDDCORE 24.4 mA in Normal Mode, 520 µA in Standby Mode •Additional Embedded Memories–16K Bytes of SRAM and 128K Bytes of ROM•External Bus Interface (EBI)–Supports SDRAM, Static Memory, Burst Flash, Glueless Connection toCompactFlash® and NAND Flash/SmartMedia™•System Peripherals for Enhanced Performance:–Enhanced Clock Generator and Power Management Controller–Two On-chip Oscillators with Two PLLs–Very Slow Clock Operating Mode and Software Power Optimization Capabilities –Four Programmable External Clock Signals–System Timer Including Periodic Interrupt, Watchdog and Second Counter–Real-time Clock with Alarm Interrupt–Debug Unit, Two-wire UART and Support for Debug Communication Channel–Advanced Interrupt Controller with 8-level Priority, Individually Maskable Vectored Interrupt Sources, Spurious Interrupt Protected–Seven External Interrupt Sources and One Fast Interrupt Source–Four 32-bit PIO Controllers with Up to 122 Programmable I/O Lines, Input Change Interrupt and Open-drain Capability on Each Line–20-channel Peripheral DMA Controller (PDC)•Ethernet MAC 10/100 Base-T–Media Independent Interface (MII) or Reduced Media Independent Interface (RMII)–Integrated 28-byte FIFOs and Dedicated DMA Channels for Receive and Transmit •USB 2.0 Full Speed (12 Mbits per second) Host Double Port–Dual On-chip Transceivers (Single Port Only on 208-lead PQFP Package)–Integrated FIFOs and Dedicated DMA Channels•USB 2.0 Full Speed (12 Mbits per second) Device Port–On-chip Transceiver, 2-Kbyte Configurable Integrated FIFOs•Multimedia Card Interface (MCI)–Automatic Protocol Control and Fast Automatic Data Transfers–MMC and SD Memory Card-compliant, Supports Up to Two SD Memory Cards •Three Synchronous Serial Controllers (SSC)–Independent Clock and Frame Sync Signals for Each Receiver and Transmitter –I2S Analog Interface Support, Time Division Multiplex Support–High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer •Four Universal Synchronous/Asynchronous Receiver/Transmitters (USART)–Support for ISO7816 T0/T1 Smart Card–Hardware Handshaking–RS485 Support, IrDA Up To 115 Kbps–Full Modem Control Lines on USART1•Master/Slave Serial Peripheral Interface (SPI)–8- to 16-bit Programmable Data Length, 4 External Peripheral Chip Selects•Two 3-channel, 16-bit Timer/Counters (TC)–Three External Clock Inputs, Two Multi-purpose I/O Pins per Channel–Double PWM Generation, Capture/Waveform Mode, Up/Down Capability•Two-wire Interface (TWI)–Master Mode Support, All 2-wire Atmel EEPROMs Supported•IEEE 1149.1 JTAG Boundary Scan on All Digital Pins•Power Supplies–1.65V to 1.95V for VDDCORE, VDDOSC and VDDPLL–3.0V to 3.6V for VDDIOP (Peripheral I/Os) and for VDDIOM (Memory I/Os)Available•in a 208-lead PQFP or 256-ball BGA Package21768IS–ATARM–30-Sep-05AT91RM9200 Summary1.DescriptionThe AT91RM9200 is a complete system-on-chip built around the ARM920T ARM Thumb pro-cessor. It incorporates a rich set of system and application peripherals and standard interfaces in order to provide a single-chip solution for a wide range of compute-intensive applications that require maximum functionality at minimum power consumption at lowest cost.The AT91RM9200 incorporates a high-speed on-chip SRAM workspace, and a low-latency External Bus Interface (EBI) for seamless connection to whatever configuration of off-chip mem-ories and memory-mapped peripherals is required by the application. The EBI incorporates controllers for synchronous DRAM (SDRAM), Burst Flash and Static memories and features specific circuitry facilitating the interface for NAND Flash/SmartMedia and Compact Flash.The Advanced Interrupt Controller (AIC) enhances the interrupt handling performance of the ARM920T processor by providing multiple vectored, prioritized interrupt sources and reducing the time taken to transfer to an interrupt handler.The Peripheral DMA Controller (PDC) provides DMA channels for all the serial peripherals, enabling them to transfer data to or from on- and off-chip memories without processor interven-tion. This reduces the processor overhead when dealing with transfers of continuous data streams.The AT91RM9200 benefits from a new generation of PDC which includes dual pointers that simplify significantly buffer chaining.The set of Parallel I/O (PIO) controllers multiplex the peripheral input/output lines with general-purpose data I/Os for maximum flexibility in device configuration. An input change interrupt, open drain capability and programmable pull-up resistor is included on each line.The Power Management Controller (PMC) keeps system power consumption to a minimum by selectively enabling/disabling the processor and various peripherals under software control. It uses an enhanced clock generator to provide a selection of clock signals including a slow clock (32 kHz) to optimize power consumption and performance at all times.The AT91RM9200 integrates a wide range of standard interfaces including USB 2.0 Full Speed Host and Device and Ethernet 10/100 Base-T Media Access Controller (MAC), which provides connection to a extensive range of external peripheral devices and a widely used networking layer. In addition, it provides an extensive set of peripherals that operate in accordance with sev-eral industry standards, such as those used in audio, telecom, Flash Card, infrared and Smart Card applications.To complete the offer, the AT91RM9200 benefits from the integration of a wide range of debug features including JTAG-ICE, a dedicated UART debug channel (DBGU) and an embedded real time trace. This enables the development and debug of all applications, especially those with real-time constraints.31768IS–ATARM–30-Sep-05 AT91RM9200 Summary2.Block DiagramBold arrows () indicate master-to-slave dependency.Figure 2-1.AT91RM9200 Block Diagram41768IS–ATARM–30-Sep-05AT91RM9200 Summary3.Key FeaturesThis section presents the key features of each block.3.1ARM920T Processor•ARM9TDMI ™-based on ARM ® Architecture v4T•Two instruction sets–ARM ® High-performance 32-bit Instruction Set–Thumb ® High Code Density 16-bit Instruction Set•5-Stage Pipeline Architecture:–Instruction Fetch (F)–Instruction Decode (D)–Execute (E)–Data Memory (M)–Register Write (W)•16-Kbyte Data Cache, 16-Kbyte Instruction Cache–Virtually-addressed 64-way Associative Cache–8 words per line–Write-though and write-back operation–Pseudo-random or Round-robin replacement–Low-power CAM RAM implementation•Write Buffer–16-word Data Buffer–4-address Address Buffer–Software Control Drain•Standard ARMv4 Memory Management Unit (MMU)–Access permission for sections–Access permission for large pages and small pages can be specified separately for each quarter of the pages–16 embedded domains–64 Entry Instruction TLB and 64 Entry Data TLB•8-, 16-, 32-bit Data Bus for Instructions and Data3.2Debug and Test•Integrated Embedded In-Circuit-Emulator•Debug Unit–Two-pin UART–Debug Communication Channel–Chip ID Register•Embedded Trace Macrocell: ETM9 Rev2a–Medium Level Implementation–Half-rate Clock Mode51768IS–ATARM–30-Sep-05 AT91RM9200 Summary–Four Pairs of Address Comparators–Two Data Comparators–Eight Memory Map Decoder Inputs–Two Counters–One Sequencer–One 18-byte FIFO•IEEE1149.1 JT AG Boundary Scan on all Digital Pins3.3Boot Program•Default Boot Program stored in ROM-based products•Downloads and runs an application from external storage media into internal SRAM •Downloaded code size depends on embedded SRAM size•Automatic detection of valid application•Bootloader supporting a wide range of non-volatile memories–SPI DataFlash ® connected on SPI NPCS0–Two-wire EEPROM–8-bit parallel memories on NCS0•Boot Uploader in case no valid program is detected in external NVM and supporting several communication media•Serial communication on a DBGU (XModem protocol)•USB Device Port (DFU Protocol)3.4Embedded Software Services•Compliant with ATPCS•Compliant with AINSI/ISO Standard C •Compiled in ARM/Thumb Interworking•ROM Entry Service•Tempo, Xmodem and DataFlash services•CRC and Sine tables3.5Reset Controller•Two reset input lines (NRST and NTRST) providing, respectively:•Initialization of the User Interface registers (defined in the user interface of each peripheral) and:–Sample the signals needed at bootup–Compel the processor to fetch the next instruction at address zero.•Initialization of the embedded ICE TAP controller.3.6Memory Controller•Programmable Bus Arbiter handling four Masters–Internal Bus is shared by ARM920T, PDC, USB Host Port and Ethernet MACMasters61768IS–ATARM–30-Sep-05AT91RM9200 Summary–Each Master can be assigned a priority between 0 and 7•Address Decoder provides selection for–Eight external 256-Mbyte memory areas–Four internal 1-Mbyte memory areas–One 256-Mbyte embedded peripheral area•Boot Mode Select Option–Non-volatile Boot Memory can be internal or external–Selection is made by BMS pin sampled at reset•Abort Status Registers–Source, Type and all parameters of the access leading to an abort are saved •Misalignment Detector–Alignment checking of all data accesses–Abort generation in case of misalignment•Remap command–Provides remapping of an internal SRAM in place of the boot NVM3.7External Bus Interface•Integrates three External Memory Controllers:–Static Memory Controller–SDRAM Controller–Burst Flash Controller•Additional logic for NAND Flash/SmartMedia and CompactFlash support•Optimized External Bus:–16- or 32-bit Data Bus–Up to 26-bit Address Bus, up to 64-Mbytes addressable–Up to 8 Chip Selects, each reserved to one of the eight Memory Areas–Optimized pin multiplexing to reduce latencies on External Memories•Configurable Chip Select Assignment:–Burst Flash Controller or Static Memory Controller on NCS0–SDRAM Controller or Static Memory Controller on NCS1–Static Memory Controller on NCS3, Optional NAND Flash/SmartMedia Support –Static Memory Controller on NCS4 - NCS6, Optional CompactFlash Support –Static Memory Controller on NCS73.8Static Memory Controller•External memory mapping, 512-Mbyte address space•Up to 8 Chip Select Lines•8- or 16-bit Data Bus•Remap of Boot Memory•Multiple Access Modes supported–Byte Write or Byte Select Lines71768IS–ATARM–30-Sep-05 AT91RM9200 Summary–Two different Read Protocols for each Memory Bank•Multiple device adaptability–Compliant with LCD Module–Programmable Setup Time Read/Write–Programmable Hold Time Read/Write•Multiple Wait State Management–Programmable Wait State Generation–External Wait Request–Programmable Data Float Time3.9SDRAM Controller•Numerous configurations supported–2K, 4K, 8K Row Address Memory Parts–SDRAM with two or four Internal Banks–SDRAM with 16- or 32-bit Data Path•Programming facilities–Word, half-word, byte access–Automatic page break when Memory Boundary has been reached–Multibank Ping-pong Access–Timing parameters specified by software–Automatic refresh operation, refresh rate is programmable•Energy-saving capabilities–Self-refresh and Low-power Modes supported•Error detection–Refresh Error Interrupt•SDRAM Power-up Initialization by software•Latency is set to two clocks (CAS Latency of 1, 3 Not Supported)•Auto Precharge Command not used3.10Burst Flash Controller•Multiple Access Modes supported–Asynchronous or Burst Mode Byte, Half-word or Word Read Accesses–Asynchronous Mode Half-word Write Accesses•Adaptability to different device speed grades–Programmable Burst Flash Clock Rate–Programmable Data Access Time–Programmable Latency after Output Enable•Adaptability to different device access protocols and bus interfaces–Two Burst Read Protocols: Clock Control Address Advance or Signal Controlled Address Advance–Multiplexed or separate address and data buses81768IS–ATARM–30-Sep-05AT91RM9200 Summary–Continuous Burst and Page Mode Accesses supported3.11Peripheral DMA Controller (PDC)•Generates transfers to/from peripherals such as DBGU, USART, SSC, SPI and MCI •Twenty channels•One Master Clock cycle needed for a transfer from memory to peripheral•Two Master Clock cycles needed for a transfer from peripheral to memory3.12Advanced Interrupt Controller•Controls the interrupt lines (nIRQ and nFIQ) of an ARM ® Processor•Thirty-two individually maskable and vectored interrupt sources–Source 0 is reserved for the Fast Interrupt Input (FIQ)–Source 1 is reserved for system peripherals (ST, RTC, PMC, DBGU…)–Source 2 to Source 31 control thirty embedded peripheral interrupts or external interrupts–Programmable Edge-triggered or Level-sensitive Internal Sources–Programmable Positive/Negative Edge-triggered or High/Low Level-sensitive External Sources•8-level Priority Controller–Drives the Normal Interrupt of the processor–Handles priority of the interrupt sources 1 to 31–Higher priority interrupts can be served during service of lower priority interrupt •Vectoring–Optimizes Interrupt Service Routine Branch and Execution–One 32-bit Vector Register per interrupt source–Interrupt Vector Register reads the corresponding current Interrupt Vector •Protect Mode–Easy debugging by preventing automatic operations•General Interrupt Mask–Provides processor synchronization on events without triggering an interrupt3.13Power Management Controller•Optimizes the power consumption of the whole system•Embeds and controls:–One Main Oscillator and One Slow Clock Oscillator (32.768Hz)–Two Phase Locked Loops (PLLs) and Dividers–Clock Prescalers•Provides:–the Processor Clock PCK–the Master Clock MCK–the USB Clocks, UHPCK and UDPCK, respectively for the USB Host Port and the USB Device Port91768IS–ATARM–30-Sep-05 AT91RM9200 Summary–Programmable automatic PLL switch-off in USB Device suspend conditions –up to thirty peripheral clocks–four programmable clock outputs PCK0 to PCK3•Four operating modes:–Normal Mode, Idle Mode, Slow Clock Mode, Standby Mode3.14System Timer•One Period Interval Timer, 16-bit programmable counter•One Watchdog Timer, 16-bit programmable counter•One Real-time Timer, 20-bit free-running counter •Interrupt Generation on event3.15Real Time Clock •Low power consumption•Full asynchronous design•Two hundred year calendar•Programmable Periodic Interrupt•Alarm and update parallel load•Control of alarm and update Time/Calendar Data In3.16Debug Unit•System peripheral to facilitate debug of Atmel’s ARM ®-based systems•Composed of the following functions–Two-pinUART–Debug Communication Channel (DCC) support–Chip ID Registers•Two-pinUART–Implemented features are 100% compatible with the standard Atmel USART –Independent receiver and transmitter with a common programmable Baud Rate Generator–Even, Odd, Mark or Space Parity Generation–Parity, Framing and Overrun Error Detection–Automatic Echo, Local Loopback and Remote Loopback Channel Modes–Interrupt generation–Support for two PDC channels with connection to receiver and transmitter •Debug Communication Channel Support–Offers visibility of COMMRX and COMMTX signals from the ARM Processor –Interrupt generation•Chip ID Registers–Identification of the device revision, sizes of the embedded memories, set of peripherals101768IS–ATARM–30-Sep-05AT91RM9200 Summary3.17PIO Controller•Up to 32 programmable I/O Lines•Fully programmable through Set/Clear Registers•Multiplexing of two peripheral functions per I/O Line•For each I/O Line (whether assigned to a peripheral or used as general purpose I/O)–Input change interrupt–Glitch filter–Multi-drive option enables driving in open drain–Programmable pull up on each I/O line–Pin data status register, supplies visibility of the level on the pin at any time •Synchronous output, provides Set and Clear of several I/O lines in a single write3.18USB Host Port•Compliance with Open HCI Rev 1.0 specification•Compliance with USB V2.0 Full-speed and Low-speed Specification•Supports both Low-speed 1.5 Mbps and Full-speed 12 Mbps USB devices •Root hub integrated with two downstream USB ports•Two embedded USB transceivers•Supports power management•Operates as a master on the Memory Controller3.19USB Device Port•USB V2.0 full-speed compliant, 12 Mbits per second•Embedded USB V2.0 full-speed transceiver•Embedded dual-port RAM for endpoints•Suspend/Resume logic•Ping-pong mode (two memory banks) for isochronous and bulk endpoints •Six general-purpose endpoints–Endpoint 0, Endpoint 3: 8 bytes, no ping-pong mode–Endpoint 1, Endpoint 2: 64 bytes, ping-pong mode–Endpoint 4, Endpoint 5: 256 bytes, ping-pong mode3.20Ethernet MAC•Compatibility with IEEE Standard 802.3•10 and 100 Mbits per second data throughput capability•Full- and half-duplex operation•MII or RMII interface to the physical layer•Register interface to address, status and control registers•DMA interface, operating as a master on the Memory Controller•Interrupt generation to signal receive and transmit completion•28-byte transmit and 28-byte receive FIFOs111768IS–ATARM–30-Sep-05AT91RM9200 Summary•Automatic pad and CRC generation on transmitted frames •Address checking logic to recognize four 48-bit addresses•Supports promiscuous mode where all valid frames are copied to memory •Supports physical layer management through MDIO interface3.21Serial Peripheral Interface•Supports communication with serial external devices–Four chip selects with external decoder support allow communication with up to 15 peripherals–Serial memories, such as DataFlash and 3-wire EEPROMs–Serial peripherals, such as ADCs, DACs, LCD Controllers, CAN Controllers and Sensors–External co-processors•Master or slave serial peripheral bus interface–8- to 16-bit programmable data length per chip select –Programmable phase and polarity per chip select–Programmable transfer delays between consecutive transfers and between clock and data per chip select–Programmable delay between consecutive transfers –Selectable mode fault detection•Connection to PDC channel optimizes data transfers–One channel for the receiver, one channel for the transmitter –Next buffer support3.22Two-wire Interface•Compatibility with standard two-wire serial memory •One, two or three bytes for slave address •Sequential Read/Write operations3.23USART•Programmable Baud Rate Generator•5- to 9-bit full-duplex synchronous or asynchronous serial communications–1, 1.5 or 2 stop bits in Asynchronous Mode or 1 or 2 stop bits in Synchronous Mode –Parity generation and error detection–Framing error detection, overrun error detection –MSB- or LSB-first–Optional break generation and detection –By 8 or by-16 over-sampling receiver frequency –Optional hardware handshaking RTS-CTS–Optional modem signal management DTR-DSR-DCD-RI –Receiver time-out and transmitter timeguard–Optional Multi-drop Mode with address generation and detection121768IS–ATARM–30-Sep-05AT91RM9200 Summary•RS485 with driver control signal•ISO7816, T = 0 or T = 1 Protocols for interfacing with smart cards–NACK handling, error counter with repetition and iteration limit •IrDA modulation and demodulation–Communication at up to 115.2 Kbps •Test Modes–Remote Loopback, Local Loopback, Automatic Echo •Connection of two Peripheral DMA Controller (PDC) channels–Offers buffer transfer without processor intervention3.24Serial Synchronous Controller•Provides serial synchronous communication links used in audio and telecom applications •Contains an independent receiver and transmitter and a common clock divider •Interfaced with two PDC channels to reduce processor overhead •Offers a configurable frame sync and data length•Receiver and transmitter can be programmed to start automatically or on detection of different event on the frame sync signal•Receiver and transmitter include a data signal, a clock signal and a frame synchronization signal3.25Timer Counter•Three 16-bit Timer Counter Channels •Wide range of functions including:–Frequency Measurement –Event Counting –Interval Measurement –Pulse Generation –DelayTiming–Pulse Width Modulation –Up/down Capabilities•Each channel is user-configurable and contains:–Three external clock inputs –Five internal clock inputs–Two multi-purpose input/output signals •Internal interrupt signal•Two global registers that act on all three TC Channels3.26MultiMedia Card Interface•Compatibility with MultiMedia Card Specification Version 2.2•Compatibility with SD Memory Card Specification Version 1.0•Cards clock rate up to Master Clock divided by 2•Embedded power management to slow down clock rate when not used131768IS–ATARM–30-Sep-05AT91RM9200 Summary•Supports two slots–One slot for one MultiMedia Card bus (up to 30 cards) or one SD Memory Card •Support for stream, block and multi-block data read and write •Connection to a Peripheral DMA Controller (PDC) channel–Minimizes processor intervention for large buffer transfers141768IS–ATARM–30-Sep-05AT91RM9200 Summary4.AT91RM9200 Product Properties4.1Power SuppliesThe AT91RM9200 has five types of power supply pins:•VDDCORE pins. They power the core, including processor, memories and peripherals; voltage ranges from 1.65V to 1.95V , 1.8V nominal.•VDDIOM pins. They power the External Bus Interface I/O lines; voltage ranges from 3.0V to 3.6V , 3V or 3.3V nominal.•VDDIOP pins. They power the Peripheral I/O lines and the USB transceivers; voltage ranges from 3.0V to 3.6V, 3V or 3.3V nominal.•VDDPLL pins. They power the PLL cells; voltage ranges from 1.65V to 1.95V , 1.8V nominal.•VDDOSC pin. They power both oscillators; voltage ranges from 1.65V to 1.95V , 1.8V nominal.The double power supplies VDDIOM and VDDIOP are identified in Table 4-1 on page 15 and Table 4-2 on page 17. These supplies enable the user to power the device differently for inter-facing with memories and for interfacing with peripherals.Ground pins are common to all power supplies, except VDDPLL and VDDOSC pins. For these pins, GNDPLL and GNDOSC are provided, respectively.4.2PinoutThe AT91RM9200 is available in two packages:•208-lead PQFP , 31.2 x 31.2 mm, 0.5 mm lead pitch •256-ball BGA, 15 x 15 mm, 0.8 mm ball pitchThe product features of the 256-ball BGA package are extended compared to the 208-lead PQFP package. The features that are available only with the 256-ball BGA package are:•Parallel I/O Controller D•ETM port with outputs multiplexed on the PIO Controller D•a second USB Host transceiver, opening the Hub capabilities of the embedded USB Host.151768IS–ATARM–30-Sep-05AT91RM9200 Summary4.2.1208-lead PQFP Package PinoutTable 4-1.AT91RM9200 Pinout for 208-lead PQFP PackagePinNumberSignal NamePinNumberSignal NamePinNumberSignal NamePinNumberSignal Name1PC2437VDDPLL 73PA27109TMS 2PC2538PLLRCB 74PA28110NTRST 3PC2639GNDPLL 75VDDIOP 111VDDIOP 4PC2740VDDIOP 76GND 112GND 5PC2841GND 77PA29113TST06PC2942PA078PA30114TST17VDDIOM 43PA179PA31/BMS 115NRST 8GND 44PA280PB0116VDDCORE 9PC3045PA381PB1117GND 10PC3146PA482PB2118PB2311PC1047PA583PB3119PB2412PC1148PA684PB4120PB2513PC1249PA785PB5121PB2614PC1350PA886PB6122PB2715PC1451PA987PB7123PB2816PC1552PA1088PB8124PB2917PC053PA1189PB9125HDMA 18PC154PA1290PB10126HDPA 19VDDCORE 55PA1391PB11127DDM 20GND 56VDDIOP 92PB12128DDP 21PC257GND 93VDDIOP 129VDDIOP 22PC358PA1494GND 130GND 23PC459PA1595PB13131VDDIOM 24PC560PA1696PB14132GND 25PC661PA1797PB15133A0/NBS026VDDIOM 62VDDCORE 98PB16134A1/NBS2/NWR227GND 63GND 99PB17135A228VDDPLL 64PA18100PB18136A329PLLRCA 65PA19101PB19137A430GNDPLL 66PA20102PB20138A531XOUT 67PA21103PB21139A632XIN 68PA22104PB22140A733VDDOSC 69PA23105JT AGSEL 141A834GNDOSC 70PA24106TDI 142A935XOUT3271PA25107TDO 143A1036XIN3272PA26108TCK144SDA10161768IS–ATARM–30-Sep-05AT91RM9200 SummaryNote: 1.Shaded cells define the pins powered by VDDIOM.4.2.2Mechanical Overview of the 208-lead PQFP PackageFigure 4-1 shows the orientation of the 208-lead PQFP package.A detailed mechanical description is given in the section Mechanical Characteristics.Figure 4-1.208-lead PQFP Pinout (Top View)145A11161PC7177CAS 193D10146VDDIOM 162PC8178SDWE 194D11147GND 163PC9179D0195D12148A12164VDDIOM 180D1196D13149A13165GND 181D2197D14150A14166NCS0/BFCS 182D3198D15151A15167NCS1/SDCS 183VDDIOM 199VDDIOM 152VDDCORE 168NCS2184GND 200GND 153GND 169NCS3/SMCS 185D4201PC16154A16/BA0170NRD/NOE/CFOE 186D5202PC17155A17/BA1171NWR0/NWE/CFWE 187D6203PC18156A18172NWR1/NBS1/CFIOR 188VDDCORE 204PC19157A19173NWR3/NBS3/CFIOW 189GND 205PC20158A20174SDCK 190D7206PC21159A21175SDCKE 191D8207PC22160A22176RAS192D9208PC23Table 4-1.AT91RM9200 Pinout for 208-lead PQFP Package (Continued)PinNumberSignal NamePinNumberSignal NamePinNumberSignal NamePinNumberSignal Name171768IS–ATARM–30-Sep-05AT91RM9200 Summary4.2.3256-ball BGA Package PinoutTable 4-2.AT91RM9200 Pinout for 256-ball BGA PackagePin Signal Name Pin Signal Name Pin Signal Name Pin Signal Name A1TDI C3PD14E5TCK G14PA1A2JT AGSEL C4PB22E6GND G15PA2A3PB20C5PB19E7PB15G16PA3A4PB17C6PD10E8GND G17XIN32A5PD11C7PB13E9PB7H1PD23A6PD8C8PB12E10PB3H2PD20A7VDDIOP C9PB6E11PA29H3PD22A8PB9C10PB1E12PA26H4PD21A9PB4C11GND E13PA25H5VDDIOP A10PA31/BMS C12PA20E14PA9H13VDDPLL A11VDDIOP C13PA18E15PA6H14VDDIOP A12PA23C14VDDCORE E16PD3H15GNDPLL A13PA19C15GND E17PD0H16GND A14GND C16PA8F1PD16H17XOUT32A15PA14C17PD5F2GND J1PD25A16VDDIOP D1TST1F3PB23J2PD27A17PA13D2VDDIOP F4PB25J3PD24B1TDO D3VDDIOP F5PB24J4PD26B2PD13D4GND F6VDDCORE J5PB28B3PB18D5VDDIOP F7PB16J6PB29B4PB21D6PD7F9PB11J12GND B5PD12D7PB14F11PA30J13GNDOSC B6PD9D8VDDIOP F12PA28J14VDDOSC B7GND D9PB8F13PA4J15VDDPLL B8PB10D10PB2F14PD2J16GNDPLL B9PB5D11GND F15PD1J17XIN B10PB0D12PA22F16PA5K1HDPA B11VDDIOP D13PA21F17PLLRCB K2DDM B12PA24D14PA16G1PD19K3HDMA B13PA17D15PA10G2PD17K4VDDIOP B14PA15D16PD6G3GND K5DDP B15PA11D17PD4G4PB26K13PC5B16PA12E1NRST G5PD18K14PC4B17PA7E2NTRST G6PB27K15PC6C1TMS E3GND G12PA27K16VDDIOM C2PD15E4TST0G13PA0K17XOUT181768IS–ATARM–30-Sep-05AT91RM9200 SummaryNote: 1.Shaded cells define the pins powered by VDDIOM.4.2.4Mechanical Overview of the 256-ball BGA PackageFigure 4-2 on page 19 shows the orientation of the 256-ball BGA Package.A detailed mechanical description is given in the section Mechanical Characteristics.L1GND N2A5P13D15T7NWR1/NBS1/ CFIOR L2HDPB N3A9P14PC26T8SDWE L3HDMB N4A4P15PC27T9GND L4A6N5A14P16VDDIOM T10VDDCORE L5GND N6SDA10P17GND T11D9L6VDDIOP N7A8R1GND T12D12L12PC10N8A21R2GND T13GND L13PC15N9NRD/NOE/CFOE R3A18T14PC19L14PC2N10RAS R4A20T15PC21L15PC3N11D2R5PC8T16PC23L16VDDCORE N12GND R6VDDIOM T17PC25L17PLLRCA N13PC28R7NCS3/SMCS U1VDDCORE M1VDDIOM N14PC31R8NWR3/NBS3/ CFIOW U2GND M2GND N15PC30R9D0U3A16/BA0M3A3N16PC11R10VDDIOM U4A19M4A1/NBS2/NWR2N17PC12R11D8U5GND M5A10P1A7R12D13U6NCS0/BFCS M6A2P2A13R13PC17U7SDCK M7GND P3A12R14VDDIOM U8CAS M9NCS1/SDCS P4VDDIOM R15PC24U9D3M11D4P5A11R16PC29U10D6M12GND P6A22R17VDDIOM U11D7M13PC13P7PC9T1A15U12D11M14PC1P8NWR0/NWE/CFWE T2VDDCORE U13D14M15PC0P9SDCKE T3A17/BA1U14PC16M16GND P10D1T4PC7U15PC18M17PC14P11D5T5VDDIOM U16PC20N1A0/NBS0P12D10T6NCS2U17PC22Table 4-2.AT91RM9200 Pinout for 256-ball BGA Package (Continued)Pin Signal Name Pin Signal Name Pin Signal Name Pin Signal Name。

基于AT91RM9200的以太网接口模块设计

摘 要:主要介绍基于AT91RM9200处理器的以太网接口模块设计,给出基于网络芯片RTL8019AS的系统外围接口相关器件选型。在硬件设计的基础上,给出了详细的编程思想、工作流程以及部分关键代码。在此设计方案下,完全可以实现通过以太网进行通信,达到嵌入式模块之间实时控制的目的。关键词:AT9பைடு நூலகம்RM9200;以太网;RTL8019AS;嵌入式模块

使发送缓冲区可以容纳下两个最大以太网帧(最大为1 514 B),第一个帧放在SEND_START_PAGEO起始页,第二个帧放在SEND_START_PAGE1起始页,剩下的缓冲区都作为接收缓冲区。 RTL8019AS内部RAM是双口 RAM,因为它要支持两个独立的操作:一个是用户CPU读取RAM中的内容,对这个操作RTL8019AS提供一个读写口,也就是寄存器中的Remote DMA Port;另一个是RTL8019AS内部控制电路把从网络接收的数据写入RAM中,这时RAM称为Local DMA。RTL8019AS通过Local DMA写入RAM是不需要用户干涉的,它通过Remote DMA Port读写RAM。 读RAM见RTLReadRam函数,代码如下:

3 以太网接口设计 在ARM系统中,以太网接口是与远程机进行通信及调试的基础,还可以进行内部局域网和互联网间的通信。而基于ARM的系统若没有以太网接口,其应用价值就会大打折扣。因此,就整个嵌入式系统而言,以太网接口电路是必不可少的,但同时也是相对复杂的。 从硬件的角度看,以太网接口电路主要由MAC控制器和物理层接口(PHY)两大部分构成。该设计中所用到的以太网接口芯片RTL8019AS,其内部结构包含这两部分。RTL8019AS是一款高集成度的以太网控制芯片,具有8/16位总线模式,集成了IEEE802.3协议标准的MAC层和PHY层的性能,与NE2000相兼容,支持以太网全双工通信方式;支持UTP,AUI和BNC自动检测,支持16位I/O基本地址选项和额外I/O地址输入/输出完全解码方式;支持存储器瞬时读写,收发可同时达到10 Mb/s的速率,内置16 KB的SRAM,可以方便地与微处理器进行连接。它支持多种嵌入式处理器芯片,内置有FIFO缓存器用于发送和接收数据。3.1 以太网接口工作原理 使用RTL8019AS作为以太网的物理层接口,它的基本工作原理是:在收到由主机发来的数据包后,侦听网络线路。如果线路忙,它就等到线路空闲为止,否则,立即发送该数据帧。在发送过程中,首先为数据包添加帧头(包括前导字段和帧开始标志),然后生成CRC校验码,最后将此数据帧发送到以太网上。 在接收过程中,它将从以太网收到的数据包在经过解码、去帧头和地址校验等步骤后缓存在片内。在CRC校验通过后,它会根据初始化配置情况,通知RTL8019AS收到了数据包。最后,用某种传输模式(I/O模式、Memory模式、DMA模式)传到ARM系统的存储区中。3.2 硬件电路设计 用RTL8019AS芯片设计的以太网控制器相关电路,可以通过RJ45连上以太网,在判断网卡芯片是否工作正常时,有两个依据,一是看状态指示LED是否有闪烁;二是用专用网络监听工具软件进行监听。在本设计中用两个LED指示灯表示接收和发送状态,当有网络连接且收发数据包时,LED闪烁。此外,网卡芯片单独不能工作,还必须有一个网络变压器在RJ45接口和网卡芯片中间进行电平转换,该设计中所用的电平转换器是20F001N。另外要特别注意,由于RTL8019AS的复位引脚是高电平有效,而AT91RM9200的NRST引脚是低电平有效,所以不能直接将两个引脚进行连接。该设计所用的解决方法是:在两引脚间加上一个共发射极的三极管,利用它的反相作用,来达到两个复位引脚间的电平匹配。同时,为了提高数据的传输速率,需要将网卡芯片设计成16位的数据通道,这就要求将RTL8019AS的IOCSl6B引脚用电阻上拉来达到设计目的。RTL8019AS与AT91RM9200进行连接还需要以下引脚:NOE,NEW,NCS2,D[O:15],一条中断线IRQ0以及地址线A[O:4](设计RTL8019AS的I/O基地址为300H,所以只需要SA[O:4]接A[O:4],而A[5:19]只需要接地即可)。至此,硬件电路已经设计完毕,整个电路的结构框图。

AT91RM9200处理器的内部启动机制

1.引言在开发基于AT91RM9200处理器的嵌入式系统时,以何种方式启动系统是一个首先要考虑的基本问题。

庆幸的是,AT91RM9200处理器提供了各种各样的启动方式,总体上可分为从外部的DATAFLASH、二线EEPROM或8位并行存储器引导启动和从内部的BOOTROM引导启动两种情况。

当从外部存储器启动时,存储器中的启动代码又是从那里来的呢?有3种手段,可以直接通过编程器将启动代码写入外部存储器,也可以通过JTAG 接口从主机下载到目标系统的闪存芯片,还可以由AT91RM9200处理器的内部BOOTROM 启动系统与主机建立通信并下载所需代码再写入闪存芯片。

那么当从内部的BOOTROM启动时,所需的启动代码又是如何得到的呢?很简单,芯片厂商在生产芯片时就嵌入了这段代码。

内嵌的启动代码被存储在AT91RM9200处理器的片内ROM中,片内ROM的起始物理地址是0x0010_0000,片内SRAM的起始物理地址为0x0020_0000。

我们都知道ARM 处理器启动时会产生复位异常,程序计数器PC指向复位异常向量地址0x0000_0000,也就是说启动时首先执行的是位于地址0x0000_0000处的指令。

因此从0x0000_0000到0x0010_0000的1M的内部存储区域(内部存储区0)在上电启动时的代码将决定系统的启动过程。

那么是应该由外部存储器中的启动代码来占据内部存储区0以实现外部启动,还是应该由位于0x0010_0000(内部存储区1)处的ROM中的内嵌启动代码来占据这一空间以实现内部启动呢?这就需要一个仲裁机制来进行选择。

这就是AT91RM9200芯片的PA31/BMS引脚(在PQFP封装中为79脚,在BGA封装中为A10脚)。

BMS即Boot Mode Select(启动模式选择),若BMS=1,则将内部存储区1的数据映射至内部存储区0,即从内部的ROM启动;若BMS=0,则将外部存储器的区域0映射至内部存储区0,即从外部存储器启动。

AT91RM9200简明手册

NRST是一个无上拉电阻的施密特触发器。NRST信号被包含到边界扫描中。

6.4 PIO 控制器A,B,C,D端口

所有的I/O口线,PA0-PA31、PB0-PB29、PC0-PC31、PD0-PD31、内部都集成了一个可编程的上拉电阻 (15K)。通过PIO控制器可以对每一个I/O的上拉电阻进行单独控制。

6

中嵌科技有限公司 表 3-1. 外设信号说明

7

中嵌科技有限公司 表 3-1. 外设信号说明

8

中嵌科技有限公司 表 3-1. 外设信号说明

4. 封装和引脚输出

7.2 调试与测试

· 集成了嵌入式内部电路仿真器 · 调试单元

- 两引脚的UART - 调试信道 - 芯片 ID 寄存器 · 嵌入式追踪宏单元:ETM9™ Rev2a - 中级实现 - 半速时钟模式 - 四对地址比较器 - 两个数据比较器 - 八个存储器映射解码器输入 - 两个计数器 - 一个序列发生器 - 一个18个字节的FIFO · 所有数字引脚的 IEEE 1149.1 JTAG 边界扫描

TDO为三态输出引脚。引脚JTAGSEL拉高时选择JTAG边界扫描功能。 NTRST引脚被用来初始化内置ICE™ TAP控制器。

6.2 测试引脚

TST1、TST0引脚用来定义器件的测试模式。这些引脚都没有集成下拉电阻所以用户必须确保这些引脚都 为低,以提供正常工作的条件(若为高将导致不可预知的结果)。与这些引脚相关的其它值保留作厂商测试 用。

4.1 208 引脚 PQFP 封装轮廓 图4-1给出208引脚PQFP封装定位。详细的机械说明见生产数据手册的AT91RM9200机械特性部分。 图 4-1. 208引脚PQFP封装(俯视图)

采用AT91RM9200处理器实现对两套导航计算机的测试设计

采用AT91RM9200处理器实现对两套导航计算机的测试设计引言导航计算机是捷联组合导航组件的组成部件,可接收来自多路输入数据接口的数据,并将结果由输出数据接口控制输出。

为了验证导航计算机的功能和性能指标,可用测试仪器来完成导航计算机的检测和测试。

导航计算机测试仪器的总体研制目标就是希望能够方便快捷地实现对两套导航计算机的测试,包括导航计算机多个接口的速率测试、接口传输数据正确性和完整性测试、以及导航计算机数据处理DSP的测试。

1 系统组成本导航计算机测试仪器主要由测试模块和显示控制模块两大部分组成。

其中测试模块主要包括测试接口与测试单元;显示控制模块是导航计算机测试仪的输入和输出设备,主要包括上位机处理单元和显示单元。

其具体组成如图l所示。

2 测试模块测试模块主要用于对导航计算机工作状态及性能的测试,包括对导航计算机各个接口的测试,以及对DSP处理性能的测试等。

测试模块主要包括测试接口与测试单元。

为了满足同时测试两套导航计算机的要求,同时为了方便升级,本设计考虑一对一的测试模式.图2所示是针对一套导航计算机的测试模块组成框图。

为满足两套导航计算机的所有接口都能同时按照要求速率工作,可选择两片处理器实现一对一测试,以保证其实时性。

测试部分的处理器可选用Atmel公司的AT91RM9200作为测试仪器的中心控制部分,其两片处理器的功能相同。

现以其中一片为例来说明,其主要功能包括:(1)按所要求的速率发送数据,并中断接收两路RS232、9路RS422A、l路RS429(1收2发)数据通讯接口的数据,同时卸帧、测试数据传输接口速率、数据正确性和数据完整性;(2)测试结果应通过RS232接口与显示部分相连,并实时显示;。

AD7490与AT91RM9200的SPI接口及其驱动程序的实现

AD7490与AT91RM9200的SPI接口及其驱动程序的实现徐伟;胡志忠;肖前贵;李志宇

【期刊名称】《计算机测量与控制》

【年(卷),期】2009(017)010

【摘要】SPI总线系统是一种同步串行外设接口,它使MCU与各种外围设备以串行方式进行通信以交换信息;设备驱动程序作为操作系统内核和硬件之间的接口,是嵌入式开发的重要组成部分;该文介绍了串行外设接口(SPI)在高速串行模数转换器AD7490与ARM微处理器AT91RM9200的接口中的应用方案;给出了详细的硬件连接图和Linux下驱动程序的实现方法,为高速数据采集的嵌入式设备提供了一个解决方案.

【总页数】3页(P2089-2091)

【作者】徐伟;胡志忠;肖前贵;李志宇

【作者单位】南京航空航天大学,信息科学与技术学院,江苏,南京,210016;南京航空航天大学,信息科学与技术学院,江苏,南京,210016;南京航空航天大学,自动化学院,江苏,南京,210016;南京航空航天大学,自动化学院,江苏,南京,210016

【正文语种】中文

【中图分类】TP212

【相关文献】

1.基于AT91RM9200的嵌入式Linux驱动程序的开发 [J], 王慧娟;刘立媛;袁全波

2.军用电站监测系统采集模块的SPI接口及其驱动程序的实现 [J], 葛庆庆;邵天章;

徐晓亮

3.基于AT91RM9200和嵌入式Linux的I2C总线驱动程序 [J], 张圣华;喻晓峰;石崇林

4.基于AT91RM9200的模拟量输入驱动程序设计 [J], 席作鹏;闫学文

5.基于AT91RM9200的LCD驱动程序设计 [J], 熊敏;万频;谷刚;詹宜巨

因版权原因,仅展示原文概要,查看原文内容请购买。

VxWorks在AT91RM9200上的BSP设计

VxWorks在AT91RM9200上的BSP设计编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望(VxWorks在AT91RM9200上的BSP设计)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为VxWorks在AT91RM9200上的BSP设计的全部内容。

VxWorks在AT91RM9200上的BSP设计摘要阐述VxWorks实时操作系统中板级支持包BSP的概念和作用;研究VxWorks映像的生成和分类,以及系统的启动流程;着重介绍VxWorks操作系统在ARM9芯片AT9lRM9200上的BSP 设计。

关键词 VxWorks BSP 映像ARM AT91RM9200VxWorks是美国Wind River公司开发的嵌入式实时操作系统,具有高性能、可裁减性好等特点,能支持多种微处理器(如PowerPC、X85、ARM、SPARC);自问世以来,以其良好的町靠性和卓越的实时性被广泛地应用于通信、航空、航天等高精尖技术及实时性要求极高的领域中。

BSP(Board Support Package,板级支持包)的作用是针对特殊的硬件平台,为操作系统内核提供操作接口,使操作系统能够独立于底层硬件。

对上层应用屏蔽具体硬件,VxWorks的高可移植性就是通过BSP实现的.AT91RM9200是Atmel公司生产的一款ARM9核芯片,本文重点介绍将VxWorks移植到该芯片过程中BSP的定制过程。

1 BSP概念BSP通常是指针对具体的硬件平台,用户所编写的启动代码和部分设备驱动程序的集合。

它所实现的功能包括初始化和驱动部分设备.最基本的BSP仅需要支持处理器复位、初始化、驱动串口和必要的时钟处理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

的 以 太 网 控 制 芯 片 ) 另 一 种 是 通 过 以 ; 太 网接 E控 制 芯 片 ( L l 如 AN9 C 6 l 9 、RT 一 L

2 MA控制 送 出去 。 接 收 数据 帧 :首 先通 过 底层 芯片 将

‘ B R 、1 T C D )…. . 按迭字节 寄存器 D MA接收 寄存器 ( SAK …… 一 面起始 地址寄存 器 P T T) 页 ( S OP) PT …… …. 停止寄存 器 页面 ( UR C R)~……一 当前 页面寄存 器 ( NR B y)…… …一 界指针 寄存器 边 ( B …… ……. 收字节寄 存器 R C) 接

制器的以太网接口 驱动程序设计来系统地 J 【上 数据 帧的控制功能 提供 MI Me i 硐 I( d a 分析以太网控制器和物理 层芯片的驱动程 l Id p n e  ̄l efc )标准管理通信接 nee dn i r e n a

n。但它本身不具有直接 从网上收发数 据 的能力 必须接台物理层数据传输 1 A 9R 20 芯片 D 1 1 M9 6 来完成对网上数据的接 T1M90 以太网控制器及物 f 理层芯片 D 9 6 工作原理 M 11 『 收解码和 敖据帧编 码发送 任务 根据圈 1 ,可以看出 MAC层是通过 DMA 控制 方式来接手发送 和接收数据 , 1 1 A 1 M9 0 融控制器… . T9 R 20 DMA 直接通过 AS B总线与存储器进行通 A 1 M9 0是 由An 公 司针对通 f T9R 20 tml 信 。EMAc( 以太 r控制 器】 蝴 与物理 层芯 片 信 领 域 , 系 统 控 制 推 出 的 一 种 基 于

.

序设计原理和实现方法 。

A R M 9 0 2 T

前言

随着嵌人式 系统在 工程应 用和人们生 括中 的运用 越来越 广 .对它 的分析 研究 也越 来越 多 ,嵌入式 系统 与通信 、网络 技术的结合可以极大地增强网络的智能化 与灵 活性 ,拓展 通信功 能 ,从而实 现各

块即以太嗣控制器部分 ,由它集台物理层 恃输芯片 D 1 1 M9 6 殛相应的驱动程序来通 过 DMA控制方式完成对网上敖据帧的读

平台 L,针对相同的底屠芯片需要编辑 不 J 写 。 同的驱动程序s 而相同的操作系 统在不同 『 12 . 鼬太网接 口控制 器的 工作 原理

的硬件平 台上也需要编辑不同的驱动程序。

维普资讯

基于 AT 1 9 RM9 0 微控 制器的 20

以太 网接 口驱 动程序设 计

程 佳佳 宋 晓红 张宁 北 京 交通 大 学计算 机 网络 管 理 中 10 4 04 0

种通 信 系统 之 间的互 联互通 根据嵌人 式 内核可 裁减 、硬 件和驱动 程序 紧密结 合的特点 ,不 同的操 作系统 在同一 个硬件

图 3 以太 网控制器 D A通道数据传输原理 图 、 M

图 2 以太网控制器内部功 能模块 图 、

D MA发送寄 存器 ( P R) T s …… …~ 发送页面 起始寄存 器

之 间通 信是通过 P O口来实现。在实际的 I 驱 动程序 编写 中可 以通过 设置 PI 口的 O

P DR ( I ia l e i e )来 配 置 使 P O D sbe R gs r t

在编写躯动程序之前首先分析 一下它

而以太网通信接 口驱动程序通常是嵌入式

的硬件电路.以太网接 I部分主要分成两 1 : 系统所必需的 ,有时为 了各种原因 ,如安 l 个部分:”. 以太嗣控制器t )物理 层实现 . 2 全性或实时性等考虑需要更换其它操作系 『 数据帻的发送和接收芯片 统,选时原有的以太网驱动程序就不再有 AT 9 1 RM9 0 2 0本身带有 以太 研控 制 用,必须更改。本文就 A I, 2 0 T9PM9 0 撇控 1 器,兼容 I E 8 2 3 议标准 .具有对 E E 0 .

据帧的 MAC地 址 ,帧头信息和 C RC校 验 码 是 否正 确 ,如 果 不正 确 就 册 除 掉 , 0 正确通过 DMA 通道将数据拷 贝到接收缓

采用 RMI 还是 MI 控 制方式视硬件 I I 电路 设 计而 定 ,如今 大 多采 用 R I( 简 MI 精

。

存 区 。这 个过 程 涉及 到 复杂 的存 储 区管

维普资讯

C N l 吃 J = o T Ur K

=

ME啪 R Y

U ^

C

1 6 IBtI . I1 2y I} 1 } tFO ¨  ̄l 8  ̄

^

卜

D^ ^ T

S S TEM Y ∞ , H O

£ M oRY

2 1D . MA通 道数据传输控制原理

图 3描述 了数据 帧是 如何由 D MA通 道 来进 行数 据 传输 , 网上接 收到 的数 据 帧通过 D l l M9 6 解码后传输 到 F F I O,然

能 MDC ( 管理数据控制 器) ,MDI ( O 管

理数据输入输 出) E 0 ( , F1 0 使能全双工 10 0 M以太网)采用 MI R I , I MI / 方式选择等

1I 2

接收 到 的数 据 帧传输 到 28字节 的接 收 F F 中, IO 当一帧数据接收完以后 ,检验数

理 ,必 须结 合 了解存 储 区 之 间的关 系 。

型 MI)方 式 ,只 需 连 两 根 线 ( XD / , I R 0 1

图 4、D MA控 制器 中发送 、接收核 心寄存器

Tx / ) D0 1 ,简洁方便。

13 以太 网控 制 器 的 功 能 及 对 发 送 和 .

接收数据 帧的控制原理