FPGA可编程逻辑器件芯片XCVU125-2FLVB1760I中文规格书

FPGA可编程逻辑器件芯片XCVU065-2FFVC1517I中文规格书

Recommended PCB Design Rules for BGA PackagesBGA PackagesXilinx provides the diameter of a land pad on the package side. This information is required prior to the start of the board layout so the board pads can be designed to match the component-side land geometry. The typical values of these land pads are described in Figure 8-1 and summarized in Table 8-1. PCB pad size is based on the BGA ball size. Typical requirements for the PCB pad size are 80-120% of ball size however, given a large package size and to prevent solder bridging, a pad size closer to 80% of the ball size isrecommended. For Xilinx BGA packages, non-solder mask defined (NSMD) pads on the board are suggested to allow a clearance between the land metal (diameter L) and the solder mask opening (diameter M) as shown in Figure 8-1.Figure 8-1:Suggested Board Layout of Soldered Pads for BGA PackagesUG575_c8_01_102213Packaging OverviewIntroduction to the UltraScale ArchitectureThe Xilinx® UltraScale™ architecture is the first ASIC-class architecture to enablemulti-hundred gigabit-per-second levels of system performance with smart processing,while efficiently routing and processing data on-chip. UltraScale architecture-based devices address a vast spectrum of high-bandwidth, high-utilization system requirements by using industry-leading technical innovations, including next-generation routing, ASIC-likeclocking, 3D-on-3D ICs, multiprocessor SoC (MPSoC) technologies, and new powerreduction features. The devices share many building blocks, providing scalability acrossprocess nodes and product families to leverage system-level investment across platforms.Virtex® UltraScale+™ devices provide the highest performance and integration capabilities in a FinFET node, including both the highest serial I/O and signal processing bandwidth, as well as the highest on-chip memory density. As the industry's most capable FPGA family, the Virtex UltraScale+ devices are ideal for applications including 1+Tb/s networking and data center and fully integrated radar/early-warning systems.Virtex UltraScale devices provide the greatest performance and integration at 20nm,including serial I/O bandwidth and logic capacity. As the industry's only high-end FPGA at the 20nm process node, this family is ideal for applications including 400G networking, large scale ASIC prototyping, and emulation.Kintex® UltraScale+ devices provide the best price/performance/watt balance in a FinFET node, delivering the most cost-effective solution for high-end capabilities, includingtransceiver and memory interface line rates as well as 100G connectivity cores. Our newest mid-range family is ideal for both packet processing and DSP-intensive functions and is well suited for applications including wireless MIMO technology, Nx100G networking, and data center.Kintex UltraScale devices provide the best price/performance/watt at 20nm and include the highest signal processing bandwidth in a mid-range device, next-generationtransceivers, and low-cost packaging for an optimum blend of capability andcost-effectiveness. The family is ideal for packet processing in 100G networking and data centers applications as well as DSP-intensive processing needed in next-generation medical imaging, 8k4k video, and heterogeneous wireless infrastructure.Solder PasteSolder paste consists of solder alloy and a flux system. A typical solder paste composition by volume is split between about 50% alloy and 50% flux. The metal load mass (solder alloy powder) is around 90%, with the remaining 10% mass a flux system. The primary purpose of the flux system is to remove the contaminations from the solder joints during the soldering process. The capability of removing contaminations is determined by the activation level of the type of solder paste. The preferred solder paste metal alloy has a lead-free composition (SnAgCu where Ag is 3–4% and Cu is 0.5–1%). A no-clean solder paste is preferred to eliminate any risk of improper cleaning that could leave active residue beneath the device and other BTC components. The paste must be suitable for printing the solder stencil aperture dimensions. Type 4 paste is recommended for better paste release performance. When using a solder paste, you must adhere to the handling recommendations of the paste manufacturer.Chapter 8:Recommended PCB Design Rules for BGA PackagesFlip-Chip BGA Packages1.0 mm Pitch0.8 mm PitchDesign RuleDimensions in mm (mils)Package land pad opening (SMD)0.53 mm (20.9 mils)0.40 mm (15.7 mils)Maximum PCB solder land (L) diameter 0.50 mm (19.7 mils)0.40 mm (15.7 mils)Opening in PCB solder mask (M) diameter 0.65 mm (25.6 mils)0.50 mm (19.7 mils)Solder ball land pitch (e)1.00 mm (39.4 mils)0.80 mm (31.5 mils)BGA PackageBGA Solder BallSolder MaskPCBUG358_aA_02_110513。

FPGA可编程逻辑器件芯片XCKU115-2FLVD1924I中文规格书

DS022-2 (v3.0) March 21, 2014Production Product Specification Data Output Bus—DO[A|B]<#:0>The data out bus reflects the contents of the memory cellsreferenced by the address bus at the last active clock edge.During a write operation, the data out bus reflects the datain bus. The width of this bus equals the width of the port.The allowed widths appear in Table 15.Inverting Control Pins The four control pins (CLK, EN, WE and RST) for each port have independent inversion control as a configuration option.Address MappingEach port accesses the same set of 4096 memory cellsusing an addressing scheme dependent on the width of theport.The physical RAM location addressed for a particular widthare described in the following formula (of interest only whenthe two ports use different aspect ratios).Start = ((ADDR port +1) * Width port ) –1End = ADDR port * Width port Table 16 shows low order address mapping for each port width.Creating Larger RAM Structures The block SelectRAM+ columns have specialized routing to allow cascading blocks together with minimal routing delays.This achieves wider or deeper RAM structures with a smaller timing penalty than when using normal routing channels. Location Constraints B lock SelectRAM+ instances can have LOC properties attached to them to constrain the placement. The blockSelectRAM+ placement locations are separate from theCLB location naming convention, allowing the LOC proper-ties to transfer easily from array to array.The LOC properties use the following form.LOC = RAMB4_R#C#RAMB 4_R0C0 is the upper left RAMB 4 location on thedevice.Conflict ResolutionThe block SelectRAM+ memory is a true dual-read/writeport RAM that allows simultaneous access of the samememory cell from both ports. When one port writes to agiven memory cell, the other port must not address thatmemory cell (for a write or a read) within the clock-to-clocksetup window. The following lists specifics of port and mem-ory cell write conflict resolution.•If both ports write to the same memory cellsimultaneously, violating the clock-to-clock setuprequirement, consider the data stored as invalid.•If one port attempts a read of the same memory cellthe other simultaneously writes, violating theclock-to-clock setup requirement, the following occurs.-The write succeeds-The data out on the writing port accurately reflectsthe data written.-The data out on the reading port is invalid.Conflicts do not cause any physical damage.Single Port Timing Figure 33 shows a timing diagram for a single port of a block SelectRAM+ memory. The block SelectRAM+ AC switching characteristics are specified in the data sheet. The block SelectRAM+ memory is initially disabled.At the first rising edge of the CLK pin, the ADDR, DI, EN,WE, and RST pins are sampled. The EN pin is High and the WE pin is Low indicating a read operation. The DO bus con-tains the contents of the memory location, 0x00, as indi-cated by the ADDR bus.At the second rising edge of the CLK pin, the ADDR, DI, EN,WR, and RST pins are sampled again. The EN and WE pins are High indicating a write operation. The DO bus mirrors the DI bus. The DI bus is written to the memory location 0x0F .At the third rising edge of the CLK pin, the ADDR, DI, EN,WR, and RST pins are sampled again. The EN pin is Highand the WE pin is Low indicating a read operation. The DObus contains the contents of the memory location 0x7E asindicated by the ADDR bus.At the fourth rising edge of the CLK pin, the ADDR, DI, EN,WR, and RST pins are sampled again. The EN pin is LowTable 16: Port Address Mapping Port WidthPort Addresses 14095...1514131211100908070605040302010022047...070605040302010041023...030201008511...010016255 (00)DS022-4 (v3.0) March 21, 2014Production Product Specification 1885AA12AJ12√VREF 1895AB12AE11√-1905AK12Y132-1915AG11AF112-1925AH11AJ112-1935AE12AG104-1945AD12AK11√-1955AJ10AC12√VREF 1965AK10AD114-1975AJ9AE94-1985AH10AF9√VREF 1995AH9AK9√-2005AF8AB112-2015AC11AG82-2025AK8AF7√VREF 2035AG7AK7√-2045AJ7AD101-2055AH6AC101-2065AD9AG6√VREF 2075AB10AJ5√-2085AD8AK52-2095AC9AJ42VREF 2105AG5AK42-2115AH5AG34-2126AC6AF3√-2136AG2AH2NA -2146AE4AB91-2156AH1AE34VREF 2166AD6AB83-2176AA10AG14-2186AD4AA91VREF 2196AD2AD5√-2206AF2AD34-2216AA7AA81-Table 27: FG900 Differential Pin Pair SummaryXCV600E, XCV1000E, XCV1600EPairBank PPin N Pin AO Other Functions 2226Y9AF1√VREF 2236AC4AB6√-2246W8AE12-2256AB4Y84-2266W9AB34VREF 2276W10AA54-2286V10AB14-2296AC1Y74VREF 2306AA3V11NA -2316U10AA24-2326AA6W71-2336Y4Y64-2346V7AA13-2356Y2Y34-2366W5Y51VREF 2376W6W4√-2386W2V64-2396V4U91-2406T8AB2√VREF 2416W1U5√-2426T9Y12-2436U3T74-2446V2T54VREF 2456T6R94-2466U2T44VREF2477R10T1NA 2487R6R54-2497R4R84VREF 2507R3R74-2517P6P104VREF 2527P2P54-2537P4P72-2547R2N4√-2557P1N7√VREF Table 27: FG900 Differential Pin Pair Summary XCV600E, XCV1000E, XCV1600E Pair Bank P Pin N Pin AO Other Functions。

FPGA可编程逻辑器件芯片XCVU080-1FFVB1760I中文规格书

XC9572XL High Performance CPLD DS057 (v2.0) April 3, 2007Product SpecificationAC Characteristics SymbolParameter XC9572XL-5XC9572XL-7XC9572XL-10Units Min Max Min Max Min Max T PDI/O to output valid - 5.0-7.5-10.0ns T SUI/O setup time before GCK 3.7- 4.8- 6.5-ns T HI/O hold time after GCK 0-0-0-ns T COGCK to output valid - 3.5- 4.5- 5.8ns f SYSTEMMultiple FB internal operating frequency -178.6-125.0-100.0MHzT PSUI/O setup time before p-term clock input 1.7- 1.6- 2.1-ns T PHI/O hold time after p-term clock input 2.0- 3.2- 4.4-ns T PCOP-term clock output valid - 5.5-7.7-10.2ns T OEGTS to output valid - 4.0- 5.0-7.0ns T ODGTS to output disable - 4.0- 5.0-7.0ns T POEProduct term OE to output enabled -7.0-9.5-11.0ns T PODProduct term OE to output disabled -7.0-9.5-11.0ns T AOGSR to output valid -10.0-12.0-14.5ns T PAOP-term S/R to output valid -10.5-12.6-15.3ns T WLHGCK pulse width (High or Low) 2.8- 4.0- 4.5-ns T APRPWAsynchronous preset/reset pulse width (High or Low) 5.0- 6.5-7.0-ns T PLH P-term clock pulse width (High or Low) 5.0- 6.5-7.0-nsFigure 3: AC Load CircuitXC9572XL High Performance CPLDDS057 (v2.0) April 3, 2007Product SpecificationInternal Timing Parameters SymbolParameter XC9572XL-5XC9572XL-7XC9572XL-10Units Min Max Min Max Min Max Buffer DelaysT INInput buffer delay - 1.5- 2.3- 3.5ns T GCKGCK buffer delay - 1.1- 1.5- 1.8ns T GSRGSR buffer delay - 2.0- 3.1- 4.5ns T GTSGTS buffer delay - 4.0- 5.0-7.0ns T OUTOutput buffer delay - 2.0- 2.5- 3.0ns T ENOutput buffer enable/disable delay -0-0-0ns Product Term Control Delays T PTCKProduct term clock delay - 1.6- 2.4- 2.7ns T PTSRProduct term set/reset delay - 1.0- 1.4- 1.8ns T PTTSProduct term 3-state delay - 5.5-7.2-7.5ns Internal Register and Combinatorial Delays T PDICombinatorial logic propagation delay -0.5- 1.3- 1.7ns T SUIRegister setup time 2.3- 2.6- 3.0-ns T HIRegister hold time 1.4- 2.2- 3.5-ns T ECSURegister clock enable setup time 2.4- 2.6- 3.0-ns T ECHORegister clock enable hold time 1.4- 2.2- 3.5-ns T COIRegister clock to output valid time -0.4-0.5- 1.0ns T AOIRegister async. S/R to output delay - 6.0- 6.4-7.0ns T RAIRegister async. S/R recover before clock 5.07.510.0ns T LOGIInternal logic delay - 1.0- 1.4- 1.8ns T LOGILPInternal low power logic delay - 5.0- 6.4-7.3ns Feedback Delays T FFast CONNECT II feedback delay - 1.9- 3.5- 4.2ns Time Adders T PTAIncremental product term allocator delay -0.7-0.8- 1.0ns T SLEW Slew-rate limited delay - 3.0- 4.0- 4.5ns。

FPGA可编程逻辑器件芯片XCVU125-1FLVB1760I中文规格书

MGTAVCC_[L or R] [N, UC, C, LC, or S](5)

Dedicated

Input

Analog power-supply pin for the receiver and transmitter internal circuits.

UltraScale Device Packaging and Pinouts UG575 (v1.14) March 18, 2020

Table 1-5: Pin Definitions (Cont’d)

Pin Name

Type

MGTAVTT_[L or R] [N, UC, C, LC, or S](5)

Dedicated

MGTVCCAUX_[L or R] [N, UC, C, LC, or S](5)

Dedicated

MGTREFCLK[0 or 1] [P or N]

Dedicated

MGTAVTTRCAL_[L or R] [N, UC, C, LC, or S](5)

Dedicated

MGTRREF_[L or R] [N, UC, C, LC, or S](5)

Dedicated

Direction

Input Input Input N/A Input

Chapter 1: Packaging Overview

104

208

XQKU040

0

104

416

XQKU060

RFA1156

0

104

416

XQKU095

0

52

46834

XQKU115

RLF1924

0

104

FPGA可编程逻辑器件芯片XCVU095-2FFVC1517I中文规格书

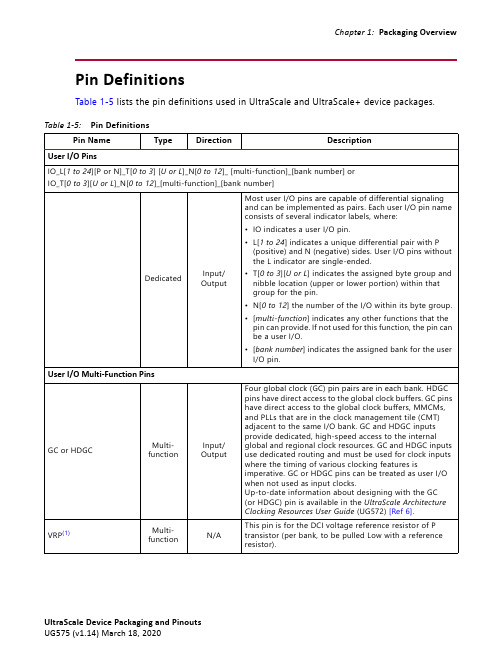

Pin DefinitionsTable1-5 lists the pin definitions used in UltraScale and UltraScale+ device packages.Table 1-5:Pin DefinitionsPin Name Type Direction DescriptionUser I/O PinsIO_L[1to24][P or N]_T[0to3] [U or L]_N[0to12]_ [multi-function]_[bank number] orIO_T[0to3][U or L]_N[0to12]_[multi-function]_[bank number]Dedicated Input/Output Most user I/O pins are capable of differential signaling and can be implemented as pairs. Each user I/O pin name consists of several indicator labels, where:•IO indicates a user I/O pin.•L[1to24] indicates a unique differential pair with P (positive) and N (negative) sides. User I/O pins without the L indicator are single-ended.•T[0 to 3][U or L] indicates the assigned byte group and nibble location (upper or lower portion) within that group for the pin.•N[0 to 12] the number of the I/O within its byte group.•[multi-function] indicates any other functions that the pin can provide. If not used for this function, the pin can be a user I/O.•[bank number] indicates the assigned bank for the user I/O pin.User I/O Multi-Function PinsGC or HDGC Multi-function Input/OutputFour global clock (GC) pin pairs are in each bank. HDGCpins have direct access to the global clock buffers. GC pinshave direct access to the global clock buffers, MMCMs,and PLLs that are in the clock management tile (CMT)adjacent to the same I/O bank. GC and HDGC inputsprovide dedicated, high-speed access to the internalglobal and regional clock resources. GC and HDGC inputsuse dedicated routing and must be used for clock inputswhere the timing of various clocking features isimperative. GC or HDGC pins can be treated as user I/Owhen not used as input clocks.Up-to-date information about designing with the GC(or HDGC) pin is available in the UltraScale ArchitectureClocking Resources User Guide (UG572) [Ref6].VRP(1)Multi-function N/A This pin is for the DCI voltage reference resistor of P transistor (per bank, to be pulled Low with a reference resistor).MGTAVTT_[L or R][N, UC, C, LC, or S](5)Dedicated Input Analog power-supply pin for the transmit driver.MGTVCCAUX_[L or R][N, UC, C, LC, or S](5)Dedicated Input Auxiliary analog Quad PLL (QPLL) voltage supply for the transceivers.MGTREFCLK[0 or 1][P or N]Dedicated Input Differential reference clock for the transceivers.MGTAVTTRCAL_[L or R][N, UC, C, LC, or S](5)Dedicated N/A Precision reference resistor pin for internal calibration termination.MGTRREF_[L or R][N, UC, C, LC, or S](5)DedicatedInputPrecision reference resistor pin for internal calibration termination.Table 1-5:Pin Definitions (Cont’d)Pin NameTypeDirectionDescriptionChapter 2:Package FilesTable 3-3:Cross-Reference to Kintex UltraScale+ and XQ Kintex UltraScale+ Device Diagrams by PackagePackage Footprint Compatible Devices Package StatusFFVA676XCKU3Ppage262XCKU5Ppage262ProductionFFVB676XCKU3Ppage264XCKU5Ppage264ProductionFFRB676XQKU5Ppage264ProductionSFVB784XCKU3Ppage266XCKU5Ppage266ProductionSFRB784XQKU5Ppage266ProductionFFVD900XCKU3Ppage268XCKU5Ppage268XCKU11Ppage270ProductionFFVE900XCKU9Ppage272XCKU13Ppage274ProductionFFVA1156XCKU11Ppage276XCKU15Ppage278ProductionFFRA1156XQKU15Ppage278ProductionFFVE1517XCKU11Ppage280XCKU15Ppage282ProductionFFRE1517XQKU15Ppage282ProductionFFVA1760XCKU15Ppage284ProductionFFVE1760XCKU15Ppage286Production。

FPGA可编程逻辑器件芯片XCKU115-2FLVF1924E中文规格书

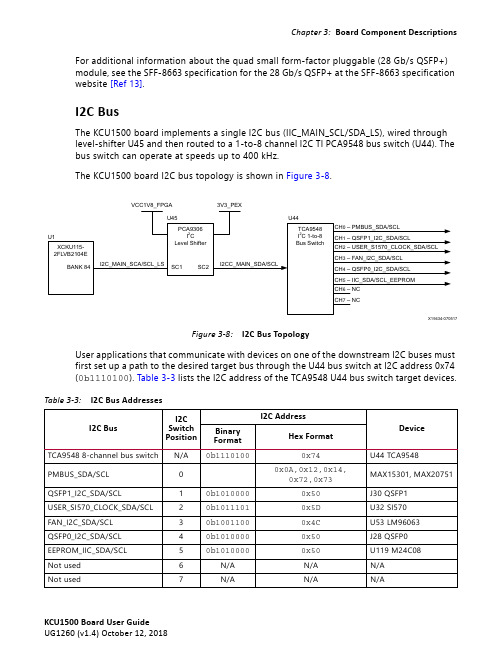

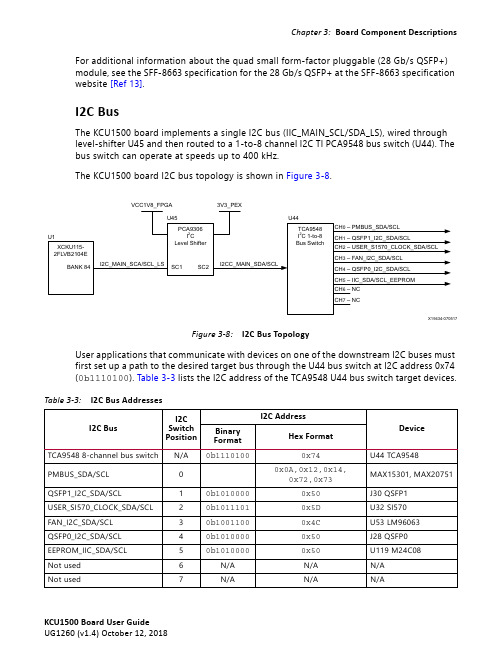

For additional information about the quad small form-factor pluggable (28 Gb/s QSFP+) module, see the SFF-8663 specification for the 28 Gb/s QSFP+ at the SFF-8663 specification website [Ref 13].I2C BusThe KCU1500 board implements a single I2C bus (IIC_MAIN_SCL/SDA_LS), wired through level-shifter U45 and then routed to a 1-to-8 channel I2C TI PCA9548 bus switch (U44). The bus switch can operate at speeds up to 400kHz.The KCU1500 board I2C bus topology is shown in Figure 3-8.User applications that communicate with devices on one of the downstream I2C buses must first set up a path to the desired target bus through the U44 bus switch at I2C address 0x74 (0b1110100). Table 3-3 lists the I2C address of the TCA9548 U44 bus switch target devices.Figure 3-8:I2C Bus TopologyTable 3-3:I2C Bus Addresses I2C BusI2C Switch PositionI2C AddressDeviceBinary FormatHex FormatTCA9548 8-channel bus switch N/A 0b11101000x74U44 TCA9548PMBUS_SDA/SCL 00x0A,0x12,0x14,0x72,0x73MAX15301, MAX20751QSFP1_I2C_SDA/SCL10b10100000x50J30 QSFP1USER_SI570_CLOCK_SDA/SCL 20b10111010x5D U32 SI570FAN_I2C_SDA/SCL 30b10011000x4C U53 LM96063QSFP0_I2C_SDA/SCL 40b10100000x50J28 QSFP0EEPROM_IIC_SDA/SCL 50b10100000x50U119 M24C08Not used 6N/A N/A N/A Not used7N/AN/AN/ARail NamePower System RegulatorsU18 CurrentSense SYSMONMultiplexer PortSchematicPageNumber Ref.Des.Device TypeVout(V)Max. I(A)Addr.Bin.Addr.PortVCCINT_FPGA U20MAX153010.95300x0A NA NA22 VCC1V8_FPGA U21MAX15301 1.80100x14001S223 VCC1V2_FPGA U25MAX15301 1.20100x12100S524 MGTAVCC_FPGA U28MAX207510.95300x72NA NA25 MGTAVTT_FPGA U37MAX20751 1.20300x73111S827Non-PMBus RegulatorsSYS_5V0U34MAX17502 5.001NA NA NA26 SYS_2V5U27MAX15027 2.501NA NA NA26 MGTVCCAUX U30MAX8869E 1.811NA NA NA26 DDR4_C0_VTT U117TPS512000.603NA NA NA26 DDR4_C1_VTT U32TPS512000.603NA NA NA26 DDR4_C2_VTT U118TPS512000.603NA NA NA26 DDR4_C3_VTT U35TPS512000.603NA NA NA26Step 2: Prepare Board Installation FilesThe SDx environment provides the xbinst utility, which generates firmware and driver files for the target board plugged into the deployment computer.1.Run the following commands to prepare files for the target board installation.See the SDx Command and Utility Reference Guide (UG1279) [Ref6] for more details on the xbinst utility. Depending on the target location, some commands must be run with root or sudo privilege. Otherwise, access permissions must be changed to enable read access for all users on that system.e the following commands to create the deployment area inside/opt/dsa/:$ mkdir /opt/dsa$ mkdir /opt/dsa/xilinx_vcu1525_dynamic_5_1$ cd /opt/dsa/xilinx_vcu1525_dynamic_5_1Note:To install and deploy the KCU1500 files, use xilinx_kcu1500_dynamic_5_0 in step 2 and 3.3.Execute xbinst to install the files needed for the deployment machine. Output similarto the following is displayed:$ xbinst --platform xilinx_vcu1525_dynamic_5_1 -d .****** xbinst v2018.2 (64-bit)**** SW Build 2254440 on Sun Jun 10 18:05:35 MDT 2018** Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.Attempting to get a license: ap_openclFeature available: ap_openclINFO: [XBINST 60-895] Target platform:/opt/Xilinx/SDx/2018.2/platforms/xilinx_vcu1525_dynamic_5_1/xilinx_vcu1525_dynamic_ 5_1.xpfmINFO: [XBINST 60-267] Packaging for PCIe...INFO: [XBINST 60-1032] Extracting DSA to./.Xil/xbinst-1273/xilinx_vcu1525_dynamic_5_1INFO: Adding section [FIRMWARE (3)] using: 'mgmt' (23192 Bytes)INFO: Adding section [SCHED_FIRMWARE (5)] using: 'sched' (9748 Bytes)Successfully completed 'xclbincat'INFO: [XBINST 60-268] Packaging for PLETEINFO: [XBINST 60-667] xbinst has successfully created a board installation directory at /opt/dsa/xilinx_vcu1525_dynamic_5_1.The files are installed in this location:/opt/dsa/xilinx_vcu1525_dynamic_5_1/xbinst:Make a note of the deployment location area because it is required at a later stage.This section refers to this location as the <xbinst-area> or as the deploymentdirectory.4.Install the drivers as described in Step 3: Install Board Drivers.Failure to Create a Compute ProgramTo check potential issues, use the clCreateProgramWithBinary()function. This function can identify issues that occur when programming the FPGA with the provided xclbin file. One scenario is that the program is not compatible with the currently programmed bitstream, which derived from the programmed firmware DSA on the configuration flash memory of the card.There are several ways to determine if the DSA matches, but they all need to check the timestamp programmed into the bitstream of the programmed DSA against the xclbin, by checking the output of dmesg:Also, to look directly into the DSA archive file for the same information: $ unzip $XILINX_SDX/platforms/<board_name>/hw/<board_name>.dsa dsa.xml -d unzip_dsa [...] inflating: unzip_dsa/dsa.xml$ grep -i time unzip_dsa/dsa.xml< ... FeatureRomTimestamp="#####">Useful Debug Operating System CommandsThis section includes some typical outputs for a VCU1525 board when running debug commands. Only the relevant output relating to accelerator boards is included. Some numbers can change depending on the deployment machine.。

FPGA可编程逻辑器件芯片XCKU115-2FLVF1924E中文规格书

For additional information about the quad small form-factor pluggable (28 Gb/s QSFP+) module, see the SFF-8663 specification for the 28 Gb/s QSFP+ at the SFF-8663 specification website [Ref 13].I2C BusThe KCU1500 board implements a single I2C bus (IIC_MAIN_SCL/SDA_LS), wired through level-shifter U45 and then routed to a 1-to-8 channel I2C TI PCA9548 bus switch (U44). The bus switch can operate at speeds up to 400kHz.The KCU1500 board I2C bus topology is shown in Figure 3-8.User applications that communicate with devices on one of the downstream I2C buses must first set up a path to the desired target bus through the U44 bus switch at I2C address 0x74 (0b1110100). Table 3-3 lists the I2C address of the TCA9548 U44 bus switch target devices.Figure 3-8:I2C Bus TopologyTable 3-3:I2C Bus Addresses I2C BusI2C Switch PositionI2C AddressDeviceBinary FormatHex FormatTCA9548 8-channel bus switch N/A 0b11101000x74U44 TCA9548PMBUS_SDA/SCL 00x0A,0x12,0x14,0x72,0x73MAX15301, MAX20751QSFP1_I2C_SDA/SCL10b10100000x50J30 QSFP1USER_SI570_CLOCK_SDA/SCL 20b10111010x5D U32 SI570FAN_I2C_SDA/SCL 30b10011000x4C U53 LM96063QSFP0_I2C_SDA/SCL 40b10100000x50J28 QSFP0EEPROM_IIC_SDA/SCL 50b10100000x50U119 M24C08Not used 6N/A N/A N/A Not used7N/AN/AN/ARail NamePower System RegulatorsU18 CurrentSense SYSMONMultiplexer PortSchematicPageNumber Ref.Des.Device TypeVout(V)Max. I(A)Addr.Bin.Addr.PortVCCINT_FPGA U20MAX153010.95300x0A NA NA22 VCC1V8_FPGA U21MAX15301 1.80100x14001S223 VCC1V2_FPGA U25MAX15301 1.20100x12100S524 MGTAVCC_FPGA U28MAX207510.95300x72NA NA25 MGTAVTT_FPGA U37MAX20751 1.20300x73111S827Non-PMBus RegulatorsSYS_5V0U34MAX17502 5.001NA NA NA26 SYS_2V5U27MAX15027 2.501NA NA NA26 MGTVCCAUX U30MAX8869E 1.811NA NA NA26 DDR4_C0_VTT U117TPS512000.603NA NA NA26 DDR4_C1_VTT U32TPS512000.603NA NA NA26 DDR4_C2_VTT U118TPS512000.603NA NA NA26 DDR4_C3_VTT U35TPS512000.603NA NA NA26Step 2: Prepare Board Installation FilesThe SDx environment provides the xbinst utility, which generates firmware and driver files for the target board plugged into the deployment computer.1.Run the following commands to prepare files for the target board installation.See the SDx Command and Utility Reference Guide (UG1279) [Ref6] for more details on the xbinst utility. Depending on the target location, some commands must be run with root or sudo privilege. Otherwise, access permissions must be changed to enable read access for all users on that system.e the following commands to create the deployment area inside/opt/dsa/:$ mkdir /opt/dsa$ mkdir /opt/dsa/xilinx_vcu1525_dynamic_5_1$ cd /opt/dsa/xilinx_vcu1525_dynamic_5_1Note:To install and deploy the KCU1500 files, use xilinx_kcu1500_dynamic_5_0 in step 2 and 3.3.Execute xbinst to install the files needed for the deployment machine. Output similarto the following is displayed:$ xbinst --platform xilinx_vcu1525_dynamic_5_1 -d .****** xbinst v2018.2 (64-bit)**** SW Build 2254440 on Sun Jun 10 18:05:35 MDT 2018** Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.Attempting to get a license: ap_openclFeature available: ap_openclINFO: [XBINST 60-895] Target platform:/opt/Xilinx/SDx/2018.2/platforms/xilinx_vcu1525_dynamic_5_1/xilinx_vcu1525_dynamic_ 5_1.xpfmINFO: [XBINST 60-267] Packaging for PCIe...INFO: [XBINST 60-1032] Extracting DSA to./.Xil/xbinst-1273/xilinx_vcu1525_dynamic_5_1INFO: Adding section [FIRMWARE (3)] using: 'mgmt' (23192 Bytes)INFO: Adding section [SCHED_FIRMWARE (5)] using: 'sched' (9748 Bytes)Successfully completed 'xclbincat'INFO: [XBINST 60-268] Packaging for PLETEINFO: [XBINST 60-667] xbinst has successfully created a board installation directory at /opt/dsa/xilinx_vcu1525_dynamic_5_1.The files are installed in this location:/opt/dsa/xilinx_vcu1525_dynamic_5_1/xbinst:Make a note of the deployment location area because it is required at a later stage.This section refers to this location as the <xbinst-area> or as the deploymentdirectory.4.Install the drivers as described in Step 3: Install Board Drivers.Failure to Create a Compute ProgramTo check potential issues, use the clCreateProgramWithBinary()function. This function can identify issues that occur when programming the FPGA with the provided xclbin file. One scenario is that the program is not compatible with the currently programmed bitstream, which derived from the programmed firmware DSA on the configuration flash memory of the card.There are several ways to determine if the DSA matches, but they all need to check the timestamp programmed into the bitstream of the programmed DSA against the xclbin, by checking the output of dmesg:Also, to look directly into the DSA archive file for the same information: $ unzip $XILINX_SDX/platforms/<board_name>/hw/<board_name>.dsa dsa.xml -d unzip_dsa [...] inflating: unzip_dsa/dsa.xml$ grep -i time unzip_dsa/dsa.xml< ... FeatureRomTimestamp="#####">Useful Debug Operating System CommandsThis section includes some typical outputs for a VCU1525 board when running debug commands. Only the relevant output relating to accelerator boards is included. Some numbers can change depending on the deployment machine.。

FPGA可编程逻辑器件芯片XCVU125FLVB1760中文规格书

7Series FPGAs Data Sheet: Overview maximum payload size of up to 1,024 bytes. The integrated block interfaces to the integrated high-speed transceivers for serial connectivity and to block RAMs for data buffering. Combined, these elements implement the Physical Layer, Data Link Layer, and Transaction Layer of the PCI Express protocol.Xilinx provides a light-weight, configurable, easy-to-use LogiCORE™ IP wrapper that ties the various building blocks (the integrated block for PCI Express, the transceivers, block RAM, and clocking resources) into an Endpoint or Root Port solution. The system designer has control over many configurable parameters: lane width, maximum payload size, FPGA logic interface speeds, reference clock frequency, and base address register decoding and filtering.Xilinx offers two wrappers for the integrated block: AXI4-Stream and AXI4 (memory mapped). Note that legacy TRN/Local Link is not available in 7series devices for the integrated block for PCI Express. AXI4-Stream is designed for existing customers of the integrated block and enables easy migration to AXI4-Stream from TRN. AXI4 (memory mapped) is designed for Xilinx Platform Studio/EDK design flow and MicroBlaze™ processor based designs.More information and documentation on solutions for PCI Express designs can be found.ConfigurationThere are many advanced configuration features, including:•High-speed SPI and BPI (parallel NOR) configuration•Built-in MultiBoot and safe-update capability•256-bit AES encryption with HMAC/SHA-256 authentication•Built-in SEU detection and correction•Partial reconfigurationXilinx 7series FPGAs store their customized configuration in SRAM-type internal latches. There are up to 450Mb configuration bits, depending on device size and user-design implementation options. The configuration storage is volatile and must be reloaded whenever the FPGA is powered up. This storage can also be reloaded at any time by pulling the PROGRAM_B pin Low. Several methods and data formats for loading configuration are available, determined by the three mode pins.The SPI interface (x1, x2, and x4 modes) and the BPI interface (parallel-NOR x8 and x16) are two common methods used for configuring the FPGA. Users can directly connect an SPI or BPI flash to the FPGA, and the FPGA's internal configuration logic reads the bitstream out of the flash and configures itself. The FPGA automatically detects the bus width on the fly, eliminating the need for any external controls or switches. Bus widths supported are x1, x2, and x4 for SPI, and x8 and x16 for BPI. The larger bus widths increase configuration speed and reduce the amount of time it takes for the FPGA to start up after power-on. Some configuration options such as BPI are not supported in all device-package combinations. Refer to UG470, 7 Series FPGAs Configuration User Guide for details.In master mode, the FPGA can drive the configuration clock from an internally generated clock, or for higher speed configuration, the FPGA can use an external configuration clock source. This allows high-speed configuration with the ease of use characteristic of master mode. Slave modes up to 32 bits wide are also supported by the FPGA that are especially useful for processor-driven configuration.The FPGA has the ability to reconfigure itself with a different image using SPI or BPI flash, eliminating the need for an external controller. The FPGA can reload its original design in case there are any errors in the data transmission, ensuring an operational FPGA at the end of the process. This is especially useful for updates to a design after the end product has been shipped. Customers can ship their products with an early version of the design, thus getting their products to market faster. This feature allows customers to keep their end users current with the most up-to-date designs while the product is already in the field.The dynamic reconfiguration port (DRP) gives the system designer easy access to the configuration and status registers of the MMCM, PLL, XADC, transceivers, and integrated block for PCI Express. The DRP behaves like a set of memory-mapped registers, accessing and modifying block-specific configuration bits as well as status and control registers.DS180 (v2.6.1) September 8, 2020Product Specification7Series FPGAs Data Sheet: OverviewEncryption, Readback, and Partial ReconfigurationIn all 7series FPGAs (except XC7S6 and XC7S15), the FPGA bitstream, which contains sensitive customer IP, can be protected with 256-bit AES encryption and HMAC/SHA-256 authentication to prevent unauthorized copying of the design. The FPGA performs decryption on the fly during configuration using an internally stored 256-bit key. This key can reside in battery-backed RAM or in nonvolatile eFUSE bits.Most configuration data can be read back without affecting the system's operation. Typically, configuration is anall-or-nothing operation, but Xilinx 7series FPGAs support partial reconfiguration. This is an extremely powerful and flexible feature that allows the user to change portions of the FPGA while other portions remain static. Users can time-slice these portions to fit more IP into smaller devices, saving cost and power. Where applicable in certain designs, partial reconfiguration can greatly improve the versatility of the FPGA.XADC (Analog-to-Digital Converter)Highlights of the XADC architecture include:•Dual 12-bit 1MSPS analog-to-digital converters (ADCs)•Up to 17 flexible and user-configurable analog inputs•On-chip or external reference option•On-chip temperature (±4°C max error) and power supply (±1% max error) sensors•Continuous JTAG access to ADC measurementsAll Xilinx 7series FPGAs (except XC7S6 and XC7S15) integrate a new flexible analog interface called XADC. When combined with the programmable logic capability of the 7series FPGAs, the XADC can address a broad range of data acquisition and monitoring requirements. For more information.The XADC contains two 12-bit 1 MSPS ADCs with separate track and hold amplifiers, an on-chip analog multiplexer (up to 17external analog input channels supported), and on-chip thermal and supply sensors. The two ADCs can be configured to simultaneously sample two external-input analog channels. The track and hold amplifiers support a range of analog input signal types, including unipolar, bipolar, and differential. The analog inputs can support signal bandwidths of at least500KHz at sample rates of 1MSPS. It is possible to support higher analog bandwidths using external analog multiplexer mode with the dedicated analog input (see UG480, 7 Series FPGAs and Zynq-7000 All Programmable SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter User Guide).The XADC optionally uses an on-chip reference circuit (±1%), thereby eliminating the need for any external active components for basic on-chip monitoring of temperature and power supply rails. To achieve the full 12-bit performance of the ADCs, an external 1.25V reference IC is recommended.If the XADC is not instantiated in a design, then by default it digitizes the output of all on-chip sensors. The most recent measurement results (together with maximum and minimum readings) are stored in dedicated registers for access at any time via the JTAG interface. User-defined alarm thresholds can automatically indicate over-temperature events and unacceptable power supply variation. A user-specified limit (for example, 100°C) can be used to initiate an automatic powerdown.DS180 (v2.6.1) September 8, 2020Product Specification。

FPGA可编程逻辑器件芯片XCZU6CG-2FFVB1156I中文规格书

Kintex UltraScale+ FPGAs Data Sheet: DC and AC Switching CharacteristicsLVDS DC Specifications (LVDS_25)The LVDS_25 standard is available in the HD I/O banks. See the UltraScale Architecture SelectIO Resources User Guide (UG571) for more information.Table 18: LVDS_25 DC SpecificationsSymbol DC Parameter Min Typ Max Units V CCO1Supply voltage 2.375 2.500 2.625VV IDIFF Differential input voltage:1003506002mV (Q – Q), Q = High(Q – Q), Q = HighV ICM Input common-mode voltage0.300 1.200 1.425V Notes:1.LVDS_25 in HD I/O banks supports inputs only. LVDS_25 inputs without internal termination have no V CCO requirements. Any V CCO can bechosen as long as the input voltage levels do not violate the Recommended Operating Condition (Table 2) specification for the V IN I/O pin voltage.2.Maximum V IDIFF value is specified for the maximum V ICM specification. With a lower V ICM, a higher V DIFF is tolerated only when therecommended operating conditions and overshoot/undershoot V IN specifications are maintained.LVDS DC Specifications (LVDS)The LVDS standard is available in the HP I/O banks. See the UltraScale Architecture SelectIO Resources User Guide (UG571) for more information.Table 19: LVDS DC SpecificationsSymbol DC Parameter Conditions Min Typ Max Units V CCO1Supply voltage 1.710 1.800 1.890VR T = 100Ω across Q and Q signals247350454mVV ODIFF2Differential output voltage:(Q – Q), Q = High(Q – Q), Q = HighV OCM2Output common-mode voltage R T = 100Ω across Q and Q signals 1.000 1.250 1.425V1003506003mVV IDIFF3Differential input voltage:(Q – Q), Q = High(Q – Q), Q = HighV ICM_DC4Input common-mode voltage (DC coupling)0.300 1.200 1.425VV ICM_AC5Input common-mode voltage (AC coupling)0.600– 1.100V Notes:1.In HP I/O banks, when LVDS is used with input-only functionality, it can be placed in a bank where the V CCO levels are different from thespecified level only if internal differential termination is not used. In this scenario, V CCO must be chosen to ensure the input pin voltage levels do not violate the Recommended Operating Condition (Table 2) specification for the V IN I/O pin voltage.2.V OCM and V ODIFF values are for LVDS_PRE_EMPHASIS = FALSE.3.Maximum V IDIFF value is specified for the maximum V ICM specification. With a lower V ICM, a higher V DIFF is tolerated only when therecommended operating conditions and overshoot/undershoot V IN specifications are maintained.4.Input common mode voltage for DC coupled configurations. EQUALIZATION = EQ_NONE (Default).5.External input common mode voltage specification for AC coupled configurations. EQUALIZATION = EQ_LEVEL0, EQ_LEVEL1, EQ_LEVEL2,EQ_LEVEL3, EQ_LEVEL4.DS922 (v1.17) February 16, 2021Product SpecificationKintex UltraScale+ FPGAs Data Sheet: DC and AC Switching CharacteristicsAC Switching CharacteristicsAll values represented in this data sheet are based on the speed specifications in the Vivado® Design Suite as outlined in the following table.Table 20: Speed Specification Version By Device2020.2.2Device1.28XCKU3P, XCKU5P, XCKU9P, XCKU11P, XCKU13P, and XCKU15PXQKU5P, XQKU15P1.32XCKU19PSwitching characteristics are specified on a per-speed-grade basis and can be designated as Advance, Preliminary, or Production. Each designation is defined as follows:•Advance Product Specification: These specifications are based on simulations only and are typically available soon after device design specifications are frozen. Although speed grades with this designation areconsidered relatively stable and conservative, some under-reporting might still occur.•Preliminary Product Specification: These specifications are based on complete ES (engineering sample) silicon characterization. Devices and speed grades with this designation are intended to give a betterindication of the expected performance of production silicon. The probability of under-reporting delays is greatly reduced as compared to Advance data.•Product Specification: These specifications are released once enough production silicon of a particular device family member has been characterized to provide full correlation between specifications and devices over numerous production lots. There is no under-reporting of delays, and customers receive formalnotification of any subsequent changes. Typically, the slowest speed grades transition to production before faster speed grades.Testing of AC Switching CharacteristicsInternal timing parameters are derived from measuring internal test patterns. All AC switching characteristics are representative of worst-case supply voltage and junction temperature conditions.For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer and back-annotate to the simulation net list. Unless otherwise noted, values apply to all Kintex UltraScale+ FPGAs.Speed Grade DesignationsSince individual family members are produced at different times, the migration from one category to another depends completely on the status of the fabrication process for each device. Table 21 correlates the current status of the Kintex UltraScale+ FPGAs on a per speed grade basis.DS922 (v1.17) February 16, 2021Product Specification。

FPGA可编程逻辑器件芯片XCVU125-2FLVC2104E中文规格书

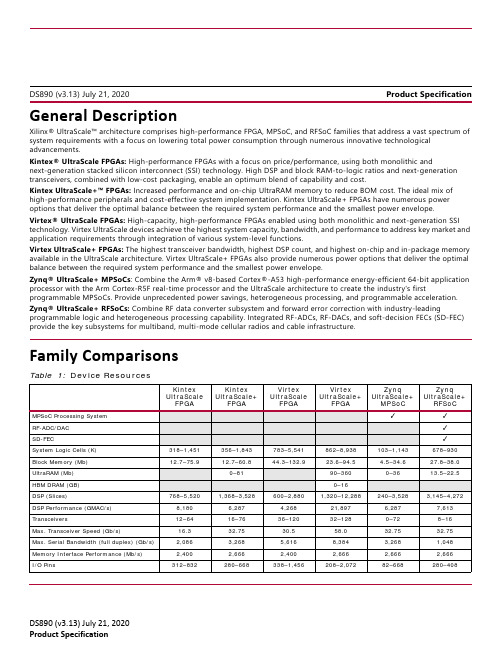

General DescriptionXilinx® UltraScale™ architecture comprises high-performance FPGA, MPSoC, and RFSoC families that address a vast spectrum of system requirements with a focus on lowering total power consumption through numerous innovative technological advancements.Kintex® UltraScale FPGAs: High-performance FPGAs with a focus on price/performance, using both monolithic andnext-generation stacked silicon interconnect (SSI) technology. High DSP and block RAM-to-logic ratios and next-generation transceivers, combined with low-cost packaging, enable an optimum blend of capability and cost.Kintex UltraScale+™ FPGAs: Increased performance and on-chip UltraRAM memory to reduce BOM cost. The ideal mix of high-performance peripherals and cost-effective system implementation. Kintex UltraScale+ FPGAs have numerous power options that deliver the optimal balance between the required system performance and the smallest power envelope.Virtex® UltraScale FPGAs: High-capacity, high-performance FPGAs enabled using both monolithic and next-generation SSI technology. Virtex UltraScale devices achieve the highest system capacity, bandwidth, and performance to address key market and application requirements through integration of various system-level functions.Virtex UltraScale+ FPGAs: The highest transceiver bandwidth, highest DSP count, and highest on-chip and in-package memory available in the UltraScale architecture. Virtex UltraScale+ FPGAs also provide numerous power options that deliver the optimal balance between the required system performance and the smallest power envelope.Zynq® UltraScale+ MPSoCs: Combine the Arm® v8-based Cortex®-A53 high-performance energy-efficient 64-bit application processor with the Arm Cortex-R5F real-time processor and the UltraScale architecture to create the industry's first programmable MPSoCs. Provide unprecedented power savings, heterogeneous processing, and programmable acceleration. Zynq® UltraScale+ RFSoCs: Combine RF data converter subsystem and forward error correction with industry-leading programmable logic and heterogeneous processing capability. Integrated RF-ADCs, RF-DACs, and soft-decision FECs (SD-FEC) provide the key subsystems for multiband, multi-mode cellular radios and cable infrastructure.Family ComparisonsDS890 (v3.13) July 21, 2020Product Specification Table 1:Device ResourcesKintex UltraScale FPGAKintexUltraScale+FPGAVirtexUltraScaleFPGAVirtexUltraScale+FPGAZynqUltraScale+MPSoCZynqUltraScale+RFSoCMPSoC Processing System✓✓RF-ADC/DAC✓SD-FEC✓System Logic Cells (K)318–1,451356–1,843783–5,541862–8,938103–1,143678–930 Block Memory (Mb)12.7–75.912.7–60.844.3–132.923.6–94.5 4.5–34.627.8–38.0 UltraRAM (Mb)0–8190–3600–3613.5–22.5 HBM DRAM (GB)0–16DSP (Slices)768–5,5201,368–3,528600–2,8801,320–12,288240–3,5283,145–4,272 DSP Performance (GMAC/s)8,1806,2874,26821,8976,2877,613 Transceivers12–6416–7636–12032–1280–728–16 Max. Transceiver Speed (Gb/s)16.332.7530.558.032.7532.75 Max. Serial Bandwidth (full duplex) (Gb/s)2,0863,2685,6168,3843,2681,048 Memory Interface Performance (Mb/s)2,4002,6662,4002,6662,6662,666I/O Pins312–832280–668338–1,456208–2,07282–668280–408Virtex UltraScale Device-Package Combinations and Maximum I/Os Table 8:Virtex UltraScale Device-Package Combinations and Maximum I/OsPackage(1)(2)(3)PackageDimensions(mm)VU065VU080VU095VU125VU160VU190VU440HR, HPGTH, GTYHR, HPGTH, GTYHR, HPGTH, GTYHR, HPGTH, GTYHR, HPGTH, GTYHR, HPGTH, GTYHR, HPGTH, GTYFFVC151740x4052, 46820,2052, 46820,2052, 46820,20FFVD151740x4052, 28632,3252, 286 32,32FLVD151740x4052, 28640, 32FFVB176042.5x42.552, 65032,1652, 650 32,16FLVB176042.5x42.552, 65036,16FFVA210447.5x47.552, 78028, 2452, 780 28,24FLVA210447.5x47.552, 78028,24FFVB210447.5x47.552, 65032,3252, 650 32,32FLVB210447.5x47.552, 65040,36FLGB210447.5x47.552, 65040,3652, 650 40, 36FFVC210447.5x47.552, 36432, 32FLVC210447.5x47.552, 36440,40FLGC210447.5x47.552, 36452,5252, 364 52, 52FLGB237750x5052, 124836, 0FLGA257752.5x52.50, 44860, 60FLGA289255x5552, 140448, 0 Notes:1.Go to Ordering Information for package designation details.2.All packages have 1.0mm ball pitch.3.Packages with the same last letter and number sequence, e.g., A2104, are footprint compatible with all other UltraScalearchitecture-based devices with the same sequence. The footprint compatible devices within this family are outlined. See the UltraScale Architecture Product Selection Guide for details on inter-family migration.RF Data Converter SubsystemZynq UltraScale+ RFSoCs contain an RF data converter subsystem consisting of multiple RF-ADCs and RF-DACs.RF-ADCsThe RF-ADCs can be configured individually for real input signals. RF-ADCs in all devices other than the XCZU43DR can also be configured as a pair for I/Q input signals. The RF-ADC tile has one PLL and a clocking instance. Decimation filters in the RF-ADCs can operate in varying decimation modes at 80% of Nyquist bandwidth with 89dB stop-band attenuation. Each RF-ADC contains a 48-bit numerically controlled oscillator (NCO) and a dedicated high-speed, high-performance, differential input buffer with on-chip calibrated 100 termination.RF-DACsThe RF-DACs can be configured individually for real outputs. RF-DACs in all devices other than the XCZU43DR can also be configured as a pair for I/Q output signal generation. The RF-DAC tile has one PLL and a clocking instance. Interpolation filters in the RF-DACs can operate in varying interpolation modes at 80% of Nyquist bandwidth with 89dB stop-band attenuation. Each RF-DAC contains a 48-bit NCO.。

FPGA可编程逻辑器件芯片XCZU7CG-1FFVC1156I中文规格书

PLL Switching Characteristics Table 39: PLL SpecificationSymbol Description1Speed Grade and V CCINT Operating VoltagesUnits 0.90V0.85V0.72V-3-2-1-2-1PLL_F INMAX Maximum input clock frequency1066933800933800MHzPLL_F INMIN Minimum input clock frequency7070707070MHz PLL_F INJITTER Maximum input clock period jitter< 20% of clock input period or 1 ns MaxPLL_F INDUTY Input duty cycle range: 70–399 MHz35–65% Input duty cycle range: 400–499 MHz40–60%Input duty cycle range: >500 MHz45–55% PLL_F VCOMIN Minimum PLL VCO frequency750750750750750MHz PLL_F VCOMAX Maximum PLL VCO frequency15001500150015001500MHz PLL_T STATPHAOFFSET Static phase offset of the PLL outputs20.120.120.120.120.12ns PLL_T OUTJITTER PLL output jitter.Note 3PLL_T OUTDUTY PLL CLKOUT0, CLKOUT0B, CLKOUT1, CLKOUT1Bduty-cycle precision40.1650.200.200.200.20ns PLL_T LOCKMAX PLL maximum lock time100µsPLL_F OUTMAX PLL maximum output frequency at CLKOUT0,CLKOUT0B, CLKOUT1, CLKOUT1B891775667725667MHz PLL maximum output frequency at CLKOUTPHY26672667240024002133MHzPLL_F OUTMIN PLL minimum output frequency at CLKOUT0,CLKOUT0B, CLKOUT1, CLKOUT1B55.86 5.86 5.86 5.86 5.86MHzPLL minimum output frequency at CLKOUTPHY 2 x VCO mode: 1500, 1 x VCO mode: 750, 0.5 x VCO mode:375MHz PLL_RST MINPULSE Minimum reset pulse width 5.00 5.00 5.00 5.00 5.00nsPLL_F PFDMAX Maximum frequency at the phase frequencydetector667.5667.5667.5667.5667.5MHzPLL_F PFDMIN Minimum frequency at the phase frequencydetector7070707070MHz PLL_F BANDWIDTH PLL bandwidth at typical1414141414MHz PLL_F DPRCLK_MAX Maximum DRP clock frequency250250250250250MHz Notes:1.The PLL does not filter typical spread-spectrum input clocks because they are usually far below the loop filter frequencies.2.The static offset is measured between any PLL outputs with identical phase.3.Values for this parameter are available in the Clocking Wizard.4.Includes global clock buffer.5.Calculated as F VCO/128 assuming output duty cycle is 50%.Device Pin-to-Pin Output Parameter GuidelinesThe pin-to-pin numbers in the following tables are based on the clock root placement in the center of the device. The actual pin-to-pin values will vary if the root placement selected is different. Consult the Vivado Design Suite timing report for the actual pin-to-pin values.。

FPGA可编程逻辑器件芯片XCVUJ125-2FLVB1760E中文规格书

DS060 (v2.0) March 1, 2013Product SpecificationOn-Chip OscillatorSpartan/XL devices include an internal oscillator. This oscil-lator is used to clock the power-on time-out, for configura-tion memory clearing, and as the source of CCLK in Master configuration mode. The oscillator runs at a nominal 8MHz frequency that varies with process, V CC , and temperature.The output frequency falls between 4MHz and 10MHz. The oscillator output is optionally available after configura-tion. Any two of four resynchronized taps of a built-in divider are also available. These taps are at the fourth, ninth, four-teenth and nineteenth bits of the divider. Therefore, if the primary oscillator output is running at the nominal 8MHz,the user has access to an 8-MHz clock, plus any two of 500kHz, 16kHz, 490Hz and 15Hz. These frequencies can vary by as much as -50% or +25%.These signals can be accessed by placing the OSC4 library element in a schematic or in HD L code. The oscillator is automatically disabled after configuration if the OSC4 sym-bol is not used in the design.Global Signals: GSR and GTS Global Set/Reset A separate Global Set/Reset line, as shown in Figure 3,page 5 for the CLB and Figure 5, page 6 for the IOB, sets or clears each flip-flop during power-up, reconfiguration, or when a dedicated Reset net is driven active. This global net (GSR) does not compete with other routing resources; it uses a dedicated distribution network. Each flip-flop is configured as either globally set or reset in the same way that the local set/reset (SR) is specified.Therefore, if a flip-flop is set by SR, it is also set by GSR.Similarly, if in reset mode, it is reset by both SR and GSR.GSR can be driven from any user-programmable pin as a global reset input. To use this global net, place an input pad and input buffer in the schematic or HDL code, driving the GSR pin of the STARTUP symbol. (See Figure 19.) A spe-cific pin location can be assigned to this input using a LOC attribute or property, just as with any other user-program-mable pad. An inverter can optionally be inserted after the input buffer to invert the sense of the GSR signal. Alterna-tively, GSR can be driven from any internal node.Global 3-State A separate Global 3-state line (GTS) as shown in Figure 6,page 7 forces all FPGA outputs to the high-impedance state, unless boundary scan is enabled and is executing an EXTEST instruction. GTS does not compete with other rout-ing resources; it uses a dedicated distribution network.GTS can be driven from any user-programmable pin as a global 3-state input. To use this global net, place an input pad and input buffer in the schematic or HDL code, driving the GTS pin of the STARTUP symbol. This is similar to whatis shown in Figure 19 for GSR except the IBUF would beconnected to GTS. A specific pin location can be assigned to this input using a LOC attribute or property, just as with any other user-programmable pad. An inverter can option-ally be inserted after the input buffer to invert the sense of the Global 3-state signal. Alternatively, GTS can be driven from any internal node.Boundary Scan The "bed of nails" has been the traditional method of testingelectronic assemblies. This approach has become less appropriate, due to closer pin spacing and more sophisti-cated assembly methods like surface-mount technology and multi-layer boards. The IEEE Boundary Scan Standard 1149.1 was developed to facilitate board-level testing of electronic assemblies. D esign and test engineers can embed a standard test logic structure in their device to achieve high fault coverage for I/O and internal logic. This structure is easily implemented with a four-pin interface on any boundary scan compatible device. IEEE 1149.1-com-patible devices may be serial daisy-chained together, con-nected in parallel, or a combination of the two.The Spartan and Spartan-XL families implement IEEE 1149.1-compatible BYP ASS, PRELOAD /SAMPLE and EXTEST boundary scan instructions. When the boundary scan configuration option is selected, three normal user I/O pins become dedicated inputs for these functions. Another user output pin becomes the dedicated boundary scan out-put. The details of how to enable this circuitry are covered later in this section.By exercising these input signals, the user can serially load commands and data into these devices to control the driving of their outputs and to examine their inputs. This method is an improvement over bed-of-nails testing. It avoids the need to over-drive device outputs, and it reduces the user inter-face to four pins. An optional fifth pin, a reset for the control logic, is described in the standard but is not implemented in the Spartan/XL devices.The dedicated on-chip logic implementing the IEEE 1149.1functions includes a 16-state machine, an instruction regis-ter and a number of data registers. The functional details can be found in the IEEE 1149.1 specification and are also discussed in the Xilinx application note: "Boundary Scan in FPGA Devices ." Figure 19: Symbols for Global Set/ResetFigure 16: Fast Carry Logic in Spartan/XL CLBDS060 (v2.0) March 1, 2013Product Specification。

FPGA可编程逻辑器件芯片EP2AGX125DF25C5N中文规格书

I NTRODUCTIONO N C HIP P ERIPHERALSRemovable Storage Interface (RSI)The removable storage interface (RSI) controller acts as the host interface for multimedia cards (MMC), secure digital memory cards (SD) and secure digital input/output cards (SDIO). The following listdescribes the main features of the RSI controller.•Support for a single MMC, SD memory or SDIO card•Support for 1-bit and 4-bit SD modes•Support for 1-bit, 4-bit, and 8-bit MMC modes•Support for eMMC 4.3 embedded NAND flash devices• A ten-signal external interface with clock, command, and up to eight data lines•Card interface clock generation from SCLK•SDIO interrupt and read wait featuresSerial Peripheral Interface (SPI)The processors have two serial peripheral interface (SPI) compatible ports that allow the processor to communicate with multiple SPI compatible devices.In its simplest mode, the SPI interface uses three pins for transferring data: two data pins (Master Output-Slave Input, MOSI, and Master Input-Slave Output, MISO) and a clock pin (serial clock, SCK). An SPI chip select input pin (SPISS) lets other SPI devices select the processor, and seven SPI chip select output pins (SPISEL7-1) let the processor select other SPI devices. The SPI select pins are reconfigured general-purpose I/O pins. Using these pins, the SPI port provides a full-duplex, synchronous serial interface, which supports both master/slave modes and multi master environments.The SPI port's baud rate and clock phase/polarities are programmable, and it has integrated DMA chan-nels for both transmit and receive data streams.Serial Port (SPORT)The processor includes three synchronous serial ports (SPORTs) that provide an inexpensive interface toa wide variety of digital and mixed-signal peripheral devices such as the AD183x family of audio CODECs,ADCs, and DACs from Analog Devices. The SPORTs consist of two data lines, a clock, and frame sync.The data lines can be programmed to either transmit or receive and each data line has a dedicated DMA channel.SPORT data can be automatically transferred to and from on-chip memory/external memory over dedi-cated DMA channels. Each of the SPORTs can work in conjunction with another SPORT to provide TDM support. In this configuration, one SPORT provides two transmit signals while the other SPORT provides the two receive signals. The frame sync and clock are shared.S YSTEM C ROSSBARS (SCB)SCB F UNCTIONAL D ESCRIPTIONSCB0 Slots and MastersTable 2-5:SCB0 Arbitration Default Settings for MI0 (DDR)Slot Master 0SI0 (C0)1SI2 (C1)2SI4 (SCB9)3SI5 (SCB5)4SI6 (SCB6)5SI7 (SCB8)6SI8 (SCB7)7SI9 (SCB1)8SI10 (SCB2)9SI11 (SCB3)10SI13 (USB)11SI12 (SCB4)12SI0 (C0)13SI2 (C1)14SI4 (SCB9)15SI5 (SCB5)16SI6 (SCB6)17SI7 (SCB8)18SI8 (SCB7)19SI9 (SCB1)20SI10 (SCB2)21SI11 (SCB3)22SI13 (USB)23SI12 (SCB4)24SI0 (C0)25SI2 (C1)26SI4 (SCB9)27SI5 (SCB5)28SI6 (SCB6)S YSTEM C ROSSBARS (SCB)SCB F UNCTIONAL D ESCRIPTIONTable 2-1:ADSP-BF60x SCB Register ListName DescriptionSCB_ARBRn Arbitration Read Channel Master Interface n RegisterSCB_ARBWn Arbitration Write Channel Master Interface n RegisterSCB_SLAVES Slave Interfaces Number RegisterSCB_MASTERS Master Interfaces Number RegisterSCB DefinitionsTo make the best use of the SCB, it is useful to understand the following terms.MI (Master Interface)SCB master interface connected to system bus interconnect slave (for example, L2, sMMR, SCB, and others).SI (Slave Interface)SCB slave interface connected to system bus interconnect master (for example, Core, DDE, SCB, and others).SCB Block DiagramThe SCB architectural model is illustrated in the following figure. This figure shows a high-level overview of the SCB and associated connections to system masters and slaves. A variable number of masters may be connected to a variable number of slaves in each SCB. In this example, all SIs are connected to all MIs as indicated by the lines connecting them.Figure 2-1:SCB Overview。

FPGA可编程逻辑器件芯片XCVU125-1FLVC2104I中文规格书

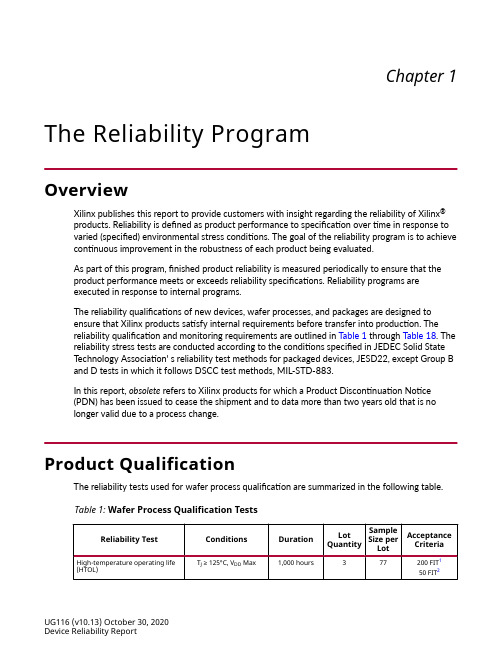

Chapter 1 The Reliability ProgramOverviewXilinx publishes this report to provide customers with insight regarding the reliability of Xilinx®products. Reliability is defined as product performance to specification over time in response to varied (specified) environmental stress conditions. The goal of the reliability program is to achieve continuous improvement in the robustness of each product being evaluated.As part of this program, finished product reliability is measured periodically to ensure that theproduct performance meets or exceeds reliability specifications. Reliability programs areexecuted in response to internal programs.The reliability qualifications of new devices, wafer processes, and packages are designed toensure that Xilinx products satisfy internal requirements before transfer into production. Thereliability qualification and monitoring requirements are outlined in Table 1 through Table 18. The reliability stress tests are conducted according to the conditions specified in JEDEC Solid StateT echnology Association' s reliability test methods for packaged devices, JESD22, except Group B and D tests in which it follows DSCC test methods, MIL-STD-883.In this report, obsolete refers to Xilinx products for which a Product Discontinuation Notice(PDN) has been issued to cease the shipment and to data more than two years old that is nolonger valid due to a process change.Product QualificationThe reliability tests used for wafer process qualification are summarized in the following table.Table 1: Wafer Process Qualification TestsReliability Test Conditions Duration LotQuantity SampleSize perLotAcceptanceCriteriaHigh-temperature operating life (HTOL)T J ≥ 125°C, V DD Max1,000 hours377200 FIT150 FIT2Table 1: Wafer Process Qualification Tests (cont'd)Reliability Test Conditions Duration LotQuantity SampleSize perLotAcceptanceCriteriaTHB3 or High-accelerated stress test (HAST)385°C, 85% RH, VDD1,000 hours3250 failures 130°C, 85% RH, VDD96 hours110°C, 85% RH, VDD264 hoursTemperature humidity (TH)3 or Unbiased high accelerated stress test (UHAST)385°C, 85% RH1,000 hours3250 failures 130°C, 85% RH96 hours110°C, 85% RH264 hoursTemperature cycling (TC)3, 4, 5, 6,–65°C to +150°C500 cycles3250 failures–55°C to+125°C1,000 cycles–40°C to +125°C1,000 cyclesData Retention Bake7 or HighTemperature Storage (HTS)T A = 150°C1,000 hours3250 failures Program Erase8TA = 25°C10,000 cycles1320 failuresNotes:1.FIT is failure in time. Phase I production is released as the qualification data demonstrates, meeting the required 200FIT failure rate and other test requirements.2.Phase II production is released as the qualification data demonstrates, meeting the required 50 FIT failure rate andother test requirements.3.Package preconditioning is performed prior to THB, HAST, temperature cycling, TH, and UHAST tests.4.For plastic QFP packages: –65°C to +150°C and 500 cycles or –55°C to +125°C and 1,000 cycles.5.For plastic BGA packages: –55°C to +125°C and 1,000 cycles.6.For flip chip packages: –55°C to +125°C and 1,000 cycles or –40°C to +125°C and 1,000 cycles.7.For CPLD and EPROM products.8.This is not a mandatory test and only for CPLD and EPROM products.Non-Hermetic and Hermetic PackagesMoisture sensitivity and reflow temperature information can be found in Device Package UserGuide (UG112).The non-hermetic package/assembly qualification is outlined in the following table. However, for hermetic package qualification, a full group B and D test per MIL-STD-833, Test Methods, isrequired.Reliability Test Conditions Duration LotQuantity SampleSize perLotAcceptanceCriteriaTHB1 or HAST185°C, 85% RH, V DD1,000 hours3250 failures130°C, 85% RH, V DD96 hours110°C, 85% RH, V DD264 hoursTemperature cycling1, 2, 3, 4–65°C to +150°C500 cycles3250 failures–55°C to +125°C1,000 cycles–40°C to +125°C1,000 cyclesAutoclave1 or temperature humidity unbiased1 or UHAST1121°C, 100% RH96 hours3250 failures 85°C, 85% RH1,000 hours130°C, 85% RH or 110°C,85% RH96 hours or264 hoursHigh-Temperature Storage (HTS)TA=150°C1,000 hours3250 failuresDataTable 23: HTOL Test Results for 220/180 nm Si Gate CMOS Device Type XC2SxxxDeviceLot Quantity Fail QuantityDevice QuantityActual Device Hours at T J ≥ 125°C EquivalentDevice Hoursat T J = 125°CFailure Rateat 60% CLand TJ = 55°C(FIT)XC2S10070315585,855660,32311XC2S1503081162,162172,345XC2S400E 104590,675113,651XC2S50104386,38793,972XC2Sxxx12484925,0791,040,291Table 24: HTOL Test Results for 130 nm Si Gate CMOS Device Type XC2VPxxxDeviceLot Quantity Fail QuantityDevice QuantityActual Device Hours at T J ≥ 125°C EquivalentDevice Hoursat T J = 125°CFailure Rateat 60% CLand TJ = 55°C(FIT)XC2VP4060269538,0451,340,0149XC2VPxxx6269538,0451,340,014DeviceLot Quantity Fail QuantityDevice QuantityActualDevice Hours at TJ ≥ 125°C Equivalent Device Hoursat T J = 125°CFailure Rateat 60% CLand TJ = 55°C(FIT)XC4VFX202090182,565267,185XC4VLX10014590,585270,878。

FPGA可编程逻辑器件芯片XCVU125FLVA2104中文规格书

Chapter 3: Product Specification When multiple channels are enabled, transactions on the AXI4 Master interface are interleaved between all selected channels. Simple round robin protocol is used to service all channels.Transactions granularity depends on host Max Payload Size (MPS), page size, and other hostsettings.C2H ChannelThe C2H channel handles DMA transfers from the card to the host. The instantiated number of C2H channels is controlled in the Vivado® IDE. Similarly the number of outstanding transfers is configured through the WNUM_RIDS, which is the number of C2H channel request IDs. In anAXI4-Stream configuration, the details of the DMA transfer are set up in advance of receivingdata on the AXI4-Stream interface. This is normally accomplished through receiving a DMAdescriptor. After the request ID has been prepared and the channel is enabled, the AXI4-Stream interface of the channel can receive data and perform the DMA to the host. In an AXI4 MMinterface configuration, the request IDs are allocated as the read requests to the AXI4 MMinterface are issued. Similar to the H2C channel, a given request ID is outstanding until the write request has been completed. In the case of the C2H channel, write request completion is when the write request has been issued as indicated by the PCIe IP.When multiple channels are enabled, transactions on the AXI4 Master interface are interleaved between all selected channels. Simple round robin protocol is used to service all channels.Transactions granularity depends on host MaxPayload Size (MPS), page size, and other hostsettings.AXI4-Lite MasterThis module implements the AXI4-Lite master bus protocol. The host can use this interface togenerate 32-bit read and 32-bit write requests to the user logic. The read or write request isreceived over the PCIe to AXI4-Lite Master BAR. Read completion data is returned back to the host through the target bridge over the PCIe IP CC bus.AXI4-Lite SlaveThis module implements the AXI4-Lite Slave bus protocol. The user logic can master 32-bit reads or writes on this interface to DMA internal registers only. You cannot access the PCIe integrated block register through this interface. This interface does not generate requests to the host.Host-to-Card Bypass MasterHost requests that reach the PCIe to DMA bypass BAR are sent to this module. The bypassmaster port is an AXI4 MM interface and supports read and write accesses.PG195 (v4.1) April 29, 2021DMA/Bridge Subsystem for PCIe v4.1Chapter 2: Overview Figure 1: DMA/Bridge Subsystem for PCI Express® OverviewX14718-042121 This diagram refers to the Requester Request (RQ)/Requester Completion (RC) interfaces, andthe Completer Request (CQ)/Completer Completion (CC) interfaces. For more information aboutthese, see the UltraScale+ Devices Integrated Block for PCI Express LogiCORE IP Product Guide(PG213).PG195 (v4.1) April 29, 2021DMA/Bridge Subsystem for PCIe v4.1。

FPGA可编程逻辑器件芯片XCVU125-H1FLVB1760E中文规格书

Summary of FeaturesRF Data Converter Subsystem OverviewMost Zynq UltraScale+ RFSoCs include an RF data converter subsystem, which contains multiple radio frequency analog to digital converters (RF-ADCs) and multiple radio frequency digital to analog converters (RF-DACs). The high-precision, high-speed, power efficient RF-ADCs and RF-DACs can be individually configured for real data or in most cases can be configured in pairs for real and imaginary I/Q data. See RF-ADCs and RF-DACs sections.Soft Decision Forward Error Correction (SD-FEC) OverviewSome Zynq UltraScale+ RFSoCs include highly flexible soft-decision FEC blocks for decoding and encoding data as a means to control errors in data transmission over unreliable or noisy communication channels. The SD-FEC blocks support low-density parity check (LDPC) decode/encode and Turbo decode for use in 5G wireless, backhaul, DOCSIS, and LTE applications.Processing System OverviewZynq UltraScale+ MPSoCs and RFSoCs feature dual and quad core variants of the Arm Cortex-A53 (APU) with dual-core Arm Cortex-R5F (RPU) processing system (PS). Some devices also include a dedicated Arm Mali™-400 MP2 graphics processing unit (GPU). See Table 2.To support the processors' functionality, a number of peripherals with dedicated functions are included in the PS. For interfacing to external memories for data or configuration storage, the PS includes amulti-protocol dynamic memory controller, a DMA controller, a NAND controller, an SD/eMMC controller and a Quad SPI controller. In addition to interfacing to external memories, the APU also includes a Level-1 (L1) and Level-2 (L2) cache hierarchy; the RPU includes an L1 cache and Tightly Coupled memory subsystem. Each has access to a 256KB on-chip memory.For high-speed interfacing, the PS includes 4 channels of transmit (TX) and receive (RX) pairs oftransceivers, called PS-GTR transceivers, supporting data rates of up to 6.0Gb/s. These transceivers can interface to the high-speed peripheral blocks that support PCIe at 5.0GT/s (Gen 2) as a root complex or Endpoint in x1, x2, or x4 configurations; Serial-ATA (SATA) at 1.5Gb/s, 3.0Gb/s, or 6.0Gb/s data rates; and up to two lanes of Display Port at 1.62Gb/s, 2.7Gb/s, or 5.4Gb/s data rates. The PS-GTR transceivers can also interface to components over USB 3.0 and Serial Gigabit Media Independent Interface (SGMII).Table 2:Zynq UltraScale+ MPSoC and RFSoC Device FeaturesMPSoCRFSoC CG DevicesEG DevicesEV DevicesDR DevicesAPU Dual-core Arm Cortex-A53Quad-core Arm Cortex-A53Quad-core Arm Cortex-A53Quad-core Arm Cortex-A53RPU Dual-core Arm Cortex-R5FDual-core Arm Cortex-R5FDual-core Arm Cortex-R5FDual-core Arm Cortex-R5FGPU –Mali-400MP2Mali-400MP2–VCU––H.264/H.265–External MemoryThe PS can interface to many types of external memories through dedicated memory controllers. The dynamic memory controller supports DDR3, DDR3L, DDR4, LPDDR3, and LPDDR4 memories. Themulti-protocol DDR memory controller can be configured to access a 2GB address space in 32-bit addressing mode and up to 32GB in 64-bit addressing mode using a single or dual rank configuration of 8-bit, 16-bit, or 32-bit DRAM memories. Both 32-bit and 64-bit bus access modes are protected by ECC using extra bits.The SD/eMMC controller supports 1 and 4 bit data interfaces at low, default, high-speed, andultra-high-speed (UHS) clock rates. This controller also supports 1-, 4-, or 8-bit-wide eMMC interfaces that are compliant to the eMMC 4.51 specification. eMMC is one of the primary boot and configuration modes for Zynq UltraScale+ MPSoCs and RFSoCs and supports boot from managed NAND devices. The controller has a built-in DMA for enhanced performance.The Quad-SPI controller is one of the primary boot and configuration devices. It supports 4-byte and3-byte addressing modes. In both addressing modes, single, dual-stacked, and dual-parallel configurations are supported. Single mode supports a quad serial NOR flash memory, while in double stacked and double parallel modes, it supports two quad serial NOR flash memories.The NAND controller is based on ONFI3.1 specification. It has an 8-pin interface and provides 200Mb/s of bandwidth in synchronous mode. It supports 24 bits of ECC thus enabling support for SLC NAND memories. It has two chip-selects to support deeper memory and a built-in DMA for enhanced performance.General ConnectivityThere are many peripherals in the PS for connecting to external devices over industry standard protocols, including CAN2.0B, USB, Ethernet, I2C, and UART. Many of the peripherals support clock gating and power gating modes to reduce dynamic and static power consumption.USB 3.0/2.0The pair of USB controllers can be configured as host, device, or On-The-Go (OTG). The core is compliant to USB 3.0 specification and supports super, high, full, and low speed modes in all configurations. In host mode, the USB controller is compliant with the Intel XHCI specification. In device mode, it supports up to 12 end points. While operating in USB3.0 mode, the controller uses the serial transceiver and operates up to 5.0Gb/s. In USB2.0 mode, the Universal Low Peripheral Interface (ULPI) is used to connect the controller to an external PHY operating up to 480Mb/s. The ULPI is also connected in USB3.0 mode to support high-speed operations.Ethernet MACThe four tri-speed ethernet MACs support 10Mb/s, 100Mb/s, and 1Gb/s operations. The MACs support jumbo frames and time stamping through the interfaces based on IEEE Std 1588v2. The ethernet MACs can be connected through the serial transceivers (SGMII), the MIO (RGMII), or through EMIO (GMII). The GMII interface can be converted to a different interface within the PL.Input/OutputAll UltraScale devices, whether FPGA, MPSoC, or RFSoCs, have I/O pins for communicating to external components. In addition, in the PS, there are another 78 I/Os that the I/O peripherals use to communicate to external components, referred to as multiplexed I/O (MIO). If more than 78 pins are required by the I/O peripherals, the I/O pins in the PL can be used to extend the MPSoC or RFSoC interfacing capability, referred to as extended MIO (EMIO).The number of I/O pins in UltraScale FPGAs and in the programmable logic of Zynq UltraScale+ MPSoCs and RFSoCs varies depending on device and package. Each I/O is configurable and can comply with a large number of I/O standards. The I/Os are classed as high-range (HR), high-performance (HP), or high-density (HD). The HR I/Os offer the widest range of voltage support, from 1.2V to 3.3V. The HP I/Os are optimized for highest performance operation, from 1.0V to 1.8V. The HD I/Os are reduced-feature I/Os organized in banks of 24, providing voltage support from 1.2V to 3.3V.The static memory interface controller (NAND, eMMC, or Quad-SPI) is configured using default settings. To improve device configuration speed, these settings can be modified by information provided in the boot image header. The ROM boot image is not user readable or executable after boot.Configuring FPGAsThe SPI (serial NOR) interface (x1, x2, x4, and dual x4 modes) and the BPI (parallel NOR) interface (x8 and x16 modes) are two common methods used for configuring the FPGA. Users can directly connect an SPI or BPI flash to the FPGA, and the FPGA's internal configuration logic reads the bitstream out of the flash and configures itself, eliminating the need for an external controller. The FPGA automatically detects the bus width on the fly, eliminating the need for any external controls or switches. Bus widths supported are x1, x2, x4, and dual x4 for SPI, and x8 and x16 for BPI. The larger bus widths increase configuration speed and reduce the amount of time it takes for the FPGA to start up after power-on.In master mode, the FPGA can drive the configuration clock from an internally generated clock, or for higher speed configuration, the FPGA can use an external configuration clock source. This allowshigh-speed configuration with the ease of use characteristic of master mode. Slave modes up to 32bits wide that are especially useful for processor-driven configuration are also supported by the FPGA. In addition, the new media configuration access port (MCAP) provides a direct connection between the integrated block for PCIe and the configuration logic to simplify configuration over PCIe.SEU detection and mitigation (SEM) IP, RSA authentication, post-configuration CRC, and Security Monitor (SecMon) IP are not supported in the KU025 FPGA.。

FPGA可编程逻辑器件芯片XCVU095-2FFVB1760I中文规格书

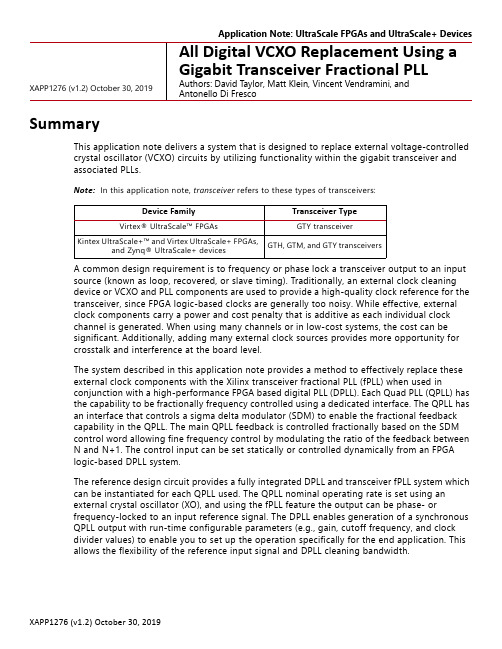

SummaryThis application note delivers a system that is designed to replace external voltage-controlled crystal oscillator (VCXO) circuits by utilizing functionality within the gigabit transceiver and associated PLLs.Note:In this application note, transceiver refers to these types of transceivers:A common design requirement is to frequency or phase lock a transceiver output to an input source (known as loop, recovered, or slave timing). Traditionally, an external clock cleaning device or VCXO and PLL components are used to provide a high-quality clock reference for the transceiver, since FPGA logic-based clocks are generally too noisy. While effective, external clock components carry a power and cost penalty that is additive as each individual clock channel is generated. When using many channels or in low-cost systems, the cost can be significant. Additionally, adding many external clock sources provides more opportunity for crosstalk and interference at the board level.The system described in this application note provides a method to effectively replace these external clock components with the Xilinx transceiver fractional PLL (fPLL) when used inconjunction with a high-performance FPGA based digital PLL (DPLL). Each Quad PLL (QPLL) has the capability to be fractionally frequency controlled using a dedicated interface. The QPLL has an interface that controls a sigma delta modulator (SDM) to enable the fractional feedback capability in the QPLL. The main QPLL feedback is controlled fractionally based on the SDM control word allowing fine frequency control by modulating the ratio of the feedback between N and N+1. The control input can be set statically or controlled dynamically from an FPGA logic-based DPLL system.The reference design circuit provides a fully integrated DPLL and transceiver fPLL system which can be instantiated for each QPLL used. The QPLL nominal operating rate is set using an external crystal oscillator (XO), and using the fPLL feature the output can be phase- orfrequency-locked to an input reference signal. The DPLL enables generation of a synchronous QPLL output with run-time configurable parameters (e.g., gain, cutoff frequency, and clock divider values) to enable you to set up the operation specifically for the end application. This allows the flexibility of the reference input signal and DPLL cleaning bandwidth.Application Note: UltraScale FPGAs and UltraScale+ DevicesXAPP1276 (v1.2) October 30, 2019All Digital VCXO Replacement Using a Gigabit Transceiver Fractional PLLAuthors: David Taylor, Matt Klein, Vincent Vendramini, and Antonello Di FrescoDevice FamilyTransceiver TypeVirtex® UltraScale™ FPGAsGTY transceiverKintex UltraScale+™ and Virtex UltraScale+ FPGAs,and Zynq® UltraScale+ devicesGTH, GTM, and GTY transceiversDesigning with FRACXOSignal Name Direction DescriptionERROR_O[20:0]Output Output of phase detector. Signed number.VOLT_O[21:0]Output Output of low-pass filter. Signed number. Only [21:4] are used.CE_PI_O Output Clock enable for accumulator.CE_PI2_O Output Clock enable for low-pass filter and digital-to-analog converter (DAC).CE_DSP_O Output Reset phase detector counters, load phase detector error into thelow-pass filter.OVF_PD Output Overflow in the phase detector.OVF_AB Output Saturation of the low-pass filter inputs.OVF_INT Output Saturation of the low-pass filter integrator.OVF_VOLT Output Saturation of the low-pass filter output.Reference DesignA DRC check is performed during opt_design, and a critical warning is generated if the aboveconditions are not met. No DRC check is performed for the reference clock frequency setting–it is your responsibility to ensure that the FRACXO covers the output frequency range required. Reference DesignThe reference design files are based on the UltraScale transceiver wrapper v1.0 [Ref3]. Thedesign targets the VCU108 development platforms that loopback the receive data to thetransmitter. The FRACXO instance locks the transmitter to the recovered clock RXRECLK.The output error_o of the phase/frequency detector can be captured when CE_DSP_O is High tomonitor the FRACXO response. When locked, ERROR_O should oscillate around 0 (see Figure9).Simulation of the example design is not supported.You can download the reference design files for this application note at(see Download the VCXO Removal Reference Design for UltraScale and 7 Series FPGAs).Table4shows the reference design matrix.Table 4: Reference Design MatrixParameter DescriptionGeneralDeveloper name David Taylor, Matt Klein, Vincent Vendramini, andAntonello Di FrescoTarget devices Virtex UltraScale XCVU095-2FFVA2104ESource code provided YesSource code format VHDLDesign uses code and IP from existing XilinxYes, Vivado ILA and VIOapplication note and reference designs or third partySimulationFunctional simulation performed NoTiming simulation performed NoTest bench used for functional and timing simulations NoTest bench format N/ASimulator software/version used N/ASPICE/IBIS simulations N/AImplementationSynthesis software tools/versions used Vivado Design Suite 2019.1Implementation software tools/versions used Vivado Design Suite 2019.1Static timing analysis performed YesReferencesZynq UltraScale+ MPSoC (One GTH Transceiver)Virtex UltraScale (One GTY Transceiver)Full Design Full Design CLB LUTs30873076 CLB registers45144510 Occupied CLB(1)716835 BlockRAM1413.5 BUFGCE/BUFG_GT3/23/2 GTY transceivers11 MMCM00。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。