基于CPLD的线阵CCD的驱动电路设计与实现

基于CPLD的彩色线阵CCD驱动信号的设计11

目录1 技术指标 (1)2 设计方案及其比较 (1)2.1方案一 (1)2.2方案二 (2)2.3方案三 (2)2.4方案比较 (3)3 实现方案 (3)3.1 CPLD驱动板介绍 (3)3.2 TCD2252D简介 (4)3.3 最终实现方案 (4)4 调试过程及结论 (7)5 心得体会 (10)6 参考文献 (10)基于CPLD的彩色线阵CCD驱动信号的设计1技术指标查TCD2252D芯片手册分析各驱动信号的时序关系,结合CCD学习套件,能够基于QuartusII软件平台使用HDL语言编写逻辑时序,驱动线阵CCD正常工作,并能够实现外部信号控制驱动频率的变化,通过示波器能够观测到输出如图1的图像。

图1 CCD线阵驱动时序图2设计方案及其比较2.1方案一方案一为单片机驱动方法。

因为大多是CCD系统里都含有单片机,所以很自然的会联想到单片机的并行锁存输出口所需的驱动脉冲信号,实现对CCD的控制。

单片机靠指令产生I/O口的输出来实现。

由于线阵CCD的典型复位脉冲为1MHz,所以对单片机还是有一定的最低要求。

简易连接图如图2所示。

图2 单片机简易连线图为了获得精确的CCD驱动,最好不要使用循环制性程序。

因为转移指令是要根据某种条件产生的程序分支,而分支程序在不同条件下之行的指令周期数是不同的,因而造成CCD的驱动时序不准确。

但是对于成千的像元的CCD来说,一个工作周期往往需要好多好多字节的程序存储器。

略有麻烦。

2.2方案二方案二为EPROM驱动方法。

所需的器件TCD1208AP的时序如图3所示。

SH为光积分脉冲信号;1、2为时钟脉冲信号;RS为复位脉冲信号;SP为采样保持脉冲信号。

由图3中的时序可以看出:在这5个信号中,最窄的是AB段,即SP和RS两个信号的高电平部分,各个信号的任何部分都是AB段的倍数。

根据这一特点,将这组信号以AB段为基本单位划分为若干个等时间间隔,称为状态。

时钟波形电平变化发生在一定状态变化时刻,这样任意一路信号都被分为上万个状态,处于某一状态时,各路信号或1或0,构成一个状态的数据,将数据依次装入可擦除只读存储器EPROM中,只要等时间间隔地依次输出这些数据就形成了CCD所需的各路波形。

线阵CCD驱动电路的可编程设计与实现

1 冼 进. Verilog HDL数字控制系统设计实例. 北京 : 中国水利水 电出版社 , 2007: 232—235

2 元华明. 高分辨率全帧 CCD 驱动电路技术研究. 西安 :中国科学 院研究生院 , 2006: 7—10

3 求是科技. CPLD / FPGA 应用开发技术. 北京 : 人民邮电出版社 , 2005: 23—35

END;

2. 3 驱动电路时序仿真与实验测试 采 用 EPM7064STC44210 作 为 目 标 器 件 , 用

VHDL 语言描述整个设计 ,并在 QuartusⅡ5. 1 集成 环境下完成整个设计的输入 、编译 、仿真 ,最终生成 编程烧录文件 。在仿真过程中 ,将 CP的周期设为 250 ns,即 CP的频率为 4 MHz。仿真波形图如图 3 所示 。

4106

科 学 技 术 与 工 程

8卷

从仿真图中可知 , sh高电平脉冲宽度为 4个 CP 周期即 1 μs, fm、fccd频率分别为 2 M、0. 5 M ,恰好 是 TCD132D 手册中的典型驱动频率要求 ,可见符合 设计要求 。

由于 sh 的 时 间 比 较 长 (在 本 设 计 中 设 定 为 10000个 CP周期 ) ,在仿真图中不能完全表现出来 , 然后 对 实 际 电 路 使 用 示 波 器 (型 号 为 R IGOL DS5152M )进行测量 ,实测波形图如图 4、图 5所示 , 对比可得出仿真结果和实测结果吻合 。电路可稳 定输出 1M 的像元同步脉冲 (它与 CCD 驱动脉冲同 频率 ) , 此处行同步脉冲周期即 CCD 积分时间为 1. 156 m s,实际应用时由于考虑到光照强度的问题 , 积分时间没有设为 2. 5 m s,而是 1. 156 m s(编程时 r 最大值取为 4 624) ,这里即体现了积分时间可调的 可编程设计思想 。

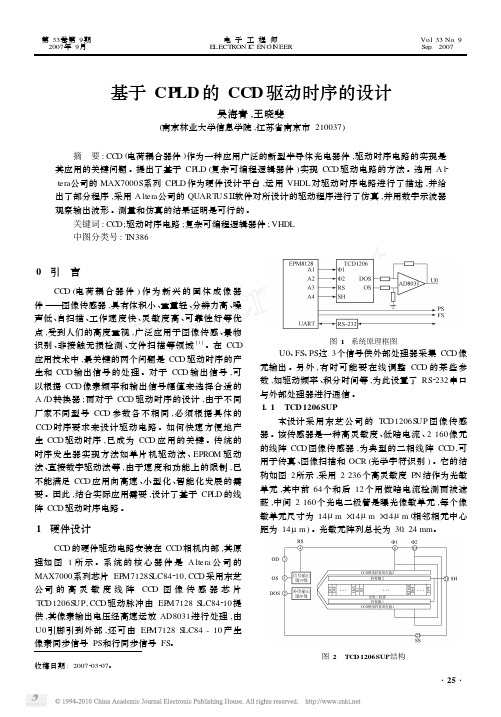

基于CPLD的CCD驱动时序的设计

CCD 驱动电路的总体设计思想是将驱动时序分 成 CCD、SH、和 BLOCK这 3个模块 ,见图 4。每个模块 内部都用 VHDL编写 ,从而大大降低设计的复杂性 。

图 3 TCD 1206SUP 完整的驱动时序

1. 2 EPM 7128 EPM7128属于 A ltera 公司 MAX7000 系列 CPLD

吴海青 ,等 :基于 CPLD 的 CCD驱动时序的设计

·微电子与基础产品 ·

a1: p rocess( clk) begin if clk’event and clk = ’1’ then if tb1 < 7 then tb1 < = tb1 + 1; else tb1 < = 0; end if; end if;

(复杂可编程逻辑器件 ) ,是以第二代多阵列 (MAX)结 构为基础的高性能 CMOS EEPMOS器件 ,其特点是 :逻 辑密度达 2 500个可用门 , 128 个宏单元 ;引脚到引脚 的逻辑延时为 6 ns,计数器工作频率 151. 5 MHz; 33 V 或 5 V 电源供电 ;具有可编程保密位 ,为设计提供全面 保护 ,最大用户 I/O 数目为 100 个 , 84 引脚等多种封 装形式 ; A ltera公司 QUARTUSⅡ开发系统提供应用设 计支持 。

基于CPLD技术的新型线阵CCDTCD1501的驱动时序设计与实现

第26卷第3期2007年9月武 汉 工 业 学 院 学 报Journal of W uhan Polytechnic University Vol 126No 13Sep 12007 收稿日期:2007204217作者简介:李强(19802),男,河南省驻马店市人,助教。

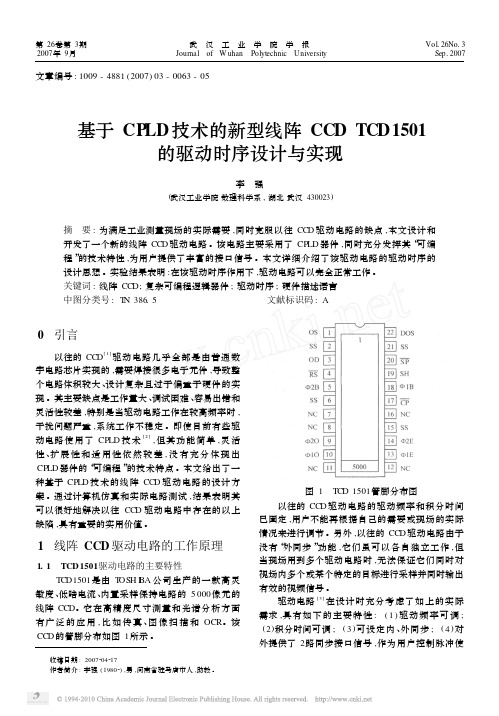

文章编号:1009-4881(2007)03-0063-05基于CP LD 技术的新型线阵CCD TCD1501的驱动时序设计与实现李 强(武汉工业学院数理科学系,湖北武汉430023)摘 要:为满足工业测量现场的实际需要,同时克服以往CCD 驱动电路的缺点,本文设计和开发了一个新的线阵CCD 驱动电路。

该电路主要采用了CP LD 器件,同时充分发挥其“可编程”的技术特性,为用户提供了丰富的接口信号。

本文详细介绍了该驱动电路的驱动时序的设计思想。

实验结果表明:在该驱动时序作用下,驱动电路可以完全正常工作。

关键词:线阵CCD;复杂可编程逻辑器件;驱动时序;硬件描述语言中图分类号:T N 386.5 文献标识码:A0 引言以往的CCD [1]驱动电路几乎全部是由普通数字电路芯片实现的,需要焊接很多电子元件,导致整个电路体积较大、设计复杂且过于偏重于硬件的实现。

其主要缺点是工作量大、调试困难、容易出错和灵活性较差,特别是当驱动电路工作在较高频率时,干扰问题严重,系统工作不稳定。

即使目前有些驱动电路使用了CP LD 技术[2],但其功能简单,灵活性、扩展性和适用性依然较差,没有充分体现出CP LD 器件的“可编程”的技术特点。

本文给出了一种基于CP LD 技术的线阵CCD 驱动电路的设计方案。

通过计算机仿真和实际电路测试,结果表明其可以很好地解决以往CCD 驱动电路中存在的以上缺陷,具有重要的实用价值。

1 线阵CCD 驱动电路的工作原理1.1 TCD 1501驱动电路的主要特性T CD1501是由T OSH I B A 公司生产的一款高灵敏度、低暗电流、内置采样保持电路的5000像元的线阵CCD 。

FPGA_ASIC-基于CPLD工作模式可调的线阵CCD驱动电路设计

驱动设计 , 需要在 修 改 硬 件 结 构 或 者 更 改 程 序 的 基 当频率较高时 , 波形易受 础上才可以改变某些功能 . 为了解决这一问题 , 实现电路的灵活多样 电路干扰 . 性, 输 出 信 号 的 稳 定 可 靠 性 ,本 文 以 型 号 为 引进一种工作模式可 T C D 1 7 0 7 D 的线阵 C C D 为例 , 调的设计方案 . 运用复杂 可 编 程 逻 辑 器 件 ( C o m l e x p , 作为时序设计 P r o r a mm a b l eL o i cD e v i c e C P L D) g g 载体 , 将选择器和外部控制电路相结合 , 用户可以在 并结合电磁兼容 宽范围 内 对 驱 动 时 序 进 行 改 变 , ( , E l e c t r oM e n e t i cC o m a t i b l i l i t EMC)技 术 令 g p y 该电路适用 C C D 电路板得到稳定可靠的 信 号 输 出 . 于高速 C 对 记 录 一 维 瞬 态 信 息 具 有 一 定 意 义, C D, 可用于线阵 C C D 推扫模式 .

2. 1 驱动电路工作原理 传统驱动 电 路 利 用 时 序 发 生 器 只 是 提 供 C C D

3期

谭露雯 , 等: 基于 C P L D 工作模式可调的线阵 C C D 驱动电路设计

4 3 7

芯片所需的时钟脉冲 , 当各时序设定好后 , 如想更改 以符合不同的实验要求 , 则必须对程序进行修改 . 基 本文在设计电路时 于T C D 1 7 0 7 D 的工作时序要 求 , 充分考虑了实际需求 , 工作原 理 框 图 如 图 2. 由外部 时钟提供主脉冲 , 各驱动时序通过编程后由编程端 口J 利用 C T AG 下 载 至 C P L D, P L D 和控制电路结 将来自外部的控制命令转换成相应的控制信号 , 合, 再传递至 C 外部控制端主要是由进行选择 C D 芯片 . 的拨动开关以及微 处 理 器 通 过 的 接 口 电 路 组 成 . 将 C C D 芯片的弱 小 信 号 进 行 一 个 放 大 处 理 后 信 号 输 出.

基于CPLD的彩色线阵CCD驱动设计

信 号 转移 到 相应 的移 位单 元 中 。S 为低 电平 时候 H 上 述转 移过 程完 成 ,光 敏单 元进 入下 一行周 期感 光

采取 自顶向下的设计方法。在完成程序 的输入 ,在 Q a u 软件平台进行编译和仿真从而验证设计的功 ur s t

占空 比约为 1 : 5的方波 ; 积分时间内,至少有 光 32 个 R 82 S脉冲。P I H 的频率 2MH ,占空比约为 5 z

1 的方波 ;但是其相位与 R 信号不 同。在保证基 : 5 S

4 2

长春理工大学学报( 自然科学版 )

2 1年 01

图 2 Qu r s 境下的原理 图 at 环 u

4 1

蓝 ;两相 5 V脉冲驱动 ,1 路驱动信号的最高频率 4

为 2MH ; 5 z 三色信号奇偶并行 ,共六路输出信号; 供电电源为 1V。扫描A 页面可以有 2 e m 2 3 4 i s m l / n

的分 辨力 。

1 驱 动 时序分 析 . 2

各时序信号的时间关系要求 。如 图 1 所示 ,规定了 这些时间意义 。注意 :在 “o ”标示 的时间内保 nt e

Ab t a t n o d rt e tt en e so o o c n ig l e ra r y CCD h p TCD2 0 D ,t i a e r s n sa d i i g s r c :I r e om e e d fc lrs a n n a ra h n i c i 73 h sp p r e e t r n p v pa rie l f n a CCD a e n CP D ,c mb n ss h mai dVHDL d sg g a et e i ed i e ,u e 4 n o l r b sdo L o ie e t a c cn e i n l u g d sg t rv r n a o n h s s7 AHC0 4

基于CPLD的光积分时间可调线阵CCD驱动电路设计

动时序和可调节积分时间的功能 , 并给 出了 C I P D实现 电路和时序仿真波形.

关键 词 : C 积分时间; C D; 可编程

文献标 识码 : A

文 章编 号 :O 41 9 ( O 6 O ・7 10 1O -6 9 2 O )51 8 -4

Ke a oaoyf rO t— lcrncT c nlg & S s ms fMii r fE uain, yL b rtr o p oE eto i eh oo y y t ns yo d cto e o t

\ ir- y tm s rh C n e ,C o g ig U i est C o g ig 4 0 4 ,C ia M c o s Ree c e tr h n qn n v r i S e a y, h n qn 0 0 4 h n

基 于 C L 的光 积分 时 间可调线 阵 C D驱 动 电路设计 PD C

姬 先举 , 温志渝

( 重庆大学微 系统研究 中心重 庆大学光电技术及系统教育部重点实验室 , 重庆 4 0 4 ) 0 0 4

摘 要 : 在分析 Sn 公司的 IX 5B型线阵 C D工作原理的基础上, oy L 54 C 针对 C D器件在光信号分析中存在的问题, C 详细介

De in o  ̄ a sg fLh e roCD ii g Cic i t u a l n e r to n s d o h LD Drvn r u t、 h T n b e I tg a in Tu e Ba e n t e CP

基于CPLD的CCD驱动电路的设计

前 3种 方法基 本偏 重硬 件 的实现 , 调试 困难 , 活性 灵 较差 。而后 一种 方法 虽 编 程 灵 活 , 但存 在 资源 浪 费

较 多 、 率较低 的缺陷 ¨ 。 频

离 行 。该 C D需要 l 驱动 信 号 。包 括 感光 区转 C 2路 移 脉 冲 ( :12,, ) 存储 区转 移脉 冲 M i i , 34 、 ( ( =1 i , =1234 、 储 区到 水 平读 出移位 寄存 器 转移 脉 , ,,)存 冲 M、 水平 读 出移 位 寄 存 器 转 移 脉 冲 2 、 出放 大器 复位脉 冲 彻 。 )读 由该 款 C D的结 构可 知 , C C C D的一个 工作 周期 分 为 两个 阶段 : 光 阶段 和 高 速 转移 阶段 。感 光 阶 感

只须将 C L 内部 逻 辑 重 新 编 程 即可 。2因此 非 常 PD l 适合 C D驱 动 电路 的 设 计 、 作 、 试 和进 一 步 开 C 制 调 发、 升级 。现 给 出一 个 基 于 C L P D技 术 的 面阵 C D C 驱动 电路 的完 整 的硬件设 计 。

S iT c n lg n gn e i g ce e h oo y a d En ie rn

基于 C L P D的 C D驱 动 电路 的 设 计 C

陈 智 邱 跃 洪 张 伯 珩 ’

( 中国科学院西安光学精密机械研究 所 西安 7 0 1 ; , 1 19 中国科学院研究生院 北京 10 3 , 0 09)

智( 9 8 ) 女 , 17 一 , 陕西西安 人, 汉族 , 中国科 学

院西安光 学精密机械 所在读博士研究生 , 研究方 向: 光电信号处理

及 C D相机设计 。E—ma : n yz i.ia Cr。 C i s dc@rp s .O la n n

基于CPLD的CCD通用驱动电路设计方法

第25卷 第2期核电子学与探测技术Vol .25 No .2 2005年 3月N uclear Electronics &Detection T echnologyMar ch 2005 基于CPLD 的CCD 通用驱动电路设计方法张 勇,唐本奇,肖志刚,王祖军,黄绍艳(西北核技术研究所,陕西西安 710024) 摘要:建立CCD 通用测试平台有助于系统研究各类CCD 器件的辐射效应及损伤机理。

探讨了一种基于CPLD 的线阵CCD 通用驱动电路设计方法与实现途径。

利用M AX -P LU SII 开发系统,选用MAX7000S 系列CPLD 芯片,设计实现了核心驱动主控制器,用于读取外部存储器驱动文件,设置相关参数寄存器,并产生符合参数要求的驱动时序脉冲。

在此方法的基础上,完成了基本驱动模块电路的设计。

基本驱动模块电路输出波形的测试结果表明,这种设计方法是完全可行的。

关键词:CP LD ;CCD ;驱动时序;电路设计中图分类号: TN99 文献标识码: A 文章编号: 0258-0934(2005)02-0214-04收稿日期:2004-05-08作者简介:张勇(1971-),男,陕西人,西北核技术研究所助理研究员,硕士生 随着CCD 器件在空间遥感、卫星侦察方面的应用,人们开始关注空间辐射环境对CCD 器件辐射损伤效应[1~3]。

研制CCD 通用测试平台有助于系统研究CCD 在模拟辐射环境中的性能参数变化。

精确的驱动时序是CCD 器件正常工作的保证。

由于CCD 的系列种类很多,不同生产商的CCD 器件的驱动时序往往是不同的,通常选用专用IC 驱动、数字电路驱动、单片机I/O 口驱动等方法产生驱动时序。

这些方法存在着调试困难、柔性较差、驱动时钟低等缺点。

本文探讨了一种基于CPLD 的线阵CCD 通用驱动电路设计方法。

利用MAX -PLUSII 开发系统,选用MAX7000S 系列CPLD 芯片,设计实现了核心驱动主控制器,用于读取外部存储器驱动文件,设置相关参数寄存器,并产生符合参数要求的驱动时序脉冲,适用于各种不同CCD 驱动时序要求。

基于CPLD 的线阵CCD 的驱动电路

1 总体方案设计线阵CCD 一般不能直接在测量装置中使用,因此CCD 驱动信号的产生及输出信号的处理是设计高精度、高可靠性和高性价比线阵CCD 驱动模块的关键。

传统驱动CCD 的设计方法使CCD 的工作频率较慢,信号输出噪声增大,不利于提高信噪比,不能应用于要求快速测量的场合。

而用器件CPLD 进行驱动,则可提高脉冲信号相位关系的精度,以及提供给CCD 驱动脉冲信号的频率,而且调试容易、灵活性高。

目前,在工业技术中,多采用基于CPLD 的实现线阵CCD 的驱动。

系统框图如图1 所示。

图1 基于CPLD 的线阵CCD 的驱动电路2 硬件设计2. 1 CPLD 的硬件电路的设计以CPLD(Complex Programmable Logic Device)器件为核心,设计线阵CCD 的驱动电路。

然后在其基础上扩展,选择其他元器件,设计出与其相配套的电路部分,经调试后组成硬件系统。

CPLD 的电路由5 部分组成,有源晶振向EPM240T100C5N 的U1A 的IO/GCLK0 口输入时钟脉冲CLK0,提供了CPLD 工作的时钟脉冲,因为时序逻辑的需要。

U1C 从JTAG 端口中下载程序,U1B 的52、54、56、58 口输出脉冲信号。

U1D 管脚接3. 3 V 电压,U1E 管脚接地。

电路原理如图2 所示。

图2 CPLD 的电路原理图2. 2 DC /DC 模块的设计为得到CPLD 所需的电压,外接电源需要经过DC /DC 模块进行转换。

为进一步减少输出纹波,可在输入输出端连接一个LC 滤波网络,电路原理如图3所示。

图3 DC/DC 模块的电路原理图设计2. 3 稳压模块的由DC /DC 模块转换的直流电压,经过一个R11电阻和一个发光二极管接地,发光二极管指示灯,然后从AMS 芯片的Vin端输入,进入到芯片的内部,经过一系列的计算,从Vout输出3. 3 V 电压,GND 端端口接地。

为消除交流电的纹波,电路采用电容滤波,分别用0. 1 μF 的极性电容和10 μF 的非极性电容组成一个电容滤波网络。

高速CCD摄像机驱动时序发生器的设计及基于CPLD技术的实现

第28卷第2期2002年3月 光学技术OPTICAL TECHN IQU E Vol 128No 12March 2002 文章编号:100221582(2002)022*******高速CCD 摄像机驱动时序发生器的设计及基于CPLD 技术的实现Ξ王军波,孙振国,陈强,赵江滨(清华大学机械工程系,北京 100084)摘 要:在分析DAL SA 公司的IA 2D1型高速CCD 器件驱动时序关系的基础上,设计了可调曝光时间的高速摄像机驱动时序发生器。

选用复杂可编程逻辑器件(CPLD )作为硬件设计平台,使用VHDL 语言对驱动时序发生器进行了硬件描述,采用EDA 软件对所设计的驱动时序发生器进行了功能仿真,针对Lattice 公司的可编程逻辑器件ISPL SI5256进行适配。

系统测试结果表明,所研制的驱动时序发生器不仅可以满足高速CCD 摄像机的驱动要求,而且还能够调节其曝光时间。

关键词:高速CCD 摄像机;驱动时序发生器;复杂可编程逻辑器件;可调曝光时间中图分类号:TN38615;TP21 文献标识码:ADesign on driving schedule generator for high 2speed CCD cameradriving and its achievement based on CPLD technologyWANG J un 2bo ,SUN Zhen 2guo ,CHE N Qiang ,ZH AO Jiang 2bin(Department of Mechanical Engineering ,Tsinghua University ,Beijing 100084,China )Abstract :Driving schedules of IA 2D1(one kind of high 2speed CCD produced by DAL SA Co 1Ltd 1)have been examined in detail 1The driving schedule generator with adjustable exposure time has been designed for high 2speed CCD camera 1Complex program logic device (CPLD )has been chosen as the hardware design platform ,driving schedule generator has been described with VHDL 1The designed generator has been successfully fulfilled function simulation with EDA software and fitted into ISP L SI 5256(a kind of CPLD products that made by Lattice )1Experiments show that designed generator is suitable for the driving of high 2speed CCD camera ,and the ex posure time of camera could be ad justed according to different applications 1K ey w ords :high 2speed CCD camera ;driving schedule generator ;complex programmable logic device ;adjustable exposure time1 引 言CCD (charge coupled device )作为近几年新兴的固体成像器件,具有体积小、重量轻、分辨率高、灵敏度高、可靠性好等优点,广泛应用于机器人视觉系统、安全保卫系统、智能交通系统以及Internet 接入装置等领域[1]。

基于CPLD的彩色线阵CCD驱动信号的设计11讲解

目录1 技术指标 (1)2 设计方案及其比较 (1)2.1方案一 (1)2.2方案二 (2)2.3方案三 (2)2.4方案比较 (2)3 实现方案 (3)3.1 CPLD驱动板介绍 (3)3.2 TCD2252D简介 (4)3.3 最终实现方案 (4)4 调试过程及结论 (7)5 心得体会 (10)6 参考文献 (10)基于CPLD的彩色线阵CCD驱动信号的设计1技术指标查TCD2252D芯片手册分析各驱动信号的时序关系,结合CCD学习套件,能够基于QuartusII软件平台使用HDL语言编写逻辑时序,驱动线阵CCD正常工作,并能够实现外部信号控制驱动频率的变化,通过示波器能够观测到输出如图1的图像。

图1 CCD线阵驱动时序图2设计方案及其比较2.1方案一方案一为单片机驱动方法。

因为大多是CCD系统里都含有单片机,所以很自然的会联想到单片机的并行锁存输出口所需的驱动脉冲信号,实现对CCD的控制。

单片机靠指令产生I/O口的输出来实现。

由于线阵CCD的典型复位脉冲为1MHz,所以对单片机还是有一定的最低要求。

简易连接图如图2所示。

图2 单片机简易连线图为了获得精确的CCD驱动,最好不要使用循环制性程序。

因为转移指令是要根据某种条件产生的程序分支,而分支程序在不同条件下之行的指令周期数是不同的,因而造成CCD的驱动时序不准确。

但是对于成千的像元的CCD来说,一个工作周期往往需要好多好多字节的程序存储器。

略有麻烦。

2.2方案二方案二为EPROM驱动方法。

所需的器件TCD1208AP的时序如图3所示。

SH为光积分脉冲信号;1、2为时钟脉冲信号;RS为复位脉冲信号;SP为采样保持脉冲信号。

由图3中的时序可以看出:在这5个信号中,最窄的是AB段,即SP和RS两个信号的高电平部分,各个信号的任何部分都是AB段的倍数。

根据这一特点,将这组信号以AB段为基本单位划分为若干个等时间间隔,称为状态。

时钟波形电平变化发生在一定状态变化时刻,这样任意一路信号都被分为上万个状态,处于某一状态时,各路信号或1或0,构成一个状态的数据,将数据依次装入可擦除只读存储器EPROM中,只要等时间间隔地依次输出这些数据就形成了CCD所需的各路波形。

基于CPLD的线阵CCD驱动电路设计方法的研究与实现

.

Iske e t e , prn i e a sg de ft e t i g s q n e t y faur s i cpl nd dei i a o i n e ue c n s h m

0 引言

C D( h reC u l e ie) C C ag o pe D vcs,电荷 耦合器件 ,是 d 七十年代初 发展起来 的新型半导体 器件 ,它是 美国 贝尔 实 验 室 的 w..o l G..mi SB ye和 ES t h于 1 7 首 先 提 出 9 0年 的 …。后 来很快 被 Ama o等 人的 实验 所证 实 。在 经历 l l 了几年 的研 究阶段之 后 ,建立 了以一维势 阱模 型为基础 的非稳态 C D基本理 论。3 C 0年来 ,C CD器件理论及其 应用技术 等的研究取 得了极大 的发展 ,尤其在 图像传感

i egn en e sT id v rs ee pdo e as f P D,adr hitrc g a e rvddfr srw t n n er g l . hs r e vl e nt s L i i fd i i id o h b io C n c e ae i la o i es i i n f s srp n e ou h

摘 要 :以典型 的线阵 C DI C  ̄像传 感器件 T D3D C 1 为例 ,设计和开发 了一种 线阵C D  ̄ 2 C  ̄ 动电路。电路主要采用 了复杂 可编程逻辑器件 (P D ,充分发挥其 “ CL) 可编程 ”的技术 特性 ,为用户提供 了丰富的接 口信号 。介 绍了

该驱 动电路 的主 要特性 、工 作原理和驱 动时序 的设 计思想 ,阐述 了逻辑 设计原理 ,给出 了cP D实现 电路和 L

基于CPLD的线阵CCD驱动电路设计

图1 基于 CL P D的 线 阵 C D 的驱 动 电路 C

2 硬 件 设 计

2 1 C L 的硬件 电路 的设 计 . P D

以 C L C m l rga mal L gcD vc ) P D( o pe Porm be oi ei 器 x e

传 统驱 动 C D的设计 方 法 使 C D 的工 作频 率 较 C C 慢 ,信 号输 出噪 声增 大 ,不利 于提 高信 噪 比 ,不能 应 用 于要 求 快 速 测 量 的 场 合 J 。而 用 可 编 程 逻 辑 器 件 CL P D进 行 驱 动 ,则 可 提 高 脉 冲信 号 相 位 关 系 的 精

s n d n ed g m o hrw r ds ncm le . B s e ,t o w r db gi pe et . B U i e ,adt i a f ad a ei o p t g h a r e g e d ei s h sf a eug gi i l ne d e t e n sm m d yQ —

中图分类号

T 32 1 P 3 .

文献标识码

A

文章编号

10 7 2 (0 10 0 3— 3 07— 8 0 2 1 )9— 7 0

The De i n o i e r CCD i i g Ci c i sg fIn a Dr v n r u t

HE n, W ANG o ng Mi Da pi

( ecig n eer nt f l tcadEet n eh o g ,T eScn rlr T ahn dR sa hU io e r n l r i T cnl y h eodAtl y a c E ci co c o ie E g er gC l g ,X’ 10 5 h a ni e n o ee in7 0 2 ,C i ) n i l a n

基于CPLD的线阵CCD驱动时序的设计与实现

收稿日期:2007-10 作者简介:林德辉(1973—),男,硕士,研究方向为嵌入式系统和CP LD 设计。

图1 TC D1208AP电路图图2 TCD1208AP 的驱动时序图基于CP LD 的线阵CC D 驱动时序的设计与实现林德辉,道克刚,钟绍俊(中国计量学院机电工程分院,浙江杭州310018) 摘要:介绍一种基于CP LD 芯片EP M7128S LC84-15的线阵CC D -TC D1208AP 的驱动设计方法,详细阐述了逻辑设计原理,给出了时序仿真图形,并给出实际波形。

实践证明,该设计方法具有一定的使用价值。

关键词:线阵CCD;CP LD;驱动时序设计中图分类号:T M930 文献标识码:B 文章编号:1006-2394(2008)04-0022-02D esi gn and I m ple m en t a ti on of L i n ear CCD D r i ver Ba sed on CPLDL IN De 2hui,DAO Ke 2gang,ZHONG Shao 2jun(Dep t .of Mechatr onics Engineering,China I nstitute of Metr ol ogy,Hangzhou 310018,China )Abstract:A driving design method of linear CCD T CD1208AP based on the CP LD chi p of EP M7128S LC84-15is described in this paper .The p rinci p le of l ogic design is given in detail .The diagra m of ti m ing sequence si m ulati on is p resented and the p ractical ti m ing sequence is dis p layed .The fact de monstrates that this method has s ome p ractical value .Key words:linear array CCD;CP LD;design of driving ti m ing sequence 本文介绍一种采用美国ALTERA 公司的MAX7000S 系列CP LD 芯片EP M7128利用VHDL 语言编程实现T CD1208AP 的驱动设计方法。

基于CPLD的线阵CCD驱动电路的设计

基于CPLD的线阵CCD驱动电路的设计作者:张晖刘晶和思铭来源:《电脑知识与技术》2012年第24期摘要:针对线阵CCD芯片TCD1206UP,提出了一种基于CPLD的驱动方案,讨论了电路的工作原理和设计特点,同时给出了电路原理图和CPLD电路的时序仿真波形。

该设计方案有效地完成了对TCD1206UP的驱动,并且具有高效开发、可重复编程,可修改的优势。

关键词:CCD;TCD1206UP;CPLD中图分类号:TP311文献标识码:A文章编号:1009-3044(2012)24-5917-02The Design of Linear CCD’s Drive Circuit Based on CPLDZHANG Hui, LIU Jing, HE Si-ming(Department of Electrician and Electron, Aviation University of Air Force, Changchun 130022, China)Abstract: In order to meet the needs of linear array CCD chip TCD1206UP,this paper presents a driving plan for linear CCD based on CPLD,In addition,the principle of operation and design of circuit were discussed and the principle circuit and the schedule simulation wave? form of CPLD were given.The design effectively completed TCD1206UP drive,and has the advantages of efficient development,being re? programmable and modified.Key words: CCD; TCD1206UP; CPLDCCD是一种完成光电转换的图像传感器,广泛应用于摄像、图像采集、扫描仪、工业测量等领域。

基于CPLD技术的线阵CCD驱动电路设计

基于CPLD技术的线阵CCD驱动电路设计

蔡泽彬;蒋跃

【期刊名称】《空军预警学院学报》

【年(卷),期】2004(018)001

【摘要】针对以往设计的电荷耦合器件(CCD)驱动电路存在着体积大、易受干扰和工作频率低的缺点,设计出一种基于复杂可编程逻辑器件(CPLD)技术的CCD驱动电路,可用于不同型号的CCD,同时提高了整个系统的稳定性和工作的效率.仿真结果表明,该电路具有一定的实用价值.

【总页数】4页(P50-52,55)

【作者】蔡泽彬;蒋跃

【作者单位】空军雷达学院基础部,湖北,武汉,430019;空军雷达学院基础部,湖北,武汉,430019

【正文语种】中文

【中图分类】TN79

【相关文献】

1.基于CPLD的带电子快门功能线阵CCD驱动电路设计 [J], 赵光兴;赵雅

2.基于CPLD的线阵CCD驱动电路设计方法的研究与实现 [J], 胡丽;宋文爱;杨录

3.基于CPLD的线阵CCD驱动电路设计 [J], 何敏;王道平

4.基于CPLD的线阵CCD的驱动电路设计与实现 [J], 郭焱

5.基于CPLD和Verilog的高精度线阵CCD驱动电路设计 [J], 黄文林;扬光永;胡国清

因版权原因,仅展示原文概要,查看原文内容请购买。

基于CPLD的CCD视频信号处理电路的设计与硬件实现

基于CPLD的CCD视频信号处理电路的设计与硬件实现陈学飞;汶德胜;郑培云;马涛;梁义涛【期刊名称】《电子器件》【年(卷),期】2008(031)003【摘要】在分析VSP1012型CCD视频信号处理芯片工作原理的基础上,设计了CCD成像系统的视频信号处理电路及其硬件电路.选用CPLD器件作为硬件设计载体,使用VHDL语言对VSP1012的初始化设置和驱动时序发生器进行了硬件描述.并针对ALTERA公司的EPM7160SLC84-10进行了RTL级仿真及配置.硬件实验结果表明,所研制的CCD视频信号处理电路不仅可以满足CCD成像系统视频信号处理的要求,而且集成度高,应用方便.【总页数】4页(P807-810)【作者】陈学飞;汶德胜;郑培云;马涛;梁义涛【作者单位】中国科学院西安光学精密机械研究所,西安,710068;中国科学院研究生院,北京,100864;中国科学院西安光学精密机械研究所,西安,710068;中国科学院西安光学精密机械研究所,西安,710068;中国科学院研究生院,北京,100864;中国科学院西安光学精密机械研究所,西安,710068;中国科学院研究生院,北京,100864;中国科学院西安光学精密机械研究所,西安,710068;中国科学院研究生院,北京,100864【正文语种】中文【中图分类】TN386.5【相关文献】1.基于CPLD的线阵CCD驱动电路设计方法的研究与实现 [J], 胡丽;宋文爱;杨录2.基于CPLD的线阵CCD-TCD1501D驱动时序的设计与实现 [J], 林德辉;谢楠3.基于CPLD的线阵CCD的驱动电路设计与实现 [J], 郭焱4.基于CPLD的面阵CCD驱动时序发生器设计及其硬件实现 [J], 陈学飞;汶德胜;郑培云5.基于CPLD的空间面阵CCD相机驱动时序发生器的设计与硬件实现 [J], 冉晓强;汶德胜;郑培云;王华;梁义涛因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ห้องสมุดไป่ตู้

摘 要: C C D驱动时序 电路 的设计实现是其应用 的关键 问题。该 文在分析 T C D 1 2 0 9 D线阵 C C D的工作原 理和驱动时序等特性的基础上 , 提 出了一种基 于 C P L D的线阵 C C D驱动电路的设计方法 , 其 中选用 MA X I l 系歹 4 C P L D作为硬件设计平台 , 运用 V H D L 语 言设计 驱动时序电路 。该设计 使用 Q u a r t u s I I 软件对所设

l o g i c d e v i c e( C P L D ) i n t h i s p a p e r . I n o r d e r t o r e a l i z e t h e t i me s e q u e n c e d r i v i n g , t h e MA X I I d e v i c e s W a S u s e d

计的驱动程序进行 了仿真 , 仿真与实验结果表 明该方案设计可行 , 电路结构简单 , 集成度较 高 , 实用性强 ,

并具有一定通用性 。 关键词 : 线阵 C C D ; 驱动时序 电路 ; 复杂可编程逻辑器件 ; V H D L

中图分类号 : T N3 8 6 . 5 文献标识码 : A 文章 编号 : 1 0 0 3 - 0 1 0 7 ( 2 0 1 3 ) 1 0 — 0 0 1 3 - 0 5

郭焱( 武汉工程大学理学院, 湖北 武汉 4 3 0 0 7 3 )

Gu oYa n ( C o l l e g e o f S c i e n c e , Wu h a nI n s t i t u t e o f T e c h n o l o g y , Hu b e i Wu h a n4 3 0 0 7 3)

r e s u l t s ob t a i n e d 行D m s i mu l a t i o n a n d t e s t s h o w t h a t t h e me t h o d i s f e a s i bl e a n d c on s t r u c t i on f o t h e c i r c u i t i s s i mp l e wh os e p r a c t i c ab i l i t y i s wi d e. T h e d r i v e c i r c u i t d es i gn e d i s p r o v i d ed wi t h g o od u ni b er s a l i t y .

CL c n u mb e r : T N 3 8 6 . 5

D o c u me n t c o d e : A

A r t i c l e I D: 1 0 0 3 — 0 1 0 7 ( 2 0 1 3 ) 1 0 - 0 0 1 3 — 0 5

Abs t r a c t : T h e d e s i gn o f t h e t i me s e qu e n c e d r i v i n g c i r c ui t i s o n e f o t h e c r u c i al pr o bl em f o r t h e a p pl i c a t i on f o

K e y wo r d s :L i n e ar Ch a r ge Co u pl e d De v i c e s ; t i me s e qu en c e dr i v i n g c i r cu i t ; c o mp l e x p r o g r a mma bl e l o gi c de v i c e; VHDL

Ch a r g e C o u p l e d De v i c e s( C CD ) . O n t h e b a s i s f o a n a l y z i n g t h e i n t e r n a l s t r u c t u r e t h e o r y a n d d r i v i n g p u l s e s o f

基于 C P L D的线阵 C C D的驱动电 路设计与实现

电子质 量 ( 2 o 1 3 第1 0 期)

基 于 CP L D 的线 阵 CCD 的 驱 动 电 路 设 计 与 实 现

De s i g n o f L i ne a r CCD Dr i v i ng Ci r c u i t Ba s e d o n CPLD

a s t h e c on  ̄o l c e n t e r wh i c h i s pr o gr a m me d wi t h VHDL a n d s i mu l a t e d f o r r e s ea r c h b y Qu a  ̄ u s I I s o f t war e. T h e