SSD1788Z中文资料

闪迪 SDSSDE60-250G-Z25 移动固态硬盘 数据表

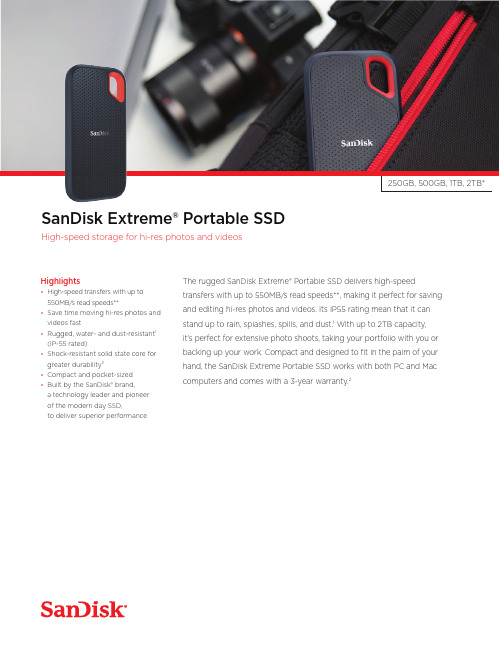

The rugged SanDisk Extreme® Portable SSD delivers high-speed transfers with up to 550MB/s read speeds**, making it perfect for saving and editing hi-res photos and videos. Its IP55 rating mean that it can stand up to rain, splashes, spills, and dust.1 With up to 2TB capacity, it’s perfect for extensive photo shoots, taking your portfolio with you or backing up your work. Compact and designed to fit in the palm of your hand, the SanDisk Extreme Portable SSD works with both PC and Mac computers and comes with a 3-year warranty.2SanDisk Extreme® Portable SSD High-speed storage for hi-res photos and videosHighlights• High-speed transfers with up to550MB/s read speeds**• Save time moving hi-res photos andvideos fast• Rugged, water- and dust-resistant 1(IP-55 rated)• Shock-resistant solid state core forgreater durability 3• Compact and pocket-sized• Built by the SanDisk® brand,a technology leader and pioneerof the modern day SSD,to deliver superior performanceWestern Digital T echnologies, Inc.951 SanDisk Drive | Milpitas | CA 95035 | USAWestern Digital T echnologies, Inc. is the seller of record and licensee in the Americas of SanDisk® products.At SanDisk®, we’re expanding the possibilities of datastorage. For more than 25 years, SanDisk’s ideashave helped transform the industry, delivering nextgeneration storage solutions for consumers and businesses around the globe.For more information, please visit* 1GB = 1,000,000,000 bytes. 1TB = 1,000,000,000,000 bytes. Actual user storage less.** Based on internal testing; performance may be lower depending on drive capacity, host device, OS and application. 1MB = 1,000,000 bytes. I EC 60529 IP55: T ested to withstand water flow (30 kPa) at 3 min.; limited dust contact does not interfere with operation. Must be clean and dry before use. see /wug Shock-resistant (up to 1500G) and vibration-resistant (5 gRMS, 10-2000 HZ), non-operating temperature (from -20°C to 70°C), operating temperature (from 0°C to 45°C).SanDisk, the SanDisk logo, and SanDisk Extreme are registered trademarks or trademarks of Western Digital Corporation or its affiliates in the US and/or other countries. All other marks are the property of their respective owners. ©2018 Western Digital Corporation or its affiliates. All rights reserved.Available capacities:250GB, 500GB, 1TB, 2TB Dimensions (H x W x L):0.348 x 1.951 x 3.787 in. (8.850 x 49.550 x 96.200 mm)Operating temperature:0°C to 45°C Storage temperature:–20°C to 70°C Interface:USB 3.1 Gen 2Durability:IP55-rated for water- and dust-resistance Shock Resistant:up to 1500G Vibration Resistant:5 gRMS, 10-2000 Hz Warranty:3-year; 3-year limited (US only)。

神舟z7-kp7gc固态硬盘协议

神舟z7-kp7gc固态硬盘协议摘要:1.神舟Z7-KP7GC 固态硬盘概述2.神舟Z7-KP7GC 支持的固态硬盘协议3.推荐的固态硬盘型号及性价比4.如何安装固态硬盘正文:## 神舟Z7-KP7GC 固态硬盘概述神舟Z7-KP7GC 是一款性能优秀的游戏笔记本,搭载了英特尔酷睿i7-9750H 处理器、NVIDIA GeForce GTX 1660 Ti 显卡,内存为16GB,存储方面则采用了一块512GB 的固态硬盘。

对于游戏玩家来说,拥有一块高速、大容量的固态硬盘是非常重要的。

## 神舟Z7-KP7GC 支持的固态硬盘协议神舟Z7-KP7GC 支持的固态硬盘协议有SATA 和NVMe。

其中,SATA 接口的固态硬盘速度相对较慢,但价格较为亲民;NVMe 接口的固态硬盘则速度更快,但价格相对较高。

## 推荐的固态硬盘型号及性价比对于神舟Z7-KP7GC 来说,推荐选择NVMe 协议的固态硬盘,以发挥机器的最大性能。

在性价比方面,可以考虑以下几款固态硬盘:1.西部数据(WD)黑盘SN750:性能优秀,读写速度可达3400MB/s,价格适中。

2.三星(SAMSUNG)970 EVO Plus:性能稳定,读写速度可达3500MB/s,价格略高。

## 如何安装固态硬盘在购买合适的固态硬盘后,需要对其进行安装。

以下是安装固态硬盘的一般步骤:1.关闭电脑电源,拔掉电源适配器。

2.打开笔记本底部的盖板,找到固态硬盘的接口。

通常会有M.2 接口和SATA 接口两种。

3.将固态硬盘正确插入相应接口,并按照螺丝孔位固定。

4.重新安装底部盖板,连接电源适配器,启动电脑。

5.通过系统自带的磁盘管理工具或者第三方软件,对固态硬盘进行分区、格式化等操作。

总之,神舟Z7-KP7GC 支持SATA 和NVMe 协议的固态硬盘,推荐选择性价比较高的NVMe 固态硬盘如西部数据SN750 或三星970 EVO Plus。

采用更成熟的96层堆叠闪存颗粒 两款中高端NVMe SSD实战体验

采用更成熟的96层堆叠闪存颗粒两款中高端NVMe SSD实战体验作者:来源:《微型计算机》2020年第21期毫無疑问,采用96层堆叠的3D NAND颗粒绝对是今年SSD新品最主要的一个特征。

毕竟96层堆叠颗粒除了堆叠层数相比64层增加50%,存储密度更高外,96层堆叠闪存还借助升级后的传输接口,拥有更高的性能。

简单来说,采用96层堆叠闪存可以给SSD带来更大的容量、更强的性能。

而到了今年下半年,96层堆叠闪存的生产技术也取得了新的进展,96层堆叠闪存的工作频率、可靠性、性能有了进一步提升。

因此金士顿在采用96层堆叠闪存的KC2000 NVMe SSD仅仅发布约半年后就推出了同级新款产品:KC2500,而闪存颗粒厂商美光科技旗下品牌英睿达也借助美光在96层闪存颗粒上的突破,在今年下半年推出了让人期待已久的高端NVMe SSD:英睿达P5。

接下来就让我们通过实战测试来看看这两款采用最新96层堆叠闪存的NVMe SSD能有怎样的表现。

性能更强的96m颗粒金士顿KC2500 M.2 NVMe固态硬盘相对于金士顿在今年发布的KC2000固态硬盘,最新的KC2500无论是在外观还是硬件规格上都与其非常相近。

首先这款SSD也是采用M.2 2280板型设计,主控则选用了支持PCIe 3.0×4接口的慧荣SM2262EN主控。

该主控是一颗ARM Cortex R5双核心CPU,频率运行在625MHz,支持8通道读写、NVMe 1.3规范,支持端到端资料路径保护、SRAM ECC,以及结合LDPC和RAID的最新第五代NANDXtend ECC等各种“错误检查和纠正”技术。

同时它还支持TCG-opal 2.0、硬件真随机数和SHA256、XTS-AES256全盘实时加密技术。

此外,金士顿也为KC2500固态硬盘配备了独立缓存,用于存放记录数据位置的FTL映射表。

在其1TB产品上,它配备了两颗DDR3L 1600512MB内存颗粒作缓存,用来存放FTL分区映射表,其缓存总容量达到1GB。

MEMORY存储芯片LPC1768FBD100中文规格书

Features•Interrupts—Seven external interrupt request (IRQ) lines—Twelve port pins with interrupt capability—The MPC866P and MPC866T have 23 internal interrupt sources; the MPC859P, MPC859T, and MPC859DSL have 20 internal interrupt sources.—Programmable priority between SCCs (MPC866P and MPC866T)—Programmable highest priority request•Communications processor module (CPM)—RISC controller—Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)—Supports continuous mode transmission and reception on all serial channels—Up to 8-Kbytes of dual-port RAM—MPC866P and MPC866T have 16 serial DMA (SDMA) channels; MPC859P, MPC859T, and MPC859DSL have 10 serial DMA (SDMA) channels.—Three parallel I/O registers with open-drain capability•Four baud rate generators—Independent (can be connected to any SCC or SMC)—Allow changes during operation—Autobaud support option•MPC866P and MPC866T have four SCCs (serial communication controller); MPC859P, MPC859T, and MPC859DSL have one SCC; and SCC1 on MPC859DSL supports Ethernet only.—Serial ATM capability on all SCCs—Optional UTOPIA port on SCC4—Ethernet/IEEE 802.3 optional on SCC1–4, supporting full 10-Mbps operation—HDLC/SDLC—HDLC bus (implements an HDLC-based local area network (LAN))—Asynchronous HDLC to support PPP (point-to-point protocol)—AppleTalk—Universal asynchronous receiver transmitter (UART)—Synchronous UART—Serial infrared (IrDA)—Binary synchronous communication (BISYNC)—Totally transparent (bit streams)—Totally transparent (frame based with optional cyclic redundancy check (CRC)•Two SMCs (serial management channels) (MPC859DSL has one SMC (SMC1) for UART.)—UART—Transparent—General circuit interface (GCI) controller—Can be connected to the time-division multiplexed (TDM) channelsMPC866/MPC859 Hardware Specifications, Rev. 24Freescale SemiconductorFeatures•One serial peripheral interface (SPI)—Supports master and slave modes—Supports multiple-master operation on the same bus•One inter-integrated circuit (I2C) port—Supports master and slave modes—Multiple-master environment support•Time slot assigner (TSA) (MPC859DSL does not have TSA.)—Allows SCCs and SMCs to run in multiplexed and/or non-multiplexed operation—Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user-defined—1- or 8-bit resolution—Allows independent transmit and receive routing, frame synchronization, and clocking—Allows dynamic changes—On MPC866P and MPC866T, can be internally connected to six serial channels (four SCCs and two SMCs); on MPC859P and MPC859T, can be connected to three serial channels (one SCC and twoSMCs).•Parallel interface port (PIP)—Centronics interface support—Supports fast connection between compatible ports on MPC866/859 or MC68360•PCMCIA interface—Master (socket) interface, compliant with PCI Local Bus Specification (Rev 2.1)—Supports one or two PCMCIA sockets whether ESAR functionality is enabled—Eight memory or I/O windows supported•Debug interface—Eight comparators: four operate on instruction address, two operate on data address, and two operate on data.—Supports conditions: = ≠ < >—Each watchpoint can generate a breakpoint internally•Normal high and normal low power modes to conserve power• 1.8 V core and 3.3 V I/O operation with 5-V TTL compatibility; refer to Table6 for a listing of the 5-V tolerant pins.•357-pin plastic ball grid array (PBGA) package•Operation up to 133 MHzMPC866/MPC859 Hardware Specifications, Rev. 2Freescale Semiconductor5。

超窄3.5英寸双面磁盘驱动器说明书

YD-702J-6637JProduct SpecificationsSUPER SLIM 3.5 FLOPPY DISK DRIVE12.7mm HEIGHT2.0/1.6/1.0 MB 3MODE TYPEFDZ-529022 REV.A4FDZ-529022 REV.A4Revisions Month/ Year RevisionReason for RevisionRevised Pages Oct., 1999Rev. A 1st editionJan., 2000Rev. A1Delete optional connector (NON-ZIF TYPE)P11Apr., 2000Rev. A2Screw fastening torque changeP13Jul., 2001Rev. A3Additional of specification (Non operating shock)P3,4Aug, 2003Rev. A4Added to comments on restrictions of liability and high safety use. Drawing adjustment.P2,12This product specification describes the YD-702J series double-sided, 3.5 floppy disk drive for portable applications.(1) I n this manual, the term “drive” refers to the YD-702J series double-sided,3.5 floppy disk drive. The term “disk” refers to the 3.5 floppy disk.z This specification may be revised without prior notice.Make sure to check the revision number when placing an order.zUnauthorized duplication of this document is prohibited.For the usage of this product for High Safety useThis product is assumed for general uses, such as an object for general office work, personal and home use, and is not designed or manufactured supposing for High safety use. Make sure not to use this product without taking measures to ensure the safety required for the high safety use.High Safety Use means the use that requires extremely high security (see examples), and that accompanies a serious danger for the life and body directly, if security cannot be ensured.*Nuclear control, airplane flight control, air traffic control, mass transportation operation control, life support,weapon launch control, etc.This product specification is subject to change without notice.Chapter 1. IntroductionThese specifications pertain to the YD-702J series of 3.5”, super slim, 5-volt single power supply, double-sided micro floppy disk drives.The YD-702J series has been designed for 3.5 (90mm) floppy disk.1. Super-sliminessWith a 12.7mm height and a weight of 158g, the YD-702J drive is approximately half the size and weight of current 3.5 floppy disk drives (compare with Y-E DATA’s YD-702D).2. Low Power ConsumptionA standard power consumption of 1.15W during operation and 15mW during standby allows for battery-driven operation.3. High PerformanceA direct drive brush less motor is used to guarantee high performance.4. Shock ResistanceShock-absorbing teeth built directly into the head carriage assembly have raised shock resistance to 980.7m/s2 {100G}(11ms half-sine wave)and 2157.5m/s2 {220G}(2ms half-sine wave).FDZ-529022 REV. A4FDZ-529022 REV.A4- 4 -Chapter 2. Product Specifications 2.1 Performance Item 2.0MB Mode 1.6MB Mode 1.0MB Mode Capacityz Unformatted z Formatted 1)Sectors/Track 2)Sectors/Track 3)Sectors/Track Recording Density (bits/mm){BPI}Track Density (tracks/mm){TPI}Cylinders Tracks Encoding Method Rotational Speed (min -1){RPM}Transfer Rate Latency(Average)Access Time z Average z Track to Track z Settling Time z Turn Around Time Motor Start Time2.0Mbytes 18: 1474.6kBytes 686.4{17434}5.315{135}80 Cylinders 160 Tracks MFM 300500 kbits/s 100 ms 94 ms 3 ms 15 ms 4 ms 0.5sec 1.6Mbytes 26: 1025.0kBytes 15: 1182.7kBytes 8: 1261.6kBytes 558.4{14184}5.315{135}77 Cylinders 154 Tracks MFM 360500 kbits/s 83 ms 91 ms 3 ms 15 ms 4 ms 0.5 ms 1.0Mbytes 16: 655.4kBytes 9: 737.3kBytes 5: 819.2kBytes 343.2{8717}5.315{135}80 Cylinders 160 Tracks MFM 300250 kbits/s 100 ms 94 ms 3 ms 15 ms 4 ms 0.5sec Table 2.1 Performance2.2 Physical Specifications 2.3 Reliability and Maintenance MTBF PM*MTTR Component Life Error Rates ●Soft Errors ●Hard Errors ●Seek Errors 30,000POH None 30 minutes 5years or 20,000POH 1 per 109 bits read 1 per 1012 bits read 1 per 106 seek operations Table 2.3 Reliability * Preventive maintenance Note: Non-operating shock and vibration values are the same as above with or without disk in the drive.Signal Connector DC Power Requirements Power Consumption Environment● OperatingTemperature Relative Humidity Maximum Wet Bulb Vibration Shock● Non operatingTemperature storageTransportationRelative HumidityVibrationShockMechanical DimensionsWidthHeightDepthWeightSafety ApprovalsFFC Connector1mm pitch, 26pinIncluding DC power lineRefer to figure 4.2Refer to Table 3.8.1.15W TYP5°C to 50°C (note 1)20% to 80%29°C 9.8m/s 2{1G}(10-200Hz)4.9m/s 2{0.5G}(200-500Hz)58.8m/s 2{6G}(11ms half-sine wave)-40°C to 60°C -40°C to 65°C No condensation 19.6m/s 2{2G}(10-500Hz)980.7m/s 2{100G}(11ms half-sine wave)2157.5m/s 2 {220G}(2ms half-sine wave)96.0mm 12.7mm 130mm 158g(TYP)UL, CSA, TÜV, CE Mounting Recommendations See figure 5.2Table 2.2 Physical SpecificationsNotes:1. Depending on the mounting orientation, drive performance may be affected at maximum temperatures. Please mount the drive to ensure that the temperature at the diskette jacket does not exceed that outlined in the media specifications.FDZ-529022 REV.A4- 5 -Chapter 3. InterfaceRefer to figure 3.6 for all interface connections.3.1 Interface Signals 3.1.1 Input signalsThe YD-702J has input lines as shown below.All lines are active (true) when “Low”(1)(2)(3)(4)(5)(6)(7)(8)DRIVE SELECT 0MOTOR ON DIRECTION SELECT STEP WRITE DATA WRITE GATE SIDE ONE SELECT MODE SELECT Table 3.1 Input Signals 3.1.1.1 DRIVE SELECT 0With the exception of the MOTOR ON signal, all the interface signals become valid when the DRIVE SELECT signal is set to low level.3.1.1.2 MOTOR ONWhen “MOTOR ON” is “Low” and a disk is inserted into the drive, the spindle motor will start. The spindle motor operates regardless of “DRIVE SELECT”. However if the disk is removed, the spindle motor will immediately stop.3.1.1.3 DIRECTION SELECTThis line determines the direction of read/write heads movement when the “STEP” line is pulsed.“HIGH” level Out(away from the center of the disk)“LOW” level In(toward the center of the disk)Table 3.2. DIRECTION SELECTAny change on this line must be done at least 1 usec.before the leading edge of the step pulse, and at least 1 usec. after the trailing edge of the step pulse.Refer to figure 8 for the timing information.3.1.1.4 STEPThis signal moves the read/ write heads in the direction defined by the “DIRECTION SELECT” signal.The access motion is initiated on each “LOW” to “HIGH”level transition, in other words, with the trailing edge of the signal pulse. In a seek operation, an 18 ms delay following the last “STEP” pulse is required for settling time before any read/write operation can be initiated.After direction switching, minimum 4 ms delay is required before initiating the next seek operation.Change of step pulse period during seek operation is not recommended for seek error.Refer to figure 1 for timing.Fig.3.1 Step3.1.1.5 WRITE DATAThe “WRITE DATA” line provides the data to be written on the disk. Each transition from “High” to “Low” onthe line causes the current through the read/ write heads to be reversed, thereby writing a data bit. This line is enabled when the “WRITE GATE” line is “Low” active.Refer to figures 3.2 and 3.11 for the timing information.FM RecordingMFM RecordingFig.3.2 WRITE DATA Notes:1.2.0 / 1.6 MB 1.0MB a 2.00us±10ns 4.00us±20ns b3.00us±15ns 6.00us±30ns c4.00us±20ns 8.00us±40ns d 150-1100ns 150-2100ns2. All timings indicate the values without write pre-compensation.3. The write precompensation value in 2.0MB is 125 ns on all tracks, and in other capacities as below:Capacity 2.0MB 1.6MB 1.0MB WPC value 125 ns 0-125 ns 0-250 ns4. The recommended condition during read operation is to not input “WRITE DATA”.3.1.1.6 WRITE GATEA “Low” active level on this line allows “WRITE DATA” to be written on the disk. A “High” inactive level enables read data logic and stepping logic. Refer to figure 3.11 for the timing information. Activation of “DRIVE SELECT”and “MOTOR ON”, changing “SIDE ONE SELECT” and/or activation of “STEP” must be delayed at least the values indicated (see the following READ RECOVERY TIME table 3.3) following deactivation of “WRITE GATE”because the erase heads remain active during this period.Capacity 2.0MB 1.6MB 1.0MB RRT MIN 650 us 590us 1000 us Table 3.3 Read Recovery TimeC C C Cdca C DDDC ca b dC: Clock D: Data3msMIN1usMINFDZ-529022 REV.A4- 6 -3.1.1.7 SIDE ONE SELECTThis line defines which side of a two sided disk will be used for reading or writing. A “High” level on this line selects the read/write head on side 0 surface on the disk. A “Low”level on this line selects the read/write head on the side 1surface. When switching heads, a 100 usec. delay is required before any read or write operation can be initiated.3.1.1.8 MODE SELECTThe YD-702J series has an internal circuit that performs the switching of the drive’s three (2.0/1.6/1.0MB) capacity modes.Please refer to below.Capacity Mode Switching Method Specifications3 Mode(2.0/1.6/1.0MB)Automatic Switching withInterface SignalThe drive is in 1.0MB mode with double density media and independent of the “MODE SELECT” signal (J1-13).If high-density media is inserted with the “MODE SELECT” signal is “LOW” when the drive is in 1.6MB mode.If high-density media is inserted with the “MODE SELECT” signal is “HIGH” when the drive is in 2.0MB mode.Table 3.4 MODE SELECT Notes:(1)To switch capacity mode is effected by a signal level on the “MODE SELECT” signal.(2)It is necessary to wait 0.5 sec. before executing a read/write operation after motor revolution speed is switched for capacity mode change. :READ DATA”, ”INDEX”, signals are inhibited to output during this term.Fig.3.3 Capacity Mode SwitchingFDZ-529022 REV.A4- 7 -3.1.2 Output signalsOutput signals are shown below. All lines are active when the “DRIVE SELECT” signal is “Low”.(1)TRACK 00(2)INDEX(3)HD(High: HD)(4)WRITE PROTECT (5)READ DATA (6)READY(7)DISK CHANGE Table 3.5 Output Signals 3.1.2.1 TRACK 00A “Low” active level on this line indicates that the read /write heads are positioned at track 00(the outermost track). The line goes “High” inactive when the heads are positioned elsewhere. Refer to Fig.3.8 for the timing information.3.1.2.2 INDEXOne index pulse is output at each revolution of the disk when the drive is ready to read/write. Normally this signal is at “High” level, and makes the transition to “Low” level when a pulse is generated. This signal is inhibited to output during seek and not ready. The controller should detect “INDEX” with the leading edge of the transition rather than with the signal level.Fig.3.4 INDEX3.1.2.3 WRITE PROTECTA “Low” active level on this line indicates that a disk with a write protect notch is loaded. During normal operation the drive will prevent writing when a protected disk has been inserted.3.1.2.4 READ DATAThis line provides the “READ DATA”(clock and data together) as detected by the drive electronics. Normally this signal is “High” level and becomes “Low” level for each flux reversal. The transition from “High” to “Low”level should be used for separation of data bits from read data. This signal is inhibited to output during seek and not ready. The different value between the leading edge of each bit pulse and its nominal position is below note 2.Timing characteristics are shown in figure 3.10.FM RecordingMFM RecordingFig.3.5 READ DATANotes:1.2.0/1.6MB 1.0MBa 2.00us NOM 4.00us NOM.b 3.00us NOM. 6.00us NOM.c 4.00us NOM.8.00us NOM.d 150-1100ns150-2100ns2.Capacity 2.0/1.6MB 1.0MB Difference±350ns±700ns3.1.2.5 DISK CHANGEThe “DISK CHANGE” signal indicates that the disk has been removed. This signal becomes “Low” after power has been applied to the drive and the disk has been removed.This signal remains active until the following conditions have satisfied:(1) A disk is correctly inserted;(2) A drive has been selected and a step pulse has been applied.C D C Cdca C DD D C ca b dC: Clock D: Data(166.7ms ±1.5%)200.0ms ±1.5%1~8msFDZ-529022 REV.A4- 8 -Fig.3.6 Interface Connection 3.1.3 Interface CircuitsThe YD-702J series uses open collector drivers as output line drivers, and TTL level gates as input line receivers.The input of each receiver is terminated in 20 k ohms pulled up to Vcc (+5V). Input/output circuit electrical specifications are as shown below.Inactive “High” Level 2.0 V to Vcc Active “Low” Level 0 to 0.8 V Input Impedance 20 k ohms pulled up to Vcc Table 3.6 Input Circuit Electrical Specifications Inactive “High” Level Open Active“Low” Level0 to 0.4VSink current: 6mA MAXTable 3.7 Output Circuit Electrical SpecificationsThe illustration below shows the recommended controller interface circuit.Fig 3.7 Interface CircuitTo connect the drives to the host system via a daisy chain,an FFC (Flexible Flat Cable) connection cable must be used. Refer to section 4.1.2 for this cable’s specifications.Also, because an FFC cable (as opposed to a conventional flat cable) is used, 2 FFC connectors are required in the host system.Caution: In the case where multiple drivers are connected in a daisy chain, it is forbidden to leave any drive unpowered.Each drive should receive power from the host system.3.1.3.2 Host System Terminal ResistorBecause the line driver of the drive is an open collector output, please use a terminal resistor (1k~5.6k Ω) on the host system side.Cable length 500mm MAXFDZ-529022 REV.A4- 9 -3.1.4 Timing3.1.4.1 Track 00 TimingFig.3.8 Track 00 Timing 3.1.4.2 Seek TimingIn order to reduce the peak current, we recommended that no seek operation be performed for 0.2 secondsafter motor start. Figure 3.9 shows the preferred timing.Fig.3.9 Seek Timing3.1.4.3 Read TimingNote:Capacity 2.0MB 1.6MB 1.0MB X us MIN 650 us 590 us 1000 usFig.3.10 Read Timing 3.1.4.4 Write TimingNote:Capacity 2.0MB 1.6MB 1.0MB X us MIN 650 us 590 us 1000 us Y us MAX4 us 4 us 8 usFig.3.11 Write TimingDIRECTlO STEP TRACK 002.9ms MAX 17us MAXMOTOR ONONDRlVEDIRECTlON SELECTSTEP0.5us MIN 1us MIN1us MIN1us MIN200 ms MIN3 ms MIN4 ms MIN3 ms MINONDRlVEMOTOR ONSTEPSIDE ONEREAD DATA (VALID)WRITE GATE500 ms MAX 18 ms MAX 100us MAX 100us MAXXus MAXVALIDVALIDONDRlVEWRITE GATEWRITE DATAMOTOR ONSTEPSIDE ONE500 ms MIN 18 ms MINYus MAX Yus MAX100us MIN Xus MINXus MINXus MINFDZ-529022 REV.A4- 10 -3.2 Power Interface3.2.1 P ower Supply Specifications VoltageOperating Mode TYP(mA)MAX(mA)Stand by 35Read 230350Write 230350+5VDC ±10%(Ripple: 100 mVp-p MAX)Seek550750Motor Start650740Peak Seek550830Table 3.8 Power Supply SpecificationsNotes:(1) “MAX” values reflect measurement taken at maximum voltage; “TYP” values reflect measurement taken at nominal voltage.(2) “Standby” refers to the state where all input signals are inactive.(3) “Read” and “Write” refer to the state where the heads are at track 40, side 1 and the In Use Lamp is on.(4) “Seek” refers to the average current with the drive continuously seeking at 3 ms and the spindle motor rotating.(5) When the spindle motor starts, “Motor Start” current will continue for approximately 200 ms.(6) Peak current of “Seek” refers to the state of maximum seek current when the spindle motor is rotating and the heads are stepping at 6 ms.The above specifications must be met when voltages are measured at power connector on PWB.3.2.2 C urrent Waveform5 V DC (TYP)MOTOR STARTSTAND BYSTAND BYSEE READ READ WRlTE[mA]1000800600400200Fig.3.12 Current WaveformChapter 4. Physical InterfaceThis drive is connected to the host system by one type of connectors.The cable connections are illustrated in figure4.1 Signal Connector and cable (J1/P1)4.1.1 J1 Signal ConnectorThe J1 Signal connector is 26pin FFC connector located at the rear of the drive.Standard:ZIF TYPE (SMK Model CFP5126-0501 or equivalent)Unit: mm Fig 4.2 J1 Signal Connector Dimensions 4.1.2 P1 CableA P1 cable connector is used to connect the J1 signal connector to the system interface.Recommended PartsFFC: •Sumitomo Electric Industries LTD’s ”sumi”card SMCD-26•Eikura Communication’s ET-C100-264.1.3 Frame GroundThe internal circuit ground on the PWB has beenconnected with the frame for shielding purposes. Theframe ground of the system will be connected to thesignal ground through the drive when the drive isinstalled into the system.The frame ground and signal ground of the systemhave to be connected except the drive.Otherwise the drive ought to be floated from the frameground of the system.4.2 Connector Pin Assignments4.2.1. Signal Connector Pin AssignmentsSignal Pin#Signal name24678910111213141618202224261,3,515~25(Odd No. pins)INDEXDRIVE SELECT 0DISK CHANGEN.C.READYHD (High: HD)MOTOR ONN.C.DIRECTION SELECTMODE SELECTSTEPWRITE DATAWRITE GATETRACK 00WRITE PROTECTREAD DATASIDE ONE SELECT+5VGNDTable 4.1 Signal Connector Pins4.3 TerminatorsAll input lines on the drive are terminated with non-removable resistors of 20k ohms.Hostsystem Drive 0Fig 4.1 Cable ConnectionsDrive 1P1J1P1J1Chapter 5. DiagramsFig.5.1 Mechanical DimensionsRecommended angle of the drive when the drive is installed is less than +30 degrees.Fig.5.2 Recommended Mounting21+/-0.490+/-0.210.91.712.7+/-0.22.5+/-0.2M2.6 tapped holes for installation depth 2.2Max(Each side x2)Eject buttonDisk LED(OPTION)2632.51196+/-0.2126+/-0.4Eject button position5+/-1 (Disk inserted)0.6+/-0.6 (Disk ejected)21+/-0.490+/-0.22.5+/-0.22729.696+/-0.2Signal connector(units:mm)Pin 1insertion32.5NOTES 1) GENERAL TOLERANCES ARE +/-0.596+/-0.2Tapping FaceZ( x4)Z 90.7+/-0.53.6+/-0.53.6+/-0.593.4+/-0.52.6+/-0.53.6+/-0.545.45+/-0.345.45+/-0.396+/-0.221+/-0.42.5+/-0.55+/-0.50+/-0.345.1 Caution on Mounting1)Mounting screws should be tightened by 0.2Nm{2kgf-cm} in torque.2)Mounting bracket is recommended not to make contact with the drive except the mounting spots, and should notbe designed that any portion on the drive except the mounting spots is pressed and/or crushed.3)Recommended to fasten the drive at 3 mounting spots with screws (4 spots available).4)Mounting bracket should be provided structure to absorb strain.5)The drive should be separated or shielded from noise sources. Do not strain the drive. Do not install the drive inlarge electromagnetic fields. Otherwise, failure may result.Not to exceed 5 mm Depth to be at exceed 0.5 mmSide mounting plateSide Mounting(Example 1)FDDFDDFDDThickness not exceed 1 mm Depth to be at exceed 0.5 mmSide mounting plateThickness not exceed 1 mmSide mounting plateThickness not exceed 1 mmFig.5.3 Caution on Mounting Washer dimensionsDiameter not to exceed 5 mm Thickness to be at least 0.5 mmNot to exceed 5 mm Side Mounting(Example 2)Side Mounting(Example 3)5.2 Caution on handling1)Strong vibration and shock can damage the drive. Itmay cause an error. Do not use or store the drive under such conditions.2)We recommend handling the drive on side frame,portion of mounting spots, of the drive as well as possible. If you handle like pressing the top or the bottom of the drive, it may cause damage of heads and PWB.3)Do not disassemble the drive by yourself because ofan adjusted product. If you do so, we can not assure you of adjusted accuracy.Chapter 6. Other Functional Characteristics6.1 Standby ModeThe YD-702J includes standby mode to reduce the load on the host system power supply when the drive is not actually in use. When the spindle motor stops, power to the read/write and spindle motor control systems is cut off, and power to the stepper is cut off when the stepper is not seeking.As a result of this built in power conservation, when all the interface input signals are inactive, typical drive power consumption is 15mW.6.2 In UseThe IN USE lamp will turn on when DRIVE SELECT is at low level and turn off when it is high.6.3 Mask Function“READ DATA” and “INDEX” signals are inhibited to output during seek (includes 18 ms MAX after the last step pulse) and not ready (500 ms MAX after motor start).6.4 Automatic Motor On/OffWhen the disk is inserted or removed, the spindle motor is controlled as follows:1)When the disk is inserted, the spindle motor willstart to rotate regardless of the “MOTOR ON” signal condition. The spindle motor will stop approximately 400 ms later if the “MOTOR ON” signal is not active, but will continue to rotate if it is active.2)When the disk is removed, the spindle motor willstop.。

ssd 基本知识

ssd 基本知识SSD基本知识随着科技的不断进步,固态硬盘(Solid State Drive,简称SSD)已经成为了越来越多人选择的存储设备。

相比传统的机械硬盘,SSD具有更快的读写速度、更低的能耗以及更高的可靠性。

在本文中,我们将介绍一些关于SSD的基本知识。

一、什么是SSD?SSD是一种使用非易失性存储芯片作为存储介质的硬盘。

与机械硬盘使用的旋转磁盘不同,SSD使用的是闪存芯片来存储数据。

闪存芯片由许多存储单元组成,每个存储单元可以存储多个位的数据。

SSD的存储单元通常是基于快门效应(Floating Gate Effect)或电荷效应(Charge Trap)。

二、SSD的优点1. 速度快:相比机械硬盘,SSD的读写速度更快。

这主要得益于闪存芯片的工作原理,它可以直接读取和写入数据,而无需进行机械运动。

2. 耐用性好:与机械硬盘相比,SSD没有机械部件,因此更耐用。

机械硬盘可能会因为磁头碰撞等原因导致数据丢失,而SSD不会受到这些问题的困扰。

3. 能耗低:由于没有机械运动,SSD的能耗通常比机械硬盘低。

这不仅有助于延长笔记本电脑的电池寿命,还可以减少能源消耗。

4. 噪音小:由于没有机械运动,SSD的工作时几乎没有噪音。

这对于那些对静音环境有要求的用户来说是一个重要的考虑因素。

三、SSD的缺点1. 价格高:与机械硬盘相比,SSD的价格通常较高。

这主要是由于闪存芯片的成本较高。

2. 容量较小:与机械硬盘相比,SSD的容量通常较小。

虽然随着技术的进步,SSD的容量不断增加,但相对于机械硬盘而言,仍然有限。

3. 寿命有限:虽然SSD的耐用性较好,但它们的寿命有限。

这主要是由于闪存芯片的擦写次数限制。

然而,随着技术的进步,SSD的寿命也在不断改善。

四、SSD的应用领域由于SSD的优点,它们在许多领域得到了广泛应用。

下面是一些常见的应用领域:1. 个人电脑:越来越多的人选择在个人电脑中使用SSD作为系统盘。

英特尔快速存储技术

英特尔快速存储技术

第一篇:英特尔快速存储技术

英特尔快速存储技术(Intel Optane Memory)是英特尔公司专为固态硬盘和传统硬盘设计的一种存储加速技术。

它通过将高速闪存与硬盘组合使用,提供更快速的读写速度和数据访问速度,从而大大加快计算机的启动速度、应用程序响应速度以及文件传输速度等。

以下是英特尔快速存储技术的特点:

1.高速读写:英特尔快速存储技术采用了3D XPoint 闪存,拥有比传统 NAND 闪存更快的读写速度。

2.容量大:英特尔快速存储技术的容量可以达到32 GB,足够把操作系统和常用应用程序都存储在其中,充分发挥高速读写的优势。

3.支持固态硬盘和传统硬盘:英特尔快速存储技术不仅可以用于固态硬盘的存储加速,也可以用于传统硬盘的存储加速。

用户只需要将英特尔快速存储技术插入主板上的 M.2 插槽中,然后通过英特尔 Rapid Storage Technology 软件设置即可。

4.易于安装:英特尔快速存储技术使用标准的 M.2 接口,安装起来非常简单,一般用户也可以很容易地完成安装。

5.兼容性强:英特尔快速存储技术可以与任何支持 SATA 硬盘的计算机兼容,不需要改变原始系统的设置,兼容性异常强。

总的来说,英特尔快速存储技术的读写性能非常强劲,可以让计算机的读写速度得到极大的提升。

如果你是一名对计

算机性能有要求的用户,那么英特尔快速存储技术或许可以满足你的需求。

SSD1289中文手册

- GD = ‘0’, G0 is 1st output Gate, Gate sequence G0, G1, G2, G3, …, G318, G319 - GD = ‘1’, G1 is 1st output Gate, Gate sequence G1, G0, G3, G2, …, G319, G318

动电路。当一个像素点=18 位时,262144 种可能的颜色可以被显示。

增压器和稳压电路 这两个功能块产生 VGH, VGOFFL, VCOM levels 和操作 LCD 所必须的

Vlcd0~63 所需电压。

震荡电路 这个模块是一个片上的低能耗的 RC 震荡电路。此震荡电路为 DC-DC 电平转

换电路提供时钟。这个时钟也用于提供显示时钟。

SSD1289 嵌入了 DC-DC 变压器和电压转换器,用于提供芯片驱动所有外部底 层元件所必需的电压。芯片包含的一个通用电压发生电路用于驱动 TFT 显示器的 反电极。另外还有一个整合的伽马控制电路,用于配合软指令以提供最大的灵活 性和最佳的显示效果。

DS1289 工作的最低电压能低到 1.16V,同时提供不同的节电模式。它适用于 任何需要长时间运行的,用便携式电池驱动的紧凑型设备。 2 特点 工作电压:VDD = 1.65V-1.95V (不规则的逻辑输入)

4 页要显示的数据形成一个 RAM 地址块存储在 GDDRAM 中。每个地址块将形 成基本的滚动地址单元。多种类型的区域滚动可以由软件根据命令“Set area Scroll” and “Set Scroll Start”设置。

Gamma(γ)/Grayscale(灰度级)电压发生器 灰度级电压电路根据灰度级γ调整电阻所设定的灰度等级产生一个 LCD 驱

SSD硬盘详细介绍

SSD硬盘详细介绍SSD(Solid State Drive)硬盘是一种使用闪存存储芯片作为存储介质的硬盘,相对于传统的机械硬盘,SSD具有更快的读写速度、更低的延迟、更小的体积和重量、更低的能耗等优点,被广泛应用于计算机、移动设备等领域。

SSD硬盘的闪存存储芯片可以分为两种类型:SATA(Serial ATA)接口和NVMe(Non-Volatile Memory Express)接口。

SATA接口是一种较早的接口标准,传输速度较低,适用于普通计算机用户需求;而NVMe接口是一种更先进的接口标准,传输速度更快,适用于高性能计算环境。

SSD硬盘的读写速度是其最大的优点之一、相比于传统的机械硬盘,SSD硬盘的数据读取速度可以提高数倍,大大加快了计算机的启动速度和文件传输速度。

这是因为SSD硬盘使用的是闪存存储芯片,可以实现随机读写访问,而不需要机械硬盘的磁头寻道操作。

另外,SSD硬盘还具有更低的延迟。

延迟是指数据读取操作的等待时间,传统机械硬盘由于需要进行机械部件的移动操作,延迟较高。

而SSD 硬盘不需要进行机械操作,可以随时随地进行数据读写,延迟较低,提高了计算机的响应速度。

SSD硬盘的体积和重量也相对较小,适用于移动设备的应用。

传统机械硬盘由于需要机械结构,体积和重量较大,不适合携带。

而SSD硬盘的体积和重量较小,可以轻松地携带在口袋或者电脑包中,满足用户对移动存储的需求。

此外,SSD硬盘的能耗较低。

传统机械硬盘需要靠电机驱动来进行机械操作,因此能耗较高。

而SSD硬盘没有机械结构,只需要靠电子元件来操作,能耗较低,延长了电池的寿命,适用于依赖电池供电的移动设备。

然而,SSD硬盘也有一些缺点需要注意。

首先,SSD硬盘的价格较高,相比传统机械硬盘,价格要贵一些。

其次,SSD硬盘的寿命相对较短,写入次数有限,长时间大量写入数据可能会影响其性能和寿命。

另外,SSD硬盘的存储容量相对较小,目前最大容量一般在2TB左右,无法满足一些大容量存储需求。

ssd方案

ssd方案SSD方案简介SSD(Solid State Drive)是一种使用了闪存存储芯片来代替传统硬盘驱动器的存储解决方案。

相比于传统的机械硬盘,SSD具有更快的数据访问速度、更低的能耗和更高的耐用性。

本文将介绍SSD方案的基本工作原理、优势和应用领域。

工作原理SSD内部包含一系列闪存存储芯片和一个控制器。

控制器负责管理和组织闪存芯片,以实现数据的读取、写入和擦除操作。

SSD的闪存芯片由多个存储单元组成,每个存储单元可以存储多个比特的数据。

数据的读取和写入是通过电压的变化来实现的,而数据的擦除是通过抹去存储单元中的电荷来实现的。

SSD的控制器使用一系列算法来管理和优化数据的读取、写入和擦除。

其中包括垃圾回收、均衡负载和错误纠正等功能。

垃圾回收是指将被删除的数据擦除并标记为可重用状态,以便新的数据可以写入。

均衡负载是指将数据均匀地分布在闪存芯片上,以提高读取和写入的性能。

错误纠正是指通过检测和纠正闪存芯片中的错误位来保证数据的可靠性。

优势相比传统的机械硬盘,SSD具有以下优势:1. 高速读写:由于使用了闪存存储芯片,SSD的数据访问速度比机械硬盘快得多。

这意味着在使用SSD的计算机上,操作系统的启动时间更短,应用程序的响应时间更快。

2. 低能耗:SSD不需要机械部件来读取和写入数据,因此能耗更低。

这不仅有助于延长电池寿命,还可以降低计算机的能耗。

3. 耐用性强:机械硬盘的读写是通过磁头接触到磁盘上的表面来实现的,所以容易受到震动和碰撞的影响。

而SSD是没有机械部件的,所以更加耐用。

4. 静音运行:机械硬盘在读写数据时产生噪音,而SSD在读写数据时完全静音。

应用领域由于其优势,SSD在多个领域得到了广泛应用,包括:1. 个人计算机:越来越多的个人计算机选择使用SSD来提升系统性能和响应速度。

2. 服务器和数据中心:SSD可以显著提高服务器和数据中心的存储和访问性能,满足大规模数据处理的需求。

3. 移动设备:SSD在移动设备中的应用也越来越普遍,因为它们可以提供更快的启动时间和应用程序响应速度,并且可以更好地适应移动设备的小尺寸和轻量性要求。

Parker SSD Drives PMAC电机Alignment for C005 Pos Fbk

Application NoteC005 Pos Fbk Alignment for PMAC motorsHA502487C005_002AC30P/D V2.13 onwardsCopyright 2018 Parker SSD Drives, a division of Parker Hannifin Ltd.All rights strictly reserved. No part of this document may be stored in a retrieval system, or transmitted in any form or by any means to persons not employed by a Parker SSD Drives company without written permission from Parker SSD Drives, a division of Parker Hannifin Ltd . Although every effort has been taken to ensure the accuracy of this document it may be necessary, without notice, to make amendments or correct omissions. Parker SSD Drives cannot accept responsibility for damage, injury, or expenses resulting therefrom.iRequirementsIntended UsersThis Application Note is to be made available to all persons who are required to install,configure or service equipment described herein, or any other associated operation.The information given is intended to enable the user to obtain maximum benefit from theequipment.Application AreaThe equipment described is intended for industrial motor speed control utilising AC induction orAC synchronous machines.PersonnelInstallation, operation and maintenance of the equipment should be carried out by qualifiedpersonnel. A qualified person is someone who is technically competent and familiar with allsafety information and established safety practices; with the installation process, operation andmaintenance of this equipment; and with all the hazards involved.HazardsRefer to the Safety Information given at the front of the Product Manual supplied with everyParker SSD Drives product.iiC005P OS F BK A LIGNMENT FOR PMACM OTORSAbstractThis Application Note gives information and how to use the Pos Fbk Alignment feature to align position frommotor feedback to the PMAC motor back EMF. This is required to run the PMAC motor in Vector Control mode. Pre-RequisiteThe pre-requisites are :- a AC30 drive- a feedback attached to the motor with the associated feedback option fitted into the drive.Parameters described below are part of PMAC Motor Data and Pos Fbk Aligmnent. IntroductionBy definition, the motor Vector Control is based on the assumption that the back EMF is crossing the 0V line in a positive direction when the electrical position is also crossing the 0° line in a positive way. Another requirement is to insure a positive ‘encoder/resolver’ rotation with a positive electrical motor rotation ( U, V, W ).1The Pos Fbk Alignment feature is used to automatically calculate any offset between the Zero encoder absolute position and the motor back EMF, as well as selecting the correct wiring of the motor ( U, V, W sequence ) with the encoder position.The feature needs to be run at least once with a PMAC motor associated to an absolute encoder type.The feature needs to be run after each power cycle with a PMAC motor associated to a relative encoder type (pulse encoder for example ). In that case, the absolute position information is lost by the power cycle and thealignment is required after power ON.The feature is run on a motor free to rotate, no load attached to the motor shaft.Regardless of the Alignment Method selected, the motor should move during the sequence.Pos Fbk Alignment operation2 Methods can be selected to align feedback and motor.Alignment Method = MANUALThe motor is moved to an electrical position corresponding to the motor phase selected by Alignment On Motor parameter.This electrical position depends on the PMAC Wiring type selected and on the real motor phase wiring.PMAC Encoder Offset is calculated by looking at real position from the active encoder compared to theoretical position where the motor is.So, it depends also on the encoder settings ( inverted or not ).For standard connections ( correct U, V, W motor wiring sequence and position from encoder varying in a positive way looking at the motor front shaft ), position offset is extracted and written back into PMAC Encoder Offset.Correct connection of the encoder means that a clockwise rotation of the motor front shaft equals a positiveposition variation.Correct motor wiring means phase U, V, W rotating in a correct sequence for a clock wise rotation of the motor front shaft.Considering a standard connection, the following table gives possible encoder and PMAC Wiring settings and results on speed control :** Looking the front shaft of the motor23*** The motor is uncontrolled. It could overspeed, be stalled, or running at constant speed without any control.Alignment Method = AUTOMATICIn case of a correct wiring of encoder and/or motor phases, the sequence is as follows :Current%Elec pos 1 2 3 4 5 6 7 8 9 10 11 12States 210°-30°90°During the final state ( 11 ) , the Alignment Offset is automatically calculated and is passed back to 1808 PMAC Encoder OffsetAlso 1809 PMAC Wiring is set to STANDARDIn the case of a wrong wiring of encoder and/or motor phases, the sequence is as follows :Current%Elec pos 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18States 210°-30°90°From State 4 to 9, a wrong direction as been detected, and the direction should be reverted. Alignment Direction is set to REVERSE.During the final state ( 17 ), the Alignment Offset is automatically calculated and is passed back to 1808 PMAC Encoder OffsetAlso 1809 PMAC Wiring is set to REVERSE.In that case, the direction of motor rotation has been changed during the Pos Alignment sequence. Please verify if the new direction is compatible with your application.If you want to change it, please change the Invert parameter of the active encoder used to control the motor and run again the Pos alignment sequence.Setting up Alignment Method = DIRECTION TEST allows to verify the direction of positive electrical position by slowly rotating the motor. A correct wiring of the motor phases should turn the motor in a clockwise direction looking at the front shaft of the motorThe motor is slowly rotated with the following sequence U, V, W, U, V, W…..It allows to verify the rotation direction and detect any wiring inversion on the motor phases.Active encoder Invert parameter has no effect during this test.Looking at the position variation from the active encoder may help to know if the active encoder is correctlywired.Considering a correct connection of the motor phases :When running this Method, either set 1257 Seq Stop Method to DISABLE VOLTAGE or 0505 Zero SpeedThreshold to 1% otherwise you may end up with a motor rotating at slow speed for 60s without any possibility to stop it.Running the sequenceThe feature is run on a motor free to rotate, no load attached to the motor shaft.Regardless of the Alignment Method selected, the motor should move during the sequence.The sequence is validated by Alignment Enable input.The drive waits for a START/TORQUE ON condition to start the cycle.The sequence can be stopped by a STOP/TORQUE OFF command anywhere during the cycle.A successful sequence sets Alignment Ended = TRUE.A STOP/TORQUE OFF command is needed to stop the sequence.If Alignment Method is set to AUTOMATIC, it is possible that the direction of motor rotation for apositive setpoint could be reversed. The parameter PMAC Wiring can be changed by the sequence ifan incompatibility of direction between the encoder and the motor phases wiring is found.Alignment on Power OnAs the feature needs to be run after each power cycle with a PMAC motor associated to a relative encoder type ( pulse encoder for example ), a parameter 1796 Alignment On Power On xould bet set up to TRUE.4Set to TRUE, it automatically trips the drive after a power up on a Start command until an Alignment sequence is run and completed successfully.ApplicationBelow is a simple example on how to force the system to run a Pos Alignment sequence on the first start after power_up :Alignment On Power On has been set to TRUEAlignment Method is set to Manual ( It could have been set to AUTOMATIC ).Alignment Enable is TRUE from Start-up.The first start command will run the Pos Alignment sequence.A running and successfully sequence resets Alignment_Enable to FALSE.A 1s negative pulse is generated at the end of the sequence ( positive at Q output of TP_1). This information can be used to toggle any command to start the system.The feature is run on a motor free of rotation, no load attached to the motor shaft.Depending of the Alignment Method selected, the motor is moving during the sequence.56。

MEMORY存储芯片MT29F32G08CBACAWP-ITZ中文规格书

Feature OperationsThe SET FEATURES (EFh) and GET FEATURES (EEh) commands are used to modify the target's default power-on behavior. These commands use a one-byte feature address to determine which subfeature parameters will be read or modified. Each feature address (in the 00h to FFh range) is defined in below. The SET FEATURES (EFh) command writes subfeature parameters (P1–P4) to the specified feature address. The GET FEA-TURES command reads the subfeature parameters (P1–P4) at the specified feature ad-dress.When a feature is set, by default it remains active until the device is power cycled. It is volatile. Unless otherwise specified in the features table, once a device is set it remains set, even if a RESET (FFh) command is issued. GET/SET FEATURES commands can be used after required RESET to enable features before system BOOT ROM process.Internal ECC can be enabled/disabled using SET FEATURES (EFh). The SET FEATURES command (EFh), followed by address 90h, followed by four data bytes (only the first da-ta byte is used) will enable/disable internal ECC.The sequence to enable internal ECC with SET FEATURES is EFh(cmd)-90h(addr)-08h(data)-00h(data)-00h(data)-00h(data)-wait(t FEAT).The sequence to disable internal ECC with SET FEATURES is EFh(cmd)-90h(addr)-00h(data)-00h(data)-00h(data)-00h(data)-wait(t FEAT). The GET FEATURES command is EEh.Table 13: Feature Address Definitions4Gb, 8Gb, 16Gb: x8, x16 NAND Flash Memory Feature OperationsPDF: 09005aef83b25735m60a_4gb_ecc_nand.pdf – Rev. M 2/12 ENTable 14: Feature Address 90h – Array Operation ModeNote: 1.These bits are reset to 00h on power cycle.SET FEATURES (EFh)The SET FEATURES (EFh) command writes the subfeature parameters (P1–P4) to the specified feature address to enable or disable target-specific features. This command is accepted by the target only when all die (LUNs) on the target are idle.Writing EFh to the command register puts the target in the set features mode. The target stays in this mode until another command is issued.The EFh command is followed by a valid feature address. The host waits for t ADL before the subfeature parameters are input. When the asynchronous interface is active, one subfeature parameter is latched per rising edge of WE#.After all four subfeature parameters are input, the target goes busy for t FEAT. The READ STATUS (70h) command can be used to monitor for command completion.Feature address 01h (timing mode) operation is unique. If SET FEATURES is used to modify the interface type, the target will be busy for t ITC.Figure 30: SET FEATURES (EFh) OperationCycle type R/B#4Gb, 8Gb, 16Gb: x8, x16 NAND Flash Memory Feature OperationsPDF: 09005aef83b25735m60a_4gb_ecc_nand.pdf – Rev. M 2/12 ENGET FEATURES (EEh)The GET FEATURES (EEh) command reads the subfeature parameters (P1–P4) from thespecified feature address. This command is accepted by the target only when all die(LUNs) on the target are idle.Writing EEh to the command register puts the target in get features mode. The targetstays in this mode until another valid command is issued.When the EEh command is followed by a feature address, the target goes busy for t FEAT.If the READ STATUS (70h) command is used to monitor for command completion, theREAD MODE (00h) command must be used to re-enable data output mode.After t FEAT completes, the host enables data output mode to read the subfeature pa-rameters.Figure 31: GET FEATURES (EEh) OperationCycle type I/OxR/B#4Gb, 8Gb, 16Gb: x8, x16 NAND Flash MemoryFeature OperationsPDF: 09005aef83b25735m60a_4gb_ecc_nand.pdf – Rev. M 2/12 EN。

SSD存储介绍

SSD存储介绍SSD(Solid State Drive)是一种使用闪存芯片作为数据储存介质的储存设备,相比传统的机械硬盘(HDD),它具有更快的读写速度、更低的能耗和更高的可靠性。

SSD的存储介质是闪存芯片,而传统的机械硬盘则是通过磁头读写磁盘上的磁性涂层来完成数据的读写操作。

这使得SSD的读写速度比机械硬盘快得多,可以达到数倍甚至数十倍的提升。

SSD的读写速度对于访问大量小文件的场景,如操作系统启动和应用程序的加载,有着明显的优势。

此外,SSD也具有更低的访问延迟,能够更快地响应用户的操作。

SSD还具有更低的能耗。

相比机械硬盘的电机驱动和磁盘旋转,SSD只需要芯片内部的电子信号传输和存储,功耗更低。

在笔记本电脑和移动设备中,SSD的低功耗可以延长电池寿命,提供更长久的使用时间。

同时,SSD的低功耗也减少了储存设备在运行时产生的热量,能够更好地保护设备内部的其他部件。

SSD的可靠性也比机械硬盘更高。

机械硬盘在读写时需要磁头与磁盘之间的物理接触,容易造成磁头脱落、磁盘刮伤等问题,从而导致数据的丢失。

而SSD则没有机械部件,不存在这些问题。

此外,SSD还具有更好的抗震性能,即使在剧烈震动或者意外撞击的情况下,也能保持数据的完整性。

SSD的存储介质是闪存芯片,根据内部存储介质的不同,可以分为三种类型:SLC(Single-Level Cell)、MLC(Multi-Level Cell)和TLC (Triple-Level Cell)。

SLC的闪存芯片一次只能存储一个二进制数据,稳定性和读写速度最高,但成本也最高;MLC的闪存芯片一次可以存储多个二进制数据,读写速度较SCL慢一些,但成本相对较低;TLC的闪存芯片可以存储更多的二进制数据,读写速度最慢,但是成本也最低。

一般来说,SLC适用于高性能和高可靠性的应用场景,如服务器和数据中心;MLC适用于台式机和笔记本电脑等常见应用场景;TLC则主要用于较低价位的储存设备。

SSD1339Z资料

This document contains information on a new product. Specifications and information herein are subject to change without notice. SSD1339 Rev 1.1 P 1/59 Jul 2005 Copyright 2005 Solomon Systech LimitedAdvance Information132RGB x 132 with 2 smart Icon lines Dot Matrix OLED/PLED Segment/Common Driver with ControllerSSD1339TABLE OF CONTENTS1. GERENAL DESCRIPTION (5)2. FEATURES (5)3. ORDERING INFORMATION (6)4. BLOCK DIAGRAM (7)5. DIE PAD FLOOR PLAN (8)6. PIN DESCRIPTION (15)7. FUNCTIONAL BLOCK DISCRIPTIONS (19)O SCILLATOR C IRCUIT AND D ISPLAY T IME G ENERATOR (19)R ESET C IRCUIT (19)C OMMAND D ECODER AND C OMMAND I NTERFACE (20)MPU P ARALLEL 6800-SERIES I NTERFACE (20)MPU P ARALLEL 8080-SERIES I NTERFACE (20)MPU S ERIAL I NTERFACE (21)G RAPHIC D ISPLAY D ATA RAM (GDDRAM) (22)G RAY S CALE AND G RAY S CALE T ABLE (26)C URRENT C ONTROL AND V OLTAGE C ONTROL (27)S EGMENT D RIVERS/C OMMON D RIVERS (27)DC-DC V OLTAGE C ONVERTER (28)8. COMMAND TABLE (29)9. COMMAND DESCRIPTIONS (34)10. MAXIMUM RATINGS (47)11. DC CHARACTERISTICS (48)12. AC CHARACTERISTICS (49)13. APPLICATION EXAMPLE (53)14. PACKAGE INFORMATION (54)SSD1339U3 P IN A SSIGNMENT (54)SSD1339U3 COF DETAILS DIMENSIONS (56)Solomon Systech Jul 2005 P 2/59 Rev 1.1 SSD1339TABLE OF FIGURESF IGURE 1 – B LOCK D IAGRAM (7)F IGURE 2 – SSD1339Z PIN ASSIGNMENT (8)F IGURE 3 – SSD1339Z ALIGNMENT MARK DIMENSIONS (13)F IGURE 4 – D IE TRAY INFORMATION (14)F IGURE 5 – O SCILLATOR C IRCUIT (19)F IGURE 6 – D ISPLAY DATA READ BACK PROCEDURE - INSERTION OF DUMMY READ (20)F IGURE 7 – D ISPLAY DATA WRITE PROCEDURE IN SPI MODE (21)F IGURE 8 – G RAPHIC D ISPLAY D ATA RAM S TRUCTURE (22)F IGURE 9 – 262K COLOR DEPTH DATA WRITING SEQUENCE IN 18-BIT MCU INTERFACE (22)F IGURE 10 – 262K COLOR DEPTH DATA WRITING SEQUENCE IN 16-BIT MCU INTERFACE IN O PTION 1 (23)F IGURE 11 – 262K COLOR DEPTH DATA WRITING SEQUENCE IN 16-BIT MCU INTERFACE IN O PTION 2 (23)F IGURE 12 – 262K COLOR DEPTH GRAPHIC DISPLAY DATA WRITING SEQUENCE IN 9-BIT MCU INTERFACE (23)F IGURE 13 – 262K COLOR DEPTH GRAPHIC DISPLAY DATA WRITING SEQUENCE IN 8-BIT MCU INTERFACE (23)F IGURE 14 – 65K COLOR DEPTH GRAPHIC DISPLAY DATA WRITING SEQUENCE IN 16-BIT MCU INTERFACE (23)F IGURE 15 – 65K COLOR DEPTH GRAPHIC DISPLAY DATA WRITING SEQUENCE IN 8-BIT MCU INTERFACE (24)F IGURE 16 – D ISPLAY DATA RAM WRITING POSITION FOR COLOR A, B AND C DATA INPUT IN 65K COLOR MODE (24)F IGURE 17 – D ISPLAY DATA RAM WRITING POSITION FOR COLOR A, B AND C DATA INPUT IN 256 COLOR MODE (25)F IGURE 18 – R ELATION BETWEEN GRAPHIC DATA RAM VALUE AND GRAY SCALE TABLE ENTRY FOR THREE COLORS26 F IGURE 19 – I LLUSTRATION OF RELATION BETWEEN GRAPHIC DISPLAY RAM VALUE AND GRAY SCALE CONTROL (27)F IGURE 20 – E XAMPLE OF COLUMN AND ROW ADDRESS POINTER MOVEMENT (34)F IGURE 21 – A DDRESS POINTER MOVEMENT OF HORIZONTAL ADDRESS INCREMENT MODE (35)F IGURE 22 – A DDRESS POINTER MOVEMENT OF VERTICAL ADDRESS INCREMENT MODE (35)F IGURE 23 – E XAMPLE OF SET DISPLAY START LINE WITH NO REMAP (37)F IGURE 24 – E XAMPLE OF SET DISPLAY OFFSET WITH NO REMAP (37)F IGURE 25 – E XAMPLE OF GAMMA CORRECTION BY GRAY SCALE TABLE SETTING (39)F IGURE 26 – S EGMENT OUTPUT CURRENT FOR DIFFERENT CONTRAST CONTROL AND MASTER CURRENT SETTING (41)F IGURE 27 – E XAMPLE OF DRAW LINE COMMAND (42)F IGURE 28 – E XAMPLE OF DRAW RECTANGLE COMMAND (42)F IGURE 29 – E XAMPLE OF DRAW CIRCLE COMMAND (43)F IGURE 30 – E XAMPLE OF COPY COMMAND (44)F IGURE 31 – E XAMPLE OF COPY + CLEAR = M OVE COMMAND (45)F IGURE 32 – 6800-SERIES MPU PARALLEL INTERFACE CHARACTERISTICS (50)F IGURE 33 – 8080-SERIES MPU PARALLEL INTERFACE CHARACTERISTICS (51)F IGURE 34 – S ERIAL INTERFACE CHARACTERISTICS (52)F IGURE 35 – A PPLICATION EXAMPLE FOR 8-BIT 6800-PARALLEL INTERFACE MODE (53)F IGURE 36 - SSD1339U3 PIN ASSIGNMENT (54)F IGURE 37 - SSD1339U3 DETAIL DIMENSIONS (56)SSD1339Rev 1.1 P 3/59 Jul 2005 Solomon SystechLIST OF TABLEST ABLE 1 – O RDERING I NFORMATION (6)T ABLE 2 – SSD1339Z D IE P AD C OORDINATES (9)T ABLE 3 – C OMMAND TABLE (29)T ABLE 4 –G RAPHIC ACCELERATION COMMAND (32)T ABLE 5 – R ESULT OF CHANGE OF BRIGHTNESS BY DIM WINDOW COMMAND (44)T ABLE 6 – M AXIMUM RATINGS (47)T ABLE 7 – DC CHARACTERISTICS (48)T ABLE 8 – AC CHARACTERISTICS (49)T ABLE 9 – 6800-S ERIES MPU PARALLEL INTERFACE TIMING CHARACTERISTICS (50)T ABLE 10 – 8080-S ERIES MPU PARALLEL INTERFACE TIMING CHARACTERISTICS (51)T ABLE 11 –S ERIAL INTERFACE TIMING CHARACTERISTICS (52)T ABLE 12 - SSD1339U3 PIN ASSIGNMENT (55)Solomon Systech Jul 2005 P 4/59 Rev 1.1 SSD13391. GERENAL DESCRIPTIONThe SSD1339 is a single-chip CMOS OLED/PLED driver with controller for organic/polymer light emitting diode dot-matrix graphic display system. It consists of 396 segments (132RGB), 132 commons and 2 smart icon lines. This IC is designed for Common Cathode type OLED panel.The SSD1339 displays data directly from its internal 132x133x18 bits Graphic Data RAM (GDDRAM).Data/Commands are sent from general MCU through the hardware selectable 6800/8000 seriescompatible Parallel Interface or Serial Peripheral Interface. It has a 256 steps contrast control and 262kcolor control2. FEATURES! Support max. 132RGB x 132 matrix panel + icon line! Power supply: VDD=2.4-3.5VVDDIO=1.5V - 3.5VVCC=7.0V - 18.0V! OLED driving output voltage, 16V maximum! DC-DC voltage booster controller! Segment maximum source current: 200uA! Common maximum sink current: 80mA! Embedded 132x133x18 bit SRAM display buffer ! 16 step master current control, and 256 step current control for the three color components! Smart Icon mode! Programmable color mode of 256, 65k, 262k! Programmable Frame Rate! Graphic Acceleration Command Set (GAC)! 8/9/16/18-bit 6800-series Parallel Interface, 8/9/16/18-bit 8080-series Parallel Interface and Serial Peripheral Interface.! Wide range of operating temperature: -40 to 90 °CSSD1339Rev 1.1 P 5/59 Jul 2005 Solomon SystechSolomon SystechJul 2005 P 6/59 Rev 1.1 SSD13393. ORDERING INFORMATIONTable 1 – Ordering InformationOrdering Part NumberSEGCOMPackage FormReferenceRemarkSSD1339Z 132RGB 132 COG Page 8• Min SEG pad pitch: 41.2 µm • Min COM pad pitch: 41.2 µmSSD1339U3 128RGB 128 COFPage 54 Punched COF4. BLOCK DIAGRAMFigure 1 – Block DiagramSSD1339Rev 1.1 P 7/59 Jul 2005 Solomon Systech5. DIE PAD FLOOR PLANFigure 2 – SSD1339Z pin assignmentSolomon Systech Jul 2005 P 8/59 Rev 1.1 SSD1339SSD1339 Rev 1.1P 9/59Jul 2005Solomon SystechTable 2 – SSD1339Z Die Pad CoordinatesSolomon SystechJul 2005 P 10/59 Rev 1.1SSD1339Figure 3 – SSD1339Z alignment mark dimensionsSpecmm (mil) W1 76.00 +/-0.1 (2992)W2 68.00 +/-0.1 (2677)W3 68.30 +/-0.1 (2689)X1 4.00 +/-0.1 (157)Y1 1.55 +/-0.1 (61)Px 22.30 +/-0.05 (878)Py 4.20 +/-0.1 (165)X 21.14 +/-0.05 (832)Y 2.40 +/-0.05 (94)Z 0.61 +/-0.05 (24)N 45 Remark1. Depth of text is 0.1mm2. Tray material: ABS3. Tray color code: Black4. Surface resistance 109 ~ 1011Ω - cm5. Tray warpage: Max 0.15mm6. Unspecifier dim's tolerance: +/- 0.15mm7. Pocket size: 21.14 x 2.40 x 0.61mmFigure 4 – Die tray information6. PIN DESCRIPTIONRES#This pin is reset signal input. When the pin is low, initialization of the chip is executed. CS#This pin is the chip select input. The chip is enabled for MCU communication only when CS# is pulled low.D/C#This pin is Data/Command control pin. When the pin is pulled high, the data at D 7-D 0 is treated as display data. When the pin is pulled low, the data at D 7-D 0 will be transferred to the command register. For detail relationship to MCU interface signals, please refer to the Timing Characteristics Diagrams.E (RD#)This pin is MCU interface input. When interfacing to a 6800-series microprocessor, this pin will be used as the Enable (E) signal. Read/write operation is initiated when this pin is pulled high and the chip is selected.When connecting to an 8080-microprocessor, this pin receives the Read (RD#) signal. Data read operation is initiated when this pin is pulled low and the chip is selected.R/W# (WR#)This pin is MCU interface input. When interfacing to a 6800-series microprocessor, this pin will be used as Read/Write (R/W#) selection input. Read mode will be carried out when this pin is pulled high and write mode will be carried out when this pin is pulled low. When 8080 interface mode is selected, this pin will be the Write (WR#) input. Data write operation is initiated when this pin is pulled low and the chip is selected.BS0, BS1, BS2These pins are MCU interface selection input. See the following table:Note: Unlike BS0, BS1 and BS2 are controlled by hardware connection, BS3 is controlled by software command, A0.6800-parallel interface (8 bit) 8080-parallel interface (8 bit) 6800-parallel interface (16 bit) 8080-parallel interface (16 bit)SerialinterfaceBS0 0 0 1 1 0 BS1 0 1 0 1 0 BS2 1 1 1 1 0 BS3 0 0 0 0 06800-parallel interface (9 bit) 8080-parallel interface (9 bit) 6800-parallel interface (18 bit) 8080-parallelinterface (18 bit) BS0 0 0 1 1 BS1 0 1 01BS2 1111BS3 1 1 1 1D17-D0These pins are 18-bit bi-directional data bus to be connected to the microprocessor’s data bus.V DDIOThis pin is a power supply pin of I/O buffer. It should be connected to V DD or external source. All I/O signal should have VIH reference to VDDIO. When I/O signal pins (BS012, M/S, CLS, D0-D17, control signals…) pull high, they should be connected to VDDIO.V DDPower Supply pin. It must be connected to external source.V SSGround. It also acts as a reference for the logic pins. It must be connected to external ground.CLThis pin is the system clock input. When internal clock is enabled, this pin should be left open. Nothing should be connected to this pin. When internal oscillator is disabled, this pin receives display clock signal from external clock source.MSThis pin must be connected to V DD to enable the chip.CLSThis pin is internal clock enable. When this pin is pulled high, internal oscillator is selected.The internal clock will be disabled when it is pulled low, an external clock source must be connected to CL pin for normal operation.VDDBThis is the power supply pin for the internal buffer of the DC-DC voltage converter. It must be connected to V DD when the converter is used. It is also recommended to connect this pin to V DD when the converter is not used to avoid floating node.VSSBThis is the GND pin for the internal buffer of the DC-DC voltage converter. It must be connected to V SS when the converter is used. It is also recommended to connect this pin to V SS when the converter is not used to avoid floating node.GDRThis output pin drives the gate of the external NMOS of the booster circuit. This pin can be left open when the converter is not used.RESEThis pin connects to the source current pin of the external NMOS of the booster circuit. This pin can be left open when the converter is not used.FBThis pin is the feedback resistor input of the booster circuit. It is used to adjust the booster output voltage level (Vcc). This pin can be left open when the converter is not used.BGGNDThis is a ground pin for analog circuits. It must be connected to external ground.VB REFThis pin is the internal voltage reference of booster circuit. A stabilization capacitor, typ. 1uF, should be connected to Vss. This pin can be left open when the converter is not used.V CCThis is the most positive voltage supply pin of the chip. It is supplied either by external high voltage source or internal boosterV COMHThis pin is the input pin for the voltage output high level for COM signals. It can be supplied externally or internally. When V COMH is generated internally, a capacitor should be connected between this pin and V SS.V REFThis pin is the reference for OLED driving voltages like V PA, V PB, V PC and V COMH. It can be either supplied externally or connected to V CC (V REF≤ V CC).V PA, V PB, V PCThese pins are the driving voltages for OLED driving segment pins SA0-SA131, SB0-SB131 and SC0-SC131 respectively. They can be supplied externally or internally generated by VP circuit. When internal VP is used, V PA, V PB, V PC pins should be left open.I REFThis pin is the segment output current reference pin. I SEG of each color is derived from I REFI SEG = (Contrast / 256) * I REF * scale factorContrast is set by command C1hScale factor = master current control register setting (C7h) + 1, i.e., with value from 1~16.A resistor should be connected between this pin and V SS to maintain the current around 10uA.VSLThis is segment voltage reference pin. This pin should be left open.VCLThis is common voltage reference pin. This pin should be connected to V SS externally.COM0-COM131These pins provide the Common switch signals to the OLED panel. These pins are in high impedance state when display is off.SA0-SA131, SB0-SB131, SC0-SC131These pins provide the OLED segment driving signals. These pins are in high impedance state when display is off.The 396 segment pins are divided into 3 groups, SA, SB and SC. Each group can have different color settings for color A, B and C.COMXThese two pins provide the Common switch signals for soft icon line to the OLED panel. These pins are in high impedance state when display is off.TR0 – TR8, VMONA, ICASA, ICASB, ICASC, GPIO0, GPIO1, M, DOF#These are reserved pins. No connection is necessary and should be left open individually.NCNo connection pins. They should be left open individually.7. FUNCTIONAL BLOCK DISCRIPTIONSOscillator Circuit and Display Time Generatorbe programmed from 1 to 16 by command B3h.Reset CircuitWhen RES# input is low, the chip is initialized with the following status:1. Display is OFF2. 132x132 Display Mode3. Normal segment and display data column address and row address mapping (SEG0 mapped toaddress 00H and COM0 mapped to address 00H)4. Shift register data clear in serial interface5. Display start line is set at display RAM address 06. Column address counter is set at 07. Normal scan direction of the COM outputs8. Contrast control register is set at 80HCommand Decoder and Command InterfaceThis module determines whether the input data is interpreted as data or command. Data is interpreted based upon the input of the D/C# pin.If D/C# pin is high, data is written to Graphic Display Data RAM (GDDRAM). If it is low, the input at D7-D0 is interpreted as a Command and it will be decoded and be written to the corresponding command register.MPU Parallel 6800-series InterfaceThe parallel interface consists of 18 bi-directional data pins (D17-D0) or 8 bi-directional data pins (D7-D0),R/W#(WR#), D/C#, E (RD#) and CS#. R/W#(WR#) input High indicates a read operation from the GraphicFigure 6 – Display data read back procedure - insertion of dummy readMPU Parallel 8080-series InterfaceThe parallel interface consists of 18 bi-directional data pins (D17-D0) or 8 bi-directional data pins (D7-D0), E (RD#), R/W#(WR#), D/C# and CS#. The E(RD#) input serves as data read latch signal (clock) when low, provided that CS# is low and high respectively. Display data or status register read is controlled by D/C#. R/W#(WR#) input serves as data write latch signal (clock) when high provided that CS# is low and high respectively. Display data or command register write is controlled by D/C#. Refer to * when 8 bit used: D0~ D7 instead; when 9 bit used: D0 ~ D8 instead; when 16 bit used: D0 ~ D15 instead; when 18 bit used: D0~ D17 instead.Figure 33 of parallel timing characteristics for Parallel Interface Timing Diagram of 8080-series microprocessor. Similar to 6800-series interface, a dummy read is also required before the first actual display data read.MPU Serial InterfaceThe serial interface consists of serial clock SCLK, serial data SDIN, D/C#, CS#. In this mode, D0 acts as SCLK, D1 acts as SDIN. For the unused data pins, D2 should be left open. D3 to D7, E and R/W pins can be connected to external ground.SDIN is shifted into an 8-bit shift register on every rising edge of SCLK in the order of D 7, D 6, ... D 0. D/C is sampled on every eighth clock and the data byte in the shift register is written to the Display Data RAM or command register in the same clock.SCLK(D0)SDIN(D1)Graphic Display Data RAM (GDDRAM)The GDDRAM is a bit mapped static RAM holding the bit pattern to be displayed. The size of the RAM is 132 x 133 x 18bits.For mechanical flexibility, re-mapping on both Segment and Common outputs can be selected by software.For vertical scrolling of the display, an internal register storing display start line can be set to control the portion of the RAM data to be mapped to the display.Each pixel has 18-bit data. Each sub-pixels for color A, B and C have 6 bits. The arrangement of data pixel in graphic display data RAM is shown below.Figure 8 – Graphic Display Data RAM StructureData access in 262k colors modeIn 262k colors depth mode, there are different MCU interface communication modes to access graphic display data RAM in OLED driver.For 18 bits mode, the communication is made up of one session of 18 data bits. MCU transmits all bits to write one 18-bit pixel data into OLED driver. This 18-bit mode can be selected by setting the A[3] bit in command A0 to 1.Bit 17 16 15 14 13 12 11 109 8 7 6 5 4 3 2 1 0 Data bits C 5 C 4 C 3 C 2 C 1 C 0 B 5 B 4 B 3 B 2 B 1 B 0 A 5 A 4 A 3 A 2 A 1 A 0Figure 9 – 262k color depth data writing sequence in 18-bit MCU interfaceFor the 1stoption of the two 16-bit modes, the communication is divided into two sessions of 16 data bits. MCU transmits two 16-bit words to write one 18-bit pixel data into OLED driver. Mode 1 is selected by setting A0h register A[7:6] bits to 10b. In below, A1, B1, C1 are pixel bits for color A, B and C, and “X” stands for don’t care value.Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 1st word X X X X X X X X X X C15 C14 C13 C12 C11 C102nd word X X B15 B14 B13 B12 B11 B10 X X A15 A14 A13 A12 A11 A10 Figure 10 – 262k color depth data writing sequence in 16-bit MCU interface in Option 1For the 2nd option of the 16-bit modes, the communication is divided into three sessions of 16 data bits.MCU transmits three 16-bit words to write two 18-bit pixels data into OLED driver. Option 2 is selected by setting A0h register A[7:6] bits to 11b. In below, A1, B1, C1 are first data pixel bits, and A2, B2, C2 are second data pixel bits.Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 1st word X X C15 C14 C13 C12 C11 C10 X X B15 B14 B13 B12 B11 B102nd word X X A15 A14 A13 A12 A11 A10 X X C25 C24 C23 C22 C21 C203th word X X B25 B24 B23 B22 B21 B20 X X A25 A24 A23 A22 A21 A20 Figure 11 – 262k color depth data writing sequence in 16-bit MCU interface in Option 2For 9-bit modes, the communication is divided into two sessions of 9 data bits. MCU transmits two 9 data bits to write one 18-bit pixel data into OLED driver. This 9-bit mode can be selected by setting the A[3] bit in command A0 to 1.Bit 8 7 6 5 4 3 2 1 01st 9 Data bits C5C4C3C2C1C0B5B4B32nd 9 Data bits B2B1B0A5A4A3A2A1A0Figure 12 – 262k color depth graphic display data writing sequence in 9-bit MCU interfaceIn 8-bit MCU interface, the communication session is divided into three times. MCU transmit three 8-bit bytes to write one 18-bit pixel data into OLED driver.Bit 7 6 5 4 3 2 1 01st byte X X C15 C14 C13 C12 C11 C102nd byte X X B15 B14 B13 B12 B11 B103rd byte X X A15 A14 A13 A12 A11 A10 Figure 13 – 262k color depth graphic display data writing sequence in 8-bit MCU interfaceData access in 65k colors modeWriting a 65K pixel in 16-bit MCU interface involves one session as follows.Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 1st word C14 C13 C12 C11 C10 B15 B14 B13 B12 B11 B10 A14 A13 A12 A11 A10 Figure 14 – 65k color depth graphic display data writing sequence in 16-bit MCU interfaceThe sequence of sending 65K color depth pixel in 8-bit MCU interface is divided into two 8-bit sessions as shown below.Bit 7 6 5 4 3 2 1 01st byte C14 C13 C12 C11 C10 B15 B14 B132nd byte B12 B11 B10 A14 A13 A12 A11 A10 Figure 15 – 65k color depth graphic display data writing sequence in 8-bit MCU interfaceWith reference to Figure 8 conventions, in writing the data into graphic display data RAM, the bit positions filled by the input data for each color is shown below.Color APosition A5 A4 A3 A2 A1 A0BitInput Data A14 A13 A12 A11 A10 A14Color BPosition B5 B4 B3 B2 B1 B0BitInput Data B15 B14 B13 B12 B11 B10Color CPosition C5 C4 C3 C2 C1 C0BitInput Data C14 C13 C12 C11 C10 C14Figure 16 – Display data RAM writing position for color A, B and C data input in 65k color modeIn data RAM, each data occupies 6-bit. However, color A and C have 5-bit length only in 65k color mode. Therefore, RAM positions A0 and C0 are empty originally. These emptied positions are filled as shown above to increase color A and C to 6-bit length in display data RAM.Data access in 256 colors modeIn 256-color mode, each pixel is composed of 8-bit. Only 8-bit MCU interface is available to access display data RAM. The communication session is done in 1 time by writing 8-bit data into RAM.Bit 7 6 5 4 3 2 1 01st byte C12 C11 C10 B12 B11 B10 A11 A10Figure 11 – 256 Color Depth Graphic Display Data Writing Sequence in 8-bit MCU InterfaceWith reference to Figure 8 conventions, in writing the data into graphic display data RAM, the bit positions filled by the input data for each color is shown below.Color APosition A5 A4 A3 A2 A1 A0BitInput Data A11 A10 A11 A11 A11 A11Color BPosition B5 B4 B3 B2 B1 B0BitInput Data B12 B11 B10 B12 B12 B12Color CPosition C5 C4 C3 C2 C1 C0BitInput Data C12 C11 C10 C12 C12 C12Figure 17 – Display data RAM writing position for color A, B and C data input in 256 color modeIn data RAM, each data occupies 6-bit. However, color B and C have 3-bit length and color A has 2-bit only in 256 color mode. Therefore, RAM positions B2~B0, C2~C0 and A3~A0 are empty originally. These emptied positions are filled as shown above to increase color A, B and C to 6-bit length in display data RAM.Gray Scale and Gray Scale TableControlling the current pulse widths from the segment driver in the current drive phase produces the gray scale display. The gray scale table stores the corresponding pulse widths (PW0 ~ PW63) of the 64 gray scale levels (GS0~GS63). The wider the pulse width, the brighter the pixel will be. Therefore, the brightness of each pixel is defined in the graphic display data RAM in term of pulse width in gray scale table.This single gray scale table supports all the three colors A, B and C. The pulse widths are entered by software commands.In graphic display data RAM, each color occupies 6-bit length. So color A, B and C each has 64 gray scale levels.Gray ScaleColor A, B, CRAM data (6 bits)0 GS11 GS22 GS33 GS44 GS: :: :: :6060 GS6161 GS6262 GS6363 GSFigure 18 – Relation between graphic data RAM value and gray scale table entry for three colorsIn 65k and 256 color modes, the length color data are less than 6 bits. They are expanded to 6-bit length as shown in Figure 16 and Figure 17 respectively.The meaning of values inside data RAM with respect to the gray scale level is best to be illustrated in an example below.Gray Scale (Pulse Width)Value/DCLKs PW0 0PW1 2PW2 5: : PW62 120PW63 125Current Control and Voltage ControlThis block is used to derive the incoming power sources into the different levels of internal use voltage and current. V CC and V DD are external power supplies. V REF is reference voltage, which is used to derive driving voltage for segments and commons. I REF is a reference current source for segment current drivers.Segment Drivers/Common DriversSegment drivers deliver 396 current sources to drive OLED panel. The driving current can be adjusted from 0 to 200uA with 256 steps. Common drivers generate voltage scanning pulse.Time Gray Scale TableDC-DC Voltage ConverterIt is a switching voltage generator circuit, designed for handheld applications. In SSD1339, internal DC-DC voltage converter accompanying with an external application circuit (shown in below figure) can generate a high voltage supply V CC from a low voltage supply input V DD. V CC is the voltage supply to the OLED driver block. Below application circuit is an example for the input voltage of 3V VDD to generate V CC of 12V @20mA ~ 30mA application.L1Passive components selection:Components Typical Value Remark22µH 2AL1 Inductor,D1 Schottky diode 2A, 25V e.g. 1N5822Q1 MOSFET N-FET with low R DS(on) and low Vth voltage.e.g. MGSF1N02LT1 [ON SEMICONDUCTOR]R1, R2 Resistor 1%,1/10WR3 Resistor, 1.5Ω1%, 1/2W1µF 16VC1 Capacitor,C2 Capacitor, 22µF Low ESR, 25VC3 Capacitor,1µF 16V10nF16VC4 Capacitor,C5 Capacitor, 1 ~ 10 µF 16VC6 Capacitor, 0.1 ~ 1µF 16V16V15nFC7 Capacitor,The VCC output voltage level can be adjusted by changing the R1 and R2 resistor values, the reference formula is:VCC = 1.2 x (R1+R2) / R28. COMMAND TABLETable 3 – Command table(C D/ = 0, W R/ (WR ) = 0, E(RD ) = 1) unless specific setting is statedSingle byte command (C D/ = 0), Multiple byte command (C D/ = 0 for first byte, C D/ = 1 for other bytes)D/C Hex D7 D6 D5 D4 D3 D2 D2D0Command Description0 15 0 0 0 1 0 1 0 1 A[7:0]: Start Address, reset=0d 1 A[7:0] A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0B[7:0]: End Address, reset=131d 1 B[7:0] B 7B 6B 5B 4B 3B 2B 1B 0Set Column AddressRange from 0d to 131d 0 75 0 1 1 1 0 1 0 1 A[7:0]: Start Address, reset=0d 1 A[7:0] A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0B[7:0]: End Address, reset=131d1 B[7:0] B 7B 6B 5B 4B 3B 2B 1B 0Set Row Address Range from 0d to 131d0 5C 0 1 0 1 1 1 0 0Write RAM Command Enable MCU to write Data into RAM 0 5D 0 1 0 1 1 1 0 1 Enable MCU to read Data from RAMRead RAM Command0 A0 1 0 1 0 0 0 0 0 A[0]=0, Horizontal address increment (POR) 1 A[7:0] A 7 A 6A 5A 4A 3A 2A 1A 0A[0]=1, Vertical address incrementA[1]=0, Column address 0 is mapped to SEG0 (POR) A[1]=1, Column address 131 is mapped to SEG0A[2]=0, Color sequence: A # B # C (POR)A[2]=1, Color sequence is swapped: C # B # AA[3]=0, Disable 9/18-bit bus interface (POR) A[3]=1, Enable 9/18-bit bus interfaceA[4]=0, Scan from COM 0 to COM [N –1] (POR)A[4]=1, Scan from COM [N-1] to COM0. Where N is the Multiplex ratio.A[5]=0, Disable COM Split Odd Even (POR) A[5]=1, Enable COM Split Odd EvenA[7:6] Set Color Depth, 00 256 color 01 65K color, (POR)10 262k color, 8/9/18-bit,16 bit (1st option) MCU interfaceSet Re-map / ColorDepth(Display RAM to Panel)11 262k color, 16 - bit MCU interface (2nd option)0 A1 1 0 1 0 0 0 0 1 Setvertical scroll by RAM from 0~131 1 A[7:0] A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0Set Display Start Line [reset=00d]。

Hiprom 1788-EN2PA-R 和 1788-CN2PA-R 通信和 GPS 产品系列说明书

Hiprom ProductsCommunications and GPS products for the Integrated Architecture™PROFIBUS PA: The 1788-EN2PA-R and 1788-CN2PA-RThe Hiprom 1788-EN2PA-R and 1788-CN2PA-R linking devices provide a fast and integrated solution for adding PROFIBUS PA eld devices to any Allen-Bradley® Logix platform. These devices provide a direct link between PROFIBUS PA and EtherNet/IP or ControlNet (Redundant). Direct Logix to PROFIBUS PA: •The unit operates as a true PA master, and does not require any DP network, DP master, coupler device or external power conditioner.Embedded Ethernet Switch technology:•the 1788-EN2PA-R hosts two Ethernet ports, which allows the unit to be connected in a Linear topology or in a Device Level Ring (DLR) topology.Seamless Integration into RSLogix™ 5000:•An Add-On Pro le (AOP) pro les automated con guration as well as diagnostics for each device. New devices can be added to the network without stopping the process.FDT/DTM technology:•Direct access to the eld devices diagnostics and parameters using an FDT frame such as FactoryTalk® AssetCentre. A eld device DTM can be launched from within the RSLogix 5000 environment using Hiprom FDT-ThinFrame technology.FDT-ThinFrame allows a device DTM to be launched from within the FactoryTalk ViewSE HMI, providing the operator a graphical view into the state and diagnostics of theeld device.Publication HIPROM-PP001A-EN-P , July 2011Copyright © 2011 Rockwell Automation, Inc. All Rights Reserved. Printed in USA.GPS Precision Timing: 1769-GPSBy harnessing the power of the Global Positioning System, the Hiprom 1769-GPS module is able to provide precision timing information across the 1769 backplane. Other GPS information is also available, including: position, velocity and GPS receiver status.Precision Timing:• Provided across the backplane bymeans of a scheduled connection between the GPS module and CompactLogix™ CPU.Sequence of Events Recording:• One millisecondaccuracy can easily be achieved in the CompactLogix CPU by executing a simple ladder routine in a 1ms periodic task.GPS Position:• Data is available in both polar coordi-nates of Longitude, Latitude, and altitude as well as in Cartesian Earth-Centered-Earth-Fixed (ECEF) coordinates X, Y and Z.GPS Velocity:• Data is available in Northerly, Easterly,and Upward velocity components as well as ECEF Vx, Vy and Vz.Status information:• An LED display located on thefront of the module provides the user with status data, such as: number of satellites locked, validity of GPS data as well as the location and signal strength of each satellite being tracked.Time Synchronization Module: 1756-TIMEThe Hiprom 1756-TIME module contains an onboard GPS receiver leveraging the accuracy of the GPS satellite atomic clocks. It hosts dual Ethernet ports for direct Ethernet time synchronization using NTP (Network Time Protocol) and PTP (Precision Time Protocol) where the modules act as Time Grandmasters.Precision Time Protocol (1588 PTP):•Recommended for the control layer where a precision of 250ns with respect to UCT (Universal Coordinate Time) can be achieved in certain network work Time Protocol (NTP): •Used tosynchronize HMI PCs without the need for any additional software.IRIG-B Input/Output:•For legacy systems, modulated IRIG-B (B-122) is supported. The module can be con gured to either transmit or receive IRIG-B.EtherNet/IP Embedded Switch Technologies:•Allows Linear Network and Device Level Ring Ethernet topologies.Cellular Communications Module: 1756-CELLThe Hiprom 1756-CELL module o ers a cost e ective and convenient method of monitoring and controlling remote sites. The module can be used to receive simple command instructions via text message and send alarm and event noti cations to responsible personnel resulting in improved response time, and in turn decreasingdowntime. The 1756-CELL module slots directly into any ControlLogix® chassis, interfacing with, and deriving all required power, from the backplane.GSM Cellular Network:•Utilize any standard GSM cellular network which has coverage in the areawhere the module is located. Low setup costs because existing GSM network structure is being utilized Messaging:•The module can send and receive SMSs (Short Message Service) by utilizing the easy to use generic message block within RSLogix5000.Diagnostics:•Easily accessible by viewing the input image, which is transferred to a user friendly UDT, simplifying the installation and commissioning process of the module.Rockwell Automation is an o cial ENERGY STAR® Industrial Service and Product Provider. It has proven it provides energy e ciency services and/or products to commercial buildings and industrial manufacturing plants in the United States by collaborating with an ENERGY STAR Industrial Partner to submit a teaming pro le that outlines the scope and resulting savings from energy e ciency-driven projects. For more information, visit ENERGY STAR for Industry at /index.cfm?c=industry.bus_industryAllen-Bradley, CompactLogix, ControlLogix, FactoryTalk, Hiprom, Integrated Architecture, RSLogix are trademarks of Rockwell Automation, Inc. Trademarks not belonging to Rockwell Automation are property of their respective companies.。

电脑存储解释指南SSD与HDD的区别

电脑存储解释指南SSD与HDD的区别电脑存储解释指南:SSD与HDD的区别电脑存储是计算机系统中至关重要的组成部分,它直接影响着系统的性能和使用体验。

目前,最常见的两种存储技术是固态硬盘(SSD)和机械硬盘(HDD)。

本文将详细解释SSD与HDD的区别,并讨论它们的优缺点。

一、SSD(Solid State Drive)固态硬盘1. 定义和原理SSD是一种使用非易失性闪存芯片作为存储介质的硬盘。

它使用固态存储器而非机械部件来存储数据,因此没有旋转的磁盘和活动的读写臂。

SSD基于闪存技术,将数据保存在芯片中的电荷中,并通过电子信号来读取和写入数据。

2. 优点(1)速度快:由于没有机械部件,SSD读写速度比机械硬盘快得多。

它可以实现更快的启动时间和文件传输速度,大幅提升系统的响应速度。

(2)抗震性强:由于没有旋转的磁盘,SSD对震动和冲击更具抵抗力,使其在移动设备和笔记本电脑中更加可靠。

(3)更低的能耗:相比于机械硬盘,SSD具有更低的能耗,延长了电池使用寿命,也有助于减少电费支出。

3. 缺点(1)容量较小:目前较大容量的SSD仍相对较为昂贵,不如机械硬盘具备大容量存储的价格优势。

(2)寿命限制:闪存芯片有一定的写入寿命,过多的写入操作可能会导致SSD的寿命缩短。

不过,随着技术的发展,当前市场上的SSD已经具备足够的寿命。

二、HDD(Hard Disk Drive)机械硬盘1. 定义和原理HDD是一种利用机械部件旋转和活动的读写臂来读写数据的存储设备。

它使用旋转磁盘和磁头将数据存储在磁性表面上,并通过磁场变化来读取和写入数据。

2. 优点(1)大容量:机械硬盘提供更大的存储容量,使其非常适用于存储大量的文件和数据。

(2)稳定性:相比于SSD,机械硬盘具备更长的历史和成熟的技术,在稳定性方面更为可靠。

3. 缺点(1)速度较慢:由于存在机械部件和旋转磁盘,HDD的读写速度相对较慢,这可能导致较长的启动时间和文件传输速度。

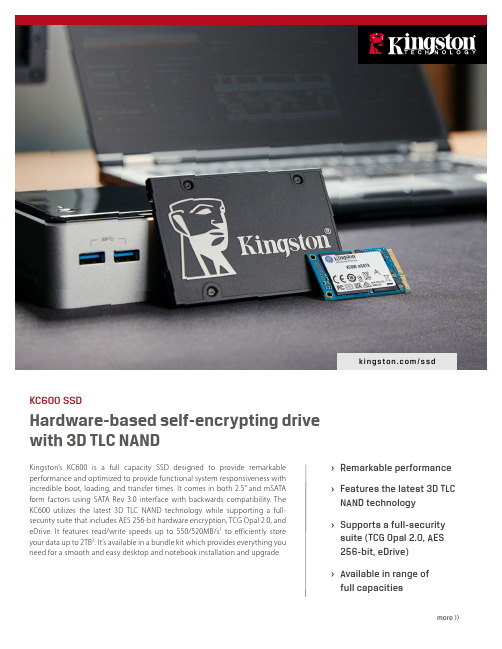

金士顿KC600硬件自加密固态硬盘说明书