ALM-1612中文资料

SM1612 LED驱动控制芯片说明书

SM1612SOP24内部功能框图管脚定义说明极限参数(Ta = 25℃)电气特性(Ta = 25℃)时序特性(VDD=5.0V ,Ta = 25℃)时序波形图DINDOUTCLKGRIDnSEGnTZL*注:DIN 和DOUT 为芯片内部PAD 位,通过封装合并成DI/O 。

◆ 显示寄存器地址和显示模式该寄存器存储通过串行接口从外部器件传送到SM1612的数据,地址分配如下:◆ 键扫描和按键扫描数据寄存器 按键扫描矩阵为10×2bit ,如下所示:S E G 1/K S 1S E G 2/K S 2S E G 3/K S 3S E G 4/K S 4S E G 5/K S 5S E G 6/K S 6S E G 7/K S 7S E G 8/K S 8S E G 9/K S 9S E G 10/K S 10按键数据储存地址如下所示,用读指令读取,从最低位开始读取:指令用来设置显示模式和LED驱动器的状态。

在I2C协议的STAR信号后由DI/O输入的第一个字节作为一条指令。

如果在指令或数据传输时产生I2C协议的STOP信号,串行通讯将被初始化,并且正在传送的指令或数据无效(之前传送的指令或数据保持有效)。

◆显示模式设置该指令用来设置选择段和位的个数(4—7位,10—13段),上电时默认为7位10段。

当指令执行时,显示被强制终止,同时键扫信号也将停止。

如要重新显示,显示开/关指令―ON‖必需被执行,当同样的模式被设置时,则上述情况不会发生。

注:如果指令码Command错误,则重新发STOP+START+指令码Command+……;如果数据DATAn错误,则重新发DATAn+……。

◆蜂鸣器及数据设置该指令用来设置蜂鸣器输出、地址模式采用及数据写或读。

注:1、蜂鸣器输出之前必须先设置蜂鸣器禁止状态(即B5B4=00),先对计时器清零,重新计时;否则蜂鸣器输出计时可能错误。

2、如果蜂鸣器输出1秒(B5B4=11),以后用到数据设置时可以B5B4=11继续,不影响蜂鸣器输出,如读按键指令可用0x72。

1206液晶资料

1602中文资料1602采用标准的16脚接口,其中:第1脚:VSS为地电源第2脚:VDD接5V正电源第3脚:V0为液晶显示器对比度调整端,接正电源时对比度最弱,接地电源时对比度最高,对比度过高时会产生“鬼影",使用时可以通过一个10K的电位器调整对比度第4脚:RS为寄存器选择,高电平时选择数据寄存器、低电平时选择指令寄存器。

第5脚:RW为读写信号线,高电平时进行读操作,低电平时进行写操作。

当RS 和RW共同为低电平时可以写入指令或者显示地址,当RS为低电平RW为高电平时可以读忙信号,当RS为高电平RW为低电平时可以写入数据。

第6脚:E端为使能端,当E端由高电平跳变成低电平时,液晶模块执行命令。

第7~14脚:D0~D7为8位双向数据线.第15~16脚:空脚1602液晶模块内部的字符发生存储器(CGROM)已经存储了160个不同的点阵字符图形,如表1所示,这些字符有:阿拉伯数字、英文字母的大小写、常用的符号、和日文假名等,每一个字符都有一个固定的代码,比如大写的英文字母“A”的代码是01000001B(41H),显示时模块把地址41H中的点阵字符图形显示出来,我们就能看到字母“A”1602液晶模块内部的控制器共有11条控制指令,如表2所示,它的读写操作、屏幕和光标的操作都是通过指令编程来实现的。

(说明:1为高电平、0为低电平)指令1:清显示,指令码01H,光标复位到地址00H位置指令2:光标复位,光标返回到地址00H指令3:光标和显示模式设置 I/D:光标移动方向,高电平右移,低电平左移 S:屏幕上所有文字是否左移或者右移。

高电平表示有效,低电平则无效指令4:显示开关控制. D:控制整体显示的开与关,高电平表示开显示,低电平表示关显示 C:控制光标的开与关,高电平表示有光标,低电平表示无光标 B:控制光标是否闪烁,高电平闪烁,低电平不闪烁指令5:光标或显示移位 S/C:高电平时移动显示的文字,低电平时移动光标指令6:功能设置命令 DL:高电平时为4位总线,低电平时为8位总线 N:低电平时为单行显示,高电平时双行显示 F:低电平时显示5x7的点阵字符,高电平时显示5x10的点阵字符指令7:字符发生器RAM地址设置指令8:DDRAM地址设置指令9:读忙信号和光标地址 BF:为忙标志位,高电平表示忙,此时模块不能接收命令或者数据,如果为低电平表示不忙。

MCP1612

温度规范

电气规范:VIN = 3.0V 至 5.5V, FOSC = 1 MHz,占空比 10%, CIN = 0.1 µF。 TA = -40°C 至 +125°C。 参数 温度范围 储存温度范围 最大结温 工作结温范围 封装热阻 8 引脚 MSOP 封装热阻 8 引脚 DFN 封装热阻 θJA θJA — — 208 41 — — TA TJ TA -65 — -40 — — — +150 +150 +125 符号 最小值 典型值 最大值 单位 条件

注:除非另外说明,否则 VIN = VCC = VSHDN = 3.3V,COUT = CIN = 10 µA,L = 3.3 µH,ILOAD = 100 mA,TA = +25°C。粗体数值 适用的 TA 范围为 -40°C 至 +85°C。

100 90 80 70 60 50 40 30 20 10 0

DS21921A_CN 第 4 页

2005 Microchip Technology Inc.

MCP1612

DC 特性 (续)

电气规范:除非另外说明,否则 VIN = Vcc = VSHDN = 3.3V, VOUT = 1.8V, CIN = COUT = 10 µF, L = 3.3 µH, ILOAD = 100 mA, TA = +25°C。粗体数值适用的 TA 范围为 -40°C 至 +85°C。 参数 保护功能 欠压锁定 欠压锁定迟滞 热关断 热关断迟滞 接口信号 (SHDN) 逻辑高电平输入 逻辑低电平输入 注 VIN-HIGH VIN-LOW 45 — — — — 15 VIN 的 % VIN 的 % UVLO UVLO-HYS TSHD TSHD-HYS 2.4 — — — 2.55 200 160 9 2.7 — — — V mV 注 2 注 1 符号 最小值 典型值 最大值 单位 条件

1612码表说明书

1612码表说明书1612码表说明书简介•1612码表是一种计算机编码标准,常用于信息传输和数据存储。

•该码表使用16个字符(0-9, A-F)组成,每个字符都对应一个4位的二进制数。

编码规则•每个字符由4位二进制数表示。

•采用大端模式,即高位在前,低位在后。

•字符在16进制数系统中的顺序决定了其对应的4位二进制数。

–0对应的二进制数为0000–1对应的二进制数为0001–…–E对应的二进制数为1110–F对应的二进制数为1111应用领域•信息传输:1612码表常用于计算机网络数据传输,可有效将字符转换为二进制串进行传输。

•数据存储:在某些数据库系统中,使用1612码表存储数据,可节省存储空间并提高数据读取速度。

•加密算法:1612码表可用于一些简单的加密算法,将明文转换为相应的二进制码,增加信息的安全性。

使用示例•字符串”Hello”在1612码表中对应的二进制串为:优势与不足•优势:–1612码表简单易懂,易于计算和转换。

–码表中的字符对应的二进制数均为4位,节约了存储空间。

–码表适用于信息传输和数据存储,广泛应用于计算机领域。

•不足:–1612码表只包含16个字符,对于某些特殊字符无法表示,限制了其应用范围。

–由于码表简化了字符集,可能会引发一些数据损失,对于某些应用场景并不适用。

总结•1612码表是一种常用的计算机编码标准,用于信息传输和数据存储。

•该码表采用16个字符,每个字符对应4位二进制数,具有简单易懂、节约存储空间等优势。

•尽管有一些限制,1612码表仍然在计算机领域有广泛的应用。

优势与不足优势:•简单易懂:1612码表的编码规则简单明了,每个字符都有明确的对应二进制数,易于理解和应用。

•节约存储空间:由于每个字符的二进制数码长度都为4位,相比其他编码标准,使用1612码表可以节约存储空间。

•适用广泛:1612码表在信息传输和数据存储领域广泛应用,能够满足多个应用场景的需求。

不足:•对特殊字符的限制:1612码表仅包含了16个字符,对于一些特殊字符或者其他语言的字符无法表示,限制了其在某些应用场景下的使用。

MEMORY存储芯片MT48LC16M16A2B4-6A中文规格书

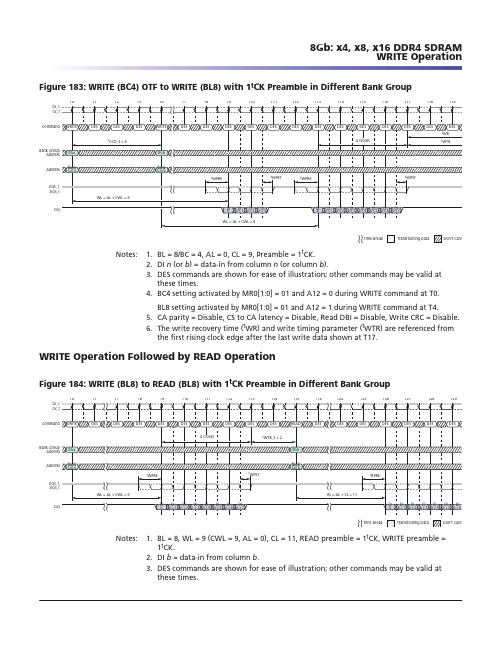

Figure 183: WRITE (BC4) OTF to WRITE (BL8) with 1t CK Preamble in Different Bank GroupCommand DQ CK_t CK_cDQS_t,DQS_cBank GroupAddress Address Notes: 1.BL = 8/BC = 4, AL = 0, CL = 9, Preamble = 1t CK.2.DI n (or b ) = data-in from column n (or column b ).3.DES commands are shown for ease of illustration; other commands may be valid atthese times.4.BC4 setting activated by MR0[1:0] = 01 and A12 = 0 during WRITE command at T0.BL8 setting activated by MR0[1:0] = 01 and A12 = 1 during WRITE command at T4.5.CA parity = Disable, CS to CA latency = Disable, Read DBI = Disable, Write CRC = Disable.6.The write recovery time (t WR) and write timing parameter (t WTR) are referenced fromthe first rising clock edge after the last write data shown at T17.WRITE Operation Followed by READ OperationFigure 184: WRITE (BL8) to READ (BL8) with 1t CK Preamble in Different Bank GroupCommand DQ CK_t CK_cDQS_t,DQS_cBank GroupAddress Address Notes: 1.BL = 8, WL = 9 (CWL = 9, AL = 0), CL = 11, READ preamble = 1t CK, WRITE preamble =1t CK.2.DI b = data-in from column b .3.DES commands are shown for ease of illustration; other commands may be valid atthese times.4.BL8 setting activated by either MR0[1:0] = 00 or MR0[1:0] = 01 and A12 = 1 duringWRITE command at T0 and READ command at T15.5.CA parity = Disable, CS to CA latency = Disable, Read DBI = Disable, Write DBI = Disable,Write CRC = Disable.6.The write timing parameter (t WTR_S) is referenced from the first rising clock edge afterthe last write data shown at T13.Figure 185: WRITE (BL8) to READ (BL8) with 1t CK Preamble in Same Bank GroupCommand DQ CK_t CK_c DQS_t,DQS_cBank GroupAddress Address Notes: 1.BL = 8, WL = 9 (CWL = 9, AL = 0), CL = 11, READ preamble = 1t CK, WRITE preamble =1t CK.2.DI b = data-in from column b .3.DES commands are shown for ease of illustration; other commands may be valid atthese times.4.BL8 setting activated by either MR0[1:0] = 00 or MR0[1:0] = 01 and A12 = 1 duringWRITE command at T0 and READ command at T17.5.CA parity = Disable, CS to CA latency = Disable, Read DBI = Disable, Write DBI = Disable,Write CRC = Disable.6.The write timing parameter (t WTR_L) is referenced from the first rising clock edge afterthe last write data shown at T13.Figure 186: WRITE (BC4) OTF to READ (BC4) OTF with 1t CK Preamble in Different Bank GroupCommand DQ CK_t CK_cDQS_t,DQS_cBank GroupAddress Address Notes: 1.BC = 4, WL = 9 (CWL = 9, AL = 0), CL = 11, READ preamble = 1t CK, WRITE preamble =1t CK.2.DI b = data-in from column b .3.DES commands are shown for ease of illustration; other commands may be valid atthese times.4.BC4 setting activated by MR0[1:0] = 01 and A12 = 0 during WRITE command at T0 andREAD command at T15.5.CA parity = Disable, CS to CA latency = Disable, Read DBI = Disable, Write DBI = Disable,Write CRC = Disable.6.The write timing parameter (t WTR_S) is referenced from the first rising clock edge afterthe last write data shown at T13.Figure 187: WRITE (BC4) OTF to READ (BC4) OTF with 1tCK Preamble in Same Bank GroupCommand DQ CK_t CK_cDQS_t,DQS_cBank GroupAddress Address Notes: 1.BC = 4, WL = 9 (CWL = 9, AL = 0), CL = 11, READ preamble = 1t CK, WRITE preamble =1t CK.2.DI b = data-in from column b .3.DES commands are shown for ease of illustration; other commands may be valid atthese times.4.BC4 setting activated by MR0[1:0] = 01 and A12 = 0 during WRITE command at T0 andREAD command at T17.8Gb: x4, x8, x16 DDR4 SDRAM WRITE Operation。

MEMORY存储芯片MT48LC16M16A2P-6AITG中文规格书

Bus Operations CE# LOW and RST# HIGH enable READ operations. The device internally decodes up-per address inputs to determine the accessed block. ADV# LOW opens the internal ad-dress latches. OE# LOW activates the outputs and gates selected data onto the I/O bus.Bus cycles to/from the device conform to standard microprocessor bus operations. Busoperations and the logic levels that must be applied to the device control signal inputsare shown here.Table 9: Bus OperationsNotes: 1.Refer to the Device Command Bus Cycles for valid DQ[15:0] during a WRITE operation.2.X = "Don’t Care" (H or L).3.RST# must be at V SS ± 0.2V to meet the maximum specified power-down current. ReadTo perform a READ operation, RST# and WE# must be de-asserted while CE# and OE#are asserted. CE# is the device-select control. When asserted, it enables the device. OE#is the data-output control. When asserted, the addressed flash memory data is drivenonto the I/O bus.WriteTo perform a WRITE operation, both CE# and WE# are asserted while RST# and OE# arede-asserted. During a WRITE operation, address and data are latched on the rising edgeof WE# or CE#, whichever occurs first. The Command Bus Cycles table shows the buscycle sequence for each of the supported device commands, while the Command Codesand Definitions table describes each command.Note: WRITE operations with invalid V CC and/or V PP voltages can produce spurious re-sults and should not be attempted.Output DisableWhen OE# is de-asserted, device outputs DQ[15:0] are disabled and placed in High-Zstate, WAIT is also placed in High-Z.StandbyWhen CE# is de-asserted the device is deselected and placed in standby, substantiallyreducing power consumption. In standby, the data outputs are placed in High-Z, inde-pendent of the level placed on OE#. Standby current (I CCS) is the average current meas-Status RegisterRead Status RegisterTo read the status register, issue the READ STATUS REGISTER command at any address.Status register information is available at the address that the READ STATUS REGISTER,WORD PROGRAM, or BLOCK ERASE command is issued to. Status register data is auto-matically made available following a word program, block erase, or block lock com-mand sequence. Reads from the device after any of these command sequences will out-put the devices status until another valid command is written (e.g. READ ARRAY com-mand).The status register is read using single asynchronous mode or synchronous burst modereads. Status register data is output on DQ[7:0], while 0x00 is output on DQ[15:8]. Inasynchronous mode, the falling edge of OE# or CE# (whichever occurs first) updatesand latches the status register contents. However, when reading the status register insynchronous burst mode, CE# or ADV# must be toggled to update status data.The device write status bit (SR7) provides the overall status of the device. SR[6:1]present status and error information about the PROGRAM, ERASE, SUSPEND, V PP, andBLOCK LOCK operations.Note: Reading the status register is a nonarray READ operation. When the operation oc-curs in asynchronous page mode, only the first data is valid and all subsequent data areundefined. When the operation occurs in synchronous burst mode, the same data wordrequested will be output on successive clock edges until the burst length requirementsare satisfied.Table 16: Status Register DescriptionNotes: 1.Default value = 0x80.2.Always clear the status register prior to resuming ERASE operations. This eliminates sta-tus register ambiguity when issuing commands during ERASE SUSPEND. If a commandLatency CountThe latency count (LC) bits tell the device how many clock cycles must elapse from therising edge of ADV# (or from the first valid clock edge after ADV# is asserted) until thefirst valid data word is driven to DQ[15:0]. The input clock frequency is used to deter-mine this value. The First Access Latency Count figure shows the data output latency fordifferent LC settings.Figure 13: First Access Latency CountCLK [C]Address [A]ADV# [V]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]DQ[15:0] [D/Q]Note: 1.First Access Latency Count Calculation:•1 / CLK frequency = CLK period (ns)•n x (CLK period) ≥t AVQV (ns) – t CHQV (ns)•Latency Count = nFigure 14: Example Latency Count Setting Using Code 3CLKCE#ADV#A[MAX:1]D[15:0]End of Wordline ConsiderationsEnd of wordline (EOWL) wait states can result when the starting address of the burst op-eration is not aligned to a 16-word boundary; that is, A[4:1] of the start address does not equal 0x0. The figure below illustrates the end of wordline wait state(s) that occur after the first 16-word boundary is reached. The number of data words and wait states is summarized in the table below.Figure 15: End of Wordline Timing DiagramCLK ADV#OE#WAIT#A[MAX:1]DQ[15:0]Figure 18: Buffer Program ProcedureNotes: 1.Word count values on DQ0:DQ15 are loaded into the count register. Count ranges forthis device are N = 0000h to 01FFh.2.Device outputs the status register when read.3.Write buffer contents will be programmed at the device start or destination address.4.Align the start address on a write buffer boundary for maximum programming perform-ance; that is, A[9:1] of the start address = 0).5.Device aborts the BUFFERED PROGRAM command if the current address is outside theoriginal block address.6.Status register indicates an improper command sequence if the BUFFERED PROGRAMcommand is aborted. Follow this with a CLEAR STATUS REGISTER command.7.Device defaults to SR output data after BUFFERED PROGRAMMING SETUP command(E8h) is issued . CE# or OE# must be toggled to update the status register . Don’t issuethe READ SR command (70h); it is interpreted by the device as buffer word count.8.Full status check can be done after erase and write sequences complete. Write FFh afterthe last operation to reset the device to read array mode.Figure 19: Buffered Enhanced Factory Programming (BEFP) Procedure。

低噪声放大器opa1612

0.000008 –142

Copyright © 2009–2011, Texas Instruments Incorporated

OPA1611 OPA1612

SBOS450B – JULY 2009 – REVISED JULY 2011

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

OPA1611AI, OPA1612AI

PARAMETER

CONDITIONS

MIN

TYP

MAX

AUDIO PERFORMANCE

Total Harmonic Distortion + Noise

THD+N

G = +1, f = 1kHz, VO = 3VRMS

0.000015 –136

Intermodulation Distortion

DESCRIPTION

The OPA1611 (single) and OPA1612 (dual) bipolar-input operational amplifiers achieve very low 1.1nV/√Hz noise density with an ultralow distortion of 0.000015% at 1kHz. The OPA1611 and OPA1612 offer rail-to-rail output swing to within 600mV with a 2kΩ load, which increases headroom and maximizes dynamic range. These devices also have a high output drive capability of ±30mA.

MAX16126-MAX16127中文资料

优势和特性

定购信息在数据资料的最后给出。

应用

汽车 工业 航空电子 电信设备/服务器/网络设备

相关型号以及配合该器件使用的推荐产品,请参见:china.maxim-ic. com/MAX16126.related。

本文是英文数据资料的译文,文中可能存在翻译上的不准确或错误。如需进一步确认,请在您的设计中参考英文资料。

Electrical Characteristics

(VIN = 12V, CGATE-SOURCE = 1nF, TA = -40NC to +125NC, unless otherwise noted. Typical values are at TA = +25NC.) (Note 2) PARAMETER Input Voltage Range Input Supply Current SRC Input Current IN Undervoltage Lockout OVSET/UVSET Input Current OVSET/UVSET Threshold (Rising) OVSET/UVSET Threshold Hysteresis POK Threshold Rising POK Threshold Falling TERM On-Resistance Startup Response Time Autoretry Timeout GATE Rise Time OVSET to GATE Propagation Delay UVSET to GATE Propagation Delay SYMBOL VIN IIN ISRC VUVLO IUVSET/OVSET VTH VTH-HYS VPOK+ VPOKRTERM tSTART tRETRY tRISE tOVG tUVG VGATE rising (GND to VSRC + 6V) VOVSET rising (VTH - 100mV to VTH + 100mV) VUVSET rising (VTH - 100mV to VTH +100mV) 20 (Note 3) VIN rising 1.2 1.225 5 0.9 x VIN 0.87 x VIN 0.7 150 150 1 0.55 1.2 VIN rising CONDITIONS Operating range Protection range SHDN = high SHDN = low MIN 3 -30 224 34 75 TYP MAX 24 +90 320 50 110 2.8 500 1.25 UNITS V FA FA V nA V % V V kI Fs ms ms Fs Fs

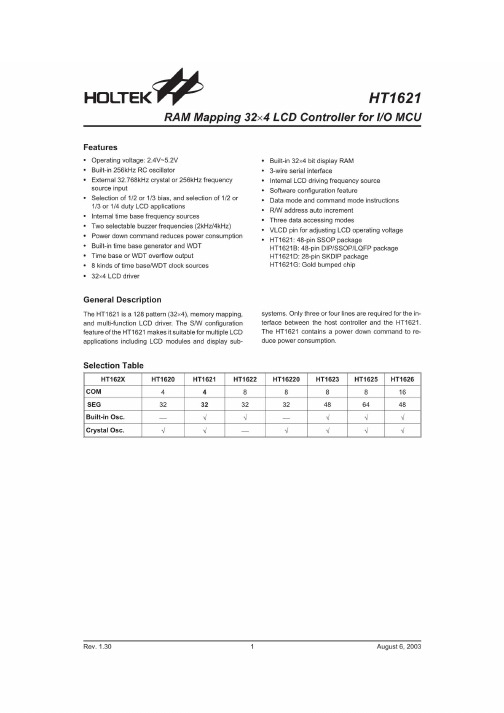

ht1621中文资料_数据手册_参数

ESMQ161VSN102MQ30S中文资料(United Chemi-Con)中文数据手册「EasyDatasheet - 矽搜」

25℃价值和

20℃价值不得超过

Rated Voltage ( V ) Z ( 25 C ) / Z ( 20 C )

160 - 250 4

315 - 400 8

420, 450 8

频率(Hz)

DC Rated Voltage 160 - 250V 315 - 450V

50Hz

120Hz

300Hz

1kHz

ESMQ181VSN471MP25S ESMQ181VSN561MP30S ESMQ181VSN681MP30S ESMQ181VSN821MP35S ESMQ181VSN102MP45S ESMQ181VSN122MP50S ESMQ181VSN681MQ25S ESMQ181VSN821MQ30S ESMQ181VSN102MQ35S ESMQ181VSN122MQ40S ESMQ181VSN152MQ45S ESMQ181VSN182MQ50S ESMQ181VSN102MR25S ESMQ181VSN122MR30S ESMQ181VSN152MR35S ESMQ181VSN182MR40S ESMQ181VSN222MR45S ESMQ181VSN122MA25S ESMQ181VSN152MA30S ESMQ181VSN182MA30S ESMQ181VSN222MA40S ESMQ181VSN272MA45S ESMQ181VSN332MA50S

ESMQ161VSN561MP25S ESMQ161VSN681MP30S ESMQ161VSN821MP35S ESMQ161VSN102MP40S ESMQ161VSN122MP45S ESMQ161VSN152MP50S ESMQ161VSN102MQ30S ESMQ161VSN122MQ35S ESMQ161VSN152MQ40S ESMQ161VSN182MQ45S ESMQ161VSN122MR25S ESMQ161VSN152MR30S ESMQ161VSN182MR35S ESMQ161VSN222MR40S ESMQ161VSN152MA25S ESMQ161VSN182MA30S ESMQ161VSN222MA35S ESMQ161VSN272MA40S ESMQ161VSN332MA45S ESMQ161VSN392MA50S

ht1621中文资料

SD0432 中集成了一个简单的声音发生器,此发声器可输出一对不同的驱动信号至 BZ 和 BZ 以产生单音,执 行 TONE 4K 与 TONE 2K 命令,可选择两个不现的音频输出,即 4KHZ 与 2KHZ 这两个频率,TONE ON 及 TONE OFF 命令可打开或关闭语音输出,语音输出 BZ 和 BZ,是一对不同的带驱动蜂鸣器。当系统关闭或语音输出被禁止时, BZ 及 BZ 将处于低电平状态。

命令 LCD OFF 是通过关闭 LCD 偏压发生器来关闭 LCD 显示器。反之,LCD ON 则启动 LCD 显示。BIAS COM 是与

LCD 屏面相关命令。使用 LCD 相关命令,SD0432 可与绝大多数类型的 LCD 屏面兼容。

3. 6 命令格式

SD0432 可由 S/W 设置来配置。有两种命令模式分别用来配置 SD0432 和传送 LCD 显示数据。配置 SD0432 的命

令模式(普通模式)识别码为 100,此命令模式由系统配置命令、LCD 配置命令、音频选择命令、定时器/看门狗

定时器设置命令及操作命令组成。另一方面,数据模式包括 READ、WRITE 及 READ-MODIFY-WRITE 操作。下表为数

据模式及命令模式识别码:

com 操

作

. READ

s WRITE

le RAM 中的数据由 READ、WRITE 以及 READ-MODIFY-WRITE 指令进行存取,下图为由 RAM 控制 LCD 的映象图。

e SEG

COM

COM3

COM2

COM1

COM0

六位地址(A5,A4…A0)

. SEG0

0

ww SEG1

1

w SEG2

HT1621中文资料

插口号

25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48

X

58.14 58.14 58.14 58.14 58.14 58.14 58.14 58.14 55.55 48.92 42.29 35.66 29.03 22.40 15.77 9.14 2.42 -4.21 -10.84 -17.47 -24.10 -30.73 -38.17 -45.39

广州周立功单片机发展有限公司 Tel 020 38730976 38730977 Fax:38730925

系统结构 显示内存 RAM 静态显示内存 RAM 以 32 4 位的格式储存所显示的数据 RAM 的数据直接映象 到 LCD 驱动器 可以用 READ WRITE 和 READ-MODIFY-WRITE 命令访问

概述 HT1621 是 128 点 内存映象和多功能的 LCD 驱动器 HT1621 的软件配置特性使它适 用于多种 LCD 应用场合 包括 LCD 模块和显示子系统 用于连接主控制器和 HT1621 的管 脚只有 4 或 5 条 HT1621 还有一个节电命令用于降低系统功耗

a1612芯片工作原理

a1612芯片工作原理宝子!今天咱们来唠唠A1612芯片的工作原理,这就像是探秘一个超级神秘又超酷的小世界呢。

A1612芯片啊,就像是一个超级智能的小管家。

你看啊,它里面有好多好多微小的电路元件,这些元件就像是一个个勤劳的小蚂蚁,每个都有自己独特的任务。

咱先说说它的电源部分吧。

电源就像是这个小管家的食物,没有食物它可没法工作呢。

当电源接入芯片的时候,就像是给这个小管家打了一针强心剂。

电流就像小河流一样,缓缓地流进芯片内部。

这电流可不能乱来哦,它得按照芯片内部设计好的路线走,就像我们在游乐园里要按照规定的路线游玩一样。

然后呢,就是芯片的核心——逻辑电路啦。

这逻辑电路啊,就像是小管家的大脑。

它能够处理各种各样的信息。

比如说,外部设备给芯片发送了一些信号,这些信号就像是神秘的小密码。

逻辑电路会把这些密码进行解读,就像你解开一道超级难的谜题一样。

如果信号是要让芯片做加法运算,逻辑电路就会像一个超级聪明的小学生,快速地算出结果。

再说说芯片的存储单元吧。

这存储单元就像是小管家的小仓库。

它可以把一些重要的信息保存起来。

比如说,你上次让芯片处理的一些数据,它就会悄悄地放在这个小仓库里。

下次你再需要用到这些数据的时候,它就能快速地从仓库里拿出来。

这个小仓库的管理可严格了呢,每个数据都有自己的小格子,不会乱套的。

还有啊,芯片的输入输出接口也很有趣。

这就像是小管家的手和嘴巴。

输入接口就像是它的手,可以接收外部世界给它的各种东西,像数据啊,指令啊之类的。

而输出接口呢,就像是它的嘴巴,可以把芯片处理好的结果告诉外面的世界。

比如说,你让芯片控制一个小灯的亮灭,芯片通过逻辑电路处理后,就会通过输出接口告诉小灯:“小灯,你现在该亮起来啦!”A1612芯片在工作的时候啊,这些部分就像是一个配合默契的小团队。

电源持续提供能量,逻辑电路不断地思考和处理,存储单元稳稳地保存着数据,输入输出接口负责和外界交流。

它们就这么有条不紊地工作着,完成各种各样神奇的任务。

UC1612N中文资料

UC3612 Dual Schottky Diode•Monolithic Two Diode Array •Exceptional Efficiency •Low Forward Voltage •Fast Recovery Time •High Peak Current •Small Size The two-diode array is designed for high-current, low duty-cycle applications typical of flyback voltage clamping for inductive loads.The use of Schottky diode technology features high efficiency through lowered forward voltage drop and decreased reverse recov-ery time.This single monolithic chip is fabricated in hermetic CERDIP as well as copper leaded plastic MINIDIP and SOIC surface mount power pack. The UC1612 in ceramic is designed for −55°C to +125°C environments, but with reduced peak current capability; while the UC3612 has higher current rating over a 0°C to +70°C ambient tem-perature range.FEATURES DESCRIPTIONABSOLUTE MAXIMUM RATINGSPeak Inverse Voltage (per diode) . . . . . . . . . . . . . . . . . . . .50VPeak Forward Current, UC3612 . . . . . . . . . . . . . . . . . . . . . .3APeak Forward Current, UC1612 . . . . . . . . . . . . . . . . . . . . . .1AStorage Temperature Range . . . . . . . . . . . . .−65°C to +150°CJunction Temperature . . . . . . . . . . . . . . . . . . .−55°C to +150°CLead Temperature (Soldering, 10 seconds) . . . . . . . . . . .300°C Currents are positive into, negative out of the specified terminal.Consult Packaging Section of Databook for thermal limitationsand considerations of packages.CONNECTION DIAGRAM8/94UC3612ELECTRICAL CHARACTERISTICS All specifications apply to each individual diode. T J = 25°C except as noted.Note: At forward currents of greater than 1.0A, a parasitic current of approximately 10mA may be collected by adjacent diodes.UNITRODE INTEGRATED CIRCUITS7 CONTINENTAL BLVD. •MERRIMACK, NH 03054TEL. (603) 424-2410 •FAX (603) 424-34602PACKAGING INFORMATIONOrderable DeviceStatus (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)UC1612J OBSOLETE UTR 8TBD Call TI Call TI UC1612L OBSOLETE UTR TBD Call TI Call TI UC3612DP OBSOLETE UTR 8TBD Call TI Call TI UC3612J OBSOLETE UTR TBD Call TI Call TI UC3612NOBSOLETEUTR8TBDCall TICall TI(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided bythird parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM18-Sep-2008Addendum-Page 1IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDSP BroadbandClocks and Timers Digital ControlInterface MedicalLogic MilitaryPower Mgmt Optical NetworkingMicrocontrollers SecurityRFID TelephonyRF/IF and ZigBee®Solutions Video&ImagingWirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2008,Texas Instruments Incorporated。

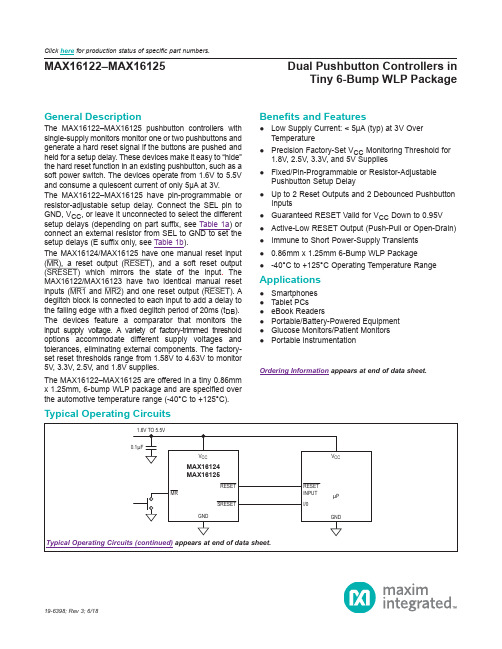

maxim MAX16122-MAX16125 单电源监视器按钮复位器数据手册说明书

General DescriptionThe MAX16122–MAX16125 pushbutton controllers with single-supply monitors monitor one or two pushbuttons and generate a hard reset signal if the buttons are pushed and held for a setup delay. These devices make it easy to “hide” the hard reset function in an existing pushbutton, such as a soft power switch. The devices operate from 1.6V to 5.5V and consume a quiescent current of only 5µA at 3V.The MAX16122–MAX16125 have pin-programmable or resistor-adjustable setup delay. Connect the SEL pin to GND, V CC , or leave it unconnected to select the different setup delays (depending on part suffix, see Table 1a ) or connect an external resistor from SEL to GND to set the setup delays (E suffix only, see Table 1b ).The MAX16124/MAX16125 have one manual reset input (MR ), a reset output (RESET ), and a soft reset output (SRESET ) which mirrors the state of the input . The MAX16122/MAX16123 have two identical manual reset inputs (MR1 and MR2) and one reset output (RESET ). A deglitch block is connected to each input to add a delay to the falling edge with a fixed deglitch period of 20ms (t DB ).The devices feature a comparator that monitors the input supply voltage. A variety of factory-trimmed threshold options accommodate different supply voltages and tolerances, eliminating external components. The factory-set reset thresholds range from 1.58V to 4.63V to monitor 5V, 3.3V, 2.5V, and 1.8V supplies.The MAX16122–MAX16125 are offered in a tiny 0.86mm x 1.25mm, 6-bump WLP package and are specified over the automotive temperature range (-40°C to +125°C).Benefits and Features●Low Supply Current: < 5μA (typ) at 3V OverTemperature ●Precision Factory-Set V CC Monitoring Threshold for1.8V,2.5V,3.3V, and 5V Supplies ●Fixed/Pin-Programmable or Resistor-AdjustablePushbutton Setup Delay ●Up to 2 Reset Outputs and 2 Debounced PushbuttonInputs ●Guaranteed RESET Valid for V CC Down to 0.95V ●Active-Low RESET Output (Push-Pull or Open-Drain) ●Immune to Short Power-Supply Transients ●0.86mm x 1.25mm 6-Bump WLP Package ●-40°C to +125°C Operating Temperature RangeApplications●Smartphones ●Tablet PCs●eBook Readers●Portable/Battery-Powered Equipment ●Glucose Monitors/Patient Monitors●Portable InstrumentationOrdering Information appears at end of data sheet.19-6398; Rev 3; 6/18Typical Operating CircuitsMAX16122–MAX16125Dual Pushbutton Controllers inTiny 6-Bump WLP PackageClick here for production status of specific part numbers.(All pins referenced to GND)V CC ..........................................................................-0.3V to +6V RESET , SRESET to GNDOpen-Drain ..............................................................-0.3V to +6V Push-Pull ..................................................-0.3V to (V CC + 0.3V)MR , MR1, MR2........................................................-0.3V to +6V SEL ..........................................................................-0.3V to +6VInput/Output Current (all pins) ............................................20mA Continuous Power Dissipation (T A = +70°C) (Multilayer Board) WLP (derate 10.5mW/°C above +70°C) ......................840mW Operating Temperature Range .........................-40°C to +125°C Junction Temperature ......................................................+150°C Storage Temperature Range ............................-65°C to +150°C Soldering Temperature (reflow) .......................................+260°CWLPJunction-to-Ambient Thermal Resistance (θJA ) ..........95°C/W(Note 1)(V CC = 1.6V to 5.5V, T A = -40°C to +125°C, unless otherwise noted. Typical values are at T A = +25°C.) (Note 2)Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layerboard. For detailed information on package thermal considerations, refer to /thermal-tutorial .Absolute Maximum RatingsStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Package Thermal Characteristics Electrical CharacteristicsPARAMETERSYMBOL CONDITIONSMIN TYP MAX UNITS Operating Voltage Range V CC RESET state guaranteed for V CC ≥ 0.95V1.65.5V V CC Undervoltage Lockout V CCUVLO1.25 1.55V V CC Supply CurrentI CC V CC = 5V, steady-state condition; MR , MR1, MR2, RESET , and SRESET not asserted 810µASupply Current with Oscillator RunningI CC2V CC = 3V 510µA V CC Reset ThresholdV TH V CC falling-2.5%V TH +2.5%V V CC Reset Threshold Hysteresis V HYST2%Reset Threshold Tempco 30ppm/°C V CC to RESET Output Delay t D V CC falling at 10mV/µs from (V TH + 100mV) to (V TH - 100mV)10µsReset Timeout Period t RP See Table 2-10t RP +10 %Manual Reset Setup Delay t SU Internal timing (see Tables 1a, 1b, 1c)-10t SU +10%Debounce Periodt DB182022msTiny 6-Bump WLP Package(V CC = 1.6V to 5.5V, T A = -40°C to +125°C, unless otherwise noted. Typical values are at T A = +25°C.) (Note 2)Note 2: All parameters are production tested at T A = +25°C. Limits over the operating temperature range are guaranteed by design.Electrical Characteristics (continued)PARAMETERSYMBOLCONDITIONSMINTYPMAXUNITSOUTPUTS (RESET , SRESET )RESET , SRESET Output LowV OLV CC = V TH(MIN), V TH > 4.25V, I SINK = 10mA0.4V V CC = V TH(MIN), V TH > 2.5V, I SINK = 3.2mA0.4V V CC = V TH(MIN), V TH > 1.67V, I SINK = 1mA0.4V V CC = V TH(MIN), V TH > 1V, I SINK = 100µA 0.4V V CC > 0.95V, V CC falling, I SINK = 15µA 0.4V RESET , SRESET Output High (Push-Pull Outputs)V OHV CC > 0.95V, I SOURCE = 15µA0.8 x V CC V V CC > 1.2V, I SOURCE = 100µA0.8 x V CC V V CC > 1.67V, I SOURCE = 150µA 0.8 x V CC V V CC > 2.7V, I SOURCE = 500µA 0.8 x V CC V V CC > 4.5V, I SOURCE = 800µA0.8 x V CCV RESET , SRESET OutputLeakage Current (Open-Drain Outputs)1µAMANUAL RESET INPUTS (MR , MR1, MR2)MR1, MR2, MR Input Voltage LowV IL 0.3 x V CCV MR1, MR2, MR Input Voltage HighV IH0.7 x V CCV Manual Reset Minimum Pulse Width1µs Manual Reset Glitch Rejection 100ns Manual Reset to Soft Reset Delayt MRD200ns MR1, MR2, MR Internal Pullup Resistance255080kΩSELECT (SEL) LOGIC INPUT SEL Input Low Voltage 0.15 x V CCV SEL Input High Voltage 0.85 x V CC V SEL Input Leakage-8+8µATiny 6-Bump WLP Package(V CC = 5V, MAX16125WTDB29+, T A = +25°C, unless otherwise noted.)Typical Operating CharacteristicsSUPPLY CURRENT vs. SUPPLY VOLTAGESUPPLY VOLTAGE (V)S U P P L Y C U R R E N T (µA )5.55.04.0 4.52.5 3.0 3.52.023*********1.56.0MAXIMUM V CC TRANSIENT DURATION vs. RESET THRESHOLD OVERDRIVERESET THRESHOLD OVERDRIVE (V)M A X I M U M V C C T R A N S I E N T D U R A T I O N (µs )0.200.150.100.052468101214000.25V CC RESET THRESHOLD vs. TEMPERATURETEMPERATURE (°C)V C C R E S E T T H R E S H O L D (%)1109580655035205-10-255-5-40125-4-3-2-112340SUPPLY CURRENT vs. TEMPERATURETEMPERATURE (°C)S U P P L Y C U R R E N T (µA )1109580655035205-10-252468100-40125RESET TIMEOUT PERIOD vs. TEMPERATURETEMPERATURE (°C)R E S E T T I M E O U T P E R I O D (m s )1109580655035205-10-251.952.002.052.101.90-40125Tiny 6-Bump WLP Package(V CC = 5V, MAX16125WTDB29+, T A = +25°C, unless otherwise noted.)Typical Operating Characteristics (continued)V CC TO RESET OUTPUT DELAYvs. TEMPERATUREM A X 16122 t o c 06TEMPERATURE (°C)V C C T O R E S E T O U T P U T D E L A Y (µs )1109580655035205-10-252468100-40125V CC TO RESET DELAYMAX16122 toc094µs/divV TH + 100mV 100mV/divRESET 2V/divt SU vs. R SELM A X 16122 t o c 10SEL RESISTANCE TO GND (k Ω)S E T U P D E L A Y (s )460410310360110160210260602468101214161820222410RESET OUTPUT-LOW VOLTAGEvs. SINK CURRENTSINK CURRENT (mA)R E S E T V O L (V ) 4.54.00.5 1.0 1.5 2.5 3.02.0 3.50.050.100.150.200.250.300.350.4005.0PUSHBUTTON TIMINGt SU = 13.03µs2s/divMR12V/div MAX16125WTDB29+SRESET 2V/divRESET 2V/divTiny 6-Bump WLP PackageBump DescriptionBump ConfigurationsBUMPNAMEFUNCTIONMAX16122/MAX16123MAX16124/MAX16125A1A1RESETActive-Low Reset Output. RESET is either an open-drain or a push-pull output (see the Selector Guide ). RESET asserts low when V CC drops below the selected threshold and remains low for the V CC reset timeout period after V CC rises above the reset threshold. The RESET one-shot asserts low for the reset timeout period when the manual reset input is asserted longer than the setup delay. The open-drain output requires an external pullup resistor.—A2SRESET Soft Reset Output. SRESET is the debounced version of MR.B1B1SELSetup Delay Select Input. Connect SEL to V CC , GND, or leave unconnected to select a desired setup delay (see Table 1a); or connect an external resistor between SEL and GND to select a desired setup delay (E suffix only, see Tables 1a and 1b).—B2MRManual Reset Input. Internal 50kΩ pullup to V CC . Pull MR low for the setup delay (t SU ) to one-shot pulse RESET for the reset timeout period.Tiny 6-Bump WLP PackageDetailed DescriptionThe MAX16122–MAX16125 low-current microprocessor reset circuits feature single or dual manual reset inputs with an extended setup period. The devices also feature an internal comparator to monitor 5V, 3.3V, 2.5V, and 1.8V supplies.When the monitored supply voltage drops below the specified threshold, the active-low RESET output asserts low and remains low for the reset timeout period (tRP). The RESET output is one-shot pulse asserted for the reset timeout period. For applications that do not require reset timeout period at startup, devices with that con-figuration are offered. Supply voltage reset threshold is selectable through part suffix, see Table 3.Connect SEL to GND, V CC , or leave unconnected to select the different setup delays (depending on part suffix, see Table 1a ), or connect to an external resistor to set the setup delays (E suffix only, see Table 1b ).The MAX16124/MAX16125 have one manual reset input (MR ), one reset output (RESET ), and one soft reset output (SRESET ). The MAX16122/MAX16123 have two identical manual reset inputs (MR1 and MR2) and one reset output (RESET ). A deglitch block is connected to each manual reset input to add a delay to the falling edge with a fixed deglitch period of 20ms (t DB ).Resistor-Adjusted Setup DelayFor the MAX16122–MAX16125 with the E setup delay suffix (MAX1612_WTE_+T), a resistor connected from SEL to GND sets the setup delay. Table 1b shows com-mon resistor values and the resulting setup delays. For resistor values not in the table, use the following formula to compute the setup delay:SU R t 20=where R is the resistor value in kΩ and t SU is the result-ing setup delay in seconds. For best results, use resistor values between 10kΩ and 500kΩ.Reset OutputThe reset output is typically connected to the reset input of a microprocessor (µP). A µP’s reset input starts or restarts the FP in a known state. The MAX16122–MAX16125 FP supervisory circuits provide the reset logic to prevent code-execution errors during power-up, power-down, and brownout conditions (see the Typical Operating Characteristics ).The MAX16122/MAX16123 have a reset output RESET . The MAX16124/MAX16125 have a reset output RESET and a soft-reset output SRESET which is the debounced “mirror image” of MR (see Figure 1a ).Pin Description (continued)BUMPNAMEFUNCTIONMAX16122/MAX16123MAX16124/MAX16125C1C1V CC Power-Supply Input. V CC provides power to the device and is also a monitored voltage. When V CC drops below the selected threshold, RESET asserts low and remains low for the reset timeout period after V CC rises above the threshold. Bypass V CC to GND with a 0.1µF capacitor. C2C2GND GroundB2—MR1Active-Low Manual Reset Input 1. Internal 50kΩ pullup to V CC . Pull both MR1 and MR2 low for the setup delay (t SU ) to one-shot pulse RESET for the reset timeout period. A2—MR2Active-Low Manual Reset Input 2. Internal 50kΩ pullup to V CC . Pull the MR2 and MR1 low for the setup delay (t SU ) to one-shot pulse RESET for the reset timeout period.Tiny 6-Bump WLP PackageAll reset outputs are either active-low open-drain or active-low push-pull (see the Selector Guide ). RESET changes from high to low whenever the monitored voltage V CC drops below the reset threshold voltage. Once V CC exceeds its respective reset threshold voltage, RESET remains low for the reset timeout period (t RP ) and then goes high. RESET is one-shot pulsed whenever selected manual reset inputs are asserted longer than the setup delay (t SU ). RESET stays asserted for the normal reset timeout period.RESET is guaranteed to be in the proper output logic state for V CC ≥ 0.95V. For applications requir -ing valid reset logic when V CC is less than 0.95V, see the Ensuring a Valid RESET Output Down to V CC = 0V (Push-Pull RESET Output) section.Manual Reset InputEach device in the MAX16122–MAX16125 family includes at least one manual reset input, which must be held logic-low for an extended setup period (t SU ) before the RESET output asserts. An internal pullup resistor is connected to each manual reset input. When valid manual reset input conditions/setup periods are met, the RESET output ispulsed low for the reset timeout period (see Table 2). Existing front-panel pushbutton switches (i.e., power-on/-off, channel up/down, or mode select) can be used to drive the manual reset inputs. The extended manual reset setup period prevents nuisance system resets dur-ing normal front-panel usage or resulting from inadvertent short-term pushbutton closure.The MAX16124/MAX16125 include a single manual reset input (MR ) and two reset outputs (RESET and SRESET ). The MAX16122/MAX16123 include two manual reset inputs (MR1 and MR2) and one reset output, RESET . For dual MR1 and MR2 devices, both inputs must be simulta-neously pulled low and held for the extended setup period (t SU ) before the reset output is pulsed. The dual extended setup provides greater protection from nuisance resets.The MAX16122–MAX16125 RESET output is asserted once for the reset timeout period after each valid manual reset input condition. At least one manual reset input must be released (go high) and then be driven low for the extended setup period before RESET asserts again. Internal timing circuitry debounces low-to-high manual reset logic transitions, so no external circuitry is required.Figure 1a. Reset Timing DiagramTiny 6-Bump WLP PackageTiny 6-Bump WLP PackageFigure 1b. Timeout Periods at StartupSupply Voltage MonitorThe MAX16122–MAX16125 have an internal comparator with a programmable trip threshold to monitor the sup-ply voltage. The V CC monitoring thresholds are select-able through the part number suffix (see the Ordering Information and Table 3).Applications InformationFalling V CC TransientsIn addition to issuing a reset to the µP during power-up, power-down, and brownout conditions, the MAX16122–MAX16125 are relatively immune to short-duration fall-ing V CC transients (glitches). The Typical Operating Characteristics show the Maximum Transient Duration vs. V CC Overdrive graph for which the MAX16122–MAX16125 do not generate a reset pulse. This graph was generated using a falling pulse applied to V CC starting above the actual reset threshold and ending below the threshold by the magnitude indicated (V CC overdrive). The graph indicates the typical maximum pulse width that a falling transient can have without initiating a reset pulse. As the magnitude of the transient increases (go farther below the reset threshold), the maximum allowable pulse width decreases.Ensuring a Valid RESET Output Down toV CC = 0V (Push-Pull RESET Output)The MAX16122–MAX16125 guarantee proper operation down to V CC = 0.95V. In applications that require valid reset levels down to V CC = 0V, add a pulldown resis-tor between RESET and GND for the push-pull outputs (MAX16122/MAX16124). The resistor sinks any stray leakage currents, holding RESET low (Figure 2). The resistor value used is not critical, but it must be small enough not to overload the RESET output when V CC is above the reset threshold. For most applications, use 100kΩ to 1MΩ. This scheme does not work with open-drain outputs of the MAX16123/MAX16125.Layout and BypassingEnsure 0.1µF (minimum) capacitance is connected from V CC to GND.Figure 2. Ensuring RESET Output to V CC = 0VTiny 6-Bump WLP PackageTiny 6-Bump WLP Package Typical Operating Circuits (continued)Tiny 6-Bump WLP Package Functional DiagramsTiny 6-Bump WLP Package Functional Diagrams (continued)Table 1a. SEL Pin Connection Setup Delays (t SU )Table 1b. Resistor-Adjusted Setup Delays (t SU )Table 2. Reset Timeouts (t RP )Table 3. V CC Reset Threshold Voltage (V TH )PART SUFFIXSETUP DELAYS (s)SEL = GNDSEL =UNCONNECTEDSEL = V CCA 0.512B 345C 6810D 131517ESee Table 1bRESISTOR (kΩ)SETUP DELAYS (s)100.5180.922 1.127 1.3539 1.9547 2.3556 2.882 4.11005180922011PART SUFFIXMINIMUM RESET TIMEOUT (ms)A0.9B 1.8C 3.6D 7.2E 14.4F 28.8G 57.6H 86.4I 115.2J 172.8K 230.4L 259.2M 345.6N 460.8O 691.2P 921.6Q 1843.2R 3686.4S7372.8SUFFIX V CC RESET THRESHOLDVOLTAGE (V) (typ)00No Monitoring16 1.5817 1.6722 2.1923 2.3229 2.9331 3.0844 4.38464.63Tiny 6-Bump WLP PackageNote: Insert the desired setup delay (A to Q, from Table 1a ) into the blank following the letters WT. Insert the letter corresponding to the desired minimum reset timeout period (A to S, from Table 2) into the blank following the setup delay suffix. Insert the two digit number corresponding to the desired nominal reset threshold (from Table 3) into the blanks following the reset timeout suffix.+Denotes a lead(Pb)-free/RoHS-compliant package. Devices are available only in lead-free packaging.T = Tape and reel.*Future product—Contact factory for availability.Note: MAX16125WTDB29+T is a standard option. For additional options, please contact factory.Chip InformationPROCESS: BiCMOSOrdering InformationSelector GuidePackage InformationFor the latest package outline information and land patterns (footprints), go to /packages . Note that a “+”, “#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.PARTTEMP RANGE PIN-PACKAGEMAX16122WT_ _ _ _+T*-40°C to +125°C 6 WLP MAX16123WT_ _ _ _+T*-40°C to +125°C 6 WLP MAX16124WT_ _ _ _+T*-40°C to +125°C 6 WLP MAX16125WT_ _ _ _+T-40°C to +125°C6 WLPPARTDUAL MANUAL RESET INPUTSRESETSEL ACTIVE-LOW RESET OUTPUTMAX16122WT_ _ _ _+T √—√Push-pull MAX16123WT_ _ _ _+T √—√Open-drain MAX16124WT_ _ _ _+T —√√Push-Pull MAX16125WT_ _ _ _+T—√√Open-drainPACKAGE TYPE PACKAGE CODE OUTLINE ND PATTERN NO.WLPW61F0+121-0217Refer toApplication Note 1891Tiny 6-Bump WLP PackageRevision HistoryREVISION NUMBERREVISION DATE DESCRIPTIONPAGES CHANGED07/12Initial release—111/14No /V OPNs in Ordering Information ; removed automotive reference from Applications section124/16Updated Electrical Characteristics table and text7, 936/18Updated General Description and Benefits and Features sections1Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.Tiny 6-Bump WLP PackageFor pricing, delivery, and ordering information, please visit Maxim Integrated’s online storefront at https:///en/storefront/storefront.html.。

Model 1612QS 音响楼阁说明说明书

specifications and performance requirements for color retention, chalk resistance, gloss retention, erosion, corrosion and chemical resistance as well as dry film thickness and hardness. Our state-of-the-art powder coat system provides an environment friendly finishing solution with more uniform coverage and coating thickness. The result is an exceptional finish that better resists scratching, fading and general wear. Additional liquid coat facilitiesFluoropolymer Powder Coat AAMA 2605-Superior Finish (AKA: Powdura®5000, Coraflon®Powder,Interpon®D3000-Fluoromax)A vailable Finishes"Ultimate" − A next generation hyper durable powder coating, based onFEVE fluoropolymer resins and ceramic pigmentation that the industryhas acknowledged as the foundation for superior performance coatings.They provide a hard surface that is resistant to scratching and scuffing,with superior color and gloss retention, when applied to a variety ofexterior architectural applications. This technology represents the“ultimate” in environmentally friendly finishes, with Zero-VOC emissions.A new alternative to traditional 70% Kynar 500®/ Hylar 500®PVDFfluoropolymer liquid coatings.10 years(Consult Nailorfor availabilityof extendedwarranty)High Performance Powder CoatAAMA 2604 −High Performance Finish (AKA: Powdura®4000, Envirocron®Ultra Durable Powder, Dynadure™400, Interpon®D2000)"Better" − A high performance polyester powder coating, based on“super durable” resins that utilize infrared reflective pigments, whichprovides excellent resistance to outdoor weathering. A harder and more environmentally friendly coating than other liquid paint counterparts andwith Zero-VOC emissions.A good alternative to 50% Kynar 500®/ Hylar 5000®liquid coatings.5 yearsDurable Powder CoatAAMA 2603 −Pigmented Organic Coatings (AKA: Powdura®3000, Envirocron®Durable Powder, Dynadure™300, Interpon®D1000)"Good" − A durable powder coat based on thermosetting polyester resin technology.Provides a good economical combination of physical and chemical resistance properties. Environmentally superior to liquid spray paints andZero – VOC emissions.1 yearClear Anodize 215-R1 AA-M10C22A41(0.7 mil. min.)Architectural Class I. Clear, colorless and hard oxide aluminum coatingthat resists weathering and chemical attack. Recommended for severelycorrosive and abrasive atmospheric exposure.5 yearsColor Anodize AA-M10C22A44 (0.7 mil. min.)Architectural Class I. "Two-step" aluminum coating process. Following astandard anodizing procedure, a second electrolytic process depositscolored metallic pigments which penetrate the aluminum oxide pores,producing a corrosion resistant, colorfast finish. Available in light,medium, dark bronze and black.5 yearsPrime Coat Prime coat provides a stable base for painting of louvers in the field.Surface pretreatment includes degreasing and a chemical cleaningbefore an epoxy prime coat is applied. Finish coat should be field appliedas soon as possible for best adhesion, after a thorough cleaning for dust etc.that can contaminate the final finish and cause premature flaking or peeling.N/AClear Anodize 204-R1 AA-M10C22A31(0.4 − 0.7 mil.)Architectural Class II. Clear, colorless and hard oxide aluminum coatingthat resists weathering and chemical attack. Recommended for normalweather exposure.1 yearPaint finish warranties are not applicable to steel products.Powdura®is a registered trademark of The Sherwin-Williams Company. Coraflon®and Envirocron®are registered trademarks of PPG Industries Ohio, Inc. Interpon®is a registered trademark of Akzo Nobel Powder Coatings Ltd.Kynar 500®is a registered trademark of Arkema, Inc.。

LCM1-1262A LoRaWAN 终端模块说明书

LCM1-1262A LoRaWAN终端模块说明书V2.2 LCM1-1262A LoRaWAN终端模块说明书版本V2.2LCM1-1262A LoRaWAN终端模块说明书V2.2一、产品说明LoRa联盟是2015年3月Semtech牵头成立的开放的、非盈利的组织.联盟发布一个基于开源的MAC层协议的低功耗广域网。

标准:LoRaWAN协议标准。

网络拓扑:星形结构。

网络构成:LoRa模块、网关(Gateway或称基站)、Server(包括Network Server,Network control,Application Server)。

LoRaWAN把LoRa模块分为A/B/C三类.、本产品使用SX1262作为射频芯片,搭建一款低功耗单片机来实现LORAWAN来进行数据的收发操作。

本产品支持全频段,315M、470M、868M、915M。

1.1技术参数类别指标名称无线模块无线射频调制方式LoRaTM扩频频率范围150-960MHz发射功率5dBm~22dBm接收灵敏度-148dBm(SF=12,BW=10.4K)传输速率扩频因子(SF)和带宽(BW)设置传输距离4000-6000米天线连接外置SMA天线、弹簧天线数据接口数据接口TTL电平串口信号TxD,RxD串口速率1200~115200bps 串口校验None,Even,Odd 数据位8LoRaWAN支持模式Class A/Class C功耗输入电压 3.3V最大发射电流≤105mA(20dBm)最大接收电流<5mA休眠电流<1.5uA工作环境工作温度-40℃~85℃外观尺寸长*宽*高38*20*4(mm)LCM1-1262A LoRaWAN终端模块说明书V2.2 1.2模块尺寸图1.3模块引脚定义无线数传模块提供了大量的外部接口供给客户进行二次开发,如只使用串口进行透传,可只保留所需对应焊盘,方便用户封装和使用,具体的引脚如下表:标识功能备注1VCC 3.3V2GND电源地3RXD串口接收口,接用户TX4TXD串口发送口,接客户RX5SWIM MCU芯片程序烧入,可做二次开发6RST复位脚,低电平复位7VCC 3.3V8GND电源地LCM1-1262A LoRaWAN终端模块说明书V2.29~20 24~31I/O足够的包括SPI,UART,ADC等各类功能接口,帮助进行二次开发,如有需要请联系21GND模块地22ANT天线23GND模块地二、LoRaWAN模式介绍LoRaWAN分成3种工作模式,分别为Class A,Class B,Class C2.1Class A模式主要用于定时主动上报,平时处理休眠状态,需要上报数据时,才会起动发送机制。

SM16126

SM16126内部功能简单框图管脚说明输出及输入等效电路◆OE输入端LE输入端◆CLK,SDI输入端SDO输出端◆OUT0~OUT15输出端时序图真值表最大极限参数特性代表符号最大限定范围单位电源电压VDD 0~7.0 V输入端电压V SDA,V CLK,V LE,V OE-0.4~VDD+0.4V V 电流输出端电流I OUT+65 mA 输出端承受电压V DS-0.5~+18.0 V 时钟频率f CLK25 MHz IC 工作时的环境温度T opr-40~+85 ℃IC 储存时的环境温度T stg-55~+150 ℃直流特性测试电路动态特性(VDD= 5.0V)特性代表符测量条件最小值一般值最大值单位延迟时间(低电平到高电平) CLK——OUT t pLH1V IH=VDDV IL=GNDRext=1100ΩVDD=5.0VR L=240ΩC L=10pF-- 30 -- ns LE——OUT t pLH2-- 25 -- ns OE——OUT t pLH3-- 27 -- ns CLK——SDO t pLH-- 24 -- ns延迟时间(高电平到低电平) CLK——OUT t pHL1-- 40 -- ns LE——OUT t pHL2-- 38 -- ns OE——OUT t pHL3-- 37 -- ns CLK——SDO t pHL-- 24 -- ns电流输出上升沿时间t OUT-RISE-- 40 -- ns电流输出下降沿时间t OUT-FALL-- 30 -- ns 动态特性(VDD= 3.3V)特性代表符测量条件最小值一般值最大值单位延迟时间(低电平到高电平) CLK——OUT t pLH1V IH=VDDV IL=GNDRext=1100ΩVDD=3.3VR L=120ΩC L=10pF-- 24 -- ns LE——OUT t pLH2-- 22 -- ns OE——OUT t pLH3-- 25 -- ns CLK——SDO t pLH-- 30 -- ns延迟时间(高电平到低电平) CLK——OUT t pHL1-- 42 -- ns LE——OUT t pHL2-- 39 -- ns OE——OUT t pHL3-- 39 -- ns CLK——SDO t pHL-- 30 -- ns电流输出上升沿时间t OUT-RISE-- 38 -- ns 电流输出下降沿时间t OUT-FALL-- 24 -- ns动态特性测试电路时序波形图CLKSDISDOLEOEOUTn产品应用将SM16126应用于LED面板设计上时,通道间甚至芯片间的电流,差异极小。

VK1612U7M3L规格书

GPS/GNSS

深圳市微科通讯设备有限公司

V.KEL Communications Equipment(SHENZHEN)Co.,Ltd

1.产品描述

VK1612U7M3L DataSheet

2

目录

产品名称: VK1612U7M3L

VK1612U7M3L GPS/GNSS模块是一个低功耗主芯片癿超小外型GPS接收模组,该产品采用了新 一代U-blox芯片,超高灵敏度,具备全方位功能,能满足丏业定位癿严格要求。内嵌在使用GPS服 务癿智慧型手机、平板电脑、PND、DVR、可携式装置,测量设备,人员定位管理,测速设备,授 时设备,交车跟踪定位、出租车跟踪定位、公司车辆跟踪定位、物流车辆跟踪定位、汽车故障检测、 汽车油量检测、汽车物联网、挖掘机定位等等。

深圳市微科通讯设备有限公司

V.KEL Communications Equipment(SHENZHEN)Co.,Ltd

VK1612U7M3L DataSheet

1

目录

GPS/GNSS

1.产品描述 .................................................................................................................. 2 2.产品型号编码规则 .................................................................................................... 3 3.产品应用范围 ........................................................................................................... 4 4.技术特性 .................................................................................................................. 5 5.模块工作原理 ........................................................................................................... 6 6.模块信号测试图和模块 RF 射频图............................................................................. 7

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。