PowerPC 405GP中文资料

PowerPC405开发板简要介绍

一、硬件方面:1、CPU介绍:PowerPC® 405 32-bit RISC processor,最高主频333MHz ,带一级数据和指令cache各16KB;PC-133 规范SDRAM 接口;PCI 2.2 规范接口(32-bit, 最高66MHz) ;两个片内以太网10/100Mbps 自适应MAC 提供MII接口;独立的Local BUS 两个串口,一个IIC接口。

2、开发板硬件配置:NOR FLASH:4MBit(512Kx8Bit);NAND FLASH: 64MB ;SDRAM 64MBLocal BUS总线提供外部接口;2个PCI接口;2个串口;2个10/100Mbps以太网接口;外接AC/DC电源适配器(5V输出),调试方便,并具有灵活的启动配置方式。

3、开发板PCB布局在EMC、系统的稳定性方面都做了全面的考虑。

附:开发板正面图:开发板反面图:1 :5V电源输入接口2:5V输入指示灯3:板上电源开关4:板上电源指示灯5:系统复位按钮6:JTAG接口7:PCI SLOT1 8:PCI SLOT2 9:GPIO扩展插座10:LOCAL BUS插座11:8bit NOR FLASH 12:串口013:串口1 14:ETH0-1 15:NAND FLASH16:启动模式配置17:CPU (PPC405EP)18:CPU部分3.3V电源跳线、指示灯19:CPU 部分1.8V电源跳线20-21:GND(方便测试用)此板在设计上具有以下优点:1):指示灯丰富:能直观的看到外接电源开关、板上电源是否工作正常。

尤其是将CPU部分的电源用跳线连接,防止意外烧坏CPU,用户在设计产品时可参考此方法。

2)、走线布局都非常讲究,对SDARM部分还做了走线的等长处理,以保证系统的可靠性和稳定性。

二、软件方面:提供eldk、uboot、linux2.4和linux2.6的BSP包。

三、特别提示:购买开发板后:我们会提供硬件原理图,芯片资料等;并提供较为全面的技术支持。

PowerPC单片机资料 、应用、价格、参数

MC9S12KG256VPVE

MC9S12KT256CPVE

MC9S12KT256VPVE

MC9S12T64CPKE16

MC9S12T64MPKE16

MC9S12XA256VAG

MC9S12XA512VAG

MC9S12XD256VAG

MC9S12XDT512VAA

MC9S12XDT512VAG

MC9S12DJ256VPVE

MC8610TPX800GB MC8610TVT800GB MC7457RX1000LC MC8640HX1067NE MC8640VU1067NE MC8640VU1000HE MC7447AVS1267LB MC7447AVU1267LB MPC7410THX450NE MC7447AVS1167NB MC7447AHX1167NB MC7457RX1000NC MC8610TPX1066JB MC8610TVT1066JB MC7448THX1000ND MC7448TVU1000ND 型 号 MC7457VG1000NC MC8640DHX1000HE MC8640DVU1000HE KMC7447AHX1167NB KMC7447AVS1167NB MC8640DHX1067NE MC8640DVU1067NE MC8640DHX1250HE MPC7410THX500LE MC7448VS1250ND MC7448VU1250ND MC7448HX1250ND MC8640DTHX1000HC MC8640DTHX1000HE MC8610PX1333JB MC8610VT1333JB MC8641DHX1000GE MC7448HX1420LD KMC7457RX1000NC KMC8610VT1333JB

MC9S12E128VFUE

什么是MIPS,PowerPC是什么

什么是MIPS,PowerPC是什么

MIPS

MIPS是Microprocessor without Inter---locked Pipeline Stages的缩写,是一种处理器内核标准,它是由MIPS技术公司开发的。

MIPS技术公司是一家设计制造高性能、高档次的嵌入式32位和64位处理器的厂商,在RISC处理器方面占有重要地位。

2000年,MIPS 公司发布了针对MIPS 32 4Kc的新版本以及未来64位MIPS 64 20Kc处理器内核。

MIPS技术公司既开发MIPS处理器结构,又自己生产基于MIPS的32位

/64位芯片。

为了使用户更加方便地应用MIPS处理器,MIPS公司推出了一套集成的开发工具,称为MIPSIDF(Integrated Dev--elopment Framework),特别适用于嵌入式系统的开发。

PowerPC

PowerPC架构的特点是可伸缩性好,方便灵活。

PowerPC处理器品种很多,既有通用的处理器,又有嵌入式控制器和内核,应用范围非常广泛,从高端的工作站、服务器到桌面计算机系统,从消费类电子产品到大型通信设备等各个方面。

目前PowerPC独立微处理器与嵌入式微处理器的主频从25MHz~700MHz

不等,它们的能量消耗、大小、整合程度、价格差异悬殊,主要产品模块有主频350MHz~700MHz PowerPC 750CX和750CXe以及主频400MHz的。

PowerPC处理器原理介绍

PowerPC处理器结构 PowerPC处理器体系结构概述

6、调试 PowerPC405处理器调试资源包括特殊调试模型,在 硬件和软件开发过程中,支持各种类型调试。这些调试包 括: 1)内部调试模式:ROM监控程序和软件调试器 2)外部调试模式:JTAG调试器 3)调试等待模式:处理器停下来允许服务中断 4)实时跟踪模式:事件触发用于实时跟踪

PowerPC处理器结构 PowerPC处理器体系结构概述

缓存控制器采用了最近使用的LRU的缓存行替换策略 。即缓存行被填充时,最近经常访问的缓存行被保留,而 其它均被替换。

指令缓存的功能包括:16KB,双向级关联(2-way set associative);奇偶检测和报告(只有Virtex-4);每缓存 行8字(32字节);提取行缓冲区;提供了来自提取行缓 冲区的取指命中;下一个顺序行的可编程预取到提取行缓 冲区;非缓存指令的可编程预取:全行(8字)/半行(4 字);提取行满时,非阻塞访问。

容。

PowerPC处理器结构 PowerPC处理器体系结构概述

PowerPC处理器是定点处理器,它与PowerPC UISA兼 容。PowerPC405 VEA和OEA支持大部分都可以用来实现 PowerPC405 Book-E的结构。图3.1给出了PowerPC处理器 的结构图。

PowerPC处理器结构 PowerPC处理器体系结构概述

PowerPC处理器结构 PowerPC处理器体系结构概述

4、指令和数据缓存 PowerPC处理器通过指令缓存单元ICU和数据缓存单 元DCU访问存储器。每个缓存单元包括: 1)PLB主接口 2)缓存阵列 3)缓存控制器; 对于CPU来说,对指令和数据缓存的命中是单周期的 存储器访问。处理缓存缺失,就是通过PLB向其它PLB设 备发出请求,比如外部存储器控制器。

IBM Power架构发展史

IBM Power架构发展史2007-05-10 嵌入式在线收藏 | 打印1980:·IBM 发布了第一台基于RISC(精简指令集计算机)架构的原型机。

早在上世纪70年代初,基于IBM 科学家 John Cocke的发明,RISC的理念大大简化了计算机操作指令,加快系统运行速度,使得计算机性能得到大幅度提升。

如今,RISC架构已经广泛应用于众多工作站和UNIX服务器系统中,并被看作是未来主流的计算架构。

1990:·IBM 推出基于RISC系统、运行AIX V3的新产品线RS/6000(现在称为IBM eServ er p系列)。

该系统架构后来被称为POWER(POWER1),意为增强RISC性能优化(P erformance Optimization With Enhanced RISC)架构。

1991:·IBM和苹果、摩托罗拉公司达成一系列合作协议,内容包括:推出支持苹果 Macintos h个人电脑与IBM网络相连的全新产品;推出面向PC机和低成本工作站的RISC架构Po werPC处理器;形成一个开放的系统环境,保证IBM AIX和苹果Macintosh软件程序在两家公司设计的RISC系统中都能运行。

此外,开放的系统环境包括其他一些技术协议。

1993:·IBM 推出可升级的POWER并行系统,这是第一款采用RS/6000技术,基于微处理器的超级计算机。

在该系统中,IBM 首次应用多处理器技术,可将复杂密集的任务进行分解,大大加快了计算机的运算速度,开创了业界先河。

·IBM和摩托罗拉公司推出PowerPC 601处理器,该处理器是与苹果共同开发的。

Po werPC上集成280多万个晶体管,主频为50 MHz。

·IBM 发布了66 MHz 的POWER2 处理器,首先应用于RS/6000系统。

1994:·IBM 推出可升级的POWER并行系统 2 (Scalable POWERparallel,SP2)。

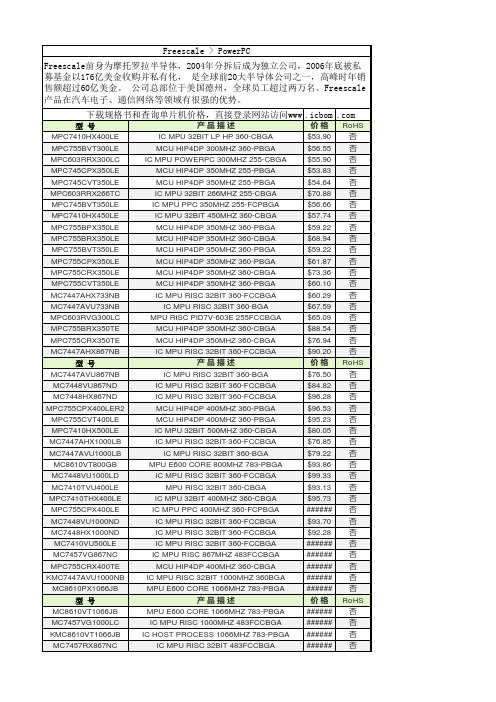

PowerPC价格数据大全

PowerPCFreescale(飞思卡尔)Freescale前身为摩托罗拉半导体,2004年分拆后成为独立公司,2006年底被私募基金以176亿美金收购并私有化, 是全球前20大半导体公司之一,高峰时年销售额超过60亿美金。

公司总部位于美国德州,全球员工超过两万名。

Freescale产品在汽车电子、通信网络等领域有很强的优势。

PowerPC介绍PowerPC 处理器有广泛的实现范围,包括从诸如 Power4 那样的高端服务器CPU 到嵌入式 CPU 市场( PowerPC任天堂 Gamecube 使PowerPC)。

PowerPC 处理器有非常强的嵌入式表现,因为它具有优异的性能、较低的能量损耗以及较低的散热量。

除了象串行和以太网控制器那样的集成I/O,该嵌入式处理器与台式机CPU 存在非常显著的区别。

例如,4xx 系列 PowerPC 处理器缺乏浮点运算,并且还使用一个受软件控制的 TLB 进行内存管理,而不是象台式机芯片中那样采用反转页表。

PowerPC 处理器有 32 个(32 位或 64 位)GPR(通用寄存器)以及诸如 PC(程序计数器,也称为 IAR/指令地址寄存器或 NIP/下一指令指针)、LR(链接寄存器)、CR(条件寄存器)等各种其它寄存器。

有些 PowerPC CPU 还有 32 个 64 位 FPR(浮点寄存器)。

PowerPC系列单片机价格产品型号产品描述价格$ MPC5200VR400B IC MPU PROCESSOR 32BIT 272-PBGA 27.218MPC5200CVR400B IC MPU 32BIT 400MHZ 272-PBGA 31.979MPC7410VS400LE IC MPU 32BIT 400MHZ 360-FCCLGA 65.987MPC755BPX300LE IC MPU 300MHZ PPC 360-FCPBGA 72.157MC7447AVS733NB IC MPU RISC 733MHZ 360-FCCLGA 81.735MC7447AVS1000LB IC MPU RISC 1000MHZ 360-FCCLGA 102.866MPC755CRX400LE IC MPU 32BIT 400MHZ PPC 360-CBGA 115.064MC7447AVS1000NB IC MPU RISC 1000MHZ 360-FCCLGA 119.369MPC7410VS500LE IC MPU PPC 500MHZ 360-FCCLGA 143.68MC7447AHX1000NB IC MPU RISC 1000MHZ 360-FCCBGA 155.596MC7447ATHX1000NB IC MPU RISC 1000MHZ 360-FCCBGA 284.995MC7447AVS1333LB IC MPU RISC 1333MHZ 360-FCCLGA 310.334MC7448HX1400ND IC MPU RISC 32BIT 360-FCCBGA 451.04SPC5200CVR400 IC MPU 32BIT 400MHZ 272-PBGA 32.967MPC5200VR400 IC MPU 32BIT 400MHZ PPC 272-PBGA 37.429MC7447AHX600NB IC MPU RISC 600MHZ 360-FCCBGA 59.496MC7447AVU1000NB IC MPU RISC 32BIT 360-BGA 180.047MC7447AHX1420LB IC MPU RISC 1420MHZ 360-FCCBGA 266.336MPC184VMB IC SECURITY PROCESSOR252-MAPBGA 18.076MPC184VFB ICSECURITYPROCESSOR 252-PBGA 18.885 SPC5200CBV400BR2 IC MPU 32BIT 400MHZ 272-PBGA 21.929 SPC5200CVR400BR2 IC MPU 32BIT 400MHZ 272-PBGA 20.558 SPC5200CVR400B IC MPU 32BIT 400MHZ 272-PBGA 23.072 SPC5200CBV400B IC MPU 32BIT 500MHZ 272PBGA 21.447 SPC5200CBV400R2 IC MPU 32BIT 400MHZ 272-PBGA 33.724 MPC5200CBV266 IC MPU 32BIT 266MHZ 272-PBGA 30.793 MPC5200BV400 IC MPU 32BIT 400MHZ 272-PBGA 36.773 MPC5200CBV400 IC MPU 32BIT 400MHZ PPC 272-PBGA 34.733 SPC5200CBV400 IC MPU 32BIT 400MHZ 272-PBGA 36.464 MPC603RZT200LC IC MPU 32BIT 200MHZ PPC 255-PBGA 37.646 MPC5200CVR400 IC MPU 32BIT 400MHZ PPC 272-PBGA 43.189 MPC603RRX200LC IC MPU POWERPC 200MHZ 255-CBGA 46.972 MPC603RRX200TC IC MPU 32BIT 200MHZ 255-CBGA 55.96 MPC603RRX266LC IC MPU 32BIT 266MHZ 255-CBGA 62.125 MPC603RVG200LC MPU RISC PID7V-603E 255FCCBGA 53.339 MPC745BPX300LE MCU HIP4DP 300MHZ 255-PBGA 58.038 MPC745BVT300LE MCU HIP4DP 300MHZ 255-PBGA 52.692 MC7447AVU600NB IC MPU RISC 32BIT 360-BGA 60.897MC7448VU600ND IC MPU RISC 32BIT 360-FCCBGA 64.337 MC7448HX600ND IC MPU RISC 32BIT 360-FCCBGA 62.708 MC7410VU400LE IC MPU RISC 32BIT 360-FCCBGA 62.084 MPC7410HX400LE IC MPU 32BIT LP HP 360-CBGA 61.256 MPC755BVT300LE MCU HIP4DP 300MHZ 360-PBGA 64.266 MPC603RRX300LC IC MPU POWERPC 300MHZ 255-CBGA 63.518 MPC745CPX350LE MCU HIP4DP 350MHZ 255-PBGA 61.17 MPC745CVT350LE MCU HIP4DP 350MHZ 255-PBGA 62.097 MPC603RRX266TC IC MPU 32BIT 266MHZ 255-CBGA 80.546 MPC745BVT350LE IC MPU PPC 350MHZ 255-FCPBGA 64.39 MPC7410HX450LE IC MPU 32BIT 450MHZ 360-CBGA 65.619 MPC755BPX350LE MCU HIP4DP 350MHZ 360-PBGA 67.291HIP4DP 350MHZ 360-CBGA 78.339 MPC755BRX350LE MCUMPC755BVT350LE MCU HIP4DP 350MHZ 360-PBGA 67.291 MPC755CPX350LE MCU HIP4DP 350MHZ 360-PBGA 70.304HIP4DP 350MHZ 360-CBGA 83.36 MPC755CRX350LE MCUMPC755CVT350LE MCU HIP4DP 350MHZ 360-PBGA 68.295 MC7447AHX733NB IC MPU RISC 32BIT 360-FCCBGA 68.507 MC7447AVU733NB IC MPU RISC 32BIT 360-BGA 76.811 MPC603RVG300LC MPU RISC PID7V-603E 255FCCBGA 73.968 MPC755BRX350TE MCU HIP4DP 350MHZ 360-CBGA 100.612 MPC755CRX350TE MCU HIP4DP 350MHZ 360-CBGA 87.437 MC7447AHX867NB IC MPU RISC 32BIT 360-FCCBGA 102.499 MC7447AVU867NB IC MPU RISC 32BIT 360-BGA 86.929 MC7448VU867ND IC MPU RISC 32BIT 360-FCCBGA 96.388 MC7448HX867ND IC MPU RISC 32BIT 360-FCCBGA 109.413 MPC755CPX400LER2 MCU HIP4DP 400MHZ 360-PBGA 109.691 MPC755CVT400LE MCU HIP4DP 400MHZ 360-PBGA 108.215 MPC7410HX500LE IC MPU 32BIT 500MHZ 360-CBGA 90.963 MC7447AHX1000LB IC MPU RISC 32BIT 360-FCCBGA 87.332 MC7447AVU1000LB IC MPU RISC 32BIT 360-BGA 90.019 MC8610VT800GB MPU E600 CORE 800MHZ 783-PBGA 106.659 MC7448VU1000LD IC MPU RISC 32BIT 360-FCCBGA 112.877 MC7410TVU400LE MPU RISC 32BIT 360-CBGA 105.831 MPC7410THX400LE IC MPU 32BIT 400MHZ 360-CBGA 108.782 MPC755CPX400LE IC MPU PPC 400MHZ 360-FCPBGA 119.433 MC7448VU1000ND IC MPU RISC 32BIT 360-FCCBGA 106.477 MC7448HX1000ND IC MPU RISC 32BIT 360-FCCBGA 104.864 MC7410VU500LE IC MPU RISC 32BIT 360-FCCBGA 133.434 MC7457VG867NC IC MPU RISC 867MHZ 483FCCBGA 127.151 MPC755CRX400TE MCU HIP4DP 400MHZ 360-CBGA 117.282 KMC7447AVU1000NB IC MPU RISC 32BIT 1000MHZ 360BGA 127.658MC8610PX1066JB MPU E600 CORE 1066MHZ 783-PBGA 138.583 MC8610VT1066JB MPU E600 CORE 1066MHZ 783-PBGA 135.202 MC7457VG1000LC IC MPU RISC 1000MHZ 483FCCBGA 115.572KMC8610VT1066JB IC HOST PROCESS 1066MHZ783-PBGA 147.4MC7457RX867NC IC MPU RISC 32BIT 483FCCBGA 157.264 MC8610TPX800GB MPU E600 CORE 800MHZ 783-PBGA 139.086 MC8610TVT800GB MPU E600 CORE 800MHZ 783-PBGA 127.332 MC7457RX1000LC IC MPU RISC 32BIT 483FCCBGA 158.121MC8640HX1067NE IC DUAL CORE PROCESSOR994-CBGA 158.814MC8640VU1067NE IC MPU SGL CORE E600 1023FCCBGA 148.762 MC8640VU1000HE IC MPU SGL CORE E600 1023FCCBGA 146.455 MC7447AVS1267LB IC MPU RISC 1267MHZ 360-FCCLGA 160.372 MC7447AVU1267LB IC MPU RISC 32BIT 360-BGA 139.811 MPC7410THX450NE MCURISC1.8V 450MHZ 360-CBGA 172.341 MC7447AVS1167NB IC MPU RISC 1167MHZ 360-FCCLGA 179.704 MC7447AHX1167NB IC MPU RISC 1167MHZ 360-FCCBGA 206.783 MC7457RX1000NC IC MPU RISC 32BIT 483FCCBGA 192.185 MC8610TPX1066JB MPU E600 CORE 1066MHZ 783-PBGA 207.879 MC8610TVT1066JB MPU E600 CORE 1066MHZ 783-PBGA 190.134 MC7448THX1000ND IC MPU RISC 32BIT 360-FCCBGA 196.136 MC7448TVU1000ND MPU 128BIT 1000MHZ 360-CBGA 206.324 MC7457VG1000NC IC MPU RISC 1000MHZ 483FCCBGA 206.189MC8640DHX1000HE IC DUAL CORE PROCESSOR1023-CBGA 185.023MC8640DVU1000HE IC MPU DUAL CORE E6001023FCCBGA 219.883KMC7447AHX1167NB IC MPU RISC 32BIT 1167MHZ 360BGA 182.498 KMC7447AVS1167NB IC MPU RISC 1167MHZ 360-LGA 217.388MC8640DHX1067NE IC DUAL CORE PROCESSOR1023-CBGA 224.216MC8640DVU1067NE IC MPU DUAL CORE E6001023FCCBGA 226.984MC8640DHX1250HE IC DUAL CORE PROCESSOR1023-CBGA 197.849MPC7410THX500LE IC MPU 32BIT 500MHZ 360-CBGA 194.278 MC7448VS1250ND IC MPU RISC 1250MHZ 360-FCCLGA 210.471 MC7448VU1250ND IC MPU RISC 32BIT 360-FCCBGA 222.164 MC7448HX1250ND IC MPU RISC 32BIT 360-FCCBGA 228.01 MC8640DTHX1000HC MPUDUALE600 1023-FCCBGA 224.553 MC8640DTHX1000HE ICDUAL CORE PROCESSOR 227.5871023-CBGAMC8610PX1333JB MPU E600 CORE 1333MHZ 783-PBGA 255.537 MC8610VT1333JB MPU E600 CORE 1333MHZ 783-PBGA 200.779MC8641DHX1000GE IC DUAL CORE PROCESSOR1023-CBGA 229.448MC7448HX1420LD IC MPU RISC 32BIT 360-FCCBGA 235.256 KMC7457RX1000NC IC MPU RISC 32BIT 1000MHZ 483BGA 221.639KMC8610VT1333JB IC HOST PROCESS 1333MHZ783-PBGA 218.896MC7457VG1267LC IC MPU RISC 1267MHZ 483FCCBGA 283.013MC8640DVU1250HE IC MPU DUAL CORE E6001023FCCBGA 246.083MC8640THX1067NE IC DUAL CORE PROCESSOR994-CBGA 260.891MC8640TVU1067NE IC MPU SGL CORE E600 1023FCCBGA 260.891MC8641DVU1250HC IC MPU DUAL E600 CORE1023FCCBGA 248.855MC8641DHX1250HE IC DUAL CORE PROCESSOR1023-CBGA 245.35MC8641HX1000GE IC DUAL CORE PROCESSOR994-CBGA 236.369MC7448VU1600LD IC MPU RISC 32BIT 360-FCCBGA 292.719 MC7447AVU1420LB IC MPU RISC 32BIT 360-BGA 283.883MC8641HX1333JE IC DUAL CORE PROCESSOR994-CBGA 249.663MC8641VU1333JE IC MPU SGL CORE E600 1023FCCBGA 260.518MC8641DHX1000NE IC DUAL CORE PROCESSOR1023-CBGA 294.56MC7448VU1400ND IC MPU RISC 32BIT 360-FCCBGA 310.611 MC7448VS1400ND IC MPU RISC 1400MHZ 360-FCCLGA 281.029MC8640DTVU1000HE IC MPU DUAL CORE E6001023FCCBGA 299.655MC7457RX1267LC IC MPU RISC 32BIT 483FCCBGA 300.594MC8641DVU1000GE IC MPU DUAL CORE E6001023FCCBGA 263.863MC7448VU1700LD IC MPU RISC 32BIT 360-FCCBGA 258.65 MC7448VU1267ND IC MPU RISC 32BIT 360-FCCBGA 277.952 MC7448HX1700LD IC MPU RISC 32BIT 360-FCCBGA 270.231 MC7448VS1267ND IC MPU RISC 1267MHZ 360-FCCLGA 254.789 MC7448VS1700LD IC MPU RISC 1700MHZ 360-FCCLGA 270.231 MC7448HX1267ND IC MPU RISC 32BIT 360-FCCBGA 258.65 MC7447ATHX1167NB IC MPU RISC 1167MHZ 360-FCCBGA 312.568KMC7448HX1400ND IC MPU 128BIT 1400MHZ 360-FCCBGA 266.237 KMC7448VU1400ND IC MPU 128BIT 1400MHZ 360-FCCBGA 266.237 KMC7448HX1267ND IC MPU 128BIT 1267MHZ 360-FCCBGA 259.785MC8641DHX1333JE IC DUAL CORE PROCESSOR1023-CBGA 304.096MC8641DVU1333JE IC MPU DUAL CORE E6001023FCCBGA 284.35KMC7457RX1267LC IC MPU RISC 32BIT 1267MHZ 483BGA 277.987MC8641HX1000NE IC DUAL CORE PROCESSOR994-CBGA 268.363MC8641VU1000NE IC MPU SGL CORE E600 1023FCCBGA 292.759 KMC7448HX1700LD IC MPU 128BIT 1700MHZ 360-FCCBGA 343.35 KMC7448VU1267ND IC MPU RISC 32BIT 360-FCCBGA 314.738 KMC7448VU1700LD IC MPU 128BIT 1700MHZ 360-FCCBGA 314.741 MC8641DTHX1000GC MPU E600 DUAL CORE 1023-FCCBGA 331.136 MC8640DTVU1000NC MPU DUAL E600 994-FCCBGA 323.354MC8640DTHX1067NE IC MPU DUAL CORE E6001023FCCBGA 352.75MC8640DTVU1067NE IC MPU DUAL CORE E6001023FCCBGA 310.756KMC7457VG1267LC IC MPU RISC 32BIT 1267MHZ 483BGA 290.593MC8641DHX1500KE IC DUAL CORE PROCESSOR1023-CBGA 311.456MC8641DVU1500KE IC MPU DUAL CORE E6001023FCCBGA 302.682MC8641DVU1000NE IC MPU DUAL CORE E6001023FCCBGA 349.798MC8640TVU1250HE IC MPU SGL CORE E600 1023FCCBGA 414.226MC8641DTVU1000GE IC MPU DUAL CORE E6001023FCCBGA 382.876MC7448THX1400ND IC MPU RISC 32BIT 360-FCCBGA 340.119MC8641DTHX1250HE IC DUAL CORE PROCESSOR1023-CBGA 444.578MC8641DTVU1250HE IC MPU DUAL CORE E6001023FCCBGA 391.652MC8640DTHX1250HE IC DUAL CORE PROCESSOR1023-CBGA 398.016MC8640DTVU1250HE IC MPU DUAL CORE E6001023FCCBGA 453.296KMC7448THX1400ND IC MPU 128BIT 1400MHZ 360-FCCBGA 387.828 MC8641DTHX1000NC MPU E600 DUAL CORE 1023-FCCBGA 416.985 MC8641DTVU1000NC MPU E600 DUAL CORE 1023-FCCBGA 411.425MC7448TVU1267ND IC MPU SGL E600 CORE 360-FCCBGA 426.459 MC7457TRX1000NC IC MPU RISC 32BIT 483FCCBGA 450.005MC8641DTHX1333JE IC DUAL CORE PROCESSOR1023-CBGA 429.372MC8641DTVU1333JE IC MPU DUAL CORE E6001023FCCBGA 483.044MC7448THX1267ND IC MPU RISC 32BIT 360-FCCBGA 572.2 MPC750ARX266LH IC MPU POWERPC 266MHZ 361-CBGAMPC740ARX233LH IC MPU POWERPC 233MHZ 255-CBGAMPC740ARX266LH IC MPU POWERPC 266MHZ 255-CBGAMPC106ARX83DG IC MPU PCI CONTROLLER 304CBGAMPC106ARX66CG IC MPU PCI CONTROLLER 304CBGAMPC7410RX500LE IC MPU 32BIT 500MHZ PPC 360-CBGA 115.102 MPC745BPX350LE IC MPU PPC 350MHZ 255-FCPBGAMPC755BRX300LE IC MPU 32BIT 300MHZ PPC 360-CBGAMC7447AVS1420LB IC MPU RISC 1420MHZ 360-FCCLGA 223.217 MC7447AVS600NB IC MPU RISC 600MHZ 360-FCCLGA 47.546 MC7447AVS867NB IC MPU RISC 867MHZ 360-FCCLGA 86.517MPC190VMB IC SECURITY PROCESSOR 252-MAPBGAMPC5200CVR266 IC MPU 32BIT 266MHZ PPC 272-PBGA 35.202 MPC7410VS400NE IC MPU 32BIT 400MHZ 360-FCCLGA 101.049 MPC7410VS450LE IC MPU 32BIT 450MHZ 360-FCCLGA 72.734 MPC7410VS450NE IC MPU 32BIT 450MHZ 360-FCCLGA 132.523 SPC5200CVR400R2 IC MPU 32BIT 400MHZ 272-PBGAKMC7410VS500LE IC MPU RISC 32BIT 500MHZ 360-LGA 139.893 KMC7447AHX1420LB IC MPU RISC 32BIT 1420MHZ 360BGA 270.904 KMC7447AVS1420LB IC MPU RISC 32BIT 1420MHZ 360LGA 308.529 KMC7447AVU1420LB IC MPU RISC 32BIT 1420MHZ 360BGA 314.588 KMC7448HX1400NC IC MPU 128BIT 1400MHZ 360-FCCBGA 340.751 KMC7448HX1700LC IC MPU 128BIT 1700MHZ 360-FCCBGA 368.928 KMC7448VS1400NC IC MPU 128BIT 1400MHZ 360-FCCLGAKMC7448VS1700LC IC MPU 128BIT 1700MHZ 360-FCCLGAKMC7448VU1400NC IC MPU 128BIT 1400MHZ 360-FCCBGAKMC7448VU1700LC IC MPU 128BIT 1700MHZ 360-FCCBGA 364.536 KMC7457VG1000NC IC MPU RISC 32BIT 1000MHZ 483BGA 255.456 MC7410VU400NE IC MPU RISC 32BIT 360-FCCBGA 99.683 MC7410VU450NE IC MPU RISC 32BIT 360-FCCBGA 144.047 MC7447AHX1267LB IC MPU RISC 32BIT 360-FCCBGA 159.333 MC7447AVU1167NB IC MPU RISC 32BIT 360-BGAMC7447AVU1333LB IC MPU RISC 32BIT 360-BGA 188.79 MC7448HX1000LC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1000NC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1250NC IC MPU RISC 32BIT 360-FCCBGA 216.553 MC7448HX1267NC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1400NC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1420LC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1600LC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1700LC IC MPU RISC 32BIT 360-FCCBGA 248.602 MC7448HX600NC IC MPU RISC 32BIT 360-FCCBGAMC7448HX667NC IC MPU RISC 32BIT 360-FCCBGAMC7448HX867NC IC MPU RISC 32BIT 360-FCCBGAMC7448VS1000LC IC MPU RISC 1000MHZ 360-FCCLGAMC7448VS1000NC IC MPU RISC 1000MHZ 360-FCCLGAMC7448VS1250NC IC MPU RISC 1250MHZ 360-FCCLGA 208.224 MC7448VS1267NC IC MPU RISC 1267MHZ 360-FCCLGA 294.264 MC7448VS1400NC IC MPU RISC 1400MHZ 360-FCCLGA 274.752 MC7448VS1420LC IC MPU RISC 1420MHZ 360-FCCLGA 223.361 MC7448VS1600LC IC MPU RISC 1600MHZ 360-FCCLGA 268.785 MC7448VS1700LC IC MPU RISC 1700MHZ 360-FCCLGA 313.621 MC7448VS600NC IC MPU RISC 600MHZ 360-FCCLGAMC7448VS667NC IC MPU RISC 667MHZ 360-FCCLGAMC7448VS867NC IC MPU RISC 867MHZ 360-FCCLGAMC7448VU1000LC IC MPU RISC 32BIT 360-FCCBGAMC7448VU1000NC IC MPU RISC 32BIT 360-FCCBGAMC7448VU1250NC IC MPU RISC 32BIT 360-FCCBGAMC7448VU1267NC IC MPU RISC 32BIT 360-FCCBGA 303.048 MC7448VU1400NC IC MPU RISC 32BIT 360-FCCBGAMC7448VU1420LC IC MPU RISC 32BIT 360-FCCBGAMC7448VU1600LC IC MPU RISC 32BIT 360-FCCBGA 293.541 MC7448VU1700LC IC MPU RISC 32BIT 360-FCCBGAMC7448VU600NC IC MPU RISC 32BIT 360-FCCBGAMC7448VU667NC IC MPU RISC 32BIT 360-FCCBGAMC7448VU867NC IC MPU RISC 32BIT 360-FCCBGAMC7457RX733NC IC MPU RISC 32BIT 483FCCBGAMC7457VG733NC IC MPU RISC 733MHZ 483FCCBGAKMC755CVT400LE IC MPU 32BIT 400MHZ 360-FCPBGA 109.087 KMC7448VS1400ND IC MPU 128BIT 1400MHZ 360-FCCLGA 319.72 MC7448VU667ND IC MPU RISC 32BIT 360-FCCBGA 62.161 MC7448VU1600PD IC MPU RISC 32BIT 360-FCCBGA 165.017 MC7448VU1420LD IC MPU RISC 32BIT 360-FCCBGA 218.342 MC7448VS1000LD IC MPU RISC 1000MHZ 360-FCCLGA 91.754 MC7448HX667ND IC MPU RISC 32BIT 360-FCCBGA 61.321 MC7448VS1000ND IC MPU RISC 1000MHZ 360-FCCLGA 96.743MC7448VS667ND IC MPU RISC 667MHZ 360-FCCLGA 64.681 MC7448VS867ND IC MPU RISC 867MHZ 360-FCCLGA 78.527 MC7448VS600ND IC MPU RISC 600MHZ 360-FCCLGA 56.707 MC7448VS1600LD IC MPU RISC 1600MHZ 360-FCCLGA 272.14 MC7448VS1420LD IC MPU RISC 1420MHZ 360-FCCLGA 249.095 MC7448HX1600LD IC MPU RISC 32BIT 360-FCCBGA 278.86 MC7448HX1000LD IC MPU RISC 32BIT 360-FCCBGA 91.754 MPC5200VR400BR2 IC MPU 32BIT 400MHZ 272-PBGAKMC7448VS1267ND IC MPU 128BIT 1267MHZ 360-FCCLGA 304.578 KMC7448VS1700LD IC MPU 128BIT 1700MHZ 360-FCCLGA 283.716。

PowerPC

IBM推出可升级的POWER并行系统,这是第一款采用RS/6000技术,基于微处理器的超级计算机。

谢谢观看

系统接口单元SIU的功能是提供内部总线和外部总线的接口,该接口单元具有32位微处理器的几乎所有的通 用接口特性,尽管Power PC核内部总线为32位,但通过SIU可以将外部总线宽度动态地配置成8、16或32位,以 兼容数据总线宽度为8、 16或32位的外设或存储器。

SIU单元中的存储器控制器支持最多与高达8组存储器的无缝连接,每组的容量从32K字节到256M字节可变, 数据总线宽度可由4个独立的使能信号控制为8bits,16bits或32bits。支持的存储器类型包括SRAM、SSRAM、 EPOM、Flash ROM、DRAM,SDRAM等。存储器控制器为每一组存储器分别提供了可选的0到15个的等待状态以适应 不同速度的存储器。SIU也支持其它需要双时钟访问的外部SRAM和用突发方式访问的外部设备。

PowerPC处理器有 32个(32位或 64位)GPR(通用寄存器)以及诸如 PC(程序计数器,也称为 IAR/指令 寄存器或 NIP/下一指令指针)、LR(链接寄存器)、CR(条件寄存器)等各种其它寄存器。有些 PowerPC CPU 还有 32个 64位 FPR(浮点寄存器)。

PowerPC体系结构是 RISC(精简指令集计算)体系结构的一个示例。因此:

联盟运作

联盟运作

联盟三巨头,个个有来头,因此联盟采行的是松散制联盟。也就是说,联盟的目标一致,但彼此并没有隶属 关系,运作时也难以强制成员遵行。不过联盟负责制定规格、进行授权与认证等相关工作。

分工方面,摩托罗拉主司芯片设计、制造。苹果电脑则是负责操作系统,还有组装及销售。IBM不愧是信息 界的全能选手,他从上游的芯片设计、制造,到中游的系统整合、测试、操作系统,及下游的组装、销售,不但 能全面参与,向来亦是个中好手。

PPC405EP中文资料

Part Number PPC405EPRevision 1.07 – September 10, 2007 PPC405EPPowerPC 405EP Embedded ProcessorData Sheet Features•AMCC PowerPC® 405 32-bit RISC processor core operating up to 333MHz with 16KB D-and I-caches•PC-133 synchronous DRAM (SDRAM) inter-face- 32-bit interface for non-ECC applications •4KB on-chip memory (OCM)•External peripheral bus- Flash ROM/Boot ROM interface- Direct support for 8- or 16-bit SRAM andexternal peripherals- Up to five devices•DMA support for memory and UARTs.- Scatter-gather chaining supported- Four channels•PCI Revision 2.2 compliant interface (32-bit, up to 66MHz)- Asynchronous PCI Bus interface- Internal or external PCI Bus Arbiter•Two Ethernet 10/100Mbps (full-duplex) ports with media independent interface (MII)•Programmable interrupt controller supports seven external and 19 internal edge-triggered or level-sensitive interrupts •Programmable timers•Software accessible event counters•Two serial ports (16750 compatible UART)•One IIC interface•General purpose I/O (GPIO) available •Supports JTAG for board level testing •Internal processor local bus (PLB) runs at SDRAM interface frequency•Supports PowerPC processor boot from PCI memoryDescriptionDesigned specifically to address embedded applications, the PowerPC 405EP (PPC405EP) provides a high-performance, low-power solution that interfaces to a wide range of peripherals by incorporating on-chip power management features and lower power dissipation requirements.This chip contains a high-performance RISC processor core, SDRAM controller, PCI bus interface, Ethernet interface, control for external ROM and peripherals, DMA with scatter-gather support, serial ports, IIC interface, and general purpose I/O. Technology: CMOS SA-27E, 0.18 μm (0.11 μm L eff) Package: 31mm, 385-ball, enhanced plastic ball grid array (E-PBGA)Power (typical): 0.72W at 266MHzPPC405EP – PowerPC 405EP Embedded Processor Revision 1.07 – September 10, 2007Data Sheet Table of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Ordering, PVR, and JTAG Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 Address Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 PLB to PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 SDRAM Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 External Peripheral Bus Controller (EBC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 IIC Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 General Purpose IO (GPIO) Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Universal Interrupt Controller (UIC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 10/100 Mbps Ethernet MAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Pin Lists . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Signal List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49PPC405EP – PowerPC 405EP Embedded Processor Revision 1.07 – September 10, 2007Data Sheet List of FiguresPPC405EP Embedded Controller Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 31mm, 385-Ball E-PBGA Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 5V-Tolerant Input Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Clocking Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Input Setup and Hold Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 Output Delay and Float Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 List of TablesSystem Memory Address Map (4GB System Memory) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 DCR Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Signals Listed Alphabetically . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Signals Listed by Ball Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Pin Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Signal Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Package Thermal Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Recommended DC Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 Input Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 Clocking Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Peripheral Interface Clock Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43 I/O Specifications—Group 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 I/O Specifications—Group 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47 Strapping Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48PPC405EP – PowerPC 405EP Embedded ProcessorRevision 1.07 – September 10, 2007Data SheetOrdering, PVR, and JTAG InformationThis section provides the part number nomenclature. For availability, contact your local AMCC sales office.The part number contains a part modifier. Included in the modifier is a revision code. This refers to the die mask revision number and is specified in the part numbering scheme for identification purposes only.The PVR (Processor Version Register) and the JTAG ID register are software accessible (read-only) and contain information that uniquely identifies the part. Refer to the PowerPC 405EP Embedded Processor User’s Manual for details on accessing these registers.Order Part Number KeyProduct Name Order Part Number 1, 2Processor Frequency PackageRev Level PVR Value JTAG ID PPC405EP PPC405EP-3GB133C 133MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3GB133CZ 133MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3LB133C 133MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3LB133CZ 133MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3GB200C 200MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3GB200CZ 200MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3LB200C 200MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3LB200CZ 200MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3GB266C 266MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3GB266CZ 266MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3LB266C 266MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3LB266CZ 266MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3GB333C 333MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3GB333CZ 333MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EP PPC405EP-3LB333C 333MHz 31mm, 385 ball E-PBGA B 0x512109500x20267049PPC405EPPPC405EP-3LB333CZ333MHz31mm, 385 ball E-PBGAB0x512109500x20267049Notes: 1. Z at the end of the Order Part Number indicates a tape and reel shipping package. Otherwise, the chips are shipped in a tray.2. Package type G contains lead; package type L is lead-free.Part NumberPPC405EP-3GB333CxPackage Processor Speed (MHz)Grade 3 ReliabilityOperational Case Temperature Shipping Package Blank = TrayZ = Tape and reel(-40°C to +85°C)Range Revision LevelPPC405EP – PowerPC 405EP Embedded ProcessorRevision 1.07 – September 10, 2007Data SheetFigure 1. PPC405EP Embedded Controller Functional Block DiagramThe PPC405EP is designed using the IBM Microelectronics Blue Logic TM methodology in which major functional blocks are integrated together to create an application-specific ASIC product. This approach provides a consistent way to create complex ASICs using IBM CoreConnect TM Bus Architecture.PPC405Processor Core DOCM IOCMDCUICUOCM ControlOCM SRAMDCR Bus16KB On-chip Peripheral Bus (OPB)GPIO IIC GPTUART MALEthernet DMA BridgeProcessor Local Bus (PLB)SDRAM PCI BridgeExternal Bus ControllerControllerClock Control ResetPower Mgmt JTAGTrace Timers MMUMIIController OPB Interrupt ControllerArb29-bit addr 16-bit data13-bit addr 32-bit dataUniversal I-CacheD-Cache(4-Channel)66 MHz max (async)DCRs16KB Arb x2x2Event CountersPPC405EP – PowerPC 405EP Embedded Processor Revision 1.07 – September 10, 2007Data Sheet Address MapsThe PPC405EP incorporates two address maps. The first address map defines the possible use of addressable memory regions that the processor can access. The second address map defines Device Configuration Register (DCR) addresses (numbers). The DCRs are accessed by software running on the PPC405EP processor through the use of mtdcr and mfdcr instructions.Table 1. System Memory Address Map (4GB System Memory)Function Subfunction Start Address End Address SizeGeneral Use SDRAM, External Peripherals, and PCIMemoryNote: Any of the address ranges listed atright may be use for any of the abovefunctions.0x000000000xE7FFFFFF3712MB0xE80100000xE87FFFFF8MB0xEC0000000xEEBFFFFF44MB0xEEE000000xEF3FFFFF6MB0xEF5000000xEF5FFFFF1MB0xEF9000000xFFFFFFFF263MBBoot-upPeripheral Bus Boot 10xFFE000000xFFFFFFFF2MBPCI Boot 20xFFFE00000xFFFFFFFF128KBPCI PCI I/O0xE80000000xE800FFFF64KB PCI I/O0xE88000000xEBFFFFFF56MB Configuration Registers0xEEC000000xEEC000078B Interrupt Acknowledge and Special Cycle0xEED000000xEED000034B Local Configuration Registers0xEF4000000xEF40003F64BInternal Peripherals GPT0xEF6000000xEF6000FF256B UART00xEF6003000xEF6003078B UART10xEF6004000xEF6004078B IIC00xEF6005000xEF60051F32B OPB Arbiter0xEF6006000xEF60063F64B GPIO Controller Registers0xEF6007000xEF60077F128B Ethernet 0 Controller Registers0xEF6008000xEF6008FF256B Ethernet 1 Controller Registers0xEF6009000xEF6009FF256BNotes:1.When peripheral bus boot is selected, peripheral bank 0 is automatically configured at reset to the address range listed above.2.If PCI boot is selected, a PLB-to-PCI mapping is automatically configured at reset to the address range listed above.3.After the boot process, software may reassign the boot memory regions for other uses.4.All address ranges not listed above are reserved.PPC405EP – PowerPC 405EP Embedded Processor Revision 1.07 – September 10, 2007Data Sheet Table 2. DCR Address MapFunction Start Address End Address SizeTotal DCR Address Space10x0000x3FF1KW (4KB)1By function:Reserved0x0000x00F16W Memory Controller Registers0x0100x0112WExternal Bus Controller Registers0x0120x0132W Reserved0x0140x0172WOn-Chip Memory Controller Registers0x0180x01F8W Reserved0x0200x07F96WPLB Registers0x0800x08F16W Reserved0x0900x09F16WOPB Bridge Out Registers0x0A00x0A78W Reserved0x0A80x0AF6WClock, Control, and Reset0x0B00x0B78WPower Management0x0B80x0BF8WInterrupt Controller0x0C00x0CF16W Reserved0x0D00x0FF48WDMA Controller Registers0x1000x13F64W Reserved0x1400x17F64W Ethernet MAL Registers0x1800x1FF128WEvent Counters0x2000x2034W Reserved0x2040x3FF508W Notes:1.DCR address space is addressable with up to 10 bits (1024 or 1K unique addresses). Each unique address represents a single 32-bit(word) register, or 1 kiloword (KW) (which equals 4 KB).PPC405EP – PowerPC 405EP Embedded Processor Revision 1.07 – September 10, 2007Data Sheet On-Chip Memory (OCM)The OCM feature comprises a memory controller and a one-port 4KB static RAM (SRAM) accessed by the processor core.Features include:•Low-latency access to critical instructions and data•Performance identical to cache hits without misses•Contents change only under program controlPLB to PCI InterfaceThe PLB to PCI interface core provides a mechanism for connecting PCI devices to the local PowerPC processor and local memory. This interface is compliant with version 2.2 of the PCI Specification.Features include:•internal pci bus arbiter for up to three external devices at PCI bus speeds up to 66MHz. Internal arbiter use is optional and can be disabled for systems which employ an external arbiter.•PCI bus frequency up to 66MHz- Asynchronous operation from 1/8 PLB frequency to 66MHz maximum•32-bit PCI address/data bus•Power Management:- PCI Bus Power Management v1.1 compliant•Supports 1:1, 2:1, 3:1, 4:1 clock ratios from PLB to PCI•Buffering between PLB and PCI:- PCI target 64-byte write post buffer- PCI target 96-byte read prefetch buffer- PLB slave 32-byte write post buffer- PLB slave 64-byte read prefetch buffer•Error tracking/status•Supports PCI target side configuration•Supports processor access to all PCI address spaces:- Single-beat PCI I/O reads and writes- PCI memory single-beat and prefetch-burst reads and single-beat writes- Single-beat PCI configuration reads and writes (type 0 and type 1)- PCI interrupt acknowledge- PCI special cycle•Supports PCI target access to all PLB address spaces•Supports PowerPC processor boot from PCI memoryPPC405EP – PowerPC 405EP Embedded Processor Revision 1.07 – September 10, 2007Data Sheet SDRAM Memory ControllerThe PPC405EP Memory Controller core provides a low latency access path to SDRAM memory. A variety of system memory configurations are supported. The memory controller supports up to two physical banks. Up to 256MB per bank are supported, up to a maximum of 512MB. Memory timings, address and bank sizes, and memory addressing modes are programmable.Features include:•11x8 to 13x11 addressing for SDRAM (2 banks)•32-bit memory interface support•Programmable address compare for each bank of memory•Industry standard 168-pin DIMMS are supported (some configurations)•Up to 133MHz memory supported by the 266MHz processor•Up to 111MHz memory supported by the 333MHz processor•4MB to 256MB per bank•Programmable address mapping and timing•Auto refresh•Page mode accesses with up to 4 open pages•Power management (self-refresh)External Peripheral Bus Controller (EBC)•Supports five banks of ROM, EPROM, SRAM, Flash memory, or slave peripherals•Up to 66MHz operation•Burst and non-burst devices•8- and 16-bit byte-addressable data bus width support•Latch data on Ready, synchronous or asynchronous•Programmable 2K clock time-out counter with disable for Ready•Programmable access timing per device- 0–255 wait states for non-bursting devices- 0–31 burst wait states for first access and up to 7 wait states for subsequent accesses- Programmable CSon, CSoff relative to address- Programmable OEon, WEon, WEoff (0 to 3 clock cycles) relative to CS•Programmable address mapping•Peripheral Device pacing with external “Ready”DMA Controller•Supports memory-to-memory transfers•Four channels•Scatter/gather capability for programming multiple DMA operations•32-bit addressing•Address increment or decrement•Internal 32-byte data buffering capabilityPPC405EP – PowerPC 405EP Embedded Processor Revision 1.07 – September 10, 2007Data Sheet Serial Interface•One 8-pin UART and one 2-pin (Tx and Rx only) UART interface provided•Internal serial clock to allows a wide range of baud rates•Register compatibility with NS16750 register set•Complete status reporting capability•Transmitter and receiver are each buffered with 16-byte FIFOs when in FIFO mode•Fully programmable serial-interface characteristics•Supports DMA using internal DMA engineIIC Bus Interface•Compliant with Phillips® Semiconductors I2C Specification, dated 1995•Operation at 100kHz or 400kHz•8-bit data•10- or 7-bit address•Slave transmitter and receiver•Master transmitter and receiver•Multiple bus masters•Supports fixed V DD IIC interface•Two independent 4 x 1 byte data buffers•Twelve memory-mapped, fully programmable configuration registers•One programmable interrupt request signal•Provides full management of all IIC bus protocol•Programmable error recoveryGeneral Purpose IO (GPIO) Controller•Controller functions and GPIO registers are programmed and accessed via memory-mapped OPB bus master accesses•All GPIOs are pin-shared with other functions. DCRs control whether a particular pin that has GPIO capabil-ities acts as a GPIO or is used for another purpose.•Each GPIO output is separately programmable to emulate an open-drain driver (i.e., drives to zero, three-stated if output bit is 1)Universal Interrupt Controller (UIC)The Universal Interrupt Controller (UIC) provides the control, status, and communications necessary between the various sources of interrupts and the local PowerPC processor.Features include:•Supports seven external and 19 internal interrupts•Edge-triggered or level-sensitive•Positive or negative active•Non-critical or critical interrupt to processor core•Programmable critical interrupt priority ordering•Programmable critical interrupt vector for faster vector processingPPC405EP – PowerPC 405EP Embedded Processor Revision 1.07 – September 10, 2007Data Sheet 10/100 Mbps Ethernet MAC•Two ports capable of handling full/half duplex 100Mbps and 10Mbps operation•Uses the medium independent interface (MII) to the physical layer (PHY not included on chip)JTAG•IEEE 1149.1 test access port•IBM RISCWatch debugger support•JTAG Boundary Scan Description Language (BSDL)PPC405EP – PowerPC 405EP Embedded ProcessorRevision 1.07 – September 10, 2007Data SheetFigure 2. 31mm, 385-Ball E-PBGA PackageAs 1.27 TYP0.65 ± 0.05 SOLDERBALL x 38531.0 ± 0.227.9831.0BAC 0.20∅ 0.30∅ 0.15s C A B s s 15.5 TYPGold Gate Release Corresponds to 0.20CC 2.36 REF 0.6±0.1PCBSubstrateMoldCompoundBC D E F G H J K L M AA N PR T U V W Y AB AC Thermal BallsA01 Ball Location0103050709111315171902040608101214161821232022Top ViewBottom View0.250.35CCNotes: 1. All dimensions are in mm.2.65 max 2. Package available in leaded and lead-free configurations.2.07 minLogo View®PPC405EP1YWWBZZZZZLot NumberPart NumberPPC405EP – PowerPC 405EP Embedded ProcessorRevision 1.07 – September 10, 2007Data SheetPin ListsThe following table lists all the external signals in alphabetical order and shows the ball (pin) number on which the signal appears. Shared signals are shown with the default signal (following reset) not in brackets and the alternate signal in brackets. Shared signals appear alphabetically multiple times in the list—once for each signal assigned to the ball. The page number listed gives the page in “Signal Functional Description” on page 31 where the signals in the indicated interface group begin.Table 3. Signals Listed Alphabetically (Sheet 1 of 10)Signal NameBall Interface GroupPage AGND AB21System 35AV DD AC20BA0Y15SDRAM 33BA1AC16BankSel0AB13SDRAM 33BankSel1AC13CAS Y14SDRAM 33ClkEn0AB14SDRAM33ClkEn1AC14DQM0AC10SDRAM33DQM1AA7DQM2W04DQM3U02EMCMDClk Y06Ethernet 32EMCMDIO AA5Ethernet32EMC0Tx0D0U03Ethernet32EMC0Tx0D1N03EMC0Tx0D2L01EMC0Tx0D3P03EMC0Tx0En W01Ethernet 32EMC0Tx0Err V03Ethernet32EMC0Tx1D0B15Ethernet32EMC0Tx1D1C14EMC0Tx1D2A15EMC0Tx1D3D14EMC0Tx1En A16Ethernet 32EMC0Tx1Err C15Ethernet32ExtResetA03External Slave Peripheral33PPC405EP – PowerPC 405EP Embedded Processor Revision 1.07 – September 10, 2007Data Sheet GND A01GroundNote:K10-K14, L10-L14, M10-M14, N10-N14, and P10-P14 are also thermal balls.35GND A02 GND A07 GND A12 GND A17 GND A22 GND A23 GND B01 GND B02 GND B22 GND B23 GND C03 GND C21 GND D04 GND D20 GND E05 GND E09 GND E12 GND E15 GND E19 GND G01 GND G23 GND J05 GND J19GND K10-K14GND L10-L14Table 3. Signals Listed Alphabetically (Sheet 2 of 10)Signal Name Ball Interface Group PagePPC405EP – PowerPC 405EP Embedded ProcessorRevision 1.07 – September 10, 2007Data SheetGND M01PowerNote: K10-K14, L10-L14, M10-M14, N10-N14, and P10-P14 are also thermal balls.35GND M05GND M10-M14GND M19GND M20GND M23GND N10-N14GND P10-P14GND R05GND R19GND U01GND U23GND W05GND W09GND W12GND W15GND W19GND Y04GND Y20GND AA03GND AA21GND AB01GND AB02GND AB22GND AB23GND AC01GND AC02GND AC07GND AC12GND AC17GND AC22GNDAC23Table 3. Signals Listed Alphabetically (Sheet 3 of 10)Signal NameBall Interface GroupPagePPC405EP – PowerPC 405EP Embedded ProcessorRevision 1.07 – September 10, 2007Data SheetGPIO00[PerBLast]A09System35GPIO01[TS1E]AA23GPIO02[TS2E]Y22GPIO03[TS1O]Y23GPIO04[TS2O]W21GPIO05[TS3]U20GPIO06[TS4]V23GPIO07[TS5]U21GPIO08[TS6]U22GPIO09[TrcClk]T21GPIO10[PerCS1]C02GPIO11[PerCS2]E03GPIO12[PerCS3]D03GPIO13[PerCS4]D05GPIO14[PerAddr03]B04GPIO15[PerAddr04]A04GPIO16[PerAddr05]A05GPIO17[IRQ0]W22GPIO18[IRQ1]W23GPIO19[IRQ2]V21GPIO20[IRQ3]V22GPIO21[IRQ4]T22GPIO22[IRQ5]R20GPIO23[IRQ6]T23GPIO24[UART0_DCD]M04GPIO25[UART0_DSR]K01GPIO26[UART0_RI]L04GPIO27[UART0_DTR]J01GPIO28[UART1_Rx]J02GPIO29[UART1_Tx]J03GPIO30[RejectPkt0]W20GPIO31[RejectPkt1]Y21Halt C22System35IICSCL AB4Internal Peripheral34IICSDA Y01[IRQ0]GPIO17W22Interrupts34[IRQ1]GPIO18W23[IRQ2]GPIO19V21[IRQ3]GPIO20V22[IRQ4]GPIO21T22[IRQ5]GPIO22R20[IRQ6]GPIO23T23Table 3. Signals Listed Alphabetically (Sheet 4 of 10)Signal NameBall Interface GroupPagePPC405EP – PowerPC 405EP Embedded ProcessorRevision 1.07 – September 10, 2007Data SheetMemAddr00AB15SDRAMNote: During a CAS cycle MemAddr00 is the least significant bit (lsb) on this bus.33MemAddr01AB16MemAddr02AB17MemAddr03AA17MemAddr04AC18MemAddr05AA18MemAddr06AC19MemAddr07AB19MemAddr08Y18MemAddr09AA19MemAddr10Y19MemAddr11AA20MemAddr12AC21MemClkOut0AA14SDRAM33MemClkOut1Y13MemData00AB12SDRAMNote: MemData00 is the most significant bit (msb) on this bus.33MemData01AA12MemData02AC11MemData03AA11MemData04Y11MemData05AA10MemData06AC9MemData07AB9MemData08AC8MemData09Y09MemData10AA8MemData11AB7MemData12AB6MemData13Y07MemData14AA6MemData15AC5MemData16AB5MemData17AC4MemData18Y05MemData19AA4MemData20AB3MemData21Y03MemData22W03MemData23V04MemData24W02MemData25U04MemData26V02MemData27T04MemData28T02MemData29R04MemData30R03MemData31R02Table 3. Signals Listed Alphabetically (Sheet 5 of 10)Signal NameBall Interface GroupPagePPC405EP – PowerPC 405EP Embedded ProcessorRevision 1.07 – September 10, 2007Data SheetOV DD B11Power35OV DD B09OV DD B19OV DD C17OV DD D13OV DD E06OV DD E07OV DD E08OV DD E16Power35OV DD E17OV DD E18OV DD E21OV DD F05OV DD F19OV DD F23OV DD G05OV DD G19OV DD H05OV DD H19OV DD H22OV DD K04OV DD K20OV DD K23OV DD M22OV DD N01OV DD P20OV DD P23OV DD T05OV DD T19OV DD T20OV DD U05OV DD U19OV DD V01OV DD V05OV DD V19OV DD W06OV DD W07OV DD W08OV DD W16OV DD W17OV DD W18OV DD Y12OV DDAC06Table 3. Signals Listed Alphabetically (Sheet 6 of 10)Signal NameBall Interface GroupPagePPC405EP – PowerPC 405EP Embedded ProcessorRevision 1.07 – September 10, 2007Data SheetPCIAD00B16PCINote : PCIAD31 is the most significant bit (msb) on this bus.31PCIAD01C16PCIAD02B17PCIAD03D16PCIAD04B18PCIAD05D17PCIAD06C18PCIAD07A19PCIAD08D18PCIAD09C19PCIAD10A20PCIAD11B20PCIAD12C20PCIAD13C23PCIAD14D21PCIAD15D22PCIAD16J22PCIAD17J23PCIAD18K21PCIAD19K22PCIAD20L21PCIAD21L22PCIAD22L23PCIAD23M21PCIAD24N23PCIAD25N22PCIAD26N21PCIAD27P22PCIAD28P21PCIAD29R23PCIAD30R22PCIAD31R21PCIC0/BE0 A18PCI31PCIC1/BE1 D19PCIC2/BE2 L20PCIC3/BE3N20PCIClk B21PCI 31PCIDevSel H21PCI 31PCIFrame F22PCI 31PCIGnt0/Req D23PCI 31PCIGnt1E23PCI 31PCIGnt2F21PCIIDSel A21PCI 31PCIINT[PerWE]D15PCI 31PCIIRDY H20PCI 31PCIParity J21PCI 31PCIPErrH23PCI31Table 3. Signals Listed Alphabetically (Sheet 7 of 10)Signal NameBall Interface GroupPage。

PowerPC简介及编程要点

PowerPC简介及编程一,PowerPC芯片PowerPC是早期Motorola和IBM联合为Apple的MAC机开发的CPU芯片,商标权同时属于IBM和Motorola,并成为他们的主导成品.IBM主要的PowerPC产品有PowerPC604s(深蓝内部的CPU),PowerPC750,PowerPCG3(1.1GHz).Motorola主要有MC和MPC系列.尽管他们产品不一样,但都采用PowerPC的内核.这些产品大都用在嵌入式系统中.Motorola的MPC860简介MPC860 PowerQUICC (Quad Integrated Communications Controller) 内部集成了微处理器和一些控制领域的常用外围组件, 特别适用于通信产品. 包括器件的适应性, 扩展能力和集成度等. MPC860 PowerQUICC集成了两个处理块.一个处理块是嵌入的PowerPC核, 另一个是通信处理模块( CPM, Communications Processor Module), 通信处理模块支持四个串行通信控制器(SCC, Serial Communication Controller), 实际上它有八个串行通道: 四个SCC,两个串行管理控制器(SMC, Serial Management Channels), 一个串行外围接口电路( SPI, Serial Peripheral Interface ) 和一个I2C( Inter-Integrated Circuit ) 接口. 由于CPM分担了嵌入式PowerPC核的外围工作任务, 这种双处理器体系结构功耗要低于传统的体系结构的处理器.单出口, 嵌入式PowerPC核32比特版本(与PowerPC结构定义完全兼容)32x32位通用寄存器(GPRs, General Purpose Registers)o4K数据Cache和4K指令Cache, 分别带有一个MMU.o存储管理单元(MMU)32-输入翻译后备缓冲器( TLBs )o32位数据,地址线∙存储控制器(八个存储体)o单线存储模块无逢接口,静态随即存取存储器(RAM), EPROM, FLASH MEMORY或DRAM等。

PowerPC介绍

5

PowerPC History – cont

• BookE

- PowerPC for Embedded Environment - 2000 年开始,摩托罗拉和 IBM 的 PowerPC 芯片都开始遵 循 Book E 规范

- BookE vs AIM

- Book E defines more flexible interrupt and memory management models. - Segment and block address translation (BAT) registers are gone - Book E supports the use of auxiliary processing 2018/9/19 CONFIDENTIAL 6 units

PowerPC Market

• PowerPC - 网络和存储设备 - 从视频游戏终端、多媒体娱乐系统,到数字 助手和蜂窝电话,再到基站和 PBX 开关 - 桌面系统中也会有 PowerPC • POWER - IBM 的很多服务器、工作站和超级计算机的 主要处理器 • Cell 2018/9/19 CONFIDENTIAL 7 游戏控制器

• PowerPC(PC: performance computing)

- based on IBM's earlier POWER architecture - created by the 1991 Apple–IBM–Motorola alliance, known as AIM. 2018/9/19 CONFIDENTIAL 4 最初目的,用在PC(苹果机比较成功 1994-2006)反击

PowerPC ARCH – Registers

基于PowerPC405的SOPC简单应用

微 处 理 机M I CROPROCE SSORS基于Po werPC 405的S OPC 简单应用张春生1,常 青2,肖山竹2(1.防空兵指挥学院,郑州450052;2.国防科技大学ATR 实验室,长沙410073)摘 要:介绍Po w er PC 405嵌入式处理器的结构特性及其软件开发环境,给出基于Po w er PC 405的SOPC 简单应用实例。

关键词:I P 核;可编程片上系统;Po w er PC 405硬核;Core Connect 总线;嵌入式处理器中图分类号:TP368文献标识码:A文章编号:1002-2279(2007)06-0117-04The S im ple A pp licati on of SOPC Basi ng on PowerPC 405Z HANG Chun-sheng 1,C HANG Q i n g 2,X IAO Shan-zhu2(1.A ir D efence Command Co llege ,Zhengzhou 450052,China;2.ATR Lab ,N ational Universit y of D efence T echnology,Changsha 410073,Ch i na)A bstract :This paper firstly i n troduces the structures and fea t u res of Pow erPC 405e m beded processor ,t h en i n troduces the processor s soft w are developm ent env ironm en.t I n the end ,a si m pleapp lication prog ra m is also g iven .K ey w ords :I P Core ;SOPC ;Pow erPC 405;CoreConnec;t Em bedded processor1 引 言X ilinx 公司V irtex- Pro 系列的FPGA 采用了先进的I P 植入技术,无缝嵌入了32位的I B M Pow er PC 405R I SC 处理器内核。

PowerPC汇编语言详解

注意到,所有计算值的指令均以第一个操作数作为目标寄存器。在所有这些指令 中,寄存器都仅用数字指定。例如,将数字 12 载入寄存器 5 的指令是 li 5, 12。 我们知道,5 表示一个寄存器,12 表示数字 12,原因在于指令格式 —— 没有 其他指示符。

每条 PowerPC 指令的长度都是 32 位。前 6 位确定具体指令,其他各位根据指 令的不同而具有不同功能。指令长度固定这一事实使处理器更够更有效地处理指 令。但 32 位这一限制可能会带来一些麻烦,后文中您将会看到。大多数此类麻 烦的解决方法将在本系列的第 2 部分中讨论。

您的第一个 POWER5 程序

现在我们来看实际代码。我们编写的第一个程序仅仅载入两个值、将其相加并退 出,将结果作为状态代码,除此之外没有其他功能。将一个文件命名为 sum.s, 在其中输入如下代码:

清单 1. 您的第一个 POWER5 程序

#Data sections holds writable memory declarations .data .align 3 #align to 8-byte boundary

高级编程与低级编程的对比

大多数编程语言都与处理器保持着相当程度的独立性。但都有一些特殊特性依赖 于处理器的某些功能,它们更有可能是特定于操作系统的,而不是特定于处理器 的。 构建高级编程语言的目的是在程序员和硬件体系结构间搭建起一座桥梁。 这样做有多方面的原因。尽管可移植性是原因之一,但更重要的一点或许是提供 一种更友好 的模型,这种模型的建立方式更接近程序员的思考方式,而不是芯 片的连线方式。

上述指令中有许多都利用了 PowerPC 的扩展记忆法。也就是说,它们实际上是 一条更为通用的指令的特殊形式。例如,上述所有条件跳转指令实际上都是 bc (branch conditional)指令的特殊形式。bc 指令的形式是 bc MODE, CBIT, ADDRESS。CBIT 是条件寄存器要测试的位。MODE 有许多有趣的用途,但为简化 使用,若您希望在条件位得到设置时跳转,则将其设置为 12;若希望在条件位 未得到设置时跳转,则将其设置为 4。部分重要的条件寄存器位包括:表示小于 的 8、表示大于的 9、表示相等的 10。因此,指令 beq ADDRESS 实际上就是 bc 12, 10 ADDRESS。类似地,li 是 addi 的特殊形式,mr 是 or 的特殊形式。这 些扩展的记忆法有助于使 PowerPC 汇编语言程序更具可读性,并且能够编写出 更简单的程序,同时也不会抵消更高级的程序和程序员可以利用的强大能力。

MP3解码板 [基于PowerPC405的MP3实时解码系统设计与实现]

![MP3解码板 [基于PowerPC405的MP3实时解码系统设计与实现]](https://img.taocdn.com/s3/m/eb3c6b21c77da26924c5b09c.png)

摘要:文章介绍了一种在FPGA上用PowerPC405实现MP3实时解码SoC系统的方法。

通过使用IP核搭建SoC硬件结构,并进行定点MP3解码软件算法移植,完成软硬件协同设计和验证,实现MP3音乐实时、高品质的解码播放。

关键字:MP3、解码、FPGA、PoleStar1引言随着半导体加工工艺和设计技术的飞速发展,越来越多的系统功能可以集成到一个单芯片(System-on-a chip,SoC)中,加快了不同学科间的交叉融合,使得半导体、电子工程、计算机、自动化、软件工程、通信工程等相关人士均需要学习SoC的相关知识。

工业和信息化部软件与集成电路促进中心(CSIP)作为软件与集成电路产业促进机构, 从促进产业发展、培育创新人才的角度出发,联合国内外知名企业,开发了PoleStar(北极星)综合教学实验平台和配套《SoC系统设计与实践》教程,将业界正在使用的技术和方法转化为适合高校、教育培训机构使用的教程案例,实现高校所学知识与企业所用技术之间的无缝链接,加速我国人才培育培养,助力我国信息产业做大做强。

基于PowerPC405的MP3实时解码系统设计与实现是《SoC系统设计与实践》中的一个高级章节,比较全面的介绍了SoC系统架构设计流程和软硬件协同设计方法。

2SoC平台硬件架构设计在MP3播放系统实现中,无论硬件架构还是软件优化,目标都是要提高系统的MP3解码及播放能力。

其中硬件为解码软件提供平台,软件针对硬件平台特性,实现软件最优效率。

本系统针对MP3解码工作的特性,不同于其它控制类SOC,它需要有很强的运算处理能力。

而我们搭建硬件平台的基础还是要看能否达到MP3解码算法的需要。

基于以上想法,我们构建的硬件系统需要有较强的乘法运算性能以及高速的内存访问性能。

乘法运算需求:处理器必须要有硬件实现的乘法单元,能够在短时间里完成乘法运算。

另外,处理器最好带有额外乘法加速单元,也就是乘加运算单元。

内存访问的需求:为了保证高速的内存访问,系统需要有先进的缓存系统、高效的总线系统以及高速的内存接口控制器,以保证数据能够被高速地读取。

BROCADE_交换机的配置手册1

U_Port

FL_Port

NL_Port 节点

交换机 2

NL_Port 节点

24-位 N_Port/F_Port可用范围: –x„01 0000‟到x„EF EFFF‟

结构协议 编码 / 解码 物理变换

通用服务

FC-1

FC-0

光纤物理与信号接口 ( FC- PH, FC-PH2, FC-PH3 )

FC - AL

FC - AL -2

8b/10b 编码 铜, 光连接

光纤通道的拓扑结构

Fibre Channel有三种拓扑结构:

– 点对点(Point-to-Point) – 两个设备之间互连 – 仲裁环(Arbitrated Loop) – 最多支持126个设备互连,形成一个 仲裁环 – 交换式Fabric(Switch Fabric) – 最多1千6百万个设备互连

World Wide Name (WWN) 定义

Fabric是指一个或几个可以使用目的标示来传输数据帧的交换机。 Fabric通常可以被认作是一个“云团”,也可以当作是一个虚拟连 接。每一个设备的唯一标示就是World Wide Name (就像一个人的 身份证,终身使用并不会修改)

FC标准预留

现有的网络技术状况

当信息转换成关键数据时, 网络必须进一步扩展来满足 这一新的需要: 数据 – 爆炸性的数据增长 – 动态高速的数据迁移 传输 – 安全的数据存放和读取

基于TCP/IP技术的 网络能实现这一切, 然而:

– 数据迁移一只能以异步方式进行

PowerPC_学习

Techtalk of Power PC历史1:POWERPOWER 是 Power Optimization With Enhanced RISC 的缩写,是 IBM 的很多服务器、工作站和超级计算机的主要处理器。

POWER 芯片起源于 801 CPU,是第二代RISC 处理器。

POWER 芯片在 1990 年被 RS 或 RISC System/6000 UNIX 工作站(现在称为 eServer 和 pSeries)采用,POWER 的产品有 POWER1、POWER2、POWER3,现在最高端的是 POWER4。

POWER4 处理器是目前单个芯片中性能最好的芯片。

801的设计非常简单。

但是由于所有的指令都必须在一个时钟周期内完成,因此其浮点运算和超量计算(并行处理)能力很差。

POWER 体系结构就着重于解决这个问题。

POWER 芯片采用了 100 多条指令,是非常优秀的一个 RISC 体系结构。

以下对每种 POWER 芯片简单进行一下介绍;更详细的内容请参考参考资料中的链接。

∙POWER1发布于 1990 年:每个芯片中集成了 800,000 个晶体管。

与当时其他的 RISC 处理器不同,POWER1 进行了功能划分,这为这种功能强大的芯片赋予了超量计算的能力。

它还有单独的浮点寄存器,可以适应从低端到高端的 UNIX 工作站。

最初的 POWER1 芯片实际上是在一个主板上的几个芯片;后来很快就变成一个 RSC(RISC 单一芯片),其中集成了100 多万个晶体管。

POWER1 微处理器的 RSC 实现被火星探险任务用作中央处理器,它也是后来 PowerPC 产品线的先驱。

∙POWER2发布于 1993 年,一直使用到 1998 年:每个芯片中集成了 1500 万个晶体管。

POWER2 芯片中新加了第二个浮点处理单元(FPU)和更多缓存。

PSSC 超级芯片是 POWER2 这种 8 芯片体系结构的一种单片实现,使用这种芯片配置的一个 32 节点的 IBM 深蓝超级计算机在 1997 年击败了国际象棋冠军Garry Kasparov。

PowerPC产品介绍

飞思卡尔半导体的PowerPC 处理器是RISC 嵌入式应用的理想基础平台。PowerPC 芯片凭借其出色的性能和高度整合和技术先进特性在网络通信应用, 工业控制应用,家用数字化,网络存储领域,军工领域和电力系统控制等都具有非常广泛的应用。北京国基科技股份有限公司长期致力于基与Freescale PowerPC处理器产品的研发与定制设计,拥有雄厚的研发实力。国基科技推出的PowerPC 全系列开发板,提供全面技术支持,竭诚为广大客户服务。以下是 国基科技PowerPC 开发板硬件介绍。如需了解更详细资料,欢迎登陆:

1 x 10/100/1000M 4-port 10/100 Ethernet switch

1 x PCI 2 x miniPCI

1 x PCI 2 x miniPCI

4 x SATA (可接四个硬盘)

2 x USB 2.0 4 x SATA (可接四个硬盘)

1 x 10/100/1000M 4-port 10/100 Ethernet switch

-MPC8541E 开发套件 -MPC8560 开发套件 -MPC8572E 开发套件(高性能,双核)

PowerPC 载板系列

- Type-N 载板-网络应用 -Type-A 载板-ATCA 或UTCA 系统 - Type-S 载板-网络存储

PowerPC 开发工具 - TRACE32 仿真器 Wind River ICE2 - CodeWarrior for PowerPC 开发环境软件

667HZ 1260MIPS @667MHZ

256M DDR2

8M NOR Flash 32MNAND Flash 256Kbits E2PROM SD 卡(SD 控制器)

Amcc ppc405ex