3.2 F2812主要功能简介-AD转换器

基于TMS320F2812的CPU片上外设功能及接口设计

CPU片上外设功能及接口由于F2812芯片集成了很多内科可以访问和控制外部设备,2812内核需要通过某种方式来读/写外设,为此处理器将所有的外设都映射到了数据存储空间。

每个外设被分配一段相应的地址空间,主要包括配置寄存器、输入寄存器、输出寄存器和状态寄存器。

每个外设只要通过简单的访问寄存器就可以使用该设备。

本章内容主要讨论的是对SCI、SPI、CAN、ADC进行硬件设计。

3.1 A/D转换电路的设计A/D转换是嵌入式控制器一个非常重要的单元,它提供了控制器与现实世界的连接通道,通过ADC可以检测诸如温度、湿度、压力、电流、电压、速度、加速度等模拟量。

这些信号都可以采用介于0~3V的正比于原始信号的电压信号来表示,ADC转换的目的是将这些模拟信号转换成数字信号。

A/D转换电路是数据采集模块的主要部分。

它的核心任务是完成信号的数据采集。

A/D转换电路的设计完全遵循参考文献的严格规定。

本系统的设计中选用TMS320F2812芯片的片内A/D接口实现信号的数据采集。

F2812芯片的内部ADC模块是一个12位带流水线的模数转化器。

模数转换单元的模拟电路包括前向模拟多路复用开关(MUXs)、采样/保持(S/H)电路、变换内核、电压参考和其它模拟辅助电路。

模数转化单元的数字电路包括可编程转换序列、结果寄存器、与模拟电路的接口等电路。

为满足绝大多数系统多传感器的需要,F2812的模数有16个通道,可配置为2个独立的8通道模块F2812芯片的A/D转换器是一个12位分辨率转换器,内含2个采样/保持电路,25MHz的ADC时钟频率,单通道转换时间为80ns,采样率高达12.5MHz,16个采集通道,可配置成两个独立的8通道,模拟输入范围0V~3V,4种触发方式可以启动A/D转换,具有灵活的中断控制。

输入模拟电压与采样结果的关系为:数字结果=4095×(输入模拟电压-ADCLO)/3,其中,ADCLO是提供普通的低边模拟输入管脚,接模拟地。

TMS320F2812自带ADC模块简介

I++;

}

//在ADC_ISR中,对各个通道进行校正:

Interrupt

Adc_Isr (void)

{

。。。。。。。。。。

newResult n= AdcRegs.ADCRESULTn*CalGain - CalOffset;

。。。。。。。。。。

}

本文来自: DSP交流网()详细出处参考:/bbs/viewthread.php?tid=291

(3)采用适当的隔离技术,将ADC模块电源引脚和数字电源隔离;

(4)如果采样电路部分是经过多路开关切换的,可以在多路开关输出上接下拉电阻到地;

(5)采样通道上的电容效应也可能会导致AD采样误差,因为采样通道上的等效电容可能还在保持有上一个采样数据的数值的时候,就对当前数据进行采样,会造成当前数据不准确。如果条件允许,可以在每次转化完成后现将输入切换到参考地,然后在对信号进行下一次采样。

Ave_LowActualCount= Sum_LowActualCount/SAMPLES;

CalGain = (HIGH_IDEAL_COUNT - LOW_IDEAL_COUNT)//计算增益系数

/ (Avg_HighActualCount - Avg_LowActualCount);

CalOffset =Avg_LowActualCount*CalGain LOW_IDEAL_COUNT; //计算偏置

TMS320F2812内部集成了ADC转换模块,该模块具有如下的功能:

1.12位ADC核,内置了双采样-保持器(S/H);

2.顺序采样模式或者同步采样模式;

3.模拟输入:0V~3V;

4.快速转换时间运行在25MHz,ADC时钟,或12.5MSPS;

TMS320F2812在PWM型开关电源设计中的应用

U 0 (Ton / T ) * E

由上式可知,开关接通时间和工作周期的比例改变,AB 间电压的平均值也随之改变,因此,随着负载及输入电 源电压的变化自动调整Ton和T的比例,便能使输出电压 U0维持不变。 改变接通时间Ton和工作周期T比例亦即改变脉冲的占空 比。这里选择了开关周期T恒定,通过改变脉冲宽度Ton 来改变占空比,这种方式称为脉宽调制方式(PWM), 用来实现对电压幅值频率的控制。

18

如图,把一个电压正弦半波N等分 (这里N=5),可以把该正弦半波 看成由N个相连的脉冲所组成的波 形,这些脉冲宽度相等但幅值不等

根据采样控制理论中的面积等效 原理,把这些等宽不等幅的脉冲, 用相等数量的等幅不等宽的 矩形 脉冲序列来代替,矩形脉冲的中点与正弦波每一等份的面 积相等,则这些脉 冲的宽度是按正弦规律变化的。

图3 开关电源控制原理图

在开关K关断时为使负载能得到连续的能量开关稳压电 源必须要有一套储能装置,在开关接通时将一部分能力储存 起来,在开关断开时向负载释放。 图3中由电感L电容C2用 以储存能量,在开关断开时,储存在电感L和C2中的能量通 过二极管D释放给负载,使负载得到连续而稳定的能量。

15

AB间的电压平均值U0可表示为:

TMS320F2812 在PWM型开关电源设计中的应用

主要内容

一、TMS320F2812简介

二、PWM型开关电源简介

三、利用TMS320F2812产生SPWM波形

2

一、TMS320F2812简介

3

1. TMS320F2812简介

TMS320C2000系列DSP控制器,具有很好的性能,集成了 Flash存储器,具有A/D转换器以及可靠的CAN模块,主要 应用于数字化的控制。

F2812主要功能简介-事件管理器

GP Timer Input & Output

Input:

内部高速外设时钟,HSPCLK 外部时钟TCLKINA/B,最高频率≤1/4 CPU时钟 方向输入引脚,TDIRA/B 复位信号,RESET

Output:

比较输出,TxCMP ADC启动转换信号 上溢、下溢、比较匹配、周期匹配 计数方向指示位

比较寄存器,TxCMPR

存放比较常数,不断与计数器比较,匹配时: 根据GPTCONA/B设置,比较输出引脚发生跳变 对应设置中断标志 中断未屏蔽,产生中断请求

周期寄存器,TxPR

存放周期值,决定定时器周期 与计数器值相等时,根据计数方式确定复位为0或转为减计数

16

GP Timer Registers 2

GPTCONA/B中的位反映计数方向 TDIRA/B引脚决定计数方向

1 增计数 0 减计数

17

GP Timer Clock

可采用内部时钟或外部时钟TCLKINA/B引脚输入 外部时钟频率≤1/4 CPU时钟 定向增/减计数模式:

T2、T4为QEP电路使用 QEP电路为定时器提供时钟、方向输入

内部/外部时钟输入,可编程分频,方向可引脚控制

4种可屏蔽中断:上溢、下溢、比较、周期

全比较单元 Full-Compare Units

3 x 2 个独立的比较单元,每个有6个比较输出

配合可编程死区发生器,产生PWM波形

可编程死区发生器 Programmable Deadband

Generation

13

GP Timer Functional Block

每个GP Timer 包括:

一个16位增/减计数器,TxCNT,RW,当前计数值 一个16位比较寄存器,TxCMPR,RW,双缓冲 一个16位周期寄存器,TxPR,EW,双缓冲 一个16位控制寄存器,TxCON,RW 内部/外部时钟输入,可定标 四个可屏蔽中断控制逻辑 一个增/减方向控制引脚,TDIRx 一个比较输出引脚,TxCMP 全局控制寄存器,GPTCONA/B

调试通过的TMS320F2812_AD转换程序

TMS320F2812 AD转换程序(已调试通过)/*=============================================================================== ===File name: F28XADC04U.COriginator: Digital Control Systems GroupTexas InstrumentsDescription: This file contains source for the F28X general purpose4 conversions ADC driver for unipolar signalsJoyshang=============================================================================== ======History:-------------------------------------------------------------------------------------27-02-2012 Release Rev 1.0----------------------------------------------------------------------------------*/#include "IQmathLib.h"#include "DSP28_Device.h"#include "f28xadc04u.h"#include "f28xbmsk.h"#define CPU_CLOCK_SPEED 6.6667L // for a 150MHz CPU clock speed#define ADC_usDELAY 5000L#define DELAY_US(A) DSP28x_usDelay(((((long double) A * 1000.0L) / (long double)CPU_CLOCK_SPEED) - 9.0L) / 5.0L)extern void DSP28x_usDelay(unsigned long Count);void F28X_adc04u_drv_init(ADCVALS *p){DELAY_US(ADC_usDELAY);AdcRegs.ADCTRL1.all = ADC_RESET_FLAG; /* Reset the ADC Module */asm(" NOP ");asm(" NOP ");AdcRegs.ADCTRL3.bit.ADCBGRFDN = 0x3; /* Power up bandgap/reference circuitry */DELAY_US(ADC_usDELAY); /* Delay before powering up rest of ADC */AdcRegs.ADCTRL3.bit.ADCPWDN = 1; /* Power up rest of ADC */AdcRegs.ADCTRL3.bit.ADCCLKPS = 6; //ADCCLK=HSPCLK/[(ADCCTRL1[7]+1)]/* Set up ADCTRL3 register */DELAY_US(ADC_usDELAY);AdcRegs.ADCTRL1.all = 0x0110; /* Set up ADCTRL1 register 0x0110 级联模式*/AdcRegs.ADCTRL2.all = 0x0100; /* Set up ADCTRL2 register 0x0100 EVA 启动转换*/AdcRegs.ADCMAXCONV.bit.MAX_CONV = 3; /* Specify four conversions */AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; //IUAdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x4; //地AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x8; //IVAdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0xC; //VREF1.5VEvaRegs.EXTCON.bit.EVSOCE = 1; //Enable SOCEvaRegs.GPTCONA.bit.T1TOADC = 1; /* Set up EV Trigger with Timer1 UF */}unsigned int tempz1;_iq tempz2;_iq tempz3;_iq tempz4;_iq tempz5;void F28X_adc04u_drv_read(ADCVALS *p){//int offset;//long tmp;/* Wait until ADC conversion is completed */while (AdcRegs.ADCST.bit.SEQ1_BSY == 1){};//offset = (int)(p->c1_out - 32767);tempz3 = AdcRegs.ADCRESULT0-AdcRegs.ADCRESULT1; //IU-地tempz4 = AdcRegs.ADCRESULT3-AdcRegs.ADCRESULT1; //VREF1.5V-地tempz5 = AdcRegs.ADCRESULT3-tempz4; //IU-tempz4tempz2 = (AdcRegs.ADCRESULT1 + 0x8000);/*Ibase=4,IQ14*/tempz2 = _IQmpy(_IQ(20),tempz2);tempz1 = (int)((tempz2 & 0x8000)>>15);if (tempz1==1){p->c1_out = ((long)( tempz2 + 0xFFFF0000));p->c1_out = _IQmpy(_IQ(32),p->c1_out);}else{p->c1_out = ((long)( tempz2 + 0x00000000));p->c1_out = _IQmpy(_IQ(32),p->c1_out);//IQ20}// tempz3 = AdcRegs.ADCRESULT0;//temp3 = _IQmpy(temp2,_IQ(10));/* IQ15 *///tempz3 = ((long)(AdcRegs.ADCRESULT1 - 0x5652 + 0x8022)<<16)>>10;//dat_q15 = (>>1)&0x7FFF; /* Convert result to Q15 (unipolar signal) *///tmp = (long)p->c1_gain*(long)dat_q15;// p->c1_out =AdcRegs.ADCRESULT0 - offset; //(int)(tmp>>13);//dat_q15 = (AdcRegs.ADCRESULT1>>1)&0x7FFF; /* Convert result to Q15 (unipolar signal) */// tmp = (long)p->c2_gain*(long)dat_q15;// p->c2_out = AdcRegs.ADCRESULT1 - offset;//dat_q15 = (AdcRegs.ADCRESULT2>>1)&0x7FFF; /* Convert result to Q15 (unipolar signal) *///tmp = (long)p->c3_gain*(long)dat_q15;// p->c3_out = AdcRegs.ADCRESULT2;AdcRegs.ADCTRL2.all |= 0x4040; /* reset the seq */}TMS320F2812的ADC模块用于采样过程的初始化代码void InitAdc(void) //初始化ADC模块{unsigned int i;AdcRegs.ADCTRL1.bit.RESET = 1; //ADC模块软复位,3个周期后,该位自动清0for(i=0;i<12;i++) NOP; //等待ADC寄存器硬件复位完备>AdcRegs.ADCTRL1.bit.SUSMOD = 3; //仿真挂起模式,0为忽略仿真挂起AdcRegs.ADCTRL1.bit.ACQ_PS = 1; //采样保持脉冲个数,即SH为1+1=2个ADCCLK AdcRegs.ADCTRL1.bit.CPS = 0; //是否再对送给ADC的时钟进行二分频AdcRegs.ADCTRL1.bit.CONT_RUN = 0; //1:进入连续运行; 0:开始停止模式AdcRegs.ADCTRL1.bit.SEQ_CASC = 0; //0:独立模式; 1:级联序列器模式AdcRegs.ADCTRL3.bit.ADCBGRFDN = 3; //带隙参考电路上电for(i=0;i<10000;i++) NOP;>AdcRegs.ADCTRL3.bit.ADCPWDN = 1; //除带隙参考电路外的其他ADC模块上电for(i=0;i<5000;i++) NOP;>AdcRegs.ADCTRL3.bit.ADCCLKPS = 3; //设置ADC的转换时钟ADCCLK = HSPCLK/(2*(ADCCLKPS+CPS))=25MHZAdcRegs.ADCTRL3.bit.SMODE_SEL = 0; //0:顺序采用模式,1:同步采样模式AdcRegs.MAX_CONV.all = 0x0000; //设置ADC的转换通道数AdcRegs.CHSELSEQ1.bit.CONV00 = 0; //设置ADCINA0为SEQ1的第一个转换通道AdcRegs.ADC_ST_FLAG.bit.INT_SEQ1_CLR=1; //清除SEQ1中断标志AdcRegs.ADCTRL2.bit.EVA_SOC_SEQ1 = 1; //使能EVASOC启动SEQ1AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 1; //使能SEQ1中断AdcRegs.ADCTRL2.bit.EVB_SOC_SEQ = 0;AdcRegs.ADCTRL2.bit.RST_SEQ1 = 0;AdcRegs.ADCTRL2.bit.INT_MOD_SEQ1 = 0;AdcRegs.ADCTRL2.bit.EXT_SOC_SEQ1 = 0;AdcRegs.ADCTRL2.bit.RST_SEQ2=0;AdcRegs.ADCTRL2.bit.SOC_SEQ2=0;AdcRegs.ADCTRL2.bit.INT_ENA_SEQ2=0;AdcRegs.ADCTRL2.bit.INT_MOD_SEQ2=0;AdcRegs.ADCTRL2.bit.EVB_SOC_SEQ2=0;AdcRegs.ADCTRL2.bit.SOC_SEQ1 = 0; //为1时,软件启动ADC转换}void InitEv(void){EvaRegs.T1CMPR = 0x0000;EvaRegs.T1PR = 75; //2MHZ的采样频率EvaRegs.GPTCONA.bit.T1TOADC = 2; //使能事情管理器A,周期中断启动ADC EvaRegs.T1CON.all = 0x1042;}interrupt void ADInterrupt(void){IFR = 0x0000;//-------------------------------------ADTemp[ADTempIndex] = (unsigned char)((AdcRegs.RESULT0)>>8); ADTempIndex = (ADTempIndex+1)&0x01;Value = ADTemp[0] + ADTemp[1];if(++aa > 1000000){aa = 0;LED3 = ~LED3;}//-------------------------------------AdcRegs.ADC_ST_FLAG.bit.INT_SEQ1_CLR = 1; //清除INT_SEQ1中断标志AdcRegs.ADCTRL2.bit.RST_SEQ1 = 1; //复位SEQ1序列PieCtrl.PIEACK.all = 0xFFFF; //允许再次响应中断}void main(void){InitSysCtrl(); //初始化系统DINT; //屏蔽全局中断IER = 0x0000; //禁止所有中断IFR = 0x0000; //清除所有中断标志InitPieCtrl(); //初始化PIE中断InitPieVectTable(); //初始化PIE中断矢量表InitGpio(); //初始化通用IO口InitSci(); //初始化SCIA寄存器,即初始化串口EALLOW; //允许操作寄存器PieVectTable.ADCINT = &ADInterrupt; //设置ADC中断入口地址EDIS; //禁止操作寄存器InitAdc(); //初始化ADC寄存器IER |= M_INT1; //使能CPU中断1,即第一组PIE中断,共12组PIE中断InitEv(); //初始化事件触发器A,用于定时采样EINT; //使能全局中断ERTM; //Enable Global realtime interrupt DBGMwhile(1){SendToPC(ASCIIBuffer,100,'U'); Delay();}}。

TMS320F2812中文手册

TMS320F2812中文手册第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x 系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征特征 F2810 F2812 指令周期(150MHz) 6.67ns 6.67ns SRAM(16位/字)18K 18K 3.3V片内Flash(16位/字) 64K 128K 片内Flash/SRAM的密钥有有有有 Boot ROM掩膜ROM 有有外部存储器接口无有事件管理器A和B(EVA和EVB)EVA、EVB EVA、EVB*通用定时器 4 4*比较寄存器/脉宽调制 16 16*捕获/正交解码脉冲电路 6/2 6/2 看门狗定时器有有 12位的ADC 有有*通道数 16 16TMS320C28x系列DSP的CPU与外设(上) ?2?续表特征 F2810 F2812 32位的CPU定时器 3 3 串行外围接口有有串行通信接口(SCI)A和B SCIA、SCIB SCIA、SCIB 控制器局域网络有有多通道缓冲串行接口有有数字输入/输出引脚(共享)有有外部中断源 3 3 核心电压1.8V 核心电压1.8V 供电电压 I/O电压3.3V I/O电压3.3V 封装128针PBK 179针GHH,176针PGF 温度选择‡ A:-40? ~ +85? PGF和GHH PBK S:-40? ~ +125? 仅适用于TMS 仅适用于TMS 产品状况‡‡产品预览(PP) AI AI 高级信息(AI)(TMP)‡‡‡ (TMP)‡‡‡ 产品数据(PD)注:‡ “S”是温度选择(-40? ~ +125?)的特征化数据,仅对TMS是适用的。

F2812主要功能简介-事件管理器

tactive (2 TxPR-TxCMPRup -TxCMPRdn )T定标输入时钟周期

TxCMPRup=0,TxCMPRdn≠0

tactive (2 TxPR-TxCMPRdn )T定标输入时钟周期

TxCMPRup=0,TxCMPRdn=0

tactive 2 TxPR T定标输入时钟周期

TxCMPRup﹥TxPR,TxCMPRdn﹥TxPR

tactive 0

35

GP Timer 复位状态

任何RESET事件发生时,都产生下列结果

计数方向位 = 1 其它所有定时器寄存器的位 = 0,定时器被禁止 所有中断标志位 = 0 功率保护中断屏蔽位 = 1,开放 其它所有中断屏蔽位 = 0 定时器比较输出被置高阻

内部/外部时钟输入,可编程分频,方向可引脚控制

4种可屏蔽中断:上溢、下溢、比较、周期

全比较单元 Full-Compare Units

3 x 2 个独立的比较单元,每个有6个比较输出

配合可编程死区发生器,产生PWM波形

可编程死区发生器 Programmable Deadband

Generation

为什么要设计6个PWM输出?

3个4位计数器,1个16位比较寄存器,死区值可编程

PWM波形发生器 PWM Waveform Generation

共可产生8个PWM波形输出

捕获单元 Capture Units

EVA:CAP1/2/3,EVB:CAP4/5/6,上/下边沿触发

3个16位 2-level-deep FIFO堆栈

不变

高 低 低 高 立即高 立即低

31

PWM输出逻辑

TMS320F2812的ADC采样配置

AdcRegs.ADCCHSELSEQ3.bit.CONV08=0x8;

AdcRegs.ADCCHSELSEQ3.bit.CONV09=0x9;

AdcRegs.ADCCHSELSEQ3.bit.CONV10=0xA;

AdcRegs.ADCCHSELSEQ3.bit.CONV11=0xB;

1

第三个:四个输入通道选择排序寄存器 ADCCHSELSEQx(X=1、2、3、4),都是 16 位的寄存器, 每个寄存器中的 4 位确定一个采样通道(因为 4 位最大值正好是 16,这样每个 4 位就可以 确定 16 个通道的任一个),这样一个寄存器确定 4 个通道,4 个寄存器正好是确定 16 个通 道。每个寄存器可以确定 4 个通道,这 4 个通道可以是一样的,甚至 4 个寄存器确定的都是 一样的,这样就实现了过采样技术。 a、双通道顺序采样 双通道顺序采样,用到的自动排序器是 SEQ1,SEQ2,其中 SEQ1 将用到 ADCADCCHSELSEQ1 和 ADCADCCHSELSEQ2,ADCCHSELSEQx 中的每 4 位的最高位设置为 0;SEQ2 将用到 ADCADCCHSELSEQ3 和 ADCADCCHSELSEQ4,ADCCHSELSEQx 中的每 4 位的最高位设置为 1;用 到 ADCMAXCONV 中最后七位的低三位和高三位。低三位 MAXCONV1_2-0 决定 SEQ1 中的采 样次数;高三位 MAXCONV2_2-0 决定 SEQ2 中的采样次数.转换顺序是从 ADCADCCHSELSEQ1 的最低 4 位开始一直到 ADCADCCHSELSEQ4 的最高 4 位这个顺序来的。 C 代码分析:这个是 16 个顺序采样的,每个通道都采样一次

TMS320F2812的ADC模

TMS320F2812的ADC模块是一个12位分辨率的、具有流水线结构的模数转换器。

它具有16个通道,可以配置为2个独立的8通道模块,也可以级联成一个16通道的模块。

有两个序列发生器,可以配置为双序列和级联模式,即两个独立的8状态序列发生器和一个16状态的序列发生器。

2812的ADC输入电压为0~3V,如果超出了这个范围,有可能将片子烧掉。

顺序采样和并发采样是对16个通道的配置,如果为顺序采样,则一次一个通道;如果为并发采样,则一次采集两个通道,对于电压和电流同时采集非常方便。

通过设置AdcRegs.ADCTR L3.bit.SMODE_SEL = 0/1;来选择,此位为0则是顺序采样,为1则是并发采样。

双序列和级联模式主要是区分序列发生器的使用,可选择两个序列发生器或者是一个序列发生器。

通过设置AdcRegs.ADCTRL1.bit.SEQ_CASC= 0/1;0为双序列发生器,1为级联模式即只有一个序列发生器。

对于启动ADC的触发源主要是有:软件触发,EVA或EVB触发,外部引脚触发。

软件触发是通过设置AdcRegs.ADCTRL2.bit.SOC_SEQ1 = 1;即可启动AD采样。

EVA或EVB触发是通过事件管理器的多种定时方式来启动,包括定时器启动、CAPTURE3或CAPTURE6、PWM等启动方式,在EV的初始化中设置相应的启动位。

例如EvbRegs.GPT CONA.bit.T4TOADC = 1;或EvbRegs.CAPCONB.bit.CAP6TOADC = 1;对于EVA或EVB触发ADC,值得注意的是:对于单序列发生器可以通过EVA或者EVB 触发,ADCTRL2寄存器的第一位EVB SOC SEQ只有在单序列发生器时才激活。

而且单序列发生器模式下,SEQ和SEQ1的设置时重合的,即设置SEQ1即使用SEQ;而在双序列发生器模式下,ADCTRL2寄存器后面的关于SEQ2的位才起作用。

TMS320F2812芯片ADC模数转换精度的分析

TMS320F2812芯片ADC模数转换精度的分析TMS320F2812是高精度的,其运算速度快,工作时钟频率达150 MHz,命令周期可达6.67 ns以内,低功耗(核心1.8 V,I/O口电压3.3 V)。

采纳哈佛结构,具有强大的操作能力、快速的中断响应和处理能力以及统一的寄存器编程模式。

并且在片上集成了Flash存储器,可实现外部存储器的扩展。

外部扩展模块(PIE)可支持96个外部中断,45个可用。

两个增加的大事管理器模块(EVA、EVB),提供了一整套用于运动控制和电机控制的功能和特性。

每个大事管理模块包括通用定时器(GP)、比较单元、捕捉单元以及正交编码脉冲。

外围设备包括3个32 bit的CPU 定时器,16通道12 bit (单个转换时光为200 ns,单路转换时光为60 ns),它不仅具有串行外围接口(SPI)和两个串行通信接口(SCI),还有改进的局域网络(eCAN)、多通道缓冲串行接口(McBSP)和串行外围接口模式。

28X核提供了高达400 的计算带宽,它能够满足大多数经典实时控制算法,在工业、光传输网络和自动控制等领域拥有应用前景。

但是,在获得其较高工作时钟频率150 MHz、低功耗的I/O口3.3 V电压的同时,对其在电磁兼容和ADC模数转换单元等实际应用提出了更高的要求。

特殊是ADC模数转换单元,受到了众多用法者的诟病,称其实测的精度甚至低于TMS320F2407的10 bit ADC模数转换精度。

有人疑惑TMS320F2812核内数字地和模拟地衔接设计有缺陷,但尚未得到TI公司的证明。

TI公司发布了SPRA989的ADC校准文档,仅修正了模数转换的增益和偏移,与彻低有用的要求尚有一定差距。

本文从实际应用的角度动身,考虑其外围设计因素,提高ADC模数转换精度。

1 ADC模数转换精度分析以及测试办法影响ADC模数转换终于结果精度的缘由无数,诸如芯片内部模数转换、模数转换的增益和偏移引起的误差,这些都是生产厂商控制和讨论的领域,本文不作研究。

TMS320F2812的AD及其精度校准

TMS320F2812内部集成了ADC转换模块,该模块具有如下的功能:1.12位ADC核,内置了双采样-保持器(S/H);2.顺序采样模式或者同步采样模式;3.模拟输入:0V~3V;4.快速转换时间运行在25MHz,ADC时钟,或12.5MSPS;5.16通道,多路选择输入;6.自动序列化,在单一时间段内最大能提供16个自动A/D转换,每个转换可编程对16个输入通道中的任何一个进行选择。

7.序列发生器可按2个独立的8状态序列发生器或1个16状态序列发生器。

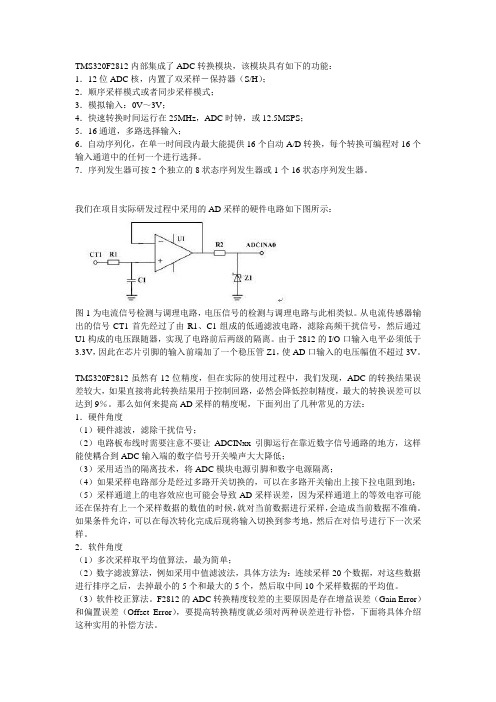

我们在项目实际研发过程中采用的AD采样的硬件电路如下图所示:图1为电流信号检测与调理电路,电压信号的检测与调理电路与此相类似。

从电流传感器输出的信号CT1首先经过了由R1、C1组成的低通滤波电路,滤除高频干扰信号,然后通过U1构成的电压跟随器,实现了电路前后两级的隔离。

由于2812的I/O口输入电平必须低于3.3V,因此在芯片引脚的输入前端加了一个稳压管Z1,使AD口输入的电压幅值不超过3V。

TMS320F2812虽然有12位精度,但在实际的使用过程中,我们发现,ADC的转换结果误差较大,如果直接将此转换结果用于控制回路,必然会降低控制精度,最大的转换误差可以达到9%。

那么如何来提高AD采样的精度呢,下面列出了几种常见的方法:1.硬件角度(1)硬件滤波,滤除干扰信号;(2)电路板布线时需要注意不要让ADCINxx引脚运行在靠近数字信号通路的地方,这样能使耦合到ADC输入端的数字信号开关噪声大大降低;(3)采用适当的隔离技术,将ADC模块电源引脚和数字电源隔离;(4)如果采样电路部分是经过多路开关切换的,可以在多路开关输出上接下拉电阻到地;(5)采样通道上的电容效应也可能会导致AD采样误差,因为采样通道上的等效电容可能还在保持有上一个采样数据的数值的时候,就对当前数据进行采样,会造成当前数据不准确。

如果条件允许,可以在每次转化完成后现将输入切换到参考地,然后在对信号进行下一次采样。

3.1 F2812主要功能简介-系统控制和中断

F2812主要功能简介 3 F2812主要功能简介 3-1 1 系统控制和中断 F2812的存储器 F2812的存储器

问题

F2812有哪些片上存储器 有哪些片上存储器? 1 F2812有哪些片上存储器? 2 各有多少?地址如何分布? 各有多少?地址如何分布?

Flash & OTP Flash on-chip (F2812) on128K x 16bit, 0x3D 8000 – 0x3F 7FFF always enabled, program & data space Multiple sectors Code security Low power modes Wait states can be adjusted based on CPU frequency Flash pipeline mode improve performance

Lowest power CPU read or fetch, active or read state

Standby State

CPU read or fetch, active or read state

Active or Read State

Highest power Prefetch mechanism

问题

密码存储在哪里? 1 密码存储在哪里? 2 地址多少? 地址多少?

CSM Functional Description

代码安全密码区 (PWL):

0x3F 7FF8 – 0x3F 7FFF 中有用户烧写, Flash 中有用户烧写,更改需知道旧密码 OTP 中 TI 公司一次性烧写

PWL全为 PWL全为 1: PWL全为 PWL全为 0:

FBANKWAIT, FBANKWAIT, Flash Waitstate Register

F2812模数转换器ADC

•

• 在A/D转换器进行采样期间,保持被转换输入信号 不变的电路称为采样保持电路;

四、采样保持器(Sample Holder)

• A/D转换器完成一次转换所需要的时间称为转换时 间;

• 不同A/D转换芯片,其转换时间各异,对于连续变 化较快的模拟信号如果不采取采样保持措施,将会 引起转换误差;

• 慢速变化的模拟信号,在A/D转换系统中,完全可 以不必采用采样保持电路,而且并不会影响A/D转 换的精度。

3.1 Quantization sample-and-hold (S/H) analog-to-digital converter (ADC)

ADC and DAC

ADC and DAC

ADC and DAC

采样就是把自变量(在这个例子里面是时间)由连续的变为离散的。 量化就是把应变量(这个例子里就是电压)由连续的变为离散的。

第五部分:F2812模/数

转换器(ADC)

ADC and DAC

现实生活中的信号大多为连续信号,而计算机只能处理数字信号。模数转换 (Analog-to-Digital Conversion ADC)和数模转换(Digital-to-Analog Conversion DAC)技术使得计算机可以处理现实生活中的信号了。数字信息有 两个重要特征:它经过采样(sampled)得到的和它是经过量化(quantized) 的,这两个因素限制了数字信号中包含信息的多少。

概述

模拟量——连续变化的物理量

模拟/数字转换器 ADC

DAC 数字/模拟转换器

数字量——时间和数值上都离散的量

模/数与数/模转换通道的组成

一般模/数转换通道由传感器、信号 处理、多路转换开关、采样保持器以及

TMS320F2812中文资料介绍

TMS320F2812中⽂资料介绍TMS320F2812中⽂资料介绍简介:德州仪器所⽣产的TMS320F2812数字讯号处理器是针对数字控制所设计的电机控制(digital motor control, DMC)、资料撷取及I/O控制(data acquisition and control, DAQ)等领域。

针对应⽤最佳化,并有效缩短产品开发周期,F28x核⼼⽀持全新CCS环境的C compiler,提供C语⾔中直接嵌⼊汇编语⾔的程序开发介⾯,可在C语⾔的环境中搭配汇编语⾔来撰写程序。

值得⼀提的是,F28x DSP核⼼⽀持特殊的IQ-math函式库,系统开发⼈员可以使⽤便宜的定点数DSP来发展所需的浮点运算算法。

F28x系列DSP预计发展⾄400MHz,⽬前已发展⾄150MHz的Flash型式。

1.⾼性能静态CMOS制成技术(1)150MHz(6.67ns周期时间)(2)省电设计(1.8VCore,3.3VI/O)(3)3.3V快取可程序电压2.JTAG扫描⽀持3.⾼效能32BitCPU(1)16x16和32x32MAC Operations(2)16x16Dual MAC(3)哈佛总线结构(4)快速中断响应(5)4M线性程序寻址空间(LinearProgramAddressReach)(6)4M线性数据寻址空间(LinearDataAddressReach)(7)TMS320F24X/LF240X程序核⼼兼容4.芯⽚上(On-Chip)的内存(1)128Kx16 Flash(4个8Kx16,6个16Kx16)(2)1Kx16OTPROM(单次可程序只读存储器)(3)L0和L1:2组4Kx16 SARAM(4)H0:1组8Kx16SARAM(5)M0和M1:2组1Kx16 SARAM共128Kx16 Flash,18Kx16 SARAM5.外部内存接⼝(1)⽀持1M的外部内存(2)可程序的Wait States(3)可程序的Read/Write StrobeTi最⼩g(4)三个独⽴的芯⽚选择(Chip Selects)6.频率与系统控制(1)⽀持动态的相位锁定模块(PLL)⽐率变更(2)On-Chip振荡器(3)看门狗定时器模块7.三个外部中断8.外围中断扩展⽅块(PIE),⽀持45个外围中断9.128位保护密码(1)保护Flash/ROM/OTP及L0/L1SARAM(2)防⽌韧体逆向⼯程10.三个32位CPU Timer11.电动机控制外围(1)两个事件管理模块(EVA,EVB)(2)与240xADSP相容12. (1)同步串⾏外围接⼝SPI模块(2)两个异步串⾏通讯接⼝SCI模块,标准UART(3)eCAN(Enhanced Controller Area Network)(4)McBSP With SPI Mode13.16个信道12位模拟-数字转换模块(ADC)(1)2x8通道的输⼊多任务(2)两个独⽴的取样-保持(Sample-and-Hold)电路(3)可单⼀或同步转换(4)快速的转换率:80ns/12.5MSPS2.2TMS320F2812硬件结构介绍2.2.1OSC与PLL⽅块F2812芯⽚上设计了⼀个相位锁定模块(PLL),这个模块将会提供整个芯⽚所需频率源。

1 TMS320F2812简介

1 TMS320F2812简介TMS320F2812是TI公司的一款用于控制的高性能、多功能、高性价比的32位定点DSP芯片。

该芯片兼容TMS320LF2407指令系统最高可在150MHz主频下工作,并带有18k×16位0等待周期片上SRAM和128k×16位片上FLASH(存取时间36ns)。

其片上外设主要包括2×8路12位ADC(最快80ns转换时间)、2路SCI、1路SPI、1路McBSP、1路eCAN等,并带有两个事件管理模块(EVA、EVB),分别包括6路PWM/CMP、2路QEP、3路CAP、2路16位定时器(或TxPWM/TxCMP)。

另外,该器件还有3个独立的32位CPU定时器,以及多达56个独立编程的GPIO引脚,可外扩大于1M×16位程序和数据存储器。

TMS320F2812采用哈佛总线结构,具有密码保护机制,可进行双16×16乘加和32×32乘加操作,因而可兼顾控制和快速运算的双重功能。

通过对TMS320F2812定点DSP芯片合理的系统配置和编程可实现快速运算,本文着重对此加以说明。

2 TMS320F2812基本系统配置2.1TMS320F2812时钟TMS320F2812的片上外设按输入时钟可分为如下4个组:(1)SYSOUTCLK组:包括CPU定时器和eCAN总线,可由PLLCR寄存器动态地修改;(2)OSCCLK组:主要是看门狗电路,由WDCR寄存器设置分频系数;(3)低速组:有SCI、SPI、McBSP,可由LOSPCP寄存器设置分频系数;(4)高速组:包括EVA/B、ADC,可由HISPCP寄存器设置分频系数。

为了使系统具有较快的工作速度,除了定时器和SCI等少数需要低速时钟的地方,其它外设均可以150MHz时钟工作。

图12.2存储空间图1所示是TMS320F2812的内部存储空间映射图。

TMS320F2812为哈佛(Harvard)结构的DSP,即在同一个时钟周期内可同时进行一次取指令、读数据和写数据的操作。

F2812模数转换器(ADC)

ADC and DAC

ADC and DAC

3.2 Sampling Theorem 只要能从采样点重构出原来的连续信号就可以说前面的采样是正确的。

概述

在自动控制和测量系统中,被控制和被测量的对 象往往是一些连续变化的物理量。如:温度、压力、 流量、速度、电流、电压等。这些随时间连续变化的 物理量,称为模拟量(Analog)。计算机参与测量和控 制时,模拟量不能直接送入计算机,必须先把它们转 换成数字量(Digital)。能够将模拟量转换成数字量的器 件称为模拟数字转换器,简称ADC。

3.1 Quantization sample-and-hold (S/H) analog-to-digital converter (ADC)

ADC and DAC

ADC and DAC

ADC and DAC

采样就是把自变量(在这个例子里面是时间)由连续的变为离散的。 量化就是把应变量(这个例子里就是电压)由连续的变为离散的。

二、信号放大处理

信号放大处理电路,接在A/D转换器与传 感器之间,用于解决以下存在问题:

• A/D转换器与传感器二者电压不匹配; • 如果是电流型输出传感器,要进行Ⅰ~Ⅴ变换与 放大处理,将电流信号对应变换成电压信号; • 传感器工作在现场,可能存在复杂的强电磁波的 干扰,通常采用RC低通滤波器,滤除叠加在传感器 输出信号上的高频干扰信号,也可采用有源滤波技 术,使得滤波特性更好。

传感器的组成材料发生改变,使得输出连续变化的

电流或电压与非电物理量的变化成正比。

由于传感器组成材料发生改变引起输出电流或 电压的变化十分微弱,容易受外界干扰,因此,在 市场上能买到的各种变送器,已将传感器与放大电 路制作在一起,输出统一标准的0~10mA或4~ 20mA电流,或0~5V电压,以便传输或直接送A/D 转换器进行A/D转换,其中,4~20mA标准电流输 出的传感器较为普遍,常说的流量变送器、压力变 送器等一般输出4~20mA标准电流,内部处于恒流 输出结构,显然电流型传感器比电压型传感器抗干 扰能力强,易于远距离传输,因此,电流型传感器 被广泛用于生产过程的检测系统中。

F2812 ADC转换时间与采样频率

F2812 ADC转换时间与采样频率F2812 ADC有多种灵活的启动方式:软件直接启动S/W,EVA的事件源,EVB的事件源和外部引脚启动。

如果采用触发方式,ADC的采样频率就是触发的频率,如果是连续自动的采样,那就是采样窗口+转换时间,这个很好理解。

需要注意的是,如果采用EV的事件启动ADC,必须保证两次启动时间的间隔大于ADC固有的转换时间。

下面给出ADC转换时间的具体计算方式,由于我采用的是序列方式,本文中只探讨这种方式,同时采样方式的转换时间可以类似求解。

图1. 序列采样时序图图1中是采样两个通道的时序图,根据这个原理,可以求解MAX_CONV为N时的转换时间。

从图中可以看到,ADC SOC tigger信号有效后,2.5个ADCCLK后开始第一次转换,Acquisition window的长度由寄存器AdcRegs.ADCTRL1.bit.ACQ_PS决定,Acquisition window=(ACQ_PS+1)*ADCCLK,而随后的寄存器更新时间为4ADCCLK,也就是说第一个寄存器出现采样结果共耗时:T1=(2.5+(ACQ_PS+1)+4)ADCCLK,同理可以推得第二个寄存器出现采样结果共耗时:T2=(2.5+(ACQ_PS+1)+4+(ACQ_PS+2))ADCCLK,类推可以得出N+1通道全部得到结果共耗时:T=(2.5+(ACQ_PS+1)+4+N*(ACQ_PS+2))ADCCLK = (7.5+2*N+(ACQ_PS+1)*N)ADCCLK PS:上图中有个问题,两个C1的长度并不相同,考虑到边沿有限,我认为两个C1都应该是4*ADCCLK,下面的实验也证明了这一点。

在试验程序中,DSP工作在150MHz,ADCCLK为7.5MHz,ACQ_PS设为1,序列采样方式,N为15(采样16通道),完成一次ADC所需的时间为:T=(7.5+2*15+(1+1)*15)/7.5us = 7us试验程序采用EVA的周期中断启动ADC,完成后产生ADC完成中断,在中断中设置信号量,观察者两个信号量的关系,就可以计算这个时间是否正确,定时周期为100us,EVA 设置如下:// Initialize EVA Timer 1:// Setup Timer 1 Registers (EV A)EvaRegs.GPTCONA.all = 0;// Set the Period for the GP timer 1 to 0x0200;EvaRegs.T1PR = T1PR_VALUE; // PeriodEvaRegs.T1CMPR = 0x0000; // Compare Reg// Enable Period interrupt bits for GP timer 1// Count up, x128, internal clk, enable compare, use own period EvaRegs.EVAIMRA.bit.T1PINT = 1;EvaRegs.EVAIFRA.bit.T1PINT = 1;// Clear the counter for GP timer 1EvaRegs.T1CNT = 0x0000;EvaRegs.T1CON.all = 0x1742;// Start EVA ADC Conversion on timer 1 Period interruptEvaRegs.GPTCONA.bit.T1TOADC = 2;EVA周期中断代码如下:interrupt void T1PINT_ISR(void) // EV-A{// Insert ISR Code hereif (i == 0){i = 1;GpioDataRegs.GPASET.bit.GPIOA0 = 1;}else{i = 0;GpioDataRegs.GPACLEAR.bit.GPIOA0 = 1;}// Enable more interrupts from this timerEvaRegs.EVAIMRA.bit.T1PINT = 1;EvaRegs.EVAIFRA.all = BIT7;// Acknowledge interrupt to receive more interrupts from PIE group 2PieCtrlRegs.PIEACK.all = PIEACK_GROUP2;}ADC中断代码如下:interrupt void ADCINT_ISR(void) // ADC{// Insert ISR Code hereif (i == 1){GpioDataRegs.GPASET.bit.GPIOA1 = 1;}else{GpioDataRegs.GPACLEAR.bit.GPIOA1 = 1;}AdcRegs.ADCTRL2.bit.RST_SEQ1 = 1; // Reset SEQ1AdcRegs.ADCST.bit.INT_SEQ1_CLR = 1; // Clear INT SEQ1 bit PieCtrlRegs.PIEACK.all = PIEACK_GROUP1; // Acknowledge interrupt to PIE}用示波器观察A0与A1的波形,可以观察到时间间隔约为7.0400us,与计算结果基本一致。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

灵活的中断控制,每个排序结束(EOS)或每两次EOS 灵活的中断控制,每个排序结束(EOS) 每两次EOS (EOS)或 …………

ADC Module Block Diagram

同步采样级联排序举例

AdcRegs.ADCTRL3.bit.SMODE_SEL = 1; AdcRegs.ADCTRL1.bit.SEQ_CASC = 1; AdcRegs.ADCMAXCONV.all = 7; AdcRegs.ADCHSELSEQ1.bit.CONV00 = 0; AdcRegs.ADCHSELSEQ1.bit.CONV01 = 1; AdcRegs.ADCHSELSEQ1.bit.CONV02 = 2; AdcRegs.ADCHSELSEQ1.bit.CONV03 = 3; AdcRegs.ADCHSELSEQ2.bit.CONV08 = 4; AdcRegs.ADCHSELSEQ2.bit.CONV09 = 5; AdcRegs.ADCHSELSEQ2.bit.CONV10 = 6; AdcRegs.ADCHSELSEQ2.bit.CONV11 = 7; // // // // // // // // // // // 同步采样 级联 8 x 2 排序 来自A0 A0和 来自A0和B0 来自A1 A1和 来自A1和B1 来自A2 A2和 来自A2和B2 来自A3 A3和 来自A3和B3 来自A4 A4和 来自A4和B4 来自A5 A5和 来自A5和B5 来自A6 A6和 来自A6和B6 来自A7 A7和 来自A7和B7

F2812 ADC Features

单12位ADC核,双S/H电路,16通道,多路选通输入 12位ADC核 S/H电路 16通道 电路, 通道, 同步采样或顺序采样, 同步采样或顺序采样,高速转换 模拟输入范围: 模拟输入范围:0~3V 通道的转换顺序可由自动排序器决定,一次可执行16 通道的转换顺序可由自动排序器决定,一次可执行16 个通道的自动转换, 个通道的自动转换,每次转换的具体通道由编程决定 两个独立的8通道的排序器, 两个独立的8通道的排序器,可以工作在独立双排序 模式, 模式,也可工作在级联模式 16个独立寻址结果寄存器 D 个独立寻址结果寄存器: 16个独立寻址结果寄存器: = 4095×(A− ADCLO)/3 多种触发源启动转换: 多种触发源启动转换:

SEQ1双排序举例

(1) (2) (3) (4) ADC初始化 ADC初始化 SOC触发信号启动转换 SOC触发信号启动转换 最大通道数载入SEQ SEQ计数 最大通道数载入SEQ计数 开始转换: 开始转换: 每转换一个,计数减1 每转换一个,计数减1 转换结果存缓存 转换完成?SEQ计数=0? 计数=0 (5) 转换完成?SEQ计数=0? !=0, (6) !=0,转(4) =0, 中断请求

问题

比较以上两例,结果一样, 比较以上两例,结果一样, 转换过程差别在哪里? 转换过程差别在哪里?

3 F2812主要功能简介 F2812主要功能简介 3-2 AD转换器 AD转换器

3 不间断的自动排序模式

问题

ADC有16个输入 16个结果缓存 个输入、 个结果缓存。 F2812 ADC有16个输入、16个结果缓存。 如何设计实现多个结果一次集中读取? TI 如何设计实现多个结果一次集中读取? 这样有什么好处? 这样有什么好处?

结果: 结果:

A0 B0 A1 B1 RESULT0 RESULT1 RESULT2 RESULT3 A2 B2 A3 B3 RESULT4 RESULT5 RESULT6 RESULT7 A4 B4 A5 B5 RESULT8 RESULT9 RESULT10 RESULT11 A6 B6 A7 B7 RESULT12 RESULT13 RESULT14 RESULT15

ADC Registers

3 F2812主要功能简介 F2812主要功能简介 3-2 AD转换器 AD转换器

2 自动转换排序器原理

ADC自动排序器

特性参数 转换触发源 最多可选择 通道数 触发转换 优先级 转换结果 寄存器 通道号 SEQ1 EVA、软件、 EVA、软件、 外引脚 8 高 RESULT0- RESULT0-7 CONV00- CONV00-07 SEQ2 EVB、 EVB、软件 8 低 RESULT8- RESULT8-15 CONV08- CONV08-15 SEQ EVA、EVB、 EVA、EVB、 软件、 软件、外引脚 16 无 RESULT0- RESULT0-15 CONV00- CONV00-15

结果: 结果:

A0 B0 A1 B1 RESULT0 RESULT1 RESULT2 RESULT3 A2 B2 A3 B3 RESULT4 RESULT5 RESULT6 RESULT7 A4 B4 A5 B5 RESULT8 RESULT9 RESULT10 RESULT11 A6 B6 A7 B7 RESULT12 RESULT13 RESULT14 RESULT15

采样保持窗宽度

ADCTRL1的 n+1个ADCCLK宽 ADCTRL1的ACQ_PS 4位, =n: n+1个ADCCLK宽

问题

能列出从晶振到ADCCLK的完整时钟链各环节吗? 能列出从晶振到ADCCLK的完整时钟链各环节吗? ADCCLK的完整时钟链各环节吗 S/H窗宽是什么意思 为什么设计成可调节的? 窗宽是什么意思? S/H窗宽是什么意思?为什么设计成可调节的?

ADC顺序采样时序

ADC同步DCTRL3.bit.SMODE_SEL = 1; // 同步采样 AdcRegs.ADCMAXCONV.all = 0x0033; // 4 x 2 排序 来自A0 A0和 AdcRegs.ADCHSELSEQ1.bit.CONV00 = 0; // 来自A0和B0 来自A1 A1和 AdcRegs.ADCHSELSEQ1.bit.CONV01 = 1; // 来自A1和B1 来自A2 A2和 AdcRegs.ADCHSELSEQ1.bit.CONV02 = 2; // 来自A2和B2 来自A3 A3和 AdcRegs.ADCHSELSEQ1.bit.CONV03 = 3; // 来自A3和B3 来自A4 A4和 AdcRegs.ADCHSELSEQ2.bit.CONV08 = 4; // 来自A4和B4 来自A5 A5和 AdcRegs.ADCHSELSEQ2.bit.CONV09 = 5; // 来自A5和B5 来自A6 A6和 AdcRegs.ADCHSELSEQ2.bit.CONV10 = 6; // 来自A6和B6 // 来自A7和B7 AdcRegs.ADCHSELSEQ2.bit.CONV11 = 7; 来自A7和 A7

ADC上电顺序 如果使用外部AD参考电源,使能该位(ADCTRL3 如果使用外部AD参考电源,使能该位(ADCTRL3 AD参考电源 bit8) 必须先使能外部参考电源,再带隙上电 (避免内外电源冲突) 避免内外电源冲突) 带隙和参考电源上电 7ms 后才能给ADC上电 后才能给ADC上电 ADC完全上电后至少延时 ADC完全上电后至少延时 20us 才能开始转换

1 A/D转换器的特点 A/D转换器的特点

问题

1 关于A/D转换, 关于A/D转换, A/D转换 你能列举哪些与之相关的关键词? 你能列举哪些与之相关的关键词? 解释“采样” 保持” 同步” 2 解释“采样”、“保持”、“同步”、 异步” 串行” 并行”等名词。 “异步”、“串行”、“并行”等名词。

SEQ1双排序举例 参见教材描述(例3.1 p96) p96) 参见教材描述( 每组七个转换:A2、A3、A2、A3、A6、A7、B4 每组七个转换:A2、A3、A2、A3、A6、A7、 Setup: Setup:

最大转换通道数: 最大转换通道数:MAXCONV1 = 6 通道选择排序器: 通道选择排序器:

3 F2812主要功能简介 F2812主要功能简介 AD转换器 3-2 AD转换器

1 2 3 4 5 6 A/D转换器的特点 A/D转换器的特点 自动转换排序器原理 不间断的自动排序模式 ADC时钟定标 ADC时钟定标 ADC寄存器 ADC寄存器 ADC的 ADC的C语言编程实例

3 F2812主要功能简介 F2812主要功能简介 3-2 AD转换器 AD转换器

ADC时钟和采样率

完整时钟链

举例

问题

最高极限ADCCLK频率是多少? 假设晶振30MHz) 最高极限ADCCLK频率是多少?(假设晶振30MHz) ADCCLK频率是多少

ADC低功耗模式 ADCTRL3

bit7ADC带隙和参考电源开关 ADCBGRFDN, bit7-6, ADC带隙和参考电源开关 ADCPWDN, bit5, ADC电源开关 ADC电源开关

问题

结果放在哪里? 结果放在哪里? 如何(自动) 如何(自动)开始下 一组转换?

排序器启/停模式

启/停模式

一组转换完成即停止, 一组转换完成即停止,不自动开始下一组转换 ADCTRL1的 RUN位须置0 ADCTRL1的CONT RUN位须置0 由触发信号启动

举例:参见教材描述( p96) 举例:参见教材描述(例3.2 p96)

ADC级联自动排序模式

ADC 双自动排序 模式

ADC自动排序器工作原理

排序器SEQ1 SEQ2中各有 排序器SEQ1、SEQ2中各有 8 个通道选择器(CONVxx) SEQ1、 通道选择器(CONVxx) 每个CONVxx都有4 CONVxx都有 对应16个输入A0 A7、B016个输入A0— 每个CONVxx都有4位:对应16个输入A0—A7、B0-B7 顺序采样:一次一个S/H SEQ1优先级较高 S/H, 顺序采样:一次一个S/H,SEQ1优先级较高 同步采样:一次2 S/H, 同步采样:一次2个S/H,但转换分先后 每次转换来自 1/16(顺序)或 A:1/8 + B:1/8(同步) 1/16(顺序) B:1/8(同步) 排序器中最大转换通道数(MAXCONV)决定SEQ重复 排序器中最大转换通道数(MAXCONV)决定SEQ重复 最大转换通道数(MAXCONV)决定SEQ 16个结果寄存器与SEQ内排序对应, 16个结果寄存器与SEQ内排序对应,并非与引脚一一对应 个结果寄存器与SEQ内排序对应 SOC、EOC信号 SOC、EOC信号 S/H 时长可编程