数电作业2

数电第2章作业答案

自我检测题解

题 2.1 答:TTL 与非门输入端采用多发射极管的主要作用是 速度快 。 题 2.2 答:TTL 与非门多余输入端的处理方法是 高电平或悬空或接电源或与其他输入 端并接 。 题 2.3 答:题 2.3 肖特基三极管是普通三极管集电结并联一个 肖特基二极管 (SBD) ,其正向压降较小容易导通。当三极管趋于深度饱和状态时,肖特基二极 管 分流 了三极管的一部分电流,使三极管工作在浅饱和状态。 题 2.4 答:TTL 与非门输出端采用推拉式输出的主要作用是 较强的负载能力 。 题 2.5 答:TTL 与非门的灌电流负载发生在输出低电平电平情况下,负载电流越大,则 输出电平越 高 。 题 2.6 答:门电路输入端个数称为门的 扇入 系数,门电路带同类门数量的多少称为门 扇出 系数。 题 2.7 答:TTL 三态门的三种可能的输出状态分别是 高电平 、 低电平 和 高阻态 。 题 2.8 答:在 TTL 三态门、OC 门、与非门和异或门电路中,能实现线与功能的门电路 有 OC 门,三态门 ,能实现总线连接方式的门电路有 三态门 。 题 2.9 答:CMOS 门电路与 TTL 门电路相比最大的优点是 低功耗 。 题 2.10 答:用工作速度来评价 TTL、ECL 和 CMOS 集成电路,速度快的集成电路依次 为 ECL;TTL;CMOS 。 题 2.11 答:用抗干扰能力来评价 TTL、ECL 和 CMOS 集成电路,抗干扰能力强的集成 电路依次为 CMOS;TTL;ECL 。 题 2.12 两输入异或电路的一输入端接地,另一输入端接信号,输出与输入的关系式 (A) F=A; (B) F=B; (C) F= A ; (D) F= B 。

川大《数字电子技术2390》20春学期在线作业2答案

22.在十六进制与十进制的转换中,FFH=256D。对吗?

答案:错误

23.8421码(自然二进制码)和8421BCD码都是四位二进制代码。对吗?

答案:错误

24.二进制代码1000和二进制代码1001都可以表示十进制数9。对吗?

答案:正确

25.TTL与非门与Βιβλιοθήκη MOS与非门的逻辑功能相同。对吗?

答案:错误

34.要改变触发器的状态,必须有CP脉冲的配合。对吗?

答案:错误

35.移位寄存器不仅可以寄存代码,而且可以实现数据的串-并行转换和处理。对吗?

答案:正确

36.若要构成七进制计数器,最少用3个触发器,并且有1个无效状态。对吗?

答案:正确

37.容量为256×4的存储器,每字4位,共计256字,1024个存储单元。对吗?

《数字电子技术2390》19秋学期在线作业2

试卷总分:100得分:97

一、单选题(共20道试题,共60分)

1.连续异或2014个1的结果是()。

A.0

B.1

C.不确定

D.逻辑关系错误

答案:A

2.在下列()的输入情况下,与非运算的结果等于逻辑0。

A.全部输入为1

B.任意输入为0

C.仅有一个输入为0

D.全部输入为0

答案:正确

答案:正确

30.正逻辑的与门是负逻辑的与非门。对吗?

答案:错误

31.普通编码器和优先编码器在某一时刻都只能输入一个有效的编码信号。对吗?

答案:错误

32.数值比较器在比较两个多位数的大小时,是按照从低位到高位的顺序逐位比较的。对吗?

答案:错误

33.基本SR锁存器电路只能由与非门组成,用或非门是不能实现的。对吗?

中南大学数电2试题答案

中南大学数电2试题答案一、选择题1. 在数字逻辑中,一个D触发器可以实现以下哪种功能?A. 边沿触发B. 水平触发C. 电平触发D. 脉冲触发答案:A2. 以下哪个选项是正确的二进制加法规则?A. 0+0=1B. 1+1=10C. 1+0=10D. 0+1=10答案:B3. 在数字电路中,什么是“同步电路”?A. 由组合逻辑电路构成的电路B. 由时序逻辑电路构成的电路C. 由异步触发器构成的电路D. 由同步触发器构成的电路答案:D4. 以下哪个是四变量逻辑函数的标准形式?A. 卡诺图B. 真值表C. 布尔表达式D. 逻辑状态图答案:C5. 一个4位二进制计数器在计数到“1111”时,下一个状态是什么?A. 0000B. 1000C. 1001D. 1100答案:A二、填空题1. 在数字电路中,__________逻辑门可以实现两个输入的逻辑与功能。

答案:AND2. 一个3线到8线译码器的输入端有__________个输入。

答案:33. 触发器的主要特性之一是具有__________功能。

答案:记忆4. 在数字电路设计中,__________是一种用于简化复杂逻辑函数的图形工具。

答案:卡诺图5. 一个计数器的输出在特定时钟周期内的变化序列称为__________。

答案:计数序列三、简答题1. 请简述数字电路与模拟电路的区别。

答:数字电路处理的是离散的信号,通常是二进制形式,它们在特定的逻辑电平上工作,如高电平或低电平。

模拟电路处理的是连续变化的信号,可以在任何电压或电流值之间变化。

数字电路的主要优点是抗干扰能力强,易于实现复杂的逻辑功能,而模拟电路则在处理连续信号,如音频和视频信号方面更为有效。

2. 什么是组合逻辑电路?答:组合逻辑电路是一种数字电路,其输出仅取决于当前的输入值,不依赖于电路之前的状态或输入历史。

这些电路不包含存储元件,如触发器,因此它们没有记忆功能。

组合逻辑电路的示例包括加法器、编码器、解码器和多路选择器。

东大20秋学期《数字电子技术基础》在线平时作业2

(单选题)1: 用二进制异步计数器从0做加法,计到十进制数178,则最少需要()个触发器。

A: 2

B: 6

C: 7

D: 8

正确答案: D

(单选题)2: 由555定时器构成的施密特触发器,改变控制电压Vco时,则()。

A: 改变输出Uo的幅值

B: 改变低电平的UOL数值

C: 改变高电平UOH的数值

D: 改变回差电压

正确答案: D

(单选题)3: 一只四输入端与非门,使其输出为0的输入变量取值组合有__________种。

A: 15

B: 8

C: 7

D: 1

正确答案: D

(单选题)4: 一位8421BCD码译码器的数据输人线与译码输出线组合是____ 。

A: 4:16

B: 1:10

C: 4:10

D: 2:4

正确答案: C

(单选题)5: 逻辑函数的对偶式

A:

B:

C:

D:

正确答案: B

(单选题)6: 欲使D触发器按工作,应使输入D= ( )。

A: 0

B: 1

C: Q

D:

正确答案: D

(单选题)7: 下列四个数中与十进制数(163)10不相等的是()。

A: (A3)16。

川大《数字电子技术2390》19秋学期在线作业2答案

试卷总分:100得分:100

一、单选题(共20道试题,共60分)

1.连续异或2014个1的结果是()。

A.逻辑关系错误

B.不确定

C.1

D.0

答案:D

2.在下列()的输入情况下,与非运算的结果等于逻辑0。

A.全部输入为1

B.全部输入为0

C.任意输入为0

D.仅有一个输入为0

A.4096

B.2048

C.1M

D.1024

答案:A

18.将三角波变换为矩形波,需选用:()。

A.施密特触发器

B.多谐振荡器

C.双稳态触发器

D.单稳态触发器

答案:A

19.555定时器不可以组成()。

A.施密特触发器

B.多谐振荡器

C.单稳态触发器

D.JK触发器

答案:D

20.A/D转换器中,转换时间最短的是()。

23.8421码(自然二进制码)和8421BCD码都是四位二进制代码。对吗?

答案:错误

24.二进制代码1000和二进制代码1001都可以表示十进制数9。对吗?

答案:正确

25.TTL与非门与CMOS与非门的逻辑功能相同。对吗?

答案:正确

26.OD门的输出端可以并联运行,实现“线与”的逻辑关系。对吗?

答案:正确

答案:B

6.的多余项是()。

A.{图}

B.{图}

C.CD

D.ABC

答案:C

7.七段显示译码器,当译码器七个输出端状态为abcdefg=0110011时(高电平有效),输入二进制代码为()。

A.0111

B.0110

C.0100

D.0011

吉大20春学期《数字电子技术》在线作业二答卷

答案:ACD

12.构成移位寄存器可以采用的触发器为( )。

A.R-S型

B.J-K型

C.主从型

D.同步型

答案:ABC

13.下列那种是描述时序电路逻辑功能的方法( )。

A.逻辑方程组

B.状态图

C.电路图

D.时序图

答案:ABD

14.下列触发器中,克服了空翻现象的有( )。

B.数据选择器

C.数值比较器

D.七段显示译码器

答案:B

5.常用的BCD码有( )。

A.奇偶校验码

B.格雷码

C.8421码

D.汉明码

答案:C

6.在下列触发器中,有约束条件的是( )。

A.主从JK F/F

B.主从D F/F

C.同步RS F/F

D.边沿D F/F

答案:C

答案:正确

17.74LS147为8-3线优先编码器。

答案:错误

18.逻辑函数的简化对于提高电路的可靠性并没有什么作用,因此实际意义不大。

答案:错误

19.一般TTL门电路的输出端可以直接相连,实现线与。

答案:错误

20.采样定理的规定,是为了能不失真地恢复原模拟信号,而又不使电路过于复杂。

D.8

答案:D

10.对于TTL与非门闲置输入端的处理,不可以( )。

A.接电源

B.通过电阻33kΩ接电源

C.接地

D.与有用输入端并联

答案:C

二、多选题 (共 5 道试题,共 20 分)

11.下列哪一个是按照电路结构对触发器进行分类的( )。

A.基本RS触发器

数字电子技术第二章(逻辑门电路)作业及答案

数字电子技术第二章(逻辑门电路)作业及答案第二章(逻辑门电路)作业及答案1.逻辑门电路如下图所示:(1)电路均为TTL电路,试写出各个输出信号的表达式。

(2)电路若改为CMOS电路,试写出各个输出信号的表达式。

答案:(1),,,(2),,,2、已知TTL反相器的电压参数为V IL(max)=0.8V,V OH(min)=3V,V TH=1.4V,V IH(min)=1.8V,V OL(max)=03V,V CC=5V,试计算其高电平噪声容限V NH和低电平噪声容限V NL。

答案:V NL= V IL(max) - V OL(max)=0.5V,V NH= V OH(min) - V IH(min) =1.2V。

3、试写出图2-1、图2-2所示逻辑电路的逻辑函数表达式。

解:(1)(2)4、试分析图2-3所示MOS电路的逻辑功能,写出Y端的逻辑函数式,并画出逻辑图。

5、试简要回答下列问题。

(1)有源(图腾柱)输出与集电极开路(OC)输出之间有什么区别?解:OC门输出端只能输出低电平和开路状态,其输出级需要上拉电阻才能输出高电平,且上拉电源可以与芯片电源不同,因此常用于不同电源电压芯片之间实现信号电平变换,OC门输出端可以并联实现线与;有源输出可以输出低电平与高电平,两个有源输出端连接在一起时,若是一个输出端输出高电平,另外一个输出端输出低电平时,可引起较大电流损坏输出级。

(2)TTL逻辑电路输入端悬空时,可视为输入高电平信号处理,而CMOS逻辑电路输入端则不允许悬空使用,试说明其原因。

解:因为CMOS电路的输入端具有非常高的输入阻抗,容易受到干扰,一旦受到干扰后,会使输出电平发生转换,产生功耗,因此输入端不能悬空,应该连接确定的逻辑电平。

6.请查阅74LS00芯片手册(常规温度范围的),回答如下问题:(1)电源电压范围;(2)输出高电平电压范围;(3)输出低电平电压范围;(4)输入高电平电压范围;(5)输入低电平电压范围;(6)该芯片的电源电流;(7)典型传播延迟时间;(8)扇出系数。

数字电子技术基础A第2次作业

(B)

2V

(C)4V

(D)3V

正确答案:B

解答参考:

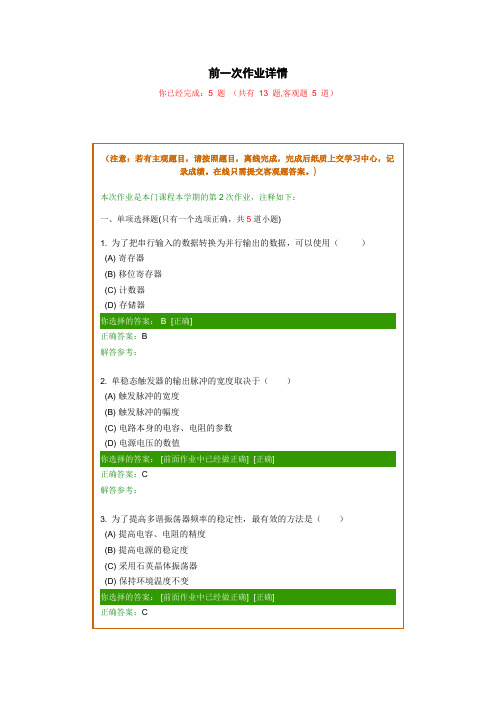

前一次作业详情

你已经完成:5题(共有13题,客观题5道)

(注意:若有主观题目,请按照题目,离线完成,完成后纸质上交学习中心,记录成绩。在线只需提交客观题答案。)

本次作业是本门课程本学期的第2次作业,注释如下:

一、单项选择题(只有一个选项正确,共5道小题)

1.为了把串行输入的数据转换为并行输出的数据,可以使用()(B)提高电源的源自定度(C)采用石英晶体振荡器

(D)保持环境温度不变

正确答案:C

解答参考:

4.已知时钟脉冲频率为fcp,欲得到频率为0.2fcp的矩形波应采用()

(A)五进制计数器

(B)五位二进制计数器

(C)单稳态触发器

(D)多谐振荡器

正确答案:A

解答参考:

5.

在图1-8用555定时器组成的施密特触发电路中,它的回差电压等于()

(A)寄存器

(B)移位寄存器

(C)计数器

(D)存储器

正确答案:B

解答参考:

2.单稳态触发器的输出脉冲的宽度取决于()

(A)触发脉冲的宽度

(B)触发脉冲的幅度

(C)电路本身的电容、电阻的参数

(D)电源电压的数值

正确答案:C

解答参考:

3.为了提高多谐振荡器频率的稳定性,最有效的方法是()

(A)提高电容、电阻的精度

数字电子技术第二次作业题及答案.doc

第2次作业一、单项选择题(本大题共40分,共20小题,每小题2分)1.4LS138译码器有(),74LS148编码器有()。

A.三个输入端,三个输出端B.八个输入端,八个输出端C.三个输入端,八个输出端D.八个输入端,三个输出端2.接通电源电压就能输岀矩形脉冲的电路是()。

A.单稳态触发器B.施密特触发器C. D触发器D.多谐振荡器3.如图所示的电路,输出F的状态是()。

A. AB. FC. 1D.04.函数F(A, B, C)二AB+BC+AC的最小项表达式为()。

A.F(A, B, C) = Lm (0, 2, 4)B.(A, B, C) = Sm (3, 5, 6, 7)C.F(A, B, C) = Zm (0, 2, 3, 4)D.F(A,B,C)二工m (2, 4, 6, 7)5.在下列逻辑电路屮,不是组合逻辑电路的是()。

A.译码器B.编码器C.全加器D.寄存器6.N个触发器可以构成最大计数长度(进制数)为()的计数器。

A. N B. 2N C. N2D. 2、7.0八(:输出范围为0〜1(^,当输入数字量为0110 (4位DAC),其输岀为()。

A.IVB.2VC.3VD.4V&十六路数据选择器的地址输入(选择控制)端有()个。

A.16B. 2C. 4D.89.电路和波形如下图,正确输出的波形是()。

A.①B・②C・③D・④10.对于钟控RS触发器,若要求其输出“0 “状态不变,则输入的RS信号应为()o A. RS=X0 B. RS=0X C. RS=X1 D. RS=1X11・已知输入A、B和输出Y的波形如下图所示,则对应的逻辑门电路是()Og—J"! JA.与门B.与非门C.或非门D.异或门12.为了把串行输入的数据转换为并行输出的数据,可以使用()。

A.寄存器B.移位寄存器C.计数器D.存储器13.存储8位二进制信息要()个触发器。

A. 2B. 3C・4D. 8 _14.欲使JK触发器按= Q n工作,可使JK触发器的输入端(J=K=1 B. J=0, K=1 C. J=0, K=0 D. J=l, K=015.在图1所示电路中,使Y二A一的电路是()。

数字电路习题集答案 (2)

=A+B+A+C =AB+AC

(或非-或非) (与或非)

(与非—与非)

(或非-或非)

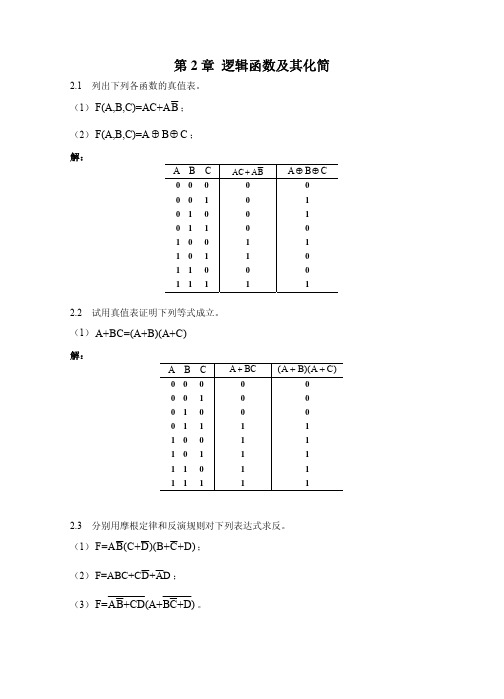

2.11 写出图 2-1 所示电路的逻辑表达式(无需化简)。

(与或非)

(a)

(b) 图 2-1 题 2.11 的逻辑图

解:(a) F1=A ⊕ B ⊕ C F2 =AB+(A ⊕ B)C

(b) Y=ABC ⋅ ABD ⋅ B ⋅ ABD ⋅ ACD ⋅ D = ABC ⋅ ABD ⋅ B+ABD ⋅ ACD ⋅ D

2.8 将下列函数展开为最小项之和和最大项之积。

(1) F(A,B,C,D)=ABC+BD+ABCD ;

(2) F(A,B,C,D)=(A+C)(A+B+D)(A+B+C+D) 解:(1) F(A,B,C,D)=ABC+BD+ABCD

= ABCD + ABCD + ABCD + ABCD + ABCD + ABCD + ABCD = Σm(1,3, 7,9,11,12,13) (2) F(A,B,C,D)=(A+C)(A+B+D)(A+B+C+D) =(A+B+C+D)(A+B+C+D)(A+B+C+D)(A+B+C+D)(A+B+C+D) (A+B+C+D) = ΠM(0,1, 4,5,8,10)

=(X+Y)Z+(X+Y)W =XZ+YZ+XYW

数电实验二 组合逻辑电路

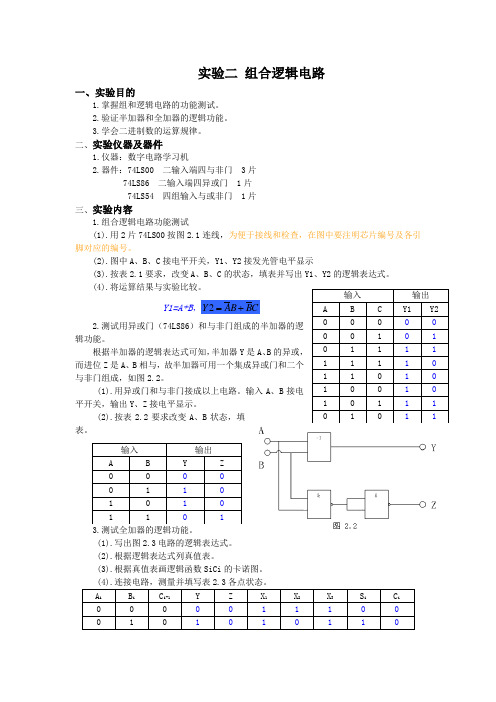

实验二 组合逻辑电路一、实验目的1.掌握组和逻辑电路的功能测试。

2.验证半加器和全加器的逻辑功能。

3.学会二进制数的运算规律。

二、实验仪器及器件1.仪器:数字电路学习机2.器件:74LS00 二输入端四与非门 3片 74LS86 二输入端四异或门 1片 74LS54 四组输入与或非门 1片三、实验内容1.组合逻辑电路功能测试(1).用2片74LS00按图2.1连线,为便于接线和检查,在图中要注明芯片编号及各引脚对应的编号。

(2).图中A 、B 、C 接电平开关,Y1、Y2接发光管电平显示(3).按表2.1要求,改变A 、B 、C 的状态,填表并写出Y1、Y2的逻辑表达式。

(4).将运算结果与实验比较。

Y1=A+B2.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。

根据半加器的逻辑表达式可知,半加器Y 是A 、B 的异或,而进位Z 是A 、B 相与,故半加器可用一个集成异或门和二个与非门组成,如图2.2。

(1).用异或门和与非门接成以上电路。

输入A 、B 接电平开关,输出Y 、Z 接电平显示。

(2).按表2.2要求改变A 、B 状态,填表。

3.测试全加器的逻辑功能。

(1).写出图2.3电路的逻辑表达式。

(2).根据逻辑表达式列真值表。

(3).根据真值表画逻辑函数SiCi 的卡诺图。

111S i C i4.测试用异或门、与或门和非门组成的全加器的功能。

全加器可以用两个半加器和两个与门一个或门组成,在实验中,常用一块双异或门、一个与或非门和一个与非门实现。

(1).写出用异或门、与或非门和非门实现全加器的逻辑表达式,画出逻辑电路图。

(2).连接电路图,注意“与或非”门中不用的“与门”输入端要接地。

(3).按表2.4记录Si 和Ci 的状态。

1-⊕⊕=i i C B A S ,AB C B A C i i +⊕=-1)(A i S iB i+ C i C i-1四、 1.整理实验数据、图表并对实验结果进行分析讨论。

数字电路第2次作业及答案

数字电路第2次作业及答案

1:[论述题]

2、逻辑函数的公式化简法的概念及其常用方法。

参考答案:1、最小项有下列性质:

(1)每一个最小项都有一组也只有一组使其值为1的对应变量取值;

(2)任意两个不同的最小项之积,值恒为0;

(3)变量全部最小项之和,值恒为1。

2、公式化简法,就是在与或表达式的基础上,利用公式和定理,消去表达式中多余的乘积项和每个乘积项中多余的因子,求出函数的最简与或式。

常用方法有并项法、吸收法、消去法、配项消项法

2:[判断题]物理量的变化在时间上或在数值上是间断的,我们把这一类物理量称为模拟量。

参考答案:错误

3:[判断题]在用数码表示不同的事物时,这些数码己没有数量大小的含义,所以将它们称为代码。

参考答案:正确

4:[判断题]二进制数的符号在数字电路中的表示方法有原码、反码和

补码。

参考答案:正确

5:[判断题]ASCII码己经由国际标准化组织(ISO)认定为国际通用的标准代码。

参考答案:正确

6:[判断题]卡诺图的主要缺点是随着变量个数的增加,图形也更简单。

参考答案:错误

7:[判断题]在八进制数中,每一位用1-8八个数码表示。

参考答案:错误

8:[判断题]基本的逻辑运算只有与、或、非三种。

参考答案:正确

9:[判断题]逻辑变量的取值可以是0,1,2。

参考答案:错误。

西南交《数字电子技术A》在线作业二【满分答案】

西南交《数字电子技术A》在线作业二---------------------------单选题1.A+BC= ( ).A. A+BB. A+CC.(A+B)(A+C)D. B+C正确答案:C2.十进制整数转换为二进制数能采用()。

A.除2取余法B.除2取整法C.除10取余法D.除10取整法正确答案:A3.一个无符号10位数字输入的DAC,其输出电平的级数为()A. 4B. 10D. 1023正确答案:C4.逻辑表达式Y=AB可以用()实现A.正或门B.正非门C.正与门D.或非门正确答案:C5.卡诺图上变量的取值顺序是采用( )的形式,以便能够用几何上的相邻关系表示逻辑上的相邻。

A.二进制码B.循环码C.ASCII码D.十进制码正确答案:B6.欲使JK触发器按Qn+1=0工作,可使JK触发器的输入端()A. J=K=1B.J=Q,K=QD.J=0,K=1 或B,C正确答案:D7.与十进制数(53.5)10等值的数或代码为( ).A.(0101 0011.0101)8421BCDB.(36.8)16C.(100101.1)2D.(65.7)8正确答案:A8.多谐振荡器可产生()A.正弦波B.矩形脉冲C.三角波D.锯齿波正确答案:B9.TTL单定时器型号的最后几位数字为()A. 555B. 556C. 7555D. 7556正确答案:A10.对于JK触发器,若J=K,则可完成()触发器的逻辑功能A. RSB. DC. TD. T'正确答案:C---------------------------多选题1.下列触发器中,克服了空翻现象的有( )。

A.边沿D触发器B.主从RS触发器C.同步RS触发器D.主从JK触发器正确答案:A2.下面代码中哪些是无权码()。

A.8421BCD码B.5421BCD码C.余三码D.格雷码正确答案:C3.在下列逻辑电路中,不是组合逻辑电路的有( )。

A.译码器B.编码器C.全加器D.寄存器正确答案:C4.在()的情况下,函数Y=AB运算的结果是逻辑“0”A.全部输入是“0”B.任一输入是“0”C.任一输入是“1”D.全部输入是“1”正确答案:A5.在()的情况下,异或运算的结果是逻辑“0”。

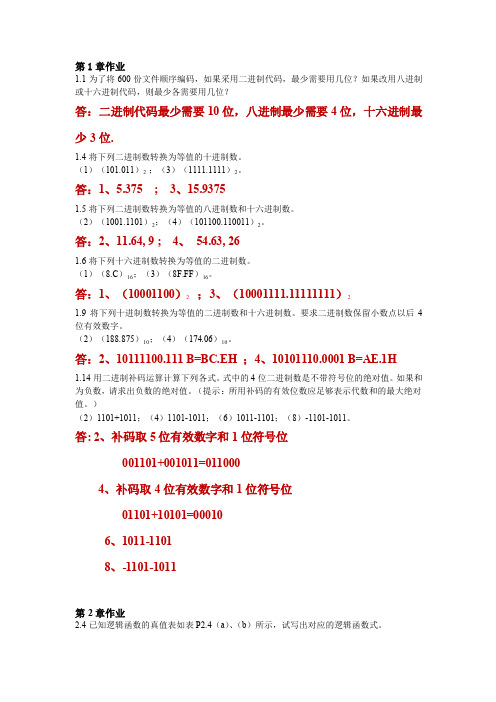

“数字电子技术”作业及答案

第1章作业1.1为了将600份文件顺序编码,如果采用二进制代码,最少需要用几位?如果改用八进制或十六进制代码,则最少各需要用几位?答:二进制代码最少需要10位,八进制最少需要4位,十六进制最少3位.1.4将下列二进制数转换为等值的十进制数。

(1)(101.011)2 ;(3)(1111.1111)2。

答:1、5.375 ; 3、15.93751.5将下列二进制数转换为等值的八进制数和十六进制数。

(2)(1001.1101)2;(4)(101100.110011)2。

答:2、11.64, 9 ; 4、54.63, 261.6将下列十六进制数转换为等值的二进制数。

(1)(8.C)16;(3)(8F.FF)16。

答:1、(10001100)2 ;3、(10001111.11111111)21.9将下列十进制数转换为等值的二进制数和十六进制数。

要求二进制数保留小数点以后4位有效数字。

(2)(188.875)10;(4)(174.06)10。

答:2、10111100.111 B=BC.EH ;4、10101110.0001 B=AE.1H1.14用二进制补码运算计算下列各式。

式中的4位二进制数是不带符号位的绝对值。

如果和为负数,请求出负数的绝对值。

(提示:所用补码的有效位数应足够表示代数和的最大绝对值。

)(2)1101+1011;(4)1101-1011;(6)1011-1101;(8)-1101-1011。

答: 2、补码取5位有效数字和1位符号位001101+001011=0110004、补码取4位有效数字和1位符号位01101+10101=000106、1011-11018、-1101-1011第2章作业2.4已知逻辑函数的真值表如表P2.4(a)、(b)所示,试写出对应的逻辑函数式。

表P2.4(a ) 表P2.4(b )2.7写出图P2.7(a )、(b )所示电路的输出逻辑函数式。

图P2.72.8已知逻辑函数Y 的波形图如图P2.8所示,试求Y 的真值表和逻辑函数式。

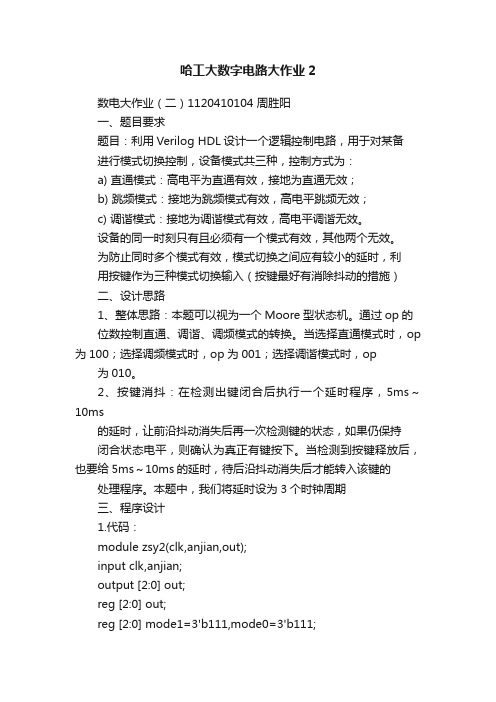

哈工大数字电路大作业2

哈工大数字电路大作业2数电大作业(二)1120410104 周胜阳一、题目要求题目:利用Verilog HDL设计一个逻辑控制电路,用于对某备进行模式切换控制,设备模式共三种,控制方式为:a) 直通模式:高电平为直通有效,接地为直通无效;b) 跳频模式:接地为跳频模式有效,高电平跳频无效;c) 调谐模式:接地为调谐模式有效,高电平调谐无效。

设备的同一时刻只有且必须有一个模式有效,其他两个无效。

为防止同时多个模式有效,模式切换之间应有较小的延时,利用按键作为三种模式切换输入(按键最好有消除抖动的措施)二、设计思路1、整体思路:本题可以视为一个Moore型状态机。

通过op的位数控制直通、调谐、调频模式的转换。

当选择直通模式时,op 为100;选择调频模式时,op为001;选择调谐模式时,op 为010。

2、按键消抖:在检测出键闭合后执行一个延时程序,5ms~10ms的延时,让前沿抖动消失后再一次检测键的状态,如果仍保持闭合状态电平,则确认为真正有键按下。

当检测到按键释放后,也要给5ms~10ms的延时,待后沿抖动消失后才能转入该键的处理程序。

本题中,我们将延时设为3个时钟周期三、程序设计1.代码:module zsy2(clk,anjian,out);input clk,anjian;output [2:0] out;reg [2:0] out;reg [2:0] mode1=3'b111,mode0=3'b111;wire anjian_done; //按键触发parameter D=3'b010,Z=3'b100,T=3'b001,; //定义了三个模式Z为直通,T为跳频,D为调谐reg shake1,shake2,shake3; //定义消抖用的三个变量always@(posedge clk) //上升沿触发beginshake1<=anjian;shake2<=shake1;shake3<=shake2;mode1=mode0; //这个模块用于消抖,程序来源于百度out=mode1;endassign anjian_done = (shake1 | shake2 | shake3);always@(anjian_done)begin //下面的部分就是一个状态机,和作业1一样。

数电 第二章习题答案

第二章2.1解:Vv v V V v T I m A I m A V v T V v a o B o B BS B o B 10T 3.0~0(2.017.0230103.0207.101.57.05I V 5v 1021.5201.510V 0v )(i i ≈≈∴<=⨯≈=-≈∴-=⨯+-=截止,负值,悬空时,都行)饱和-=时,=当截止时,=当都行)=饱和,,-=悬空时,都行)饱和。

-=时,=当=截止为负值时,=当V V v I m A I m A V V v T I m A I m A Vv T v b o B BS B o B BS B o B 3.0~0(2.0T 05.008.0187.87.47.05I 3.0~0(2.005.0250542.0187.87547.05I V 5v 5V 0v )(i i ∴<==-≈∴<=⨯≈=-∴2.3解:s 闭合时,输入低电平,此时ΩΩ=='≤≤'⨯=20020024.054.04.05222的最大允许值为R mA V I R V I R V IL IL ILs 断开时,输入为高电平,此时212121R K 10101.015445)(-最大允许值为R K mAV I V V R R VI R R V V IH cc IH cc IH ∴Ω==-≤+≥⨯+-=2.4解:2002.04.0I (max)I N 204.08I (max)I N OH OL ====IH M IL M G G =系数输出为高电平时,扇出=系数输出为低电平时,扇出所以,N =202.5解:为输入端的个数)分母中的=系数输出为高电平时,扇出=系数输出为低电平时,扇出2(504.024.02I (max)I N 106.116I (max)I N OH OL =⨯===IH M IL M G G 所以,N =52.6解:由于TTL 型或非门输入结构不同,每个输入端都有一个三极管个相同的或非门最多能驱动==高低5504.024.02I (max)I N 56.12162I (max)I N OH OL ∴=⨯==⨯=IH IL2.7解:根据公式:KR K K I m I V V R K mI nI V V R L IL LM OL cc L IH OH OH cc L 568.068.04.0384.05502.031.032.35(min)(max)<<∴≈⨯--='--==⨯+⨯-=+-=2.8解:K R I R R V V R V V V LM BE OL cc IH I 1.11.00I T 1321B ≥⇒≤+---=同时要满足=必须满足截止条件:时,当 K R K KR I I I R I V V R V V I I I I I m A R m A R V V BS BE OH OH cc OH B c cc I 46.41.146.443.087.0I 1I ,I I T V 0113222113133BS BS B ≤≤∴≤⇒⎪⎪⎪⎭⎪⎪⎪⎬⎫+=+=---==+=≈≥===,必须满足饱和条件:时,当β2.9解:KR K mA I I mA I R V I I I mA I mAI B c BS L c cc L R c L LM c 1.333.008.083.074.1516)1(≤≤==⇒=+-=+=⇒=⨯==可解得:同上题解法:β(2)把OC 门换成TTL 门时,若门输出为低电平时两者相同,无影响;但输出高电平时两者截然不同,OC 门向内流进(漏电流),而TTL 的电流是向外流出,I B =I RB +I OH ,I OH 为TTL 输出高电平时的输出电流。