ADT7490ARQZ-R7中文资料

SST-ST45SF 450W 切换电源文档说明书

(10% TO 95% OF FINAL OUTPUT VALUE, @FULL LOAD)

115V-rms or 230V-rms

+ 3.3Vdc : 20ms Maximum + 5Vdc : 20ms Maximum + 12Vdc : 20ms Maximum + 5Vsb : 20ms Maximum - 12Vdc : 20ms Maximum

The specification below is intended to describe as detailedly as possible the functions and performance of the subject power supply. Any comment or additional requirements to this specification from our customers will be highly appreciated and treated as a new target for us to approach.

4.5. OVER VOLTAGE PROTECTION

Voltage Source +3.3V +5V +12V

Protection Point 3.76V-4.8V 5.6V-7.0V 13.0V-16.5V

4.6. OVER-CURRENT PROTECTION

OUTPUT VOLTAGE +3.3V +5V +12V1

Max. over current limit 60A 48A 45A

04

4.7. SHORT CIRCUIT PROTECTION

AAT 器件选型指南.pdf说明书

Part No.

Amplifiers Include

Vcc (V)

Icc

Ptot

(mA) (mW)

Toper Vio Iio (℃) (mV) (nA)

PKG

Replace Brand

LM358 LM393 LM324 LM339

2

16~32 50

500

0~70

2

2

SOP-8/DIP-8

2

2~36 0.4

128*8 256*8 512*8 1028*8 2056*8 5012*8 10024*8

Frequency Icc

Isb

(KHz)

(mA) (µA)

PKG

Replace Brand

Application

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

400

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

400

0.4~3 0.6~18 SOP-8/DIP-8 ATMEL/ISSI/ST/ROHM

■ AAT General Line-up

I2-PAK

TO-220AB

TO-220IS

AAT PRODUCTS FOR CUSTOMERS

General Freque

Vcc

Device

ncy

Name

(KHz)

(V)

Vout (V)

Io (A)

7805

---

5~18

AD7747ARUZ资料

24-Bit Capacitance-to-Digital Converterwith Temperature SensorAD7747Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.FEATURESCapacitance-to-digital converterNew standard in single chip solutionsInterfaces to single or differential grounded sensors Resolution down to 20 aF (that is, up to 19.5-bit ENOB) Accuracy: 10 fF Linearity: 0.01%Common-mode (not changing) capacitance up to 17 pF Full-scale (changing) capacitance range ±8 pF Update rate: 5 Hz to 45 HzSimultaneous 50 Hz and 60 Hz rejection at 8.1 Hz update Active shield for shielding sensor connection Temperature sensor on-chipResolution: 0.1°C, accuracy: ±2°C Voltage input channel Internal clock oscillator2-wire serial interface (I 2C® compatible) Power2.7 V to 5.25 V single-supply operation 0.7 mA current consumptionOperating temperature: −40°C to +125°C 16-lead TSSOP packageAPPLICATIONSAutomotive, industrial, and medical systems for Pressure measurement Position sensing Proximity sensing Level sensing Flow metering Impurity detectionGENERAL DESCRIPTIONThe AD7747 is a high-resolution, Σ-Δ capacitance-to-digital converter (CDC). The capacitance to be measured is connected directly to the device inputs. The architecture features inherent high resolution (24-bit no missing codes, up to 19.5-bit effective resolution), high linearity (±0.01%), and high accuracy (±10 fF factory calibrated). The AD7747 capacitance input range is ±8 pF (changing), and it can accept up to 17 pF common-mode capacitance (not changing), which can be balanced by a program-mable on-chip digital-to-capacitance converter (CAPDAC). The AD7747 is designed for single-ended or differential capacitive sensors with one plate connected to ground. For floating (not grounded) capacitive sensors, the AD7745 or AD7746 are recommended.The part has an on-chip temperature sensor with a resolution of 0.1°C and accuracy of ±2°C. The on-chip voltage reference and the on-chip clock generator eliminate the need for any external components in capacitive sensor applications. The part has a standard voltage input that, together with the differential reference input, allows easy interface to an external temperature sensor, such as an RTD, thermistor, or diode.The AD7747 has a 2-wire, I 2C-compatible serial interface. The part can operate with a single power supply of 2.7 V to 5.25 V . It is specified over the automotive temperature range of −40°C to +125°C and is housed in a 16-lead TSSOP package.FUNCTIONAL BLOCK DIAGRAMVDDCIN1(+)SDA SCLRDYCIN1(–)05469-001Figure 1.AD7747Rev. 0 | Page 2 of 28TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 General Description.........................................................................1 Functional Block Diagram..............................................................1 Revision History...............................................................................2 Specifications.....................................................................................3 Timing Specifications..................................................................5 Absolute Maximum Ratings............................................................6 ESD Caution..................................................................................6 Pin Configuration and Function Descriptions.............................7 Typical Performance Characteristics.............................................8 Output Noise and Resolution Specifications..............................11 Serial Interface................................................................................12 Read Operation...........................................................................12 Write Operation..........................................................................12 AD7747 Reset..............................................................................13 General Call.................................................................................13 Register Descriptions.....................................................................14 Status Register.............................................................................15 Cap Data Register.......................................................................15 VT Data Register........................................................................15 Cap Setup Register.....................................................................16 VT Setup Register.......................................................................16 EXC Setup Register....................................................................17 Configuration Register..............................................................18 Cap DAC A Register..................................................................19 Cap DAC B Register...................................................................19 Cap Offset Calibration Register...............................................20 Cap Gain Calibration Register..................................................20 Volt Gain Calibration Register.................................................20 Circuit Description.........................................................................21 Overview.....................................................................................21 Capacitance-to-Digital Converter............................................21 Active AC Shield Concept.........................................................21 CAPDAC.....................................................................................21 Single-Ended Capacitive Configuration.................................22 Differential Capacitive Configuration.....................................22 Parasitic Capacitance.................................................................23 Parasitic Resistance....................................................................23 Parasitic Serial Resistance.........................................................23 Capacitive Gain Calibration.....................................................23 Capacitive System Offset Calibration......................................24 Internal Temperature Sensor....................................................24 External Temperature Sensor...................................................24 Voltage Input...............................................................................25 V DD Monitor................................................................................25 Typical Application Diagram....................................................26 Outline Dimensions.......................................................................27 Ordering Guide.. (27)REVISION HISTORY1/07—Revision 0: Initial VersionAD7747Rev. 0 | Page 3 of 28SPECIFICATIONSV DD = 2.7 V to 3.6 V or 4.75 V to 5.25 V; GND = 0 V; EXC = ±V DD × 3/8; −40°C to +125°C, unless otherwise noted. Table 1.Parameter Min Typ Max Unit Test Conditions/Comments CAPAC I T I VE I NPUT Conversion Input Range ±8.192 pF 1 Factory calibrated Integral Nonlinearity (INL)2 ±0.01 % of FSR 1No Missing Codes 224 Bit Conversion time ≥ 124 ms Resolution, p-p 16.5 Bit Conversion time 124 ms, see Table 5 Resolution Effective 19.1 Bit Conversion time 124 ms, see Table 5 Output Noise, rms 11.0 aF/√Hz Conversion time 124 ms, see Table 5 Absolute Error 3 ±10 fF 1 25°C, V DD = 5 V, after offset calibrationOffset Error 4, 5 32 aF 1After system offset calibration,excluding effect of noise 4System Offset Calibration Range 5 ±1 pFOffset Deviation over Temperature 20.4 fF See Figure 6Gain Error 6 0.02 0.11 % of FS 125°C, V DD = 5 V Gain Drift vs. Temperature 2 −23 −26 −29 ppm of FS/°CPower Supply Rejection 20.5 4 fF/V Normal Mode Rejection 5 72 dB 50 Hz ± 1%, conversion time 124 ms 60 dB 60 Hz ± 1%, conversion time 124 ms CAPDAC Full Range 17 21 pF 6-bit CAPDAC Differential Nonlinearity (DNL) 0.3 LSB See Figure 16 Drift vs. Temperature 2 26 ppm of FS/°CEXCITATIONFrequency 16 kHzAC Voltage Across Capacitance ±V DD × 3/8 V To be configured via digital interface Average DC Voltage Across Capacitance V DD /2 V TEMPERATURE SENSOR 7 V REF internal Resolution 0.1 °CError 2±0.5 ±2 °C Internal temperature sensor ±2 °C External sensing diode 8 VOLTAGE INPUT 7 V REF internal or V REF = 2.5 V Differential VIN Voltage Range ±V REF V Absolute VIN Voltage 2 GND − 0.03 V DD + 0.03 V Integral Nonlinearity (INL) ±3 ±15 ppm of FS No Missing Codes 2 24 Bit Conversion time = 122.1 ms Resolution, p-p 16 Bits Conversion time = 62 ms,see Table 6 and Table 7Output Noise 3 μV rms Conversion time = 62 ms,see Table 6 and Table 7Offset Error ±3 μV Offset Drift vs. Temperature 15 nV/°CFull-Scale Error 2, 90.025 0.1 % of FS Full-Scale Drift vs. Temperature 5 ppm of FS/°C Internal reference 0.5 ppm of FS/°C External reference Average VIN Input Current 300 nA/V Analog VIN Input Current Drift ±50 pA/V/°C Power Supply Rejection 80 dB Internal reference, V IN = V REF /2 90 dB External reference, V IN = V REF /2AD77471 Capacitance units: 1 pF = 10−12 F; 1 fF = 10−15 F; 1 aF = 10−18 F. Full scale (FS) = 8.192 pF; full-scale range (FSR) = ±8.192 pF.2 Specification is not production tested, but is supported by characterization data at initial product release.3 Factory calibrated. The absolute error includes factory gain calibration error, integral nonlinearity error, and offset error after system offset calibration, all at 25°C.At different temperatures, compensation for gain drift over temperature is required.4 The capacitive input offset can be eliminated using a system offset calibration. The accuracy of the system offset calibration is limited by the offset calibration register LSB size (32 aF) or by converter + system p-p noise during the system capacitive offset calibration, whichever is greater. To minimize the effect of the converter + system noise, longer conversion times should be used for system capacitive offset calibration. The system capacitance offset calibration range is ±1 pF; the larger offset can be removed using CAPDACs.5 Specification is not production tested, but guaranteed by design.6 The gain error is factory calibrated at 25°C. At different temperatures, compensation for gain drift over temperature is required.7 The VTCHOP bit in the VT SETUP register must be set to 1 for the specified temperature sensor and voltage input performance.8 Using an external temperature sensing diode 2N3906, with nonideality factor n f = 1.008, connected as in Figure 37, with total serial resistance <100 Ω.9 Full-scale error applies to both positive and negative full scale.Rev. 0 | Page 4 of 28AD7747Rev. 0 | Page 5 of 28TIMING SPECIFICATIONSV DD = 2.7 V to 3.6 V , or 4.75 V to 5.25 V; GND = 0 V; Input Logic 0 = 0 V; Input Logic 1 = V DD ; −40°C to +125°C, unless otherwise noted. Table 2.Parameter Min Typ Max Unit Test Conditions/Comments SERIAL INTERFACE 1, 2 See Figure 2 SCL Frequency 0 400 kHz SCL High Pulse Width, t HIGH 0.6 μs SCL Low Pulse Width, t LOW 1.3 μs SCL, SDA Rise Time, t R 0.3 μs SCL, SDA Fall Time, t F 0.3 μs Hold Time (Start Condition), t HD;STA 0.6 μs After this period, the first clock is generated Setup Time (Start Condition), t SU;STA 0.6 μs Relevant for repeated start condition Data Setup Time, t SU;DAT0.1 μs Setup Time (Stop Condition), t SU;STO 0.6 μs Data Hold Time, t HD;DAT (Master) 0 μs Bus-Free Time (Between Stop and Start Condition, t BUF ) 1.3 μs1 Sample tested during initial release to ensure compliance.2All input signals are specified with input rise/fall times = 3 ns, measured between the 10% and 90% points. Timing reference points at 50% for inputs and outputs. Output load = 10 pF.Figure 2. Serial Interface Timing DiagramAD7747Rev. 0 | Page 6 of 28ABSOLUTE MAXIMUM RATINGST A = 25°C, unless otherwise noted. Table 3.Parameter RatingPositive Supply Voltage V DD to GND −0.3 V to +6.5 VVoltage on any Input or Output Pin to GND−0.3 V to V DD + 0.3 V ESD Rating (ESD Association Human Body Model, S5.1)2000 VOperating Temperature Range −40°C to +125°CStorage Temperature Range −65°C to +150°CJunction Temperature 150°C TSSOP Package θJA(Thermal Impedance-to-Air)128°C/W TSSOP Package θJC(Thermal Impedance-to-Case) 14°C/W Peak Reflow Soldering Temperature Pb Free (20 sec to 40 sec) 260°C Stresses above those listed under Absolute Maximum Ratingsmay cause permanent damage to the device. This is a stressrating only and functional operation of the device at these orany other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolutemaximum rating conditions for extended periods may affect device reliability. ESD CAUTIONAD7747Rev. 0 | Page 7 of 28PIN CONFIGURATION AND FUNCTION DESCRIPTIONS05469-003SDA NC VDDGNDVIN(–)VIN(+)NCNCNC = NO CONNECTFigure 3. Pin ConfigurationIAD7747Rev. 0 | Page 8 of 28TYPICAL PERFORMANCE CHARACTERISTICS80–80–8–7–6–5–4–3–1–2805469-004INPUT CAPACITANCE (pF)I N L (p pm )6040200–20–40–6001234567 Figure 4. Capacitance Input Integral Nonlinearity;V DD = 5 V, CAPDAC = 0x3F2000–3000–5015005469-005TEMPERATURE (ºC)G A I N E R R O R (p p m )10000–1000–2000–250255075100125 Figure 5. Capacitance Input Gain Drift vs. Temperature;V DD = 5 V, CIN(+) to GND = 8 pF.20–0.30–5015005469-006TEMPERATURE (ºC)O F F S E T E R R O R (f F )–250255075100125.15.10.050–0.05–0.10–0.15–0.20–0.25Figure 6. Capacitance Input Offset Drift vs. Temperature;V DD = 5 V, CIN(+) Open 10–5060050005469-007CAPACITANCE SHLD TO GND (pF)C A P E R R O R (f F )–20–10–30–4050100150200250300350400450550Figure 7. Capacitance Input Error vs. Capacitance Between SHLD and GND;CIN(+) to GND = 8 pF, V DD = 2.7 V, 3 V, 3.3 V, and 5 V10–5060050005469-008CAPACITANCE SHLD TO GND (pF)C A P E R R O R (f F )–20–10–30–4050100150200250300350400450550Figure 8. Capacitance Input Error vs. Capacitance Between SHLD and GND;CIN(+) to GND = 25 pF, V DD = 2.7 V, 3 V, 3.3 V, and 5 V10–5060050005469-009CAPACITANCE CIN TO SHLD (pF)C A P E R R O R (f F )–20–10–30–4050100150200250300350400450550Figure 9. Capacitance Input Error vs. Capacitance Between CIN(+) and SHLD;CIN(+) to GND = 8 pF, V DD = 2.7 V, 3 V, 3.3 V, and 5VAD7747Rev. 0 | Page 9 of 28150–15001k 05469-010PARALLEL RESISTANCE (M Ω)C A P E R R O R (f F )1010010050–50–100Figure 10. Capacitance Input Error vs. Parallel Resistance;CIN(+) to GND = 8 pF, V DD = 5 V0–100020005469-058CIN TO SHLD RESISTANCE (k Ω)C A P E R R O R (f F )–100–200–300–400–500–600–700–800–900255075100125150175Figure 11. Capacitance Input Error vs. Resistance Between CIN1(+) and SHLD;CIN(+) to GND = 8 pF, V DD = 5 V100–10000.09105469-059CIN TO SHLD RESISTANCE (M Ω)C A P E R R O R (f F )–1000–200–300–400–500–600–700–800–9000.270.480.96525100Figure 12. Capacitance Input Error vs. Resistance Between CIN(+) and SHLD;CIN(+) to GND = 25 pF, V DD = 5 V 1.0–1.00.0110005469-066SHLD TO GND RESISTANCE (M Ω)C A P E R R O R (p F )0.11.010.00.80.60.40.20–0.2–0.4–0.6–0.8Figure 13. Capacitance Input Error vs. Resistance Between SHLD and GND;CIN(+) to GND = 8 pF; V DD = 5 V10–100110005469-067SERIAL RESISTANCE (k Ω)C A P E R R O R (f F )100–10–20–30–40–50–60–70–80–90Figure 14. Capacitance Input Error vs. Serial Resistance;CIN(+) to GND = 8 pF and 25pF, V DD = 5 V0.2–0.62.55.505469-062VDD (V)C A P E R R O R (f F)–0.2–0.43.0 3.54.0 4.55.0Figure 15. Capacitance Input Power Supply Rejection (PSR);CIN(+) to GND = 8 pFAD7747Rev. 0 | Page 10 of 28200–20006405469-050CAPDAC CODEC A PD A C D N L (fF )150100500–50–100–1508162432404856Figure 16. CAPDAC Differential Nonlinearity (DNL)2.0–2.0–5015005469-034TEMPERATURE (°C)E R R O R (°C )1.51.00.50–0.5–1.0–1.5–250255075100125Figure 17. Internal Temperature Sensor Error vs. Temperature1.0–3.0–5015005469-035TEMPERATURE (°C)E R R O R (°C )0.50–0.5–1.0–1.5–2.0–2.5–250255075100125Figure 18. External Temperature Sensor Error vs. Temperature–12001k05469-051INPUT SIGNAL FREQUENCY (Hz)G A I N (d B )–20–40–60–80–100100200300400500600700800900Figure 19. Capacitive Channel Frequency Response;Conversion Time = 22 ms–120020005469-052INPUT SIGNAL FREQUENCY (Hz)G A I N (d B)–20–40–60–80–100255075100125150175Figure 20. Capacitive Channel Frequency Response;Conversion Time = 124 ms–120040005469-039INPUT SIGNAL FREQUENCY (Hz)G A I N (d B )–20–40–60–80–10050100150200250300350Figure 21. Voltage Channel Frequency Response;Conversion Time = 122.1 msOUTPUT NOISE AND RESOLUTION SPECIFICATIONSThe AD7747 resolution is limited by noise. The noise performance varies with the selected conversion time.Table 5 shows typical noise performance and resolution for the capacitive channel. These numbers were generated from 1000 data samples acquired in continuous conversion mode, at an excitation of 16 kHz, ±V DD × 3/8, and with all CIN and SHLD pins connected only to the evaluation board (no external capacitors). Table 6 and Table 7 show typical noise performance and resolution for the voltage channel. These numbers were generated from 1000 data samples acquired in continuous conversion mode with VIN pins shorted to ground.RMS noise represents the standard deviation and p-p noise represents the difference between minimum and maximum results in the data. Effective resolution is calculated from rms noise, and p-p resolution is calculated from p-p noise.Table 5. Typical Capacitive Input Noise and Resolution vs. Conversion Time (Bold line represents default setting)Conversion Time (ms) Output DataRate (Hz)−3 dB Frequency(Hz)RMS Noise(aF/√Hz)RMSNoise(aF)P-PNoise(aF)Effective Resolution(Bits)P-P Resolution(Bits)22.0 45.5 43.6 28.8 190 821 16.4 14.323.9 41.9 39.5 23.2 146 725 16.8 14.5 40.0 25.0 21.8 11.1 52 411 18.3 15.3 76.0 13.2 10.9 11.2 37 262 18.7 15.9 124.0 8.1 6.9 11.0 29 174 19.1 16.5 154.0 6.5 5.3 10.4 24 173 19.3 16.5 184.0 5.4 4.4 10.0 21 141 19.6 16.8 219.3 4.6 4.0 9.0 18 126 19.9 17.0Table 6. Typical Voltage Input Noise and Resolution vs. Conversion Time, Internal Voltage ReferenceConversion Time (ms) Output DataRate (Hz)−3 dB Frequency(Hz)RMS Noise(μV)P-P Noise(μV)Effective Resolution(Bits)P-P Resolution(Bits)20.1 49.8 26.4 11.4 62 17.6 15.2 32.1 31.2 15.9 7.1 42 18.3 15.7 62.1 16.1 8.0 4.0 28 19.1 16.3 122.1 8.2 4.0 3.0 20 19.5 16.8Table 7. Typical Voltage Input Noise and Resolution vs. Conversion Time, External 2.5 V Voltage ReferenceConversion Time (ms) Output DataRate (Hz)−3 dB Frequency(Hz)RMS Noise(μV)P-P Noise(μV)Effective Resolution(Bits)P-P Resolution(Bits)20.1 49.8 26.4 14.9 95 18.3 15.6 32.1 31.2 15.9 6.3 42 19.6 16.8 62.1 16.1 8.0 3.3 22 20.5 17.7 122.1 8.2 4.0 2.1 15 21.1 18.3SERIAL INTERFACEThe AD7747 supports an I2C-compatible 2-wire serial interface. The two wires on the I2C bus are called SCL (clock) and SDA (data). These two wires carry all addressing, control, and data information one bit at a time over the bus to all connected peripheral devices. The SDA wire carries the data, while the SCL wire synchronizes the sender and receiver during the data transfer. I2C devices are classified as either master or slave devices.A device that initiates a data transfer message is called a master, while a device that responds to this message is called a slave. To control the AD7747 device on the bus, the following protocol must be followed. First, the master initiates a data transfer by establishing a start condition, defined by a high-to-low transition on SDA while SCL remains high. This indicates that the start byte follows. This 8-bit start byte is made up of a 7-bit address plus an R/W bit indicator.All peripherals connected to the bus respond to the start condition and shift in the next 8 bits (7-bit address + R/W bit). The bits arrive MSB first. The peripheral that recognizes the transmitted address responds by pulling the data line low during the ninth clock pulse. This is known as the acknowledge bit. All other devices withdraw from the bus at this point and maintain an idle condition. An exception to this is the general call address, which is described later in this document. The idle condition is where the device monitors the SDA and SCL lines waiting for the start condition and the correct address byte. The R/W bit determines the direction of the data transfer. A Logic 0 LSB in the start byte means that the master writes information to the addressed peripheral. In this case, the AD7747 becomes a slave receiver. A Logic 1 LSB in the start byte means that the master reads information from the addressed peripheral. In this case, the AD7747 becomes a slave transmitter. In all instances, the AD7747 acts as a standard slave device on the I2C bus.The start byte address for the AD7747 is 0x90 for a write and0x91 for a read.READ OPERATIONWhen a read is selected in the start byte, the register that is currently addressed by the address pointer is transmitted on to the SDA line by the AD7747. This is then clocked out by the master device and the AD7747 awaits an acknowledge from the master.If an acknowledge is received from the master, the address auto-incrementer automatically increments the address pointer register and outputs the next addressed register content on to the SDA line for transmission to the master. If no acknowledge is received, the AD7747 returns to the idle state and the address pointer is not incremented.The address pointer’s auto-incrementer allows block data to be written or read from the starting address and subsequent incremental addresses. In continuous conversion mode, the address pointer’s auto-incrementer should be used for reading a conversion result. That means the three data bytes should be read using one multibyte read transaction rather than three separate single byte transactions. The single byte data read transaction may result in the data bytes from two different results being mixed. The same applies for six data bytes if both the capacitive and thevoltage/temperature channel are enabled.The user can also access any unique register (address) on a one-to-one basis without having to update all the registers. The address pointer register’s contents cannot be read.If an incorrect address pointer location is accessed, or if the user allows the auto-incrementer to exceed the required register address, the following applies:•In read mode, the AD7747 continues to output various internal register contents until the master device issues ano acknowledge, start, or stop condition. The addresspointer auto-incrementer’s contents are reset to point tothe status register at Address 0x00 when a stop condition is received at the end of a read operation. This allows thestatus register to be read (polled) continually withouthaving to constantly write to the address pointer.•In write mode, the data for the invalid address is not loaded into the AD7747 registers, but an acknowledge isissued by the AD7747.WRITE OPERATIONWhen a write is selected, the byte following the start byte is always the register address pointer (subaddress) byte, which points to one of the internal registers on the AD7747. The address pointer byte is automatically loaded into the address pointer register and acknowledged by the AD7747. After the address pointer byte acknowledge, a stop condition, a repeated start condition, or another data byte can follow from the master.A stop condition is defined by a low-to-high transition on SDA while SCL remains high. If a stop condition is ever encountered by the AD7747, it returns to its idle condition and the address pointer is reset to Address 0x00.If a data byte is transmitted after the register address pointer byte, the AD7747 loads this byte into the register that is currently addressed by the address pointer register, sends an acknowledge, and the address pointer auto-incrementer automatically increments the address pointer register to the next internal register address. Thus, subsequent transmitted data bytes are loaded into sequentially incremented addresses. If a repeated start condition is encountered after the address pointer byte, all peripherals connected to the bus respond exactly as outlined above for a start condition, that is, a repeated start condition is treated the same as a start condition. When a master device issues a stop condition, it relinquishes control ofthe bus, allowing another master device to take control of the bus. Therefore, a master wanting to retain control of the bus issues successive start conditions known as repeated start conditions.AD7747 RESETTo reset the AD7747 without having to reset the entire I 2C bus, an explicit reset command is provided. This uses a particular address pointer word as a command word to reset the part and upload all default settings. The AD7747 does not respond to the I 2C bus commands (do not acknowledge) during the default values upload for approximately 150 μs (max 200 μs). The reset command address word is 0xBF. GENERAL CALLWhen a master issues a slave address consisting of seven 0s with the eighth bit (R/W bit) set to 0, this is known as the general call address. The general call address is for addressing every device connected to the I 2C bus. The AD7747 acknowledges this address and read in the following data byte.If the second byte is 0x06, the AD7747 is reset, completely uploading all default values. The AD7747 does not respond to the I 2C bus commands (do not acknowledge) during the default values upload for approximately 150 μs (200 μs maximum). The AD7747 does not acknowledge any other general call commands.P 981–7981–798S SDATASCLOCKSTART ADDR ACK ACKDATAACKSTOPSUBADDRESS 1–705469-011Figure 22. Bus Data TransferWRITE SEQUENCEREAD SEQUENCE05469-012Figure 23. Write and Read Sequences。

ATA系列自动电源转换装置产品介绍说明书

ATA系列自动电源转换装置出众的整体解决方案 ATA—执行机构IZM9系列ATA 系列自动电源转换装置ATA 系列自动电源转换装置ATA 系列概述 ...................................................................................4型号说明 ...............................................................................5主要技术数据及性能指标 .................................................................6控制器 .................................................................................7电气线缆 ..............................................................................16执行断路器IZM9系列型号说明 ..............................................................................17脱扣器技术参数 ........................................................................18系统概览 ..............................................................................19可选附件 ..............................................................................23外形及安装尺寸 ........................................................................24系统电气图 ............................................................................48选型与订货 ............................................................................69订购指南 (73)ATA 系列执行断路器IZM9系列目录3ATA系列自动电源转换装置概述ATA系列产品描述伊顿的ATA系列自动转换开关装置,满足额定电压AC400V以下电源的自动转换。

25AA640中文资料

I/O Control Logic

Memory

X

Control

Logic

Dec

EEPROM Array

Page Latches

SI SO

CS SCK HOLD WP

VCC VSS

Y Decoder

Sense Amp. R/W Control

*25xx640 is used in this document as a generic part number for the 25AA640/25LC640/25C640 devices. SPI is a trademark of Motorola.

Input

0.5 VCC

Output

0.5 VCC

Note 1: For VCC ≤ 4.0V

2: For VCC > 4.0V

TABLE 1-2: DC CHARACTERISTICS

All parameters apply over the Commercial (C): Tamb = 0°C to +70°C

*Notice: Stresses above those listed under ‘Maximum ratings’ may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for an extended period of time may affect device reliability

JUPITER系列合成器:Roland JUPITER-80和JUPITER-50的产品介绍说明书

n Four types of LPFs with unique behavior

The JUPITER-80 and -50 feature four types of LPFs. Each filter behaves differently, even if their cutoff and resonance parameters are the same. The LPF is personalized by its parameter settings and real-time control cutoff frequency and resonance.

Seven types of analog waveforms provide the DNA of vintage synthesizers.

SAW

SQUARE

PULSE/PWM

JUPITER-4

1978 — Roland's first polyphonic analog synthesizer (4 voices). The 4VCO sound in unison mode is superb, and it also has a user patch-memory function built in.

SuperNATURAL sound — ultimate expression and authenticity

Enhanced SuperNATURAL Synthesizer Tones

Authentic synth sounds — from classic vintage analog to modern digital

JUPITER-6

1983 — Scaling down the JUPITER‑8 to 6‑voice polyphony, coupled with creative tweaking by Roland's engineers, allowed the JUPITER‑6 to hit the market at half the price of its big brother. It also made news with its MIDI terminal and highly stable oscillator.

AMS——精选推荐

AMS航空材料规范AMS 5659k耐腐蚀钢材,棒料,线材,锻件,环状件,热压件,15Cr-4.5Ni-0.30Cb-3.5Cu可消耗电极熔炼,固溶热处理,沉淀硬化1.范围:1.1 形式:本规范包括耐腐蚀钢棒料、线材、锻件、闪光对焊环状件、热压件和锻件、闪光对焊环状件、冲模的原材料。

1.2应⽤:这些产品主要⽤于抗腐蚀,在316℃以上具有⾼的强度,具有好的塑性并且在横截⾯积较⼤的零件上,横向具有⾼的强度。

1.2.1零件的设计和⼯艺可能导致零件容易产⽣应⼒腐蚀裂纹:ARP1110⾥的条款可以减少这些情况的发⽣。

1.3分类本规范中的零件可以按照以下⽅法来分类:1类-在重熔过程中在真空可消耗电极中多次熔炼的钢2类-在精炼过程中经多次电渣熔炼的钢1.3.1除⾮指定特殊的类型,可以采⽤以上中的任意⼀种。

2.参考⽂献以下出版物可以作为参考⽂献的⼀部分,可以采⽤SAE最近的出版物,其它的出版物在定单⽇起⽣效。

2.1SAE出版物可以从SAE,400Commonwealth Drive,Warrendale,PA 15096-0001获得。

AMS 2241 公差,耐热耐腐蚀钢,铁合⾦,钛,钛合⾦棒料和线材AMS 2241 公差,公制,耐热耐腐蚀钢,铁合⾦,钛,钛合⾦棒料和线材AMS 2248 化学检验分析要求,精炼耐热耐腐蚀钢和合⾦,马⽒体时效钢和其它⾼合⾦钢,铁合⾦AMS 2300 优质航空质量钢清洗,磁粉探伤检测程序AMS 2300优质航空质量钢清洗,磁粉探伤检测程序,公制(SI)计量AMS 2315 Delta 铁素体含量AMS 2371 质量保证取样和测试,耐热耐腐蚀钢和合⾦,精炼产品和锻坯AMS 2374 质量保证取样和测试,耐热耐腐蚀钢和合⾦,锻件AMS 2750 ⾼温测量技术AMS 2806 鉴别,棒料,线材,机械管材,热压件,碳钢和合⾦钢,耐热耐腐蚀钢和合⾦AMS 2808 鉴别,锻件AMS 7490 环状件,闪光焊接,耐热耐腐蚀奥⽒体钢和奥⽒体型铁、镍或钴合⾦或沉淀硬化合⾦ARP 1110 精炼钢件最低应⼒腐蚀开裂,耐热耐腐蚀钢和合⾦2.2ASTM出版物可以从ASTM,100Barr Harbor Drive,West Conshohocken,PA 19428-2959。

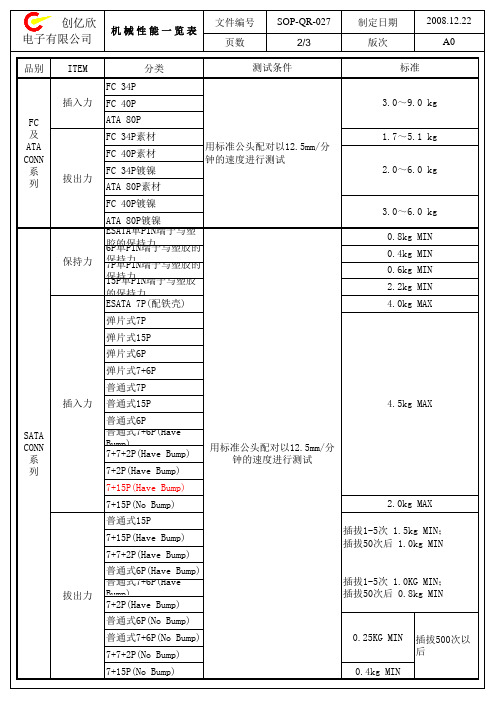

SOP-QR-027 CONNECTOR 机械性能一览表

插拔1-5次 1.0KG MIN; 插拔50次后 0.8kg MIN

普通式6P(No Bump)

普通式7+6P(No Bump) 7+7+2P(No Bump)

0.25KG MIN 插拔500次以 后

7+15P(No Bump)

0.4kg MIN

创亿欣电 子有限公司

机械性能一览表

文件编号 页数

SOP-QR-027 3/3

制定日期 版次

2008.12.22 A0

品别

SATA CONN 系 列

HDMI CONN 系 列

ITEM

分类 ESATA 7P(配铁壳)

普通式7P

测试条件

用标准公头配对以12.5mm/分 钟的速度进行测试

标准 1.0kg MIN(插拔2500次以后)

创亿欣 机 械 性 能 一 览 表 电子有限公司

文件编号 页数

SOP-QR-027 2/3

制定日期 版次

2008.12.22 A0

品别

FC 及 ATA CONN 系 列

SATA CONN 系 列

ITEM 插入力 拔出力 保持力

插入力

拔出力

分类

测试条件

标准

FC 34P

FC 40P

3.0~9.0 kg

ATA 80P

FC 34P素材 FC 40P素材 FC 34P镀镍

用标准公头配对以12.5mm/分 钟的速度进行测试

1.7~5.1 kg 2.0~6.0 kg

ATA 80P素材

FC 40P镀镍

ATA 80P镀镍 ESATA单PIN端子与塑 胶6P的单保PI持N端力子与塑胶的 保7P持单力PIN端子与塑胶的 保15持P单力PIN端子与塑胶 的保持力 ESATA 7P(配铁壳)

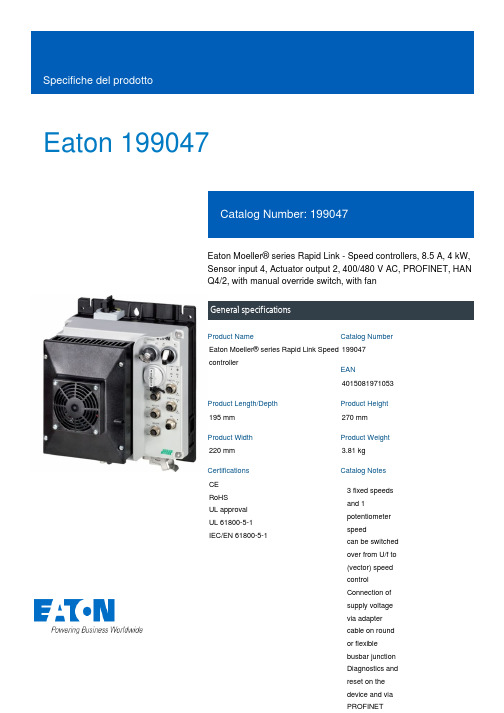

艾特顿199047产品说明说明书

Eaton 199047Eaton Moeller® series Rapid Link - Speed controllers, 8.5 A, 4 kW, Sensor input 4, Actuator output 2, 400/480 V AC, PROFINET, HAN Q4/2, with manual override switch, with fanGeneral specificationsEaton Moeller® series Rapid Link Speed controller1990474015081971053195 mm 270 mm 220 mm 3.81 kg CE RoHS UL approval UL 61800-5-1 IEC/EN 61800-5-1Product NameCatalog NumberEANProduct Length/Depth Product Height Product Width Product Weight Certifications Catalog Notes 3 fixed speeds and 1 potentiometer speedcan be switched over from U/f to (vector) speed control Connection of supply voltage via adapter cable on round or flexible busbar junction Diagnostics and reset on the device and via PROFINETInternal and on heat sink, temperature-controlled Fan Parameterization: KeypadParameterization: FieldbusParameterization: drivesConnect mobile (App) Parameterization: drivesConnectKey switch position HANDThermo-click with safe isolationControl unitInternal DC linkKey switch position OFF/RESET2 Actuator outputsFanManual override switchSelector switch (Positions: REV - OFF - FWD)PC connectionIGBT inverterPTC thermistor monitoringTwo sensor inputs through M12 sockets (max. 150 mA) for quick stop and interlocked manual operationKey switch position AUTO3 fixed speeds1 potentiometer speedFor actuation of motors with mechanical brake NEMA 12IP651st and 2nd environments (according to EN 61800-3)IIISpeed controllerPROFINET IOC2, C3: depending on the motor cable length, the connected load, and ambient conditions. External radio interference suppression filters (optional) may be necessary.C1: for conducted emissions only2000 VAC voltagePhase-earthed AC supply systems are not permitted.Center-point earthed star network (TN-S network)Vertical15 g, Mechanical, According to IEC/EN 60068-2-27, 11 ms, Half-sinusoidal shock 11 ms, 1000 shocks per shaftResistance: According to IEC/EN 60068-2-6Resistance: 6 Hz, Amplitude 0.15 mmResistance: 10 - 150 Hz, Oscillation frequencyResistance: 57 Hz, Amplitude transition frequency on accelerationFeatures Fitted with:Functions Degree of protectionElectromagnetic compatibility Overvoltage categoryProduct categoryProtocolRadio interference classRated impulse withstand voltage (Uimp) System configuration typeMounting positionShock resistanceVibrationAbove 1000 m with 1 % performance reduction per 100 m Max. 2000 m-10 °C40 °C-40 °C70 °CIn accordance with IEC/EN 50178< 95 %, no condensation Adjustable, motor, main circuit0.8 - 8.5 A, motor, main circuit< 10 ms, Off-delay< 10 ms, On-delay98 % (η)7.8 A3.5 mA120 %Maximum of one time every 60 seconds 380 V480 V380 - 480 V (-10 %/+10 %, at 50/60 Hz)BLDC motorsSensorless vector control (SLV)PM and LSPM motorsSynchronous reluctance motorsU/f control0 Hz500 HzFor 60 s every 600 sAt 40 °C12.7 AAltitudeAmbient operating temperature - min Ambient operating temperature - max Ambient storage temperature - min Ambient storage temperature - max Climatic proofing Current limitationDelay timeEfficiencyInput current ILN at 150% overload Leakage current at ground IPE - max Mains current distortionMains switch-on frequencyMains voltage - minMains voltage - maxMains voltage toleranceOperating modeOutput frequency - minOutput frequency - maxOverload currentOverload current IL at 150% overload45 Hz66 Hz4 kW480 V AC, 3-phase400 V AC, 3-phase0.1 Hz (Frequency resolution, setpoint value)200 %, IH, max. starting current (High Overload), For 2 seconds every 20 seconds, Power section50/60 Hz8 kHz, 4 - 32 kHz adjustable, fPWM, Power section, Main circuitAC voltagePhase-earthed AC supply systems are not permitted.Center-point earthed star network (TN-S network)5 HP≤ 0.6 A (max. 6 A for 120 ms), Actuator for external motor brakeAdjustable to 100 % (I/Ie), DC - Main circuit≤ 30 % (I/Ie)400/480 V AC -15 % / +10 %, Actuator for external motor brake10 kAType 1 coordination via the power bus' feeder unit, Main circuit400/480 V AC (external brake 50/60 Hz)24 V DC (-15 %/+20 %, external via AS-Interface® plug)PROFINET, optionalPlug type: HAN Q4/2Max. total power consumption from AS-Interface® power supply unit (30 V): 250 mASpecification: S-7.4 (AS-Interface®)Number of slave addresses: 31 (AS-Interface®)C1 ≤ 1 m, maximum motor cable length C3 ≤ 25 m, maximum motor cable length C2 ≤ 5 m, maximum motor cable lengthMeets the product standard's requirements.Rated frequency - minRated frequency - maxRated operational power at 380/400 V, 50 Hz, 3-phase Rated operational voltageResolutionStarting current - maxSupply frequencySwitching frequencySystem configuration type Assigned motor power at 460/480 V, 60 Hz, 3-phase Braking currentBraking torqueBraking voltageRated conditional short-circuit current (Iq)Short-circuit protection (external output circuits) Rated control voltage (Uc)Communication interfaceConnectionInterfacesCable length10.2.2 Corrosion resistanceMeets the product standard's requirements.Meets the product standard's requirements.Meets the product standard's requirements.Meets the product standard's requirements.Does not apply, since the entire switchgear needs to be evaluated.Does not apply, since the entire switchgear needs to be evaluated.Meets the product standard's requirements.Does not apply, since the entire switchgear needs to be evaluated.Meets the product standard's requirements.Does not apply, since the entire switchgear needs to be evaluated.Does not apply, since the entire switchgear needs to be evaluated.Is the panel builder's responsibility.Is the panel builder's responsibility.Is the panel builder's responsibility.Is the panel builder's responsibility.Is the panel builder's responsibility.Rapid Link 5 - brochureDA-SW-drivesConnect - installation helpDA-SW-USB Driver PC Cable DX-CBL-PC-1M5DA-SW-Driver DX-CBL-PC-3M0DA-SW-drivesConnect - InstallationshilfeDA-SW-USB Driver DX-COM-STICK3-KITDA-SW-drivesConnectMaterial handling applications - airports, warehouses and intra-logisticseaton-bus-adapter-rapidlink-speed-controller-dimensions-003.eps eaton-bus-adapter-rapidlink-speed-controller-dimensions-005.eps eaton-bus-adapter-rapidlink-speed-controller-dimensions-004.eps eaton-bus-adapter-rapidlink-speed-controller-dimensions-002.epsETN.RASP5-8424PNT-412R001S1.edzIL034093ZUramo5_v32.dwgrasp5_v32.stpGeneration Change RA-SP to RASP5Generation change RAMO4 to RAMO5Generation change from RA-MO to RAMO 4.0Configuration to Rockwell PLC for Rapid LinkGeneration Change RASP4 to RASP5Generation change from RA-SP to RASP 4.0DA-DC-00004508.pdfDA-DC-00003964.pdfDA-DC-00004514.pdfDA-DC-00004184.pdf10.2.3.1 Verification of thermal stability of enclosures10.2.3.2 Verification of resistance of insulating materials to normal heat10.2.3.3 Resist. of insul. mat. to abnormal heat/fire by internal elect. effects10.2.4 Resistance to ultra-violet (UV) radiation10.2.5 Lifting10.2.6 Mechanical impact10.2.7 Inscriptions10.3 Degree of protection of assemblies10.4 Clearances and creepage distances10.5 Protection against electric shock10.6 Incorporation of switching devices and components10.7 Internal electrical circuits and connections10.8 Connections for external conductors10.9.2 Power-frequency electric strength10.9.3 Impulse withstand voltage10.9.4 Testing of enclosures made of insulating material BrochureDisegnieCAD modelIstruzioni di installazione mCAD modelNote per l'applicazione Report di certificazioneEaton Corporation plc Eaton House30 Pembroke Road Dublin 4, Ireland © 2023 Eaton. Tutti i diritti riservati. Eaton is a registered trademark.All other trademarks areproperty of their respectiveowners./socialmediaThe panel builder is responsible for the temperature rise calculation. Eaton will provide heat dissipation data for the devices.Is the panel builder's responsibility. The specifications for the switchgear must be observed.Is the panel builder's responsibility. The specifications for the switchgear must be observed.The device meets the requirements, provided the information in the instruction leaflet (IL) is observed.10.10 Temperature rise10.11 Short-circuit rating10.12 Electromagnetic compatibility10.13 Mechanical function。

24AA04中文资料

• Self-timed write cycle (including auto-erase)

• Page-write buffer for up to 16 bytes

• 2 ms typical write cycle time for page-write

• Hardware write protect for entire memory

- 10 µA standby current typical at 5.5V

- 3 µA standby current typical at 1.8V

• Organized as 2 or 4 blocks of 256 bytes (2 x 256 x 8) or (4 x 256 x 8)

• 2-wire serial interface bus, I2C™ compatible

7

24AA04/08

14

NC

13

VCC

12

WP

11

NC

10

SCL

9

SDA

8

NC

BLOCK DIAGRAM

WP

HV GENERATOR

I/O CONTROL

LOGIC

MEMORY CONTROL

LOGIC

XDEC

SDA SCL

EEPROM ARRAY PAGE LATCHES

YDEC

VCC

SENSE AMP

元器件交易2网4AwwAw.c0ec4b2/b0.co8m

1.0 ELECTRICAL CHARACTERISTICS

1.1 Maximum Ratings*

VCC...................................................................................7.0V All inputs and outputs w.r.t. VSS .............. -0.6V to VCC +1.0V Storage temperature ..................................... -65˚C to +150˚C Ambient temp. with power applied ................ -65˚C to +125˚C Soldering temperature of leads (10 seconds) ............. +300˚C ESD protection on all pins ..................................................≥ 4 kV *Notice: Stresses above those listed under “Maximum ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

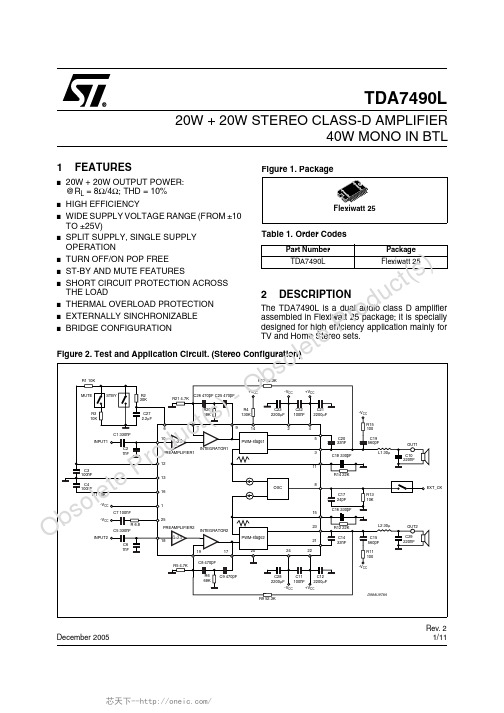

TDA7490L, 规格书,Datasheet 资料

1/11TDA7490LDecember 20051FEATURES■20W + 20W OUTPUT POWER: @R L = 8Ω/4Ω; THD = 10%■HIGH EFFICIENCY■WIDE SUPPLY VOLTAGE RANGE (FROM ±10 TO ±25V)■SPLIT SUPPLY, SINGLE SUPPLY OPERATION■TURN OFF/ON POP FREE ■ST-BY AND MUTE FEATURES■SHORT CIRCUIT PROTECTION ACROSS THE LOAD■THERMAL OVERLOAD PROTECTION ■EXTERNALLY SINCHRONIZABLE ■BRIDGE CONFIGURATION2DESCRIPTIONThe TDA7490L is a dual audio class D amplifier assembled in Flexiwatt 25 package; it is specially designed for high efficiency application mainly for TV and Home Stereo sets.20W + 20W STEREO CLASS-D AMPLIFIER40W MONO IN BTLFigure 2. Test and Application Circuit. (Stereo Configuration)Rev. 2Figure 1. PackageTable 1. Order CodesPart Number Package TDA7490LFlexiwatt 25t eP r od u c t (s)Ob so l e t ePr od u c t (s )- O bs ol TDA7490L2/11Figure 3. Test and Application Circuit. (Bridge Configuration)Table 2. Absolute Maximum RatingsTable 3. Thermal DataSymbol ParameterValue Unit V CC DC Supply Voltage (no signal)±30V P tot Power Dissipation T case = 70°C35W T stg , T j Storage and Junction T emperature –40 to 150°C T op Operating T emperature Range0 to 70°C V 6,8,10,18Maximum Voltage on pins # 6,8,10,18 referred to GND±5VSymbolParameterValue Unit R th j-caseThermal Resistance Junction-caseTyp.1°C/WOb so l e t ePr od u3/11TDA7490LFigure 4. Application in Supply VoltageOb sol e t ePr od u c t (s ) -O bs o l e t eP r odTDA7490L4/11Figure 5. Pin ConnectionTable 4. Pin DescriptionPin N°Name Function1-V CC sign/sub Negative signal/substrate supply 2-V CCpow1Negative power supply CH13out 1PWM output of CH14+V CCpow1Positive power supply CH15BOOT1Bootstrap CH16STBY -MUTE Control State Pin7FEED1Feedback pin 1 CH18OSC Master Oscillator Setting Freequency Pin (or external sync.)9FEED2Feedback pin2 CH110IN1Input CH111T1T riangular waveform CH112+5V+5V regulator (only for internal purposes)13GNDSignal ground 14CURREF Setting current resistor 15T2T riangular waveform CH216-5V -5V regulator (only for internal purposes)17FEED3Feedback pin1 CH218IN2Input CH219FEED4Feedback pin2 CH220NC Not connected 21BOOT2Bootstrap CH222+V CCpow2Positive power supply CH223OUT2PWM output of CH224-V CCpow2Negative power supply CH225V reg10V regulatorOb so l e t ePr od u c t (s ) -O bs o l e t eP r od u c t(s) 5/11TDA7490L*: Po = measured across the load using the following inductor: COIL58120 MPPA 2 (magnectics) TURNS= 20∅ 1 mm (1) L = 15µH, C = 470nF(3) ∆Gv is intended with R2, R17, R5, R9 1% precision (4) Fsw = 0.25 · (1/(300ns + R13 · (C17 + 76pF) . 0.85)(5) V RMAX = (+Vcc) - (-Vcc) when V R ≥V RMAX the device goes in Stand-By modeTable 5. Electrical Characteristics(Refer to the test circuit, V CC = ±19V; R L = 8Ω; Demod. filter L = 30µH, C = 220nF; f = 1KHz; f sw = 200kHz;T amb = 25°C unless otherwise specified.)Symbol ParameterTest ConditionMin. Typ.Max.Unit V S Supply Range±10±25V I q T otal Quiescent Current R L = ∞ no LC filter70120mA V OS Output Offset Voltage -150+150mV P o Output PowerTHD = 10%THD= 1%2016W W P o(BTL)Output Power in Bridge ConfigurationV S = ±20V ; R L = 16ΩTHD = 10%THD=1%4032W W V S =±15.5V; R L = 8ΩTHD = 10%THD=1%4032W WP o (1)Output PowerR L = 4Ω Vcc=±13.5V THD = 10%THD=1%1814.5W W P D Maximum Dissipated Power V CC = ±19V; R L = 8ΩP ο = 20W + 20W; THD = 10% 5.6W ηEfficiency (')P o = 20W + 20W 86%THD T otal Harmonic Distortion R L = 8Ω; Po = 1 W 0.1%I max Overcurrent Protection ThresholdR L = 05A T j Thermal Shut-down Junction T emperature 150°CG v Closed Loop Gain 293031dB ∆G v (3)Gain Matching -1+1dB e N T otal Input Noise R G = 50Ω A Curvef = 20Hz to 22KHz712µV µV C T Cross talk f = 1 KHz, P o = 1W55dB R i Input Resistance2030k ΩSVR Supply Voltage Rejection f = 100Hz; V r = 0.560dBV rmax Overvoltage Threshold (5)5560V T r , T t Rising and Falling Time5070ns R DSON Power T ransistor on Resistance 0.40.8ΩFsw (4)Switching Frequency Range100200230KHzMUTE & STAND-BY FUNCTIONS V ST-BY Stand-by range 00 7V V MUTE Mute Range 1.7 2.5V V PLAY Play Range 45V A MUTE Mute Attenuation5560dB I qST-BYQuiescent Current @ Stand-by35mAOb so l e t ePr od u c t (s ) -O bs o l e t eP r od u c t (s) TDA7490L6/11Figure 6. P.C. Board and Component Layout of the Figs. 2, 3 (for Stereo and Bridge CompatibleConfiguration)Component SideSolderSide)7/11TDA7490L Figure 7. Distortion vs. Output PowerFigure 8. Distortion vs. Output PowerFigure 9. Crosstalk vs. FrequencyFigure 10. Frequency ResponseFigure 11. Power Dissipation vs. Output PowerFigure 12. Distortion vs. Output Power in BTLO b s ol e te Pr o du ct(s)-O bs ol e te Pr o du ct(sTDA7490L8/11Figure 13. Distortion vs. Output Power in BTL Figure 14. Pout vs Supply VoltageTDA7490L Figure 15. Flexiwatt 25 Mechanical Data & Package Dimensions9/11Ob so l e t ePr od u c t (s ) -O bs o l e t eP r od u c t (s) TDA7490L10/11Table 6. Revision HistoryDate RevisionDescription of ChangesMarch 20011First IssueDecember 20052Corrected the value of the inductance in the caption of the T able 5 “Electrical Characteristics”.O b s ol e te Pr o du ct(s)-O bs ol e te Pr o du ct(s)Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics.All other names are the property of their respective owners© 2005 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America11/11TDA7490L 芯天下--/。

常用开关电源芯片大全之欧阳育创编

常用开关电源芯片大全第1章DC-DC电源转换器/基准电压源1.1 DC-DC电源转换器1.低噪声电荷泵DC-DC电源转换器AAT3113/AAT31142.低功耗开关型DC-DC电源转换器ADP30003.高效3A开关稳压器AP15014.高效率无电感DC-DC电源转换器FAN56605.小功率极性反转电源转换器ICL76606.高效率DC-DC电源转换控制器IRU30377.高性能降压式DC-DC电源转换器ISL64208.单片降压式开关稳压器L49609.大功率开关稳压器L4970A10.1.5A降压式开关稳压器L497111.2A高效率单片开关稳压器L497812.1A高效率升压/降压式DC-DC电源转换器L597013.1.5A降压式DC-DC电源转换器LM157214.高效率1A降压单片开关稳压器LM1575/LM2575/LM2575HV15.3A降压单片开关稳压器LM2576/LM2576HV16.可调升压开关稳压器LM257717.3A降压开关稳压器LM259618.高效率5A开关稳压器LM267819.升压式DC-DC电源转换器LM2703/LM270420.电流模式升压式电源转换器LM273321.低噪声升压式电源转换器LM275022.小型75V降压式稳压器LM500723.低功耗升/降压式DC-DC电源转换器LT107324.升压式DC-DC电源转换器LT161525.隔离式开关稳压器LT172526.低功耗升压电荷泵LT175127.大电流高频降压式DC-DC电源转换器LT176528.大电流升压转换器LT193529.高效升压式电荷泵LT193730.高压输入降压式电源转换器LT195631.1.5A升压式电源转换器LT196132.高压升/降压式电源转换器LT343333.单片3A升压式DC-DC电源转换器LT343634.通用升压式DC-DC电源转换器LT346035.高效率低功耗升压式电源转换器LT346436.1.1A升压式DC-DC电源转换器LT346737.大电流高效率升压式DC-DC电源转换器LT378238.微型低功耗电源转换器LTC175439.1.5A单片同步降压式稳压器LTC187540.低噪声高效率降压式电荷泵LTC191141.低噪声电荷泵LTC3200/LTC3200-542.无电感的降压式DC-DC电源转换器LTC325143.双输出/低噪声/降压式电荷泵LTC325244.同步整流/升压式DC-DC电源转换器LTC340145.低功耗同步整流升压式DC-DC电源转换器LTC340246.同步整流降压式DC-DC电源转换器LTC340547.双路同步降压式DC-DC电源转换器LTC340748.高效率同步降压式DC-DC电源转换器LTC341649.微型2A升压式DC-DC电源转换器LTC342650.2A两相电流升压式DC-DC电源转换器LTC342851.单电感升/降压式DC-DC电源转换器LTC344052.大电流升/降压式DC-DC电源转换器LTC344253.1.4A同步升压式DC-DC电源转换器LTC345854.直流同步降压式DC-DC电源转换器LTC370355.双输出降压式同步DC-DC电源转换控制器LTC373656.降压式同步DC-DC电源转换控制器LTC377057.双2相DC-DC电源同步控制器LTC380258.高性能升压式DC-DC电源转换器MAX1513/MAX151459.精简型升压式DC-DC电源转换器MAX1522/MAX1523/MAX152460.高效率40V升压式DC-DC电源转换器MAX1553/MAX155461.高效率升压式LED电压调节器MAX1561/MAX159962.高效率5路输出DC-DC电源转换器MAX156563.双输出升压式DC-DC电源转换器MAX1582/MAX1582Y64.驱动白光LED的升压式DC-DC电源转换器MAX158365.高效率升压式DC-DC电源转换器MAX1642/MAX164366.2A降压式开关稳压器MAX164467.高效率升压式DC-DC电源转换器MAX1674/MAX1675/MAX167668.高效率双输出DC-DC电源转换器MAX167769.低噪声1A降压式DC-DC电源转换器MAX1684/MAX168570.高效率升压式DC-DC电源转换器MAX169871.高效率双输出降压式DC-DC电源转换器MAX171572.小体积升压式DC-DC电源转换器MAX1722/MAX1723/MAX172473.输出电流为50mA的降压式电荷泵MAX173074.升/降压式电荷泵MAX175975.高效率多路输出DC-DC电源转换器MAX180076.3A同步整流降压式稳压型MAX1830/MAX183177.双输出开关式LCD电源控制器MAX187878.电流模式升压式DC-DC电源转换器MAX189679.具有复位功能的升压式DC-DC电源转换器MAX194780.高效率PWM降压式稳压器MAX1992/MAX199381.大电流输出升压式DC-DC电源转换器MAX61882.低功耗升压或降压式DC-DC电源转换器MAX62983.PWM升压式DC-DC电源转换器MAX668/MAX66984.大电流PWM降压式开关稳压器MAX724/MAX72685.高效率升压式DC-DC电源转换器MAX756/MAX75786.高效率大电流DC-DC电源转换器MAX761/MAX76287.隔离式DC-DC电源转换器MAX8515/MAX8515A88.高性能24V升压式DC-DC电源转换器MAX872789.升/降压式DC-DC电源转换器MC33063A/MC34063A90.5A升压/降压/反向DC-DC电源转换器MC33167/MC3416791.低噪声无电感电荷泵MCP1252/MCP125392.高频脉宽调制降压稳压器MIC220393.大功率DC-DC升压电源转换器MIC229594.单片微型高压开关稳压器NCP1030/NCP103195.低功耗升压式DC-DC电源转换器NCP1400A96.高压DC-DC电源转换器NCP140397.单片微功率高频升压式DC-DC电源转换器NCP141098.同步整流PFM步进式DC-DC电源转换器NCP142199.高效率大电流开关电压调整器NCP1442/NCP1443/NCP1444/NCP1445100.新型双模式开关稳压器NCP1501101.高效率大电流输出DC-DC电源转换器NCP1550102.同步降压式DC-DC电源转换器NCP1570103.高效率升压式DC-DC电源转换器NCP5008/NCP5009 104.大电流高速稳压器RT9173/RT9173A105.高效率升压式DC-DC电源转换器RT9262/RT9262A106.升压式DC-DC电源转换器SP6644/SP6645107.低功耗升压式DC-DC电源转换器SP6691108.新型高效率DC-DC电源转换器TPS54350109.无电感降压式电荷泵TPS6050x110.高效率升压式电源转换器TPS6101x111.28V恒流白色LED驱动器TPS61042112.具有LDO输出的升压式DC-DC电源转换器TPS6112x 113.低噪声同步降压式DC-DC电源转换器TPS6200x114.三路高效率大功率DC-DC电源转换器TPS75003115.高效率DC-DC电源转换器UCC39421/UCC39422116.PWM控制升压式DC-DC电源转换器XC6371117.白光LED驱动专用DC-DC电源转换器XC9116118.500mA同步整流降压式DC-DC电源转换器XC9215/XC9216/XC9217119.稳压输出电荷泵XC9801/XC9802120.高效率升压式电源转换器ZXLB16001.2 线性/低压差稳压器121.具有可关断功能的多端稳压器BAXXX122.高压线性稳压器HIP5600123.多路输出稳压器KA7630/KA7631124.三端低压差稳压器LM2937125.可调输出低压差稳压器LM2991126.三端可调稳压器LM117/LM317127.低压降CMOS500mA线性稳压器LP38691/LP38693128.输入电压从12V到450V的可调线性稳压器LR8129.300mA非常低压降稳压器(VLDO)LTC3025130.大电流低压差线性稳压器LX8610131.200mA负输出低压差线性稳压器MAX1735132.150mA低压差线性稳压器MAX8875133.带开关控制的低压差稳压器MC33375134.带有线性调节器的稳压器MC33998135.1.0A低压差固定及可调正稳压器NCP1117136.低静态电流低压差稳压器NCP562/NCP563137.具有使能控制功能的多端稳压器PQxx138.五端可调稳压器SI-3025B/SI-3157B139.400mA低压差线性稳压器SPX2975140.五端线性稳压器STR20xx141.五端线性稳压器STR90xx142.具有复位信号输出的双路输出稳压器TDA8133143.具有复位信号输出的双路输出稳压器TDA8138/TDA8138A144.带线性稳压器的升压式电源转换器TPS6110x145.低功耗50mA低压降线性稳压器TPS760xx146.高输入电压低压差线性稳压器XC6202147.高速低压差线性稳压器XC6204148.高速低压差线性稳压器XC6209F149.双路高速低压差线性稳压器XC64011.3 基准电压源150.新型XFET基准电压源ADR290/ADR291/ADR292/ADR293151.低功耗低压差大输出电流基准电压源MAX610x152.低功耗1.2V基准电压源MAX6120153.2.5V精密基准电压源MC1403154.2.5V/4.096V基准电压源MCP1525/MCP1541155.低功耗精密低压降基准电压源REF30xx/REF31xx156.精密基准电压源TL431/KA431/TLV431A第2章AC-DC转换器及控制器1.厚膜开关电源控制器DP104C2.厚膜开关电源控制器DP308P3.DPA-Switch系列高电压功率转换控制器DPA423/DPA424/DPA425/DPA4264.电流型开关电源控制器FA13842/FA13843/FA13844/FA138455.开关电源控制器FA5310/FA53116.PWM开关电源控制器FAN75567.绿色环保的PWM开关电源控制器FAN76018.FPS型开关电源控制器FS6M07652R9.开关电源功率转换器FS6Sxx10.降压型单片AC-DC转换器HV-2405E11.新型反激准谐振变换控制器ICE1QS0112.PWM电源功率转换器KA1M088013.开关电源功率转换器KA2S0680/KA2S088014.电流型开关电源控制器KA38xx15.FPS型开关电源功率转换器KA5H0165R16.FPS型开关电源功率转换器KA5Qxx17.FPS型开关电源功率转换器KA5Sxx18.电流型高速PWM控制器L499019.具有待机功能的PWM初级控制器L599120.低功耗离线式开关电源控制器L659021.LINK SWITCH TN系列电源功率转换器LNK304/LNK305/LNK30622.LINK SWITCH系列电源功率转换器LNK500/LNK501/LNK52023.离线式开关电源控制器M51995A24.PWM电源控制器M62281P/M62281FP25.高频率电流模式PWM控制器MAX5021/MAX502226.新型PWM开关电源控制器MC4460427.电流模式开关电源控制器MC4460528.低功耗开关电源控制器MC4460829.具有PFC功能的PWM电源控制器ML482430.液晶显示器背光灯电源控制器ML487631.离线式电流模式控制器NCP120032.电流模式脉宽调制控制器NCP120533.准谐振式PWM控制器NCP120734.低成本离线式开关电源控制电路NCP121535.低待机能耗开关电源PWM控制器NCP123036.STR系列自动电压切换控制开关STR8xxxx37.大功率厚膜开关电源功率转换器STR-F665438.大功率厚膜开关电源功率转换器STR-G865639.开关电源功率转换器STR-M6511/STR-M652940.离线式开关电源功率转换器STR-S5703/STR-S5707/STR-S570841.离线式开关电源功率转换器STR-S6401/STR-S6401F/STR-S6411/STR-S6411F 442.开关电源功率转换器STR-S651343.离线式开关电源功率转换器TC33369~TC3337444.高性能PFC与PWM组合控制集成电路TDA16846/TDA1684745.新型开关电源控制器TDA1685046.“绿色”电源控制器TEA150447.第二代“绿色”电源控制器TEA150748.新型低功耗“绿色”电源控制器TEA153349.开关电源控制器TL494/KA7500/MB375950.Tiny SwitchⅠ系列功率转换器TNY253、TNY254、TNY25551.Tiny SwitchⅡ系列功率转换器TNY264P~TNY268G52.TOP Switch(Ⅱ)系列离线式功率转换器TOP209~TOP22753.TOP Switch-FX系列功率转换器TOP232/TOP233/TOP23454.TOP Switch-GX系列功率转换器TOP242~TOP25055.开关电源控制器UCX84X56.离线式开关电源功率转换器VIPer12AS/VIPer12ADIP57.新一代高度集成离线式开关电源功率转换器VIPer53第3章功率因数校正控制/节能灯电源控制器1.电子镇流器专用驱动电路BL83012.零电压开关功率因数控制器FAN48223.功率因数校正控制器FAN75274.高电压型EL背光驱动器HV8265.EL场致发光背光驱动器IMP525/IMP5606.高电压型EL背光驱动器/反相器IMP8037.电子镇流器自振荡半桥驱动器IR21568.单片荧光灯镇流器IR21579.调光电子镇流器自振荡半桥驱动器IR215910.卤素灯电子变压器智能控制电路IR216111.具有功率因数校正电路的镇流器电路IR216612.单片荧光灯镇流器IR216713.自适应电子镇流器控制器IR252014.电子镇流器专用控制器KA754115.功率因数校正控制器L656116.过渡模式功率因数校正控制器L656217.集成背景光控制器MAX8709/MAX8709A18.功率因数校正控制器MC33262/MC3426219.固定频率电流模式功率因数校正控制器NCP165320.EL场致发光灯高压驱动器SP440321.功率因数校正控制器TDA4862/TDA486322.有源功率因数校正控制器UC385423.高频自振荡节能灯驱动器电路VK05CFL24.大功率高频自振荡节能灯驱动器电路VK06TL第4章充电控制器1.多功能锂电池线性充电控制器AAT36802.可编程快速电池充电控制器BQ20003.可进行充电速率补偿的锂电池充电管理器BQ20574.锂电池充电管理电路BQ2400x5.单片锂电池线性充电控制器BQ2401xB接口单节锂电池充电控制器BQ2402x7.2A同步开关模式锂电池充电控制器BQ241008.集成PWM开关控制器的快速充电管理器BQ29549.具有电池电量计量功能的充电控制器DS277010.锂电池充电控制器FAN7563/FAN756411.2A线性锂/锂聚合物电池充电控制器ISL629212.锂电池充电控制器LA5621M/LA5621V13.1.5A通用充电控制器LT157114.2A恒流/恒压电池充电控制器LT176915.线性锂电池充电控制器LTC173216.带热调节功能的1A线性锂电池充电控制器LTC173317.线性锂电池充电控制器LTC173418.新型开关电源充电控制器LTC198019.开关模式锂电池充电控制器LTC400220.4A锂电池充电器LTC400621.多用途恒压/恒流充电控制器LTC400822.4.2V锂离子/锂聚合物电池充电控制器LTC405223.可由USB端口供电的锂电池充电控制器LTC405324.小型150mA锂电池充电控制器LTC405425.线性锂电池充电控制器LTC405826.单节锂电池线性充电控制器LTC405927.独立线性锂电池充电控制器LTC406128.镍镉/镍氢电池充电控制器M62256FP29.大电流锂/镍镉/镍氢电池充电控制器MAX150130.锂电池线性充电控制器MAX150731.双输入单节锂电池充电控制器MAX1551/MAX155532.单节锂电池充电控制器MAX167933.小体积锂电池充电控制器MAX1736B接口单节锂电池充电控制器MAX181135.多节锂电池充电控制器MAX187336.双路输入锂电池充电控制器MAX187437.单节锂电池线性充电控制器MAX189838.低成本/多种电池充电控制器MAX190839.开关模式单节锂电池充电控制器MAX1925/MAX192640.快速镍镉/镍氢充电控制器MAX2003A/MAX200341.可编程快速充电控制器MAX712/MAX71342.开关式锂电池充电控制器MAX74543.多功能低成本充电控制器MAX846A44.具有温度调节功能的单节锂电池充电控制器MAX8600/MAX860145.锂电池充电控制器MCP73826/MCP73827/MCP7382846.高精度恒压/恒流充电器控制器MCP73841/MCP73842/MCP73843/MCP73844 647.锂电池充电控制器MCP73861/MCP7386248.单节锂电池充电控制器MIC7905049.单节锂电池充电控制器NCP180050.高精度线性锂电池充电控制器VM7205。

Am79R70

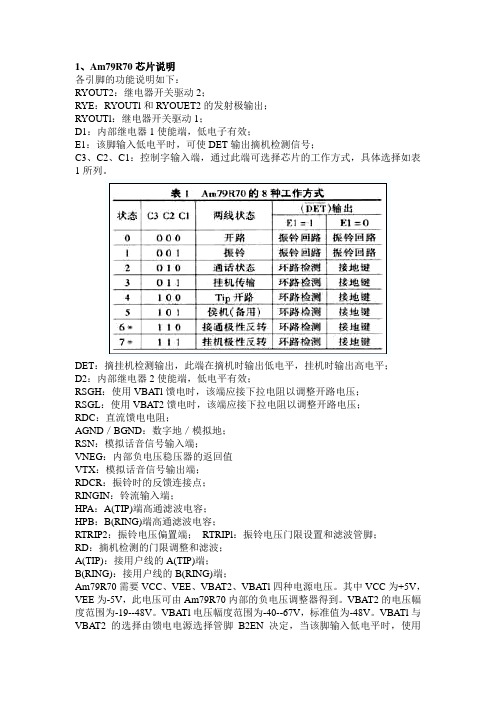

1、Am79R70芯片说明各引脚的功能说明如下:RYOUT2:继电器开关驱动2;RYE:RYOUTl和RYOUET2的发射极输出;RYOUTl:继电器开关驱动1;D1:内部继电器1使能端,低电子有效;E1:该脚输入低电平时,可使DET输出摘机检测信号;C3、C2、C1:控制字输入端,通过此端可选择芯片的工作方式,具体选择如表1所列。

DET:摘挂机检测输出,此端在摘机时输出低电平,挂机时输出高电平;D2:内部继电器2使能端,低电平有效;RSGH:使用VBATl馈电时,该端应接下拉电阻以调整开路电压;RSGL:使用VBAT2馈电时,该端应接下拉电阻以调整开路电压;RDC:直流馈电电阻;AGND/BGND:数字地/模拟地;RSN:模拟话音信号输入端;VNEG:内部负电压稳压器的返回值VTX:模拟话音信号输出端;RDCR:振铃时的反馈连接点;RINGIN:铃流输入端;HPA:A(TIP)端高通滤波电容;HPB:B(RING)端高通滤波电容;RTRIP2:振铃电压偏置端;RTRIPl:振铃电压门限设置和滤波管脚;RD:摘机检测的门限调整和滤波;A(TIP):接用户线的A(TIP)端;B(RING):接用户线的B(RING)端;Am79R70需要VCC、VEE、VBAT2、VBATl四种电源电压。

其中VCC为+5V,VEE为-5V,此电压可由Am79R70内部的负电压调整器得到。

VBAT2的电压幅度范围为-19--48V。

VBATl电压幅度范围为-40--67V,标准值为-48V。

VBATl与VBAT2的选择由馈电电源选择管脚B2EN决定,当该脚输入低电平时,使用VBAT2馈电;该脚输入高电平时,使用VBATl馈电。

由于振铃时回路所需的馈电电压较高,所以振铃时采用VBATl馈电,而平时采用VBAT2馈电。

在实际应用电路中,只需要外接VCC、VBATl两种电压,因为VBATl与VBAT2可以连接在一起。

2 、Am79R70在ALU的应用ALU(模拟用户接口单元)是连接普通模拟话机和数字交换网络的接口电路,CCITT为程控数字交换机的模拟用户接口规定了7项功能,这七项功能分述如下。

电子元器件芯片AD780BRZ-REEL7中文规格书

AD4000/AD4004/AD4008Data Sheet Rev. E | Page 10 of 40ABSOLUTE MAXIMUM RATINGSNote that the input overvoltage clamp cannot sustain theovervoltage condition for an indefinite amount of time. Table 5.ParameterRating Analog InputsIN+, IN− to GND 1−0.3 V to V REF + 0.4 V or ±130 mA 2 Supply VoltageREF, VIO to GND−0.3 V to +6.0 V VDD to GND−0.3 V to +2.1 V VDD to VIO−6 V to +2.4 V Digital Inputs to GND−0.3 V to VIO + 0.3 V Digital Outputs to GND−0.3 V to VIO + 0.3 V Storage Temperature Range−65°C to +150°C Junction Temperature150°C Lead Temperature Soldering260°C reflow as per JEDEC J-STD-020 ESD RatingsHuman Body Model4 kV Machine Model200 V Field Induced Charged Device Model 1.25 kV 1See the Analog Inputs section for an explanation of IN+ and IN−. 2 Current condition tested over a 10 ms time interval.Stresses at or above those listed under Absolute MaximumRatings may cause permanent damage to the product. This is astress rating only; functional operation of the product at theseor any other conditions above those indicated in the operationalsection of this specification is not implied. Operation beyondthe maximum operating conditions for extended periods mayaffect product reliability.THERMAL RESISTANCE Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required. θJA is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure. θJC is the junction-to-case thermal resistance. Table 6. Thermal Resistance Package Type 1θJA θJC Unit RM-10147 38 °C/W CP-10-9114 33°C/W 1 Test Condition 1: thermal impedance simulated values are based upon use of 2S2P JEDEC PCB. See the Ordering Guide. ESD CAUTIONData SheetAD4000/AD4004/AD4008Rev. E | Page 11 of 40 PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONSREFVDD IN+IN–GND VIO SDI SCK SDO CNV 14956-003Figure 3. 10-Lead MSOP Pin Configuration 1REF 2VDD 3IN+4IN–5GND 10VIO 9SDI 8SCK 7SDO 6CNV AD4000/AD4004/AD4008TOP VIEW (Not to Scale)14956-004NOTES 1.CONNECT THE EXPOSED PAD TO GND.THIS CONNECTION IS NOT REQUIRED TO MEET THE SPECIFIED PERFORMANCE.Figure 4. 10-Lead LFCSP Pin Configuration1AI is analog input, P is power, DI is digital input, and DO is digital output.2 N/A means not applicable.。

半导体传感器AD7490SRUZ-EP-RL7中文规格书

REV.AD744–8–EXTERNAL FREQUENCY COMPENSATIONEven though the AD744 is useable without compensation inmost applications, it may be externally compensated for evenmore flexibility. This is accomplished by connecting a capacitorbetween Pins 5 and 8. Figure 28, a simplified schematic of theAD744, shows where this capacitor is connected. This feature isuseful because it allows the AD744 to be used as a unity gainvoltage follower. It also enables the amplifier to drive capacitiveloads up to 2000 pF and greater.–INNULL NULL +V SOUTPUT –V S Figure 28.AD744 Simplified Schematic The slew rate and gain bandwidth product of the AD744 are in-versely proportional to the value of the compensation capacitor,C COMP . Therefore, when trying to maximize the speed of theamplifier, the value of C COMP should be minimized. C COMP canalso be used to slow the amplifier to a point where the slew rateis perfectly symmetrical and well controlled. Figure 29 sum-marizes the effect of external compensation on slew rate andbandwidth.C COMP – pF 20G A I N B A ND W I D T H – M H z 200.020.210100100010S LE W R A T E – V /s 1000.11.0Figure 29.Gain Bandwidth and Slew Rate vs. C COMPThe following section provides tables to show what C COMP values will provide the necessary compensation for given circuit configurations and capacitive loads. In each case, the recommended C COMP is a minimum value. A larger C COMP can always be used, but slew rate and bandwidth performance will be degraded.Figure 30 shows the AD744 configured as a unity gain voltage follower. In this case, a minimum compensation capacitor of 5 pF is necessary for stable operation. Larger compensation ca-pacitors can be used for driving larger capacitive loads. Table I outlines recommended minimum values for C COMP based on the desired capacitive load. It also gives the slew rate and band-width that will be achieved for each case.V OUTV Figure 30.AD744 Connected as a Unity Gain Voltage Follower Table I. Recommended Values of C COMP vs.Various Capacitive Loads Max –3 dB C LOAD C COMP Slew Rate Bandwidth Gain(pF)(pF)(V/s)(MHz)150537 6.511501025 4.3120002512.5 2.0Figures 31 and 32 show the AD744 as a voltage follower with gain and as an inverting amplifier. In these cases, external compensation is not necessary for stable operation. How-ever, compensation may be applied to drive capacitive loads above 50 pF. Table II gives recommended C COMP values, alongwith expected slew rates and bandwidths for a variety of loadconditions and gains for the circuits in Figures 31 and 32.V OUT C *Figure 31. AD744 Connected as a Voltage FollowerOperating at Gains of 2 or GreaterDREV. AD744–9–Table II. Recommended Values of C COMP vs. Various Load Conditions for the Circuits of Figures 31 and 32.V *Product D。

矽普特产品简介

3W,AB 类 1W,AB

类

2W,AB 类

1.8W, AB 类 1W,AB

类

2.7W, AB 类 3W,AB

类 4W,AB

类

5V,THD<10%, 2.6W(ESOP8), 2.4W(SOP8),4Ω 5V,THD<10%,

2×2.6W, THD<1%,2×

1.8W,4Ω 5V,THD<10%,

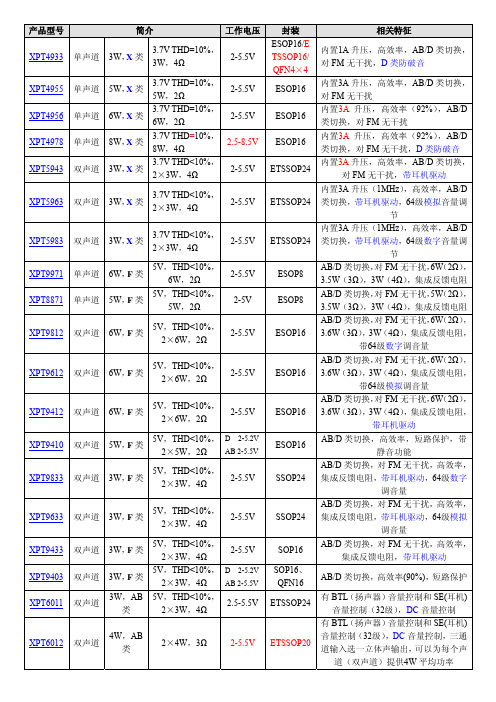

产品型号 XPT4933 XPT4955 XPT4956 XPT4978 XPT5943 XPT5963

XPT5983 XPT9971 XPT8871 XPT9812

XPT9612

XPT9412 XPT9410 XPT9833

XPT9633 XPT9433 XPT9403 XPT6011

XPT6012

2-5.5V

3W,F 类

5V,THD<10%, 2×3W,4Ω

2-5.5V

3W,F 类

3W,F 类 3W,AB

类

5V,THD<10%,

2×3W,4Ω

2-5.5V

5V,THD<10%, D 2-5.2V

2×3W,4Ω AB 2-5.5V

5V,THD<10%,

2×3W,4Ω

2.5-5.5V

4W,AB 类

低电平关断,XPT4863则相反。 XPT4963完全兼容 LM4863。

单端模式,5V,THD+N≤0.5%,75mW (32Ω)。完全兼容 LM4863,CSC4863。

适用于台式、手提电脑及低压音响系统 等领域,是一款市场普遍认可并广泛采

用的典型芯片 适用于台式、手提电脑及低压音响系统 等领域,是一款市场普遍认可并广泛采

TDA7491MV中文规格书

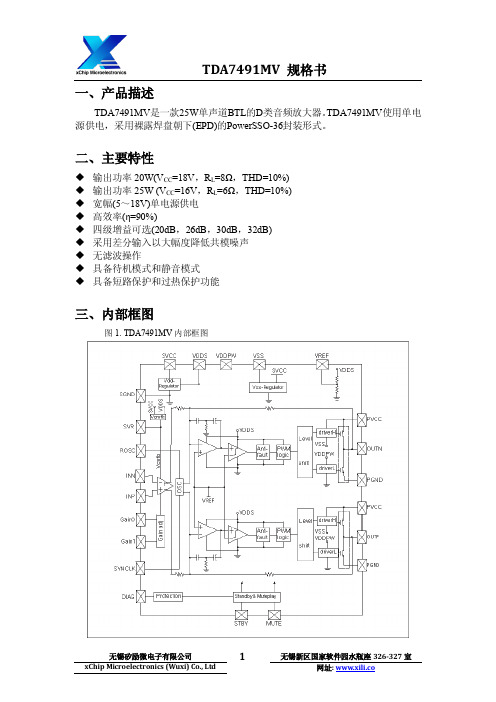

一、产品描述TDA7491MV是一款25W单声道BTL的D类音频放大器。

TDA7491MV使用单电源供电,采用裸露焊盘朝下(EPD)的PowerSSO-36封装形式。

二、主要特性◆输出功率20W(V CC=18V,R L=8Ω,THD=10%)◆输出功率25W (V CC=16V,R L=6Ω,THD=10%)◆宽幅(5~18V)单电源供电◆高效率(η=90%)◆四级增益可选(20dB,26dB,30dB,32dB)◆采用差分输入以大幅度降低共模噪声◆无滤波操作◆具备待机模式和静音模式◆具备短路保护和过热保护功能三、内部框图图1. TDA7491MV内部框图目录1. 引脚描述 (3)2. 电气特性 (5)3. 性能指标 (7)4. 应用信息 (12)5. 封装参数 (20)6. 订购信息 (22)1.引脚描述1.1引脚排列图2. TDA7491MV引脚排列(顶视图)1.2引脚定义2.电气特性2.1极限工作条件2.2热学参数2.3电气特性下表中的数据适用如下额定工作条件(特殊注明除外):V CC=18V, R L=8Ω, R OSC=R3=39kΩ, C8=100nF, f=1kHz,G V=20dB, T amb=25℃符号描述条件最小值典型值最大值单位3.性能指标以下测量结果均基于如下测试条件(特殊注明的除外):8Ω负载:L=33μH,C=220nF图3. 输出功率vs. 电源电压图4. THD vs. 输出功率(1kHz)图5. THD vs. 输出功率(100Hz)图6. THD vs. 频率图7. 频率响应图8. FFT特性(0 dB)图9. FFT特性(-60 dB)图10. 闭环增益vs. 频率图11. 耗散功率和效率vs. 输出功率图12. 衰减vs. 电压(引脚MUTE)图13. 电流消耗vs. 电压(引脚STBY)图14. 衰减vs. 电压(引脚STBY)图15. 电源抑制比vs. 频率4.应用信息4.1应用电路图图16. 应用电路图4.2模式选择TDA7491MV的三种工作模式是由STBY (引脚20)和MUTE (引脚21)来设置的。

QC_T 749

76 QC/T 745-2006 液化石油气汽车橡胶管路

77 QC/T 746-2006 压缩天然气汽车高压管路 78 QC/T3 3-2006 汽车发动机硅油风扇离合器试验方法 79 QC/T 747-2006 汽车发动机硅油风扇离合器技术条件

QC/T 33-1992

80 QC/T 748-2006 汽车发 动机气 门 一气 门座强 化磨损 台架试 验方法

3.4

射 程 range 喷射 部 件 出口至液流端点的距离。

3.5

罐体 有 效 容积 thev alidv olumeo fta nk 罐体 允 许 装水的最大容量。

3.6

吸水 深 度 pumpd epth 正 常 作 业 的喷 洒车所 在水平 面至被 吸液 面的距 离

4 要求

4.1 基本要求 4.1., 喷洒车应符合本标准的规定,并按照经规定程序批准的图样和技术文件制造。 4.1.2 外购件 、外协件应符合有关标准的规定,并具有制造厂的合格证 ,经生产厂检验合格后方可 使用。所有 自制零、部件经检验合格后方可装配。 4.1.3 强制性要求应符合国家有关规定。 4.1.4 装配件 、连接件应牢固、可靠,不得松脱。 4.2 外观质量 4.2.1 焊接应均匀平直,无漏焊、裂纹、夹渣 、气孔、咬边 、飞溅 、焊穿等缺陷。铸件表面无飞边 、包砂 等缺陷 。 4.2.2 涂漆质量应符合 QC/T4 84的规定。 4.2.3 外露黑色金属件应进行防腐处理。 4.3 整车 4.3.1 整车外廓尺寸 、整车满载总质量 、转向轴(轮)载质量应符合 GB1 589的规定。 4.3.2 最高车速应符合原汽车底盘的要求 ;侧倾稳定角应符合 GB7 258的规定;整车行驶性能应符 合原汽车底盘的规定。 4.3.3 喷洒车加速行驶时车外噪声应符合 GB1 495的规定,在常用工作压力下行驶工作时,作业人 员耳边噪声不得大于 90dB( A)o 4.3.4 喷洒车的防护装置应符合 GB1 1567.1 和 GB1 1567.2的规定。 4.3.5 喷洒车的照明和信号装置应符合 GB7 258和 GB4 785的规定。 4.3.6 喷洒车的行驶可靠性试验里程应符合 QC/T2 52的规定。 4.3.7 喷洒车的作业可靠性考核时间为 150h,其 中喷药作业时间不少于总考核时间的50%,其他 专用性能装置作业时间占50%。首次故障前工作时间不少于 100h,平均无故障时间不少于 50h,可

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。