74Ls290芯片构成N进制计数器

时序逻辑电路练习题及答案

第五章时序逻辑电路练习题及答案[]分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

图[解]驱动方程:丿广心=2, 状态方程:Q;J00" +型0 =型㊉G:厶=©=©, er = +Q-Q"=0 ㊉er ;、=Q、QJ 电Q;Q:l人=G0,K输出方程:Y = Q^由状态方程可得状态转换表,如表所示;由状态转换表可得状态转换图,如图所示。

电路可以自启动。

表[]试分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。

A为输入逻辑变量。

>C1il1D|y >ci p-1CP1Q2 图[解] _驱动方程:D] = AQ2, D2 = AQ.Q 2状态方程:ft"1 = , 0广=4議=4(0;'+0")由状态方程可得状态转换表,如表所示;由状态转换表町得状态转换图,如图所示。

电路的逻辑功能是:判断A是否连续输入四个和四个以上“1” 信号,是则Y=l,否则Y=0。

Q2Q1 A/Y 佗0Y0 0 00 10 0 0 1 1 00 0 1 0 1 100 1 10 011 0 0 1 11 1 1 1 1 00 1 1 00 10 1 0 10 00[] 试分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,检查电路能否自启动。

r-0Q1 TF1^=>C1 IK O->C11KCP [解]J严殛3, K严1;J2=Q lt K严玆;=巫・g ;er1 = ae2+me2;丿3 = Q1Q29位=Q2 Qr=Q.QA^QAY= O2O3电路的状态转换图如图所示,电路能够自启动。

Q3Q2Q1 /Y表[] 分析图给岀的时序电路,画岀电路的状态转换图,检查电路能否自启动,说明电 路实现的功能。

A 为输入变量。

基于计数器74LS290的Multisim仿真出现的问题及处理

基于计数器74LS290的Multisim仿真出现的问题及处理作者:胡洁微周宦银胥飞燕李丽蓉单坤来源:《中国教育技术装备》2016年第24期摘要 Multisim仿真软件是电路分析和设计中常用的一种辅助手段,但若时序逻辑电路设计不当,因时延造成信号畸变,引发电路输出状态偏离原有的“轨道”,将使得电路功能无法实现。

因此,竞争冒险是时序电路设计中必须考虑的重要方面,加入复位电路设计,是解决时序逻辑电路测试生成问题的有效方法。

关键词计数器;Multisim仿真;竞争冒险;复位电路中图分类号:TP391.9 文献标识码:B文章编号:1671-489X(2016)24-0023-03A Problem-solving of Counter 74LS290 Multisim Simulation Cir-cuit//HU Jiewei, ZHOU Huanyin, XU Feiyan, LI Lirong, SHAN KunAbstract Circuit simulation is a common auxiliary analysis and de-sign means by Multisim software, but if the sequential logic circuit design is not correct, the signal distortion may be caused by time delay,and then the output state will deviate from its original orbit, what makesthe circuit functions cannot be achieved. So the race and hazard is quite essential and must be considered when designing logic circuit. Sometimes adding reset circuit design is an important method of sol-ving the sequential logic circuit test generation problem.Key words counter; Multisim simulation; race and hazard; reset circuit1 前言在数字电路中使用最多的时序电路就是计数器电路,计数器不仅可以用于计数,而且可以用于定时、分频、产生脉冲以及进行数字运算等。

触发器及时序逻辑电路考试试题(电工电子技术大学专业试卷)

触发器及时序逻辑电路考试试题一.填空题:1、欲将D 触发器作成翻转触发器,应令D = ;欲将JK 触发器作成翻转触发器,最简单的方法是 令J = ,K = 。

2、与非门构成的基本RS 触发器输入为D S 、D R ,工作时的约束条件为 。

3、时序逻辑电路的特点是 。

4、一个JK 触发器,现态Q n =0,要求在CP 作用下进入次态Q n+1=1,可令J = , K= 。

5、设计一个五进制计数器,最少需要触发器的个数是 。

6、具有置0、置1、保持和翻转功能的触发器是 触发器;只具有置0、置1功的触发器是 触发器。

7、D 触发器的特征方程为 ,JK 触发器的特征方程为 。

8、若要将T 触发器转换为/T 触发器,可将T 端接 电平。

9、要存储n 位二进制信息需要 个触发器? 10、触发器的状态是指 端的状态. 二.选择题:1、输入时钟脉冲频率为100KH Z 时,则十进制计数器最高一级触发器输出脉冲的频率为( )。

A .10KH ZB .20KH ZC .50KH ZD .100KH Z2、具有置0、置1、保持、翻转四种功能的触发器为 ( ) 。

A .RS 触发器B .JK 触发器C .D 触发器 D .T 触发器3.设计一个七进制计数器,最少需要触发器的个数是( ) 。

A .2个B .3个C .8个D .15个 4、四位二进制加法计数器能计的最大十进制数位为 ( )。

A .4B .10C .15D .16 5、四位二进制加法计数器的有效状态有( )个。

A .4B .10C .15D .167、下列电路中,是时序电路的是( )A .编码器B .寄存器C .译码器D .加法器 8、/T 触发器具有( )功能。

A .置0B .置1C .保持D .翻转9、与非门组成的基本RS 触发器的输入端D S 称为直接置1端,D R 称为直接置0端,若要使该触发器实现置1功能,应令( )。

A .0S D = 0R D =B .1S D = 0R D =C .B .0SD = 1R D = D .B .1S D = 1R D =10、图2-1所示是一个由74LS290型集成芯片构成的计数器,分析它是一个( )进制计数器?A .五进制B .六进制C .七进制D .十四进制三、判断题:( )1、一个十进制计数器可以作为十分频器使用。

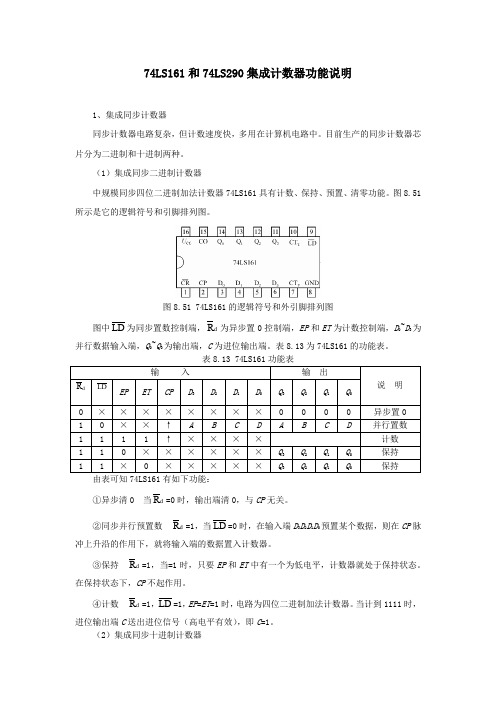

74LS161和74LS290集成计数器功能说明

74LS161和74LS290集成计数器功能说明1、集成同步计数器同步计数器电路复杂,但计数速度快,多用在计算机电路中。

目前生产的同步计数器芯片分为二进制和十进制两种。

(1)集成同步二进制计数器中规模同步四位二进制加法计数器74LS161具有计数、保持、预置、清零功能。

图8.51所示是它的逻辑符号和引脚排列图。

图8.51 74LS161的逻辑符号和外引脚排列图图中LD为同步置数控制端,d R为异步置0控制端,EP和ET为计数控制端,D0~D3为并行数据输入端,Q0~Q3为输出端,C为进位输出端。

表8.13为74LS161的功能表。

R=0时,输出端清0,与CP无关。

①异步清0 当dR=1,当LD=0时,在输入端D3D2D1D0预置某个数据,则在CP脉②同步并行预置数d冲上升沿的作用下,就将输入端的数据置入计数器。

R=1,当=1时,只要EP和ET中有一个为低电平,计数器就处于保持状态。

③保持d在保持状态下,CP不起作用。

R=1,LD=1,EP=ET=1时,电路为四位二进制加法计数器。

当计到1111时,④计数d进位输出端C送出进位信号(高电平有效),即C=1。

(2)集成同步十进制计数器集成同步十进制加法计数器74LS160的管脚图和功能表与74LS161基本相同,唯一不同的是74LS160是十进制计数器,而74LS161是二进制计数器。

2、集成异步计数器异步计数电路简单,但计数速度慢,多用于仪器、仪表中。

(1)集成计数器74LS290图8.52是二-五-十进制集成计数器74LS290的逻辑结构图。

它兼有二进制、五进制和十进制三种计数功能。

当十进制计数时,又有8421BCD 和5421BCD 码选用功能,表8.14是它的功能表。

95481213131011CP 0CP 1Q 0Q 1Q 3Q 2R O(1)R O(2)S 9(1)S 9(2)图8.52 74LS290的逻辑结构图由表可知,74LS290具有如下功能:①异步置0 当R 0(1)=R 0(2)=1且S 9(1)或S 9(2)中任一端为0,则计数器清零,即Q D Q C Q B Q A =0000。

课程设计——秒表计时器

天津机电职业技术学院《电子技术》课程设计论文电子秒表.完成时间:2009.12.30—2010.1.6班级:08电气自动化三班姓名:马赛男李丽美学号:*********200812060前言21世纪是一个电子技术和电子元件有更大发展的世纪。

回顾百年来电子技术和电子工业发展的成就,举世瞩目。

可以看到,从国民经济到日常生活的各个方面,电子产品无所不在,体事例无庸枚举,其发展前景未可限量。

作为一个学习电子专业的大学生,我们不但要有扎实的基础知识、课本知识,还应该有较强的动手能力。

现实也要求我们既精通电子技术理论,更要掌握电子电路设计、实验研究和调试技术。

课程设计就是一个理论联系实际的机会。

本次设计主要完成具备基本功能的电子秒表的理论设计,电子秒表是重要的记时工具,广泛运用于各行各业中。

作为一种测量工具,电子秒表相对其它一般的记时工具具有便捷、准确、可比性高等优点,不仅可以提高精确度,而且可以大大减轻操作人员的负担,降低错误率。

在写本报告的过程中,摘编了生产厂家和各种电子类报刊、参考书的资料,特向提供资料的同学及作者表示感谢。

由于水平有限,报告中定有不妥之处,请提出宝贵意见。

目录一、题目-------------------------------------------------------1二、题目说明-------------------------------------------------1三、原理介绍-------------------------------------------------1四、单元电路设计-------------------------------------------21、时基信号发生器-------------------------------------22、计数器-------------------------------------------------73、译码器-------------------------------------------------114、显示器-------------------------------------------------135、防抖开关----------------------------------------------15五、总装图----------------------------------------------------17六、名细表----------------------------------------------------18七、分工情况-------------------------------------------------19八、后记-------------------------------------------------------20九、参考资料-------------------------------------------------21报告内容一.题目电子秒表二.题目说明秒表计时器常常用于体育竞赛及各种其他要求有较精确时间的各领域中。

国开作业《数字电子电路》实验3集成计数器设计参考40

实验3 集成计数器设计实验报告

实验目的:

1.熟悉任意进制计数器的工作原理及其设计方法。

2.熟悉中规模集成电路计数器74LS161、74LS290的逻辑功能及使用方法

实验仪器与设备:

1.数字电路实验箱。

2.集成电路计数器74LS161两片、74LS290一片

实验原理:

1. 二进制同步加法计数器74LS161

图3-1 74LS161管脚图和逻辑功能示意图

集成芯片74LS161是由四个主从J-K触发器构成二进制同步加法计数

器,图中:D

3、D

2

、D

1

、D

为触发器输入端,Q

3

、Q

2

、Q

1

、Q

为触发器输出

端;CP时钟上升沿有效;R

D 为异步清零端,低电平有效;L

D

为同步预置

端,低电平有效;EP、ET为两个使能端,便于多片级联;RCO为输出进位端。

表3-1 二进制同步加法计数器74LS161功能表。

2020—2021学年非毕业班集成电路设计与集成系统专业《数字逻辑电路》期末考试题及答案(试卷A)

院系: 专业班级: 学号: 姓名: 座位号:XXX 大学2020—2021学年非毕业班集成电路设计与集成系统专业《数字逻辑电路》期末考试题及答案(试卷A )题 号 一 二 三 四 五 总分 评卷人 分 值 20 20 10 20 30 100得 分得 分一、 选择题;(每小题2分,共20分)。

1、将幅值上、时间上离散的阶梯电平统一归并到最邻近的指定电平的过程称为( )。

A 、采样;B 、量化;C 、保持;D 、编码;2、8个输入端的编码器按二进制数编码时,输出端的个数是教研室主任审核(签名): 教学主任(签名):课程代码: 适用班级:命题教师:任课教师:院系: 专业班级: 学号: 姓名: 座位号:( )。

A 、2个;B 、3个;C 、4个;D 、8个;3、下列电路中,不属于组合逻辑电路的是( )。

A 、译码器;B 、全加器;C 、寄存器;D 、编码器;4、CMOS 数字集成电路与TTL 数字集成电路相比突出的优点是( )。

A 、微功耗;B 、高速度;C 、高抗干扰能力;D 、电源范围宽;5、指出下列各式中哪个是四变量A 、B 、C 、D 的最大项( )。

A 、ABC ;B 、A+B+C+D ;C 、D ABC ; D 、B AC ;6、同步时序电路和异步时序电路比较,其差异在于后者( )。

院系: 专业班级: 学号: 姓名: 座位号:A 、没有触发器;B 、没有统一的时钟脉冲控制;C 、没有稳定状态;D 、输出只与内部状态有关;7、两片74LS290芯片扩展而成的计数器,最大模数是( )。

A 、80;B 、20;C 、54;D 、100;8、由与非门组成的基本RS 触发器不允许输入的变量组合S 、R 为( )。

A 、1==S R ; B 、10==S R 、; C 、01==S R 、;D 、==S R ;9、逻辑函数的表示方法中具有唯一性的是( )。

A 、真值表;B 、表达式;C 、表达式;D 、卡诺图;10、将TTL 与非门作非门使用,则多余输入端应做的处理是( )。

数字电子技术考试

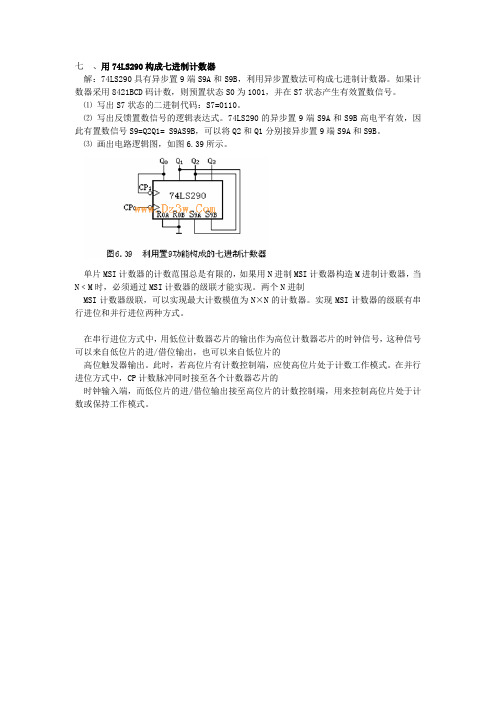

七、用74LS290构成七进制计数器

解:74LS290具有异步置9端S9A和S9B,利用异步置数法可构成七进制计数器。

如果计数器采用8421BCD码计数,则预置状态S0为1001,并在S7状态产生有效置数信号。

⑴ 写出S7状态的二进制代码:S7=0110。

⑵ 写出反馈置数信号的逻辑表达式。

74LS290的异步置9端S9A和S9B高电平有效,因此有置数信号S9=Q2Q1= S9AS9B,可以将Q2和Q1分别接异步置9端S9A和S9B。

⑶ 画出电路逻辑图,如图6.39所示。

单片MSI计数器的计数范围总是有限的,如果用N进制MSI计数器构造M进制计数器,当N﹤M时,必须通过MSI计数器的级联才能实现。

两个N进制

MSI计数器级联,可以实现最大计数模值为N×N的计数器。

实现MSI计数器的级联有串行进位和并行进位两种方式。

在串行进位方式中,用低位计数器芯片的输出作为高位计数器芯片的时钟信号,这种信号可以来自低位片的进/借位输出,也可以来自低位片的

高位触发器输出。

此时,若高位片有计数控制端,应使高位片处于计数工作模式。

在并行进位方式中,CP计数脉冲同时接至各个计数器芯片的

时钟输入端,而低位片的进/借位输出接至高位片的计数控制端,用来控制高位片处于计数或保持工作模式。

电气控制技术习题

试画出对应的逻辑电路图, 并分析其逻辑功能。

电气控制技术习题

5.3 析图题5.3(a)所示时序电路的逻辑功能。根据图题5.3(b) 所示输入信号波形, 画出对应的输出Q2、Q1的输出波形。

CR Q1 RD CP C F1 D Q Q RD C F2 D Q Q Q2 CP CR

(a)

(b)

图题5.3 (a) 逻辑电路图; (b) 输入波形图

+UCC

B EN C Y=(ABC )·( ABC ) (f)

图题 2.2

电气控制技术习题

2.3 已知电路两个输入信号的波形如图题2.3所示, 信号的 重复频率为1MHz, 每个门的平均延迟时间tpd=20ns。试 画出: (1) 不考虑tpd时的输出波形。 (2)考虑tpd时的输出波形。

R CP S (a) R CP S (d ) Q CP Q “0” Q Q CP “1” R S (b) Q CP Q S (c) Q R Q

1

2

3

4

(e)

图题4.2 同步RS触发器和CP波形

电气控制技术习题

4.3 同步触发器接成图题4.3(a)、 (b)、 (c)、 (d)所示形式,设初 始状态为0,试根据图(e)所示的CP波形画出Qa、Qb、c、Qd的 波形。

电气控制技术习题

第1章 低压电器

• • • • • • • • • • • • • 自测题 一、选择题: 1.胶木闸刀开关安装时,手柄 。 A.向上 B.向下 按钮。 2.在机床上,启动按钮通常采用 A.红色 B.黄色 C.绿色 D.白色 3.胶木闸刀开关接线时,应将电动机引线接在 上。 A.静插座 B.动触片 4.在机订控制线路中起限位保护的电器元件是 。 A.闸刀开关 B.行程开关 C.组合开关 。 5.交流接触器铁芯上嵌有短路环,其作用是 A.短路 B.动作迅速 C.增强吸力 D.减小振动 6.交流接触器除了具有接通和断开主电路和控制电路功能外,还 兼可实现 保护。 • A.短路 B.过载 C.欠压

集成计数器功能描述及说明

集成计数器功能描述及说明一、计数器概述集成计数器具有功能完善、通用性强、功耗低、工作速度快、功能可扩展等许多优点,应用非常广泛。

目前用得最多、性能较好的是高速CMOS集成计数器,其次是TTL计数器。

由于定型产品的种类毕竟有限,就计数进制而言,在集成计数器中,只有二进制和十进制计数两大系列。

因此,学习集成计数器,必须掌握用已有的计数器芯片构成其它任意进制计数器的连接方法。

1、集成同步计数器同步计数器电路复杂,但计数速度快,多用在计算机电路中。

目前生产的同步计数器芯片分为二进制和十进制两种。

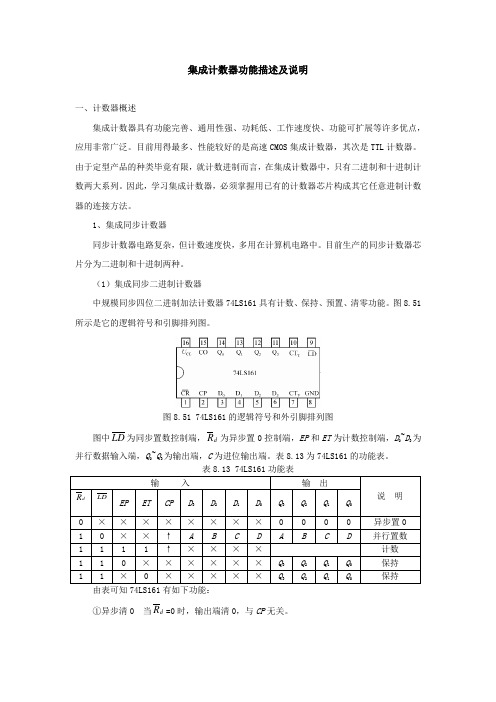

(1)集成同步二进制计数器中规模同步四位二进制加法计数器74LS161具有计数、保持、预置、清零功能。

图8.51所示是它的逻辑符号和引脚排列图。

图8.51 74LS161的逻辑符号和外引脚排列图图中LD为同步置数控制端,d R为异步置0控制端,EP和ET为计数控制端,D0~D3为并行数据输入端,Q0~Q3为输出端,C为进位输出端。

表8.13为74LS161的功能表。

R=0时,输出端清0,与CP无关。

①异步清0 当d②同步并行预置数 d R =1,当LD =0时,在输入端D 3D 2D 1D 0预置某个数据,则在CP 脉冲上升沿的作用下,就将输入端的数据置入计数器。

③保持 d R =1,当=1时,只要EP 和ET 中有一个为低电平,计数器就处于保持状态。

在保持状态下,CP 不起作用。

④计数 d R =1,LD =1,EP =ET =1时,电路为四位二进制加法计数器。

当计到1111时,进位输出端C 送出进位信号(高电平有效),即C =1。

(2)集成同步十进制计数器集成同步十进制加法计数器74LS160的管脚图和功能表与74LS161基本相同,唯一不同的是74LS160是十进制计数器,而74LS161是二进制计数器。

2、集成异步计数器异步计数电路简单,但计数速度慢,多用于仪器、仪表中。

(1)集成计数器74LS290图8.52是二-五-十进制集成计数器74LS290的逻辑结构图。

电子技术及技能训练 习题1-11章

电子技术及技能训练习题(1—11章)习题1单项选择题(1)二极管加正向电压时,其正向是由()。

A 多数载流子扩散形成B 多数载流子漂移形成C 少数载流子漂移形成(2) PN结反向击穿电压的数值增大,()。

A 其反向电流增大B 其反向电流减小C :其反向电流基本不变(3)稳压二极管是利用PN结的()。

A 单向导电性B 反向击穿性C 电容特性(4)变容二极管在电路中使用时,其PN结是()。

A 正向运用B 反向运用(5)当晶体管工作在放大区时,()。

A 发射结和集电结均反偏; B发射结正偏,集电结反偏; C发射结和集电结均正偏;简答题(1)什么是PN结?PN结有什么特性?(2)为什么二极管可以当做一个开关来使用?(3)三极管有哪3种工作状态?各有什么特点?(4)三极管的电流分配关系是怎样的?你如何理解三极管的电流放大作用?(5)三极管共射放大电路中直流β和交流β的含义是什么?它们之间有何关系?(6)场效应管和三极管在性能上有哪些区别?在使用场效应管时,应注意哪些问题?分析题(1)二极管电路如图所示,试判断图中的二极管VD1~VD6是导通还是截止,并求出AO 两端的电压U AO值(设二极管是理想状态。

)。

图题(6)中的图(2)测得放大电路中三极管中的各极电位分别为U1=-9V,U2=-6V,U3=-,试识别管脚,标上e,b,c,并判断三极管是NPN型还是PNP型?是硅管还是锗管?(3)现有3只三极管:甲管=240,I CEO=400;乙管=8,I CEO=2;丙管=60,I CEO=5,其他参数大致相同,分析哪个三极管放大用效果比较好。

习题2选择判断题(1) 在基本放大电路中,基极偏置电阻R b的作用是( )A.放大电流B.调节偏流I BC.防止输入信号交流短路D.把放大了的电流转换成电压(2)对于基本共射放大电路的特点,其错误的结论是()A.输出电压与输入电压相位相同B.输入电阻,输出电阻适中C.电压放大倍数大于1 D.电流放大倍数大于1(3).由NPN型晶体管组成的共射基本放大电路中,若静态工作点I CQ选择过高,容易使电路输出信号产生()失真。

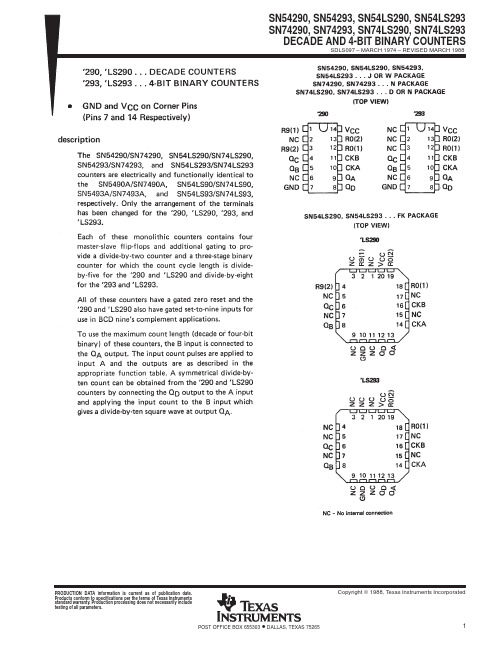

74LS290芯片介绍

Copyright © 1988, Texas Instruments Incorporated PRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instrumentsstandard warranty. Production processing does not necessarily includetesting of all parameters.1POST OFFICE BOX 655303 • DALLAS, TEXAS 752652POST OFFICE BOX 655303 • DALLAS, TEXAS 75265POST OFFICE BOX 655303 • DALLAS, TEXAS 752654POST OFFICE BOX 655303 • DALLAS, TEXAS 752655 POST OFFICE BOX 655303 • DALLAS, TEXAS 752656POST OFFICE BOX 655303 • DALLAS, TEXAS 752657 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments IncorporatedThis datasheet has been downloaded from: Datasheets for electronic components.。

74LS290技术手册

54/74290二,五,十进制计数器 简要说明:290为二,五,十进制计数器,共有54/74290和54/74LS290两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):型号f C P D 54290/74290 42MHz 145mW 54LS290/74LS290 42MHz 45mW 异步清零端MR1,MR2为高电平时,只要置9端MS1,MS2有一个为低电平,就可以完成清零功能。

当MS1,MS2均为高电平时,不管其他输入端状态如何,就可以完成置9功能。

当MR1,MR2中有一个以及MS1,MS2中有一个同时为低电平时,在时钟端/CP0,/CP1脉冲下降沿作用下进行计数操作:a) 十进制计数。

应将/CP1与Q0连接,计数脉冲由/CP0输入。

b) 二、五混合进制计数。

应将/CP0与Q1连接,计数脉冲由/CP1输入。

c) 二分频、五分频计数。

Q0为二分频输出,Q1~Q3为五分频输出。

引出端符号: /CP0二分频时钟输入端(下降沿有效) /CP1 五分频时钟输入端(下降沿有效) Q0~Q3 输出端 MR1,MR2 异步复位端 MS1.MS2 异步置9端 外部管腿图:逻辑图:功能表:极限值:电源电压 …………………………………………. 7V 输入电压54/74290、54/74LS290的/CP0、/CP1…………. 5.5V 54/74290、54/74LS290的MR1,MR2.MS1,MS2. 7V 工作环境温度54XXX …………………………………. -55~125℃ 74XXX …………………………………. 0~70℃ 存储温度 …………………………………………. -65~150℃推荐工作条件:54290/74290 54LS290/74LS290最小 额定 最大 最小 额定 最大 单位54 4.5 5 5.5 4.5 5 5.5电源电压Vcc74 4.75 5 5.25 4.75 5 5.25V 输入高电平电压V iH2 2 V 54 0.8 0.7输入低电平电压V iL74 0.8 0.8V 输出高电平电流I OH-800 -400 uA 54 16 4输出低电平电流I OL74 16 8 mA /CP0 0 32 0 32时钟频率f cp/CP1 0 16 0 16 MHz /CP0 15 15 /CP1 30 30 脉冲宽度t wMR,MS 15 15ns 建立时间t set (MR 、MS 无效)25 25 ns静态特性(TA 为工作环境温度范围)290 LS290参 数 测 试 条 件【1】最小 最大 最小 最大单位I ik =-12mA -1.5V V IK 输入嵌位电压 Vcc=最小I ik =-18mA-1.5 54 2.4 2.5 V OH 输出高电平电压Vcc =最小,V IL =最大,V IH =2V ,I OH =最大 74 2.4 2.7V 54 0.4 0.4 V OL 输出低电平电压Vcc=最小,V IL =最大,V IH =2V,I OL =最大74 0.4 0.5 V V I =5.5V 1MR,MSV I =7V 0.1/CP0 1 0.2I I 最大输入电压时输入电流/CP1Vcc =最大 V I =5.5V 1 0.4 mAMR,MS40 20/CP080 40I IH 输入高电平电流 /CP1Vcc =最大,V IH =2.4V(LS290为2.7V)120 80 uA MR,MS-1.6 -0.4/CP0-3.2 -2.4I IL 输入低电平电流/CP1Vcc =最大,V IL =0.4V -4.8 -3.2mA 54 -20 -57 -20 -100I OS 输出短路电流 Vcc =最大 74 -18 -57 -20 -100mAIcc 电源电流Vcc =最大,MR1,MR2瞬时接4.5V后接地。

集成计数器构成n进制计数器的方法及步骤

标题:集成计数器构成n进制计数器的方法及步骤一、引言计数器是电子系统中的重要组成部分,用于记录时间和事件。

在数字系统中,计数器通常由逻辑门和触发器等基本电路组成。

其中,n进制计数器是指计数器的计数单位采用n位二进制数。

在实际应用中,n进制计数器具有方便的编码和解码功能,因此在许多场合得到广泛应用。

本文将介绍集成计数器构成n进制计数器的方法及步骤。

二、方法及步骤1. 确定计数器的进制首先,需要根据实际应用需求确定计数器的进制,即计数单位采用多少位二进制数。

常见的进制包括二进制、三进制、六进制等。

2. 选择适当的集成计数器芯片根据确定的进制,选择适当的集成计数器芯片。

不同的进制需要不同的芯片,因此需要根据实际需求选择合适的芯片。

目前市面上有多种n进制集成计数器芯片可供选择。

3. 连接电路将所选的集成计数器芯片按照电路图连接至电源、时钟等其他电路部件。

连接时需要注意芯片的输入输出端子,按照说明书正确连接。

同时,还需要考虑时钟信号的频率和相位等问题。

4. 编程控制对于可编程的集成计数器,需要进行编程控制。

根据实际需求,编写相应的程序,将程序下载到计数器芯片中。

通过编程,可以实现计数器的启动、停止、清零等功能。

5. 调试与测试连接好电路并完成编程后,需要对计数器进行调试和测试。

测试时需要注意计数器的计数精度、稳定性和抗干扰能力等指标。

测试通过后,即可投入实际应用。

三、注意事项1. 确保所选的集成计数器芯片符合实际需求,避免不合适的芯片导致电路性能下降。

2. 连接电路时,要严格按照说明书操作,避免出现错误导致电路故障。

3. 调试和测试过程中,要确保测试环境的稳定性和可靠性,避免测试结果失真。

4. 在实际应用中,要根据具体需求对计数器进行配置和调整,以达到最佳性能。

总之,集成计数器构成n进制计数器需要按照一定的方法和步骤进行。

在选择芯片、连接电路、编程控制和调试测试过程中,需要注意相关事项,以确保计数器的性能和稳定性。

计数器逻辑功能和设计

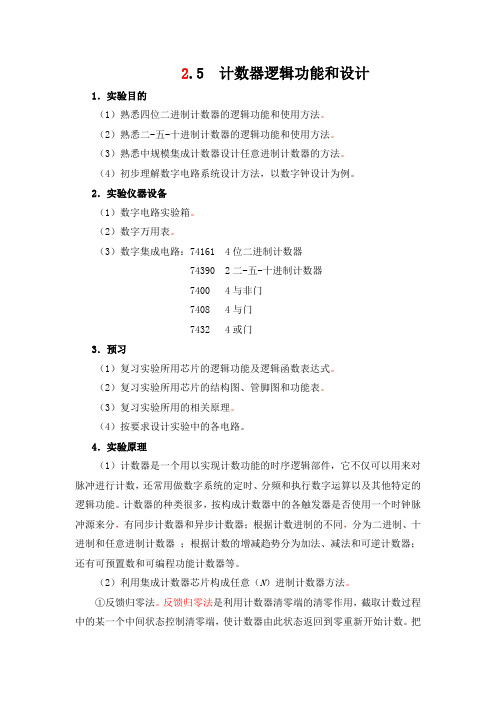

2.5 计数器逻辑功能和设计1.实验目的(1)熟悉四位二进制计数器的逻辑功能和使用方法。

(2)熟悉二-五-十进制计数器的逻辑功能和使用方法。

(3)熟悉中规模集成计数器设计任意进制计数器的方法。

(4)初步理解数字电路系统设计方法,以数字钟设计为例。

2.实验仪器设备(1)数字电路实验箱。

(2)数字万用表。

(3)数字集成电路:74161 4位二进制计数器74390 2二-五-十进制计数器7400 4与非门7408 4与门7432 4或门3.预习(1)复习实验所用芯片的逻辑功能及逻辑函数表达式。

(2)复习实验所用芯片的结构图、管脚图和功能表。

(3)复习实验所用的相关原理。

(4)按要求设计实验中的各电路。

4.实验原理(1)计数器是一个用以实现计数功能的时序逻辑部件,它不仅可以用来对脉冲进行计数,还常用做数字系统的定时、分频和执行数字运算以及其他特定的逻辑功能。

计数器的种类很多,按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器;根据计数进制的不同,分为二进制、十进制和任意进制计数器;根据计数的增减趋势分为加法、减法和可逆计数器;还有可预置数和可编程功能计数器等。

(2)利用集成计数器芯片构成任意(N)进制计数器方法。

①反馈归零法。

反馈归零法是利用计数器清零端的清零作用,截取计数过程中的某一个中间状态控制清零端,使计数器由此状态返回到零重新开始计数。

把模数大的计数器改成模数小的计数器,关键是清零信号的选择。

异步清零方式以N作为清零信号或反馈识别码,其有效循环状态为0~N-1;同步清零方式以N-1作为反馈识别码,其有效循环状态为0~N-1。

还要注意清零端的有效电平,以确定用与门还是与非门来引导。

②反馈置数法。

反馈置数法是利用具有置数功能的计数器,截取从Nb到Na 之间的N个有效状态构成N进制计数器。

其方法是当计数器的状态循环到Na时,由Na构成的反馈信号提供置数指令,由于事先将并行置数数据输入端置成了Nb 的状态,所以置数指令到来时,计数器输出端被置成Nb,再来计数脉冲,计数器在Nb基础上继续计数至Na,又进行新一轮置数、计数,其关键是反馈识别码的确定与芯片的置数方式有关。

74Ls290芯片构成N进制计数器

图5-32(b) 五进制计数器

2019/2/17 7

2.基本工作方式

(3) 8421BCD码十进制计数:将Q0与CP1相连, 计数脉冲CP由CP0输入

计数 顺序 0 1 2 3 4 5 6 7 8 9 10 计 数 器 状 态 Q3 Q2 Q1 Q0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 1 1 1 1 0 0 0 0 0 1 1 0 0 1 1 0 0 0 0 1 0 1 0 1 0 1 0 1 0

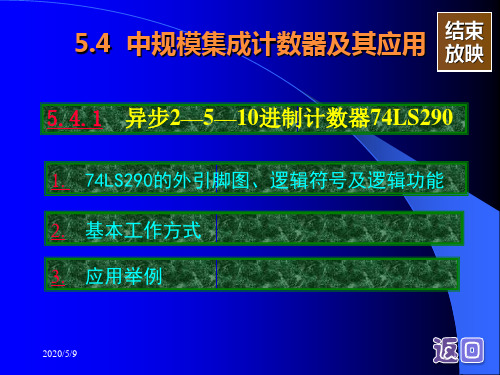

1. 74LS290的外引脚图、逻辑符号及逻辑功能 输出

CP输入

图5-31 74LS290 2-5-10进制计数器

(a) 外引脚图

(b) 逻辑符号

异步 置数

表5-12 74LS290功能表

CP下降 沿有效

2019/2/17

CP1-Q3Q2Q1 5进制

CP0-Q0 2进制

5

2.基本工作方式

(1)二进制计数:将计数脉冲由CP0输入,由 Q0输出

仿真

2019/2/17

图5-34 74LS290构成二十三进制计数器

15

图5-32(c) 8421BCD码 8

2.基本工作方式

(4) 5421BCD码十进制计数:把CP0和Q3相连, 计数脉冲由CP1输入 计数 计 数 器 状 态

顺序 0 1 2 3 4 5 6 7 8 9 10 Q0 Q3 Q2 Q1 0 0 0 0 0 1 1 1 1 1 0 0 0 0 0 1 0 0 0 0 1 0 0 0 1 1 0 0 0 1 1 0 0 0 1 0 1 0 0 1 0 1 0 0

仿真

2019/2/17

图5-33(a)七进制计数器

12

② 构成六进制计数器

电子电工设计实验之31进制设计

31进制设计

1、设计题目:

31进制设计

2 、设计目的:

1 熟悉74LS290的接线

2 熟悉任意进制计数器的工作原理

3、设计原理:

(1)实验电路框图如下:

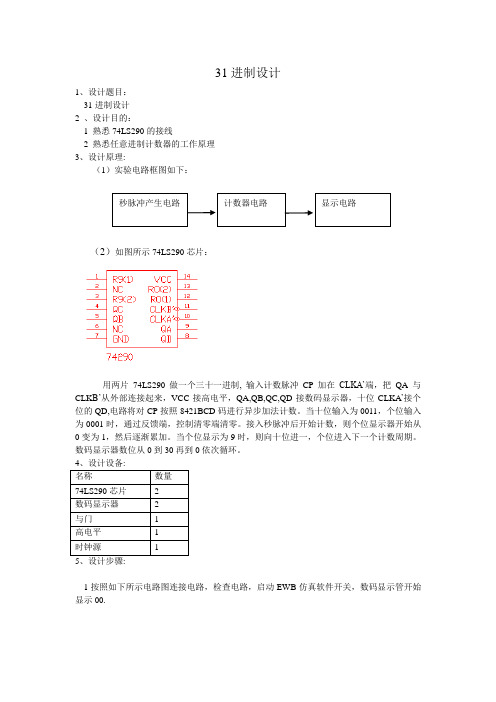

(2)如图所示74LS290芯片:

用两片74LS290做一个三十一进制, 输入计数脉冲CP加在CLKA’端,把QA与CLK B’从外部连接起来,VCC接高电平,QA,QB,QC,QD接数码显示器,十位CLKA’接个位的QD,电路将对CP按照8421BCD码进行异步加法计数。

当十位输入为0011,个位输入为0001时,通过反馈端,控制清零端清零。

接入秒脉冲后开始计数,则个位显示器开始从0变为1,然后逐渐累加。

当个位显示为9时,则向十位进一,个位进入下一个计数周期。

数码显示器数位从0到30再到0依次循环。

5、设计步骤:

1按照如下所示电路图连接电路,检查电路,启动EWB仿真软件开关,数码显示管开始显示00.

2当数码显示管显示数数据到30时,通过74LS290清零法到31时自动清零,31不会显示出来,然后又从00开始显示,依次循环,如图所示。

6、设计分析总结:

通过这次设计实验的学习,让我对学过的理论知识有了进一步的认识,同时也让我注意到理论和实践的联系与区别。

根据显示器特性连接后可实现三十一进制计数器功能,让我们对EWB仿真软件的基本操作和任意进制计数器的工作原理有了进一步的了解,对书本的知

识有了更深的了解。

第三、四节4. 计数器(3)

G1

CP Q Q

1

01

2&

3

4 88 分 频

5

6 CP

7 1 8 2

0 0 0 1 0 0 0 0

3

QC1P B

Q1 Q2 Q3 Q4 S N 7 4 9 0 -2 R 01 R 02

Q Q Q Q

1 2 3 4

C PA 2 S 01 S 02

3

B

QA4 A

1 0

0

G4 1

G2 &

& G3

A

1

0000→0001→0010→0011→ 0000→0001→0010→0011→0100→0101→0110→0111→1000

将接成十进制(5421码)计数 形式(Q1 与CPB 相连),前六 种状态为有效,后四种为无效 状态。显然当第七个CP下降沿 到来后,

RD R01 R02 ( R D1 ) 0

R01=Q1=1,R02=Q3=1

置“0”

进位输出(进位信号下降沿有效)

Q1 Q2 Q3 Q4 CP CPB CPA S 01 S 02 R 01 R 02

J F4 K

Q Q RD

R D2

& CPA R 01 R 02 CPB 2-5-10 进 制 计 数 器 SN7490A

& S 01 S 02

置“1”端S01、S02 SD=RD2=0;

S D S 01 S 02 ( R D 2 )

,只有S01=S02=1时,

SD=0:F4、F1两个JK触发器置“1”; RD2=0:F3、F2两个JK触发器置“0”; 此时:Q4Q3Q2Q1=1001(置成9,8421码)

①与非门G1的输出由1→0。基本RS触发器:A=1→R01、R02, 使 RD R01 R02 ( R D1 ) 0