电子科技大学数字电路期末考试样题

数字电路2011期末考试题-参考解答

电子科技大学2010 -2011学年第二学期期末考试 A 卷课程名称:_数字逻辑设计及应用__ 考试形式:闭卷考试日期:20 11 年7 月7 日考试时长:_120___分钟课程成绩构成:平时30 %,期中30 %,实验0 %,期末40 %本试卷试题由__六___部分构成,共__6___页。

I. Fill your answers in the blanks(2’ X 10=20’)1. A parity circuit with N inputs need N-1XOR gate s. If the number of “1” in an N logic variables set, such as A、B、C、…W, is even number, then__________A B C W⊕⊕⊕⋅⋅⋅⋅⊕=0 .2. A circuit with 4 flip-flops can store 4bit binary numbers, that is, include 16 states at most.3. A modulo-20 counter circuit needs 5 D filp-flops at least. A modulo-288 counter circuit needs 3 4-bit counters of 74x163 at least.4. A 8-bit ring counter has 8 normal states. If we want to realize the same number normal states, we need a 4bit twisted-ring counter.5. If the input is 10000000 of an 8 bit DAC, the corresponding output is 5v. Then an input is 00000001 to the DAC, the corresponding output is 5/128 (0.0391) V; if an input is 10001000, the corresponding DAC output is 5.3125V.II. Please select the only one correct answer in the following questions.(2’ X 5=10)B ) chips of 4K ⨯4 bits RAM to form a 16 K ⨯ 8 bits RAM.A) 2 B) 8 C) 4 D) 162. To design a "01101100" serial sequence generator by shift registers, we need a( A)-bit shift register as least.A) 5 B) 4 C) 3 D) 63. For the following latches or flip-flops, ( B) can be used to form shift register.A) S-R latch B) master-slave flip-flop C) S-R latch with enable D) S’-R’ latch4. Which of the following statements is correct? ( C )A) The outputs of a Moore machine depend on inputs as well as the states.B) The outputs of a Mealy machine depend only on the states.C) The outputs of a Mealy machine depend on inputs as well as the states. D) A), B), C) are wrong.5. There is a state/output table of a sequential machine as the table 1, what the input sequences isdetected? ( D )A) 11110 B) 11010 C) 10010 D) 10110Table 1III.Analyze the sequential-circuit as shown in figure 1. [15’]1. Write out the excitation equations, transitionequations and output equation. [5’]2. Assume the initial state is Q 2Q 1=00, complete thetiming diagram for Q 2 ,Q 1 and Z.( Don ’t need consider propagation delay of each component)[10’]Figure-1解答:激励方程: D 1=Q 1⊕Q 2,D 2= Q /1+ Q /2转移方程:Q 1 *= D 1=Q 1⊕Q 2,Q 2 *=D 2= Q /1+ Q /2 输出方程:Z= Q 1•Q 2IV. Design a Mealy sequential detector with one input x and one output z. If and only if xdescribe the state meaning and finish the state/output table. [15] Example : x :0 1 0 1 1 1 1 0 0 1 1 0 0 1 1 1 1 1 z :0 0 0 0 0 0 1 0 0 1 0 0 0 1 0 0 1 1XState meaningS 0 1 Initial A A,0 B,0 Received 1 B C,0 D,0 Received 10 C E,0 B,0 Received 11 D C,0 F,0 Received 100 E A,0 B,1 Received 111 F C,0F,1S*,ZV. Analyze the circuit as shown below, which contains a 74x163 4-bit binary counter, a 74x138[15’] ’ output F. [5’]2. Write out the sequence of states for the 74x161 in the circuit. [7’]3. Describe the modulus(模) of the circuit. [3’]解答:F=D2=Y6/=(QDQCQBQA /)/ 状态序列:0,1,2,3,4,5,6,7,8,9,10,11,12,13,14,0,1,2,… M=15VI.the state transition sequence is 0→2→4→1→3→0→…with the binary code. 1. Fill out the transition/output table. [8’]2. Write out the excitation equations and output equation. [4’]3. List the complete transition/output table, and check the self-correct. [3’] transition/output table : 74X161的功能表输入 当前状态 下一状态 输出CLR_L LD_L ENT ENP QD QC QB QA QD* QC* QB* QA* RCO 0 X X X X X X X 0 0 0 0 1 0 X X X X X X D C B A 1 1 0 X X X X X QD QC QB QA 1 1 X 0 X X X X QD QC QB QA 1 1 1 1 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 1 0 0 1 0 1 1 1 1 0 0 1 0 0 0 1 1 1 1 1 1 0 0 1 1 0 1 0 0complete transition/output table:输出方程:Z=Q1Q0检查自启动:当Q2Q1Q0=101,可得下一状态为001;当Q2Q1Q0=110,可得下一状态为101;当Q2Q1Q0=111,可得下一状态为001。

电子科大模电期末真题10~11.doc

电子科大模电期末真题10~11学院___________________ 系别____________ 班次_____________ 学号__________ 姓名________________………….……密…..……….封……..……线………..…以………..…内………....答…………...题…………..无…….….效…..………………..电子科技大学二零一零至二零一一学年第 1 学期期末考试模拟电路基础课程考试题A卷(120 分钟)考试形式:开卷考试日期2011年1 月 5 日课程成绩构成:平时20 分,期中20 分,实验0 分,期末60 分一二三四五六七八九十合计复核人签名得分签名一、填空题(共30分,共 15个空格,每个空格2 分)1、共发射极放大器(NPN管),若静态工作点设置偏高,可能产生_饱和__失真,此时集电极电流会出现__上___(上、下)削峰失真。

2、某晶体管的极限参数P CM = 200 mW,I CM = 100 mA,U(BR)CEO = 30 V,若它的工作电压U CE为10 V,则工作电流不得超过20 mA;若工作电流I C = 1 mA,则工作电压不得超过30 V。

4、电路及直流测试结果如图1所示,分别指出它们工作在下列三个区中的哪一个区(恒流区、夹断区、可变电阻区)。

得图1(a) 恒流区 ; (b) 可变电阻区 。

5、由三端集成稳压器构成的直流稳压电路如图2所示。

已知W7805的输出电压为5V ,I Q =10 mA ,晶体管的β=50,|U BE |=0.7 V ,电路的输入电压U I =16 V ,三极管处于放大 (放大,饱和,截止)状态, R 1上的电压为 5.7 V ,输出电压U o 为 9 V 。

图26、设图3中A 均为理想运放,请求出各电路的输出电压值。

U 01= 6 V; U 02= 6 V; U 03= 4 V; U 04= 10 V; U 05= 2 V; U 06= 2 V 。

电子科大数字电路期末试题半期测验

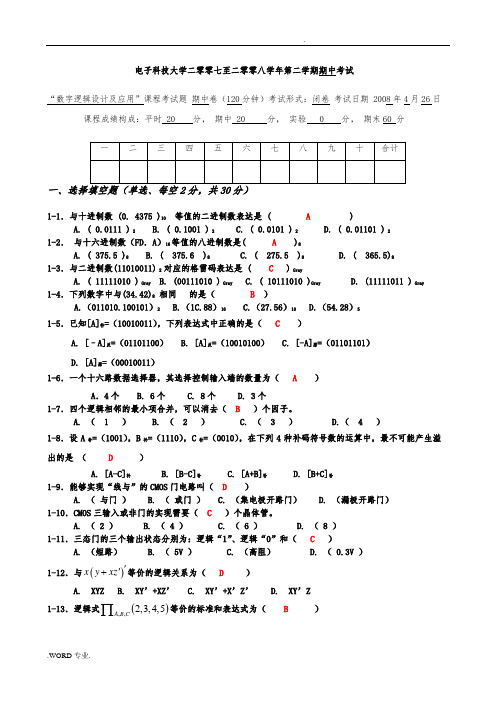

电子科大数字电路期末试题半期测验————————————————————————————————作者:————————————————————————————————日期:电子科技大学二零零七至二零零八学年第二学期期中考试“数字逻辑设计及应用”课程考试题 期中卷(120分钟)考试形式:闭卷 考试日期 2008年4月26日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末60 分一 二 三 四 五 六 七 八 九 十 合计一、选择填空题(单选、每空2分,共30分)1-1.与十进制数 (0. 4375 )10 等值的二进制数表达是 ( A ) A. ( 0.0111 ) 2 B. ( 0.1001 ) 2 C. ( 0.0101 ) 2 D. ( 0.01101 ) 2 1-2. 与十六进制数(FD .A )16等值的八进制数是( A )8A. ( 375.5 )8B. ( 375.6 )8C. ( 275.5 )8D. ( 365.5)8 1-3.与二进制数(11010011) 2 对应的格雷码表达是 ( C ) GrayA. ( 11111010 ) GrayB. (00111010 ) GrayC. ( 10111010 )GrayD. (11111011 ) Gray 1-4.下列数字中与(34.42)8 相同 的是( B )A.(011010.100101)2B.(1C.88)16 C.(27.56)10D.(54.28)5 1-5.已知[A]补=(10010011),下列表达式中正确的是( C )A. [–A]反=(01101100)B. [A]反=(10010100)C. [-A]原=(01101101)D. [A]原=(00010011)1-6.一个十六路数据选择器,其选择控制输入端的数量为( A )A .4个 B. 6个 C. 8个 D. 3个1-7.四个逻辑相邻的最小项合并,可以消去( B )个因子。

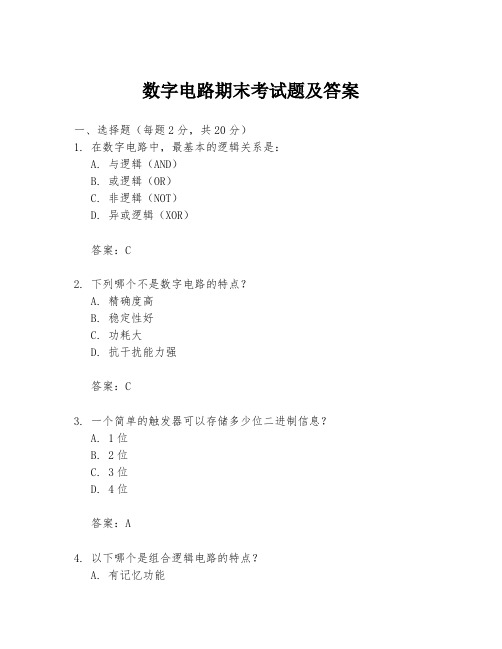

数字电路期末考试题及答案

数字电路期末考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是:A. 与逻辑(AND)B. 或逻辑(OR)C. 非逻辑(NOT)D. 异或逻辑(XOR)答案:C2. 下列哪个不是数字电路的特点?A. 精确度高B. 稳定性好C. 功耗大D. 抗干扰能力强答案:C3. 一个简单的触发器可以存储多少位二进制信息?A. 1位B. 2位C. 3位D. 4位答案:A4. 以下哪个是组合逻辑电路的特点?A. 有记忆功能B. 无记忆功能C. 可以进行算术运算D. 可以进行逻辑运算答案:B5. 在数字电路中,同步计数器与异步计数器的主要区别是:A. 同步计数器速度更快B. 同步计数器结构更复杂C. 同步计数器计数更准确D. 异步计数器计数更准确答案:A6. 一个4位二进制计数器最多能计数到:A. 15B. 16C. 8D. 4答案:B7. 以下哪个是数字电路中常用的存储元件?A. 电阻B. 电容C. 电感D. 晶体管答案:D8. 以下哪个不是数字电路中的逻辑门?A. NANDB. NORC. XORD. TRIAC答案:D9. 一个完整的数字电路设计流程包括以下哪些步骤?A. 需求分析B. 电路设计C. 仿真测试D. 所有选项答案:D10. 以下哪个是数字电路中的时序逻辑电路?A. 门电路B. 触发器C. 运算放大器D. 模数转换器答案:B二、简答题(每题5分,共20分)1. 简述数字电路与模拟电路的区别。

答案:数字电路主要处理离散的数字信号,具有逻辑功能,而模拟电路处理连续的模拟信号,主要用于信号放大、滤波等。

2. 解释什么是触发器,并说明其在数字电路中的作用。

答案:触发器是一种具有记忆功能的逻辑电路,能够存储一位二进制信息。

在数字电路中,触发器用于存储数据,实现计数、定时等功能。

3. 什么是组合逻辑电路?请举例说明。

答案:组合逻辑电路是由逻辑门组成的电路,其输出只依赖于当前的输入状态,不具有记忆功能。

电子科大数字电路,期末试题101102半期考试试卷-答案

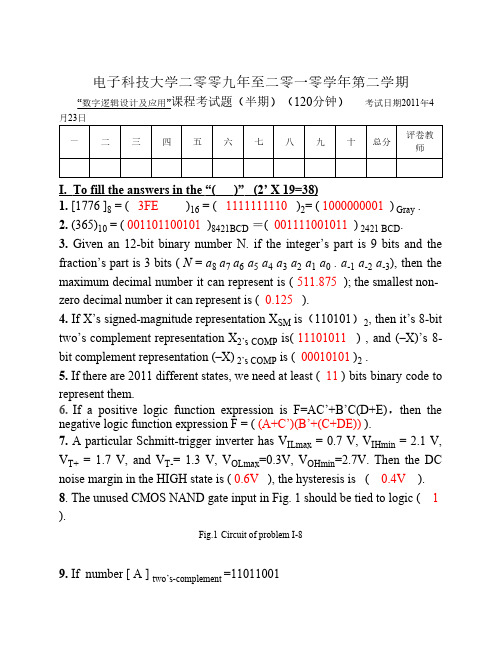

电子科技大学二零零九年至二零一零学年第二学期“数字逻辑设计及应用”课程考试题(半期)(120分钟)考试日期2011年4月23日一二三四五六七八九十总分评卷教师I. To fill the answers in the “( )” (2’ X 19=38)1. [1776 ]8 = ( 3FE )16 = ( 1111111110 )2= ( 1000000001 ) Gray .2. (365)10 = ( 001101100101 )8421BCD=( 001111001011 ) 2421 BCD.3.Given an 12-bit binary number N. if the integer’s part is 9 bits and the fraction’s part is 3 bits ( N = a8 a7 a6 a5 a4 a3 a2 a1 a0 . a-1 a-2 a-3), then the maximum decimal number it can represent is ( 511.875 ); the smallest non-zero decimal number it can represent is ( 0.125 ).4. If X’s signed-magnitude representation X SM is(110101)2, then it’s 8-bit two’s complement representation X2’s COMP is( 11101011 ) , and (–X)’s 8-bit complement representation (–X) 2’s COMP is ( 00010101 )2 .5. If there are 2011 different states, we need at least ( 11 ) bits binary code to represent them.6.If a positive logic function expression is F=AC’+B’C(D+E),then the negative logic function expression F = ( (A+C’)(B’+(C+DE)) ).7. A particular Schmitt-trigger inverter has V ILmax = 0.7 V, V IHmin = 2.1 V, V T+= 1.7 V, and V T-= 1.3 V, V OLmax=0.3V, V OHmin=2.7V. Then the DC noise margin in the HIGH state is ( 0.6V ), the hysteresis is ( 0.4V ). 8.The unused CMOS NAND gate input in Fig. 1 should be tied to logic ( 1 ).Fig.1Circuit of problem I-89. If number [ A ] two’s-complement =11011001and [ B] two’s-complement=10011101 , calculate[-A-B ]two’s-complement, [-A+B ]two’s-complement and indicate whether or not overflow occurs.[-A-B ] two’s-complement=[ 10001010 ], overflow: [ yes ][-A+B ] two’s-complement=[ 11000100 ], overflow: [ no ].10.The following logic diagram Fig.2 implements a function of 3-variable with a 74138. The logic function can be expressed as F (A,B,C) = ∑A,B,C ( 0,1,2 ).Fig.2 Circuit of problem I-10II. There is only one correct answer in the following questions.(3’ X 9 = 27)1. Which of the following Boolean equations is NOT correct? ( B )A) A+0=A B) A1 = AC) D)2. Suppose A2’s COMP =(1011),B2’s COMP =(1010),C2’s COMP =(0010). In the following equations, the most unlikely to produce overflow is( C )。

最新电子科大数字电路,期末试题-2006-1数电半期考试

电子科技大学二零零五至二零零六学年第二学期期中考试“数字逻辑设计及应用”课程考试题 期中卷(120分钟)考试形式:闭卷 考试日期 2006年4月22日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末60 分一、填空题(每空1分,共15分)1、( 323 )10 =( 101000011 ) 22、(0. 4375 )10 =( 0.0111 ) 23、(1101.0011) 2 = ( 13.1875 )104、(FD .A )16 = ( 11110000.1010 ) 2= ( 360.50 )85、( 4531 )10 = ( 0100 0101 0011 0001 ) 8421BCD 。

6、写出与下列十进制数对应的8-bit 原码(signed-magnitude),补码(two ’s-complement)和反码 (one ’s-complement)表达:7、已知二进制数 A = 10110100,对应的格雷码(GRAY CODE )表达为( 1110 1110 ) 8、与非逻辑门电路的未用输入端应接在( 高电平或某一个输入信号端 )上。

9、已知二进制数 A 的补码为:[A]补= 10110100,求 [-A]补=( 01001100 )二、填空题(每空3分,共30分)1、已知一个函数的积之和(与或式, The sum of productions )列表表达式为 F =∑ABC (1,4,5,6,7),问与其对应的最简积之和表达式为:F =( A + B ’C )。

2、对于按照逻辑式 F AC BC '=+ 实现的电路,存在静态( 1 )型冒险。

3、四变量逻辑函数F = ∑ABCD (2,4,5,7,9,14)的反函数 F ’=∏ABCD ( 2,4,5,7,9,14 )。

4、已知带符号的二进制数 X1 = +1110 ,X2 = -1011,求以下的表达,并要求字长为8位。

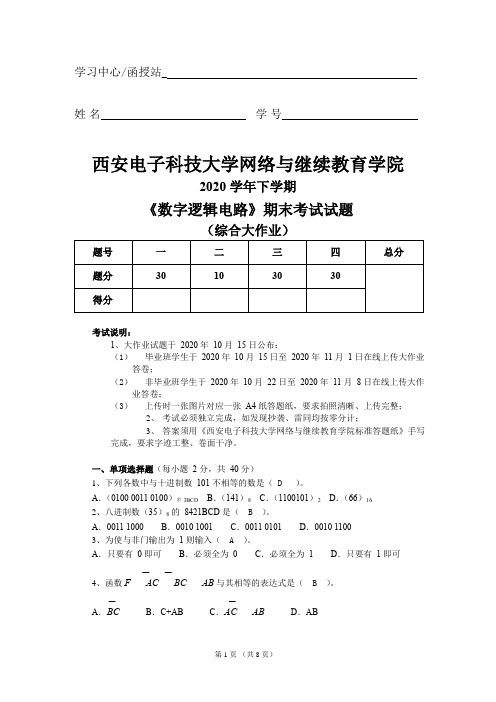

2020秋西安电子科技大学《数字逻辑电路》大作业期末试题及答案

学习中心/函授站_姓名学号西安电子科技大学网络与继续教育学院2020 学年下学期《数字逻辑电路》期末考试试题(综合大作业)题号一二三四总分题分30 10 30 30得分考试说明:1、大作业试题于2020 年10 月15 日公布:(1)毕业班学生于2020 年10 月15 日至2020 年11 月1 日在线上传大作业答卷;(2)非毕业班学生于2020 年10 月22 日至2020 年11 月8 日在线上传大作业答卷;(3)上传时一张图片对应一张A4 纸答题纸,要求拍照清晰、上传完整;2、考试必须独立完成,如发现抄袭、雷同均按零分计;3、答案须用《西安电子科技大学网络与继续教育学院标准答题纸》手写完成,要求字迹工整、卷面干净。

一、单项选择题(每小题2 分,共40 分)1、下列各数中与十进制数101 不相等的数是( D )。

A.(0100 0011 0100)余3BCD B.(141)8C.(1100101)2D.(66)162、八进制数(35)8的8421BCD 是( B )。

A.0011 1000B.0010 1001C.0011 0101D.0010 11003、为使与非门输出为1 则输入( A )。

A.只要有0 即可B.必须全为0C.必须全为1D.只要有1 即可4、函数F AC BC AB与其相等的表达式是( B )。

A.BC B.C+AB C.AC AB D.AB5、使函数F AB AC BC 等于 0 的输入 ABC 的组合是( C )。

A .ABC=111 B .ABC=110 C .ABC=100 D .ABC=0116、四变量的最小项ABCD 的逻辑相邻项是( A )。

A .ABCDB .ABCDC .ABCD D .ABCD 7、函数 F ABC B .C (A D )BC 的对偶式是( C )。

A .G (A B C )(B C )(AD B C )B .G A BC (B C )ADB CC .G A B C (B C )(AD B C )D .G A BC (B C )AD B C8、FA B C ADE BDE ABC 的最简式为( A )。

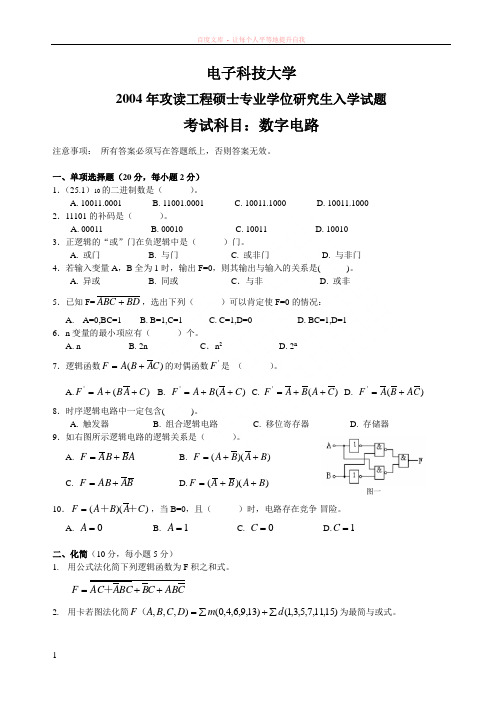

电子科技大学年数字电路试题

电子科技大学 2004年攻读工程硕士专业学位研究生入学试题 考试科目:数字电路 注意事项: 所有答案必须写在答题纸上,否则答案无效。

一、单项选择题(20分,每小题2分)1.(25.1)10的二进制数是( )。

A. 10011.0001B. 11001.0001C. 10011.1000D. 10011.10002.11101的补码是( )。

A. 00011B. 00010C. 10011D. 100103.正逻辑的“或”门在负逻辑中是( )门。

A. 或门B. 与门C. 或非门D. 与非门4.若输入变量A ,B 全为1时,输出F=0,则其输出与输入的关系是( )。

A. 异或B. 同或 C .与非 D. 或非5.已知F=BD ABC +,选出下列( )可以肯定使F=0的情况:A. A=0,BC=1B. B=1,C=1C. C=1,D=0D. BC=1,D=16.n 变量的最小项应有( )个。

A. nB. 2n C .n 2 D. 2n7.逻辑函数)(C A B A F +=的对偶函数'F 是 ( )。

A.)('C A B A F ++=B. )('C A B A F ++=C. )('C A B A F ++=D. )('C A B A F +=8.时序逻辑电路中一定包含( )。

A. 触发器B. 组合逻辑电路C. 移位寄存器D. 存储器 9.如右图所示逻辑电路的逻辑关系是( )。

A. A B B A F +=B. ))((B A B A F ++=C. B A AB F +=D.))((B A B A F ++= 10.))((C AB A F ++=,当B=0,且( )时,电路存在竞争-冒险。

A. 0=A B. 1=A C. 0=C D.1=C二、化简(10分,每小题5分)1. 用公式法化简下列逻辑函数为F 积之和式。

C AB C B BC A AC F ++=+2. 用卡若图法化简)15,11,7,5,3,1()13,9,6,4,0(),,,d m D C B A F ∑+∑=(为最简与或式。

电子科大数字电路_期末试题0708_2半期考试

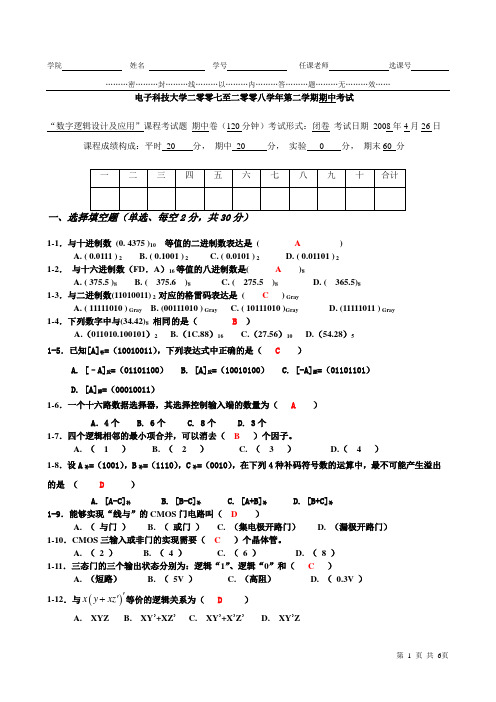

电子科技大学二零零七至二零零八学年第二学期期中考试“数字逻辑设计及应用”课程考试题 期中卷(120分钟)考试形式:闭卷 考试日期 2008年4月26日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末60 分1-1.与十进制数 (0. 4375 )10 等值的二进制数表达是 ( A )A. ( 0.0111 ) 2B. ( 0.1001 ) 2C. ( 0.0101 ) 2D. ( 0.01101 ) 2 1-2. 与十六进制数(FD .A )16等值的八进制数是( A )8A. ( 375.5 )8B. ( 375.6 )8C. ( 275.5 )8D. ( 365.5)8 1-3.与二进制数(11010011) 2 对应的格雷码表达是 ( C ) GrayA. ( 11111010 ) GrayB. (00111010 ) GrayC. ( 10111010 )GrayD. (11111011 ) Gray 1-4.下列数字中与(34.42)8 相同 的是( B )A.(011010.100101)2B.(1C.88)16 C.(27.56)10D.(54.28)5 1-5.已知[A]补=(10010011),下列表达式中正确的是( C )A. [–A]反=(01101100)B. [A]反=(10010100)C. [-A]原=(01101101)D. [A]原=(00010011)1-6.一个十六路数据选择器,其选择控制输入端的数量为( A )A .4个 B. 6个 C. 8个 D. 3个1-7.四个逻辑相邻的最小项合并,可以消去( B )个因子。

A. ( 1 )B. ( 2 )C. ( 3 )D.( 4 )1-8.设A 补=(1001),B 补=(1110),C 补=(0010),在下列4种补码符号数的运算中,最不可能产生溢出的是 ( D )A. [A-C]补B. [B-C]补C. [A+B]补D. [B+C]补 1-9.能够实现“线与”的CMOS 门电路叫( D )A. ( 与门 )B. ( 或门 )C. (集电极开路门)D. (漏极开路门) 1-10.CMOS 三输入或非门的实现需要( C )个晶体管。

电子科大数字电路,期末试题0708-2半期考试

………密………封………线………以………内………答………题………无………效……电子科技大学二零零七至二零零八学年第二学期期中考试“数字逻辑设计及应用”课程考试题 期中卷(120分钟)考试形式:闭卷 考试日期 2008年4月26日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末60 分1-1.与十进制数 (0. 4375 )10 等值的二进制数表达是 ( A ) A. ( 0.0111 ) 2 B. ( 0.1001 ) 2 C. ( 0.0101 ) 2 D. ( 0.01101 ) 2 1-2. 与十六进制数(FD .A )16等值的八进制数是( A )8A. ( 375.5 )8B. ( 375.6 )8C. ( 275.5 )8D. ( 365.5)8 1-3.与二进制数(11010011) 2 对应的格雷码表达是 ( C ) GrayA. ( 11111010 ) GrayB. (00111010 ) GrayC. ( 10111010 )GrayD. (11111011 ) Gray 1-4.下列数字中与(34.42)8 相同 的是( B )A.(011010.100101)2B.(1C.88)16 C.(27.56)10D.(54.28)5 1-5.已知[A]补=(10010011),下列表达式中正确的是( C )A. [–A]反=(01101100)B. [A]反=(10010100)C. [-A]原=(01101101)D. [A]原=(00010011)1-6.一个十六路数据选择器,其选择控制输入端的数量为( A )A .4个 B. 6个 C. 8个 D. 3个1-7.四个逻辑相邻的最小项合并,可以消去( B )个因子。

A. ( 1 )B. ( 2 )C. ( 3 )D.( 4 )1-8.设A 补=(1001),B 补=(1110),C 补=(0010),在下列4种补码符号数的运算中,最不可能产生溢出的是 ( D )A. [A-C]补B. [B-C]补C. [A+B]补D. [B+C]补 1-9.能够实现“线与”的CMOS 门电路叫( D )A. ( 与门 )B. ( 或门 )C. (集电极开路门)D. (漏极开路门) 1-10.CMOS 三输入或非门的实现需要( C )个晶体管。

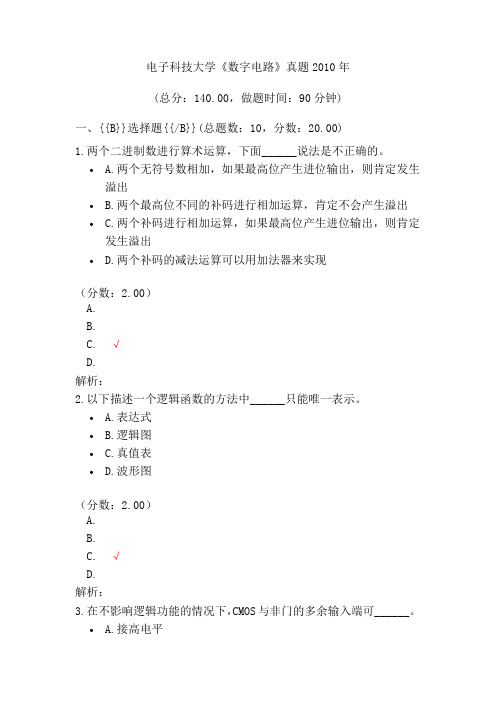

电子科技大学《数字电路》真题2010年

电子科技大学《数字电路》真题2010年(总分:140.00,做题时间:90分钟)一、{{B}}选择题{{/B}}(总题数:10,分数:20.00)1.两个二进制数进行算术运算,下面______说法是不正确的。

• A.两个无符号数相加,如果最高位产生进位输出,则肯定发生溢出• B.两个最高位不同的补码进行相加运算,肯定不会产生溢出• C.两个补码进行相加运算,如果最高位产生进位输出,则肯定发生溢出• D.两个补码的减法运算可以用加法器来实现(分数:2.00)A.B.C. √D.解析:2.以下描述一个逻辑函数的方法中______只能唯一表示。

• A.表达式• B.逻辑图• C.真值表• D.波形图(分数:2.00)A.B.C. √D.解析:3.在不影响逻辑功能的情况下,CMOS与非门的多余输入端可______。

• A.接高电平• B.接低电平• C.悬空• D.通过电阻接地(分数:2.00)A. √B.C.D.解析:4.欲产生序列信号11010111,则至少需要______级触发器。

• A.2• B.3• C.4• D.5(分数:2.00)A.B. √C.D.解析:5.一个8位二进制减法计数器,初始状态为00000000,问经过268个输入脉冲后,此计数器的状态为______。

• A.11001111• B.11110100• C.11110010• D.11110011(分数:2.00)A.B. √C.D.解析:6.为构成4096×16的RAM区,共需1024×4位的RAM芯片______片。

• A.64• B.8• C.16• D.32(分数:2.00)A.B.C. √D.解析:7.逻辑函数F1=∑A,B,C,D(2,3,5,8,11,13)和F2=∏A,B,C,D(2,4,7,10,12,13)之间满足______关系。

• A.对偶• B.相等• C.香农展开• D.反演(分数:2.00)A. √B.C.D.解析:8.移位寄存器由8级触发器组成,用它构成的扭环形计数器具有______种有效状态;用它构成的环形计数器具有______种有效状态,构成线性反馈移位寄存器具有______种有效状态。

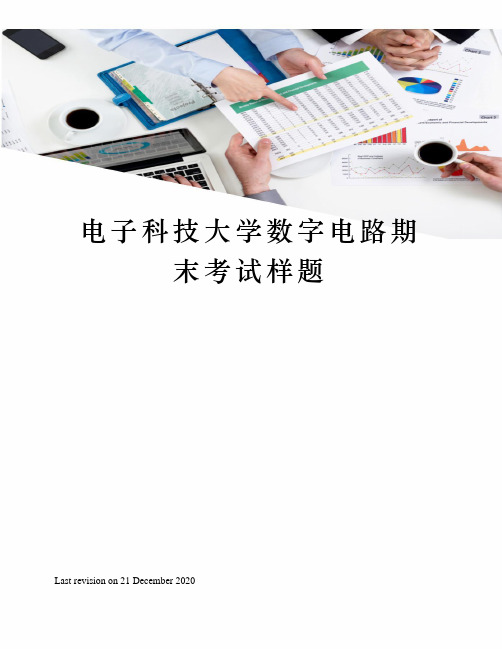

电子科技大学数字电路期末考试样题

电子科技大学数字电路期末考试样题Last revision on 21 December 2020一、填空题1.五个变量构成的所有最小项之和等于 ( )。

2.已知某数的二进制原码表示为 ( 110110) 2 , 则其对应的8-bit 补码表示为 ( )2。

3.已知∑=C B A F ,,)3,0(,则∑='C B A F ,,( )。

4.要使D 触发器按'*Q Q =工作,则D 触发器的输入D=( )。

5.用移位寄存器产生1101010序列,至少需要( )位的移位寄存器。

二、单项选择题:1. 若要将一异或门当作反相器(非门)使用,则输入端A 、B 端的连接方式是( )。

A. A 或B 中有一个接“0”B. A 或B 中有一个接“1”C. A 和B 并联使用D. 不能实现 2.组合电路的竞争冒险是由于( )引起的。

A. 电路不是最简B. 电路有多个输出C. 电路中使用不同的门电路D. 电路中存在延时3.某一逻辑函数真值表确定后,下面描述该函数逻辑功能的表达式中,具有唯一性的是( )。

A .该逻辑函数的最简与或式B .该逻辑函数的积之和标准型C .该逻辑函数的最简或与式D .该逻辑函数的和之积式4.若最简状态转换表中,状态数为n ,则所需状态变量数K 为 ( )的整数.0000010110101111图 A .n K 2log = B .n K 2log < C . n K 2log ≥ D . n K 2log ≤5.某计数器的状态转换图如图1所示,其该计数器的模为( )。

A . 八 B. 五 C. 四 D. 三三、 组合电路分析:1.求逻辑函数 Z Y X Y X Z X F ⋅'⋅+⋅+⋅'= 的最简积之和表达式。

2.已知逻辑函数∑=Z Y X F ,,)7,5,1(, 请写出该函数的标准和(最小项之和)表达式: 3.找出逻辑表达式X W Y W F ⋅+'⋅'=对应的电路的所有静态冒险。

电子科大数电期末考试样题13

电⼦科⼤数电期末考试样题13I. Fill out your answers in the blanks (3’ X 10=30’)1. If a 74x138 binary decoder has 110 on its inputs CBA, the active LOW output Y5 should be ( 1 or high ).2. If the next state of the unused states are marked as “don’t-cares” when designing a finite state machine, this approach is called minimal ( cost ) approach.3.The RCO_L of 4-bit counter 74x169 is ( 0 or low ) when counting to 0000 in decreasing order.4. To design a "001010" serial sequence generator by shift registers, the shift register should need ( 4 ) bit at least.5. One state transition equation is Q*=JQ’+K’Q. If we use T flip-flop with enable to complete the equation,the enable input of T flip-flop should have the function EN=( JQ’+KQ ).6. A 4-bit Binary counter can have ( 16 ) normal states at most, 4-bit Johnson counter with no self-correction can have ( 8 ) normal states, 4-bit linear feedback shift-register (LFSR) counter with self-correction can have (16 ) normal states.7. If we use a ROM, whose capacity is 16 × 4 bits, to construct a 4-bit binary code to gray code converter, when the address inputs are 1001, ( 1101 ) will be the output.8. When the input is 10000000 of an 8 bit DAC, the corresponding output voltage is 2V. The output voltage is ( 3.98 ) V when the input is 11111111.II. Please select the only one correct answer in the following questions.(2’ X 5=10’)1. If a 74x85 magnitude comparator has ALTBIN=1, AGTBIN=0, AEQBIN=0, A3A2A1A0=1101, B3B2B1B0=0111 on its inputs, the outputs are ( D ).A) ALTBOUT=0, AEQBOUT=0, AGTBOUT=0 B) ALTBOUT=1, AEQBOUT=0, AGTBOUT=0C) ALTBOUT=1, AEQBOUT=0, AGTBOUT=1 D) ALTBOUT=0, AEQBOUT=0, AGTBOUT=12. As shown in Figure 1, what would the outputs of the 4-bit adder 74x283 be ( B ) when A3A2A1A0=0100, B3B2B1B0=1110 and S/A=1.A) C4=1, S3S2S1S0=0010 B) C4=0, S3S2S1S0=0110 C) C4=0, S3S2S1S0=1010D) C4=0, S3S2S1S0=1110Figure 13. Which of the following statements is INCORRECT? ( A )A) A D latch is edge triggered and it will follow the input as long as the control input C is activelow.B) A D flip flop is edge triggered and its output will not change until the edge of the controllingCLK signal.C) An S-R latch may go into metastable state if both S and R are changing from 11 to 00simultaneously.D) The pulse applying to any input of an S -R latch must meet the minimum pulse width requirement.4. The capacity of a memory that has 13 bits address bus and can store 8 bits at each address is ( B ).A) 8192 B) 65536 C) 104 D) 2565. Which state in Figure 2 is NOT ambiguous ( C ).A) A B) B C) C and D D) CFigure 2III. Analyze the sequential-circuit as shown in Figure 3,D Flip-Flop with asynchronous preset and clear inputs. [15’]1.Write out the excitation equations, transition equations and output equation. [5’]2.Assume the initial state Q2Q1=00, complete the timing diagram for Q2 ,Q1 and Z. [10’]Figure 3激励⽅程: D1=Q2/,D2= Q1转移⽅程:Q1*= D1=Q2/,Q2*=D2= Q1输出⽅程:Z= (CLK+Q2)/IV. Analyze the sequential-circuit as shown below, which contains two 74x163 4-bit binary counter. [15’]1. Write out the logic expression LD_L for U1 and CLR_L for U2.[4’]2. Assume the initial state is 310, write out the state sequence for the circuit. [8’]3. Describe the modulus for the circuit. [3’]1. LD_L=Q 3/,CLR_L=(Q 5Q 4Q 3)/2. 状态序列:⼗六进制数表⽰:03,...08,13,...18,23,...28,33,...38,03, (08)或⼗进制数表⽰:3,…8,19,…24,35,…40,51,…56,3,…8[8’]3. m=24V . Design a sequence signal generator with self-correcting to generate a serial output sequence of 101100, using a 74x194 and a 74x151.[15’] 1. List the transition table .[4’] 2. Write out the canonical sum of feedbackfunction LIN.[[4’] 3. Draw the circuit diagram.[7’]1. 转移表2. 反馈函数LIN=D 0=∑m (0,2,4,5)3. 电路图。

电子科技大学数字电路2010期末考试题和答案

电子科技大学二零零九至二零一零学年第 二 学期期 末 考试数字逻辑设计及应用 课程考试题 A 卷(120分钟)考试形式:闭卷 考试日期2010年7月12日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末 60 分一、To fill your answers in the blanks (1’×25)1. If [X]10= - 110, then [X]two's-complement =[ 10010010 ]2,[X]one's-complement =[ 10010001 ]2. (Assumed the number system is 8-bit long) 2. Performing the following number system conversions: A. [10101100]2=[ 000111010010 ]2421B. [1625]10=[]excess-3C. [ 1010011 ]GRAY =[10011000 ]8421BCD3. If ∑=C B A F ,,)6,3,2,1(, then F D ∑=C B A ,,( 1,4,5,6 )=C B A ,,∏(0,2,3,7 ).4. If the parameters of 74LS-series are defined as follows: V OL max = 0.5 V , V OH min = 2.7 V , V IL max = 0.8 V , V IH min = 2.0 V , then the low-state DC noise margin is ,the high-state DC noise margin is .5. Assigning 0 to Low and 1 to High is called positive logic. A CMOS XOR gate in positive logic is called XNOR gate in negative logic.6. A sequential circuit whose output depends on the state alone is called a Moore machine.7. To design a "001010" serial sequence generator by shift registers, the shift register should need 4 bit as least.8. If we use the simplest state assignment method for 130 sates, then we need at least 8 state variables.9. One state transition equation is Q*=JQ'+K'Q. If we use D flip-flop to complete the equation, theD input terminal of D flip-flop should be have the function D= JQ'+K'Q.10.Which state in Fig. 1 is ambiguous D11.A CMOS circuit is shown as Fig. 2, its logic function z= A’B’+ABFig. 1 Fig. 212.If number [A]two's-complement =01101010 and [B]one's-complement =1001, calculate [A-B]two's-complement and indicate whether or not overflow occurs.(Assumed the number system is 8-bit long)[A-B]two's-complement = 01110000, overflow no13. If a RAM’s capacity is 16K words × 8 bits, the address inputs should be 14bits; We need 8chips of 8K ⨯8 bits RAM to form a 16 K ⨯ 32 bits ROM..14. Which is the XOR gate of the following circuit A .15.There are 2n-n invalid states in an n-bit ring counter state diagram.16.An unused CMOS NOR input should be tied to logic Low level or 0 .17.The function of a DAC is translating the Digital inputs to the same value of analogoutputs.二、Complete the following truth table of taking a vote by A,B,C, when more than two of A,B,C approve a resolution, the resolution is passed; at the same time, the resolution can’t go through if A don’t agree.For A,B,C, assume 1 is indicated approval, 0 is indicated opposition. For the F,A B C F0 0 0 0三、The circuit to the below realizes a combinational function F of four variables. Fill in the Karnaugh map of the logic function F realized by the multiplexer-based circuit. (6’)四、(A) Minimize the logic function expressionF = A·B + AC’ +B’·C+BC’+B’D+BD’+ADE(H+G) (5’)F = A·B + AC’ +B’·C+BC’+B’D+BD’= A·(B ’C )’ +B’·C+BC’+B’D+BD’= A +B’·C+BC’+B’D+BD’+C ’D (或= A +B’·C+BC’+B’D+BD’+CD ’)= A +B’·C+BD’+C ’D (或= A + BC’+B’D +CD ’)(B) To find the minimum sum of product for F and use NAND-NAND gates to realize it (6’)=),,,(Z Y X W F Π(1,3,4,6,9,11,12,14)------3分 F= X ’Z ’+XZ -----2分 =( X ’Z ’+XZ)’’=(( X ’Z ’)’(XZ)’)’ ------1分五、Realize the logic function using one chip of 74LS139 and two NAND gates.(8’)∑=)6,2(),,(C B A F ∑=)3,2,0(),,(E D C GF(A,B,C)=C’∑(1,3) ---- 3分 G(C,D,E)=C’∑(0,2,3) ----3分六、Design a self-correcting modulo-6 counter with D flip-flops. Write out the excitation equations and output equation. Q2Q1Q0 denote the present states, Q2*Q1*Q0* denote the next states, Z denote the output. The state transition/output table is as following.(10’)Q2Q1Q0Q2*Q1*Q0*Z000 100 0100 110 0110 111 0111 011 0011 001 0001 000 1激励方程式:D2=Q0’D1=Q2D0=Q1修改自启动:D2=Q0 +Q2Q1’D1=Q2+Q1Q0’D0=Q1+Q2Q0输出方程式:Z=Q1’Q0得分七、Construct a minimal state/output table for a moore sequential machine, that will detect the input sequences: x=101. If x=101 is detected, then Z=1.The input sequences DO NOT overlap one another. The states are denoted with S0~S3.(10’)For example:X:0 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 0 0 1 1 ……Z:0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 ……state/output tableS X Z 0 1 S0 S0 S1 0 S1 S2 S1 0 S2 S0 S3 0 S3 S0S11 S*八、Please write out the state/output table and the transition/output table and the excitation/output table of this state machine.(states Q2 Q1=00~11, use the state name A~D )(10’)Transition/output table State/output table Excitation/output tableQ2Q1 X Z 01 00 01 11 1 01 00 10 1 10 01 01 0 11 01 01 1Q2*Q1*SX Z 0 1 A B D 1 B A C 1 CB B 0 DBB1S*Q2Q1 X Z 01 00 01 11 1 01 00 10 1 10 01 01 0 11 01 01 1D2 D1得 分九、Clocked Synchronous State Machine Design(15’)74x163 is a synchronous 4-bit binary counter with synchronous CLEAR input and LOAD input. LD_L=(Q B Q C)', CLR_L=(Q D'Q B)'in the following circuit.1. Finish the logic circuit.2. Draw the state diagram with all states of “Q3Q2Q1Q0” . (“Q3Q2Q1Q0” is the output of 74x163)3. Write the sequence of Y.Y is the output of 74x151. (Assumed state of 74x163 start in Q3Q2Q1Q0=0000.)YCLOCK====Word 行业资料分享--可编辑版本--双击可删====解答:(1) Finish the logic circuit.(见下页图) LD_L=(Q B Q C )', CLR_L=(Q D 'Q B )' (2) Q3Q2Q1Q0: 清零优先级高于置数 0000—0001—0010—0000 0011—00000100—0101—0110—0000 0111—00001000—1001—1010—1011--1100—1101—1110--11001111—1100 (3) Y=010*******Function table for a 74x163Inputs Current State Next state OutputCLR_L LD_L ENT ENP Q D Q C Q B Q A Q D * Q C * Q B * Q A * RCO 0 X X X X X X X 0 0 0 0 0 1 0 X X X X X X D C B A 0 1 1 0 X X X X X Q D Q C Q B Q A 0 1 1 X 0 X X X X Q D Q C Q B Q A 0 1 1 1 1 0 0 0 0 0 0 0 1 0 1 1 1 1 0 0 0 1 0 0 1 0 0 1 1 1 1 0 0 1 0 0 0 1 1 0 1 1 1 1 0 0 1 1 0 1 0 0 0 1 1 1 1 …………. ………….. 0 1 1 1 1 1 1 1 1 0 0 0 0 1====Word行业资料分享--可编辑版本--双击可删====。

电子科技大学数字逻辑电路期末英文考试题及试卷

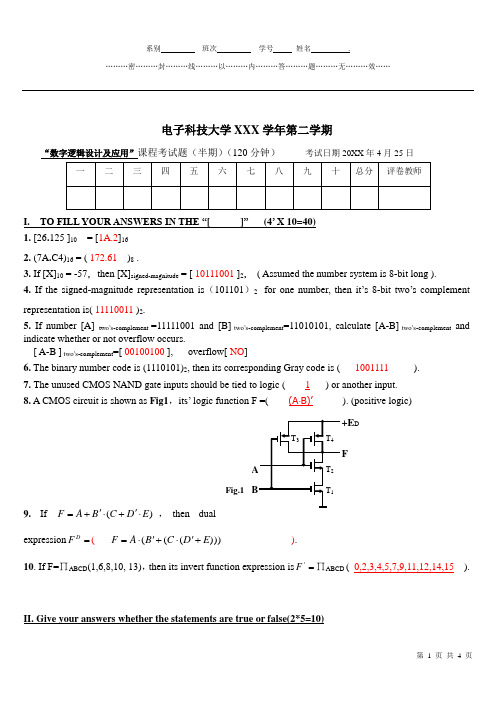

电子科技大学XXX 学年第二学期“数字逻辑设计及应用”课程考试题(半期)(120分钟) 考试日期20XX 年4月25日I. TO FILL YOUR ANSWERS IN THE “[ ]” (4’ X 10=40) 1. [26.125 ]10 = [1A.2]16 2. (7A .C4)16 = ( 172.61 )8 .3. If [X]10 = -57,then [X]signed-magnitude = [ 10111001 ]2, ( Assumed the number system is 8-bit long ).4. If the signed-magnitude representation is (101101)2 for one number, then it ’s 8-bit two ’s complement representation is( 11110011 )2.5. If number [A] tw o’s -complement =11111001 and [B] two’s -complement =11010101, calculate [A-B] two’s -complement and indicate whether or not overflow occurs.[ A-B ] two’s -complement =[ 00100100 ], overflow[ NO ] 6. The binary number code is (1110101)2, then its corresponding Gray code is ( 1001111). 7. The unused CMOS NAND gate inputs should be tied to logic (____1___) or another input. 8. A CMOS circuit is shown as Fig1,it s’ logic function F =(____(A ⋅B)’______). (positive logic)9. If )(E D C B A F ⋅'+⋅'+=,then dualexpression =D F (___)))(((E D C B A F +'⋅+'⋅=______________).10. If F=∏ABCD (1,6,8,10, 13),then its invert function expression is ='F ∏ABCD (_0,2,3,4,5,7,9,11,12,14,15__).II. Give your answers whether the statements are true or false(2*5=10)F+E DFig.11. ( F ) If AB=AC is true for logic equation ,then B=C is true.2. ( F ) A product expression for all minterms of a logic function must be 1.3. ( T ) If a logic function )7,3,1(,,C B A F ∏=,then it s’ inverse funcation )7,3,1(,,'C B A F ∑=.4. ( T ) when inputs is one “1” and 1000 “0” for XOR gate, then output is “1”.5. ( T ) A properly designed two-level sum-of-products (AND-OR) circuit has no static-0 hazards.III. there is only one correct answer in the following questions.(3’ X 10=30)1. For a logical function, which representation as follows is one and only (唯一). ( C )A) logic expression B) logic diagram C) truth table D) timing diagram 2. The following logic expressions, the hazard-free one is ( D ).A) F=B ’C ’+AC+A ’B B) F=A ’C ’+BC+AB ’C) F=A ’C ’+BC+AB ’+A ’B D) F=B ’C ’+AC+A ’B+BC+AB ’+A ’C ’ 3. The output signal of ( A ) circuit is 1-out-of-M code.A) binary decoder B) binary encoder C) seven-segment decoder D) decade counter4. The logic equation for a 2-input,1-bit multiplexer is F=AC+BC ’. If we want to build a two-input OR gate (F=X+Y )with this multiplexer , show how to tie the input A, B and C? ( A ).A). The input A should be tied to logic “1”, B to X, and C to Y . B). The input A should be tied to X, B to logic “0” and C to Y . C). The input A and B should be tied together to X, and C to Y . D). The input A should be tied to logic “0”, B to X, and C to Y .5. For a NAND gate in positive logic, if negative logic is adopted ,then NAND gate will be changed to ( D )。

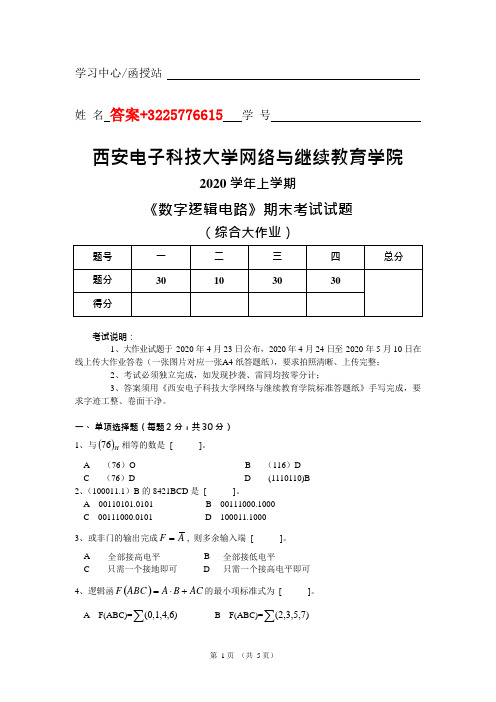

西安电子科技大学2020 学年上学期《数字逻辑电路》期末考试试题(综合大作业)

学习中心/函授站_姓名答案+3225776615学号西安电子科技大学网络与继续教育学院2020 学年上学期《数字逻辑电路》期末考试试题(综合大作业)考试说明:1、大作业试题于2020 年4 月23 日公布,2020 年4 月24 日至2020 年5 月10 日在线上传大作业答卷(一张图片对应一张A4 纸答题纸),要求拍照清晰、上传完整;2、考试必须独立完成,如发现抄袭、雷同均按零分计;3、答案须用《西安电子科技大学网络与继续教育学院标准答题纸》手写完成,要求字迹工整、卷面干净。

一、单项选择题(每题 2 分,共 30 分)1、与(76)H 相等的数是[ ]。

A (76)OB (116)DC (76)D D (1110110)B2、(100011.1)B 的8421BCD 是[ ]。

A 00110101.0101B 00111000.1000C 00111000.0101D 100011.10003、或非门的输出完成F =A , 则多余输入端[ ]。

A 全部接高电平B 全部接低电平C 只需一个接地即可D 只需一个接高电平即可4、逻辑函F (ABC )=A ⋅B +AC 的最小项标准式为[ ]。

A F(ABC)= ∑(0,1,4,6)B F(ABC)= ∑(2,3,5,7)C F(ABC)= ∑(2,6,7)D F(ABC)= ∑(0,1,4,6)5、与AB+AC+B ⋅C 相等的表达式为[ ]。

A ACB ABC AB+ACD A+ B ⋅C6、函数F=(A B +C)(B+ACD )的对偶式函数表达式是[ ]。

A G=( A +B)·C +B ·A +C +DB G=A+B C+B·A +C +DC G=(A+B )·C+B·A +C +DD G=(A B )·C +(B+ A +C +D )7、逻辑函数A B C D 的逻辑相邻项是[ ]。

电子科技大学《电路分析基础》20春期末考试.doc

1.正弦稳态电路中,若无源单口网络吸收的复功率=80+j60 VA,则功率因数λ=()。

A.0.6B.0.4C.0.3D.0.8【参考答案】: D2.图示一阶电路中,开关在t=0时打开,求i ()=()。

A.3 AB.2 AC.4 AD.0 A【参考答案】: D3.若电阻上电压u与电流i为非关联参考方向,则电导G的表达式为()。

A. B. C.- D.【参考答案】: C4.图示一阶电路中,开关在t=0时打开,求a,b两点间的电压()=()。

A.3 VB.2 VC.4 VD.0 V【参考答案】: D5.一段导体的电阻为,将其对折后的等效电阻为()A. B. C.D.【参考答案】: B6.通过一个理想独立电压源的电流数值及其方向A.必定大于零, 仅取决于外电路, 与电压源无关B.可为任意值, 仅取决于电压源, 与外电路无关C.必定大于零, 取决于外电路与电压源本身D.可为任意值, 取决于外电路与电压源本身【参考答案】: D7.图示理想变压器变比为1:2,则Uo应为()。

A.UiB.2UiC.0.5UiD.4Ui【参考答案】: B8.若电感L=2H的电流i =2cos(10t+30°)A (设u, i为关联参考方向),则它的电压u为()。

A.2cos(10t + 120°)VB.40cos(10t + 120°)VC.40cos(10t +30°)V D.2sin(10t + 30°)V【参考答案】: B9.KVL体现了电路中()守恒的法则。

A.电荷B.功率C.电压D.能量【参考答案】: D10.正弦稳态L,C串联电路中, 电容电压有效值为8V , 电感电压有效值为12V , 则总电压有效值为()V。

A.4B.8C.5D.20【参考答案】: A11.正弦稳态电路中,电流超前电压-90°的元件是()。

A.电阻B.电感C.电容D.二极管【参考答案】: B12.图示含源支路中,=1A , = ( )V。

西安电子科技大学2021数电期末试题

考试时间 120 分钟一、基础部分(共40分)1.(2分)完成下列数制转换:(25.25)10 = ( )2= ( )16 2.(2分)将十进制数转换为相应的编码表示。

(12)10 = ( )8421BCD= ( )余3码3.(4分)按照反演规则和对偶规则分别写出下列函数的反函数和对偶函数。

F =AB +E̅̅̅̅̅̅̅̅̅̅̅∙D +BC F̅ =__________________________________ F ∗=_________________________________4.(3分)按照要求写出下列函数的等价形式:5.(9分)已知某逻辑函数F 表达式如下,试完成下列内容:F =A̅C ̅+A ̅B ̅+BC +A ̅C ̅D ̅(1)在下图基础上完成该逻辑函数的卡诺图(下画线处也需要填写)(3分)。

===+=BC B A F (或与式) (与非与非式) (与或非式)(2)用卡诺图化简,写出该逻辑函数的最简与或式(2分)。

(3)根据化简结果,列出函数F的真值表(2分)。

(4)根据最简与或式画出该逻辑函数的电路图(2分)。

6.(6分)下图所示电路用于产生2相时钟信号,按照要求完成下述内容。

CQ1Q2(1)分别写出该电路的输出Q1和Q2的逻辑表达式(2分)。

(2)完成下列波形图,并说明在A 取不同值的情况下电路功能(初态为0)(4分)。

C Q Q2AQ1该电路的功能:_______________________________________________________ ____________________________________________________________________。

7.(6分)74194是双向移位寄存器,试判断下列电路的功能,并画出其状态表和状态图。

1(1)在下表中填写电路的状态表,并画出状态图(4分)状态图如下:(2)该电路的功能是:__________________________;(2分)装 订 线8.(8分)阅读如下电路,完成各项以下内容。

电子科技大学数字逻辑电路期末考试题

………密………封………线………以………内………答………题………无………效……电子科技大学二零零七年至二零零八学年第一学期期末一、填空题 (每题1.5分,共15分)1、已知74LS 系列的V OL max = 0.5 V , V OH min = 2.7 V , V IL max = 0.8 V, V IH min = 2.0 V , 则直流噪声容限是( )。

2、若EPROM 的容量为512K 字×8位,则地址码应取( )位。

3、b n⨯2 EPROM 可视为存储一个( )输入( )输出的真值表。

4、CMOS 门电路中,NMOS 的串联可实现( )操作,NMOS 的并联可实现( )操作。

5、已知带符号二进制反码为 ( 001101) 2 , 问 对应的8-bit 的补码为 ( ) 2.6、DAC 的功能是将输入的( )成正比地转换成( )输出。

7、CMOS 或非门的未用输入端应连接到( )电平上。

二、判断题 (每题1分,共5分)1、 ( )仅由与非门构成的电路是组合逻辑电路。

2、 ( )若)7,3,1(,,C B A F ∏=,则)7,3,1(,,'C B A F ∑= 3、 ( )具有n 个输入、m 个输出、p 个触发器的状态机有pn +2个状态。

4、 ( )1个“1”与1000个“0”的同或(异或非)运算,结果为“1”。

5、 ( )若AC AB ≠,则C B ≠。

三、(1)将F 1函数进行卡诺图化简,并以或非/或非结构予以实现。

(5分)∑∑+=),(),,,,,(98d 13127654m F 1………密………封………线………以………内………答………题………无………效……(2)将F 2函数进行卡诺图化简,并以与非/与非结构予以实现。

(5分)),,,,,,,(14121196431M F 2∏=四、现有下列真值表,其中A2、A1、A0是电路的输入, D1和D0是电路的输出。

电子科技大学模电期末0506A题&答案

………密………封………线………以………内………答………题………无………效……电子科技大学二零零 五 至二零零 六 学年第 一 学期期 末 考试模拟电路基础 课程考试题 A 卷 ( 120 分钟) 考试形式: 开卷 考试日期 2006 年 1月 12 日课程成绩构成:平时 10 分, 期中 30 分, 实验 0 分, 期末 60分1.(8答:(2(2(22.(3答:(1(13.(34.(6f 。

3.直流平衡电阻R p若图中集成运算放大器的电压增益为A o ,带宽为f BW 。

试求:4.带宽BWf ′………密………封………线………以………内………答………题………无………效……si R 阻oR图2解:22()4( 1.5)D GS T GS k V V V I =−=−————————————(1分)………密………封………线………以………内………答………题………无………效……28.90.7512R VV I R I GS DD D s D R R =−=−+——————(1分) 7.97, 2.91DGSmA V V I——————————————-—(2分)gRi RBEV =b R 1. 2.解:1. 3cc R T RV e 、、D、、z 构成固定VBE的恒流源——————————(2分)2. 36B EE Z V V V V =−+=−———————————————————(1分)………密………封………线………以………内………答………题………无………效……30.13V V V B BE EEImA E R e −−——————————————(1分)110.0523E II I mA E E ≈=————————————————(1分)1. 2. 3.解:1.由57R R 、构成直流负反馈,稳定静态工作点————————————————(2分)由462C R R 、、构成交流电压串联负反馈,提高输入电阻,稳定输出电压————(3分)………密………封………线………以………内………答………题………无………效……2. 244122v v R R R o o A vf v v R R i f +=≈==+————————————————(2分) 3.去掉上述交流反馈支路44C R 、以及6C ———————————————————(1分)A。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子科技大学数字电路

期末考试样题

Company number:【0089WT-8898YT-W8CCB-BUUT-202108】

一、填空题

1.五个变量构成的所有最小项之和等于 ( )。

2.已知某数的二进制原码表示为 ( 110110) 2 , 则其对应的8-bit 补码表示为 ( )2。

3.已知∑=C B A F ,,)3,0(,则∑='C B A F ,,( )。

4.要使D 触发器按'*Q Q =工作,则D 触发器的输入D=( )。

5.用移位寄存器产生1101010序列,至少需要( )位的移位寄存器。

二、单项选择题:

1. 若要将一异或门当作反相器(非门)使用,则输入端A 、B 端的连接方式是( )。

A. A 或B 中有一个接“0”

B. A 或B 中有一个接“1”

C. A 和B 并联使用

D. 不能实现 2.组合电路的竞争冒险是由于( )引起的。

A. 电路不是最简

B. 电路有多个输出

C. 电路中使用不同的门电路

D. 电路中存在延时

3.某一逻辑函数真值表确定后,下面描述该函数逻辑功能的表达式中,具有唯一性的是( )。

A .该逻辑函数的最简与或式

B .该逻辑函数的积之和标准型

C .该逻辑函数的最简或与式

D .该逻辑函数的和之积式

4.若最简状态转换表中,状态数为n ,则所需状态变量数K 为 ( )的整数.

00

00

01

01

10

1011

11图 A .n K 2log = B .n K 2log < C . n K 2log ≥ D . n K 2log ≤

5.某计数器的状态转换图如图1所示,其该计数器的模为( )。

A . 八 B. 五 C. 四 D. 三

三、 组合电路分析:

1.求逻辑函数 Z Y X Y X Z X F ⋅'⋅+⋅+⋅'= 的最简积之和表达式。

2.已知逻辑函数∑=Z Y X F ,,)7,5,1(, 请写出该函数的标准和(最小项之和)表达式: 3.找出逻辑表达式X W Y W F ⋅+'⋅'=对应的电路的所有静态冒险。

四、组合电路设计:

1、试用一片三输入八输出译码器74X138和适当的与非门实现函数:

画出电路连接图。

译码器如右图所示。

2、一个多路复用器,具有4个2位输入总线P 、Q 、R 、T ,3个选择输入端S2~S0根据表1选定4个输入总线中的一个来驱动2位输出总线Y 。

如图2所示,可以使用一片74x153(四选一多路复用器)和一个码转换器实现该功能,试写出图2中“码转换器”对应的真值表和逻辑表达式。

1(21)C S S '=⋅,0(10)C S S '=⋅

五、 时钟同步状态机设计:

表1

S 2 S 1 S 0 选择的输入 0 0 0 P 0 0 1 P 0 1 0 P 0 1 1 Q 1 0 0 P 1 0 1 P 1 1 0 R 码

1、 写出一个3位同步格雷(GRAY )码计数器的转移/输出表:

Q2Q1Q0 Q2*Q1*Q0* Z

2、构造J-K 触发器的应用表。

已知某状态机的转移/输出表如表2所示,写出针对J-K 触发器的激励/输出表。

表2:转移/输出表 Q1Q0 X 0 1 00 01,0 10,0 01 11,0 01,0 11 01,1 00,0 10 01,0 11,0

Q1*Q0*,Z

3、已知某状态机针对D 触发器的激励/输出表如表3所示,请导出最小成本激励方程和输出方程。

101D Q X Q X =⋅+⋅,010D Q Q X ''=⋅⋅

六、时钟同步状态机分析:

1、已知电路

如图3所

示,写出电路的激励方程、转移方程并建立转移表

图3

激励/输出表 Q1Q0 X

0 1 00 0d,1d,0 1d,0d,0 01 1d,d0,0 0d,d0,0 11 d1,d0,1 d1,d1,0 10

d1,1d,0 d0,1d,0

J1K1,J0K0,Z

J-K 触发器的应用表 Q Q* J K 0 0 0 d 0 1 1 d 1 0 d 1 1

1

d

表3:激励/输出表

Q1Q

0 X 0 1 0 0 0 0 ,0 0 1 ,0 0 1 0 0 ,0 1 0 ,0 1 0 0 0 ,0 1 0 ,1 D1D0 , Z

2、已知某时序电路的转移/输出表如表4所示,请画出与输入波形对应的输出Y 的波形图(设起始状态为Q 1Q 0=00)。

/输出表。

A Z=0

B Z=0

D Z=1

C Z=0

X

X ’11Y

’Y ’

XY ’

七、设计一个MEALY 型序列检测器,当

且仅当输入X 是1111或1101时,输出Z 为1。

允许重叠。

写出最简状态/输出表或状态图。

比如:

X : 0 0 1 1 0 1 1 1 1 0 1 1 1 0 1 0 0 0 0 Z : 0 0 0 0 0 1 0 0 1 0 1 0 0 0 1 0 0 0 0 解:状态/输出表:

含义 S X

0 1 未收到1位有效码

A A ,0

B ,0 收到1个1 B A ,0

C ,0 收到11 C

D ,0

E ,0 收到110 D A ,0 B ,1 收到111

E

A ,0

E ,1

表4:转移/输出表

Q1Q 0 A

0 1 00 01,0 00,0 01 01,0 11,0 10 01,0 00,1 11

01,0

00,1 图4

状态/输出表 S

XY

Z

00 01

10

11

S*

八、74x163为同步清零,同步计数的4位二进制计数器,利用74x163和集成多路选择器74x151构成的序列发生器电路如图5所示。

1)试分析当M=0和M=1时,电路中Q2Q1Q0的输出序列以及计数器分别工作在几进制。

2)写出当M=0和M=1输出Y处产生的序列。

图5

解:1)M=0时,Q2Q1Q0的输出序列为:000001010011100101110111 000,为八进制计数器;

M=1时,Q2Q1Q0的输出序列为: 001010011100101110111001,为七进制计数器。

M=1时,输出Y处产生的序列:1011010。