VGA时序

VGA产生行同步(HSYNC)

【原创】基于Verilog的VGA显示控制(有源码)一、VGA时序下面的图是本人画了一个晚上的结果,个人认为能够比较详细的阐述VGA的信号时序。

VGA的时序根据不同的显示分辨率和刷新频率会有变化,具体各种类型的时序信息可以参考下面的网站,这里非常详细的说明的每一种显示模式的VGA时序信息。

/vga-timing二、VGA电平VSYNC,HSYNC为标准TTL电平,0V~3.3V。

RGB的电平在0V~0.7V之间(0V为黑色,0.7V为全色)。

三、程序顶层框图VGA产生行同步(HSYNC),场同步信号(VSYNC),并产生每个像素的地址输入单口ROM(显存)中,ROM输出该点需要显示的颜色值。

四、单口ROM(显存)设计程序的显示模式为800*600,72Hz刷新频率,像素频率为50MHz。

每个像素需要显示的颜色存储在单口RAM中,每种颜色用8个字节表示,则如果要显示8 00*600分辨率,则需要800*600字节(480KB)的单口ROM,由于FPGA内部没有这么大的RAM(我用的是ep2c8),因此我把屏幕上100*100个像素组成的矩形作为一个逻辑像素(即显示同一种颜色),这样只要8*6字节(48字节),用FPGA自带的RAM是很容易实现的。

ROM中颜色存储地址表将全屏划分成8*6的方格,每个方格的颜色存储在ROM中,VGA控制器不断产生行坐标(ROM水平地址)和场坐标(ROM垂直地址),最后组合成ROM实际地址输入ROM中,ROM输出该地址的颜色值,显示在LCD中。

五、程序设计VGA控制器程序module VGA(clk,rst_n,hsync,vsync,vga_r,vga_g,vga_b);input clk;//50MHzinput rst_n;//复位信号output hsync;//行同步信号output vsync;//场同步信号//R、G、B信号输出output[1:0]vga_r;output[2:0]vga_g;output[2:0]vga_b;//--------------------------------------------------reg[10:0]x_cnt;//行坐标(这里包括了行同步、后沿、有效数据区、前沿)reg[9:0]y_cnt;//列坐标(这里包括了场同步、后沿、有效数据区、前沿)reg[5:0]Xcoloradd;reg[2:0]Ycoloradd;parameterLeft=184,PixelWidth=100,Top=29;always@(posedge clk or negedge rst_n)if(!rst_n)x_cnt<=10'd0;else if(x_cnt==11'd1040)x_cnt<=10'd0;//行计数记到1040else x_cnt<=x_cnt+1'b1;always@(posedge clk or negedge rst_n)//产生行地址(ROM水平地址)if(!rst_n)Xcoloradd<=6'b000000;else if(x_cnt>=Left&&x_cnt<Left+PixelWidth)Xcoloradd<=6'b000000;else if(x_cnt>=Left+PixelWidth&&x_cnt<Left+2*PixelWidth)Xcoloradd<=6'b000001;else if(x_cnt>=Left+2*PixelWidth&&x_cnt<Left+3*PixelWidth)Xcoloradd<=6'b000010;else if(x_cnt>=Left+3*PixelWidth&&x_cnt<Left+4*PixelWidth)Xcoloradd<=6'b000011;else if(x_cnt>=Left+4*PixelWidth&&x_cnt<Left+5*PixelWidth)Xcoloradd<=6'b000100;else if(x_cnt>=Left+5*PixelWidth&&x_cnt<Left+6*PixelWidth)Xcoloradd<=6'b000101;else if(x_cnt>=Left+6*PixelWidth&&x_cnt<Left+7*PixelWidth)Xcoloradd<=6'b000110;else if(x_cnt>=Left+7*PixelWidth&&x_cnt<Left+8*PixelWidth)Xcoloradd<=6'b000111;else Xcoloradd<=6'b110000;//背景颜色地址always@(posedge clk or negedge rst_n)if(!rst_n)y_cnt<=10'd0;else if(y_cnt==10'd666)y_cnt<=10'd0;//场同步记到666else if(x_cnt==11'd1040)y_cnt<=y_cnt+1'b1;//每计数完一行,场同步就加一always@(posedge clk or negedge rst_n)//产生列地址(ROM垂直地址)if(!rst_n)Ycoloradd<=3'b000;else if(y_cnt>=Top&&y_cnt<Top+PixelWidth)Ycoloradd<=3'b000;else if(y_cnt>=Top+PixelWidth&&y_cnt<Top+2*PixelWidth)Ycoloradd<=3'b001;else if(y_cnt>=Top+2*PixelWidth&&y_cnt<Top+3*PixelWidth)Ycoloradd<=3'b010;else if(y_cnt>=Top+3*PixelWidth&&y_cnt<Top+4*PixelWidth)Ycoloradd<=3'b011;else if(y_cnt>=Top+4*PixelWidth&&y_cnt<Top+5*PixelWidth)Ycoloradd<=3'b100;else if(y_cnt>=Top+5*PixelWidth&&y_cnt<Top+6*PixelWidth)Ycoloradd<=3'b101;else Ycoloradd<=3'b110;//背景颜色地址//--------------------------------------------------//signal port ROMwire[7:0]color;wire[5:0]coloradd;assign coloradd={Ycoloradd,3'b000}|Xcoloradd;//将水平地址和垂直地址合成ROM实际地址sprom u1(coloradd,clk,color);//---------------------------------------------------wire valid;//有效数据显示区标志,就是你在液晶屏幕上可以看到的区域assign valid=(x_cnt>10'd184)&&(x_cnt<10'd984)&&(y_cnt>10'd29)&&(y_cnt<10'd629);//--------------------------------------------------reg hsync_r,vsync_r;always@(posedge clk or negedge rst_n)if(!rst_n)beginhsync_r<=1'b0;vsync_r<=1'b0;endelse beginhsync_r<=x_cnt>=10'd120;//产生hsync信号(行同步)when x_c nt>=50,then hsync_r=1,else0;低电平同步vsync_r<=y_cnt>=10'd6;//产生vsync信号(场同步)my LCD islow syncendassign hsync=hsync_r;assign vsync=vsync_r;//--------------------------------------------------//颜色输出assign vga_r[1]=valid?color[7]:1'b0;assign vga_r[0]=valid?color[6]:1'b0;assign vga_g[2]=valid?color[5]:1'b0;assign vga_g[1]=valid?color[4]:1'b0;assign vga_g[0]=valid?color[3]:1'b0;assign vga_b[2]=valid?color[2]:1'b0;assign vga_b[1]=valid?color[1]:1'b0;assign vga_b[0]=valid?color[0]:1'b0;endmodule六、运行结果七、后记在这次程序中只在ROM中存储了一些随机的数,因此显示出来是一些小方格,如果ROM做的更大,完全可以存储一幅图像,显示在LCD中。

VGA显示控制

基于FPGA 的VGA显示控制摘要VGA(Video Graphics Array)即视频图形阵列,是IBM公司1987年推出的一种传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛应用。

本次课程设计是基于FPGA和主芯片为 EP4CE30F23C8N的ALTER公司的开发板Cyclone IV来实现的。

数字图像信息在VGA接口显示器正确、完整地显示,涉及到时序的构建和数字图像信息的模拟化两方面,提出一种能够广泛应用的VGA显示接口方案,详细阐述了数字图像数据DA转化并输出到VGA接口显示器显示的方法,其中包括接口的硬件设计、视频DA转换器的使用方法、通过FPGA构造VGA时序信号的方法等等。

方案可以应用于各种仪器,数字视频系统、高分辨率的彩色图片图像处理、视频信号再现等。

课设主要用到的芯片是ADV7123,它是一款高速、高精度数模转换芯片。

拥有三路十位D/A转换器,能够将代表颜色的数据锁存到数据寄存器中,然后通过D/A 转换器转换成模拟信号输出,得到我们要的色彩。

VGA显示的硬件设计和原理1.1 FPGA主芯片课程设计所用开发板的主芯片是EP4CE30F23C8N——Cyclone IV,其由Altera公司开发,值得注意的是该开发板所支持的QUARTUS II的版本较高,并且11.0的版本较12.0的版本编译好的程序更好下载。

图-11.2 ADV7123实现VGA的控制显示主要用到的芯片就是ADV7123,ADV7123由完全独立的三个I0位高速D/A转换器组成,RGB(红绿蓝)视频数据分别从R9~R0、G9~G0、B9~B0输入,在时钟CLOCK的上升沿锁存到数据寄存器中,然后经告诉D/A转换器转换成模拟信号。

三个独立的视频D/A转换器都是电流型输出,可以接成差分输出,也可以接成单端输出。

DE2-115上按单端输出,在模拟输出端用75欧姆电阻接地,以满足工业标准。

VGA信号一些分辨率的参数(摘抄)

VGA信号⼀些分辨率的参数(摘抄) VGA的接⼝时序如图所⽰,场同步信号VSYNC在每帧(即送⼀次全屏的图像)开始的时候产⽣⼀个固定宽度的⾼脉冲,⾏同步信号HSYNC在每⾏开始的时候产⽣⼀个固定宽度的⾼脉冲,⾊彩数据在某些固定的⾏和列交汇处有效。

如前所述,我们通常以⼀个基准时钟驱动VGA信号的产⽣,⽤这个基准时钟为时间单位来产⽣的时序如图所⽰。

对于⼀个刷新频率为60Hz,分辨率为640X480的标准VGA显⽰驱动,若它的基准驱动时钟为25.175MHz,它的脉冲计数表如下所⽰。

注意列的单位为“⾏”,⽽⾏的单位为“基准时钟周期数”,即25.175MHz时钟脉冲数。

VGA驱动时序参数表⾏/列同步脉冲后沿脉冲显⽰脉冲前沿脉冲帧长列23348010525⾏964864016800⽽对于640*480在75hz的刷新频率下的驱动参数如下,其中驱动时钟是31.5M,⾏/列同步脉冲后沿脉冲显⽰脉冲前沿脉冲帧长列3164801500⾏6412064016840对于⼀个刷新频率为72Hz,分辨率为800X600的SVGA显⽰驱动,若它的基准驱动时钟为50MHz,它的计数脉冲参数如表所⽰。

注意列的单位为“⾏”,⽽⾏的单位为“基准时钟周期数”,即50MHz时钟脉冲数。

SVGA驱动时序参数表⾏/列同步脉冲后沿脉冲显⽰脉冲前沿脉冲帧长列62360037666⾏12064800561040⽽对于800*600@60HZ,驱动时钟为40MHZ,参数如下:⾏/列同步脉冲后沿脉冲显⽰脉冲前沿脉冲帧长列4236001628⾏12888800401056⽽对于800*600@75HZ,驱动时钟为49.5MHZ,参数如下:⾏/列同步脉冲后沿脉冲显⽰脉冲前沿脉冲帧长列3216001625⾏80160800161056对于⼀个刷新频率为60Hz,分辨率为1024X768的显⽰驱动,若它的基准驱动时钟为65MHz,它的计数脉冲参数如表所⽰。

VGA接口详解及其单片机驱动方法

由于单片机达不到很高工作频率,从而使其是否能够满足 VGA 接口时序 成为问题。采用 STC 增强型 51 单片机,对其可行性进行分析。

STC12 系列单片机是 1T 单片机(工作频率与外部振荡器频率相同),最高 可以达到 35MHz,这相当于传统 51 单片机的 420MHz(内部 12 分频),这使 得 VGA 时序的实现成为可能。

VGA 接口详解及其单片机驱动方法

VGA(视频图形阵列)作为一种标准的显示接口已经得到了广泛的应用。对 VGA 接口 时序进行深入的研究,从而采用单片机实现显示器的驱动。由于 VGA 接口对于时序十分严 格,而传统单片机在处理速度上并不能达到其时序要求。现采用增强型高速单片机,实现了 VGA 接口的显示器的驱动。下面对 VGA 接口进行详细的介绍。

13 HSYNC 或 CSYNC 行同步

14 VSYNC

场同步

15 ID3 或 SCL

显示器标识位 3

通常情况下,对 VGA 显示器进行驱动只需要 5 个信号即可,包括:行、

场帧同步信号,红、绿、兰三色信号。其中行、场同步信号为数字信号,红、

绿、兰三色信号为模拟信号。三色信号的输入电压范围是 0.0V~0.7V,采用 DAC

(1) VGA 接口定义

(2)

针脚功能详述

编号 标识

功能描述

1

VGA显示控制资料

基于FPGA 的VGA显示控制摘要VGA(Video Graphics Array)即视频图形阵列,是IBM公司1987年推出的一种传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛应用。

本次课程设计是基于FPGA和主芯片为 EP4CE30F23C8N的ALTER公司的开发板Cyclone IV来实现的。

数字图像信息在VGA接口显示器正确、完整地显示,涉及到时序的构建和数字图像信息的模拟化两方面,提出一种能够广泛应用的VGA显示接口方案,详细阐述了数字图像数据DA转化并输出到VGA接口显示器显示的方法,其中包括接口的硬件设计、视频DA转换器的使用方法、通过FPGA构造VGA时序信号的方法等等。

方案可以应用于各种仪器,数字视频系统、高分辨率的彩色图片图像处理、视频信号再现等。

课设主要用到的芯片是ADV7123,它是一款高速、高精度数模转换芯片。

拥有三路十位D/A转换器,能够将代表颜色的数据锁存到数据寄存器中,然后通过D/A 转换器转换成模拟信号输出,得到我们要的色彩。

VGA显示的硬件设计和原理1.1 FPGA主芯片课程设计所用开发板的主芯片是EP4CE30F23C8N——Cyclone IV,其由Altera公司开发,值得注意的是该开发板所支持的QUARTUS II的版本较高,并且11.0的版本较12.0的版本编译好的程序更好下载。

图-11.2 ADV7123实现VGA的控制显示主要用到的芯片就是ADV7123,ADV7123由完全独立的三个I0位高速D/A转换器组成,RGB(红绿蓝)视频数据分别从R9~R0、G9~G0、B9~B0输入,在时钟CLOCK的上升沿锁存到数据寄存器中,然后经告诉D/A转换器转换成模拟信号。

三个独立的视频D/A转换器都是电流型输出,可以接成差分输出,也可以接成单端输出。

DE2-115上按单端输出,在模拟输出端用75欧姆电阻接地,以满足工业标准。

VGA时序图

基于Verilog的VGA驱动设计(一)VGA时序分析VGA时序分析电阻DAC转换网络和640X480的VGA时序图:图1扫描频率显示器采用光栅扫描方式,即轰击荧光屏的电子束在CRT屏幕上从左到右(受水平同步信号HSYNC控制)、从上到下(受垂直同步信号VSYNC控制)做有规律的移动。

光栅扫描又分逐行扫描和隔行扫描。

电子束采用光栅扫描方式,从屏幕左上角一点开始,向右逐点进行扫描,形成一条水平线;到达最右端后,又回到下一条水平线的左端,重复上面的过程;当电子束完成右下角一点的扫描后,形成一帧。

此后,电子束又回到左上方起点,开始下一帧的扫描。

这种方法也就是常说的逐行扫描显示。

1.Horizonal Timing图2A (us) Line Period(1040*20ns)B (us) Sync pulse lenghtC (us) Back porchD (us) Active video timeE (us) Front porch2.Vertical Timing图3O (ms) Frame Period 帧周期P (ms) Sync lengthQ (ms) Back porchR (ms) Active video timeS (ms) Front porchHorizonal timing information 水平扫描时序图4Notes:•Active area is actually an active area added with 6 overscan border pixels (in some other VGA timing tables those border pixels are included in back and front porch)Vertical timing information 垂直扫描时序图5Notes:•Active area is actually an active area added with 4 overscan border lines (in some other VGA timing tables those border lines are included in back and front porch)•Note than when the active part of VGA page is widened, it passes by the rising edge of the vertical sync signal in some modes (marked with *)根据上面的水平和垂直扫描时序可以分析显示800x600模式,FPGA系统时钟采用Spartan-3E Starter Kit板上的50MHz的有源晶振。

FPGA—VGA显示

VGA一、设计目的1、利用VHDL语言的描述方法进行设计完成VGA显示的系统设计;2、自行选择VGA显示模式;3、通过FPGA产生VGA Monitor的控制时序;4、通过FPGA产生彩条图形,在VGA显示器上显示;5、扩展要求:可以在拨动开关控制下,通过FPGA+VGA接口的系统在屏幕上显示不同图像。

二、设计原理1、VGA简要介绍显示绘图阵列(video graphic array,VGA)接口是LCD液晶显示设备的标准接口,大多应用在显示器与显卡之间,同时还可以用在等离子电视输入图像的模数转换上。

VGA显示输出RGB三原色信号,RGB色彩模式是工业界的一种颜色标准,是通过对红(R)、绿(G)、蓝(B)三个颜色通道的变化以及它们相互之间的叠加来得到各式各样的颜色,目前在图像显示领域中应用非常广泛。

2、VGA的显示特点(1)扫描格式繁多,分辨率从320×200一直延伸到1280×102,行频15.8~70Hz,场频50~100Hz。

常见的行频有31.4Hz,37.8Hz,57.9Hz,62.5Hz 等,常见场频有50Hz,60Hz,70Hz,100Hz,16700K之分。

(2)显示器的显示方式有两种:A/N显示方式和APA显示方式,即文本显示方式和图形显示方式。

A/N方式已淘汰不用,目前微机都采用APA图形方式。

(3)VGA接口为显示器提供两类信号,一类是数据信号,一类是控制信号。

数据信号包括红(Red)、绿(Green)、蓝(Blue)信号,简称RGB信号,控制信号包括水平同步信号和垂直同步信号。

输出不同分辨率时,水平同步信号和垂直同步信号的频率也不相同。

3、VGA显示原理常见的彩色显示器一般由CRT(阴极射线管)构成,彩色是由R(红)、G(绿)、B(蓝)三种基色组成。

显示是采用逐行扫描的方式,阴极射线枪发出的电子束打在涂有荧光粉的荧光屏上,产生RGB三色基,最后合成一个彩色图像。

VGA和HDMI的时序格式

VGA和HDMI的时序格式由上述两个标准设置组分别定义:VESA 和CEA/EIA。

VESA时序格式的定义参见“VESA监视时序和协同视频时序标准”;HDMI时序格式的定义参见CEA-861。

VESA时序格式包括主要用于PC和笔记本电脑的标准,如VGA、XGA、SXGA 等。

CEA-861描述电视和增清/高清显示器所用的标准,如480p、576p、720p和1080p等。

在这些时序格式中,只有640 × 480p @ 60 Hz这一种格式是强制性的,为VESA和CEA-861标准所共有。

PC和电视均必须支持这种模式,因此本例使用该模式。

表2比较了一般支持的视频标准。

详细数据请参阅相应的规范。

表2. 最常用的VESA和CEA-861标准(p = 逐行;i = 隔行)网上资料好像HD4600核显的输出,最高只有1920*1080,那就是16:9的显示器比较合适。

但是个人想使用16:10的显示器,即1920*1200,也许以后有机会2560*1600,所以想表问下HD4600的输出分辨率。

ms intel的核显只有DP口才支持2560X1440集成显卡HD Graphics 4600支持最大多少分辨率的输出?比如:1920 x 1080还是更高京东回复:您好!这个要问主板显示接口是否支持想要输出4K分辨率的图像,硬件方面的也不能含糊。

虽然较早之前就有声称可以解码4K 视频的高清播放机,但是支持输出4K分辨率的高清播放机也是在最近才开始登陆市场,而且大都只能输出24Hz或者是30Hz的刷新率。

想要输出60Hz刷新率下的4K图像,目前PC仍然是最好的选择。

决定PC能否输出4K分辨率的硬件是显卡,目前只有Kepler架构、GCN架构或者是更新架构的独立显卡支持输出4K分辨率,集显平台方面则要用到Haswell 架构处理器或者是Kaveri APU方能支持。

决定PC能否输出4K分辨率的硬件是显卡,目前只有Kepler架构、GCN架构或者是更新架构的独立显卡支持输出4K分辨率,集显平台方面则要用到Haswell架构处理器或者是Kaveri APU方能支持。

VGA简介

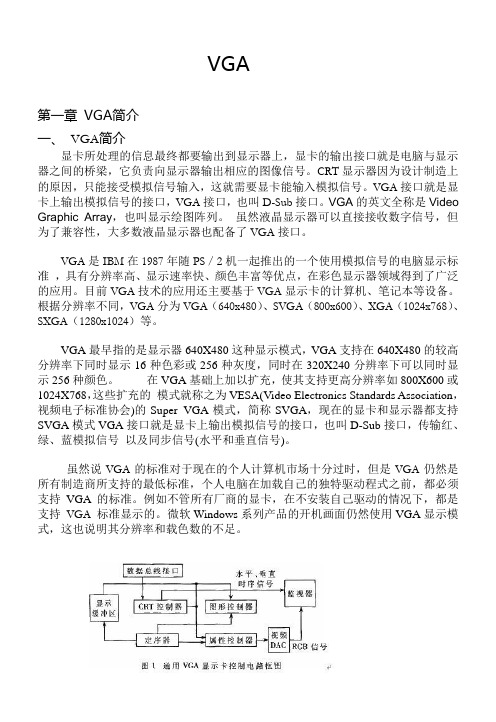

VGA第一章VGA简介一、VGA简介显卡所处理的信息最终都要输出到显示器上,显卡的输出接口就是电脑与显示器之间的桥梁,它负责向显示器输出相应的图像信号。

CRT显示器因为设计制造上的原因,只能接受模拟信号输入,这就需要显卡能输入模拟信号。

VGA接口就是显卡上输出模拟信号的接口,VGA接口,也叫D-Sub接口。

VGA的英文全称是Video Graphic Array,也叫显示绘图阵列。

虽然液晶显示器可以直接接收数字信号,但为了兼容性,大多数液晶显示器也配备了VGA接口。

VGA是IBM在1987年随PS/2机一起推出的一个使用模拟信号的电脑显示标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。

目前VGA技术的应用还主要基于VGA显示卡的计算机、笔记本等设备。

根据分辨率不同,VGA分为VGA(640x480)、SVGA(800x600)、XGA(1024x768)、SXGA(1280x1024)等。

VGA最早指的是显示器640X480这种显示模式,VGA支持在640X480的较高分辨率下同时显示16种色彩或256种灰度,同时在320X240分辨率下可以同时显示256种颜色。

在VGA基础上加以扩充,使其支持更高分辨率如800X600或1024X768,这些扩充的模式就称之为VESA(Video Electronics Standards Association,视频电子标准协会)的Super VGA模式,简称SVGA,现在的显卡和显示器都支持SVGA模式VGA接口就是显卡上输出模拟信号的接口,也叫D-Sub接口,传输红、绿、蓝模拟信号以及同步信号(水平和垂直信号)。

虽然说VGA的标准对于现在的个人计算机市场十分过时,但是VGA仍然是所有制造商所支持的最低标准,个人电脑在加载自己的独特驱动程式之前,都必须支持VGA的标准。

例如不管所有厂商的显卡,在不安装自己驱动的情况下,都是支持VGA 标准显示的。

视频传输标准

VGA概述VGA(Video Graphics Array)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。

目录[隐藏]VGA应用VGA原理内存寻址程序技巧技术性细节标准文字模式VGA色版VGA线路VGA 公插头(通常位于显示器侧)[编辑本段]VGA应用VGA技术的应用还主要基于VGA显示卡的计算机、笔记本等设备,而在一些既要求显示彩色高分辨率图像又没有必要使用计算机的设备上,VGA技术的应用却很少见到。

本文对嵌入式VGA显示的实现方法进行了研究。

基于这种设计方法的嵌入式VGA显示系统,可以在不使用VGA显示卡和计算机的情况下,实现VGA图像的显示和控制。

系统具有成本低、结构简单、应用灵活的优点,可广泛应用于超市、车站、飞机场等公共场所的广告宣传和提示信息显示,也可应用于工厂车间生产过程中的操作信息显示,还能以多媒体形式应用于日常生活。

[编辑本段]VGA原理1 显示原理与VGA时序实现通用VGA显示卡系统主要由控制电路、显示缓存区和视频BIOS程序三个部分组成。

控制电路如图1所示。

控制电路主要完成时序发生、显示缓冲区数据操作、主时钟选择和D /A转换等功能;显示缓冲区提供显示数据缓存空间;视频BIOS作为控制程序固化在显示卡的ROM中。

1.1 VGA时序分析通过对VGA显示卡基本工作原理的分析可知,要实现VGA显示就要解决数据来源、数据存储、时序实现等问题,其中关键还是如何实现VGA时序。

VGA的标准参考显示时序如图2所示。

行时序和帧时序都需要产生同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序段(Display interval c)和显示前沿(Front porch d)四个部分。

几种常用模式的时序参数如表1所示。

1.2 VGA时序实现首先,根据刷新频率确定主时钟频率,然后由主时钟频率和图像分辨率计算出行总周期数,再把表1中给出的a、b、c、d各时序段的时间按照主计数脉冲源频率折算成时钟周期数。

VGA时序及原理

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

隔行扫描是指电子束扫描时每隔一行扫一线,完成一屏后在返回来扫描剩下的线,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。

完成一行扫描的时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描的时间称为垂直扫描时间,其倒数称为场频率,即刷新一屏的频率,常见的有60Hz,75Hz等等。

标准的VGA显示的场频60Hz,行频31.5KHz。

行场消隐信号:是针对老式显像管的成像扫描电路而言的。

电子枪所发出的电子束从屏幕的左上角开始向右扫描,一行扫完需将电子束从右边移回到左边以便扫描第二行。

在移动期间就必须有一个信号加到电路上,使得电子束不能发出。

不然这个回扫线会破坏屏幕图像的。

这个阻止回扫线产生的信号就叫作消隐信号,场信号的消隐也是一个道理。

显示带宽:带宽指的显示器可以处理的频率范围。

如果是60Hz刷新频率的VGA,其带宽达640x480x60=18.4MHz,70Hz的刷新频率1024x768分辨率的SVGA,其带宽达1024x768x70=55.1MHz。

时钟频率:以640x480@59.94Hz(60Hz)为例,每场对应525个行周期(525=10+2+480+33),其中480为显示行。

每场有场同步信号,该脉冲宽度为2个行周期的负脉冲,每显示行包括800点时钟,其中640点为有效显示区,每一行有一个行同步信号,该脉冲宽度为96个点时钟。

由此可知:行频为525*59.94=31469Hz,需要点时钟频率:525*800*59.94约25MHz.一、VGA时序分析:VESA中定义行时序和场时序都需要同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序段(Display interval c)和显示前沿(Front porch d)四部分。

VGA信号测试基本知识

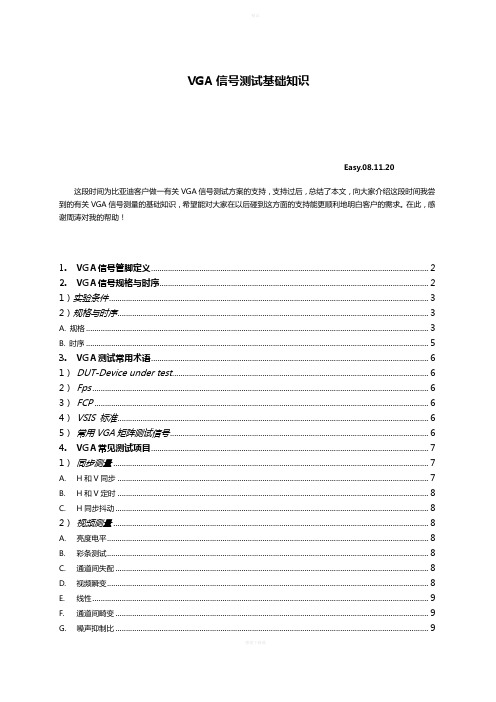

VGA信号测试基础知识Easy.08.11.20这段时间为比亚迪客户做一有关VGA信号测试方案的支持,支持过后,总结了本文,向大家介绍这段时间我尝到的有关VGA信号测量的基础知识,希望能对大家在以后碰到这方面的支持能更顺利地明白客户的需求。

在此,感谢周涛对我的帮助!1. VGA信号管脚定义 (2)2. VGA信号规格与时序 (2)1)实验条件 (3)2)规格与时序 (3)A. 规格 (3)B. 时序 (5)3. VGA测试常用术语 (6)1)DUT-Device under test (6)2)Fps (6)3)FCP (6)4)VSIS 标准 (6)5)常用VGA矩阵测试信号 (6)4. VGA常见测试项目 (7)1)同步测量 (7)A. H和V同步 (7)B. H和V定时 (8)C. H同步抖动 (8)2)视频测量 (8)A. 亮度电平 (8)B. 彩条测试 (8)C. 通道间失配 (8)D. 视频瞬变 (8)E. 线性 (9)F. 通道间畸变 (9)G. 噪声抑制比 (9)5. 小结 (9)1.VGA信号管脚定义虽说有15根线,但常用测试项目中只要这么几根:A.红基色B.绿基色C.蓝基色D.蓝基,绿基,红基(这三根线与线缆的屏蔽线拧一起,起到模拟共地作用)E.行同步F.场同步G.数字地线以上七条线就是在测试过程中必用的线。

2.VGA信号规格与时序给大家实验图片目的:让大家看到真实的信号后,再来向大家介绍信号的规格与时序。

1)实验条件A.视频信号源(把另一部电脑作为信号源):a.分辨率800*600b.刷新率60Hzc.装了Nokia Monitor Test,产生标准的视频信号软件。

B.匹配阻抗75欧C.示波器PXI-59222)规格与时序A.规格a.红基色: VPP=1.4V,Vmax=700mvb.绿基色: VPP=1.4V,Vmax=700mvc.蓝基色: VPP=1.4V,Vmax=700mvd.场同步: TTL脉冲电平,每扫描完一场输出一个脉冲。

VGA信号测试基本知识

VGA信号测试基础知识Easy.08.11.20这段时间为比亚迪客户做一有关VGA信号测试方案的支持,支持过后,总结了本文,向大家介绍这段时间我尝到的有关VGA信号测量的基础知识,希望能对大家在以后碰到这方面的支持能更顺利地明白客户的需求。

在此,感谢周涛对我的帮助!1.VGA信号管脚定义 (2)2. VGA信号规格与时序 (2)1)实验条件 (2)2)规格与时序 (3)A. 规格 (3)B. 时序 (4)3. VGA测试常用术语 (6)1)DUT-Device under test (6)2)Fps (6)3)FCP (6)4)VSIS 标准 (6)5)常用VGA矩阵测试信号 (6)4. VGA常见测试项目 (7)1)同步测量 (7)A. H和V同步 (7)B. H和V定时 (7)C. H同步抖动 (7)2)视频测量 (8)A. 亮度电平 (8)B. 彩条测试 (8)C. 通道间失配 (8)D. 视频瞬变 (8)E. 线性 (8)F. 通道间畸变 (8)G. 噪声抑制比 (8)5. 小结 (9)1.VGA信号管脚定义虽说有15根线,但常用测试项目中只要这么几根:A.红基色B.绿基色C.蓝基色D.蓝基,绿基,红基(这三根线与线缆的屏蔽线拧一起,起到模拟共地作用)E.行同步F.场同步G.数字地线以上七条线就是在测试过程中必用的线。

2.VGA信号规格与时序给大家实验图片目的:让大家看到真实的信号后,再来向大家介绍信号的规格与时序。

1)实验条件A.视频信号源(把另一部电脑作为信号源):a.分辨率800*600b.刷新率60Hzc.装了Nokia Monitor Test,产生标准的视频信号软件。

B.匹配阻抗75欧C.示波器PXI-59222)规格与时序A.规格a.红基色: VPP=1.4V,Vmax=700mvb.绿基色: VPP=1.4V,Vmax=700mvc.蓝基色: VPP=1.4V,Vmax=700mvd.场同步: TTL脉冲电平,每扫描完一场输出一个脉冲。

VGA时序

尚丽娜

VGA(Video Graphics Array)是IBM于 1987年提出的一个使用模拟信号的电脑显示 标准。VGA一改以前显示卡采用的数字视频 信号输出, 而用模拟视频信号输出, VGA 卡内 的D/A 转换器将数字信号转换为控制R、G、 B 三原色的模拟信号, 使像素色彩变化非常平 滑, 更适合人的视觉感受

确定VGA显示接口时序主要应考虑行同步信 号(HSYNC)、场同步信号(VSYNC)、蓝基色 (B)、红基色(R)、绿基色(G)这5个信号,如 果能从FPGA中按其时的需要求准确发送这 些信号到VGA接口。就可以实现对VGA的控 制。

产生行同步脉冲信号HSYNC的周期 e=a+b+c+d。其中a为同步信号时间,b为行 消隐后肩时间,c为数据有效时间,d为行消 隐前肩。从图(b)可以看出,场同步时序与行 同步时序类似。也是显示一屏数据的时 序.这里以行为单位。场同步脉冲信号 VSYNC的周期L=h+i+j+k.其中h为同步信 号时间,i为场消隐后肩时间,j为数据有效时 间,k为场消隐前肩时间。

module vga_time_generator(

input pixel_clk,

input [11:0]h_disp,//640 input [11:0]h_fporch,//16 input [11:0]h_sync, //96 input [11:0]h_bporch,//48

wire [11:0] h_total; assign h_total = h_disp+h_fporch+h_sync+h_bporch; reg [11:0]h_counter; reg VGA_HS_o; reg VGA_BLANK_HS_o; always @(posedge pixel_clk)begin if (h_counter < (h_total-1) ) h_counter <= h_counter+1; else h_counter <= 0; end

基于Verilog的VGA显示控制电路设计

0 引言近年来,随着数字电路设计技术的逐步发展,集成电路的发展越来越趋近于超大规模、更低功耗及超高速[1]。

Verilog HDL就是在迫切需要设计者使用EDA工具完成大规模集成电路设计发展要求的情况下应运而生的,它使用编写代码的方法来完成数字电路的设计,不管是底层的门级电路,还是高层的行为描述,都可以通过代码实现,这种方式大大的提高了数字电路的设计效率[2]。

本文就是采用Verilog_HDL语言来实现一个VGA显示控制电路。

VGA接口由于具有传输速率高,协议简单,成本低等特点,因此被广泛使用。

1 设计原理1.1 VGA时序分析VGA主要用于计算机显卡传输图像到显示器的桥梁,将显卡处理的视频图像数据实时传输到显示器上进行显示。

广义的VGA为VGA显示器,狭义的VGA为VGA分辨率的时序。

由IBM公司推出的采用RGB模拟信号的VGA视频传输标准,定义了具有60Hz刷新频率、可产生1677万种色彩的640×480像素格式。

VGA的行扫描时序情况,如图1所示。

行同步时期a、行消隐后肩b、行显示时期c、行消隐前肩d四部分组成一个完整的扫描周期。

开始扫描,首先进行行同步操作,同步完成后才开始数据的扫描。

同样,场扫描时序图和行扫描时序图类似,如图2所示。

一个场扫描周期由n个行扫描周期所组成。

并且一次场扫描时序由完整的场消隐前肩、场同步时期、场消隐后肩、场显示时期组成,且自成体系。

1.2 VGA分辨率分辨率就是一个用来表示物体精确度的参数,若显示器的分辨率参数越大,则其显示的图像越清晰,包含的信息量越大,画质中的细节越多,图像的保真性越高。

由于人的视觉暂留,想要实现CRT显示器画面不闪烁,至少需收稿日期:2019-03-07*基金项目:四川省教育厅科研基金重点项目(15ZA0145)作者简介:王涌(1994—),男,四川宜宾人,硕士研究生,研究方向:软件无线电、EDA 技术及SOPC 技术。

通讯作者:肖顺文(1970—),男,四川金堂人,硕士,教授,研究方向:软件无线电、EDA 技术及SOPC 技术教学及研究。

VGA显示器工作原理之同步信号

VGA显示器工作原理之同步信号VGA显示器是如何显示图像的?我们的FPGA和MCU要怎样配置才能让VGA显示器正确显示?经常有朋友这样问,网上相关的介绍也不少,我这里从FPGA或MCU的LCD控制器的角度来讨论这个问题。

我们先来看看显示器显示一个图像需要哪些信号(此图来自LCD 显示模组的规格书)从图可以看出,LCD显示图像需要Hsync,Vsync, D[n:0],CLK,DE,而且这些信号要满足上述时序关系,我们再来看VGA显示器的输入信号(此图来自VESA Monitor Timing Specifications )从上图可以看出,这里只有3个信号Hsync,Vsync,Video 和LCD需要的信号比较,Hsync,Vsync,是共同都有的,Video和D[n:0]其实是同一个信号,就是视频信号,显示器要显示的内容,LCD是数字输入的,所以用Data[n:0]来描述了,简写D[n:0],n表示每个像素的灰度,灰度 = 2的n次方,通常取值是8或6;但是还少了DE和CLK 信号。

这里我们来描述VGA显示是如何得到DE和CLK信号的,这也是本文要描述的重点。

Hsync和Vsyn是我们要分析的根本,一个同步信号通常有这几个参数,频率,极性,同步头的宽度。

频率:这个不用说了;极性:有正极性和负极性,信号中高电平时间长,低电平时间短就是负极性,反之就是正极性,前图的LCD信号图中的Hsync就是负极性,VGA显示器输入信号图中的Hsync是正极性;同步头宽度:有些也叫同步时间,就是描述同步信号中较短的电平的时间,通常单位是CLK,可以用时间单位描述;识别分辨率是得到CLK和DE的关键,VESA标准中每个不同的分辨率(包含刷新频率)Hsync,Vsync的频率和极性是不同的,VGA显示器就是根据这个来确定输入图像的分辨率的。

一旦分辨率确定,一切都定了,你就可以查VESA标准得知VGA输入信号图中的全部参数。