(完整版)Xilinx+CPLD介绍

可编程逻辑器件CPLD和FPGA的特点和应用

可编程逻辑器件CPLD和FPGA的特点和应用一、可编程逻辑器件(CPLD)的特点和应用:CPLD是一种具有很高逻辑容量的可编程逻辑器件,它通常由可编程逻辑单元(PLE)和可编程互连网络(PIN)组成。

CPLD的主要特点如下:1.逻辑容量大:CPLD的逻辑容量通常可以达到数千个逻辑门等效。

这使得CPLD非常适合那些需要大规模逻辑功能的应用,如控制器、通信接口和高级数学运算等。

2.可编程性强:CPLD可以通过编程操作来实现不同的逻辑功能。

它使用类似于电荷耦合器(CPL)的可编程逻辑单元来实现逻辑功能,其中每个CPL可以实现与或非门、与非门或非与门等逻辑运算。

3.器件内部拓扑复杂:CPLD具有丰富的内部互连网络,可以将各个逻辑元件之间的信号按照需要进行连接。

这使得CPLD可以实现复杂的信号处理和数据流处理功能。

4.快速重编程:CPLD可以在运行时进行在线编程,从而允许系统进行动态配置和故障恢复。

这一特点使得CPLD广泛应用于技术验证、原型设计和快速迭代开发等场景。

CPLD的应用主要集中在以下几个领域:1.控制器:CPLD可以用于实现各种控制器,如数字信号处理器(DSP)的外围控制器、数据采集/输出控制器等。

其高逻辑容量和可编程性强的特点使得CPLD非常适合这些应用场景。

2. 通信接口:CPLD可以实现多种通信协议和接口,如串行通信接口(SPI/I2C/UART)、嵌入式总线接口(PCI/USB/Ethernet)等。

这些接口在通信系统中起到了关键的作用。

3.高级数学运算:CPLD可以实现各种高级数学运算,如矩阵运算、滤波运算、FFT运算等。

这些运算对于数字信号处理(DSP)和图像处理等应用非常重要。

4.逻辑分析仪:CPLD可以实现逻辑分析仪的功能,用于捕获和分析数字信号的时序和逻辑关系。

逻辑分析仪在系统调试和故障分析中非常有用。

二、现场可编程门阵列(FPGA)的特点和应用:FPGA是一种具有大规模逻辑容量和可编程性的可编程逻辑器件。

CPLD简介

CPLD简介CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL 和GAL(通用逻辑阵列)器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围,是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。

其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。

CPLD主要是由可编程逻辑宏单元(MC,Macro Cell)围绕中心的可编程互连矩阵单元组成。

其中MC结构较复杂,并具有复杂的I/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能。

由于CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。

发展历史及应用领域20世纪70年代,最早的可编程逻辑器件--PLD诞生了。

其输出结构是可编程的逻辑宏单元,因为它的硬件结构设计可由软件完成(相当于房子盖好后人工设计局部室内结构),因而它的设计比纯硬件的数字电路具有很强的灵活性,但其过于简单的结构也使它们只能实现规模较小的电路。

为弥补PLD只能设计小规模电路这一缺陷,20世纪80年代中期,推出了复杂可编程逻辑器件--CPLD。

此应用已深入网络、仪器仪表、汽车电子、数控机床、航天测控设备等方面。

器件特点它具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强、价格大众化等特点,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。

几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。

CPLD器件已成为电子产品不可缺少的组成部分,它的设计和应用成为电子工程师必备的一种技能。

fpGa_CPLD设计工具xilinxISE使用详解

1.第一章:FPGA/CPLD简介●FPGA一般是基于SRAM工艺的,其基于可编程逻辑单元通常是由查找表(LUT,look up table)和寄存器(register)组成。

其中内部的查找表通常是4输入的,查找表一般完成纯组合逻辑功能;●Xilinx可编程逻辑单元叫做slice,它由上下两部分组成,每部分都由一个register加上一个LUT组成,被称为LC(logic cell,逻辑单元),两个LC之间有一些共用逻辑,可以完成LC之间的配合工作与级连;●Altera可编程逻辑单元叫做LE(Logic Element,逻辑单元),由一个register加上一个LUT构成;Lattice的底层逻辑单元叫做PFU(programmable Function unit,可编程功能单元),它由8个LUT和9个register组成。

●Ram和dpram/spram/伪双口RAM,CAM(content addressable memory)。

Fpga中其实没有专业的rom硬件资源,实现ROM是对RAM赋初置,并且保存此初值●CAM,即内容地址储存器,在其每个存储单元都包含了一个内嵌的比较逻辑,写入cam的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所以内部数据的地址。

总结:RAM是一种根据地址读/写数据的存储单元;而CAM 和RAM恰恰相反,它返回的是与端口数据相匹配的内部地址。

使用很广,比如路由器中的地址交换表等等●Xilinx块ram大小是4kbit和18kbit两种结构。

Lattice块ram是9kbit●分布式ram适合用于多块小容量的ram的设计;●Dll(delay-locked loop)延迟锁定回环或者pll(phase locked loop)锁相环,可以用以完成时钟的高精度,地抖动的倍频/分频/占空比调整/移相等功能。

Xilinx主要集成的是DLL,叫做CLKDLL,在高端的FPGA中,CLKDLL的增强型模块为DCM (digital clock manager,数字时钟管理模块)。

cpld原理

cpld原理

CPLD是复杂可编程逻辑器件(Complex Programmable Logic Device)的缩写,它是一种集成电路芯片,通过对其内部的逻

辑门、触发器和可编程互连资源进行编程,实现不同的逻辑功能。

CPLD的原理主要基于可编程逻辑阵列(PAL)和可编程压缩

阵列(GAL)。

它由一个或多个可编程逻辑单元(PLU)或宏单元组成,每个单元包含逻辑门和触发器等基本逻辑元件。

CPLD的内部结构主要由两部分组成:可编程逻辑单元(PLU)和全局输入/输出(IO)资源。

PLU是CPLD的核心部分,它由多个可编程逻辑单元组成,

每个单元接收输入信号并输出相应的逻辑运算结果。

其中每个单元可以实现任意的逻辑功能,并通过互连通道与其他单元进行连接。

全局IO资源用于连接CPLD与外部器件,包括输入输出引脚、时钟信号等。

它提供了与外界通信的接口。

CPLD的编程通常采用硬件描述语言(HDL)或可编程逻辑阶

梯(PLD)语言,如VHDL、Verilog等。

通过编写逻辑描述

代码,并使用专门的软件工具进行综合、布局和布线,可以将逻辑功能转化为CPLD内部资源的配置和连接。

在编程完成后,CPLD可以实现各种逻辑功能,如组合逻辑、

时序逻辑、状态机等。

它还可以实现多个逻辑块之间的通信和控制,具有较高的灵活性和可扩展性。

总而言之,CPLD原理是通过对其内部逻辑资源进行编程,实

现不同的逻辑功能。

它由可编程逻辑单元和全局IO资源组成,通过编写逻辑描述代码并使用专门的软件工具进行编程,可以实现各种逻辑功能,并与外部器件进行通信和控制。

复杂可编程逻辑器件CPLD

- -进程语句,用a、b信号触发进程执行

MAX

65 64

23

63

24 25

EPM7128SLC84

62 61

26

60

27

59

28

58

29

57

30

56

31

55

32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54

CPU编程数据经过此端口下

GND

I/O.TD0 载到CPLD中旳

暂存数据。 如: VARIABLE a,b:STD_LOGIC;- -定义a,b为原则逻辑位变量

✓信号阐明语句: 信号有IN、OUT、INOUT、BUFFER4种流动方向。分外部端

口和内部信号,其作用是在设计旳单元电路之间实现互连 如:SIGNAL b:BIT; - -定义b为位逻辑型信号

3.变量与信号旳赋值语句

1脚: 全局清零端

2、83脚: 2个全局时钟输入端

VCCIO

GND VCCINT GND VCCIO

取得最高旳工作速度

专用输入脚,不用时不允许悬空,预防CMOS器件输 入击穿损坏。

VCCIO

GND INPUT/GCLK1

INPUT/OE1 INPUT/GCLRn INPUT/OE2/GCVLCCKIN2T

VHDL语言对硬件系统旳描述, 有三种描述方式:行为描述、 数据流描述、构造化描述。

输入端口描述

逻辑关系描述

输出端口描述

实体(ENTITY)描述

构造体 (ARCHITECTURE) 描述

VHDL 程序

库支持: 定义程序中所涉及旳数据类型、元件和子程序等。

精品课件-Xilinx FPGACPLD设计初级教程-第1章

第1章 PLD概述

2) 现场可编程门阵列(Field Programmable Gate Array, FPGA)

FPGA是在PAL、GAL、PLD等可编程器件的基础上进一步发 展的产物。它是作为专用集成电路(ASIC)领域中的一种半定 制电路出现的,既解决了定制电路的不足,又克服了原有可编 程器件门电路数有限的缺点。FPGA采用了逻辑单元阵列 LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻 辑模块CLB(Configurable Logic Bolck)、输入/输出模块 IOB(Input Output Block)和内部连线(Interconnect)三个部 分。可以说,FPGA芯片是小批量系统提高系统集成度、可靠 性的最佳选择之一。

CPLD是从PAL和GAL器件发展起来的,相对而言规模大, 结构复杂,属于大规模集成电路范围。CPLD也是当前另一主 流的PLD器件。

第1章 PLD概述

现在PLD器件仍向着高密度、高速度、低功耗的方向发展。 特别是FPGA器件,现在它的集成度已经不能和以前的FPGA相 提并论。另外,由于专用集成电路(ASIC)芯片设计具有周期 长、难点多、耗资大等缺点,因此用PLD器件来代替一般的 ASIC芯片进行设计已经成为一种发展趋势。

3) 可编程阵列逻辑(Programmable Array Logic,PAL) PAL是20世纪70年代末由MMI公司率先推出的一种可编程 逻辑器件。它采用双极型工艺制作,并采用熔丝编程方式。 PAL器件由可编程的与逻辑阵列、固定的或逻辑阵列和输出电 路三部分组成。通过对与逻辑阵列编程可以获得不同形式的组 合逻辑函数。

CPLD基本结构

CPLD的基本结构1.基于乘积项的CPLDCPLD (Complex Programmable Logic Device)直译的话称为复杂可编程逻辑芯片。

它也属于大规模集成电路LSI (Large Scale Integrated Circuit)里的专用集成电路ASIC (Application Specific Integrated Circuit)。

适合控制密集型数字型数字系统设计,其时延控制方便。

CPLD是目前集成电路中发展最快的器件之一.结构C PLDPLD即programmable logic device,译为可编程逻辑器件,是一个可以产生任意逻辑输出的通用型数字逻辑电路器件。

PLD有很高的集成度,足以满足设计一般的数字系统的需要,与门、或门、非门是PLD最基本的构成。

的结构是基于乘积项(Product-te rm)的,现在以Xilinx公司的XC9500XL系列芯片为例介绍CPLD的基本结构,如图1所示,其他型号CPLD的结构与此非常类似。

CPLD可分为3部分:功能模块(Functi ON Block)、快速互连矩阵(FastCON NEC T ⅡSwitch Matrix)和I/O控制模块。

每个功能模块包括可编程与阵列、乘积项分配器分配器是有线电视传输系统中分配网络里最常用的部件,用来分配信号的部件。

它的功能是将一路输入信号均等地分成几路输出,通常有二分配、三分配、四分配、六分配等。

有线电视网的频率不断提升,功能不断加强,因此对分配器的要求不断提高。

在接口设备上分配器是将音视频信号分配至多个显示设备或投影显示系统上的一种控制设备。

它是专门分配信号的接口形式的设备. [全文]和18个宏单元,功能模块的结构如图2所示.快速互连矩阵负责信号传递,连接所有的功能模块.I/O控制模块负责输人输出的电气特性控制,比如可以设定集电极开路输出、三态输出等。

图1中的I/O/GCK,I/O/GSR,1/0/GTS是全局时钟、全局复位和全局输出使能信号,这几个信号有专用连线与CPLD中每个功能模块相连,信号到每个功能模块的延时相同并且延时最短。

(完整版)CPLD选型

经过几十年的发展,全球各大开发商和供货商都开发出了多种可编程逻辑器件 . 比较典型的就是Xilinx 公司的FPGA 器件和Altera 公司的CPLD 器件系列,他们开发较早,占有大部分市场?在欧洲用Xilinx 的人多,而Altera 公司占有日本和亚太地区的大部分市场,在美国则是平分秋色。

以上两家公司占有了全球60% 以上的市场份额,他们共同决定了PLD 技术的发展方向。

Lattice 公司在1999 年收购了Vantis ,成为第三大PLD 供应商。

其它供货商还有Actel ,Quicklogic ,Lucent 等等,下面作一简要介绍:Altera 公司是90 年代以后发展最快、最大的可编程逻辑器件供应商之一。

主要产品有: MAX3000/7000 ,FLEX10K ,APEX20K ,ACEX1K ,Stratix ,Cyclone 等;开发软件为MaxplusⅡ和QuartusⅡ。

其中MaxplusⅡ是公认的最成功的PLD 开发平台之一,配合使用Altera 公司提供的免费OEM HDL 综合工具可以达到最高的效率。

公司提供免费试用版或演示版( 当然商业版大都要收费的) ,可以免费从其公司网站上下载MaxplusⅡ(BASELINE 版或学生版) ,或向其代理商索取该软件,然后再从其专业网站上申请注册文件license 进行注册以后便可使用。

这套软件能够满足一般学习和简单开发的要求?Xilinx 公司是FPGA 的发明者,也是全球最大的可编程逻辑器件的供应商之一。

产品种类较全,主要有:XC9500/4000 ,Coolrunner(XPLA3) ,Spartan ,Virtex 等;开发软件为Foundation 和ISE 。

ISE(Integrated System Configuration) 提供从设计输入、仿真、编译、布局布线和下载的全程功能,其最新版本为6 .1 版,支持Xilinx 公司推出的所有最新的FPGA 器件,如Virtex-ⅡPro ,Virtex-Ⅱ,Spartan-ⅡE 和coolrunner-Ⅱ。

CPLD

第一章1数字电子系统:简称为数字系统。

是可以完成某种(或多种)特定的、功能不单一的一种电子系统。

2数字器件:即数字IC芯片。

是构成数字系统的基本部件,是数字系统的“元素”或“细胞”。

3一个数字电子设备(产品),小到一个数字电子钟,大到一台数控车床或超级计算机,都是一个“数字电子系统”。

4数字系统与数字器件的主要区别数字系统一般应包含某种控制器及受控单元,并且功能不那么单一。

5单片系统集成度高、功耗低、功能强大,工作可靠.编程逻辑器件PLD是一种通用的电子器件,其功能不是固定不变的,而是可根据用户的需要而进行改变,即:可通过编程设计的方法来定义器件的逻辑功能。

但是PLD与MCU有基本的不同:MCU是通过软件(指令)来实现预期的功能;而PLD是通过内部硬件布线、以硬件来实现预期的功能。

所以PLD完成逻辑功能的工作速度比MCU要快得多。

构建数字系统的途径1.标准化的中、小规模数字集成电路。

标准化的中、小规模数字集成电路是设计数字系统的基本方法之一。

2.2.基于LSI(大规模集成)或VLSI(超大规模集成技术)的微处理器。

如各种通用或嵌入式CPU、MCU(微控制器)及数字信号处理器DSP。

特点:CPU、MCU、DSP依靠执行指令(软件)可以方便的实现几乎任意的数字逻辑功能,其应用灵活性极强。

但这些微处理器一般需要一定的数字接口器件相配合才能有效工作;依靠执行软件来完成数字逻辑功能的工作方法导致其工作速度相对较慢,故在一些需要高速、实时工作的应用场合它们的应用就受到一定的限制。

3.基于LSI或VLSI的专用集成电路ASICASIC是一种为完成某种特定的电路功能而专门设计、生产的IC器件。

按功能的不同可分为:数字ASIC、模拟ASIC及混合型ASIC4.基于LSI/VLSI的可编程逻辑器件PLD 由用户自定义器件的功能、大规模集成。

设计周期短、设计风险低、应用灵活、系统功能强大、功耗低。

最早的可编程逻辑器件就是5. 可写入存贮器(PROM),包括(三种)6.▲可编程只读存贮器(PROM)、7.▲紫外线可擦除的只读存贮器(EPROM)8.▲电可擦除只读存贮器(EEPROM) 。

(完整版)Xilinx+CPLD介绍

XC95144XV 144 3200 144 5 3.5 3.5 222 2

续表 XC95288XL

6 4.0 3.8 208

XC95288XV 288 6400 288 6 4 3.8 208 4

表 1-4 XC9500 CPLD 封装及 I/O 引脚数

XC9536

XC9572

XC95108

XC95144

1.1.1 XC9500 系列 CPLD 器件

Xilinx 公司的 CPLD 器件被广泛地应用在通信系统、网络、计算机系统及控制系统等电 子系统中。 XC9500 系列 CPLD 器件的 tPD 最快达 3.5ns,宏单元数达 288 个,可用门数达 6400 个,系统时钟可达到 200MHz 。XC9500 系列器件采用快闪存储技术 ( FastFLASH ),与 E2CMOS 工艺相比,功耗明显降低。 XC9500 系列产品均符合 PCI 总线规范;含 JTAG 测试接口电路, 具有可测试性;具有在系统可编程( In System Programmable , ISP)能力。

XC9500XL 和 XC9500XV 器件为低电压、低功耗的 CPLD 器件,使用 XC9500XV 器件 可以比 XC9500 器件节省 75%的功率,同时成本也大大降低。低电压不仅具有最佳的系统性

能,同时确保灵活性和布通率, 可以很方便地设计出工作频率近 200MHz 的快速同步 DRAM

控制器以及与微处理器配合更紧密的接口。

100

112(TQFP160 )、192( BGA256 )

100

384(BGA492 )

200

32(VQFO44 、CSP48)

32(VQFP44 )、 167

44(CSP56)、 64( VQFP100 )

CPLD入门知识简单描述

CPLD入门知识简单描述CPLD按英语说是复杂器件,对于一个硬件工程师来说,能应用cpld技术是一个十分强大的能力。

它的应用可在根本上解决许多设计的问题,能大幅度改变设计思想,大幅度提高工作效率,甚至可以把以前的数十颗普通分立芯片的功能用一个芯片实现。

它还有一个十分优秀的优点,在硬件原理设计和布线的时候,不用考虑引脚的顺序,可从布线方便的角度安排需要的信号位置,使得布线难度大幅度降低。

由于布线难度下降,直接带来布线优化的好处。

本文就cpld初学者面对的问题做一个简单描述。

希望对有志于学习cpld的硬件工程师有所启发。

我的老师大学毕业时,还没有cpld呢,可现在是他在指导我做fpga设计工作。

1:首先进行的准备是有针对性的学习cpld物理构造和资源先不要着急去买开发板,不要着急写逻辑。

了解硬件本身更加重要。

Cpld 是一个很大的范畴,初学者会淹没在众多厂家、众多资料的海洋中。

针对这个问题,笔者建议大家有所针对的进行知识获取,推荐大家以altera的max ii一个小技巧,针对EPM240和570来说,常用的封装是T100的,就是TQFP100,这2个芯片的封装是向下兼容的,因此,设计时,即便决定使用240,也要按570去画板子。

焊接是兼容的,同时万一 240不够了,可以改焊570。

2:向应用cpld走近一步,用开发板练习。

有了上面的基础,可以投资买开发板了,一般卖板子的都配套好软件和编程器了。

针对240的开发板可能很少,可能570的好买。

注意买cpld的开发板, 不要急于用fpga的,学会cpld之后,再用fpga就容易多了。

要一步一步来。

570的开发板,带仿真器,带软件,带练习光盘,一整套下来估计200-300元人民币。

这个资金对你要学会的技术来说,微不足道。

开发板光盘有许多例子程序,可以先跑跑看,很容易就上手了。

对于初学者来说,cpld技术是一个很大的领域,切记不要急于求成,上来就弄个fpga 去加载视频编解码算法,那会十分困难。

CPLD简介

利用 CPLD 进行设计

了解 CPLD 使用的特性与优势, 有助于简化设计、降低开发成本并加速产品上 unner-II 1.8

宏单元

32-512

I/O

21-270

I/O 容限

1.5V、1.8V、2.5V、3.3V

TPD / ƒ max (最快)

3.8/323

超低待机功耗

28.8µW*

I/O 标准

LVTTL、LVCMOS、HSTL、SSTL

*利用 CoolRunner-II 高级特性 DataGATE,可实现最低的系统功耗。

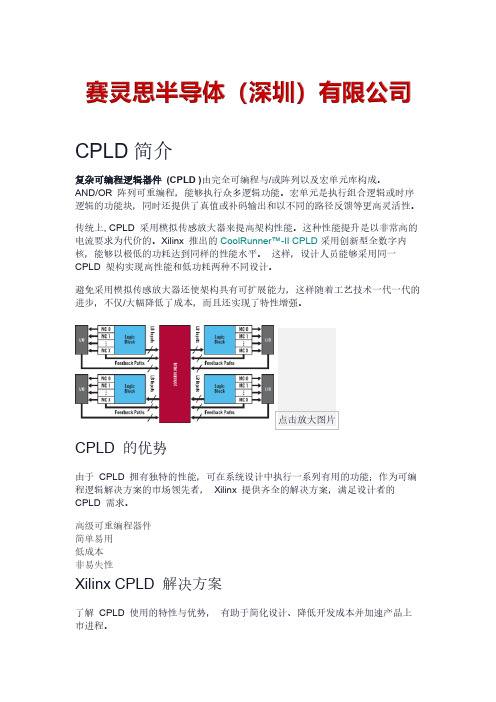

CPLD 简介

复杂可编程逻辑器件 (CPLD )由完全可编程与/或阵列以及宏单元库构成。 AND/OR 阵列可重编程,能够执行众多逻辑功能。宏单元是执行组合逻辑或时序 逻辑的功能块,同时还提供了真值或补码输出和以不同的路径反馈等更高灵活性。 传统上, CPLD 采用模拟传感放大器来提高架构性能。这种性能提升是以非常高的 电流要求为代价的。Xilinx 推出的 CoolRunner™-II CPLD 采用创新型全数字内 核,能够以极低的功耗达到同样的性能水平。 这样,设计人员能够采用同一 CPLD 架构实现高性能和低功耗两种不同设计。 避免采用模拟传感放大器还使架构具有可扩展能力,这样随着工艺技术一代一代的 进步,不仅/大幅降低了成本,而且还实现了特性增强。

点击放大图片

CPLD 的优势

由于 CPLD 拥有独特的性能,可在系统设计中执行一系列有用的功能;作为可编 程逻辑解决方案的市场领先者, Xilinx 提供齐全的解决方案,满足设计者的 CPLD 需求。 高级可重编程器件 简单易用 低成本 非易失性

Xilinx CPLD 解决方案

了解 CPLD 使用的特性与优势, 有助于简化设计、降低开发成本并加速产品上 市进程。

cpld芯片

cpld芯片CPLD(Complex Programmable Logic Device)是一种数字逻辑设备,它集成了大量可编程逻辑门和时钟控制器等元件。

在数字电路设计中,CPLD芯片可以用来实现各种逻辑函数和时序控制。

CPLD芯片由可编程逻辑单元(PLU)、输入/输出单元(IOU)、时钟管理单元(CMU)、区域互连单元(ACU)等主要功能模块构成。

其中,可编程逻辑单元是最重要的部分,它由逻辑单元阵列(Logic Array)和可编程互连单元(Programmable Interconnect Array)组成。

逻辑单元阵列是由一系列的逻辑门组成,逻辑门的功能可以通过编程来定义。

可编程互连单元可以实现逻辑单元之间的互联,通过编程来确定信号的传输路径。

CPLD芯片的可编程性使其在数字电路设计中具有很大的灵活性和适应性。

首先,CPLD芯片具有丰富的逻辑门资源,可以实现各种逻辑函数。

其次,CPLD芯片可以通过编程来定义逻辑函数和时序控制。

设计人员可以使用硬件描述语言(HDL)来描述所需的逻辑函数和时序控制,然后通过编程工具将其烧录到CPLD芯片中。

这样,可以在不改变硬件电路的情况下,通过重新编程来改变系统的功能,提高设计的灵活性。

CPLD芯片还具有较快的响应速度和较低的功耗。

由于CPLD芯片内部采用了并行计算的结构,可以同时执行多个逻辑操作,提高了响应速度。

同时,CPLD芯片的功耗较低,可以满足一些功耗敏感的应用场景。

CPLD芯片在数字逻辑设计中有着广泛的应用。

例如,可以使用CPLD芯片来实现数字系统中的逻辑函数、时序控制和状态机等功能。

另外,CPLD芯片还可以用于FPGA(Field Programmable Gate Array)的前端逻辑设计,实现FPGA芯片中部分逻辑和时序控制功能的优化。

总的来说,CPLD芯片是一种功能强大、灵活性高且易编程的数字逻辑设备。

它可以用于实现各种逻辑函数和时序控制,具有较快的响应速度和较低的功耗。

Xilinx CPLD 在线编程参考指南

Xilinx CPLD 在线编程参考指南广州致远电子股份有限公司目录1. Xilinx CPLD简介 (1)2. AK100Pro-4P简介 (2)3. 准备条件 (4)3.1准备待烧写板 (4)3.2安装KFlashPro软件 (4)3.3连接待烧写板至AK100Pro-4P (5)4. 基本烧写 (7)4.1创建工程 (7)4.2参数配置 (7)4.2.1硬件选择 (7)4.2.2主要设置 (8)4.2.3程序烧写 (9)4.3烧写配置 (10)4.4进行烧写 (11)5. 高级烧写 (12)5.1量产烧写配置 (13)5.2加密与解密 (14)5.2.1加密 (14)5.2.2解密 (15)6. 技术支持 (16)7. 订购信息 (17)1. Xilinx CPLD简介Xilinx的CPLD有CoolRunner TM-Ⅱ家族和XC9500XL家族的芯片。

被广泛地应用在通信系统、网络、计算机系统及控制系统等电子系统中。

CoolRunner TM-Ⅱ家族的芯片具有小封装、高性能、低功耗的特点。

采用0.18微米制造工艺,核心电压1.8V,IO口兼容1.5V、1.8V、2.5V和3.3V操作。

Xilinx CoolRunner TM-ⅡCPLD器件提供高运算速度,易于与XC9500/XL/XV系列CPLD联合使用。

在单一CPLD 里,消耗极低的功率可实现XPLA3TM系列多功能性。

这一点意味着通过系统内可编程功能使得原来同一部分可被用作数据高速通信、计算系统以及使得便携式产品达到其领先技术水平。

功率的低功耗和运算的高速度结合于同一器件中,使得运用更容易、花费更有效。

已经获得Xilinx专利的FZP(Fast Zero Power TM)结构提供固有的低功率性能,而不需要任何专门的设计措施。

Clocking技术和其他的能量节省特性延伸了用户的功率预算。

XC9500XL家族的芯片采用闪存储技术(FastFLASH),符合PCI总线规范。

CPLD(复杂可编程逻辑器件)

FPGA与CPLD的辨别和分类

FPGA与CPLD的辨别和分类主要是根据其结构特点和工作原理。通常的分类方法是: 将以乘积项结构方式构成逻辑行为的器件称为CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列、Altera的MAX7000S系列和Lattice(原Vantis)的Mach系列等。

CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统.

将以查表法结构方式构成逻辑行为的器件称为FPGA,如Xilinx的SPARTAN系列、Altera的FLEX10K或ACEX1K系列等。

尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于CPLD和FPGA结构上的差异,具有各自的特点:

①CPLD更适合完成各种算法和组合逻辑,FP GA更适合于完成时序逻辑。换句话说,FPGA更适合于触发器丰富的结构,而CPLD更适合于触发器有限而乘积项丰富的结构。

器件特点

它具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强、价格大众化等特点,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。CPLD器件已成为电子产品不可缺少的组成部分,它的设计和应用成为电子工程师必备的一种技能。

(完整版)Xilinx+CPLD介绍

144 3200

72

108

144

7.5

7.5

7.5

4.5

4.5

4.5

4.5

4.5

4.5

125

125

125

83.3

83.3

83.3

XC95216 216 4800 216 10 6.0 6.0 111.1 66.7

XC95288 288 6400 288 15 8.0 8.0 92.2 56.6

系列器件 宏单元 可用门数 寄存器

XC95144XV 144 3200 144 5 3.5 3.5 222 2

续表 XC95288XL

6 4.0 3.8 208

XC95288XV 288 6400 288 6 4 3.8 208 4

表 1-4 XC9500 CPLD 封装及 I/O 引脚数

XC9536

XC9572

XC95108

XC95144

36

144 脚 CSP

256 脚 BGA

34

52

72

81

117

117

168

38

117

192

XC9500 系列产品采用第二代 “支持 ISP”的引脚锁定结构, 它拥有一个 54bit 输入函数块, 使用户可以在进行多种改变的同时保持输出引脚固定。 这个特点给设计带来了灵活性, 如时钟

完全受控。既可以对每个宏单元作输出使能反转,也可对个别的乘积项时钟作使能反转。

件。 1999 年 8 月, Xilinx 收购了 Philips 的 CoolRunner 生产线并开始提供 XPLA (eXtenden

Programmable Logic Array ,加强型可编程逻辑阵列)系列器件,如表

CPLD、FPGA简介

可以獲得最佳的性能(如速ቤተ መጻሕፍቲ ባይዱ、功率)、 最高的元件密集度(即最小的晶片面積)

成本高

8

Cell Based ICs

晶細胞IC乃將設計之邏輯電路中的不 同模組,均先以Cell方式建立,而所設 計完成之Cell 儲存在Cell Library,可供 以後使用,設計時只需配置及繞線即 可

節省設計時間、金錢 製造時間長

CPLD/FPGA 簡介

控制與訊號處理實驗室

1

數位電路設計的發展

CPLD简介

的开关矩阵)实现相互连接。

1 CPLD的结构

更多成积项、更多宏单元、更多的输入信号。

逻辑块

可 编 程 内 部

I/O

逻辑块

逻辑块

逻辑块

I/O

连

逻辑块

线 矩 阵

逻辑块

逻辑块

逻辑块

通用的CPLD器件逻辑块的结构

宏单元 1

内部 可编 程连 线区

n

可编 程乘 积项 阵列

乘积 项分 配

宏单元 2

宏单元 3 宏单元 m

多个CPLD器件串行编程 将多个CPLD器件以串行的方式连接起来,一次完成多个器件 的编程。这种连接方式称为菊花链连接。

TDII1 SDO 1 SDI2

EPM7032S U2 SDO 2 SDI3

EPM7032S U3 SDO 3

CPLD与FPGA的区别

80个36变量的乘积项宏单元16个到上一个宏单元来自上一个宏单元乘积项分配电路g3s8g2g1s6s7乘积全局复位m2s1s2s3s4s5m1m4g5g4全局时钟clkffm5全局置位乘积项复位乘积项输出使能oem3到内部可编程连线区ptoe到下一个宏单元来自下一个宏单元单元outxg500系列乘积项分配和宏单元可编程数据分配可编程数据选择器宏输出可编程内部连线可编程内部连线的作用是实现逻辑块与逻辑块之间逻辑块与io块之间以及全局信号到逻辑块和io块之间的连接

m m

内部 可编 程连 线区 I/O 块

Xilnx XG500: 90个36变量的乘积项,宏单元36个

Altera MAX7000:80个36变量的乘积项,宏单元16个

XG500系列乘积项分配和宏单元

可编程 数据分配 器

到上一个宏单元 来自上一个宏单元 全局置位 乘积项分配电路 全局复位 S6 G1 S7 S1 S2 S3 S4 S5 来自下一个宏单元 到下一个宏单元 G2 S 8 G3 1 0 M1 G4 3 M4 乘积项 复位 M5 乘积项输出使能 OE 乘积 项置 位 全局时钟 3 M2 G5 到内部可编 程连线区

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

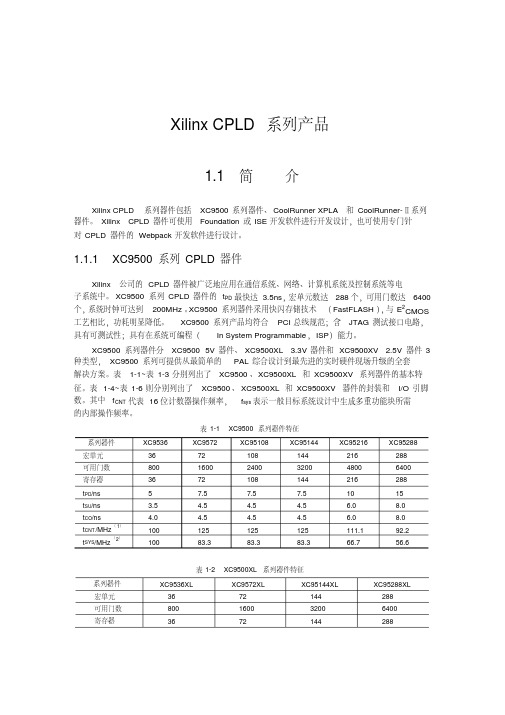

Xilinx CPLD系列产品1.1 简介Xilinx CPLD 系列器件包括XC9500系列器件、CoolRunner XPLA 和CoolRunner-Ⅱ系列器件。

Xilinx CPLD器件可使用Foundation或ISE开发软件进行开发设计,也可使用专门针对CPLD器件的Webpack开发软件进行设计。

1.1.1 XC9500系列CPLD器件Xilinx 公司的CPLD器件被广泛地应用在通信系统、网络、计算机系统及控制系统等电子系统中。

XC9500系列CPLD器件的t PD最快达3.5ns,宏单元数达288个,可用门数达6400个,系统时钟可达到200MHz。

XC9500系列器件采用快闪存储技术(FastFLASH),与E2CMOS 工艺相比,功耗明显降低。

XC9500系列产品均符合PCI总线规范;含JTAG测试接口电路,具有可测试性;具有在系统可编程(In System Programmable,ISP)能力。

XC9500系列器件分XC9500 5V器件、XC9500XL 3.3V器件和XC9500XV 2.5V器件3种类型,XC9500系列可提供从最简单的PAL综合设计到最先进的实时硬件现场升级的全套解决方案。

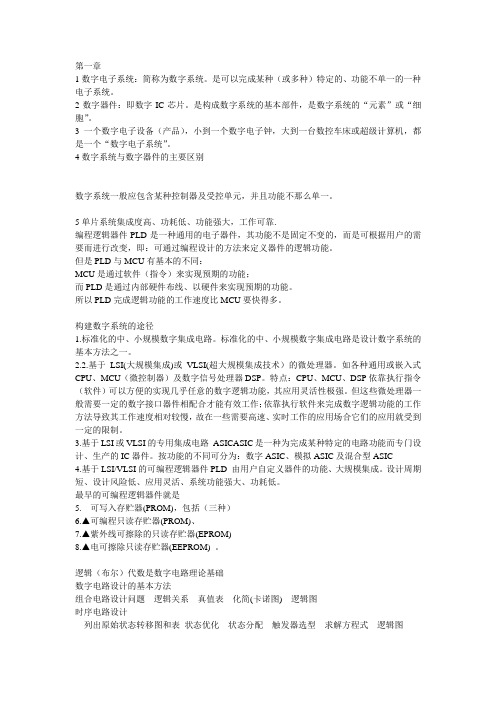

表1-1~表1-3分别列出了XC9500、XC9500XL和XC9500XV系列器件的基本特征。

表1-4~表1-6则分别列出了XC9500、XC9500XL和XC9500XV器件的封装和I/O引脚数。

其中f CNT代表16位计数器操作频率,f sys表示一般目标系统设计中生成多重功能块所需的内部操作频率。

表1-1 XC9500系列器件特征表1-2 XC9500XL系列器件特征表1-3 XC9500XV系列器件特征表1-4 XC9500 CPLD封装及I/O引脚数·7·表1-6 XC9500XV CPLD封装及I/O引脚数(不包括4个专用JTAG引脚)XC9500系列产品采用第二代“支持ISP”的引脚锁定结构,它拥有一个54bit输入函数块,使用户可以在进行多种改变的同时保持输出引脚固定。

这个特点给设计带来了灵活性,如时钟完全受控。

既可以对每个宏单元作输出使能反转,也可对个别的乘积项时钟作使能反转。

XC9500XL和XC9500XV器件为低电压、低功耗的CPLD器件,使用XC9500XV器件可以比XC9500器件节省75%的功率,同时成本也大大降低。

低电压不仅具有最佳的系统性能,同时确保灵活性和布通率,可以很方便地设计出工作频率近200MHz的快速同步DRAM 控制器以及与微处理器配合更紧密的接口。

与XC9500相比,XC9500XL和XC9500XV除具有速度优势外,性能也增强了许多。

它增加了用于动态噪声控制的输入滞后功能,还增加了一条支持改进的互连测试的JTAGQ钳位指令。

XC9500系列器件主要有以下几个特点。

(1)高密度:XC9500系列器件内有36~288个宏单元(每个宏单元内有一个寄存器),800~6400个等效门,封装引脚44~352个。

(2)高性能:XC9500系列器件所有信号都有相同的延时,而与其路径无关。

其引脚到引脚的传输时间t PD最快可达3.5ns,相应的计数器频率f CNT可达125MHz。

XC9500XL CPLD 器件t PD最快可达4ns,相应的计数器频率f CNT可达200MHz。

(3)系统内编程:所有XC9500系列器件均含有JTAG测试接口电路,具有5V或3.3V 系统内编程(ISP)能力,且达到最小1万次编程/擦除次数。

系统内编程通过边界扫描测试引脚进行。

(4)快速闪存技术:所有XC9500系列器件均采用先进的CMOS 0.35μm FastFlash技术,比E2CMOS工艺功耗明显降低。

(5)5V和3.3V工作电压混合模式:XC9500系列器件可在5V正常电压和3.3V的低电压条件下安全工作。

低电压器件XC9500XL CPLD具有比XC9500 CPLD更高的性能,其输出电压为3.3V或2.5V,其I/O引脚可接受5V、3.3V和2.5V的电压输入。

这两种器件均可安全地工作在混合电压系统中。

XC9500XL CPLD器件的输出可作为XC9500 CPLD器件的输入,而XC9500 CPLD型器件的输出也可作为XC9500XL CPLD型器件的输入。

(6)保密和抗干扰:XC9500器件包含先进的数据保密特性,它可以完整保护编程数据不被非法读取和擦除。

表1-7所示为4个不同的可用保密设置。

写入保密位提供附加的保护,防止用户偶然的摒除器件或重新编程。

除保密特性外,XC9500 CPLD系列器件的每个I/O都有一个可编程输出摆率控制位,从而可减少系统噪声。

·8·表1-7 数据保密选择(7)驱动负载能力强:XC9500 CPLD的每个输入/输出端口的负载电流可达24mA,与Lattice公司的CPLD相比,其负载能力更强,可直接驱动LED显示而无须附加驱动电路。

(8)增强引脚锁定功能:XC9500系列器件的结构特性注重系统内编程的要求,增强的引脚锁定功能可以避免重做昂贵的印制电路板。

1.1.2 CoolRunner系列CPLD器件Xilinx CoolRunner 系列CPLD器件分CoolRunner-Ⅱ系列和CoolRunner XPLA 3系列器件。

1999年8月,Xilinx收购了Philips的CoolRunner生产线并开始提供XPLA(eXtenden Programmable Logic Array,加强型可编程逻辑阵列)系列器件,如表1-8所示。

表1-8 XPLA系列器件基本特性XPLA系列器件包括加强型器件、XPLA2器件和XPLA3器件,其显著特点是高速度和低功耗,特别适合应用于手持、移动等功耗要求较低的设备,如PDA、笔记本电脑、移动电话等。

表1-8列出了XPLA系列器件的基本特性。

下面以XPLA器件为例,说明XPLA系列器件的主要特点。

(1)高密度:器件含有34~382个宏单元。

·9·(2)高性能:器件所有信号都有相同的延时,与其路径无关。

t PD最快可达4ns。

(3)低功耗:完整的CMOS结构,采用FZP(Fast Zero Power)技术,器件静态电流100μA,正常工作时也比其他公司的CPLD小50%~67%。

(4)总线友好I/O:无须外接上拉电阻,3.3V工作电压,可接受5V I/O信号。

(5)在系统可编程:所有器件具有在系统可编程特性,可达1万次编程/擦除次数。

(6)多时钟:多时钟资源使设计更方便。

Xilinx CoolRunner TM-ⅡCPLD器件提供高运算速度,易于与XC9500/XL/XV系列CPLD 联合使用。

在单一CPLD里,消耗极低的功率可实现XPLA3TM系列多功能性。

这一点意味着通过系统内可编程功能使得原来同一部分可被用作数据高速通信、计算系统以及使得便携式产品达到其领先技术水平。

功率的低功耗和运算的高速度结合于同一器件中,使得运用更容易、花费更有效。

已经获得Xilinx专利的FZP(Fast Zero Power TM)结构提供固有的低功率性能,而不需要任何专门的设计措施。

Clocking技术和其他的能量节省特性延伸了用户的功率预算。

目前,ISE 4.1Ⅰ、WebFITTER和ISE Webpack均支持这一设计特性。

表1-9给出了CoolRunner-ⅡCPLD系列器件的宏单元数和关键时间参数。

表1-10则详细描述了CoolRunner-ⅡCPLD系列器件的高级特性。

而表1-11为CoolRunner-ⅡCPLD包及提供相应的I/O数。

表1-9 CoolRunner-II CPLD系列器件参数表1-10 CoolRunner-II CPLD系列器件特性·10·表1-11 CoolRunner-II CPLD 包及相应的I/O数系列器件XC2C32 XC2C64 XC2C128 XC2C256 XC2C384 XC2C512 PC44 33 33VQ44 33 33CP56 33 45VQ100 64 80 80CP132 100 106TQ144 100 118 118PQ208 173 173 173 FT256 184 212 212 FG324 240 2701.2 XC9500系列器件的结构XC9500系列器件(XC9500、XC9500XL、XC9500XV)在结构上基本相同,如图1-1所示。

图1-1 XC9500系列结构每个XC9500器件是由一个多功能块FB(Function Block)和输入/输出块IOB组成,并有一个开关矩阵FastCONNECT完全互连的子系统。

每个FB提供具有36个输入和18个输·11·出的可编程逻辑;IOB则提供器件输入和输出的缓冲;FastCONNECT开关矩阵将所有输入信号及FB的输出连到FB的输入端。

对于每个FB,有12~18个输出(取决于封装的引脚数)及相关的输出使能信号直接驱动IOB。

在图1-1中,功能块输出线中的粗线直接驱动IOB。

1.功能块如图1-2所示,每个功能块FB由18个独立的宏单元组成,每个宏单元可实现一个组合电路或寄存器的功能。

FB除接收来自FastCONNECT的输入外,还接收全局时钟、输出使能和复位/置位信号。

FB产生驱动FastCONNECT开关矩阵的18个输出,这18个信号和相应的输出使能信号也驱动IOB。

图1-2 XC9500系列功能模块FB的逻辑是利用一个积之和的表达式(即与或阵列)来实现的。

36个输入连同其互补信号共72个信号(对XC9500XL器件来说是54个输入连同其互补信号共108个信号)在可编程与阵列中可形成90个乘积项。

乘积项分配器则将这90个乘积项的任何数目分配到每个宏单元。

每个FB支持局部反馈通道,它允许任何数目的FB输出驱动到它本身的可编程与阵列,而不是输出到FB的外部。

这一特性便于实现非常快速的计数器或状态机功能,因为所有的状态寄存器都在同一个FB之内。

2.宏单元XC9500器件的每个宏单元(Macrocell)可以单独配置成组合或寄存的功能,宏单元和相应的FB逻辑如图1-3所示。

与阵列中的5个直接乘积项用作原始的数据输入。

用OR或XOR门来实现组合功能,它们也可用作时钟、复位/置位和输出使能的控制输入。

乘积项分配器的功能与每个宏单元如何选择利用这5个直接乘积项有关。

宏单元的寄存器可以配置成D触发器或T触发器,也可以被旁路(即该寄存器被忽略),从而使宏单元只作为组合逻辑使用。

每个寄存器均支持非同步的复位与置位,在加电期间,·12·所有的用户寄存器都被初始化为用户定义的预加载状态(默认值为0)。