基于单片机的复杂可编程逻辑器件快速配置方法

采用单片机实现对FPGA的配置

Science &Technology Vision科技视界0引言可编程逻辑器件(PLD)的应用越来越广泛。

基于查找表技术、SRAM 工艺的FPGA 具有密度高且触发器多等特点,多用于复杂的时序逻辑和高速数据处理中。

FPGA 器件由于工艺原因在应用时需要进行数据配置。

配置数据决定了FPGA 内部互连和功能,改变配置数据,也就改变了器件的逻辑功能。

配置数据必须保存在FPGA 器件以外的非易失存储器内,这给实际应用带来了不便[1]。

为了实现在线可重配置(ICR),通常的方法有两种。

一是采用专用的配置芯片(如ALTERA 的EPC1、EPC2等)来存储配置数据。

专用的配置芯片比较昂贵,显著增加了系统成本。

而由于FPGA 器件在数值计算方面明显地劣于微处理器,所以,经常是单片机和FPGA 并行出现在系统中。

应用单片机的剩余程序存储区来存放配置数据,上电后由单片机控制实现对FPGA 器件的数据配置[2]。

本文通过从被动串行(PS)配置时序出发,介绍应用单片机来实现对FPGA 的数据配置方法。

1被动串行配置(PS)及硬件连接FPGA 配置方式主要分为两大类:主动配置和被动配置。

主动配置方式由FPGA 器件引导配置操作过程,它控制着外部存储器和初始化过程;而被动配置方式则由外部计算机或微处理器控制配置过程。

根据数据线的多少又可以将FPGA 器件配置方式分为并行配置和串行配置两大类。

下面介绍用单片机实现的被动串行配置。

几乎所有FPGA 器件都支持被动串行配置。

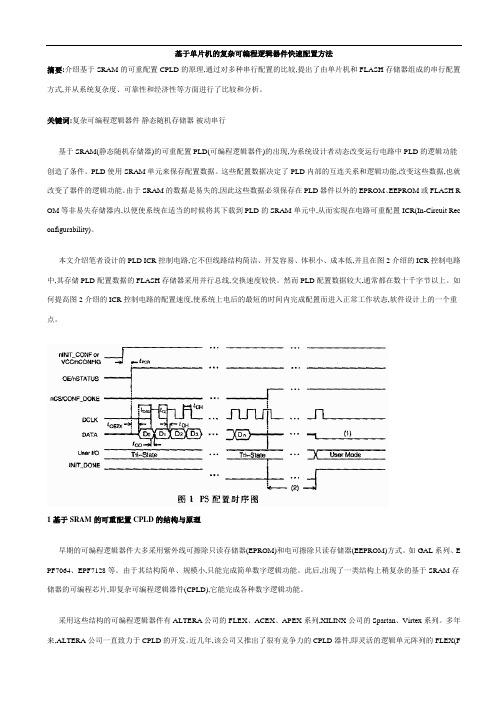

被动串行配置的时序图如图1所示,在这种配置方式中没有握手信号,配置时钟的工作频率必须在器件允许的范围,最低频率没有限制。

为了开始配置,配置管脚和JTAG 管脚所在的bank 的VCCINT、VCCIO 必需供电。

FPGA 上电后进入复位状态。

nCONFIG 被置为低电平,使FPGA 进入复位状态;nCONFIG 由低到高的电位跳变启动配置过程。

图1FPGA 的被动串行(PS)配置时序图整个配置包括三个阶段:复位、配置和初始化。

用单片机配置CPLD器件

用单片机配置CPLD器件ALTERA公司的可编程序逻辑器件APEX20K、FLEX10K和FLEX6000虽应用广泛,但由于其内部采用SRAM存储配置数据,每次系统上电时,必须用配置芯片对其进行配置,只有在配置正确的情况下,系统才能正常工作。

配置芯片是一个能产生配置时序的ROM,分为一次编程型和可擦除型两种,一次编程型芯片只能写入一次,不适合开发阶段反复调试和修改,可擦除型芯片价格昂贵且擦写次数有限(100次左右),增加了开发成本。

而且,由于ALTERA公司提供的配置芯片容量有限,对于容量很大的可编程逻辑器件,需要一片以上的配置芯片组成菊花链形进行配置,这无疑加大了设计复杂度和开发成本。

目前,在可编程逻辑器件的开发阶段多采用可擦写的配置芯片,例如EPC2LC20,最终产品采用不可擦写的配置芯片,例如EPC1441PC8。

至今还没有低成本的可擦写配置芯片出现,而我们采用单片机与外部串行EEROM组成的配置板可实现对一次编程型和可擦除型配置芯片的无缝替代。

它可以代替不同型号、不同容量芯片,可实现反复擦写(1000K次)且用户无须增加任何附加电路(实现无缝替代),并支持多电压配置。

PS配置方式分析配置方式分为主动、被动以及边界扫描配置方式。

我们主要讨论被动配置方式,被动配置方式又可分为被动串行(PS)、被动异步串行(PSA)、被动同步并行(PPS)和被动异步并行(PPA)。

无论哪种方式均是由配置器件控制配置时序,并在控制信号的作用下向目标器件传送串行/并行数据流。

不同的配置方式有不同的配置时序,可针对不同系列的CPLD器件。

对于FLEX10系列芯片,比较常用的是采用PS方式进行配置,PS方式配置时的管脚及控制信号的功能如下:MSEL1, MSEL0:选择配置方式。

均接地,为PS方式。

CONF_DONE:此信号需经1K电阻上拉。

配置过程中,10K电阻将此信号拉低,成功配置完毕后,芯片释放端口,由上拉电阻将其电平抬高。

DSPIC单片机应用教学器件配置

DS70194E_CN 第 25-2 页

© 2009 Microchip Technology Inc.

第 25 章 器件配置

寄存器 25-1: U-0 — bit 23 U-0 — bit 15 R/P RBS<1:0> bit 7 图注: R = 可读位 -n = POR 时的值 bit 23-8 bit 7-6 P = 可编程位 1=置1 U = 未实现位,读为 0 0 = 清零 x = 未知 R/P U-0 — U-0 — R/P R/P BSS<2:0> R/P R/P BWRP bit 0 U-0 — U-0 — U-0 — U-0 — U-0 — U-0 — FBS:引导代码段配置寄存器 U-0 — U-0 — U-0 — U-0 — U-0 — U-0 — U-0 — bit 16 U-0 — bit 8

bit 6-3 bit 2-0

DS70194E_CN 第 25-6 页

© 2009 Microchip Technology Inc.

第 25 章 器件配置

寄存器 25-5: U-0 — bit 23 U-0 — bit 15 R/P bit 7 图注: R = 可读位 -n = POR 时的值 bit 23-8 bit 7-6 P = 可编程位 1=置1 U = 未实现位,读为 0 0 = 清零 x = 未知 R/P R/P IOL1WAY U-0 — U-0 — R/P OSCIOFNC R/P R/P bit 0 U-0 — U-0 — U-0 — U-0 — U-0 — U-0 — FOSC:振荡器配置寄存器 U-0 — U-0 — U-0 — U-0 — U-0 — U-0 — U-0 — bit 16 U-0 — bit 8

可编程逻辑器件及应用 配位

可编程逻辑器件及应用配位

可编程逻辑器件是一种集成电路,能够实现逻辑功能的数字电路。

通过对器件内部的逻辑门进行编程,可以实现不同的逻辑功能。

配合适当的应用,可编程逻辑器件在各个领域都有着广泛的应用。

一般来说,可编程逻辑器件主要包括可编程逻辑阵列(PLA)、可编程逻辑门阵列(PLD)、复杂可编程逻辑器件(CPLD)和场可编程逻辑器件(FPGA)等。

这些器件具有灵活性高、可重构性强的特点,适用于需要频繁更改逻辑功能的应用场景。

在现代电子领域,可编程逻辑器件已经成为数字电路设计中的重要组成部分。

它们被广泛应用于通信、计算机、工业控制、汽车电子、医疗设备等各个领域。

比如,在通信领域,可编程逻辑器件可以用来实现信号处理、数据传输控制等功能;在计算机领域,可编程逻辑器件可以用来实现处理器的控制逻辑、存储器控制等功能;在工业控制领域,可编程逻辑器件可以用来实现各种工业控制系统的逻辑功能。

除了在硬件设计领域广泛应用外,可编程逻辑器件还在软件开发中扮演着重要的角色。

例如,在嵌入式系统开发中,可编程逻辑器件可以用来实现硬件加速、接口控制等功能,提高系统性能和效率。

同时,在虚拟化技术中,可编程逻辑器件也可以用来实现逻辑分区、资源管理等功能,提高系统的灵活性和可靠性。

总的来说,可编程逻辑器件及其应用在现代电子领域扮演着重要的角色。

它们为数字电路设计提供了灵活性和可重构性,为各种应用场景提供了高效、可靠的解决方案。

随着技术的不断进步,可编程逻辑器件的功能和性能将会不断提升,为电子领域的发展带来更多的可能性。

单片机指令的逻辑运算与位操作技巧

单片机指令的逻辑运算与位操作技巧在单片机编程中,逻辑运算和位操作是非常常见的操作。

通过逻辑运算和位操作,我们可以对数据进行逻辑判断、位取反和位移等操作,极大地提高了程序的效率和灵活性。

本文将介绍一些常用的单片机指令的逻辑运算与位操作技巧。

一、逻辑运算技巧1. 与运算与运算是指将两个二进制数的对应位进行逻辑与运算,结果为1则输出1,否则输出0。

与运算常用于屏蔽和提取二进制数的某些位,可以通过逻辑与运算将不需要的位屏蔽掉。

例如,要将一个8位二进制数的低4位置零保留高4位,可以使用与运算。

2. 或运算或运算是指将两个二进制数的对应位进行逻辑或运算,结果为1则输出1,否则输出0。

或运算常用于将某些位设置为1,可以通过逻辑或运算将需要的位设为1。

例如,要将一个8位二进制数的低4位置1保留高4位,可以使用或运算。

3. 非运算非运算是指将一个二进制数的每一位取反,即1变为0,0变为1。

非运算常用于位的取反操作。

例如,要将一个8位二进制数的低4位取反,可以使用非运算。

4. 异或运算异或运算是指将两个二进制数的对应位进行逻辑异或运算,结果为1则输出1,否则输出0。

异或运算常用于判断两个二进制数的对应位是否相同。

例如,可以通过异或运算判断一个8位二进制数的低4位是否全为0。

二、位操作技巧1. 位取反位取反是指将一个二进制数的某些位取反,可以使用逻辑非运算实现。

位取反常用于将某些位翻转,即1变为0,0变为1。

例如,要将一个8位二进制数的低4位取反,可以使用位取反操作。

2. 位与操作位与操作是指将两个二进制数的对应位进行逻辑与运算,结果为1则输出1,否则输出0。

位与操作常用于屏蔽和提取二进制数的某些位。

例如,要提取一个8位二进制数的低4位,可以使用位与操作。

3. 位或操作位或操作是指将两个二进制数的对应位进行逻辑或运算,结果为1则输出1,否则输出0。

位或操作常用于将某些位设置为1。

例如,要将一个8位二进制数的低4位设置为1,可以使用位或操作。

采用单片机实现对FPGA的配置

采用单片机实现对FPGA的配置作者:郑宝华韩桂杰孙万懿来源:《科技视界》2013年第31期【摘要】FPGA应用越来越广泛,但专用配置器件比较昂贵。

在具有微处理器和FPGA的综合应用系统中,使用微处理器来实现对FPGA的数据配置,是一种经济实用的方法。

本文介绍了应用单片机来实现对FPGA的数据配置方法。

同时,给出了对FPGA的被动串行配置的时序和具体硬件、软件的实现方法。

【关键词】单片机;FPGA;被动串行;配置数据0 引言可编程逻辑器件(PLD)的应用越来越广泛。

基于查找表技术、SRAM工艺的FPGA具有密度高且触发器多等特点,多用于复杂的时序逻辑和高速数据处理中。

FPGA器件由于工艺原因在应用时需要进行数据配置。

配置数据决定了FPGA内部互连和功能,改变配置数据,也就改变了器件的逻辑功能。

配置数据必须保存在FPGA器件以外的非易失存储器内,这给实际应用带来了不便[1]。

为了实现在线可重配置(ICR),通常的方法有两种。

一是采用专用的配置芯片(如ALTERA的EPC1、EPC2等)来存储配置数据。

专用的配置芯片比较昂贵,显著增加了系统成本。

而由于FPGA器件在数值计算方面明显地劣于微处理器,所以,经常是单片机和FPGA 并行出现在系统中。

应用单片机的剩余程序存储区来存放配置数据,上电后由单片机控制实现对FPGA器件的数据配置[2]。

本文通过从被动串行(PS)配置时序出发,介绍应用单片机来实现对FPGA的数据配置方法。

1 被动串行配置(PS)及硬件连接FPGA配置方式主要分为两大类:主动配置和被动配置。

主动配置方式由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程;而被动配置方式则由外部计算机或微处理器控制配置过程。

根据数据线的多少又可以将FPGA器件配置方式分为并行配置和串行配置两大类。

下面介绍用单片机实现的被动串行配置。

几乎所有FPGA器件都支持被动串行配置。

被动串行配置的时序图如图1所示,在这种配置方式中没有握手信号,配置时钟的工作频率必须在器件允许的范围,最低频率没有限制。

基于单片机P89C61X2的FPGA配置

片 专 用 配置 芯 片 。在 上 电时 , 这 个 专 用 配 置 芯 片 把 数 由

据 加 载 到 F G 中 , 后 F G 就 可 以 正 常 工 作 。 这就 是 P A 然 PA

在 线 可 重 配置 I R(n Crut cniua mt) 式 。 C I- i iReo f rb y 方 c g

进行 串 行化 处 理 时 不 需 要 配 置 外 部 时钟 的 驱 动 , 接 口更 但 复 杂 。边 界 扫 描 方 式 在 现 场 采 用 较 少 , 常 用 在 计 算 机 通 通

擦 除操作是将 整个程序存储 区都擦除 ; 而块擦 除可实现对

任 意 Fah块 进 行 擦 除 。对 P 9 6 X 进 行 在 系统 编 程 和 ls 8C 1 2

标 准的并 行编程都是 可行 的。片 内产 生 的擦 除和写入 时

序 为用 户 提 供 了 良好 的 编 程 接 口 。P 9 6 X 8 C 1 2的 Fah l 存 s 储 器 甚 至 在 经 过 1 0 00 0次 擦 除 和 编 程 之 后 仍 能 可 靠 地 保 存 存 储 器 内容 。使 用 + 5V 的 Vp p即 可 实 现 对 其 进 行 擦

一

储 器 , 通 过 并 行 编 程 或 在 系 统 编 程 (S 的方 法 进 行 编 可 I P) 程 。支 持 6时 钟 和 1 2时 钟 模 式 , 应 地 有 2种 速 度 范 围 : 相 6时 钟模 式 时 , , 0 MHz 1 0 ̄2 - ; 2时 钟模 式 时 ,~ 3 O 3 MHz L 。

维普资讯

经 验 交 流

基于单片机 P 9 6 2的 F G 8C 1 X A配 置 * P

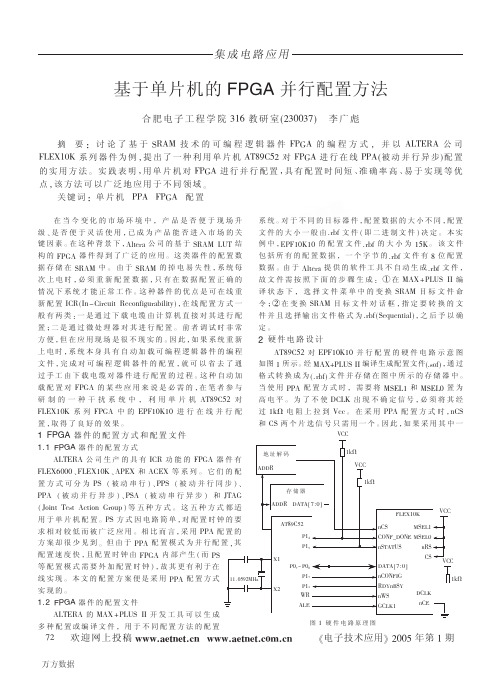

基于单片机的FPGA并行配置方法

’ 硬件电路设计

#&234!5 对 1,;"*B"* 并 行 配 置 的 硬 件 电 路 示 意 图

如图 " 所示 $ 经 E#6],0=8 >> 编译生成配置文件 NF[STX ! 通 过 格 式 转 换 成 为 NFLVTX 文 件 并 存 储 在 图 中 所 示 的 存 储 器 中 $ 当 使 用 ,,# 配 置 方 式 时 ! 需 要 将 E810" 和 E810* 置 为 高 电 平 $ 为 了 不 使 $40B 出 现 不 确 定 信 号 ! 必 须 将 其 经 过 "D! 电 阻 上 拉 到 CQQ $ 在 采 用 ,,# 配 置 方 式 时 ! 748 和 48 两 个 片 选 信 号 只 需 用 一 个 $ 因 此 ! 如 果 采 用 其 中 一

式时序参数如表 " 所示#

!"$ 配 置 软 件 设 计

单片机实现配置过程的控制程序流程图如图 E 所示 # 汇编程序设计如下% 3#45$6% >P* 3’(1(*’ >P* .)/30’/ >P* #45$B)45> >P* 4.% 2222+ =QM- M165 4.% 22E2+ -" 9 A -" 9 ! -" 9 E -" 9 :

& : &2 2 ! &22 !2 29: " "9; !2 "2 &22 &22

!< !< 3< 3< !< 3< 3< !< 3< !< 3< 3<

! 软件设计

!"# 配 置 原 理 --1 配 置 方 式 的 下 载 时 序 如 图 & 所 示 # 由 图 可 以 看

基于单片机的可编程逻辑器件配置及加密

基于单片机的可编程逻辑器件配置及加密[摘要]本文介绍了基于SRAM的可编程逻辑器件的原理,以Altera公司的FLEX 10K系列芯片为例,从系统的复杂度、经济性、可扩展性和保密性等方面,对多种系统配置方式进行比较,提出了由单片机和E2PROM存储器组成的被动串行配置方式,并采用单片机产生长伪随机码序列的方法,实现对系统的加密。

[关键词]现场可编程门阵列(FPGA) 静态随机存储器(SRAM) 被动串行配置(PS)引言基于SRAM的可重配置FPGA用来实现各种存储器及复杂的逻辑功能,系统内硬件功能完全由软件程序实现,允许系统设计者全面控制FPGA内部的逻辑功能,非常方便快捷地反复修改设计。

另外,FPGA重配置控制电路线路结构简洁、开发容易、体积小、成本低,因而深受设计者青睐。

1.基于SRAM的可重配置FPGA的结构基于SRAM LUT结构的FPGA器件,由于是易失性器件,配置数据必须保存在FPGA器件以外的EPROM、E2PROM或Flash ROM等非易失性存储器内,以便使系统在适当的时候将其下载到FPGA中。

因此,它没有ISP(在系统可编程)的概念,代之以ICR(在线可重配置)。

2.可编程逻辑器件的配置原理概述(1)FPGA的工作状态FPGA的工作状态分为三种:一种称之为用户状态(User),指电路中FPGA 器件正常工作时的状态;另一种是配置状态(Configuration),指将编程数据装入FPGA器件的过程,也可以称为构造;第三种是初始化状态(Initialization),FPGA 复位各类寄存器,让I/O引脚为逻辑器件正常工作做准备。

(2) 配置方式分类Altera的FPGA可以使用6种配置模式,由模式选择引脚MSEL1和MSEL2的电平来决定。

(1)配置器件,如用EPC器件进行配置;(2)PS(被动串行)模式:MSEL1=0,MSEL2=0;(3)PPS(被动并行同步)模式:MSEL1=1,MSEL2=0;(4)PPA(被动并行异步)模式:MSEL1=1,MSEL2=1;(5)PSA(被动串行异步)模式:MSEL1=1,MSEL2=0;(6)JTAG模式:MSEL1=0,MSEL2=0。

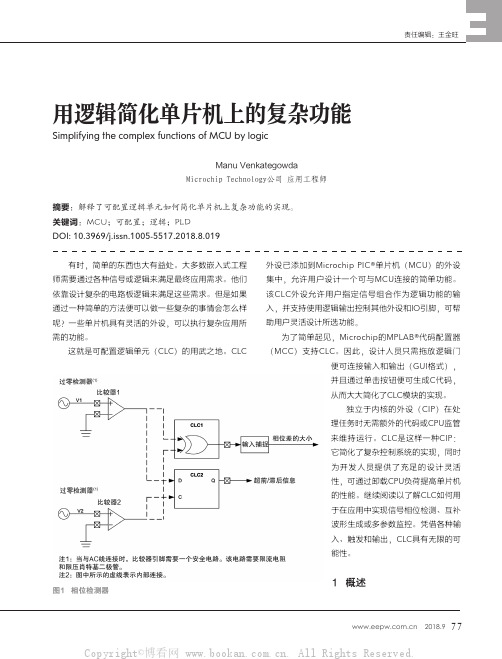

用逻辑简化单片机上的复杂功能

图1 相位检测器CLC是用户可配置的外设,类似于可编程逻辑器件(PLD),但集成在单片机中。

可以选择内部和外部输入作为CLC的输入。

CLC接收来自其他外设或输入引脚的输入。

之后,它会执行预期的逻辑操作,并提供可用于控制其他外设或其他IO引脚的输出。

CLC可以接收信号,例如内部时钟信号、其他外设的输出以及定时器输入等外设事件。

可以通过信号门控级将所选择的输入信号指向所需的逻辑功能。

CLC支持各种逻辑功能,如AND、OR、NOT、XOR、NAND、NOR和XNOR。

在CLC中,数据门控级的输出是逻辑功能选择级的输入。

输出极性级是CLC的最后一级,可以选择所需的极性。

CLC可用作独立外设来实现顺序和组合逻辑功能,从而促进快速事件触发和响应。

它还可以与其他外设一起使用,通过促进硬件中复杂功能的自定义实现来帮助扩展外设功能。

作为独立于内核的外设,CLC通过将许多简单的逻辑事件响应从CPU卸载到外设,有效地降低了应用的CPU带宽需求。

它还降低了闪存和RAM要求,因为不需要软件算法。

与软件中实现的逻辑功能相比,硬件中实现的逻辑功能具有更快的事件响应。

此外,CLC无需任何外部组件之间的距离。

在使用CLCOR逻辑功能可用于实现小,D型触发器前和滞后信息。

模拟信号(例如正弦波CLC的相位检测器的配置将相位差待测的源信号作为输入馈送到两个比较器,这两个比较器被配置为过零检测器将输入模拟信号转换为相同频率的方波方波,则不需要CLC模块。

CLC1和输入捕捉小。

CLC1配置为功能。

CLC1的经接到IC。

凭借经个波之间的相位差的大小CLC1输出不产生信号为了确定两个输入波形的相位超前和滞后信息CLC配置为D-FF个用作时钟。

CLC2输入的相位超前还是滞后于时钟输入图2 边沿对齐模式下使用CLC的互补波形发生器两个信号之间的相位角在许多应用中都十分有用,包括计量、数字电源系统、通信和医疗仪器。

3 互补波形发生器使用C L C的另一种方法是在互补波形发生器(CWG)中。

FPGACPLD可编程逻辑器件的在系统配置方法

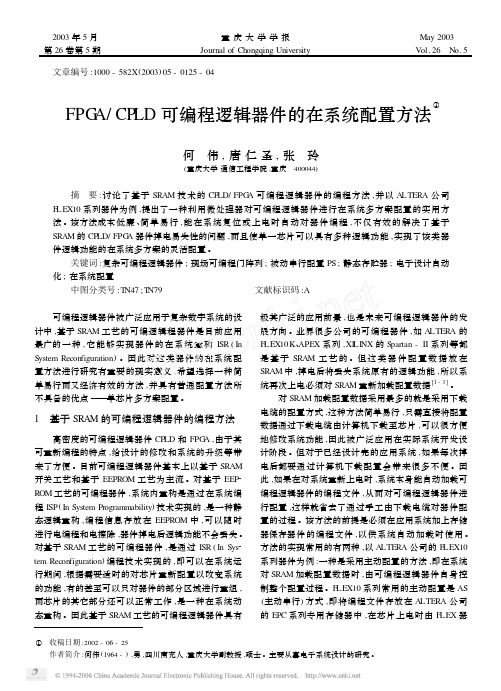

2003年5月重庆大学学报May2003 第26卷第5期Journal of Chongqing University Vol.26 No.5 文章编号:1000-582X(2003)05-0125-04FPG A/CP LD可编程逻辑器件的在系统配置方法①何 伟,唐仁圣,张 玲(重庆大学通信工程学院,重庆 400044)摘 要:讨论了基于SRAM技术的CP LD/FPG A可编程逻辑器件的编程方法,并以A LTERA公司F LEX10系列器件为例,提出了一种利用微处理器对可编程逻辑器件进行在系统多方案配置的实用方法。

该方法成本低廉、简单易行,能在系统复位或上电时自动对器件编程,不仅有效的解决了基于SRAM的CP LD/FPG A器件掉电易失性的问题,而且使单一芯片可以具有多种逻辑功能,实现了该类器件逻辑功能的在系统多方案的灵活配置。

关键词:复杂可编程逻辑器件;现场可编程门阵列;被动串行配置PS;静态存贮器;电子设计自动化;在系统配置中图分类号:T N47;T N79文献标识码:A 可编程逻辑器件被广泛应用于复杂数字系统的设计中,基于SRAM工艺的可编逻辑程器件是目前应用最广的一种,它能够实现器件的在系统重构ISR(In System Recon figuration)。

因此对这类器件的在系统配置方法进行研究有重要的现实意义,希望选择一种简单易行而又经济有效的方法,并具有普通配置方法所不具备的优点———单芯片多方案配置。

1 基于SRAM的可编程逻辑器件的编程方法高密度的可编程逻辑器件CP LD和FPG A,由于其可重新编程的特点,给设计的修改和系统的升级等带来了方便。

目前可编程逻辑器件基本上以基于SRAM 开关工艺和基于EEPROM工艺为主流。

对基于EEP2 ROM工艺的可编程器件,系统内重构是通过在系统编程ISP(In System Programmability)技术实现的,是一种静态逻辑重构,编程信息存放在EEPROM中,可以随时进行电编程和电擦除,器件掉电后逻辑功能不会丢失。

最新-基于单片机的复杂可编程逻辑器件快速配置方法 精品

基于单片机的复杂可编程逻辑器件快速配置方法摘要介绍基于的可重配置的原理,通过对多种串行配置的比较,提出了由单片机和存储器组成的串行配置方式,并从系统复杂度、可靠性和经济性等方面进行了比较和分析。

关键词复杂可编程逻辑器件静态随机存储器被动串行基于静态随机存储器的可重配置可编程逻辑器件的出现,为系统设计者动态改变运行电路中的逻辑功能创造了条件。

使用单元来保存配置数据。

这些配置数据决定了内部的互连关系和逻辑功能,改变这些数据,也就改变了器件的逻辑功能。

由于的数据是易失的,因此这些数据必须保存在器件以外的、或等非易失存储器内,以便使系统在适当的时候将其下载到的单元中,从而实现在电路可重配置-。

本文介绍笔者设计的控制电路,它不但线路结构简洁、开发容易、体积小、成本低,并且在图2介绍的控制电路中,其存储配置数据的存储器采用并行总线,交换速度较快。

然而配置数据较大,通常都在数十千字节以上。

如何提高图2介绍的控制电路的配置速度,使系统上电后的最短的时间内完成配置而进入正常工作状态,软件设计上的一个重点。

范文先生网收集整理1基于的可重配置的结构与原理早期的可编程逻辑器件大多采用紫外线可擦除只读存储器和电可擦除只读存储器方式。

如系列、7064、7128等。

由于其结构简单、规模小,只能完成简单数字逻辑功能。

此后,出现了一类结构上稍复杂的基于存储器的可编程芯片,即复杂可编程逻辑器件,它能完成各种数字逻辑功能。

采用这些结构的可编程逻辑器件有公司的、、系列,公司的、系列。

多年来,公司一直致力于的开发。

近几年,该公司又推出了很有竞争力的器件,即灵活的逻辑单元阵列的系列产品。

基于单片机的复杂可编程逻辑器件快速配置方法(全面)

基于单片机的复杂可编程逻辑器件快速配置方法摘要:介绍基于SRAM的可重配置CPLD的原理,通过对多种串行配置的比较,提出了由单片机和FLASH存储器组成的串行配置方式,并从系统复杂度、可靠性和经济性等方面进行了比较和分析。

关键词:复杂可编程逻辑器件静态随机存储器被动串行基于SRAM(静态随机存储器)的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。

PLD使用SRAM单元来保存配置数据。

这些配置数据决定了PLD内部的互连关系和逻辑功能,改变这些数据,也就改变了器件的逻辑功能。

由于SRAM的数据是易失的,因此这些数据必须保存在PLD器件以外的EPROM、EEPROM或FLASH R OM等非易失存储器内,以便使系统在适当的时候将其下载到PLD的SRAM单元中,从而实现在电路可重配置ICR(In-Circuit Rec onfigurability)。

本文介绍笔者设计的PLD ICR控制电路,它不但线路结构简洁、开发容易、体积小、成本低,并且在图2介绍的ICR控制电路中,其存储PLD配置数据的FLASH存储器采用并行总线,交换速度较快。

然而PLD配置数据较大,通常都在数十千字节以上。

如何提高图2介绍的ICR控制电路的配置速度,使系统上电后的最短的时间内完成配置而进入正常工作状态,软件设计上的一个重点。

1 基于SRAM的可重配置CPLD的结构与原理早期的可编程逻辑器件大多采用紫外线可擦除只读存储器(EPROM)和电可擦除只读存储器(EEPROM)方式。

如GAL系列、E PF7064、EPF7128等。

由于其结构简单、规模小,只能完成简单数字逻辑功能。

此后,出现了一类结构上稍复杂的基于SRAM存储器的可编程芯片,即复杂可编程逻辑器件(CPLD),它能完成各种数字逻辑功能。

采用这些结构的可编程逻辑器件有ALTERA公司的FLEX、ACEX、APEX系列,XILINX公司的Spartan、Virtex系列。

基于单片机的复杂可编程逻辑器件快速配置方法

基于单片机的复杂可编程逻辑器件快速配置方法

刘晓明;王军;谢明钦

【期刊名称】《电子技术应用》

【年(卷),期】2002(028)010

【摘要】介绍基于SRAM的可重配置CPLD的原理,通过对多种串行配置的比较,提出了由单片机和FLASH存储器组成的串行配置方式,并从系统复杂度、可靠性和经济性等方面进行了比较和分析.

【总页数】3页(P9-11)

【作者】刘晓明;王军;谢明钦

【作者单位】重庆大学通信工程学院,400044;重庆大学通信工程学院,400044;重庆大学通信工程学院,400044

【正文语种】中文

【中图分类】TP3

【相关文献】

1.基于单片机的可编程逻辑器件配置及加密 [J], 何惠芳;唐小煜

2.基于数字信号处理芯片和复杂可编程逻辑器件的永磁重合器的研究与设计 [J], 张维;王焕文;郭上华

3.复杂可编程逻辑器件与80C196MC型单片机的数据传输方案 [J], 李畸勇;韦海燕

4.基于单片机和复杂可编程逻辑器件的智能电机故障诊断仪 [J], 贺小亮;赵军红;王

新军

5.基于复杂可编程逻辑器件的流速快速测量系统 [J], 李刚;黄同愿;邵桂芳;项德明因版权原因,仅展示原文概要,查看原文内容请购买。

基于单片机P89C61X2的FPGA配置

基于单片机P89C61X2的FPGA配置MAX+PLUS II不自动生成.rbf文件,须根据下面的步骤生成:①在MAX 十PLUS II编译状态下,挑选文件菜单的变换SRAM目标文件指令;②在变换SRAM目标文件对话框中指定要转换的文件并且挑选输出文件格式为.rbf,然后确定。

针对单片机P89C61X2,可以通过在系统编程(ISP)的办法实现。

这里采纳广州致远有限公司开发的在线编程下载软件ZLGICD。

该软件支持.hex文件。

.hex文件为十六进制文件,MAX+PLUS II编译时会自动生成该文件,假如没有也可采纳类似产生.rbf文件的办法生成。

用P89C61X2来配置FPGA,需将引导配置代码(.hex文件)和FPGA的配置数据(.hex文件)一起通过编程器写入P89C61X2。

配置数据需要转变现有地址来让引导程序调用,否则会造成矛盾。

可以自己编写一个小程序来实现此功能。

注重.hex文件的格式。

因为引导配置代码不长,通常小于1 KB,因此有足够的空间来存放配置数据。

3 软件设计软件编程时,本系统只用到了串行口移位寄存器的输出方式,串行数据通过RXD引脚输出,移位时钟由TXD引脚输出。

当有一个字节数据写入串行数据缓冲器SBUF时,开头发送。

而串行口输出方式本身就满足配置时最低位(LSB)先送出的要求。

下面给出用编写的子程序:uchar fpga_config(uint Address){uchar reconfig=0;uchar j;init;nconfig=0;delay-ms(1);nconfig= 1;reconfig++;第1页共2页。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于单片机的复杂可编程逻辑器件快速配置方法摘要:介绍基于SRAM的可重配置CPLD的原理,通过对多种串行配置的比较,提出了由单片机和FLASH存储器组成的串行配置方式,并从系统复杂度、可靠性和经济性等方面进行了比较和分析。

关键词:复杂可编程逻辑器件静态随机存储器被动串行基于SRAM(静态随机存储器)的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。

PLD使用SRAM单元来保存配置数据。

这些配置数据决定了PLD内部的互连关系和逻辑功能,改变这些数据,也就改变了器件的逻辑功能。

由于SRAM的数据是易失的,因此这些数据必须保存在PLD器件以外的EPROM、EEPR OM或FLASH ROM等非易失存储器内,以便使系统在适当的时候将其下载到PLD的SRAM单元中,从而实现在电路可重配置ICR(In-Circuit Reconfigurability)。

本文介绍笔者设计的PLD ICR控制电路,它不但线路结构简洁、开发容易、体积小、成本低,并且在图2介绍的ICR控制电路中,其存储PLD配置数据的FLASH存储器采用并行总线,交换速度较快。

然而PLD配置数据较大,通常都在数十千字节以上。

如何提高图2介绍的ICR控制电路的配置速度,使系统上电后的最短的时间内完成配置而进入正常工作状态,软件设计上的一个重点。

1 基于SRAM的可重配置CPLD的结构与原理早期的可编程逻辑器件大多采用紫外线可擦除只读存储器(EPROM)和电可擦除只读存储器(EEPROM)方式。

如GAL 系列、EPF7064、EPF7128等。

由于其结构简单、规模小,只能完成简单数字逻辑功能。

此后,出现了一类结构上稍复杂的基于SRAM存储器的可编程芯片,即复杂可编程逻辑器件(CPLD),它能完成各种数字逻辑功能。

采用这些结构的可编程逻辑器件有ALTERA公司的FLEX、ACEX、APEX系列,XILINX公司的Spartan、Virtex系列。

多年来,ALTERA公司一直致力于CPLD的开发。

近几年,该公司又推出了很有竞争力的CPLD器件,即灵活的逻辑单元阵列的FLEX(Flexible Logic Element Matrix)系列产品。

相对于其它一些厂家的FPGA产品来说,ALTERA公司的FLEX系列产品有其独特之处。

这主要表现在高密度、在线配置功能、高速度和连续式布线结构等方面。

查找表LUT(Look-Up-Table)是基于SRAM的可重配置PLD的一个重要组成部分,LUT本质上就是一个RAM。

目前CP LD中多使用4输入的LUT,所以每一个LUT可以看成个有4位地址线的16×1bit的RAM。

当用户通过GDF原理图或VHDL 语言描述了一个逻辑电路后,CPLD开发软件会自动计算逻辑电路的所有可能结果,并把结果事先存入查找表。

这样,当多信信号进行逻辑运算时就等于输入一个地址进行查表,找出地址所对应的内容,然后将其输出即可。

2 可编程逻辑器件的配置原理首先在开发软件MAX+PLUS II的ASSIGN菜单下选择将要采用的基于SRAM的器件名称。

经过编译、优化、逻辑综合、仿真等步骤达到设计要求后,软件会自动产生一个编程文件(扩展名为.SOF文件)。

对于基于SRAM工艺的可编程逻辑器件(如ALTERA的所有FLEX、ACEX、APEX系列,XILINX的Sparten、Vertex系列),由于SRAM存储器的特点,掉电后数据会消失,因此在调试期间可以采用并口ByteblasteMV下载电缆多次重复配置PLD器件。

当电路设计成功,调试完成后,需要将配置数据烧写固化在一个由ALTERA生产的专用EEPROM(如EPC1441)中。

上电时,由这片配置EEPROM先对PLD 加载数据,几十毫秒后,PLD即可正常工作。

CPLD器件的工作状态分为三种:首先是上电配置状态(Configuration Mode),将编程的数据装入CPLD器件的过程,也可称之为构造;然后是初始化状态(Initialization Mode),在配置完成后,CPLD器件复位内部各类寄存器,让I/O引脚为逻辑器件正常工作做准备;最后是用户状态(User Mode),指电路中CPLD器件正常工作时的状态。

ALTERA公司具有ICR功能的PLD器件有FLEX8000、FLEX10K、APEX和ACEX系列,它们的配置方式可分为PS、PPS 和JTAG(Joint Test Action Group)等方式。

PS方式因PLD与配置电路的互连最简单,对配置时钟的最小频率没有限制而应用最广泛,因此在ICR控制电路中通常采用PS配置方式来实现ICR功能。

被动串行(PS)配置方式:在该配置方式下,由ByteblasteMV下载电缆产生一个由低到高的跳变送到nCONFIG引脚脚复位PLD,然后将配置数据送到DATA0引脚,直到CONF_DONE引脚变为高电平。

图1是PS配置方式的时序图。

CONF_DON E变成高电平后,DCLK必须多余十个周期来初始化该器件。

器件的初始化由下载电缆自动执行。

在PS方式中没有握手信号,所以配置时钟的工作频率必须低于10MHz。

在多器件PS配置方式中,第一片PLD的nCEO引脚级联到下一片PLD的nCE引脚。

在配置完第一个器件后,nCEO输出为低,使第二个PLD器件的nCE有效,开始对第二块器件进行配置。

3 用WINBOND78E58单片机配置可编程逻辑器件用单片机配置可编程逻辑器件与上述PS配置方式原理一致,只需模拟PS配置方式中DATA0、DCLK、nCONFIG、CONF_DO NE、nSTATUS引脚的配置时序,将配置数据串行移入PLD。

配置引脚的功能如表1所示。

3.1 硬件设计用单片机配置PLD,可以使用普通输入输出口或单行口。

使用普通I/O口(如P1口),向PLD发送1Bit数据至少需要4个指令周期。

一个指令给DATA0赋值,两个指令产生DCLK时钟,一个指令移位取数据。

如果晶振为fosc,一个指令周期为12/fosc,因此它的下载速率为fosc/48。

然而如果采用串行口方式0,其下载速率提高为fosc/12。

考虑到PLD配置文件数据比较大,通常都在数十千字节以上(其配置文件大小如表2),为了加快配置速度,并适合各种不同规模的PLD,采用了WINBON D78E58单片机。

该单片机外接晶振最大频率为40MHz,它在串行口方式0下波特率可设置为fosc/4。

另外通过设置特殊功能寄存器CKCON 的MD0、MD1、MD2三位,可以将MOVX、MOVC等指令周期缩短至2个机器周期。

与普通单片机相比,可使配置时间大为缩短。

WINBOND78E58单片机内部拥有32KB FLASH ROM.由配置文件数据表2可知,只需一片单片机就可以对EPF10K20系列以下的PLD进行配置了。

本系统中使用了一片APEX20K300E,因此在硬件电路设计中,扩展了一片WINBOND29C040 FL ASH存储器(容量为512KB),其电路如图2。

DATA0与RXD、DCLK与TXD、nCONF与P15、CONFIG_DONE与P16、n STATUS与P17分别相连。

3.2 软件设计在软件编程时,使用了串行口移位寄存器输入输出方式。

本系统只需用到输出方式,串行数据通过RXD引脚输出,而在T XD引脚输出移位时钟。

当一字节数据写入串行数据缓冲器SBUF时,就开始发送。

在此期间,发送控制器送出移位信号,使发送移位寄存器的内容右移一位,直至最高位(D7位)数字移出后,停止发送数据和移位时钟脉冲。

RXD、TXD时序如图3。

由图3可知,它可以用来模拟配置时序。

发送完一字节数据后,硬件置发送标志位TI为1,向CPU申请中断。

若CPU响应中断,则从0023H单元开始执行串行中断服务程序。

为了提高配置速度,单片机程序用汇编语言编写。

单片机上电后使nCONFI G脚由低到高复位待配置PLD;当判断到nSTATUS为高后,开始从外部FLASH存储器取数据串行移位。

配置过程中,查询CONF_DONE。

一旦为高,配置完成,但还要送40个DCLK脉冲,PLD才能进入用户工作状态。

用户设计PLD程序经MAXPLUS II或QUARTUS编译后将产生后缀后为.sof的SRAM目标文件。

该文件含有除配置数据以外的控制字符,不能直接写入到PLD中去,需要利用软件的编程文件转换功能将文件转换成.rbf(Raw Binary File)十六进制文件。

把.rbf文件烧写到存储器中,单片机通过MOVX指令读入后,串行移位到PLD。

部分asm语言源程序如下:NCONFIG BIT P1.5CONFDONE BIT P.6NSTATUS BIT P1.7ORG 000h……CLR SM0CLR SM1 ;SM0,SM1为0,串口工作于方式0CLR SM2 ;串口波特率为fosc/4CLR RENANL 8EH,#0f8h ;地址8EH是CKCON单元,MD0、MD1、MD2清0CLR EAWJRESTART:CLR NCONFIGSETB NCONFIG ;上升沿复位PLDWAIT:JNB NSTATUS,WAIT ;NSTATUS为高,可进行配置WJPEIZHI:MOV P1,COUNTER3MOV DPH,COUNTER2MOV DPL,COUNTER1 ;配置数据大,需3个单元作地址记数MOVX A,@DPTAMOV SBUF,A ;串行移位NOPNOP ;采用填充2个空指令,正好使一个字节发送完成,可发送下一个字节INC COUNTER1 ;地址加MOV A,COUNTER1JB CONFDONE,WJEND1CJNE A,#0,WJPEIZHIINC COUNTER2NOV A,COUNTER2CJNE A,#0,WJPEIZHIINC COUNTER3LJMP WJPEIZHIWJEND1:MOV R0,#60WJEND:WOV A,#55H……MOV SBUF,A ;由此产生40个DCLK时钟DJNZ R0,WJENDWERE:LJMP HERE ;配置完成,进入用户工作模式使用OTP(One Time Programming)器件配置CPLD具有一定的冒险性,一次简单的代码更换就可能意味着更换OTP器件,并重新开始所有的程序。

被动串行微处理器(Passive Serial With Processor)配置方式以EEPROM为基础,允许对这些存储器进行多次编程,所有其它芯片都无需从已装配的印制电路板上拆卸下来。

高速读写周期的FLASH存储器能确保1万次编程,而且能对任何以SRAM为基础的PLD下载。