封装技术及分类

芯片封装原理及分类

芯片封装原理及分类1.芯片封装原理芯片封装是指将微电子器件(包括集成电路、晶体管等)连接到封装基座上的工艺过程。

其原理是将芯片导线通过焊接或焊球连接到封装基座上的金属脚,然后采用封装材料将芯片进行封装。

这样可以保护芯片免受外界环境的影响,并且提供了芯片与外部世界之间的连接接口。

2.芯片封装分类(1)DIP封装(Dual In-line Package)DIP封装是最早的一种芯片封装方式,其特点是通过两排金属脚与外部电路连接。

这种封装方式成本低、可焊接,但体积大,适用于较低密度的集成电路。

(2)SOP封装(Small Outline Package)SOP封装是DIP封装的改进版,其特点是脚距更近,体积更小,适用于较高密度的集成电路。

SOP封装有多种形式,如SOIC(Small Outline Integrated Circuit)、TSOP(Thin Small Outline Package)等。

(3)QFP封装(Quad Flat Package)QFP封装是一种表面贴装封装方式,其特点是四个侧面都带有金属端子,适用于较高密度、中等规模的集成电路。

QFP封装有多种形式,如TQFP(Thin Quad Flat Package)、LQFP(Low-profile Quad Flat Package)等。

(4)BGA封装(Ball Grid Array)BGA封装是一种表面贴装封装方式,在封装基座上布置了一定数量的焊球来实现与外部电路的连接。

BGA封装的特点是密封性好、性能稳定,并且适用于超高密度的集成电路。

BGA封装有多种形式,如CABGA (Ceramic Ball Grid Array)、TBGA(Thin Ball Grid Array)等。

(5)CSP封装(Chip Scale Package)CSP封装是一种紧凑型封装方式,其特点是尺寸和芯片相似,在封装基座上布置了少量焊球或焊盘。

CSP封装的优势在于占据空间小、重量轻、功耗低,并且适用于高密度的集成电路。

相变材料封装技术分类

相变材料封装技术分类一、常见的相变材料封装技术1. 传统封装技术传统封装技术是指使用传统的封装材料(如塑料、金属等)对相变材料进行封装。

这种封装技术简单、成本低,但对相变材料的性能保护有限,无法实现高效的相变温度控制。

2. 微封装技术微封装技术是指利用微纳加工技术将相变材料封装在微小尺寸的器件中。

这种封装技术可以实现对相变材料的高度集成和微观尺度的相变控制,但制造工艺复杂,成本较高。

3. 柔性封装技术柔性封装技术是指使用柔性基底材料(如聚合物薄膜)对相变材料进行封装。

这种封装技术可以实现对相变材料的柔性应用,具有良好的可变形性能和适应性,但对相变温度控制和稳定性要求较高。

二、新兴的相变材料封装技术1. 纳米封装技术纳米封装技术是指利用纳米材料对相变材料进行封装。

这种封装技术可以实现对相变材料的纳米级封装,提高封装效果和性能稳定性,但制备工艺复杂,成本较高。

2. 多功能封装技术多功能封装技术是指在相变材料封装过程中加入其他功能材料,使封装材料具备更多的功能。

例如,加入导热材料可以提高封装材料的导热性能;加入光学材料可以实现光学调控等。

这种封装技术可以实现对相变材料的多功能应用,拓展了其应用领域。

3. 3D打印封装技术3D打印封装技术是指利用3D打印技术对相变材料进行封装。

这种封装技术可以根据具体应用需求进行定制化设计和制造,实现对相变材料的高度个性化封装。

同时,3D打印技术还可以实现对相变材料的复杂结构封装,提高封装效果和性能控制精度。

三、相变材料封装技术的发展趋势1. 封装效果和性能的提升随着科技的不断进步,相变材料封装技术将不断提升封装效果和性能稳定性,实现更精确的相变温度控制和更高的封装密度。

2. 多功能化和智能化相变材料封装技术将向多功能化和智能化方向发展。

封装材料将具备更多的功能,并能根据环境和用户需求实现智能调控,拓展相变材料的应用领域。

3. 环境友好和可持续发展相变材料封装技术将注重环境友好和可持续发展。

集成电路封装方式

集成电路封装方式在现代电子技术中,集成电路(Integrated Circuit,简称IC)的封装是非常重要的环节。

封装是将芯片固定在外部载体上,并提供电气连接和机械支撑的工艺过程。

不同的封装方式可以满足不同的应用需求,影响着集成电路的性能、功耗和成本等方面。

一、封装的重要性集成电路的封装是将微小的芯片封装到外部载体中,以便在实际应用中使用。

封装可以提供电气连接、机械支撑和热管理等功能,并保护芯片免受外部环境的影响。

同时,封装还可以为芯片提供更好的散热条件,以确保芯片的正常工作。

因此,合理选择封装方式对于集成电路的性能和可靠性非常重要。

二、封装方式的分类根据不同的封装方式,集成电路的封装可以分为多种类型,包括裸片封装、贴片封装和插装封装等。

1. 裸片封装裸片封装是将芯片直接粘合到基板上,然后通过线缆或焊接将芯片与基板连接起来的封装方式。

裸片封装具有尺寸小、重量轻、成本低等优点,适用于高集成度和小尺寸的应用场景。

然而,由于裸片封装没有外壳保护,芯片容易受到机械损伤和环境影响,对环境要求较高。

2. 贴片封装贴片封装是将芯片粘贴在基板上,并使用导线将芯片与基板连接起来的封装方式。

贴片封装可以分为表面贴装技术(SMT)和无引线封装技术(BGA)等。

SMT是将芯片直接焊接在基板表面的封装方式,具有工艺简单、成本低等优点,适用于大规模生产。

BGA是一种无引线封装技术,通过焊球连接芯片和基板,具有高密度、高可靠性的特点,适用于高性能和高可靠性要求的应用场景。

3. 插装封装插装封装是将芯片插入到插座中,并通过插针与插座进行连接的封装方式。

插装封装具有更好的可替换性和维修性,适用于开发调试和小批量生产。

然而,插装封装的尺寸较大,不适合高集成度和小尺寸的应用。

三、封装方式的选择在选择封装方式时,需要综合考虑应用场景、性能要求、成本和生产规模等因素。

1. 应用场景不同的应用场景对封装方式有不同的要求。

例如,对于手机等便携设备,尺寸和重量是重要考虑因素,因此常采用贴片封装。

元器件封装定义及分类

元器件封装定义及分类

元器件封装是将电子元器件包装在外壳内,以保护其内部电路并便于安装和使用的过程。

根据元器件的不同形状、尺寸和功能,元器件封装可以分为多种不同的类型。

1. DIP封装

双列直插封装,是一种传统的元器件封装方式,广泛用于集成电路、二极管、三极管等元器件。

2. SOP封装

小型外形封装,是一种比DIP封装更为紧凑、高密度的封装方式,常用于微处理器、存储器等元器件。

3. QFP封装

方形扁平封装,是一种常见的封装方式,主要用于高密度的集成电路和微处理器。

4. BGA封装

球形网格阵列封装,是一种目前使用最广泛的封装方式之一,被广泛应用于CPU、芯片组、存储器等高端集成电路。

5. COB封装

芯片贴装技术,是一种无外壳封装的技术,将芯片直接粘贴在PCB板上,主要应用于微型芯片和传感器等。

以上是目前常见的元器件封装类型,随着科技的不断发展,封装技术也在不断更新换代,未来还会出现更多新的封装方式。

- 1 -。

封装工艺

10、SOT(Small Outline Transistor )

小外形晶体管。SOT系列主要有SOT-23、 SOT-223、SOT25、SOT-26、SOT323、 SOT-89等。当电子产品尺寸不断缩小 时, 其内部使用的半导体器件也必须变小, 更小的半导体器件使得电子产品能够更 小、更轻、更便携,相同尺寸包含的功 能更多。 SOT-25 SOT-26 SOT-223 SOT-23

图示过程:

抓片头 装片头 框架 银浆分 配器 校正台 簿膜 吸嘴 芯片 簿膜 顶头

圆片

四.键合过程

键合(wire bonding)的目的

为了使芯片能与外界传送及接收信号,就必须在 芯片的接触电极与框架的引脚之间,一个一个对 应地用键合线连接起来。这个过程叫键合。

框架 内引 脚 芯片接处电极 键合引线

3.吸水性,透湿率要低。

4.热膨胀系数要高,导热率要低。

5.成型收缩率和内部应力要小。

6.成型,硬化时间要短,脱模性要好。

7.流动性及充填好,飞边少。

使用塑封封装的理由:

1.工艺简单,便于大量生产,成本低。

2.工作温度较低

3.芯片事先加了保护性钝化膜。

4.塑封材料符合封装的要求。

六.电镀工程

电镀的目的:

(2)由于温度降低,可以减少金铝间的金属化合物的产生,从 而提高键合强度,降低接触电阻。 (3)能键合不能耐300 ℃ 以上高温的器件。 (4)键合压力,超声功率可以降低一些。 (5)有残余的钝化层或有轻微氧化的铝压点也能键合。

五.塑封工程

IC密封的目的

密封是为了保护器件不受环境影响(外部冲击, 热及水伤)而能长期可靠工作。

全自动切割方式

贴膜 划片洗净及干燥 装片

封装技术

41

二、封装工艺和控制

2、工艺过程和作用

K、出货(SHIPPING) 按客户要求进行外包装后发往客

户指定地点.

42

二、封装工艺和控制

3、工艺优化方法 A、对分法 B、0.618法.适用于单因素. C、DOE正交试验法,适用于多因素多条件

超级连接1 优选法 正交实验设计(1).doc

缺角

24

擦伤 厚度

划片 装片 键合 塑封 去飞边

电镀 打印 切筋

划偏

缺角

擦伤

沾污

断丝

塌丝

未充填 麻点/气孔

引线框变 飞边残留 形

未镀上 污染

白板

沾污

断筋

弯脚

擦伤 掉片 内外/脱 偏心 塑封体 打毛 变色 倾斜 偏心

沾污 倾斜 强度 溢料

镀层不足 印记错误 缺角

超 级

46

三、封装失效和可靠性

2、封装失效及比例

插装式的结构便于自动化安装和高的可靠 性焊接,体积大。

表面安装式结构引线密度高,体积小, 焊接要求高。

6

一、封装基础知识

4、半导体器件分类

双极型集成电路:

以双极型晶体管为基本有源器件构成的单片集成电路,特点:电路速度 高、阀值电压低、稳定性好负载能力强,但工艺复杂。

MOS集成电路:

以MOS晶体管为基本有源器件构成的单片集成电路,特点:工艺简单、 集成度高、输入阻抗高、功耗小。

Chip Carrier 塑料有引线芯

片载体

9

一、封装基础知识

B、封装形式命名

CLCC Ceramic Leaded Chip Carrier 塑料无引线 芯片载体

IC封装工艺简介

IC封装工艺简介集成电路(IC)封装工艺是制造IC的重要步骤之一,它关系到IC的稳定性、散热效果和外形尺寸等方面。

通过不同的封装工艺,可以满足不同类型的IC器件的需求。

封装工艺分类目前常见的IC封装工艺主要有以下几种类型:1.贴片封装:是将IC芯片直接粘贴在PCB基板上的封装方式,适用于小型、低功耗的IC器件。

2.裸片封装:IC芯片和封装基板之间没有任何封装材料,可以获得更好的散热效果。

3.塑封封装:将IC芯片封装在塑料基板内部,并封装成标准尺寸的芯片,适用于多种场合。

4.BGA封装:球栅阵列封装是一种高端封装技术,通过焊接球栅来连接芯片和PCB基板,适用于高频高性能的IC器件。

封装工艺流程IC封装工艺包括以下几个主要步骤:1.芯片测试:在封装之前,需要对芯片进行测试,确保芯片的功能正常。

2.粘贴:在贴片封装中,IC芯片会被粘贴到PCB基板上,需要精确的定位和固定。

3.焊接:通过焊接技术将IC芯片和PCB基板连接起来,确保信号传输的可靠性。

4.封装:将IC芯片包裹在封装材料中,形成最终的封装芯片。

5.测试:封装完成后需要进行最终的测试,确保IC器件性能符合要求。

封装工艺发展趋势随着技术的不断进步,IC封装工艺也在不断发展,主要体现在以下几个方面:1.多功能集成:随着对IC器件功能和性能需求的提高,封装工艺需要支持更多的功能集成,如封装中集成无源器件或传感器等。

2.微型化:随着电子产品体积的不断缩小,IC封装工艺也在朝着微型化的方向发展,以满足小型化产品的需求。

3.高性能封装:为了提高IC器件的性能和可靠性,封装工艺需要支持更高频率、更高功率的IC器件。

综上所述,IC封装工艺在集成电路制造中扮演着重要的角色,通过不断的创新和发展,可以满足各类IC器件的需求,推动整个电子产业的不断进步。

40种封装技术

1、BGA 封装(ball grid array)球形触点陈列,表面贴装型封装之一.在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封.也称为凸点陈列载体(PAC).引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小.例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0。

5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1。

5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理. 美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP 封装(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫)以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装.引脚中心距0。

635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA 封装(butt joint pin grid array)表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C—(ceramic) 封装表示陶瓷封装的记号.例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip 封装用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

电子元件封装及封装常识

电子元件封装及封装常识电子元件是电子设备中不可缺少的基本组成部分,在电子设备中起到非常重要的作用。

电子元件封装则是保护电子元件的重要手段,在电子元件的使用和存储等方面起到至关重要的作用。

本文将介绍电子元件封装的基本知识和封装常识。

一、电子元件封装的基本知识1、电子元件封装的概念电子元件封装是指将片式电子元件、插针式电子元件、导线式电子元件等电子元件,按照一定的形状、大小和尺寸进行封装,从而形成带有引脚或焊盘的封装体,以便于使用和制造电子设备的过程中固定元件、连通电路和保护元件。

2、电子元件封装的分类电子元件的封装可以根据元件封装的性质来进行分类,主要分为以下几种类型:(1)插入式封装:插正、插反、插侧、插角、磨角、磨角侧插方、板插等。

(2)表面贴装封装:QFP、BGA、TSOP、SOP等。

(3)接插板式封装:DIP、SIP等。

(4)芯片式封装:QFN、CSP等。

二、电子元件封装常识1、电子元件的常见封装方式(1)DIP封装方式:DIP封装又称为插装式封装,是最早的一种封装方式。

这种封装方式把电子元件引脚直接插到插座或插板上,插座或插板是印制电路板上的零件之一,通过插头或插片的方式,使电路板上的元件与外部元件形成可拆卸连接。

(2)SMD封装方式:SMD封装是Surface-Mount Device,表面安装技术的缩写。

这种封装方式比DIP封装更加紧凑,是芯片、光电器件、传感器、电感等组成的封装。

封装器件数量多、体积小,可以和PCB一起焊接。

(3)TSOP封装方式:TSOP封装是Thin Small Outline Package,是一种表面贴装封装方式。

电子元件的引脚是双列的若干行,每行引脚数不等,封装尺寸一般为3.0×6.4mm。

2、电子元件的封装规格电子元件的封装规格指的是电子元件封装的尺寸、形状、引脚数、引脚间距、封装材料等多个方面。

根据不同的应用需求,电子元件的封装规格也会有所不同。

芯片封装原理及分类

部分芯片建模时可将各边管脚统一建立; 管脚数较小应将各管脚单独建出. fused lead 一定要单独建出 Tie bars 一般可以忽略.

Bond Wires

Die

Die Flag

Leadframe

常规

Die

Bond Wires

主要类型的PBGA封装

Wire-Bonded PBGA (Die-up)

BT Dielectric

Thermal Vias

Solder Balls (37Pb/63Sn)

Epoxy-based Encapsulant

Silicon Die

Die Attach & Solder Mask

Gold Bond Wires

封装参数 (结构、材料参数)

根据各种封装特点离散出 各种热阻网络拓朴结构

详细 模型

发布

简化 模型

多种边界条件可以表 示自然对流、强迫对流、 散热器等多种环境

根据各热阻节点的温度值优 化得出具有最小误差的热阻值

DELPHI项目组定义了99种 边界条件;

Flopack应用了44种或88种

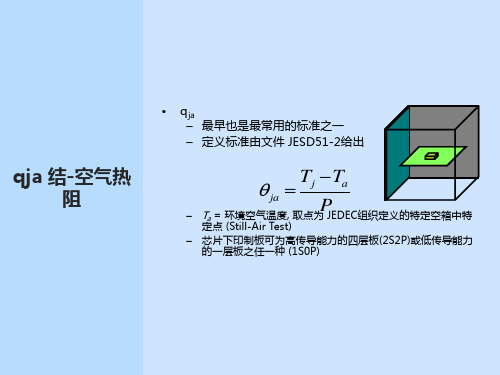

PBGA封装模型的建立

Case

qjb

qjb 结板热阻

qjb 从结点至印制板的热阻 定义标准由文件 JESD51-8给出

严格地讲,Theta-JB不仅仅反映了芯片的内热阻,同时也反映了部份环境热阻,如印制板。正因如些, Theta-JB相对于其它热阻而言,虽然JEDEC组织在99年就发布了它的热阻定义方式,但是芯片供应商采用较慢。 部份传热路径严重不对称芯片,如TO-263目前尚无该热阻的定义标准

DEvelopment of Libraries of PHysical models for an Integrated design environment

集成电路封装技术

第一章集成电路芯片封装技术1. (P1)封装概念:狭义:集成电路芯片封装是利用膜技术及微细加工技术,将芯片及其他要素在框架或基板上布置、粘贴固定及连接,引出接线端子并通过可塑性绝缘介质灌封固定,构成整体结构的工艺。

广义:将封装体与基板连接固定,装配成完整的系统或电子设备,并确保整个系统综合性能的工程。

2. 芯片封装实现的功能:1 传递电能,主要是指电源电压的分配和导通。

2 传递电路信号,主要是将电信号的延迟尽可能减小,在布线时应尽可能使信号线与芯片的互连路径以及通过封装的IO接口引出的路径达到最短。

3 提供散热途径,主要是指各种芯片封装都要考虑元器件、部件长期工作时如何将聚集的热量散出的问题。

4 结构保护与支持,主要是指芯片封装可为芯片和其他连接部件提供牢固可靠的机械支撑,并能适应各种工作环境和条件的变化。

3.在确定集成电路的封装要求时应注意以下儿个因素:1 成本2 外形与结构3 可靠性4 性能4.在选择具体的封装形式时,主要需要考虑4种设计参数:性能、尺寸、重量、可靠性和成本目标。

5.封装工程的技术层次:第一层次(Level1或First Level):该层次又称为芯片层次的封装(Chip Level Packaging),是指把集成电路芯片与封装基板或引脚架(Lead Frame)之间的粘贴固定、电路连线与封装保护的工艺,使之成为易于取放输送,并可与下一层次组装进行连接的模块(组件Module)元件。

第二层次(Level2或Second Level:将数个第一层次完成的封装与其他电子元器件组成个电路卡(Card〉的工艺.第三层次(Level3或Third Level):将数个第二层次完成的封装组装成的电路卡组合成在一个主电路板(Board)上使之成为一个部件或子系(Subsystem)的工艺。

第四层次(Level4或Fourth Level)将数个子系统组装成为一个完整电子产品的工艺过程。

在芯片上的集成电路元器件间的连线工艺也称为零级层次(Level 0)的封装,6.封装的分类:按照封装中组合集成电路芯片的数目,芯片封装可分为:单芯片封装与多芯片封装两大类。

集成电路封装与测试技术

集成电路封装与测试技术随着信息技术的快速发展和应用的广泛普及,集成电路在现代社会中扮演着重要的角色。

而集成电路封装与测试技术作为集成电路制造的重要环节,对于电子产品的性能、可靠性和稳定性起着至关重要的作用。

本文将介绍集成电路封装与测试技术的基本概念、重要性以及相关的发展趋势。

一、集成电路封装技术1.1 封装技术的定义与作用集成电路封装技术是将裸片芯片进行外包装,以提供对芯片的保护、连接和便于插拔。

其主要目标是保证芯片的电性能、机械可靠性和环境适应性,同时满足产品的体积、功耗和成本要求。

1.2 封装技术的分类根据不同的封装方式和结构,集成电路封装技术可以分为裸片封装、芯片级封装和模块级封装等多种形式。

其中,裸片封装是指将芯片直接粘贴在PCB板上,不进行封装的方式;芯片级封装是将芯片封装成单芯片或多芯片封装;模块级封装是将集成电路芯片与其他元器件进行封装。

1.3 封装技术的发展趋势随着集成电路的功能不断增强和尺寸不断缩小,封装技术也在不断创新与发展。

目前,多芯片封装、三维封装、无线封装等是集成电路封装技术的研究热点与发展方向。

这些新技术的应用将进一步提高集成电路的性能和可靠性。

二、集成电路测试技术2.1 测试技术的定义与作用集成电路测试技术是对封装好的集成电路芯片进行功能、电性能和可靠性等方面的验证和测试。

通过测试可以确保芯片的质量和性能符合设计要求,提高产品的可靠性和稳定性。

2.2 测试技术的分类根据不同的测试目的和方法,集成电路测试技术可以分为芯片测试、模块测试和系统测试等多种形式。

其中,芯片测试是对单个芯片进行测试,模块测试是对芯片封装后的模块进行测试,系统测试是对整个集成电路系统进行测试。

2.3 测试技术的发展趋势随着集成电路的复杂度不断提高,传统的测试技术已经无法满足需求。

因此,新型测试技术如板级测试、全片测试、MEMS测试等正在逐渐发展起来。

这些新技术的应用将提高测试效率、降低测试成本,并能同时满足不同级别的测试需求。