PIC32MX695F512H模块使用说明书

MICROCHIP Section 12计时器 dsPIC30F系列参考手册

Section 12. TimersHIGHLIGHTS12.1Introduction..................................................................................................................12-2 12.2Timer Variants..............................................................................................................12-3 12.3Control Registers.........................................................................................................12-6 12.4Modes of Operation.....................................................................................................12-9 12.5Timer Prescalers........................................................................................................12-14 12.6Timer Interrupts..........................................................................................................12-14 12.7Reading and Writing 16-bit Timer Module Registers.................................................12-15 12.8Low Power 32 kHz Crystal Oscillator Input................................................................12-15 12.932-bit Timer Configuration..........................................................................................12-16 12.1032-bit Timer Modes of Operation...............................................................................12-18 12.11Reading and Writing into 32-bit Timers......................................................................12-21 12.12Timer Operation in Power Saving States...................................................................12-21 12.13Peripherals Using Timer Modules..............................................................................12-22 12.14Design Tips................................................................................................................12-24 12.15Related Application Notes..........................................................................................12-2512.16Revision History.........................................................................................................12-26dsPIC30F Family Reference Manual12.1IntroductionDepending on the specific variant, the dsPIC30F device family offers several 16-bit timers. Thesetimers are designated as Timer1, Timer2, Timer3, ..., etc.Each timer module is a 16-bit timer/counter consisting of the following readable/writableregisters:•TMRx: 16-bit timer count register•PRx: 16-bit period register associated with the timer•TxCON: 16-bit control register associated with the timerEach timer module also has the associated bits for interrupt control:•Interrupt Enable Control bit (TxIE)•Interrupt Flag Status bit (TxIF)•Interrupt Priority Control bits (TxIP<2:0>)With certain exceptions, all of the 16-bit timers have the same functional circuitry. The 16-bittimers are classified into three types to account for their functional differences:•Type A time base•Type B time base•Type C time baseSome 16-bit timers can be combined to form a 32-bit timer.This section does not describe the dedicated timers that are associated with peripheral devices.For example, this includes the time bases associated with the Motor Control PWM module andthe Quadrature Encoder Interface (QEI) module.Section 12. Timers12.2Timer VariantsAll 16-bit timers available on the dsPIC30F devices are functionally identical with certain exceptions. The 16-bit timers are classified into three functional types; Type A timers, Type B timers and Type C timers. 12.2.1Type A TimerAt least one Type A timer is available on most dsPIC30F devices. For most dsPIC30F devices,Timer1 is a Type A timer. A Type A timer has the following unique features over other types:•can be operated from the device Low Power 32 kHz Oscillator•can be operated in an Asynchronous mode from an external clock sourceIn particular, the unique features of a Type A timer allow it to be used for Real-Time Clock (RTC)applications. A block diagram of the Type A timer is shown in Figure 12-1.Figure 12-1:Type A Timer Block DiagramNote:Please refer to the device data sheet for the available timers and the type of each.TONSyncSOSCISOSCOPRxTxIFEqualComparator x 16 TMRxResetNote 1:Refer to Section 7.“Oscillator” for information on enabling the LP Oscillator.LPOSCENEvent Flag(Note 1)1TSYNCQQ D CKTGATETCKPS<1:0>Prescaler 1, 8, 64, 2562TGATE T CY1 0T C S 1 X0 1T G A T E0 0Gate SyncdsPIC30F Family Reference Manual12.2.2Type B TimerTimer2 and Timer4, if present, are Type B timers on most dsPIC30F devices. A Type B timer has the following unique features over other types of timers:• A Type B timer can be concatenated with a Type C timer to form a 32-bit timer. The TxCON register for a Type B timer has the T32 control bits to enable the 32-bit timer function.•The clock synchronization for a Type B timer is performed after the prescale logic.A block diagram of the Type B timer is shown in Figure 12-2.Figure 12-2:Type B Timer Block DiagramTONSyncPRxTxIFEqualComparator x 16TMRx ResetEvent FlagQQ D CKTGATETCKPS<1:0>Prescaler 1, 8, 64, 2562TGATET CY1 0T C S 1 X 0 1T G A T E0 0Gate TxCKISyncSection 12. Timers12.2.3Type C TimerTimer3 and Timer5 are Type C timers on most dsPIC30F devices. A Type C timer has the following unique features over other types of timers:• A Type C timer can be concatenated with a Type B timer to form a 32-bit timer.•On a given device, at least one Type C timer has the ability to trigger an A/D conversion.A block diagram of the Type C timer is shown in Figure 12-3.Figure 12-3:Type C Timer Block DiagramTONPRxTxIFEqualComparator x 16TMRxReset Event FlagQQ D CKTGATETCKPS<1:0>Prescaler 1, 8, 64, 2562TGATET CY1 0T C S 1 X 0 1T G A T E0 0TxCKADC Event Note:In certain variants of the dsPIC30F family, the TxCK pin may not be available. Refer to the device data sheet for the I/O pin details. In such cases, the timer must use the system clock (F OSC /4) as its input clock, unless it is configured for 32-bit operation.Sync TriggerdsPIC30F Family Reference Manual12.3Control RegistersRegister 12-1:TxCON: Type A Time Base RegisterUpper Byte:R/W-0U-0R/W-0U-0U-0U-0U-0U-0TON—TSIDL—————bit 15bit 8Lower Byte:U-0R/W-0R/W-0R/W-0U-0R/W-0R/W-0U-0— TGATE TCKPS<1:0>—TSYNC TCS—bit 7bit 0bit 15TON: Timer On Control bit1 = Starts the timer0 = Stops the timerbit 14Unimplemented: Read as ‘0’bit 13TSIDL: Stop in Idle Mode bit1 = Discontinue timer operation when device enters Idle mode0 = Continue timer operation in Idle modebit 12-7Unimplemented: Read as ‘0’bit 6TGATE: Timer Gated Time Accumulation Enable bit1 = Gated time accumulation enabled0 = Gated time accumulation disabled(TCS must be set to ‘0’ when TGATE = 1. Reads as ‘0’ if TCS = 1)bit 5-4TCKPS<1:0>: Timer Input Clock Prescale Select bits11 = 1:256 prescale value10 = 1:64 prescale value01 = 1:8 prescale value00 = 1:1 prescale valuebit 3Unimplemented: Read as ‘0’bit 2TSYNC: Timer External Clock Input Synchronization Select bitWhen TCS = 1:1 = Synchronize external clock input0 = Do not synchronize external clock inputWhen TCS = 0:This bit is ignored. Read as ‘0’. Timer1 uses the internal clock when TCS = 0.bit 1TCS: Timer Clock Source Select bit1 = External clock from pin TxCK0 = Internal clock (F OSC/4)bit 0Unimplemented: Read as ‘0’Legend:R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’-n = Value at POR‘1’ = Bit is set‘0’ = Bit is cleared x = Bit is unknownSection 12. TimersRegister 12-2:TxCON: Type B Time Base Register Upper Byte:R/W-0U-0R/W-0U-0U-0U-0U-0U-0TON —TSIDL—————bit 15bit 8Lower Byte:U-0R/W-0R/W-0R/W-0R/W-0U-0R/W-0U-0—TGATE TCKPS<1:0>T32—TCS—bit 7bit 0bit 15TON: Timer On bitWhen T32 = 1 (in 32-bit Timer mode):1 = Starts 32-bit TMRx:TMRy timer pair 0 = Stops 32-bit TMRx:TMRy timer pair When T32 = 0 (in 16-bit Timer mode):1 = Starts 16-bit timer 0 = Stops 16-bit timer bit 14Unimplemented: Read as ‘0’bit 13TSIDL: Stop in Idle Mode bit1 = Discontinue timer operation when device enters Idle mode 0 = Continue timer operation in Idle mode bit 12-7Unimplemented: Read as ‘0’bit 6TGATE: Timer Gated Time Accumulation Enable bit 1 = Timer gated time accumulation enabled 0 = Timer gated time accumulation disabled (TCS must be set to logic ‘0’ when TGATE = 1)bit 5-4TCKPS<1:0>: Timer Input Clock Prescale Select bits 11 = 1:256 prescale value 10 = 1:64 prescale value 01 = 1:8 prescale value 00 = 1:1 prescale valuebit 3T32: 32-bit Timer Mode Select bits1 = TMRx and TMRy form a 32-bit timer0 = TMRx and TMRy form separate 16-bit timer bit 2Unimplemented: Read as ‘0’bit 1TCS: Timer Clock Source Select bit 1 = External clock from pin TxCK 0 = Internal clock (F OSC /4)bit 0Unimplemented: Read as ‘0’Legend:R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’-n = Value at POR‘1’ = Bit is set‘0’ = Bit is clearedx = Bit is unknowndsPIC30F Family Reference ManualRegister 12-3:TxCON: Type C Time Base RegisterUpper Byte:R/W-0U-0R/W-0U-0U-0U-0U-0U-0TON—TSIDL—————bit 15bit 8Lower Byte:U-0R/W-0R/W-0R/W-0U-0U-0R/W-0U-0—TGATE TCKPS<1:0>——TCS—bit 7bit 0bit 15TON: Timer On bit1 = Starts 16-bit TMRx0 = Stops 16-bit TMRxbit 14Unimplemented: Read as ‘0’bit 13TSIDL: Stop in Idle Mode bit1 = Discontinue module operation when device enters Idle mode0 = Continue module operation in Idle modebit 12-7Unimplemented: Read as ‘0’bit 6TGATE: Timer Gated Time Accumulation Enable bit1 = Timer gated time accumulation enabled0 = Timer gated time accumulation disabled (Read as ‘0’ if TCS = 1)(TCS must be set to logic ‘0’ when TGATE = 1)bit 5-4TCKPS<1:0>: Timer Input Clock Prescale Select bits11 = 1:256 prescale value10 = 1:64 prescale value01 = 1:8 prescale value00 = 1:1 prescale valuebit 3-2Unimplemented: Read as ‘0’bit 1TCS: Timer Clock Source Select bit1 = External clock from pin TxCK0 = Internal clock (F OSC/4)bit 0Unimplemented: Read as ‘0’Legend:R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’-n = Value at POR‘1’ = Bit is set‘0’ = Bit is cleared x = Bit is unknownSection 12. Timers12.4Modes of OperationEach timer module can operate in one of the following modes:•As a synchronous timer •As a synchronous counter •As a gated timer•As an asynchronous counter (Type A time base only)The Timer modes are determined by the following bits:•TCS (TxCON<1>): Timer Clock Source Control bit•TSYNC (T1CON<2>): Timer Synchronization Control bit (Type A time base only)•TGATE (TxCON<6>): Timer Gate Control bitEach timer module is enabled or disabled using the TON Control bit (TxCON <15>). 12.4.1Timer ModeAll types of timers have the ability to operate in Timer mode. In Timer mode, the input clock to the timer is provided from the internal system clock (F OSC /4). When enabled, the timer increments once per instruction cycle for a 1:1 prescaler setting. The Timer mode is selected by clearing the TCS control bit (TxCON<1>). The Synchronous mode control bit, TSYNC (T1CON<2>), has no effect, since the system clock source is used to generate the timer clock. Example 12-1:Initialization Code for 16-bit Timer Using System ClockNote:Only Type A time bases support the External Asynchronous Clock mode.;The following code example will enable Timer1 interrupts, ;load the Timer1 Period register and start Timer1.;When a Timer1 period match interrupt occurs, the interrupt ;service routine must clear the Timer1 interrupt status flag ;in software. CLR T1CON ; Stops the Timer1 and reset control reg. CLR TMR1; Clear contents of the timer register MOV #0xFFFF, w0; Load the Period register MOVw0, PR1; with the value 0xFFFFBSET IPC0, #T1IP0; Setup Timer1 interrupt for BCLR IPC0, #T1IP1; desired priority levelBCLR IPC0, #T1IP2; (this example assigns level 1 priority)BCLR IFS0, #T1IF ; Clear the Timer1 interrupt status flag BSET IEC0, #T1IE ; Enable Timer1 interruptsBSETT1CON, #TON; Start Timer1 with prescaler settings ; at 1:1 and clock source set to ; the internal instruction cycle; Example code for Timer1 ISR __T1Interrupt:BCLR IFS0, #T1IF; Reset Timer1 interrupt flag ; User code goes here.RETFIE; Return from ISRdsPIC30F Family Reference Manual12.4.2Synchronous Counter Mode Using External Clock InputWhen the TCS control bit (TxCON<1>) is set, the clock source for the timer is provided externallyand the selected timer increments on every rising edge of clock input on the TxCK pin.External clock synchronization must be enabled for a Type A time base. This is accomplished bysetting the TSYNC control bit (TxCON<2>). For Type B and Type C time bases, the externalclock input is always synchronized to the system instruction cycle clock, T CY.When the timer is operated in the Synchronized Counter mode, there are minimum requirementsfor the external clock high time and low time. The synchronization of the external clock sourcewith the device instruction clock is accomplished by sampling the external clock signal at twodifferent times within an instruction cycle.A timer operating from a synchronized external clock source will not operate in Sleep mode,since the synchronization circuit is shut-off during Sleep mode.Note:The external input clock must meet certain minimum high time and low timerequirements when Timerx is used in the Synchronous Counter mode. Refer to thedevice data sheet “Electrical Specifications” section for further details.Example 12-2:Initialization Code for 16-bit Synchronous Counter Mode Using anExternal Clock Input;The following code example will enable Timer1 interrupts, load the;Timer1 Period register and start Timer1 using an external clock;and a 1:8 prescaler setting.;When a Timer1 period match interrupt occurs, the interrupt service;routine must clear the Timer1 interrupt status flag in software.CLR T1CON; Stops the Timer1 and reset control reg.CLR TMR1; Clear contents of the timer registerMOV#0x8CFF, w0; Load the Period registerMOV w0, PR1; with the value 0x8CFFBSET IPC0,#T1IP0; Setup Timer1 interrupt forBCLR IPC0,#T1IP1; desired priority levelBCLR IPC0,#T1IP2; (this example assigns level 1 priority)BCLR IFS0,#T1IF; Clear the Timer1 interrupt status flagBSET IEC0,#T1IE; Enable Timer1 interruptsMOV#0x8016, W0; Start Timer1 with prescaler settings at; 1:8 and clock source set to the externalMOV w0, T1CON; clock in the synchronous mode;Example code for Timer1 ISR__T1Interrupt:BCLR IFS0,#T1IF; Reset Timer1 interrupt flag; User code goes here.RETFIE; Return from ISR12.4.3Type A Timer Asynchronous Counter Mode Using External Clock InputA Type A time base has the ability to operate in an Asynchronous Counting mode, using an external clock source connected to the TxCK pin. When the TSYNC control bit (TxCON<2>) is cleared, the external clock input is not synchronized with the device system clock source. The time base continues to increment asynchronously to the internal device clock.The asynchronous operation time base is beneficial for the following applications:•The time base can operate during Sleep mode and can generate an interrupt on period register match that will wake-up the processor.•The time base can be clocked from the low power 32 kHz oscillator for real-time clock applicationsPlease see Section 12.12.1“Timer Operation in Sleep Mode” for more details..Example 12-3:Initialization Code for 16-bit Asynchronous Counter Mode Using anExternal Clock Input Note 1:Only Type A time bases support the Asynchronous Counter mode.2:The external input clock must meet certain minimum high time and low timerequirements when Timerx is used in the Asynchronous Counter mode. Refer to thedevice data sheet “Electrical Specifications” section for further details.3:Unexpected results may occur when reading Timer1, in asynchronous mode. ;The following code example will enable Timer1 interrupts, load the;Timer1 Period register and start Timer1 using an asynchronous;external clock and a 1:8 prescaler setting.;When a Timer1 period match interrupt occurs, the interrupt service;routine must clear the Timer1 interrupt status flag in software.CLR T1CON ; Stops the Timer1 and reset control reg.CLR TMR1; Clear contents of the timer registerMOV #0x7FFF, w0; Load the Period registerMOV w0, PR1; with the value 0x7FFFBSET IPC0,#T1IP0; Setup Timer1 interrupt forBCLR IPC0,#T1IP1; desired priority levelBCLR IPC0,#T1IP2; (this example assigns level 1 priority)BCLR IFS0,#T1IF ; Clear the Timer1 interrupt status flagBSET IEC0,#T1IE ; Enable Timer1 interruptsMOV #0x8012, w0; Start Timer1 with prescaler settings at; 1:8 and clock source set to the externalMOV w0, T1CON ; clock in the asynchronous mode; Example code for Timer1 ISR__T1Interrupt:BCLR IFS0,#T1IF ; Reset Timer1 interrupt flag; User code goes here.RETFIE ; Return from ISR12.4.4Timer Operation with Fast External Clock SourceIn some applications, it may be desirable to use one of the timers to count clock edges from arelatively high frequency external clock source. In these situations, Type A and Type B timebases are the most suitable choices for counting the external clock source, because the clocksynchronization logic for these timers is located after the timer prescaler (see Figure12-1 andFigure12-2). This allows a higher external clock frequency to be used that will not violate theminimum high and low times required by the prescaler. When a timer prescaler ratio other than1:1 is selected for a Type A or Type B time base, the minimum high and low times for the externalclock input are reduced by the chosen prescaler ratio.A Type A time base is unique because it can be operated in an Asynchronous Clock mode,eliminating any prescaler timing requirements.Note that in all cases, there are minimum high and low times for the external clock signal thatcannot be exceeded. These minimum times are required to satisfy the I/O pin timingrequirements.Please refer to the device data sheet for the external clock timing specifications associated withthe time bases.12.4.5Gated Time Accumulation ModeThe Gated Time Accumulation mode allows the internal timer register to increment based uponthe duration of the high time applied to the TxCK pin. In the Gated Time Accumulation mode, thetimer clock source is derived from the internal system clock. When the TxCK pin state is high, thetimer register will count up until a period match has occurred, or the TxCK pin state is changedto a low state. A pin state transition from high to low will set the TxIF interrupt flag. Depending onwhen the edge occurs, the interrupt flag is asserted 1 or 2 instruction cycles after the falling edgeof the signal on the TxCK pin.The TGATE control bit (TxCON<6>) must be set to enable the Gated Time Accumulation mode.The timer must be enabled, TON (TxCON<15>) = 1, and the timer clock source set to the internalclock, TCS (TxCON<1>) = 0.The gate operation starts on a rising edge of the signal applied to the TxCK pin and terminateson the falling edge of the signal applied to the TxCK pin. The respective timer will increment whilethe external gate signal is high.The falling edge of the gate signal terminates the count operation, but does not reset the timer.The user must reset the timer if it is desired to start from zero on the next rising edge gate input.The falling edge of the gate signal generates an interrupt.Note:The timer will not interrupt the CPU when a timer period match occurs in Gate TimeAccumulation mode.The resolution of the timer count is directly related to the timer clock period. For a timer prescalerof 1:1, the timer clock period is one instruction cycle. For a timer prescaler of 1:256, the timerclock period is 256 times the instruction cycle. The timer clock resolution can be associated tothe pulse width of the gate signal. Refer to the “Electrical Specifications” section in the devicedata sheet for further details on the gate width pulse requirements.Figure 12-4: Gated Timer Mode OperationExample 12-4:Initialization Code for 16-bit Gated Time Accumulation ModeTxIF00010002TMRx 1 Instruction Cycle (T CY )00040003TxCK pin00050000TxIF bit cleared by user in software.;The following code example will enable Timer2 interrupts, load the;Timer2 Period register and start Timer2 using an internal clock;and an external gate signal. On the falling edge of the gate;signal a Timer2 interrupt occurs. The interrupt service;routine must clear the Timer2 interrupt status flag in software .CLR T2CON ; Stops the Timer2 and reset control reg.CLR TMR2; Clear contents of the timer registerMOV #0xFFFF, w0; Load the Period register withMOV w0, PR2; the value 0xFFFFBSET IPC1,#T2IP0; Setup Timer2 interrupt forBCLR IPC1,#T2IP1; desired priority levelBCLR IPC1,#T2IP2; (this example assigns level 1 priority)BCLR IFS0,#T2IF ; Clear the Timer2 interrupt status flagBSET IEC0,#T2IE ; Enable Timer2 interruptsBSET T2CON,#TGATE ; Set up Timer2 for operation in Gated; Time Accumulation modeBSET T2CON,#TON ; Start Timer2;Example code for Timer2 ISR__T2Interrupt:BCLR IFS0,#T2IF ; Reset Timer2 interrupt flag; User code goes here.RETFIE ; Return from ISR12.5Timer PrescalersThe input clock (F OSC /4 or external clock) to all 16-bit timers has prescale options of 1:1, 1:8,1:64 and 1:256. The clock prescaler is selected using the TCKPS<1:0> control bits (TxCON<5:4>). The prescaler counter is cleared when any of the following occurs:• A write to the TMRx register•Clearing TON (TxCON<15>) to ‘0’•Any device Reset12.6Timer InterruptsA 16-bit timer has the ability to generate an interrupt on a period match or falling edge of the external gate signal, depending on the Operating mode.The TxIF bit is set when one of the following conditions is true:•The timer count matches the respective period register and the timer module is notoperating in Gated Time Accumulation mode.•The falling edge of the “gate” signal is detected when the timer is operating in Gated Time Accumulation mode.The TxIF bit must be cleared in software.A timer is enabled as a source of interrupt via the respective timer interrupt enable bit, TxIE.Furthermore, the interrupt priority level bits (TxIP<2:0>) must be written with a non-zero value in order for the timer to be a source of interrupt. Refer to Section 6.“Reset Interrupts” for further details.Figure 12-5:Interrupt Timing for Timer Period MatchNote:The TMRx register is not cleared when TxCON is written.Note: A special case occurs when the period register is loaded with 0x0000 and the timeris enabled. No timer interrupts will be generated for this configuration.TxIF0003000547FE 47FF 4800000047FD TMR200041 Instruction Cycle (T CY )4800PR20002TMR2 Resets Here 0001Cleared by User12.7Reading and Writing 16-bit Timer Module Registers•All timer module SFRs can be written to as a byte (8-bits) or as a word (16-bits).•All timer module SFRs can only be read as a word (16-bits).12.7.1Writing to the 16-bit TimersThe timer and its respective period register can be written to while the module is operating. The user should be aware of the following when byte writes are performed:•If the timer is incrementing and the low byte of the timer is written to, the upper byte of the timer is not affected. If 0xFF is written into the low byte of the timer, the next timer count clock after this write will cause the low byte to rollover to 0x00 and generate a carry into the high byte of the timer.•If the timer is incrementing and the high byte of the timer is written to, the low byte of the timer is not affected. If the low byte of the timer contains 0xFF when the write occurs, the next timer count clock will generate a carry from the timer low byte and this carry will cause the upper byte of the timer to increment.When the TMRx register is written to (word or byte) via an instruction, the TMRx register increment is masked and does not occur during that instruction cycle.Writes to a timer with an asynchronous clock source should be avoided in a real-timekeeping application. See Section 12.4.1“Timer Mode” for more details.12.7.2Reading from the 16-bit TimersAll reads of the timers and their associated SFRs must be word reads (16-bits). A byte read will have no effect (‘0’ will be returned).The timer and respective period register can be read while the module is operating. A read of the TMRx register does not prevent the timer from incrementing during the same instruction cycle.12.8Low Power 32 kHz Crystal Oscillator InputIn each device variant, the Low Power 32 kHz Crystal Oscillator is available to a Type A timer module for Real-Time Clock (RTC) applications.•The LP Oscillator becomes the clock source for the timer when the LP Oscillator isenabled and the timer is configured to use the external clock source.•The LP Oscillator is enabled by setting the LPOSCEN control bit in the OSCCON register.•The 32 kHz crystal is connected to the SOSCO/SOSCI device pins.Refer to Section 7.“Oscillator” for further details.12.932-bit Timer ConfigurationA 32-bit timer module can be formed by combining a TypeB and a TypeC 16-bit timer module.The Type C time base becomes the MSWord of the combined timer and the Type B time base isthe LSWord.When configured for 32-bit operation, the control bits for the Type B time base control the operationof the 32-bit timer. The control bits in the TxCON register for the Type C time base have no effect.For interrupt control, the combined 32-bit timer uses the interrupt enable, interrupt flag andinterrupt priority control bits of the Type C time base. The interrupt control and status bits for theType B time base are not used during 32-bit timer operation.Note:Refer to the device data sheet for information on the specific Type B and Type Ctime bases that can be combined.The following configuration settings assume Timer3 is a Type C time base and Timer2 is a Type Btime base:•TON (T2CON<15>) = 1.•T32 (T2CON<3>) = 1.•TCKPS<1:0> (T2CON<5:4>) are used to set the Prescaler mode for Timer2(Type B time base).•The TMR3:TMR2 register pair contains the 32-bit value of the timer module; the TMR3(Type C time base) register is the Most Significant Word, while the TMR2 (Type B timebase) register is the Least Significant Word of the 32-bit timer value.•The PR3:PR2 register pair contains the 32-bit period value that is used for comparison withthe TMR3:TMR2 timer value.•T3IE (IEC0<7>) is used to enable the 32-bit timer interrupt for this configuration.•T3IF (IFS0<7>) is used as a status flag for the timer interrupt.•T3IP<2:0> (IPC1<14:12>) sets the interrupt priority level for the 32-bit timer.•T3CON<15:0> are “don’t care” bits.A block diagram representation of the 32-bit timer module using Timer2 and Timer3 as anexample is shown in Figure12-6.。

芯海科技 ARM M M0-based MCU 输出手册说明书

输出手册版本历史版本号说明日期1.0 初版2019-6-171.1 1. LRC频率:min(30->27),max(50->62)2. ADC特性更新: fADC-40℃≤ Trange ≤ 85℃,fADC≤14MHz,支持电压范围2.65≤ VDDA ≤5.5V;-40℃≤ Trange ≤ 105℃,fADC≤14MHz,支持电压范围2.7≤ VDDA ≤5.5V;-40℃≤ Trange ≤ 105℃,fADC≤12MHz,支持电压范围2.4≤ VDDA ≤5.5V;进入校准模式,fADC≤12MHz。

进入正常转换模式,fADC≤14MHz。

支持:-40℃≤ Trange ≤ 105℃和电压范围2.4≤ VDDA ≤5.5V;3. ADC特性更新:VDDA=2.4V时,Offset和ERR Gain更新2020-6-31.2 1.增加G6U6版本相关信息2020-6-191.3 1.更新温度传感器线性度参数,区分不同温度范围2020-8-262/56文件编号:CS-QR-YF-054A02目录输出手册版本历史 (2)目录 (3)1介绍 (5)2功能 (6)3器件一览 (8)4引脚描述 (10)4.1LQFP48 (10)4.2LQFP32 (10)4.3QFN28L (11)4.4TSSOP20 (11)4.5引脚描述 (12)5I/O 复用 (15)5.1PA口复用功能 (15)5.2PB口复用功能 (16)6存储器 (17)7功能描述 (21)7.1ARM®C ORTEX®-M0内核 (21)7.2存储器 (21)7.3时钟 (21)7.4工作环境 (23)7.4.1工作电压 (23)7.5启动模式 (23)7.6电源管理 (23)7.6.1低功耗模式 (23)7.6.2RTC和备用寄存器的电源电压VBAT (23)7.6.3上电复位/掉电复位(POR/PDR) (23)7.6.4低电压复位模块(LVD) (24)7.7通用输入输出端口(I/O) (24)7.8模数转换器(ADC) (24)7.8.1温度传感器(TS) (24)7.8.2内部参考电压 (24)7.8.3VBAT监测 (25)7.9定时器 (25)7.9.1高级定时器 (TIM1) (25)7.9.2通用定时器 (TIM3, 14, 15,16, 17) (25)7.9.3基本定时器(TIM6) (26)7.9.4独立看门狗定时器(FWDT) (26)7.9.5窗看门狗定时器(WWDT) (26)7.9.6滴答定时器(SysTick) (26)7.10直接内存存取(DMA) (26)3/56文件编号:CS-QR-YF-054A027.11中断和事件 (26)7.12实时时钟(RTC)和备用寄存器 (26)7.13串行外设总线(SPI)/集成电路内置音频总线(I2S) (27)7.14通用同步异步收发器(USART) (27)7.15内置集成电路接口(I2C) (29)7.16循环冗余校验 (29)7.17串行调试端口(SWD-DP) (29)8电气特性 (30)8.1说明 (30)8.2绝对最大额定值 (31)8.3工作条件 (31)8.4I/O端口特性 (32)8.5低功耗模式唤醒时间 (33)8.6RC振荡特性 (33)8.7晶振特性 (34)8.8外部时钟特性 (36)8.9PLL特性 (36)8.10功耗 (37)8.11内部参考电压特性 (38)8.12ADC特性 (38)8.13温度传感器特性 (39)8.14VBAT监测器特性 (39)8.15F LASH 特性 (39)8.16定时器特性 (40)8.17SPI/I2S特性 (40)8.18I2C特性 (44)8.19ESD特性 (44)9封装信息 (46)9.1LQFP48 (46)9.2LQFP32 (48)9.3QFN28L (49)9.4TSSOP20 (51)10订货信息 (52)11勘误表 (53)12缩略语 (54)13销售和服务 (56)4/56文件编号:CS-QR-YF-054A021介绍CS32F030系列微控制器采用高性能的32位ARM® Cortex®-M0 内核,嵌入高达64Kbytes flash和8Kbytes SRAM,最高工作频率48MHz。

usb数据采集卡V52_32使用说明书

usb数据采集卡V52_32使⽤说明书USB 数据采集卡V5.2_32使⽤⼿册新郑市恒凯电⼦科技有限公司2016/3USB2.0总线AD 采集模块 32路同步单端输⼊16位 20KHz AD,192K FIFO 缓冲 2路12位0—10V 量程DA 输出16路单向输⼊⼝/16路单向输出⼝在开始使⽤前请仔细阅读下⾯说明检查打开包装请查验如下:USB数据采集卡V52_32⼀块配套电源及USB数据线安装将数据采集卡插⼊主机的任何⼀个USB2.0插槽中并将外部的输⼊、输出线连好。

如果主机USB电源供应能⼒差,请连接附送的电源。

保修本产品⾃售出之⽇起⼀年内,⽤户遵守储存、运输和使⽤要求,⽽产品质量不合要求,凭保修单免费维修。

因违反操作规定和要求⽽造成损坏的,需缴纳器件费及相应的运输费⽤,如果板卡有明显烧毁、烧糊情况原则上不予维修。

如果板卡开箱测试有问题,可以免费维修(限购买板卡10天内)。

软件⽀持服务⾃销售之⽇起提供6个⽉的免费开发咨询。

(如有刊误,敬请批评指正!)⽬录⽬录 (2)⼀、USB数据采集卡V52_32说明 (4)USB数据采集卡V52_32板简介 (4)特点: (4)主要特点、性能: (5)AD部分: (5)DA输出 (5)开关量输⼊输出 (5)软件⽀持: (6)其他特性 (6)⼆、原理说明 (7)2-1:模拟输⼊输出接⼝ (7)AD数据排列 (7)AD数据转换 (7)内部定时器时钟与外部时钟 (7)触发开始采样 (8)过采样及相关说明 (8)2-2:开关量部分的原理: (10)2-3:模拟输出DA (10)三、安装与连接 (11)3-1:安装 (11)关于USB (11)USB延长线 (11)3-2:信号连接注意事项 (11)3-3:连接器插座定义 (12)16 DIN定义: (12)16 DOUT定义: (13)3-4:配套端⼦板 (13)四、软件 (15)4-1:软件安装与说明 (15)软件说明 (15)驱动安装 (16)测试软件安装 (19)4-2:接⼝函数说明 (22)设备操作函数 (22)AD操作函数 (23)DA操作函数 (25)单向开关量输⼊操作函数 (25)单向开关量输出操作函数 (26)4-3:VC程序编程说明 (28)4-4 Labview程序编程说明 (29)⼀、USB数据采集卡V52_32说明USB数据采集卡V52_32板简介USB数据采集卡V5.2_32是⼀款基于USB总线的⾼性能多功能数据采集卡,具有32路单端16位⾼速同步模拟信号采集(最⾼同步采样速率50KSPS,同步采样即每通道都是50KSPS)、2路12位模拟信号输出(只有单次低速输出模式)、16路数字信号单向输⼊/16路数字信号单向输出。

OKdo 5MP 摄像头模块说明书

5MP Camera User ManualSKU: 202-04561. GeneralThe OKdo 5MP Camera is a low-cost wider Field View camera module, designed for the whole Raspberry Pi series(P4/Pi3 B+/PI3 A+/PI3/PI ZERO/PI ZERO W/CM3+/CM3). The OKdo 5MP Camera has a 5M Pixel sensor, and connects via a ribbon cable to the CSI connector on the Raspberry Pi.Plug and Play device, driver-free. Supports all Raspberry Pi original camera tools, such as raspistill, raspivid etc.2. Features1. The OKdo 5MP Camera is a low-cost wider field view camera module that designed for Raspberry Pi 4, Pi 3 B+, Pi 3, Pi 2, Pi B+, Pi A, Pi Zero/Zero W. Comes with both ribbon cable sizes for compatibility with classic Raspberry Pi and Zero.2.Connects to the CSI connector of Raspberry Pi directly. High bandwidth communication from the camera module to the Raspberry pi.3.Sensor type: On-board OmniVision OV5647[6] Color CMOS QSXGA (5-megapixel); Video: 1080p at 30 fps with codec H.264 (AVC).4.Lens Feature: 2.8 Focal Length. F/NO: 2.2. Field Of view: D=90° H=74°. Element: 4G+IR. CRA: 10°. Relative Illumination: 52%. Focal distance is adjustable.5.Plug and Play device, driver-free for all raspberry pi boards, no need to install extra software.3.Hardware Description 3.1 Overview3.2 Size3.3 Wiring4.Software Description4.1Load imagePrepare a capacity of more than 8GB TF card and a card reader. Load the image file on to the SD card, using the instructions provided on the Raspberry Pi website for Linux, Mac or PC:https:///documentation/installation/installing-images/README.md Raspbian Raspberry Pi OS Image download:https:///downloads/If your Raspberry Pi OS is not the latest version. Y ou can use below command update. sudo apt-get updatesudo apt-get upgrade4.2Enable Camera(1) Open the raspi-config tool when you first set up your Raspberry Pi:sudo raspi-config(2)Select ‘Interfacing Options’ → ‘Camera’. and then enable camer and reboot.4.3Take Photos(1)take a picture name ‘test’.raspistill -o test.jpg(2)take a picture name ‘test’ with resolution 640*480raspistill -o test.jpg -w 640 -h 480(3)take a picture name ‘test’ after 10 seconds(10000ms).raspistill -t 10000 -o test.jpg(4)Take a picture name ‘test’ with PNG format(raw date) . If will take more time to save. raspistill -o test.png -e png4.4Take H.264 Video(1)take a 10s(10000ms) video name ‘test’.raspivid -o test.h264 -t 10000(2)take a 10s(10000ms) video name ‘test’ with resolution 1280*720.raspivid -o test.h264 -t 10000 -w 1280 -h 7204.5ReferenceThe OKdo 5MP Camera can be used in the same way as a standard Pi camera.For more information, please refer to below link:https:///en/projects/getting-started-with-picamerahttps:///forums/viewforum.php?f=43&sid=7b94c5651e50c2fc2af0a049 066cdfda。

基于KSZ8873的双网口协议转换模块设计

图2 软件架构 预先对管脚进行上下拉操作。

表1给出了网口1、网口2和RMII 总线在KSZ8873芯片的管脚分布。网 口1和网口2为对外网口。RMII接口与 PIC32单片机的RMII接口连接。 1.3 单片机以及外围电路

单片机PIC32MX695F512H主要 使用资源包括UART1、UART2和RMII 接口。其中UART1和UART2分别经过 MAX232和MAX485芯片转换成RS232 和RS485接口。RMII接口与KSZ8873 的RMII接口连接。该部分电路成熟度 高,在此不作赘述。

务。每个子任务主要完成从驱动层接

收并解析数据帧,传入应用层;或者

从应用层获取实时数据,按照协议进

行组帧后,传入驱动层发送。

为了提高软件执行效率和可靠

性,采用时分方式进行子任务调度,

调度时间间隔为10ms。系统使用1ms

图4 组网模式

表1 KSZ8873接口分布

接口 网口1 网口2

RMII接口

网络名 NET_RXN1 NET_RXP1 NET_TXN1 NET_TXP1 NET_RXN2 NET_RXP2 NET_TXN2 NET_TXP2

针对新建设备网络和旧设备网络 化改造两方面问题,本文提出的双网 口转换模块,既可对新设备进行网络 化设计,又能对旧设备进行网络化改 造。具有低成本、高可靠等优点。

1 硬件设计 1.1 模块原理

如图1所示,模块包含两个子模 块,交换子模块和转换子模块。

交换子模块的主要器件为 KSZ8873[1],包含了两个对外的RJ45 接口(标准网口)和一个对内的RMII 接口,其中对外RJ45网口由KSZ8873 的两组标准差分总线经网络变压器转 换生成,RMII接口由KSZ8873的标准 RMII总线[2]转换而来。交换子模块有 两个主要功能,一是实现两个对外 网口间的数据交换,该过程完全由 KSZ8873芯片自动完成,不需要软件 参与;二是完成两个对外网口与对内 RMII接口间的数据交换,该过程需要 与转换子模块配合进行。

大连东福彩色液晶显示器模块使用说明书

EDM12232-06图形点阵式液晶显示模块使用说明大连东福彩色液晶显示器有限公司1. 使用范围----------------------------------------------------22. 质量保证----------------------------------------------------23. 性能特点----------------------------------------------------24. 外形图-------------------------------------------------------65. I/O接口特性-----------------------------------------------76. 质量等级---------------------------------------------------167. 可靠性---------------------------------------------------198. 生产注意事项---------------------------------------------199. 使用注意事项---------------------------------------------20第 2 页共 20页第 3 页 共 20页1、使用范围该检验标准适用于大连东福公司设计提供的标准液晶显示模块。

如果在使用中出现了异常问题或没有列明的项目,建议同最近的供应商或本公司联系。

2、质量保证 如在此手册列明的正常条件下使用、储存该产品,公司将提供12个月的质量保证。

3、性能特点3-1.性能:显示方式 : 半透、正显黄绿色 STN LCD 显示颜色 : 显示点: 深蓝色背景:黄绿色显示形式 : 122(w)×32 (h) 全点阵 输入数据 : 来自MPU 的8位并行数据接口 驱动路数 : 1/32 Duty视 角 :6 点3-2.机械性能:项 目 规 格 单位外形尺寸 84.0(W)×44.0(H) ×14.0 Max. Mm 显示点阵数 122(W) ×32 (H) Dots —视 域 60.0(W)×18.0(H) Mm 显示图形域 48.76(W)×15.32H) Mm 点间距 0.4(W)×0.45(H) Mm 点尺寸 0.36(W)×0.41(H) Mm 重量 Approx. 40 G3-3. 极限参数:项目 符 号 最小值 最大值 单位 注 释逻辑 Vdd-0.3 7.0 V 电源电压 LCD 驱动 Vdd – Vee VDD-13.5VDD-3.5V 输入电压 Vi -0.3 VDD+0.3V 操作温度 Top -10 50 ℃ 储存温度 Tstg -20 60 ℃ 湿度 — — 90 %RH 背光驱动动电压 VBL — 5.0 VLCD 模块使用手册第 4 页 共 20页3-4. 电气特性:3-4-1 电气参数项 目 符 号 条 件 最小值典型值 最大值 单 位 逻辑 Vdd 4.5 5.00 5.5电源电压LCD 驱动 Vdd–Vee — 5.0 —高电平 Vih Vdd=5V ±5% 2.0 — Vdd输入电压低电平 Vil 0 — 0.8V频 率 Fflm Vdd=5V — 75 — Hz逻辑 Idd — 0.44 —功 耗 LCD 驱动 Iee Vdd=5V Vdd–Vee=5.2VFflm=75Hz — 0.42 —mA Ta= -20℃φ=0°,θ=0°— — —Ta= 25℃φ=0°,θ=0°— 5.0 — LCD 驱动电压 (推荐电压) Vdd–Vee Ta= 60℃φ=0°,θ=0° — — —VNote: <1> 驱动路数=1/32 <2> 所有点在静态条 3-5. 光电特性项 目 符号温度 条件 最小值典型值最大值 单位 注释 -20℃ — — —25℃ — 5.0 — LCD 驱动电压 (推荐电压) V LCD 60℃ φ=0°,θ=0°— — — V 1,2,5-20℃ — 750 1100 上升时间 tr25℃ — 150 200 -20℃ — 1000 1500响应时间 衰退时间 td 25℃ φ=0°,θ=0° — 150 200Ms 1,3,5垂直 — +50/-45—视 角Δφ 25℃水平 — +55/-55—deg. 1,4,5对比度 K 25℃ φ=0°,θ=0°2 — 5 — 1,5,6注意:<1> φ和θ的定义<2> 在此电压范围内能获得对比度大于2(k≥2)第 5 页共 20页第 6 页 共 20页注意:<6> 对比度定义(K)正显负显非选择点的亮度(B2) 选择点的亮度(B1)4、外形图第 7 页 共 20页5、I/O 接口特性5-1. I/O 接口表:管脚号 符号功 能1 Vcc 电源电压2 Vss 接地3 Vee LCD 驱动电压4 RES 复位信号5 E1 使能信号6 E2 使能信号7 R/W 读写控制信号8 A0 显示数据.指令数据控制信号 9~16 DB0~DB7数据线 17 LED+ 背光电源 18 LED - 背光电源5-2.时序及时序图:项目 符号 条件最小值 最大值 单位 E 使能信号周期 Tc 1000 — E 高电屏保持时间 Twh 450 — E 低电屏保持时间 Twl450 — E 上升时间 Tr — 25 E 下降时间 Tf — 25R/W 建立时间 Tasu140 —R/W 保持时间 Tah10 — 数据上升时间 Tdsu 200 — 数据延时时间 Td — 320 写数据保持时间 Tdhw 20 — 读数据保持时间 TdhrVdd=5V ±5%Vss=0V Ta=25℃ 10 —ns时序图如下:(a) 写时序图第 8 页 共 20页(b)读时序图5-3. 电源连接图5-4. 电路图解(图解参见Fig.5-4)LCD 模块需逻辑电压(Vdd )和LCD 驱动电压(Vee )注释: 当信号线直接连到C-MOS电路且没有内部上拉或下拉电阻时,有必要隔离外部干扰来保护信号线。

单片机实验板功能模块说明说明

AT89S51单片机实验板各个功能模块连线使用说明上图为整个试验板的供电接口,可以外接5V直流电源或者通过电脑USB接口供电;上图为74HC164串行显示电路,串行显示电路只要用到单片机的TXD,RXD接口,可以节省大量I/O;硬件连接为:164的CLK连接到单片机的TXD口,DATA连接到单片机的RXD 口,使用时只要将相应的插针用跳线帽连接上即可。

上图为单片机串口预留插针,位于实验板左下角,由于实验板上的串行显示控制电路只有一位数码管在实际应用中时不够的,一般会有一个独立的8为串口显示板,这样将显示板的VCC、GND、TXD、RXD对应插到预留插针上就可以使用了。

上图为动态数码管显示电路,在使用该部分电路时将左边的拨码开关全部拨到ON位置(右边拨码开关最好全部拨下来),电路硬件连接为:A……H笔端依次接到单片机的P00……P07口,S1……S8 八个数码管的位选依次接到P20……P27口,最右边数码管为第一位。

注意在做动态显示等实验时要将液晶电路部分的PSB跳线帽去掉,因为PSB与P24口相连。

上图右部为8*8点阵电路,使用该模块时将点阵正上方的八位拨码开关全部拨到ON位置(右边拨码开关全部拨下来),电路硬件连接为:点阵的行控制依次连接到P20……P27口,列控制依次连接到P00……P07口。

上图为8路LED电路,电路的硬件连接为:P20……P27分别对应控制LED8……LED1,低电平时LED灯亮,使用时只要将相应的插针用跳线帽连接上即可。

注意在做流水灯等实验时要将液晶电路部分的PSB跳线帽去掉,因为PSB与P24口相连。

上图为DS1302时钟电路,使用该部分电路时显示方式只能在LCD和动态数码管两种方式中任选其一,两者不能同时使用。

电路的硬件连接为:DS1302的RST I/O SCLK分别与单片机的P37、P36、P35相连,使用时只要将相应的插针用跳线帽连接上即可。

上图上半部分为I2C存储电路(A T24C04),电路硬件连接为:AT24C04的CLK 、DA TA分别连接到P20 、P21口,使用时只要将相应的插针用跳线帽连接上即可。

32路模拟量采集模块说明书

5 模块应用技术

5.1 MODBUS协议解释

请参考《V2.4单相三相LEDLCD仪表通用说明书》中关于MODBUS的介绍。 可以用我们提供的测试工具查看采集的数据。如下图。 测试接入-12V和+12V。

根据不同的量程选择合适的小数个数,可以获得更高的分辨率。如下图,是燃料电池用的 32 路 2V 量程的模 块。用户的测试电压在-0.5V-+2V之间,要求精度误差 2mV 以内。因此选择 4 位小数,实际测量数据非常准 确,误差能控制在 0.2mV 以内。

硬件信息寄存器信息表

字地址

字节 位置

描述

参数说明

属性

12H

16 位 保留

R

13H

16 位 保留

R

14H

16 位 采样位数

16:16 位,18:18 位,24:24 位

R

15H

16 位 AD 参考电压 VREF 值,单位:mV。例如:256=0.256V

R

16H………1DH

共8 个单元,16 个BYTES。是型号信息,例如: R

68H

第 9 路模拟量输入值

78H

第 25 路模拟量输入值

69H

第 10 路模拟量输入值 79H

第 26 路模拟量输入值

6AH

第 11 路模拟量输入值 7AH

第 27 路模拟量输入值

6BH

第 12 路模拟量输入值 7BH

第 28 路模拟量输入值

6CH

第 13 路模拟量输入值 7CH

第 29 路模拟量输入值

1 概述

1.1:KHAQ-PLC32-V,16位、18位单端输入,32路电压采集模块

此模块的最大应用领域是串联电池组单体电压测量,常用规格如下:

MC9S12DP512核心板使用说明

100 99 98 96 95 94 93 92 91 90 89 88 87 82 81 80 表 3 JA4 的管脚定义

PM5 PJ6 PJ7 PS7 PS6 PS5 PS4 PS3 PS2 PS1 PS0 PM6 PM7 PAD15 PAD07 PAD14

管脚编号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22

2

对应单片机管脚的名称 GND PP1 PP2 PP3 PP4 PP5 PP6 PP7 PK7 PM0 PM1 PM2 PM3 PM4

网店地址

15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30

网店地址

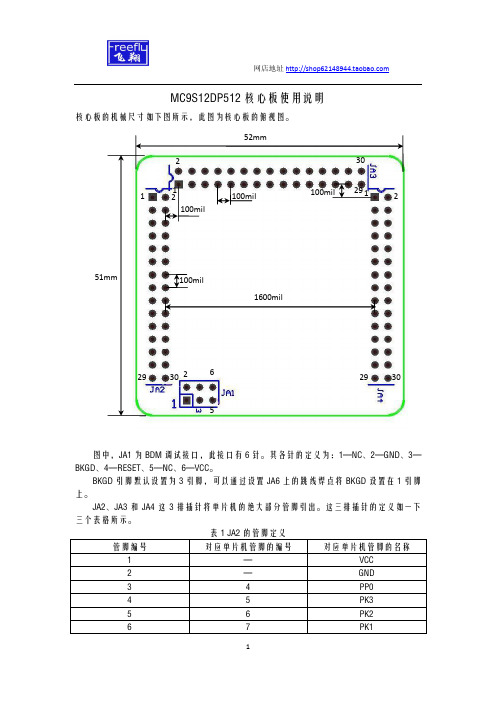

MC9S12DP512 核心板使用说明

核心板的机械尺寸如下图所示,此图为核心板的俯视图。 52mm 2 1 2 100il

2

51mm

100mil 1600mil

29

30 2

6

29

30

5

图中,JA1 为 BDM 调试接口,此接口有 6 针。其各针的定义为:1—NC、2—GND、3— BKGD、4—RESET、5—NC、6—VCC。 BKGD 引脚默认设置为 3 引脚,可以通过设置 JA6 上的跳线焊点将 BKGD 设置在 1 引脚 上。 JA2、JA3 和 JA4 这 3 排插针将单片机的绝大部分管脚引出。这三排插针的定义如一下 三个表格所示。 表 1 JA2 的管脚定义 管脚编号 1 2 3 4 5 6 对应单片机管脚的编号 — — 4 5 6 7

网店地址

23 24 25 26 27 28 29 30

56 55 54 53 52 51 50 49

PLC硬件模块资料

PACsystems RX3i系统及软件

21

七、模拟量输入模块IC695ALG600

IC695ALG600是通用型模拟量 输入模块,提供8路通用输入通 道和两路冷段补偿输入通道。每 路通道均能够接电压、电流、热 电偶、热电阻输入。

2020/7/3

PACsystems RX3i系统及软件

22

模拟量输入模块IC695ALG600

在数字量输入模块前面的拨动开关可 以模拟开关量输入设备的运行,开关处 于ON位置时导致在输入状态表(%I)

中产生一个逻辑1 。

PACsystems RX3i系统及软件

16

五、IC694MDL754开关量输出模块

PAC3i 控制器的开关量输出模块共有 16种。

可输入电压有120VAC,120/240VAC, 124/240 VAC,125VDC, 12/24 VDC, 5/24VDC(TTL)六种。

在模块后背板上有两个DIP开关用于选择输 出故障后的模式:强制关或者保持故障前的状 态。

标签上的蓝条表明MDL754是低电压模块。

2020/7/3

PACsystems RX3i系统及软件

18

IC694MDL754输出模块接图

2020/7/3

PACsystems RX3i系统及软件

19

六、IC695ETM001以太网接口模块

20

IC695ETM001以太网接口模块

2020/7/3

发光二极管含义: Ethernet OK:指示灯指示该模块是否能执

行正常工作。有开、闪烁两种状态,闪 烁次数表示两位错误代码。 LAN OK: 指示灯指示是否连接以太网络。 闪烁状态表明以太网接口正在直接从以 太网接收数据或发送数据。 Log Empty:亮状态表示正常运行状态,如 果有事件被记录,指示灯呈“熄灭”状 态。 两个以太网速度指示灯(100Mbps) 指示网络 数据传输速度(10 (熄灭) 或者 100Mb/sec (亮))。

X系列操作说明书模板

X系列操作说明书模板预览说明:预览图片所展示的格式为文档的源格式展示,下载源文件没有水印,内容可编辑和复制欢迎阅读异步LED显示屏控制卡客户端应用软件X show图文编辑软件用户手册目录1.简述 (4)2.简单介绍一下各种控制卡 (4)3.软件操作流程 (5)3.1 启动软件 (5)3.2 连接控制卡 (5)3.2.1 串口通讯 (6)3.2.2 网口通讯.............................................................. 错误!未定义书签。

3.2.3 gprs或互联网通讯 (6)3.3 添加屏幕 (7)3.4 添加节目 (7)3.5 添加区域 (8)3.5.1 如何添加图文区域 (8)3.5.2 添加字幕 (9)3.5.3 添加炫动字区域 (9)3.5.4 添加时钟区域 (9)3.5.5 添加表盘区域 (10)3.5.6 添加计时区域 (10)3.5.7 添加温度 (10)3.6 预览及发送 (10)3.7 串口和网口控制操作 (11)3.7.1 校时 (11)3.7.2 亮度调节 (11)3.7.3 请求型号 (11)3.7.4 定时开关机 (12)3.8 集群管理 (12)3.8.1 网口集群 (12)3.8.2 gprs集群 (12)3.9 工程保存和如何导入 (12)3.9.1 常规内容保存和导入 (12)3.9.2 特殊内容保存和导入方式 (12)4. 常规问题处理办法 (13)4.1 如何修改STR极性和数据极性 (13)4.2 如何自定义新的扫描方式 (13)4.3 X卡各种常见现象 (17)1.简述X show图文编辑软件是针对公司所有X系列产品的软件,具体的型号如下:X2,XU4,X4S,X4,X6,X8,X16,X32八种控制卡的软件。

X show图文编辑软件采取节目管理方式,您可以将您需要显示的内容编辑为若干个节目,节目可以在您指定的时间段内播放,也可以播放一定的时间长度。

1.3inch LCD HAT 用户手册说明书

产品概述1.3inch LCD HAT 是微雪电子专为树莓派开发的1.3寸LCD显示屏模块,分辨率为240 * 240,LCD带有内部控制器,使用SPI接口通信,与树莓派ZERO大小一致,已封装好基本函数,可以实现图片旋转、画点、线、圆、矩形,显示英文字符,显示BMP图片。

提供树莓派BCM2835库,WiringPi库,以及python例程。

产品参数工作电压: 3.3V通信接口:SPI屏幕类型:TFT控制芯片:ST7789VM分辨率:240(H)RGB x 240(V)显示尺寸:23.4(H)x 23.4(V)mm像素大小:0.0975(H)x 0.0975(V)mm产品尺寸65 x 30.2(mm)1接口说明2硬件说明1.LCD及其控制器本款LCD使用的内置控制器为ST7789VM,是一款240 x RGB x 320像素的LCD控制器,而本LCD本身的像素为240(H)RGB x 240(V),同时由于初始化控制可以初始化为横屏和竖屏两种,因此LCD的内部RAM并未完全使用。

查看数据手册可以得知该控制器支持12位,16位以及18位每像素的输入颜色格式,即RGB444,RGB565,RGB666三种颜色格式,本屏幕使用RGB565格式的颜色格式,这也是常用的RGB格式。

对于大部分的LCD控制器而言,都可以配置控制器的通信方式,通常都有8080并行接口、三线SPI、四线SPI等通信方式。

此LCD使用四线SPI通信接口,这样可以大大的节省GPIO 口,同时通信速度也会比较快。

2.通信协议从上的得知使用的是4线SPI通信,查阅数据手册可以得到如下的通信时序图,以传输RGB556为例:注:与传统的SPI协议不同的地方是:由于是只需要显示,故而将从机发往主机的数据线进行了隐藏,该表格详见Datasheet Page 105。

3RESX为复位,模块上电时拉低,通常情况下置1;CSX为从机片选,仅当CS为低电平时,芯片才会被使能。

PIC单片机实时时钟和日历

RTCC SFR 汇总

Bit 31/23/15/7 — Bit 30/22/14/6 — Bit 29/21/13/5 — Bit 28/20/12/4 — CAL<7:0> — — — — — — RTCOE Bit 27/19/11/3 — Bit 26/18/10/2 — Bit 25/17/9/1 Bit 24/16/8/0

AMASK<3:0>

写入时会将 RTCTIME 中的选定位清零,读取时获得的值未定义 写入时会将 RTCTIME 中的选定位置 1,读取时获得的值未定义 写入时会将 RTCTIME 中的选定位取反,读取时获得的值未定义 YEAR10<3:0> MONTH10<3:0> DAY10<3:0> — — — YEAR01<3:0> MONTH01<3:0> DAY01<3:0> WDAY01<3:0>

DS61125D_CN 第 29-2 页

初稿

© 2010 Microchip Technology Inc.

第 29 章 实时时钟和日历

图 29-1: RTCC 框图

来自 SOSC 振荡器的 32.768 kHz 输入

RTCC 预分频器 0.5s RTCC 定时器 闹钟 事件 RTCVAL 年, 月, 日 星期 小时, 分钟, 秒 比较器 月, 日 比较寄存器 (带掩码) 重复计数器 ALRMVAL 星期 小时, 分钟, 秒

第 29 章 实时时钟和日历

目录

本章包括下列主题: 29.1 29.2 29.3 29.4 29.5 29.6 29.7 29.8 29.9 29.10 29.11 29.12 简介 ......................................................................................................................... 29-2 状态和控制寄存器 .................................................................................................... 29-4 工作模式 ................................................................................................................ 29-24 闹钟 ....................................................................................................................... 29-35 中断 ....................................................................................................................... 29-40 节能和调试模式下的操作 ....................................................................................... 29-42 各种复位的影响 ..................................................................................................... 29-43 使用 RTCC 模块的外设 .......................................................................................... 29-43 I/O 引脚控制........................................................................................................... 29-44 设计技巧 ................................................................................................................ 29-45 相关应用笔记 ......................................................................................................... 29-47 版本历史 ................................................................................................................ 29-48

GE Fanuc RX3i PACSystem IC695MDL765 智能数字输出模块说明书

Rx3i PacSystem919-535-3180*******************GE Fanuc IC695MDL765/automation/ge-fanuc/rx3i-pacsystem/IC695MDL765Smart Digital Output ModulePACSystems* RX3iIC695MDL765GFK-2591A Digital Output Module with Diagnostics – 16-ChannelAugust 2011* Indicates a trademark of GE Intelligent Platforms, Inc. and/or its affiliates. All other trademarks are the property of their respective owners.The 24/125 volt DC 2A Smart Digital Output module, IC695MDL765, provides 16 discrete outputs in two isolated groups of 8 outputs. Each group of 8 outputs is referenced to an isolated common, providing group-to-group isolation. The module uses 24 VDC or 125 VDCThe outputs are positive logic or sourcing-type outputs; they switch the loads on the positive side of the power supply, and supply current to the load. The outputs can switch user loads over the ranges of +18 V to +30 VDC or 105 V to 132 VDC and can source a maximum current of 2 Amps per point. Power for the loads must be provided by the user.The field status LEDs (S1 and S2) indicate whether the external +24 VDC or +125 VDC power supply is present and above the minimum level, whether faults are present, and whether the terminal block is locked into place. The module also logs an Addition of Terminal Block or Loss of Terminal Block message to the I/O fault table to report the terminal block status.Each point has electronic short circuit protection (ESCP) that shuts down an output and generates an individual fault if capacitive or incandescent surge currentexceeds 10 amps, or if it exceeds 2 amps for more than 10 ms. In addition to output driver faults being sent back to the RX3i controller, the module provides a loss of field side power fault, ESCP point failure within a group and field terminal block ON/OFF status.Features of the Smart Digital Output module include:▪ Output Pulse Test Capability ▪ Output Hold Last State or Default Additional Diagnostics include:▪ Over temperature ▪ Failed Switch Detection▪ Overload Detection and Shutdown ▪No-load DetectionThis module can be used with either a Box-style (IC694TBB032) or Spring-style (IC694TBS032) front Terminal Block. The Terminal Block is ordered separately. The red bands on the label show that the MDL765 is a high-voltage module. This module can be installed in any I/O slot in an RX3i system.Electronic Short-circuit ProtectionEach output point provides protection against overcurrent, short circuit and overtemperature. The fault is present until the condition that caused the fault is removed and the faulted point is turned off. Each output point provides transient voltage protection to clamp high voltages at or below 136VDC.GFK-2591ARefer to the PACSystems RX3i System Manual, GFK-2314, for product standards, and general operating specifications, and installation requirements. Manuals can be downloaded from /support.GFK-2591AMDL765 Thermal Derating CurveWith output currents of 1 amp per channel, no temperature derating is required, and all channels can operate within the entire Surrounding Air temperature range. With output currents of 2 amps per channel, the number of active channels must be reduced as temperature increases, according to the following derating curve.Surrounding Air Temperature, °C20 30 40 50 60Maximum Number of Active Channels10 1555GFK-2591AMDL765 Field WiringField wiring connections to the module are made to the removable terminal assembly, as described in the RX3i System Manual , GFK-2314.Field Wiring Terminals Field WiringCircuit OperationTwo Eight-Circuit DC Sourcing GroupsThe DC sourcing circuit groups have all output devices connected to the negative side of the power supply (DC-). The sourcing circuit outputs provide power to the output devices. For sourcing circuit outputs, an ON condition is logic 1 and an OFF condition is logic 0.K FieldOutput DeviceModuleGFK-2591ALED Operation1 – 16Channel StatusOK S1S2The 16 green/amber channel status LEDs on the module indicate the ON/OFF status of points 1 through 16. The Module OK LED indicates module status. The field status LEDs (S1 and S2) indicate whether the external +24 VDC or +125 VDC power supply is present and is above the minimum level, whether faults are present, and whether the terminal block is locked into place. The module also logs an Addition of Terminal Block or Loss of Terminal Block message to the I/O fault table to report the Terminal Block status.Note: The OK, S1 and S2 LEDs blink green in unison when the module is in firmware update mode.GFK-2591AInput and Output Data FormatsOutput Value DataThe application uses these bits (one bit per output), beginning at the configured Outputs Reference Address to write the commanded output values to the module.Output Command Value Feedback DataThe module uses these bits (one bit per output), beginning at the configured Output Command Reference Address to report the output feedback data values.Channel Diagnostic and Status DataThe module can be configured to report channel diagnostic and status data to the CPU. The CPU stores this data at the module’s configured Diagnostic Reference Address. Use of this feature is optional.The data for each channel occupies two words whether the channel is used or not.Note:At least two sweeps must occur to clear the diagnostic bits: one scan to send the %Q data to the module and one scan to return the %I data to the CPU. Because module processing isasynchronous to the controller sweep, more than two sweeps may be needed to clear the bits,depending on the sweep rate and the point at which the data is made available to the module.Module Status DataThe module can be configured to return two words of module status data to the CPU. The CPU stores this data in the module’s 32-bit configured Module Status reference area.GFK-2591APulse Test Command Output DataThe module uses these bits (one bit per output), beginning at the configured Pulse Command OutputReference Address to command an on-demand pulse test. To command an on-demand pulse test, the Pulse Test Enable parameter for the channel must be set to Enabled – Manual.DiagnosticsThe module always performs its standard diagnostic checks, plus one optional output diagnostic. Themodule returns current circuit diagnostics to %I bits for all circuits.For Overtemperature, Short Circuit, Failed Switch and Overload, the user must de-assert the output %Q bit to clear the error. The corresponding %I bit will be turned off within at least two CPU sweeps.Over Temperature DiagnosticsEach circuit has a built-in thermal sensor. If the internal temperature exceeds the allowable limit the module logs an OVERTEMPERATURE fault in the I/O fault table and turns off the circuit to protect its internalelectronics. The temperature must decrease below the allowable limit before the output can turn on again.This diagnostic is always performed for all the outputs.Short circuit DiagnosticsOutput circuits are protected by a short circuit threshold sensor at the switching device. If the instantaneous current on an output exceeds 10 amps the module turns the output off within microseconds. The module will try to restart the load; if two additional attempts are unsuccessful, the output circuit is forced off, and the module logs a SHORT CIRCUIT fault in the I/O fault table. To restore normal operation to output the cause of the current surge must be removed, then the diagnostic must be cleared from the CPU.This diagnostic detects shorts across the load only. Also, systems with floating power supplies do not detect shorts of I/O points to ground because there is no return current path. Systems with power suppliesgrounded on the negative side detect grounded output points as Short Circuit.Partial (high resistance) shorts may not draw enough current to be detected by the Pulse Test.Failed Switch DiagnosticsThe module automatically monitors all circuits for several types of faults, which may be reported as Failed Switch diagnostics.Failed Switch is reported if the circuit’s switch state is not the same as its commanded state. The module logs a FAILED SWITCH fault in the I/O fault table identifying the failed circuit. The logic state of the circuit is set to OFF.When an output fault occurs, the actual condition of the output switch is not known. If the output switch has failed shorted (or closed), current flow is not interrupted when the module forces the output state OFF. Action external to the module must be taken to remedy the problem. The FAILED SWITCH fault can alert personnel or cause program logic to be activated, possibly shutting off power to the module, I/O section, or process.GFK-2591ANo L oad DiagnosticsReporting for this diagnostic can be enabled or disabled for individual outputs.By default, outputs are configured to report No-Load conditions. In this configuration, energizing the output activates a no-load current level. If the load does not continuously draw 50mA from the output circuit, the module logs a NO LOAD fault in the I/O fault table. This diagnostic should be not be used for circuits on which very small loads (small relays or indicating lamps) will draw less than 50 mA. To clear the No-Load error, a load of at least 85mA must be applied to the output.Overload DiagnosticIn addition to the protection provided by the module’s built-in Short Circuit detection, Overload Shutdown provides further protection for output loads, field wiring, and switching devices. If a load exceeds 2 amps DC continuously for 10ms, the module turns the output off and logs an OVERLOAD fault in the I/O fault table. Under-Voltage DetectionThe field power supply on each group includes support for detecting supply voltages below the minimum voltage for the selected voltage standard. The fault can be disabled by group. Detecting the fault has no impact on the state of the output control.Output Pulse TestThe Output Pulse Test is an optional diagnostic feature that exercises the output points to confirm they can be switched to a known state.The pulse test attempts to switch the output from its Normal State to its Default State. For a load with a Normal State of ON, the source output is pulsed OFF. For a load with a Normal State of OFF, the source output is pulsed on. A fault is logged in the I/O fault table if a failure is detected in the output point.Pulse Testing should remain enabled if the module has loads that hold one state for long periods of time, unless any load(s) are sensitive to pulses or interruptions of up to 16ms. It should be disabled if the module’s loads will normally change state as the program executes. These will report faults during normal operation, and do not need to be pulsed.Pulse Test Selections: Pulse test frequencyOutput Default State / Output Normal StateOn Demand Pulse TestTo use this feature, the channel’s Pulse Test Enable parameter must be set to Enabled-Manual. Tocommand a pulse test, set the Pulse Test Command bit for the channel(s) to be pulse tested.The module performs one or more pulse tests for each channel selected. Since this will take many sweeps, you should keep the Pulse Test Command bit set until the Pulse Test Complete bit is set for that channel in the Channel Diagnostic and Status Data.The module keeps the Pulse Test Complete bit set as long as the Pulse Test Command bit is set. If the pulse test fails, the Pulse Test Failed bit is set at the same time as the Pulse Test Complete bit. One output scan with the Pulse Test Command bit cleared clears the Pulse Test Complete status bit and Pulse Test Failure diagnostic bit.Automatic Pulse TestTo use this feature, set the channel’s Pulse Test Enable parameter to Enabled-Auto. The Output Pulse Test occurs at a frequency selected in the Hardware Configuration, with no intervention from the CPU. The pulse test execution is based on the Time of Day clock set in the CPU, and the frequency is relative to 12:00am.For example, a frequency of 12 hours will result in a pulse test run at 12:00am and 12:00pm.If the pulse test fails, the Pulse Test Failed bit is set.GFK-2591A ConfigurationGFK-2591AGFK-2591AImportant Product Information for this ReleaseUpgradesIf a module exhibits the symptoms described in “Problems Resolved by Release 1.01” contact GE Intelligent Platforms for corrective actions. The primary firmware upgrade can not be installed on a module that has boot firmware version 1.00.UL Class 1 Division 2 & ATEX Zone 2 Hazardous Area Warnings1.EQUIPMENT LABELED WITH REFERENCE TO CLASS I, GROUPS A, B, C, D, DIV. 2 HAZARDOUSAREAS IS SUITABLE FOR USE IN CLASS I, DIVISION 2, GROUPS A, B, C, D OR NON–HAZARDOUS LOCATIONS ONLY.2. WARNING – EXPLOSION HAZARD – SUBSTITUTION OF COMPONENTS MAY IMPAIR SUITABILITYFOR CLASS I, DIVISION 2 & ATEX ZONE 2.3. WARNING – EXPLOSION HAZARD – DO NOT DISCONNECT EQUIPMENT UNLESS POWER HASBEEN SWITCHED OFF OR THE AREA IS KNOWN TO BE NON–HAZARDOUS.ATEX Zone 2 Hazardous Area RequirementsIn order to maintain compliance with the ATEX Directive, an RX3i system located in a Zone 2 area (Category3) must be installed within a protective enclosure meeting the criteria detailed below:∙IP54 or greater, and∙Mechanical strength to withstand an impact energy of 3.5 Joules。

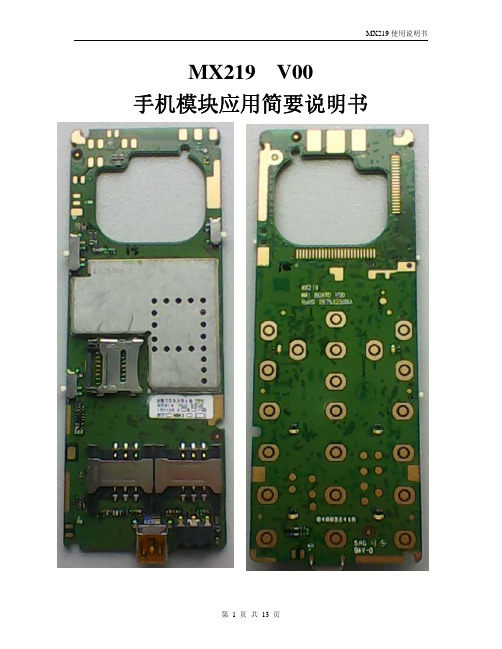

MX219 V00使用说明书

MX219V00手机模块应用简要说明书一、概述 (3)二、原理框图 (3)三、功能接口简介 (4)3.1音频接口 (4)3.2LCD接口 (5)3.3摄像头接口 (7)3.4IO接口 (8)3.4.1充电功能 (9)3.4.2耳机功能 (9)3.4.3FM收音机天线 (9)3.4.4USB接口 (9)3.6马达接口 (10)3.7电池接口 (10)3.8扩展功能 (10)3.8.1手电筒功能 (10)3.8.2LOCK/SOS功能 (11)3.9GSM天线 (12)3.10蓝牙天线 (12)3.11FM外放功能 (13)四、模块版本信息 (13)五、结构尺寸 (13)一、概述本说明书简要介绍MX219V00手机模块各接口定义及快速手机开发。

本说明书仅用于MX219V00版。

三、功能接口简介3.1音频接口MX219主板上共有三组音频接口,位置及描述如下:Speaker接口位置:Receriver接口位置:MIC接口位置:麦克风焊接时,一定要注意正负极3.2LCD接口MX219主板提供一组并行LCD接口,支持共阳并联背光。

LCD1.77/2.0/2.3寸接口定义:管脚号管脚名Dir.描述备注1Y2TP信号不使用时悬空2X1TP信号不使用时悬空3Y1TP信号不使用时悬空4X2TP信号不使用时悬空5VCC_2.8V LCD电源6VCCIO_1.8V LCD IO电源7/CS LCD片选信号8/RS LCD命令与数据信号9/WR LCD写信号10/RD LCD读信号11DB0LCD数据D012DB1LCD数据D113DB2LCD数据D214DB3LCD数据D315DB4LCD数据D416DB5LCD数据D517DB6LCD数据D618DB7LCD数据D719/REST LCD复位信号20LED_A LCD背光LED正极21LED_K1LCD背光LED负极22LED_K2LCD背光LED负极23LED_K3LCD背光LED负极24LED_K4LCD背光LED负极25GND地3.3摄像头接口MX219提供一组并行摄像头接口。

MICROCHIP PIC32MX5XX 6XX 7XX 数据手册

PIC32MX5XX/6XX/7XX数据手册具有USB、CAN和以太网的32位闪存单片机 2010 Microchip Technology Inc.初稿DS61156B_CNDS61156B_CN 第2页初稿2010 Microchip Technology Inc.提供本文档的中文版本仅为了便于理解。

请勿忽视文档中包含的英文部分,因为其中提供了有关Microchip 产品性能和使用情况的有用信息。

Microchip Technology Inc.及其分公司和相关公司、各级主管与员工及事务代理机构对译文中可能存在的任何差错不承担任何责任。

建议参考Microchip Technology Inc.的英文原版文档。

本出版物中所述的器件应用信息及其他类似内容仅为您提供便利,它们可能由更新之信息所替代。

确保应用符合技术规范,是您自身应负的责任。

Microchip 对这些信息不作任何明示或暗示、书面或口头、法定或其他形式的声明或担保,包括但不限于针对其使用情况、质量、性能、适销性或特定用途的适用性的声明或担保。

Microchip 对因这些信息及使用这些信息而引起的后果不承担任何责任。

如果将Microchip 器件用于生命维持和/或生命安全应用,一切风险由买方自负。

买方同意在由此引发任何一切伤害、索赔、诉讼或费用时,会维护和保障Microchip 免于承担法律责任,并加以赔偿。

在Microchip 知识产权保护下,不得暗中或以其他方式转让任何许可证。

商标Microchip 的名称和徽标组合、Microchip 徽标、dsPIC 、K EE L OQ 、K EE L OQ 徽标、MPLAB 、PIC 、PICmicro 、PICSTART 、PIC 32徽标、rfPIC 和 UNI/O 均为Microchip Technology Inc .在美国和其他国家或地区的注册商标。

FilterLab 、Hampshire 、HI-TECH C 、Linear ActiveThermistor 、MXDEV 、MXLAB 、SEEVAL 和The Embedded Control Solutions Company 均为Microchip Technology Inc .在美国的注册商标。

PIC32MX Trace Interface 连接指南说明书

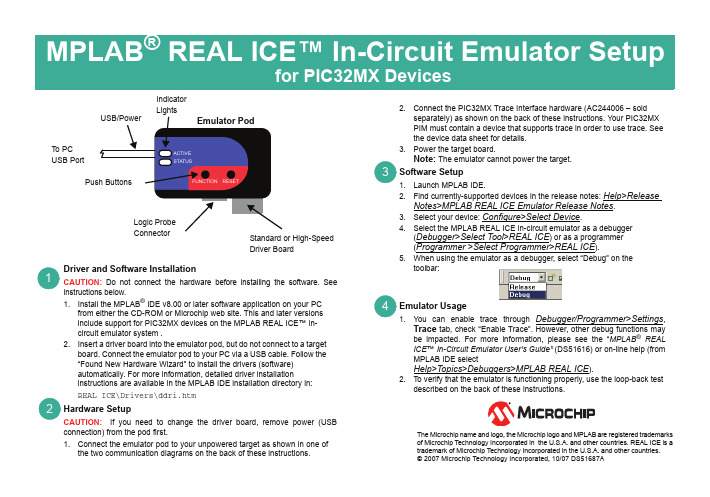

2.Connect the PIC32MX Trace Interface hardware (AC244006 – soldseparately) as shown on the back of these instructions. Your PIC32MX PIM must contain a device that supports trace in order to use trace. See the device data sheet for details.3.Power the target board.Note: The emulator cannot power the target.Software Setupunch MPLAB IDE.2.Find currently-supported devices in the release notes: Help>ReleaseNotes>MPLAB REAL ICE Emulator Release Notes .3.Select your device: Configure>Select Device .4.Select the MPLAB REAL ICE in-circuit emulator as a debugger(Debugger>Select Tool>REAL ICE ) or as a programmer (Programmer >Select Programmer>REAL ICE ).5.When using the emulator as a debugger, select “Debug” on thetoolbar:Emulator Usage1.You can enable trace through Debugger/Programmer>Settings ,Trace tab, check “Enable Trace”. However, other debug functions may be impacted. For more information, please see the “MPLAB ® REAL ICE ™ In-Circuit Emulator User’s Guide” (DS51616) or on-line help (from MPLAB IDE selectHelp>Topics>Debuggers>MPLAB REAL ICE ).2.To verify that the emulator is functioning properly, use the loop-back testdescribed on the back of these instructions.34Driver and Software InstallationCAUTION: Do not connect the hardware before installing the software. See instructions below.1.Install the MPLAB ® IDE v8.00 or later software application on your PCfrom either the CD-ROM or Microchip web site. This and later versions include support for PIC32MX devices on the MPLAB REAL ICE™ in-circuit emulator system .2.Insert a driver board into the emulator pod, but do not connect to a targetboard. Connect the emulator pod to your PC via a USB cable. Follow the “Found New Hardware Wizard” to install the drivers (software) automatically. For more information, detailed driver installationinstructions are available in the MPLAB IDE installation directory in:REAL ICE\Drivers\ddri.htmHardware SetupCAUTION: If you need to change the driver board, remove power (USB connection) from the pod first .1.Connect the emulator pod to your unpowered target as shown in one ofthe two communication diagrams on the back of these instructions.21USB/PowerEmulator PodLogic Probe ConnectorIndicatorLightsPush ButtonsStandard or High-Speed Driver BoardTo PC USB PortThe Microchip name and logo, the Microchip logo and MPLAB are registered trademarks of Microchip T echnology Incorporated in the U.S.A. and other countries. REAL ICE is a trademark of Microchip T echnology Incorporated in the U.S.A. and other countries.© 2007 Microchip Technology Incorporated, 10/07 DS51687AEmulator PodTarget BoardPIC32MX PIMStandard Driver BoardStandard CommunicationEmulator PodTarget BoardHigh-Speed Driver BoardPIC32MX PIMHigh-Speed Receiver BoardHigh-Speed CommunicationExternal Triggersor TraceExternal Triggersor TraceDebug/Programmer InterfaceDebug/Programmer InterfacePerformance PakP I C 32trace portPIMPIC32MX Trace InterfaceTarget BoardEmulatorPodStandard Driver Board Loop-Back Test B oardModular Cable Logic Probe Connector Driver Board Slot Loop-Back TestT o verify that the emulator is function-ing properly, use the loop-back test board. Disconnect the emulator fromthe target and PC, plug in the stan-dard driver board and loop-back test board as shown, reconnect the emu-lator to the PC, and select the emula-tor as in “Software Setup”, Step 3, on the front of these instructions toautomatically run the loop-back test.Trace Adaptertrace cableEmulator Podlogic probe connectorDebug/Programmer InterfaceOR。

JPEG 压缩模块设备说明说明书

JPEG Camera-2MJPEG Compression 2M Camera ModuleGeneral DescriptionThe JPEG compression module performs as a video camera or a JPEG compressed still camera and can be attached to a wireless or PDA host. Users can send out a snapshot command from the host in order to capture a full resolution single-frame still picture. The picture is then compressed by the JPEG engine and transferred to the host.Block DiagramVGA Image SensorVCC TxD RxD GNDFeatures. Low-cost, & low-powered solution for high resolution image capture. Built-in down-sampling, clamping and windowing circuits for 1600*1200/1280*960/1024*768/800*600/VGA/QVQAF/160x120 image resolutions. RS-232: 115.2K bps for transferring JPEG still pictures or 160x120 preview @8bpp with 0.75~6 fps. JPEG CODEC with variable quality settings for different resolutionsSystem ConfigurationCamera SensorsDSP Serial BridgeThe DSP Serial Bridge is a controller chip that can transfer image data from CameraChips to external device. The DSP takes 8-bit YCbCr 422 progressive video data from an CameraChip. The camera interface synchronizes with input video data and performs down sampling, clamping and windowing functions with desired resolution, as well as color conversion that is requested by the user through serial bus host commands.The JPEG CODEC with variable quality settings can achieve higher compression ratio & better image quality for various image resolutions.Program MemoryA serial type program memory is built-in for JPEG RS-232 Camera, which provides user-friendly commands to interface external control units.Pin DescriptionVCC Power 5VDCTxD Data TransmitRxD Data ReceiveGND Power GroundLens : CL4022IR (f3.6mm F/No 2.2) with IR Cut filterGeneral Description:1.Small in size(32*32MM).low cost and low powered(3.3V or 5.0V).2.Power on or reset,rs-232 baud rate is 115200.Serial Interface1.Single Byte Timing DiagramA Single byte RS-232 transmission consists of the start bit,8-bit contents and the stop bit .Astart bit is always 0,while a stop bit is always 1.LSB is sent out first and is right after the start bit.Command Set1.Reset56 00 26 00Receiving ACK command76 00 26 002. Snapshot56 0036 01 00Receiving ACK command76 00 36 003 Length of data of the Snapshot Picture56 00 34 01 00Receiving ACK command76 00 34 00 04 00 00 Byte0 Byte1Byte0 Byte1 is Length of data of the Snapshot PictureByte0 Length High ByteByte1 Length Low Byte4.Read Data of the Snapshot Picture56 00 32 0c 00 0a 00 00 Addr0 Addr1 00 00 Data0 Data 1 00 0aAddr0 Addr1 is start Addr of the packageData0 Data is package Sizepackage Size is a multiple of 8Receiving ACK command76 00 32 00 00 。

PIC32 Ethernet Starter Kit 产品介绍说明书

DM320004Your Electronic Engineering ResourceMicrochip - DM320004- PIC32 Ethernet Starter Kit Overview:The PIC32 Ethernet Starter Kit provides the easiest and lowest costmethod to experience 10/100 Ethernet development with PIC32.Combined with Microchip's free TCP/IP software, your project willbe running in no time. The PIC32 has an available CAN2.0bperipheral and USB host/device/OTG.The Ethernet Starter Kit has a compatible form factor and expansionconnector as other PIC32 Starter Kits.Kit Content:∙PIC32 Ethernet Starter Kit development board∙USB Mini-B to full-sized A cable – USB debug cable to debug and power the board∙USB Micro-B to full-sized A cable – PIC32 USB cable to communicate with the PIC32 USB port∙RJ-45 CAT5 Ethernet patch cable – Ethernet CAT5 cable to communicate with the PIC32 Ethernet port ∙ Software CDKey Features:∙PIC32MX795F512L 32-bit microcontroller.∙PIC32MX440F512H USB microcontroller for on-board debugging.∙Green power indicator LED.∙On-board crystal for precision microcontroller clocking (8 MHz).∙USB connectivity for on-board debugger communications.∙Orange debug indicator LED.∙Three push button switches for user-defined inputs.∙Three user-defined indicator LEDs.∙USB Type A receptacle connectivity for PIC32 host-based applications.∙HOST mode power jumper.∙RJ-45 Ethernet port.∙Ethernet 10/100 bus speed indicator LED.∙50 MHz Ethernet PHY oscillator.∙32 kHz oscillator (optional).∙USB Host and OTG power supply for powering PIC32 USB applications.Your Electronic Engineering ResourceOrdering Information: Products:Part NumberManufacturerFarnell P/NNewark P/N DM320004 Microchip 177805951R8564Associated Products:Part NumberManufacturerDescription Support DeviceFarnell P/NNewark P/NPIC32MX795F512L-80I/PF MicrochipMCU, 32BIT,512K FLASH, USB, 100TQFPPIC32MX795F512L1778491 53R0338TC1262-2.5VDB MicrochipVoltageRegulatorTC1262NA69K0481MCP1253-33X50I/MS MicrochipDC/DCChargePumpConverter IC MCP12531332067 03H5060DP83848CVV Microchip10/100ETHERNETPHY , SMD,LQFP48DP838481286816 79K6187Similar Products:Part NumberManufacturerDescriptionSupport DeviceFarnell P/NNewark P/NDM320001 Microchip PIC32MX STARTERKIT PIC32 1523317 71M0037DM320002 Microchip PIC32 I/O ExpansionBoard PIC321621784 03P1607 DM320003 MicrochipBOARD, DEMO, USBOTG, PIC32 PIC32 1621787 03P1608 DM320003-2 Microchip KIT, STARTER, USB,PIC32 PIC321778060 51R8563 DM330011 Microchip KIT, STARTER, MPLABFOR DSPICPIC321621788NAYour Electronic Engineering ResourceMA320002 Microchip KIT, PIC32 USB PLUGIN MODULEPIC32155860188M9291PIC-P32MX Olimex KIT, DEV,PIC32MX340F512BOARDPIC32170153125R4926MA320001 MicrochipPIC32MX360F512L PLUG-IN MODULEPIC32 1523316 73M8723 AC320002 MicrochipDevelopment Tools &Eval/Demo BoardsPIC32 1621785 07P8858 Document List: Datasheets:Part Number DescriptionSizePIC32MX795F512L Datasheet 2.08MBTC1262 TC1262 Datasheet 463KBMCP1253MCP1252/53 Datasheet 440KBApplication Notes:File NameSizeAN1108 - Microchip TCP/IP Stack with BSD Socket API for PIC32MX 430KBAN1109 - SNMP Agent using BSD Socket API for PIC32MX 682KBAN1111 - FTP Server using BSD Socket API for the PIC32MX 417KBAN1140 - USB Embedded Host Stack 467KBAN1141 - USB Embedded Host Stack Programmer?s Guide 543KBAN1142 - USB Mass Storage Class on an Embedded Host 360KBAN1143 - Generic Client Driver for a USB Embedded Host 263KBAN833 - Microchip TCP/IP Stack Application Note 430KBHardware & Software:File NameSizePIC32 Ethernet Starter Kit Schematics & Gerbers 425 KBPIC32 TCPIP BSD Stack Installer 4862 KBHelp File for 128/196/256 bit AES Software for PIC32 117 KBDM320004。