PCA9539

PCA9539中文资料

元器件交易网BUS TRANSACTIONSWriting to the port registersData is transmitted to the PCA9539 by sending the device address and setting the least significant bit to a logic 0 (see Figure 5 for device address). The command byte is sent after the address and determines which register will receive the data following the command byte.The eight registers within the PCA9539 are configured to operateas four register pairs. The four pairs are Input Ports, Output Ports, Polarity Inversion Ports, and Configuration Ports. After sending data to one register, the next data byte will be sent to the other register in the pair (see Figures 6 and 7). For example, if the first byte is sent to Output Port (register 3), then the next byte will be stored in Output Port 0 (register 2). There is no limitation on the number of data bytes sent in one write transmission. In this way, each 8-bit register may be updated independently of the other registers.Reading the port registersIn order to read data from the PCA9539, the bus master must first send the PCA9539 address with the least significant bit set to a logic 0 (see Figure 5 for device address). The command byte is sent after the address and determines which register will be accessed.After a restart, the device address is sent again but this time, the least significant bit is set to a logic 1. Data from the register defined by the command byte will then be sent by the PCA9539 (see Figures 8 , 9, and 10). Data is clocked into the register on the falling edge of the acknowledge clock pulse. After the first byte is read, additional bytes may be read but the data will now reflect the information in the other register in the pair. For example, if you read Input Port 1, then the next byte read would be Input Port 0. There is no limitation on the number of data bytes received in one read transmission but the final byte received, the bus master must not acknowledge the data.Interrupt OutputThe open-drain interrupt output is activated when one of the port pins change state and the pin is configured as an input. The interrupt is deactivated when the input returns to its previous state or the input port register is read (see Figure 9). A pin configured as an output cannot cause an interrupt. Since each 8-bit port is read independently, the interrupt caused by Port 0 will not be cleared by a read of Port 1 or the other way around.Note that changing an I/O from an output to an input may cause a false interrupt to occur if the state of the pin does not match the contents of the Input Port register.SO24:plastic small outline package; 24 leads; body width 7.5 mm SOT137-1TSSOP24:plastic thin shrink small outline package; 24 leads; body width 4.4 mm SOT355-1HVQFN24:plastic thermal enhanced very thin quad flat package; no leads; 24 terminals;body 4 x 4 x 0.85 mm SOT616-1Philips Semiconductors Product data sheetPCA9539 16-bit I2C and SMBus, low power I/O port with interruptDefinitionsShort-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.DisclaimersLife support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status ‘Production’), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.Contact informationFor additional information please visit.Fax: +31 40 27 24825For sales offices addresses send e-mail to:© Koninklijke Philips Electronics N.V. 2004All rights reserved. Printed in U.S.A.Date of release: 09-04Document order number:9397 750 14048元器件交易网。

PCA9633中文资料

Software programmable LED Group and three Sub Call I2C addresses allow all or defined groups of PCA9633 devices to respond to a common I2C address, allowing for example, all red LEDs to be turned on or off at the same time or marquee chasing effect, thus minimizing I2C-bus commands.

I Software Reset feature (SWRST Call) allows the device to be reset through the I2C-bus

元器件交易网

PCA9633

4-bit Fm+ I2C-bus LED driver

Rev. 03 — 20 December 2006

Product data sheet

ห้องสมุดไป่ตู้

1. General description

The PCA9633 is an I2C-bus controlled 4-bit LED driver optimized for Red/Green/Blue/Amber (RGBA) color mixing applications. Each LED output has its own 8-bit resolution (256 steps) fixed frequency Individual PWM controller that operates at 97 kHz with a duty cycle that is adjustable from 0 % to 99.6 % to allow the LED to be set to a specific brightness value. A fifth 8-bit resolution (256 steps) Group PWM controller has both a fixed frequency of 190 Hz and an adjustable frequency between 24 Hz to once every 10.73 seconds with a duty cycle that is adjustable from 0 % to 99.6 % that is used to either dim or blink all LEDs with the same value.

NXP_PCA9539PW 技术规格书

INPUT/ OUTPUT PORTS

LP FILTER

IO1_0 IO1_1 IO1_2 IO1_3 IO1_4 IO1_5 IO1_6 IO1_7

IO0_0 IO0_1 IO0_2 IO0_3 IO0_4 IO0_5 IO0_6 IO0_7 VDD

INT

Remark: All I/Os are set to inputs at reset. Fig 1. Block diagram of PCA9539; PCA9539R

The PCA9539; PCA9539R is identical to the PCA9555 except for the removal of the internal I/O pull-up resistor which greatly reduces power consumption when the I/Os are held LOW, replacement of A2 with RESET and a different address range.

002aad722

PCA9539_PCA9539R_4

Product data sheet

Rev. 04 — 19 May 2008

© NXP B.V. 2008. All rights reserved.

3 of 32

NXP Semiconductors

PCA9539; PCA9539R

16-bit I2C-bus and SMBus low power I/O port with interrupt and reset

3. Ordering information

Table 1. Ordering information

Motorola 3.5 kHz 产品说明书

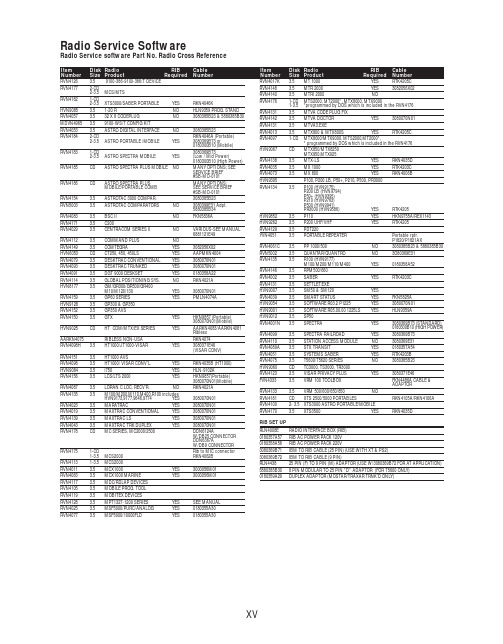

RVN4126 3.59100-386-9100-386/T DEVICERVN41772-CD2-3.5MCS/MTSRVN41821-CD2-3.5XTS3000/SABER PORTABLE YES RKN4046KHVN9085 3.51-20 R NO HLN9359 PROG. STAND RVN4057 3.532 X 8 CODEPLUG NO3080385B23 & 5880385B30 MDVN4965 3.59100-WS/T CONFIG KITRVN4053 3.5ASTRO DIGITAL INTERFACE NO3080385B23RVN41842-CD RKN4046A (Portable) 2-3.5ASTRO PORTABLE /MOBILE YES3080369B73 or0180300B10 (Mobile) RVN41831-CD3080369B732-3.5ASTRO SPECTRA MOBILE YES(Low / Mid Power)0180300B10 (High Power) RVN4185CD ASTRO SPECTRA PLUS MOBILE NO MANY OPTIONS; SEESERVICE BRIEF#SB-MO-0101RVN4186CD ASTRO SPECTRA PLUS MANY OPTIONS;MOBILE/PORTABLE COMB SEE SERVICE BRIEF#SB-MO-0101RVN4154 3.5ASTROTAC 3000 COMPAR.3080385B23RVN5003 3.5ASTROTAC COMPARATORS NO3080399E31 Adpt.5880385B34RVN4083 3.5BSC II NO FKN5836ARVN4171 3.5C200RVN4029 3.5CENTRACOM SERIES II NO VARIOUS-SEE MANUAL6881121E49RVN4112 3.5COMMAND PLUS NORVN4149 3.5COMTEGRA YES3082056X02HVN6053CD CT250, 450, 450LS YES AAPMKN4004RVN4079 3.5DESKTRAC CONVENTIONAL YES3080070N01RVN4093 3.5DESKTRAC TRUNKED YES3080070N01RVN4091 3.5DGT 9000 DESKSET YES0180358A22RVN4114 3.5GLOBAL POSITIONING SYS.NO RKN4021AHVN8177 3.5GM/GR300/GR500/GR400M10/M120/130YES3080070N01RVN4159 3.5GP60 SERIES YES PMLN4074AHVN9128 3.5GP300 & GP350RVN4152 3.5GP350 AVSRVN4150 3.5GTX YES HKN9857 (Portable)3080070N01(Mobile) HVN9025CD HT CDM/MTX/EX SERIES YES AARKN4083/AARKN4081RiblessAARKN4075RIBLESS NON-USA RKN4074RVN4098H 3.5HT1000/JT1000-VISAR YES3080371E46(VISAR CONV)RVN4151 3.5HT1000 AVSRVN4098 3.5HT1000/ VISAR CONV’L.YES RKN4035B (HT1000) HVN9084 3.5i750YES HLN-9102ARVN4156 3.5LCS/LTS 2000YES HKN9857(Portable)3080070N01(Mobile) RVN4087 3.5LORAN C LOC. RECV’R.NO RKN4021ARVN4135 3.5M100/M200,M110,M400,R100 includesHVN9173,9177,9646,9774YES3080070N01RVN4023 3.5MARATRAC YES3080070N01RVN4019 3.5MAXTRAC CONVENTIONAL YES3080070N01RVN4139 3.5MAXTRAC LS YES3080070N01RVN4043 3.5MAXTRAC TRK DUPLEX YES3080070N01RVN4178CD MC SERIES, MC2000/2500DDN6124AW/DB25 CONNECTORDDN6367AW/DB9 CONNECTOR RVN41751-CD Rib to MIC connector 1-3.5MCS2000 RKN4062BRVN41131-3.5MCS2000RVN4011 3.5MCX1000YES3000056M01RVN4063 3.5MCX1000 MARINE YES3000056M01RVN4117 3.5MDC/RDLAP DEVICESRVN4105 3.5MOBILE PROG. TOOLRVN4119 3.5MOBITEX DEVICESRVN4128 3.5MPT1327-1200 SERIES YES SEE MANUALRVN4025 3.5MSF5000/PURC/ANALOG YES0180355A30RVN4077 3.5MSF5000/10000FLD YES0180355A30RVN4017K 3.5MT 1000YES RTK4205CRVN4148 3.5MTR 2000YES3082056X02RVN4140 3.5MTRI 2000NORVN41761-CD MTS2000, MT2000*, MTX8000, MTX90001-3.5*programmed by DOS which is included in the RVN4176RVN4131 3.5MTVA CODE PLUG FIXRVN4142 3.5MTVA DOCTOR YES3080070N01RVN4131 3.5MTVA3.EXERVN4013 3.5MTX800 & MTX800S YES RTK4205CRVN4097 1-CD MTX8000/MTX9000,MTS2000,MT2000*,* programmed by DOS which is included in the RVN4176HVN9067CD MTX850/MTX8250MTX950,MTX925RVN4138 3.5MTX-LS YES RKN4035DRVN4035 3.5MX 1000YES RTK4203CRVN4073 3.5MX 800YES RKN4006BHVN9395 P100, P200 LB, P50+, P210, P500, PR3000RVN4134 3.5P100 (HVN9175)P200 LB (HVN9794)P50+ (HVN9395)P210 (HVN9763)P500 (HVN9941)PR3000 (HVN9586)YES RTK4205HVN9852 3.5P110YES HKN9755A/REX1143 HVN9262 3.5P200 UHF/VHF YES RTK4205RVN4129 3.5PDT220YVN4051 3.5PORTABLE REPEATER Portable rptr.P1820/P1821AXRVN4061C 3.5PP 1000/500NO3080385B23 & 5880385B30 RVN5002 3.5QUANTAR/QUANTRO NO3O80369E31RVN4135 3.5R100 (HVN9177)M100/M200/M110/M400YES0180358A52RVN4146 3.5RPM500/660RVN4002 3.5SABER YES RTK4203CRVN4131 3.5SETTLET.EXEHVN9007 3.5SM50 & SM120YESRVN4039 3.5SMART STATUS YES FKN5825AHVN9054 3.5SOFTWARE R03.2 P1225YES3080070N01HVN9001 3.5SOFTWARE R05.00.00 1225LS YES HLN9359AHVN9012 3.5SP50RVN4001N 3.5SPECTRA YES3080369B73 (STANDARD)0180300B10 (HIGH POWER) RVN4099 3.5SPECTRA RAILROAD YES3080369B73RVN4110 3.5STATION ACCESS MODULE NO3080369E31RVN4089A 3.5STX TRANSIT YES0180357A54RVN4051 3.5SYSTEMS SABER YES RTK4203BRVN4075 3.5T5600/T5620 SERIES NO3080385B23HVN9060CD TC3000, TS3000, TR3000RVN4123 3.5VISAR PRIVACY PLUS YES3080371E46FVN4333 3.5VRM 100 TOOLBOX FKN4486A CABLE &ADAPTORRVN4133 3.5VRM 500/600/650/850NORVN4181CD XTS 2500/5000 PORTABLES RKN4105A/RKN4106A RVN41002- 3.5XTS3000 ASTRO PORTABLE/MOBILERVN4170 3.5XTS3500YES RKN4035DRIB SET UPRLN4008E RADIO INTERFACE BOX (RIB)0180357A57RIB AC POWER PACK 120V0180358A56RIB AC POWER PACK 220V3080369B71IBM TO RIB CABLE (25 PIN) (USE WITH XT & PS2)3080369B72IBM TO RIB CABLE (9 PIN)RLN443825 PIN (F) TO 9 PIN (M) ADAPTOR (USE W/3080369B72 FOR AT APPLICATION) 5880385B308 PIN MODULAR TO 25 PIN ”D” ADAPTOR (FOR T5600 ONLY)0180359A29DUPLEX ADAPTOR (MOSTAR/TRAXAR TRNK’D ONLY)Item Disk Radio RIB Cable Number Size Product Required Number Item Disk Radio RIB Cable Number Size Product Required NumberUtilizing your personal computer, Radio Service Software (RSS)/Customer Programming Software (CPS)/CustomerConfiguration Software (CCS) enables you to add or reprogram features/parameters as your requirements change. RSS/CPS/CCS is compatible with IBM XT, AT, PS/2 models 30, 50, 60 and 80.Requires 640K RAM. DOS 3.1 or later. Consult the RSS users guide for the computer configuration and DOS requirements. (ForHT1000, MT/MTS2000, MTX838/8000/9000, Visar and some newer products —IBM model 386, 4 MEG RAM and DOS 5.0 or higher are recommended.) A Radio Interface Box (RIB) may be required as well as the appropriate cables. The RIB and cables must be ordered separately.Licensing:A license is required before a software (RVN) order is placed. The software license is site specific (customer number and ultimate destination tag). All sites/locations must purchase their own software.Be sure to place subsequent orders using the original customer number and ship-to-tag or other licensed sites; ordering software without a licensed customer number and ultimate tag may result in unnecessary delays. To obtain a no charge license agreement kit, order RPX4719. To place an order in the U.S. call 1-800-422-4210. Outside the U.S., FAX 847-576-3023.Subscription Program:The purchase of Radio ServiceSoftware/Customer Programming/Customer ConfigurationSoftware (RVN & HVN kits) entitles the buyer/subscriber to three years of free upgrades. At the end of these three years, the sub-scriber must purchase the same Radio Service Software kit to receive an additional three years of free upgrades. If the sub-scriber does not elect to purchase the same Radio Service Software kit, no upgrades will be sent. Annually a subscription status report is mailed to inform subscribers of the RSS/CPS/CCS items on our database and their expiration dates.Notes:1)A subscription service is offered on “RVN”-Radio Service Software/Customer Programming/Customer Configuration Software kits only.2)“RVN” software must only be procured through Radio Products and Services Division (RPSD). Software not procured through the RPSD will not be recorded on the subscription database; upgrades will not be mailed.3)Upgrades are mailed to the original buyer (customer number & ultimate tag).4)SP software is available through the radio product groups.The Motorola General Radio Service Software Agreement is now available on Motorola Online. If you need assistance please feel free to submit a “Contact Us” or call 800-422-4210.SMART RIB SET UPRLN1015D SMART RIB0180302E27 AC POWER PACK 120V 2580373E86 AC POWER PACK 220V3080390B49SMARTRIB CABLE (9 PIN (F) TO 9 PIN (M) (USE WITH AT)3080390B48SMARTRIB CABLE (25 PIN (F) TO 9 PIN (M) (USE WITH XT)RLN4488ASMART RIB BATTERY PACKWIRELESS DATA GROUP PRODUTS SOFTWARERVN4126 3.59100-386/9100T DEVICES MDVN4965 3.59100-WS/T CONFIG’TN RVN41173.5MDC/RDLAP DEVICESPAGING PRODUCTS MANUALS6881011B54 3.5ADVISOR6881029B90 3.5ADVISOR ELITE 6881023B20 3.5ADVISOR GOLD 6881020B35 3.5ADVISOR PRO FLX 6881032B30 3.5BR8506881032B30 3.5LS3506881032B30 3.5LS5506881032B30 3.5LS7506881033B10 3.5LS9506881035B20 3.5MINITOR III8262947A15 3.5PAGEWRITER 20008262947A15 3.5PAGEWRITER 2000X 6881028B10 3.5TALKABOUT T3406881029B35 3.5TIMEPORT P7308262947A15 3.5TIMEPORT P930NLN3548BUNIVERSAL INTERFACE KITItem Disk Radio NumberSize Product。

EUD诊断程序操作手册

密级:公开文档编号:Study-201005214 第 1版分册名称:F5 EUD诊断程序操作手册第 1册/共 1册【F5 EUD诊断程序】【操作手册】成都信诺瑞得网络科技有限公司总页数正文附录生效日期:编制:审核:批准:1. 用串口线连接PC与设备,设置参数如下2. 设备加电启动,若终端没有出现启动信息,长按F5 液晶面板上的“√”重启设备3. 设备启动完成后进入系统启动选择菜单,选择启动“End User Diagnostics”进入诊断系统(PS:如果版本比较老的F5系统,EUD没有测试菜单,需要安装EUD(下载EUD安装程序,上传到F5,执行im安装)或者升级系统到9.4.7之后,自带新的EUD。

)4. 诊断系统启动完毕后出现功能选择菜单,选择需要测试的功能项即可。

在big ip v9 的新设备中我们选择进行全部测试(快速内存测试),选项是A5. 诊断程序开始后根据终端提示进行操作,根据提示按下F5液晶面板上的相应按钮同时观察状态灯是否正常6. 测试完毕后保存相关测试信息备查总体的测试统计,这种状态表示所有的测试都正常通过由于是没有激活的设备,所以不能生成eud.log(如生成此文件,目录是shared/log), 我们可以在EUD的菜单中选择D查看测试结果的详情,并复制出来保存。

测试结果详情Select a Menu Item #: DProduct: F5 Networks End User DiagnosticsBuild: build 12.6.0.431.0Build date: Fri Nov 20 16:23:46 PST 2009Platform: C103Platform 200: 200-0293-15 REV A*************** EUD_LOOP_TEST_START ************************* LCD Test Started at 05 23 2010 18:02:44 **********05 23 2010 18:02:44 Test Begin: LCD Test05 23 2010 18:02:44 Firmware version: ULM: h1.5, f0.18Is F5 Logo Ball Flashing..?(y/n) yLCD backlight toggling On-Off...press any key to startIs LCD backlight toggling On-Off..?(y/n) yV erify LCD contrast changes smoothly...press any key to start Did LCD contrast change smoothly? (y/n) yLCD keypad Test...press any key to startPress the [UP] key on the LCD Panel...[UP]Press the [LEFT] key on the LCD Panel...[LEFT]Press the [ENTER] key on the LCD Panel...[ENTER]Press the [RIGHT] key on the LCD Panel...[RIGHT]Press the [CANCEL] key on the LCD Panel...[CANCEL]Press the [DOWN] key on the LCD Panel...[DOWN]05 23 2010 18:04:2105 23 2010 18:04:21 Test Complete: LCD Test: PASSED********** LCD Test Ended at 05 23 2010 18:04:21 ********** ********** LED Test Started at 05 23 2010 18:04:25 ********** 05 23 2010 18:04:25 Test Begin: LED Test05 23 2010 18:04:25 Test Begin: Front Panel LED TestIs the Alarm LED Amber? (Y/N)yIs the Alarm LED Red? (Y/N)yIs the Alarm LED Off? (Y/N)yIs the Status LED Green? (Y/N)yIs the Status LED Amber? (Y/N)y05 23 2010 18:04:51 Test Complete: Front Panel LED Test: PASSED05 23 2010 18:04:56 Test Begin: Port LED TestAre the LEDs Steady Green? (Y/N)yAre the LEDs Blinking Green? (Y/N)yAre the LEDs Steady Amber? (Y/N)yAre the LEDs Blinking Amber? (Y/N)y05 23 2010 18:05:43 Test Complete: Port LED Test: PASSED05 23 2010 18:05:43 Test Complete: LED Test: PASSED********** LED Test Ended at 05 23 2010 18:05:43 ******************** System Report Started at 05 23 2010 18:05:56 **********05 23 2010 18:05:56 Test Begin: System Report05 23 2010 18:05:57 SYS Serial Num: f5-rtoh-phvv05 23 2010 18:05:57 200 Part Num: 200-0293-15 REV A05 23 2010 18:05:59 AOM Sys Info: Linux 2.6.23.1 mips05 23 2010 18:06:00 AOM MGMT MAC Addr: 00:01:D7:B2:A9:4005 23 2010 18:06:02 AOM CFE (nub): 1.5.1 Tue May 13 09:48:12 PDT 200805 23 2010 18:06:04 AOM CFE (boota): 1.5.1 Tue May 13 09:48:12 PDT 200805 23 2010 18:06:06 AOM CFE (bootb): 1.5.1 Tue May 13 09:48:07 PDT 200805 23 2010 18:06:13 AOM Kernel: 10.1.3.298.0 Tue Jul 7 11:58:59 PDT 200905 23 2010 18:06:20 AOM Recovery: 10.1.3.298.0 Tue Jul 7 11:58:59 PDT 2 00905 23 2010 18:06:26 Power Supply 1: POWER-ONE FNP300-1012S144 05 00001220 05 23 2010 18:06:28 Power Supply 2: Not Present05 23 2010 18:06:29 HOST Sys Info: Linux 2.6.9-prep-F5-11.x.x i686 GNU/Linux05 23 2010 18:06:29 BIOS V ersion: F5 Platform: MERCURY OBJ-0272-03 BIOS S 0.0 Date:04/24/200905 23 2010 18:06:29 CPLD V ersion: 0x1305 23 2010 18:06:30 LCD FW V ersion: ULM: h1.5, f0.1805 23 2010 18:06:37 SSL Version: CNPx-MC-SSL-MAIN-0.9905 23 2010 18:06:37 HOST MGMT MAC Addr: 00:01:D7:B2:A9:4105 23 2010 18:06:37 Physical CPU #: 105 23 2010 18:06:37 CPU Model Name: Intel(R) Core(TM)2 Duo CPU E6400 @ 2.13GHz05 23 2010 18:06:37 CPU stepping: 1305 23 2010 18:06:38 DIMM1 Part Number: D2-56CG107SQ8V-55505 23 2010 18:06:39 DIMM1 Serial Number: 017f3f8405 23 2010 18:06:40 DIMM2 Part Number: D2-56CG107SQ8V-55505 23 2010 18:06:40 DIMM2 Serial Number: 017f3f8305 23 2010 18:06:40 TOTAL MEMORY(MB): 409605 23 2010 18:06:40 DISK DRIVE HDA INFO: SILICONSYSTEMS INC 8GB05 23 2010 18:06:40 DISK DRIVE SDA INFO: Vendor: ATA Model: WDC WD3202ABYS-02B7A0 SN: WD-WCA T1E753126 Rev: 02.03B0305 23 2010 18:06:40 DISK DRIVE HDA SIZE: 8455 MB05 23 2010 18:06:41 DISK DRIVE SDA SIZE: 320.0 GB05 23 2010 18:06:41 Test Complete: System Report PASSED********** System Report Ended at 05 23 2010 18:06:41 ******************** Sensor Report Started at 05 23 2010 18:06:44 **********05 23 2010 18:06:44 Test Begin: Sensor Report05 23 2010 18:06:44 Test Begin: AOM Sensor Test05 23 2010 18:06:44 AOM ADM Temp (C) 3105 23 2010 18:06:44 CPU Temperature (C) 3105 23 2010 18:06:44 Air inlet Temp (C) 2805 23 2010 18:06:44 Sys Fan1 (rpm) 1125005 23 2010 18:06:44 Sys Fan2 (rpm) 1205305 23 2010 18:06:44 Sys Fan3 (rpm) 1205305 23 2010 18:06:44 Sys Fan4 (rpm) 1163705 23 2010 18:06:44 SIO__BA T (V) 3.0505 23 2010 18:06:44 +5V (V) 5.0805 23 2010 18:06:44 +12V (V) 12.1305 23 2010 18:06:44 VCCP (V) 1.2105 23 2010 18:06:44 5VSB (V) 4.9905 23 2010 18:06:44 VCC2.5_MCH (V) 2.5105 23 2010 18:06:44 VCC2.5 (V) 2.5105 23 2010 18:06:44 2.5VSB (V) 2.5105 23 2010 18:06:44 5836_1.25 (V) 1.2505 23 2010 18:06:44 VCC_ICH (V) 1.0405 23 2010 18:06:44 DVDD_1V (V) 1.0005 23 2010 18:06:44 VTT_DDR (V) 0.9105 23 2010 18:06:44 Power Supply1 GOOD05 23 2010 18:06:44 Power Supply2 Not Present 05 23 2010 18:06:44 Test Complete: AOM Sensor Test: PASSED05 23 2010 18:06:48 Test Begin: Host Sensor Test05 23 2010 18:06:48 Sys Fan1 (rpm) 1088705 23 2010 18:06:48 Sys Fan2 (rpm) 1163705 23 2010 18:06:48 Sys Fan3 (rpm) 1125005 23 2010 18:06:48 Sys Fan4 (rpm) 1125005 23 2010 18:06:48 CPU Temperature (C) 3405 23 2010 18:06:48 Air inlet Temperature (C) 2805 23 2010 18:06:48 SIO__BA T (V) 3.0305 23 2010 18:06:48 +5V (V) 5.0505 23 2010 18:06:48 +12V (V) 12.0605 23 2010 18:06:48 VCCP (V) 1.2005 23 2010 18:06:48 5VSB (V) 5.0205 23 2010 18:06:48 VCC2.5_MCH (V) 2.5005 23 2010 18:06:48 VCC2.5 (V) 2.5105 23 2010 18:06:48 2.5VSB (V) 2.5105 23 2010 18:06:48 5836_1.25 (V) 1.2505 23 2010 18:06:48 VCC_ICH (V) 1.0405 23 2010 18:06:48 DVDD_1V (V) 1.0005 23 2010 18:06:48 VTT_DDR (V) 0.9005 23 2010 18:06:48 Thermal Status Flag OFF05 23 2010 18:06:48 Thermal Status Log OFF05 23 2010 18:06:48 Test Complete: Host Sensor Test: PASSED05 23 2010 18:06:48 Test Complete: Sensor Report: PASSED********** Sensor Report Ended at 05 23 2010 18:06:48 ******************** SFP/XFP+ Report Started at 05 23 2010 18:06:51 **********05 23 2010 18:06:51 Test Begin: SFP/SFP+ Report05 23 2010 18:06:54 Port 2.1 SFP : Not Present05 23 2010 18:06:54 Port 2.2 SFP : Not Present05 23 2010 18:06:55 Test Complete: SFP/SFP+ Report: PASSED********** SFP/XFP+ Report Ended at 05 23 2010 18:06:55 ********** ********** I2C Test Started at 05 23 2010 18:06:58 **********05 23 2010 18:06:58 Test Begin: I2C Test05 23 2010 18:06:58 Test Begin: AOM I2C Test05 23 2010 18:06:58 Present: PCA953905 23 2010 18:06:58 Present: EEPROM05 23 2010 18:06:58 Present: CPLD05 23 2010 18:06:58 Present: ADM102605 23 2010 18:06:58 Present: ZM731605 23 2010 18:06:58 Present: PWRSPLY105 23 2010 18:06:58 Test Complete: AOM I2C Test: PASSED05 23 2010 18:07:02 Test Begin: Host I2C Test05 23 2010 18:07:02 Present: DDR2 SDRAM105 23 2010 18:07:02 Present: DDR2 SDRAM205 23 2010 18:07:02 Present: ICS95410105 23 2010 18:07:02 Present: EEPROM05 23 2010 18:07:02 Present: PCA954005 23 2010 18:07:02 Present: ADM102605 23 2010 18:07:02 Test Complete: Host I2C Test: PASSED05 23 2010 18:07:02 Test Complete: I2C Test: PASSED********** I2C Test Ended at 05 23 2010 18:07:02 ******************** PCI Test Started at 05 23 2010 18:07:05 **********05 23 2010 18:07:06 Test Begin: PCI Test05 23 2010 18:07:06 Test Begin: verify HOST PCI05 23 2010 18:07:06 HOST PCI devices found:00:00.0 Host bridge: Intel Corporation E7230/3000/3010 Memory Controller Hub (rev c0)00:01.0 PCI bridge: Intel Corporation E7230/3000/3010 PCI Express Root Port ( rev c0)00:03.0 PCI bridge: Intel Corporation 82975X/3010 PCI Express Root Port (revc0)00:1d.0 USB Controller: Intel Corporation 82801G (ICH7 Family) USB UHCI Contr oller #1 (rev 01)00:1d.1 USB Controller: Intel Corporation 82801G (ICH7 Family) USB UHCI Contr oller #2 (rev 01)00:1d.2 USB Controller: Intel Corporation 82801G (ICH7 Family) USB UHCI Contr oller #3 (rev 01)00:1d.7 USB Controller: Intel Corporation 82801G (ICH7 Family) USB2 EHCI Cont roller (rev 01)00:1e.0 PCI bridge: Intel Corporation 82801 PCI Bridge (rev e1)00:1f.0 ISA bridge: Intel Corporation 82801GB/GR (ICH7 Family) LPC Interface Bridge (rev 01)00:1f.1 IDE interface: Intel Corporation 82801G (ICH7 Family) IDE Controller (rev 01)00:1f.2 SATA controller: Intel Corporation 82801GR/GH (ICH7 Family) SATA AHCI Controller (rev 01)00:1f.3 SMBus: Intel Corporation 82801G (ICH7 Family) SMBus Controller (rev 0 1)01:01.0 Ethernet controller: Broadcom Corporation NetXtreme BCM5788 Gigabit E thernet (rev 03)01:02.0 Network controller: Broadcom Corporation BCM5695 12-port + HiGig Mult i-Layer Gigabit Ethernet Switch (rev 11)02:00.0 Network and computing encryption device: Cavium Networks Nitrox XL NP X (rev 01)03:00.0 PCI bridge: Broadcom EPB PCI-Express to PCI-X Bridge (rev b5)04:04.0 Ethernet controller: Broadcom Corporation NetXtreme BCM5715S Gigabit Ethernet (rev a3)04:04.1 Ethernet controller: Broadcom Corporation NetXtreme BCM5715S Gigabit Ethernet (rev a3)05 23 2010 18:07:06 Test Complete: verify HOST PCI: PASSED05 23 2010 18:07:06 Test Begin: verify PCIe devices05 23 2010 18:07:06 Checking PCIe Bridge 0:3.0: Device 2:0.0: Cavium Nitrox:05 23 2010 18:07:06 Device 2:0.0: Cavium Nitrox: passed05 23 2010 18:07:06 Checking PCIe Bridge 0:1.0: Device 3:0.0: Broadcom BCM571 5S PCIe Bridge:05 23 2010 18:07:06 Device 3:0.0: Broadcom BCM5715S PCIe Bridge: passed05 23 2010 18:07:06 Test Complete: verify PCIe devices: PASSED05 23 2010 18:07:06 Test Complete: PCI Test: PASSED********** PCI Test Ended at 05 23 2010 18:07:06 ******************** Quick System RAM Test Started at 05 23 2010 18:07:10 **********05 23 2010 18:07:10 Test Begin: Quick System RAM Test05 23 2010 18:07:14 Test Begin: AOM Mem Test05 23 2010 18:07:14 Total memory detected: 60 MB05 23 2010 18:07:14 Using 39 MB granularity (65%)05 23 2010 18:15:21 AOM Mem Test: PASSED05 23 2010 18:15:21 Test Begin: Host Mem Test05 23 2010 18:15:21 Total memory detected: 4054 MB05 23 2010 18:15:21 Using 1024 MB granularity05 23 2010 18:15:21 Starting 3 memory test processes...05 23 2010 18:16:08 Host Mem Test: PASSED05 23 2010 18:16:08 Time to run: 538 seconds05 23 2010 18:16:08 Test Complete: AOM MEM Test PASSED05 23 2010 18:16:08 Test Complete: HOST MEM Test PASSED05 23 2010 18:16:08 Test Complete: Quick System RAM Test: PASSED********** Quick System RAM Test Ended at 05 23 2010 18:16:08 ******************** ECC Status Test Started at 05 23 2010 18:16:12 **********05 23 2010 18:16:12 Test Begin: ECC Status Test05 23 2010 18:16:12 Test Complete: ECC Status Test: PASSED********** ECC Status Test Ended at 05 23 2010 18:16:12 ******************** Internal Packet Path Test Started at 05 23 2010 18:16:15 **********05 23 2010 18:16:15 Test Begin: Internal Packet Path Test05 23 2010 18:16:23 Switch to CPU Port ETH1 Packet Test05 23 2010 18:16:25 Test Complete: Switch to CPU Port ETH1 Packet Test: PASSED 05 23 2010 18:16:26 Switch to CPU Port ETH2 Packet Test05 23 2010 18:16:29 Test Complete: Switch to CPU Port ETH2 Packet Test: PASSED 05 23 2010 18:16:30 CPU Port ETH1 to Switch Packet Test05 23 2010 18:16:32 Test Complete: CPU Port ETH1 to Switch Packet Test: PASSED 05 23 2010 18:16:33 CPU Port ETH2 to Switch Packet Test05 23 2010 18:16:35 Test Complete: CPU Port ETH2 to Switch Packet Test: PASSED 05 23 2010 18:16:37 Test Complete: Internal Packet Path Test: PASSED********** Internal Packet Path Test Ended at 05 23 2010 18:16:37 ******************** Internal Loopback Test Started at 05 23 2010 18:16:40 **********05 23 2010 18:16:40 Test Begin: Internal Loopback Test05 23 2010 18:16:48 Port 1.1 PHY Loopback Test05 23 2010 18:16:53 Test Complete: Port 1.1 PHY Loopback: PASSED05 23 2010 18:16:54 Port 1.2 PHY Loopback Test05 23 2010 18:16:58 Test Complete: Port 1.2 PHY Loopback: PASSED05 23 2010 18:16:59 Port 1.3 PHY Loopback Test05 23 2010 18:17:03 Test Complete: Port 1.3 PHY Loopback: PASSED05 23 2010 18:17:04 Port 1.4 PHY Loopback Test05 23 2010 18:17:08 Test Complete: Port 1.4 PHY Loopback: PASSED05 23 2010 18:17:09 Port 1.5 PHY Loopback Test05 23 2010 18:17:14 Test Complete: Port 1.5 PHY Loopback: PASSED05 23 2010 18:17:15 Port 1.6 PHY Loopback Test05 23 2010 18:17:19 Test Complete: Port 1.6 PHY Loopback: PASSED05 23 2010 18:17:20 Port 1.7 PHY Loopback Test05 23 2010 18:17:24 Test Complete: Port 1.7 PHY Loopback: PASSED05 23 2010 18:17:25 Port 1.8 PHY Loopback Test05 23 2010 18:17:30 Test Complete: Port 1.8 PHY Loopback: PASSED05 23 2010 18:17:31 Port 2.1 MAC Loopback Test05 23 2010 18:17:35 Test Complete: Port 2.1 MAC Loopback: PASSED05 23 2010 18:17:36 Port 2.2 MAC Loopback05 23 2010 18:17:40 Test Complete: Port 2.2 MAC Loopback: PASSED05 23 2010 18:17:42 Test Complete: Internal Loopback Test: PASSED********** Internal Loopback Test Ended at 05 23 2010 18:17:42 ********** ********** SSL Test Started at 05 23 2010 18:17:45 **********05 23 2010 18:17:47 Test Begin: SSL Test05 23 2010 18:17:47 Executing SSL test on device 0...Soft Reset Test Result: PASSEDRegister Read/Write Test Result: PASSEDGet BIST Reg V al Test Result: PASSEDRandom Numbers Test Result: PASSEDRC4 Crypto Test Result: PASSEDHMAC Crypto Test Result: PASSED3DES Crypto Test Result: PASSEDAES Crypto Test Result: PASSEDMod Ex Crypto Test Result: PASSEDKey Memory and DMA Test Result: PASSEDGet Unit Enable Reg V al Test Result: PASSEDGet Exec Units Avail Test Result: PASSEDRequest Unit Test (16) Result: PASSEDRequest Unit Test (17) Result: PASSEDRequest Unit Test (18) Result: PASSEDRequest Unit Test (19) Result: PASSEDGet Chip CSR: PASSEDGet PCI CSR: PASSED05 23 2010 18:18:01 Test Complete: SSL Test: PASSED********** SSL Test Ended at 05 23 2010 18:18:02 ******************** SMART Test Started at 05 23 2010 18:18:05 **********05 23 2010 18:18:05 Test Begin: SMART Test05 23 2010 18:18:05 Gathering SMART data for /dev/sda...05 23 2010 18:18:05 /dev/sda SMART overall-health self-assessment test: passe d05 23 2010 18:18:05 Test Complete: SMART Test: PASSED********** SMART Test Ended at 05 23 2010 18:18:05 ******************** Power System Test Started at 05 23 2010 18:18:09 **********05 23 2010 18:18:09 Test Begin: Power System Test05 23 2010 18:18:08 Test Begin: DPM POL Status Test05 23 2010 18:18:08 Found ZM7316 running software version A0405 23 2010 18:18:08 DPM Status: OK05 23 2010 18:18:09 ZPOL0 Status: OK05 23 2010 18:18:09 ZPOL0 ID: OK05 23 2010 18:18:09 ZPOL0 V oltage Setpoint: OK05 23 2010 18:18:09 ZPOL1 Status: OK05 23 2010 18:18:09 ZPOL1 ID: OK05 23 2010 18:18:09 ZPOL1 V oltage Setpoint: OK05 23 2010 18:18:09 ZPOL2 Status: OK05 23 2010 18:18:09 ZPOL2 ID: OK05 23 2010 18:18:09 ZPOL2 V oltage Setpoint: OK05 23 2010 18:18:09 ZPOL3 Status: OK05 23 2010 18:18:09 ZPOL3 ID: OK05 23 2010 18:18:09 ZPOL3 V oltage Setpoint: OK05 23 2010 18:18:09 ZPOL4 Status: OK05 23 2010 18:18:09 ZPOL4 ID: OK05 23 2010 18:18:09 ZPOL4 V oltage Setpoint: OK05 23 2010 18:18:09 ZPOL5 Status: OK05 23 2010 18:18:09 ZPOL5 ID: OK05 23 2010 18:18:09 ZPOL5 V oltage Setpoint: OK05 23 2010 18:18:09 ZPOL6 Status: OK05 23 2010 18:18:09 ZPOL6 ID: OK05 23 2010 18:18:09 ZPOL6 V oltage Setpoint: OK05 23 2010 18:18:09 ZPOL7 Status: OK05 23 2010 18:18:09 ZPOL7 ID: OK05 23 2010 18:18:09 ZPOL7 V oltage Setpoint: OK05 23 2010 18:18:09 ZPOL8 Status: OK05 23 2010 18:18:09 ZPOL8 ID: OK05 23 2010 18:18:09 ZPOL9 Status: OK05 23 2010 18:18:09 ZPOL9 ID: OK05 23 2010 18:18:09 Test Complete: DPM POL Status Test: PASSED05 23 2010 18:18:13 Test Complete: Power System Test: PASSED********** Power System Test Ended at 05 23 2010 18:18:13 ***************************** TEST SUMMARY *****************05 23 2010 18:06:41 Test Complete: 1 System Report PASSED05 23 2010 18:06:48 Test Complete: 2 Sensor Report: PASSED05 23 2010 18:06:55 Test Complete: 3 SFP/SFP+ Report: PASSED05 23 2010 18:04:21 Test Complete: 4 LCD Test: PASSED05 23 2010 18:05:43 Test Complete: 5 LED Test: PASSED05 23 2010 18:07:02 Test Complete: 6 I2C Test: PASSED05 23 2010 18:07:06 Test Complete: 7 PCI Test: PASSED05 23 2010 18:16:08 Test Complete: 8 Quick System RAM Test: PASSED05 23 2010 18:16:12 Test Complete: 10 ECC Status Test: PASSEDBooting 'BIG-IP 9.4.8 Build 355.0 - drive sda.1'kernel (hd1,1)/boot/1/vmlinuz ro root=UUID=c6250798-5f1f-4cba-a55e-1601068f40feconsole=tty0 console=ttyS0,19200 panic=1 platform=Mercury quiet Red Hat nash version 3.5.13 startingMounting /proc filesystem * Creating block devices * Scanning logical volumes * vgscan -- reading all physical volumes (this may take a while...) *vgscan -- "/etc/lvmtab" and "/etc/lvmtab.d" successfully created *vgscan -- WARNING: This program does not do a VGDA backup of your volume group* * Activating logical volumes * vgchange -- no volume groups found **************************************************************************** Creating root device* keys to select which entry is highlighted.Mounting root filesystemt the selected OS, 'e' to edit theINIT: version 2.85 bootinging, 'a' to modify the kernel argumentsbefore booWelcome to BIG-IP 9.4.8 Build 355.0 .................Not forcing file system integrity check due to default setting.sda.1-root: clean, 20708/1544320 files, 77025/3086488 blocksconds. ...........shared: recovering journalshared: clean, 230/7815168 files, 256397/15627228 blockssda.1-config: recovering journalsda.1-config: clean, 130/1544320 files, 56998/3086487 blockssda.1-var: recovering journalTestsda.1-var: clean, 2599/9273344 files, 323804/18518928 blockssda.1-usr: recovering journalsda.1-usr: clean, 13587/1544320 files, 166555/3086487 blocks ing /lib/modules/2.4.21-9.4.8.355.0smp/kernel/drivers/net/lasthop.o INIT: Entering runlevel: 3uires User Interaction, Quick Ram Test) ...............................................n Not Required, Quick Ram Test)BIG-IP 9.4.8 Build 355.0 and 5 (User Interaction Not Required, Full Ram Test) Kernel 2.4.21-9.4.8.355.0smp on an i686。

学习笔记1-I2C架构篇

学习笔记1: Linux设备驱动程序之I2C 基础架构篇I2C (Inter-Integrated Circuit)总线是一种由PHILIPS 公司开发的两线式串行总线,用于连接微控制器及其外围设备。

I2C 总线最主要的优点是其简单性和有效性。

由于接口直接在组件之上,因此I2C 总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。

I2C 总线概述I2C 总线是由数据线SDA 和时钟SCL 构成的串行总线,可发送和接收数据,每个器件都有一个惟一的地址识别。

I2C 规程运用主/从双向通讯。

器件发送数据到总线上,则定义为发送器,器件接收数据则定义为接收器。

主器件和从器件都可以工作于接收和发送状态。

总线必须由主器件(通常为微控制器)控制,主器件产生串行时钟(SCL)控制总线的传输方向,并产生起始和停止条件。

SDA线上的数据状态仅在SCL 为低电平的期间才能改变,SCL 为高电平的期间,SDA状态的改变被用来表示起始和停止条件。

另外,I2C是一种多主机控制总线.它和USB总线不同,USB是基于master-slave机制,任何设备的通信必须由主机发起才可以.而 I2C 是基于multi master机制.一同总线上可允许多个master.I2C 总线在传送数据过程中共有三种类型信号,它们分别是:开始信号、结束信号和应答信号。

开始信号:SCL 为高电平时,SDA 由高电平向低电平跳变,开始传送数据。

结束信号:SCL 为低电平时,SDA 由低电平向高电平跳变,结束传送数据。

应答信号:接收数据的IC 在接收到8bit 数据后,向发送数据的IC 发出特定的低电平脉冲,表示已收到数据。

CPU 向受控单元发出一个信号后,等待受控单元发出一个应答信号,CPU 接收到应答信号后,根据实际情况作出是否继续传递信号的判断。

若未收到应答信号,由判断为受控单元出现故障。

Linux 的I2C 驱动架构Linux 中I2C 总线的驱动分为两个部分,总线驱动(BUS)和设备驱动(DEVICE)。

PCA9543资料

元器件交易网SO14:plastic small outline package; 14 leads; body width 3.9 mm SOT108-1TSSOP14:plastic thin shrink small outline package; 14 leads; body width 4.4 mm SOT402-1DefinitionsShort-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.DisclaimersLife support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status ‘Production’), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.Contact informationFor additional information please visit.Fax: +31 40 27 24825For sales offices addresses send e-mail to:© Koninklijke Philips Electronics N.V. 2004All rights reserved. Published in the U.S.A.Date of release: 10-04Document number:9397 750 14112。

PCA9533D

1.General descriptionThe PCA9533is a 4-bit I 2C-bus and SMBus I/O expander optimized for dimming LEDs in 256 discrete steps for Red/Green/Blue (RGB) color mixing and back light applications.The PCA9533 contains an internal oscillator with two user programmable blink rates and duty cycles coupled to the output PWM. The LED brightness is controlled by setting the blink rate high enough (>100Hz)that the blinking cannot be seen and then using the duty cycle to vary the amount of time the LED is on and thus the average current through the LED.The initial setup sequence programs the two blink rates/duty cycles for each individual PWM.From then on,only one command from the bus master is required to turn individual LEDs ON, OFF , BLINK RATE 1 or BLINK RATE 2. Based on the programmed frequency and duty cycle, BLINK RATE 1 and BLINK RATE 2 will cause the LEDs to appear at a different brightness or blink at periods up to 1.69second. The open-drain outputs directly drive the LEDs with maximum output sink current of 25mA per bit and 100mA per package.To blink LEDs at periods greater than 1.69second the bus master (MCU, MPU, DSP ,chip set, etc.) must send repeated commands to turn the LED on and off as is currently done when using normal I/O expanders like the NXP Semiconductors PCF8574 or PCA9554. Any bits not used for controlling the LEDs can be used for General Purpose parallel Input/Output (GPIO)expansion,which provides a simple solution when additional I/O is needed for ACPI power switches, sensors, push-buttons, alarm monitoring, fans,etc.The Power-On Reset (POR) initializes the registers to their default state, causing the bits to be set HIGH (LED off).Due to pin limitations, the PCA9533 is not featured with hardware address pins. The PCA9533/01 and the PCA9533/02 have different fixed I 2C-bus addresses allowing operation of both on the same bus.2.FeaturesI 4 LED drivers (on, off, flashing at a programmable rate)I Two selectable, fully programmable blink rates (frequency and duty cycle) between 0.591Hz and 152Hz (1.69second and 6.58milliseconds)I 256 brightness stepsI Input/outputs not used as LED drivers can be used as regular GPIOs I Internal oscillator requires no external components I I 2C-bus interface logic compatible with SMBusPCA95334-bit I 2C-bus LED dimmerRev. 03 — 27 April 2009Product data sheetI Internal power-on resetI Noise filter on SCL/SDA inputsI 4 open-drain outputs directly drive LEDs to 25mA I Edge rate control on outputs I No glitch on power-up I Supports hot insertion I Low standby currentI Operating power supply voltage range of 2.3V to 5.5V I 0Hz to 400kHz clock frequencyIESD protection exceeds 2000V HBM per JESD22-A114, 150V MM per JESD22-A115 and 1000V CDM per JESD22-C101I Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100mA I Packages offered: SO8, TSSOP8 (MSOP8)3.Ordering information3.1Ordering optionsTable 1.Ordering informationType numberPackage NameDescriptionVersion PCA9533D/01SO8plastic small outline package; 8leads;body width 3.9mmSOT96-1PCA9533D/02PCA9533DP/01TSSOP8plastic thin shrink small outline package; 8leads;body width 3mmSOT505-1PCA9533DP/02Table 2.Ordering optionsType number Topside mark Temperature range PCA9533D/01P9533/1T amb =−40°C to +85°C PCA9533D/02P9533/2T amb =−40°C to +85°C PCA9533DP/01P33/1T amb =−40°C to +85°C PCA9533DP/02P33/2T amb =−40°C to +85°C4.Block diagram5.Pinning information5.1Pinning5.2Pin descriptionRemark:Only one I/O shown for clarity.Fig 1.Block diagram of PCA9533002aae626I 2C-BUS CONTROLINPUT FILTERSPCA9533POWER-ON RESETSCL SDAV DDV SSLEDnOSCILLATORPRESCALER 1REGISTERPRESCALER 0REGISTER PWM1REGISTERPWM0REGISTER INPUT REGISTERLED SELECT (LSn)REGISTERBLINK0BLINK11Fig 2.Pin configuration for SO8Fig 3.Pin configuration for TSSOP8PCA9533D/01PCA9533D/02LED0V DD LED1SDA LED2SCL V SSLED3002aae62412346587LED0V DD LED1SDA LED2SCL V SSLED3002aae62512346587PCA9533DP/01PCA9533DP/02Table 3.Pin descriptionSymbol Pin Description LED01LED driver 0LED12LED driver 1LED23LED driver 2V SS 4supply ground LED35LED driver 36.Functional descriptionRefer to Figure 1 “Block diagram of PCA9533”.6.1Device addressFollowing a START condition, the bus master must output the address of the slave it is accessing. The address of the PCA9533/01 is shown in Figure 4 and the address of PCA9533/02 is shown in Figure 5.The last bit of the address byte defines the operation to be performed.When set to logic 1a read is selected, while a logic 0 selects a write operation.6.2Control registerFollowing the successful acknowledgement of the slave address,the bus master will send a byte to the PCA9533, which will be stored in the Control register.The lowest 3bits are used as a pointer to determine which register will be accessed.If the Auto-Increment (AI) flag is set, the three low order bits of the Control register are automatically incremented after a read or write. This allows the user to program theregisters sequentially.The contents of these bits will rollover to ‘000’after the last register is accessed.When Auto-Increment flag is set (AI =1) and a read sequence is initiated, the sequence must start by reading a register different from the INPUT register (B2B1B0≠000).Only the 3 least significant bits are affected by the AI flag. Unused bits must be programmed with zeroes.SCL 6serial clock line SDA 7serial data line V DD8supply voltageTable 3.Pin description …continuedSymbol Pin Description Fig 4.PCA9533/01 slave address Fig 5.PCA9533/02 slave address002aae627111R/Wslave address002aae6281111R/Wslave address Reset state: 00hFig 6.Control registerB0002aad744000AI 0B2B1register addressAuto-Incrementflag6.2.1Control register definition6.3Register descriptions6.3.1INPUT - Input registerThe INPUT register reflects the state of the device pins. Writes to this register will be acknowledged but will have no effect.Remark:The default value ‘X’is determined by the externally applied logic level (normally logic 1) when used for directly driving LED with pull-up to V DD .6.3.2PCS0 - Frequency Prescaler 0PSC0 is used to program the period of the PWM output.The period of BLINK0=(PSC0+1)/152.6.3.3PWM0 - Pulse Width Modulation 0The PWM0register determines the duty cycle of BLINK0.The outputs are LOW (LED on)when the count is less than the value in PWM0 and HIGH (LED off) when it is greater. If PWM0 is programmed with 00h, then the PWM0 output is always HIGH (LED off).The duty cycle of BLINK0=PWM0/256.Table 4.Register summaryB2B1B0Symbol Access Description 000INPUT read only input register 001PSC0read/write frequency prescaler 0010PWM0read/write PWM register 0011PSC1read/write frequency prescaler 1100PWM1read/write PWM register 111LS0read/writeLED selectorTable 5.INPUT - Input register descriptionBit 76543210Symbol ----LED3LED2LED1LED0DefaultXXXXTable 6.PSC0 - Frequency Prescaler 0 register descriptionBit 76543210Symbol PSC0[7]PSC0[6]PSC0[5]PSC0[4]PSC0[3]PSC0[2]PSC0[1]PSC0[0]DefaultTable 7.PWM0 - Pulse Width Modulation 0 register descriptionBit 76543210Symbol PWM0[7]PWM0[6]PWM0[5]PWM0[4]PWM0[3]PWM0[2]PWM0[1]PWM0[0]Default16.3.4PCS1 - Frequency Prescaler 1PSC1 is used to program the period of the PWM output.The period of BLINK1=(PSC1+1)/152.6.3.5PWM1 - Pulse Width Modulation 1The PWM1register determines the duty cycle of BLINK1.The outputs are LOW (LED on)when the count is less than the value in PWM1 and HIGH (LED off) when it is greater. If PWM1 is programmed with 00h, then the PWM1 output is always HIGH (LED off).The duty cycle of BLINK1=PWM1/256.6.3.6LS0 - LED selectorThe LSn LED selector register determines the source of the LED data.00=output is set high-impedance (LED off; default)01=output is set LOW (LED on)10=output blinks at PWM0 rate 11=output blinks at PWM1 rateTable 8.PSC1 - Frequency Prescaler 1 register descriptionBit 76543210Symbol PSC1[7]PSC1[6]PSC1[5]PSC1[4]PSC1[3]PSC1[2]PSC1[1]PSC1[0]DefaultTable 9.PWM1 - Pulse Width Modulation 1 register descriptionBit 76543210Symbol PWM1[7]PWM1[6]PWM1[5]PWM1[4]PWM1[3]PWM1[2]PWM1[1]PWM1[0]Default1Table 10.LS0 - LED selector register bit description Legend: * default value.Register Bit Value Description LS07:600*LED3 selected 5:400*LED2 selected 3:200*LED1 selected 1:000*LED0 selected6.4Pins used as GPIOsLEDn pins not used to control LEDs can be used as General Purpose I/Os (GPIOs).For use as input, set LEDn to high-impedance (00) and then read the pin state via the INPUT register.For use as output, connect external pull-up resistor to the pin and size it according to the DC recommended operating characteristics. LEDn output pin is HIGH when the output is programmed as high-impedance,and LOW when the output is programmed LOW through the ‘LED selector’ register. The output can be pulse-width controlled when PWM0 orPWM1 are used.6.5Power-on resetWhen power is applied to V DD, an internal Power-On Reset (POR) holds the PCA9533 ina reset condition until V DD has reached V POR.At that point,the reset condition is releasedand the PCA9533 registers are initialized to their default states, all the outputs in theOFF state. Thereafter, V DD must be lowered below 0.2V to reset the device.7.Characteristics of the I 2C-busThe I 2C-bus is for 2-way,2-line communication between different ICs or modules.The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must beconnected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.7.1Bit transferOne data bit is transferred during each clock pulse.The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals (see Figure 7).7.1.1START and STOP conditionsBoth data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOWtransition of the data line while the clock is HIGH is defined as the START condition (S).A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P) (see Figure 8).7.2System configurationA device generating a message is a ‘transmitter’; a device receiving is the ‘receiver’. The device that controls the message is the ‘master’ and the devices which are controlled by the master are the ‘slaves’ (see Figure 9).Fig 7.Bit transfermba607data line stable;data validchange of data allowedSDASCLFig 8.Definition of START and STOP conditionsmba608SDASCLPSTOP conditionSSTART condition7.3AcknowledgeThe number of data bytes transferred between the START and the STOP conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by oneacknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter,whereas the master generates an extra acknowledge related clock pulse.A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse,so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse; set-up and hold times must be taken into account.A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.Fig 9.System configuration002aaa966MASTER TRANSMITTER/RECEIVERSLAVE RECEIVERSLAVETRANSMITTER/RECEIVERMASTER TRANSMITTERMASTER TRANSMITTER/RECEIVERSDA SCLI 2C-BUS MULTIPLEXERSLAVEFig 10.Acknowledgement on the I 2C-bus002aaa987S START condition9821clock pulse for acknowledgementnot acknowledgeacknowledgedata output by transmitterdata output by receiverSCL from master7.4Bus transactionsFig 11.Write to register0ASslave address (PCA9533/01)START condition R/Wacknowledge from slave002aae629AI0B2B1B00command byteAacknowledge from slave12345678SCL9SDA DATA 1Awrite to registerdata out from portt v(Q)acknowledge from slaveDATA 1 VALIDdata to register111Fig 12.Read from register110AS1START conditionR/Wacknowledge from slave002aae630Aacknowledge from slaveSDA APacknowledge from masterdata from registerDATA (first byte)slave address (PCA9533/01)STOP conditionS(repeated)START condition (cont.)(cont.)1AR/W acknowledge from slaveslave address (PCA9533/01)at this moment master-transmitter becomes master-receiver and slave-receiver becomes slave-transmitterNA no acknowledgefrom masterdata from register DATA (last byte)command byte 0AI0B2B10B0Auto-Increment register address if AI = 1111Remark:This figure assumes the command byte has previously been programmed with 00h.Fig 13.Read input port register111AS1START conditionR/Wacknowledge from slave002aae631Aacknowledge from masterSDA NA read fromportdata intoportPt h(D)data from port no acknowledge from masterdata from port DATA 4slave address (PCA9533/01)DATA 1STOP conditionDATA 2DATA 3DATA 4t su(D)DATA 18.Application design-in information8.1Minimizing I DD when the I/Os are used to control LEDsWhen the I/Os are used to control LEDs, they are normally connected to V DD through a resistor as shown in Figure 14. Since the LED acts as a diode, when the LED is off the I/O V I is about 1.2V less than V DD . The supply current, I DD , increases as V I becomes lower than V DD and is specified as ∆I DD in Table 13 “Static characteristics”.Designs needing to minimize current consumption, such as battery power applications,should consider maintaining the I/O pins greater than or equal to V DD when the LED is off.Figure 15 shows a high value resistor in parallel with the LED.Figure 16 shows V DD less than the LED supply voltage by at least 1.2V . Both of these methods maintain the I/O V I at or above V DD and prevents additional supply current consumption when the LED is off.Fig 14.Typical applicationPCA9533LED0LED1SDA SCL5 VI 2C-BUS/SMBusMASTER002aae632SDASCLV DDV SS5 VLED2LED310 k Ω10 k ΩFig 15.High value resistor in parallel withthe LEDFig 16.Device supplied by a lower voltage002aac189LEDV DDLEDn 100 k ΩV DD002aac190LEDV DDLEDn3.3 V5 V8.2Programming exampleThe following example will show how to set LED0and LED1off.It will set LED2to blink at 1Hz at a 50% duty cycle. LED3 will be set to be dimmed at 25% of their maximum brightness (duty cycle =25%). PCA9533/01 is used in this example.9.Limiting valuesTable 11.Programming PCA9533Program sequenceI 2C-bus ST ARTS PCA9533 addressC4h PSC0 subaddress + Auto-Increment11h Set prescaler PSC0 to achieve a period of 1second:PSC0=15197hSet PWM0 duty cycle to 50%:PWM0=12880hSet prescaler PCS1 to dim at maximum frequency:PSC1=000h Set PWM1 output duty cycle to 25%:PWM1=6440h Set LED0 on, LED1 off; LED2 set to blink at PSC0, PWM0; LED3 set to blink at PSC1, PWM1E1h STOPP Blink period 1PSC01+152-----------------------==PWM0256-----------------0.5=Blink period max =PWM1256-----------------0.25=Table 12.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol Parameter ConditionsMin Max Unit V DD supply voltage−0.5+6.0V V I/O voltage on an input/output pin V SS −0.5 5.5V I O(LEDn)output current on pin LEDn -25mA I SS ground supply current -100mA P tot total power dissipation -400mW T stg storage temperature −65+150°C T ambambient temperatureoperating −40+85°C10.Static characteristics[1]Typical limits at V DD =3.3V , T amb =25°C.[2]V DD must be lowered to 0.2V in order to reset part.[3]Each I/O must be externally limited to a maximum of 25mA and the device must be limited to a maximum current of 100mA.Table 13.Static characteristicsV DD =2.3V to 5.5V; V SS =0V; T amb =−40°C to +85°C; unless otherwise specified.Symbol ParameterConditionsMinTyp [1]MaxUnitSupplies V DD supply voltage 2.3- 5.5V I DD supply current operating mode; V DD =5.5V; no load;V I =V DD or V SS ; f SCL =100kHz -350550µA I stb standby currentStandby mode; V DD =5.5V; no load;V I =V DD or V SS ; f SCL =0kHz- 1.9 3.0µA ∆I DDadditional quiescent supply current Standby mode; V DD =5.5V;every LED I/O at V I =4.3V;f SCL =0kHz --325µAV POR power-on reset voltage no load; V I =V DD or V SS[2]- 1.7 2.2V Input SCL; input/output SDAV IL LOW-level input voltage −0.5-+0.3V DD V V IH HIGH-level input voltage 0.7V DD- 5.5V I OL LOW-level output current V OL =0.4V 3 6.5-mA I L leakage current V I =V DD =V SS −1-+1µA C i input capacitance V I =V SS- 3.75pF I/Os V IL LOW-level input voltage −0.5-+0.8V V IH HIGH-level input voltage 2.0- 5.5V I OLLOW-level output currentV OL =0.4V V DD =2.3V [3]9--mA V DD =3.0V [3]12--mA V DD =5.0V [3]15--mA V OL =0.7V V DD =2.3V [3]15--mA V DD =3.0V [3]20--mA V DD =5.0V[3]25--mA I LI input leakage current V DD =3.6V; V I =0V or V DD−1-+1µA C ioinput/output capacitance-2.15pF(1)maximum (2)average (3)minimum(1)maximum (2)average (3)minimumFig 17.Typical frequency variation over process atV DD =2.3V to 3.0V Fig 18.Typical frequency variation over process atV DD =3.0V to 5.5V−20 %0 %20 %percent variation−40 %T amb (°C)−40100−20002aac191020406080(2)(1)(3)−20 %0 %20 %percent variation−40 %T amb (°C)−40100−20002aac192020406080(1)(2)(3)11.Dynamic characteristics[1]t VD;ACK = time for Acknowledgement signal from SCL LOW to SDA (out) LOW.[2]t VD;DA T = minimum time for SDA data output to be valid following SCL LOW.[3]C b =total capacitance of one bus line in pF .Table 14.Dynamic characteristics SymbolParameterConditionsStandard-modeI 2C-bus Fast-mode I 2C-busUnitMinMax Min Max f SCL SCL clock frequency01000400kHz t BUF bus free time between a STOP and ST ART condition4.7- 1.3-µs t HD;STA hold time (repeated) START condition 4.0-0.6-µs t SU;ST A set-up time for a repeated ST ART condition4.7-0.6-µs t SU;STO set-up time for STOP condition 4.0-0.6-µs t HD;DA T data hold time0-0-ns t VD;ACK data valid acknowledge time [1]-600-600ns t VD;DA T data valid time LOW-level [2]-600-600ns HIGH-level[2]-1500-600ns t SU;DA T data set-up time250-100-ns t LOW LOW period of the SCL clock 4.7- 1.3-µs t HIGH HIGH period of the SCL clock 4.0-0.6-µs t r rise time of both SDA and SCL signals -100020+0.1C b [3]300ns t f fall time of both SDA and SCL signals -30020+0.1C b [3]300ns t SPpulse width of spikes that must be suppressed by the input filter -50-50nsPort timing t v(Q)data output valid time -200-200ns t su(D)data input set-up time 100-100-ns t h(D)data input hold time1-1-µs12.Test informationFig 19.Definition of timingt SPt BUFt HD;STAPPSt LOWt rt HD;DAT t ft HIGH t SU;DATt SU;STASrt HD;STAt SU;STOSDASCL002aaa986Rise and fall times refer to V IL and V IH .Fig 20.I 2C-bus timing diagramSCLSDAt HD;STA t SU;DA T t HD;DA T t ft BUFt SU;ST At LOWt HIGHt VD;ACK 002aab175t SU;STOprotocolST ART condition (S)bit 7MSB (A7)bit 6(A6)bit 0(R/W)acknowledge(A)STOP condition (P)1/fSCLt rt VD;DA T R L = load resistor for LEDn. R L for SDA and SCL > 1k Ω (3mA or less current).C L = load capacitance includes jig and probe capacitance.R T = termination resistance should be equal to the output impedance Z o of the pulse generators.Fig 21.Test circuitry for switching timesPULSE GENERATORV OC L 50 pFR L 500 Ω002aab880R TV IV DDDUTV DD open V SS13.Package outlineFig 22.Package outline SOT96-1 (SO8)UNIT Amax.A 1A 2A 3b p c D (1)E (2)(1)e H E L L p Q Z y w v θ REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IEC JEDEC JEITAmm inches1.750.250.101.451.250.250.490.360.250.195.04.8 4.03.8 1.276.25.81.050.70.60.70.380o o 0.250.10.25DIMENSIONS (inch dimensions are derived from the original mm dimensions)Notes1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.2. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.1.00.4SOT96-1Xw MθAA 1A 2b pD H EL pQdetail XE Z ecL v M A(A )3A45pin 1 index18y076E03MS-0120.0690.0100.0040.0570.0490.010.0190.0140.01000.00750.200.190.160.150.050.2440.2280.0280.0240.0280.0120.010.010.0410.0040.0390.0160 2.5 5 mmscaleSO8: plastic small outline package; 8 leads; body width 3.9 mmSOT96-199-12-2703-02-18Fig 23.Package outline SOT505-1 (TSSOP8)UNIT A 1A max.A 2A 3b p L H E L p w y v c e D (1)E (2)Z (1)θ REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDECJEITAmm0.150.050.950.800.450.250.280.153.12.93.12.90.655.14.70.700.356°0°0.10.10.10.94DIMENSIONS (mm are the original dimensions)Notes1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.0.70.4SOT505-199-04-0903-02-18w Mb pD Ze0.251485θAA 2A 1L p (A 3)detail XLH EE cv M AXAy2.5 5 mm0scaleTSSOP8: plastic thin shrink small outline package; 8 leads; body width 3 mm SOT505-11.1pin 1 index14.Handling informationAll input and output pins are protected against ElectroStatic Discharge (ESD) undernormal handling. When handling ensure that the appropriate precautions are taken asdescribed in JESD625-A or equivalent standards.15.Soldering of SMD packagesThis text provides a very brief insight into a complex technology.A more in-depth accountof soldering ICs can be found in Application Note AN10365 “Surface mount reflowsoldering description”.15.1Introduction to solderingSoldering is one of the most common methods through which packages are attached toPrinted Circuit Boards(PCBs),to form electrical circuits.The soldered joint provides boththe mechanical and the electrical connection. There is no single soldering method that isideal for all IC packages. Wave soldering is often preferred when through-hole andSurface Mount Devices (SMDs) are mixed on one printed wiring board; however, it is notsuitable for fine pitch SMDs. Reflow soldering is ideal for the small pitches and highdensities that come with increased miniaturization.15.2Wave and reflow solderingWave soldering is a joining technology in which the joints are made by solder coming froma standing wave of liquid solder. The wave soldering process is suitable for the following:•Through-hole components•Leaded or leadless SMDs, which are glued to the surface of the printed circuit boardNot all SMDs can be wave soldered. Packages with solder balls, and some leadlesspackages which have solder lands underneath the body, cannot be wave soldered. Also,leaded SMDs with leads having a pitch smaller than ~0.6mm cannot be wave soldered,due to an increased probability of bridging.The reflow soldering process involves applying solder paste to a board, followed bycomponent placement and exposure to a temperature profile. Leaded packages,packages with solder balls, and leadless packages are all reflow solderable.Key characteristics in both wave and reflow soldering are:•Board specifications, including the board finish, solder masks and vias•Package footprints, including solder thieves and orientation•The moisture sensitivity level of the packages•Package placement•Inspection and repair•Lead-free soldering versus SnPb soldering15.3Wave solderingKey characteristics in wave soldering are:•Process issues, such as application of adhesive and flux, clinching of leads, board transport, the solder wave parameters, and the time during which components areexposed to the wave•Solder bath specifications, including temperature and impurities15.4Reflow solderingKey characteristics in reflow soldering are:•Lead-free versus SnPb soldering;note that a lead-free reflow process usually leads to higher minimum peak temperatures (see Figure24) than a SnPb process, thusreducing the process window•Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board•Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature) and cooling down. It is imperative that the peaktemperature is high enough for the solder to make reliable solder joints(a solder pastecharacteristic). In addition, the peak temperature must be low enough that thepackages and/or boards are not damaged. The peak temperature of the packagedepends on package thickness and volume and is classified in accordance withTable15 and16Table 15.SnPb eutectic process (from J-STD-020C)Package thickness (mm)Package reflow temperature (°C)Volume (mm3)< 350≥ 350< 2.5235220≥ 2.5220220Table 16.Lead-free process (from J-STD-020C)Package thickness (mm)Package reflow temperature (°C)Volume (mm3)< 350350 to 2000> 2000 < 1.62602602601.6 to2.5260250245> 2.5250245245Moisture sensitivity precautions, as indicated on the packing, must be respected at alltimes.Studies have shown that small packages reach higher temperatures during reflowsoldering, see Figure24.For further information on temperature profiles, refer to Application Note AN10365“Surface mount reflow soldering description”.16.AbbreviationsMSL: Moisture Sensitivity LevelFig 24.Temperature profiles for large and small components001aac844temperaturetimeminimum peak temperature = minimum soldering temperaturemaximum peak temperature = MSL limit, damage levelpeak temperatureTable 17.AbbreviationsAcronym DescriptionACPI Advanced Configuration and Power Interface CDM Charged Device Model DSP Digital Signal Processor DUT Device Under Test ESD ElectroStatic Discharge GPIO General Purpose Input/Output HBM Human Body Model I 2C-bus Inter-Integrated Circuit bus LED Light Emitting Diode MCU MicroController Unit MM Machine Model MPU MicroProcessor Unit POR Power-On ResetRC Resistor-Capacitor network SMBusSystem Management Bus。

Connect Tech XMC to PCIe 104 Adapter 用户指南说明书

XMC to PCIe/104 AdapterConnect Tech Inc.Tel:519-836-129142 Arrow Road Toll:800-426-8979 (North America only) Guelph, Ontario Fax:519-836-4878N1K 1S6 Email:********************************************Table of ContentsTable of Contents (2)Preface (3)Disclaimer (3)Customer Support Overview (3)Contact Information (3)Limited Product Warranty (4)Copyright Notice (4)Trademark Acknowledgment (4)ESD Warning (5)Revision History (5)Introduction (6)Product Features and Specifications (6)Product Overview (7)Connector Summary & Locations (7)Jumper Summary & Locations (8)Detailed Feature Description (9)PCIe/104 Connector (9)Description (9)Connectors & Jumpers (9)XMC Expansion Slot (10)Description (10)Connectors & Jumpers (10)Indicator LEDs (11)Description (11)Connectors & Jumpers (11)Typical Installation (12)PrefaceDisclaimerThe information contained within this user’s guide, including but not limited to any product specification, is subject to change without notice.Connect Tech assumes no liability for any damages incurred directly or indirectly from any technical ortypographical errors or omissions contained herein or for discrepancies between the product and the user’s guide.Customer Support OverviewIf you experience difficulties after reading the manual and/or using the product, contact the Connect Tech reseller from which you purchased the product. In most cases the reseller can help you with product installation and difficulties.In the event that the reseller is unable to resolve your problem, our highly qualified support staff can assist you.Our support section is available 24 hours a day, 7 days a week on our website at:/sub/support/support.asp. See the contact information section below for moreinformation on how to contact us directly. Our technical support is always free.Contact InformationMail/CourierConnect Tech Inc.Technical Support42 Arrow RoadGuelph, OntarioCanada N1K 1S6Email/Internet********************************************Telephone/FacsimileTechnical Support representatives are ready to answer your call Monday through Friday, from 8:30 a.m. to 5:00 p.m. Eastern Standard Time. Our numbers for calls are:Toll Free: 800-426-8979 (North America only)Telephone: 519-836-1291 (Live assistance available 8:30 a.m. to 5:00 p.m. EST,Monday to Friday)Facsimile: 519-836-4878 (on-line 24 hours)Limited Product WarrantyConnect Tech Inc. provides a 2 year Warranty for the XMC to PCIe/104 Adapter. Should this product, in Connect Tech Inc.'s opinion, fail to be in good working order during the warranty period, Connect Tech Inc.will, at its option, repair or replace this product at no charge, provided that the product has not been subjected to abuse, misuse, accident, disaster or non-Connect Tech Inc. authorized modification or repair.You may obtain warranty service by delivering this product to an authorized Connect Tech Inc. business partner or to Connect Tech Inc. along with proof of purchase. Product returned to Connect Tech Inc. must be pre-authorized by Connect Tech Inc. with an RMA (Return Material Authorization) number marked on the outside of the package and sent prepaid, insured and packaged for safe shipment. Connect Tech Inc. will return this product by prepaid ground shipment service.The Connect Tech Inc. Limited Warranty is only valid over the serviceable life of the product. This is defined as the period during which all components are available. Should the product prove to be irreparable, Connect Tech Inc. reserves the right to substitute an equivalent product if available or to retract the Warranty if no replacement is available.The above warranty is the only warranty authorized by Connect Tech Inc. Under no circumstances willConnect Tech Inc. be liable in any way for any damages, including any lost profits, lost savings or otherincidental or consequential damages arising out of the use of, or inability to use, such product. Copyright NoticeThe information contained in this document is subject to change without notice. Connect Tech Inc. shall not be liable for errors contained herein or for incidental consequential damages in connection with the furnishing, performance, or use of this material. This document contains proprietary information that is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of Connect Tech, Inc.Copyright 2016 by Connect Tech, Inc.Trademark AcknowledgmentConnect Tech, Inc. acknowledges all trademarks, registered trademarks and/or copyrights referred to in this document as the property of their respective owners. Not listing all possible trademarks or copyrightacknowledgments does not constitute a lack of acknowledgment to the rightful owners of the trademarks and copyrights mentioned in this document.ESD WarningElectronic components and circuits are sensitive toElectroStatic Discharge (ESD). When handling any circuit board assemblies including Connect Tech COM Express carrier assemblies, it is recommended that ESD safety precautions be observed. ESD safe best practices include, but are not limited to:∙ Leaving circuit boards in their antistatic packaginguntil they are ready to be installed.∙ Using a grounded wrist strap when handling circuitboards, at a minimum you should touch a grounded metal object to dissipate any static charge that may be present on you.∙ Only handling circuit boards in ESD safe areas, whichmay include ESD floor and table mats, wrist strap stations and ESD safe lab coats.∙ Avoiding handling circuit boards in carpeted areas. ∙ Try to handle the board by the edges, avoiding contactwith components.Revision HistoryIntroductionConnect Tech’s XMC to PCIe/104 Adapter Board is an engineering tool for the purpose of enabling rapid development of systems requiring the use of next generation form factor peripheral cards. This product complies with the VITA 42 specification.Product Features and SpecificationsProduct Overview Connector Summary & Locations ADG095 Top ViewADG095 BottomViewJumper Summary & LocationsDetailed Feature DescriptionPCIe/104 ConnectorDescriptionPCIe/104 interface to CPU module Connectors & JumpersXMC Expansion SlotDescriptionM.2 interface slots for expansion cards. Can be ordered in either key E or key BM. Card type support is listed below.See Part Numbers/Ordering Information section for more ordering details.Connectors & JumpersIndicator LEDsDescriptionIndicator LED’s Connectors & JumpersTypical InstallationCard may be installed in a stack-up or stack-down configuration. 10mm height, M2.5 standoffs required between XMC adapter and XMC expansion card. Example stack-up on Connect Tech’s Com Express Type 6 104e Carrier shown below:。

XRA1203_100_092011

FEATURES

• 1.65V to 3.6V operating voltage • 16 General Purpose I/Os (GPIOs) • 5V tolerant inputs • Maximum stand-by current of 1uA at +1.8V • I2C/SMBus bus interface

I/O General purpose I/O P8-P15. All GPIOs are configured as inputs upon powerI/O up or after a reset. I/O I/O I/O I/O I/O I/O

Pwr 1.65V to 3.6V VCC supply voltage.

DEVICE STATUS

Active Active Active Active

FIGURE 2. PIN OUT ASSIGNMENTS

P6 P7 GND P8 P9 P10

RESET# A1 IRQ# VCC SDA SCL

24 23 22 21 20 19

P0 1

18 A0

P1 2

17 P15

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 •

XRA1203

16-BIT I2C/SMBUS GPIO EXPANDER WITH RESET

As inputs, the internal pull-up resistors can be enabled or disabled and the input polarity can be inverted. The interrupt can be programmed for different behaviors. The interrupts can be programmed to generate an interrupt on the rising edge, falling edge or on both edges. The interrupt can be cleared if the input changes back to its original state or by reading the current state of the inputs.

信号一致性测试

Agilent Technologies 周英航

内容安排

DDR原理及测试方法 PCIE原理及测试方法 USB3.0原理及测试方法 SATA原理及测试方法

DP原理及测试方法

HDMI1.4原理及测试方法 Ethernet原理及1G/10G的测试方法

Double Data Rate (DDR)技术

Separation of Read and Write with Infiniiscan

READ

Must not intersect this zone Must intersect this zone

WRITE

Must not intersect these zone

Most popular way to separate read/write 1) Trigger at the falling edge of DQS (Trigger at the preamble) 2) Use Infiniiscan zone qualify to DQS to separate read and write.

读/写相对于DQS信号的时序不同; 读数据时,DQS和DQ边沿对齐; 写数据时,DQS 的边沿对准DQ的 中心,即有90度的相位偏移。

DDR3 Application Tests Parameters

Specification JESD79-3 DDR3 SDRAM Specifications

DIMM FPGA Design DDR DRAM

Comparison of DDR1/2/3

Voltage

Memory Speed Roadmap

DDR4 3.2 GT/s DDR3 1.6 GT/s

迈普大客户专线接入产品

目录GV220系列接口转换器 (1)NB110系列以太网桥 (3)FT160系列网管型光端机 (7)MP9400大客户专线接入平台 (11)MP9710多业务大客户专线接入平台 (16)EPAS360专线接入服务器 (23)GV220系列接口转换器GV220系列接口转换器包括GV220、GV220S两个型号,是迈普公司研发生产的G.703-V.35转换器,可实现G.703与V.35接口之间数据的转换。

GV220外观图产品特点⏹速率:GV220 提供N*64K (N=1~32)速率数据转换;GV220S 提供2Mbps透明数据传输⏹数据时钟沿反转:发送和接收数据时钟沿可为上升沿,也可为下降沿⏹多时钟源:支持内时钟、G.703外时钟、V.35外时钟⏹设置简便:使用DIP开关设置全部工作方式⏹监测直观:设备面板即可观测G.703、V.35接口信号状态⏹维护方便:全硬件实现,性能更稳定,无升级之忧技术规范描述GV220GV220S接口特性G.703接口传输速率:N×64Kbps(N=1~32)线路码型:HDB3码线路阻抗:75Ω(不平衡)/120Ω(平衡)接口标准:CCITT G.703标准V.35接口接口标准:DCE传输速率:N×64Kbps(N=1~32)接口标准:DCE传输速率:2Mbps物理指标外形尺寸(H×W×D):30mm×120mm×210mm 重量:约0.6Kg电源要求交流电源输入电压:交流160~240V/50HZ 适配器输入电流:≤0.04A整机功率:≤4W 直流电源输入电压:-40~-57V适配器输入电流:≤0.12A整机功率:≤4W定购信息产品型号描述GV220支持N*64K (N=1~32)速率数据转换,1个G.703接口、1个V.35接口,标配外置交流电源,可选直流电源模块GV220S 支持2Mbps透明数据传输,1个G.703接口、1个V.35接口,标配外置交流电源,可选直流电源模块GVPA077W外置交流电源模块,输入电压160~240V/50-60Hz,输出5V/1.4A,配GV220 GVPD066W外置直流电源模块,输入电压-40~-57V,输出5V/1.2A,配GV220AD8-1S003Y8W外置交流电源模块,输入电压100-240V/50-60Hz,输出5V/1.6A,配GV220S PWM10-DD48S5V310W外置直流电源模块,输入电压-40--57V,输出5V/1.6A,配GV220S典型应用网点路由器网点路由器GV220SGV220S用户中心路由器上图为GV220S/GV220的典型应用,通过GV220S/GV220与局端具有E1接口的设备(ATM、路由器或DDN节点机等)相连,实现V.35与G.703接口之间数据的2M透明转换。

Your complete choice for I2C bus peripherals 15669

New Fast-mode Plus devices operate at 1 MHz with higher drive I2C-bus slave data can be transmitted longer distances using bus buffers like the P82B96

NXP Semiconductors is the world’s leading supplier of I2C-bus products. We invented the technology more than 20 years ago and never looked back. Since then, we’ve taken performance to new levels, introduced a wide variety of vital functions, and continue to offer the most fl exible options for the most important applications. We offer the industry’s broadest portfolio of I2C-bus logic, providing essential components like GPIO, LED blinkers/ dimmers, Hot Swap bus buffers, bus expanders, bus hubs/ repeaters, DIP switches, muxes and switches, EEPROMs, data converters, LCD segment drives, and more.

PCA9535DB中文资料

The system master can reset the PCA9535 in the event of a timeout or other improper operation by utilizing the power-on reset feature, which puts the registers in their default state and initializes the I2C/SMBus state

The device outputs (latched) have high-current drive capability for directly driving LEDs. The device has low current consumption.

Although pin-to-pin and I2C address compatible with the PCF8575, software changes are required due to the enhancements.

2

Submit Documentation Feedback

元, SSOP (DB), QSOP (DBQ), TSSOP (PW), AND TVSOP (DGV)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

machine.

The PCA9535 open-drain interrupt (INT) output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system master that an input state has changed.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

BUS TRANSACTIONSWriting to the port registersData is transmitted to the PCA9539 by sending the device address and setting the least significant bit to a logic 0 (see Figure 5 for device address). The command byte is sent after the address and determines which register will receive the data following the command byte.The eight registers within the PCA9539 are configured to operateas four register pairs. The four pairs are Input Ports, Output Ports, Polarity Inversion Ports, and Configuration Ports. After sending data to one register, the next data byte will be sent to the other register in the pair (see Figures 6 and 7). For example, if the first byte is sent to Output Port (register 3), then the next byte will be stored in Output Port 0 (register 2). There is no limitation on the number of data bytes sent in one write transmission. In this way, each 8-bit register may be updated independently of the other registers.Reading the port registersIn order to read data from the PCA9539, the bus master must first send the PCA9539 address with the least significant bit set to a logic 0 (see Figure 5 for device address). The command byte is sent after the address and determines which register will be accessed.After a restart, the device address is sent again but this time, the least significant bit is set to a logic 1. Data from the register defined by the command byte will then be sent by the PCA9539 (see Figures 8 , 9, and 10). Data is clocked into the register on the falling edge of the acknowledge clock pulse. After the first byte is read, additional bytes may be read but the data will now reflect the information in the other register in the pair. For example, if you read Input Port 1, then the next byte read would be Input Port 0. There is no limitation on the number of data bytes received in one read transmission but the final byte received, the bus master must not acknowledge the data.Interrupt OutputThe open-drain interrupt output is activated when one of the port pins change state and the pin is configured as an input. The interrupt is deactivated when the input returns to its previous state or the input port register is read (see Figure 9). A pin configured as an output cannot cause an interrupt. Since each 8-bit port is read independently, the interrupt caused by Port 0 will not be cleared by a read of Port 1 or the other way around.Note that changing an I/O from an output to an input may cause a false interrupt to occur if the state of the pin does not match the contents of the Input Port register.SO24:plastic small outline package; 24 leads; body width 7.5 mm SOT137-1TSSOP24:plastic thin shrink small outline package; 24 leads; body width 4.4 mm SOT355-1HVQFN24:plastic thermal enhanced very thin quad flat package; no leads; 24 terminals;body 4 x 4 x 0.85 mm SOT616-1Philips Semiconductors Product data sheetPCA9539 16-bit I2C and SMBus, low power I/O port with interruptDefinitionsShort-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.DisclaimersLife support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status ‘Production’), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.Contact informationFor additional information please visit.Fax: +31 40 27 24825For sales offices addresses send e-mail to:© Koninklijke Philips Electronics N.V. 2004All rights reserved. Printed in U.S.A.Date of release: 09-04Document order number:9397 750 14048。