K9G8G08U0M-W

K9F1G08UOM数据手册

m A 5 5 15 15 1 10 10 20 20 1 µA 10 50 10 50

页 编 ICC2 程 擦除 ICC3 ISB1 等待状态电流 (TTL) 等待状态电流 (CMOS) 输入开漏电流 输出开漏电流

ISB2

IL1 IL0

-

-

±10 ±10

-

-

±10 ±10 VCC V +0.3 0.8 -

6. 命令/地址/ 数据复用端口: 7. 硬件数据保护:编程/擦除操作在电源转换时关闭。 8. 可靠的 CMOS 浮置门技术: --保证:100K 编程/ 擦除次数。 --数据保持时间: 10 年。 9. 命令寄存器操作 10. 为高速编程设置的缓冲编程操作。 11. 通电自动读操作。 12. 智能复制拷贝操作。 13.为防盗版而设置的唯一的 ID 保护。 14. 封装。 - K9F1GXXX0M-YCB0/YIB0 48 - Pin TSOP I (12 x 20 / 0.5 mm pitch) - K9F1G08U0M-VCB0/VIB0 48 - Pin WSOP I (12X17X0.7mm)

器件描述

三星 K9F1GXXX0M 提供了 128M*8Bit/64M*16Bit 的存储容量,另外还有 32 M 的空闲存储器,它是采用 NAND 技术的大容量、高可靠的 Flash 存储器。 它对 2112 字节一页(*8device )或者 1056 字(*16device)一页的写操作。典型 时间是 300 微秒。对 128 字节/64K 字一块的擦除时间是 50 纳秒。输出引脚可 以作为数据/地址/命令复用。每一页的数据读出时间也很快,平均每个字节只 需 50 纳秒。片内的写控制器,可以自动执行写操作和擦除功能,包括必要的脉 冲产生器,内部校验和冗余数据。 K9F1G08 提供了实时映像算法的纠错码,写 操作系统可以利用 K9F1G08U0M 扩展的 100K 编程/ 擦除。K9F1G08U0M 为大 容量存储,新型电可擦写的非易失性半导体存储器,提供了最优方案。

K9K8G08U0A

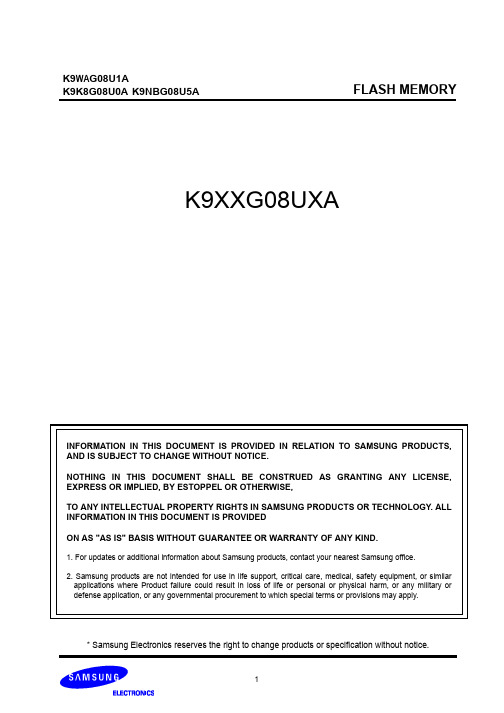

K9WAG08U1A K9K8G08U0A K9NBG08U5A

FLASH MEMORY

K9XXG08UXA

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE. NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDED ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND. 1. For updates or additional information about Samsung products, contact your nearest Samsung office. 2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar

使用的NandFlash为三星的K9F2G08U0M

使用的Nand Flash为三星的K9F2G08U0M,存储为256M,数据宽度为8bit.具体的资料可以参考datasheet.由于S3C2440里面包括了Nand FLash 控制器,所以,我们的工作就是根据芯片手册配置一下寄存器。

包括的寄存器如下:NFCONF; NFCONT;NFCMD;NFADDR;NFDATA; NFMECCD0; NFMECCD1;NFSECCD; N FSTAT; NFESTAT0; NFESTAT1;NFMECC0;NFMECC1;NFSECC;NFSBLK;NFEBLK;(1) 对于每个寄存器的地址,每一位的功能可以参考S3C2440芯片手册!对于目前的编程主要涉及到如下五个寄存器:NFCONT;NFCMD;NFADDR;NFDATA;NFSTAT;使用宏定义:#define rNFCONF (*(volatile unsigned *)0x4E000000)#define rNFCONT (*(volatile unsigned *)0x4E000004)#define rNFCMD (*(volatile unsigned *)0x4E000008) #define rNFADDR (*(volatile unsigned char*)0x4E00000C)#define rNFDATA8 (*(volatile unsigned char*)0x4E000010)#define rNFSTAT (*(volatile unsigned *)0x4E000020)特别注明:对于NFCONF寄存器,特别要说明的是TACLS,TWRPH0,TWRPH1,这三个参数。

如何设置这三个参数,主要得看K9F2G08U0M 手册上的时序表,参数表,上面已经写好了CLE ,ALEsetup时间,WE_N的Pulse WiDth,WE_N HIGH HOLD TIME .根据这些参数,设置个合适的TACLS,TWRPH0,TWRPH1值!(2) 命令! Nand Flash编程时涉及到很多命令,其实这些命令帮助我们完成了很多的工作,我们现在只需做发送命令的工作。

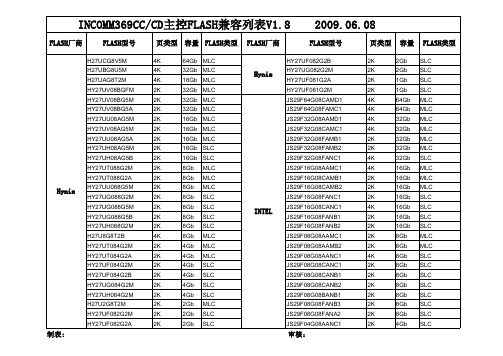

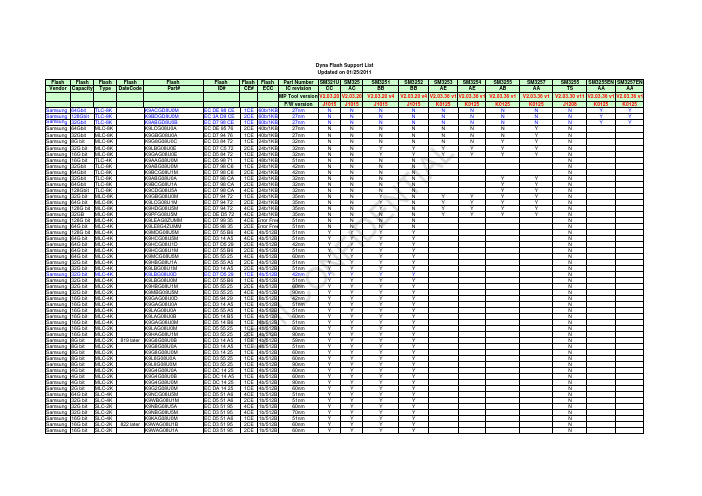

INCOM369CC CD主控FLASH支持表1.8.xls(09-06-08)

HY27UF082G2B

Hynix

HY27UG082G2M HY27UF081G2A HY27UF081G2M JS29F64G08CAMD1 JS29F64G08FAMC1 JS29F32G08AAMD1 JS29F32G08CAMC1 JS29F32G08FAMB1 JS29F32G08FAMB2 JS29F32G08FANC1 JS29F16G08AAMC1 JS29F16G08CAMB1 JS29F16G08CAMB2 JS29F16G08FANC1 JS29F16G08CANC1 JS29F16G08FANB1 JS29F16G08FANB2 JS29F08G08AAMC1 JS29F08G08AAMB2 JS29F08G08AANC1 JS29F08G08CANC1 JS29F08G08CANB1 JS29F08G08CANB2 JS29F08G08BANB1 JS29F08G08FANB3 JS29F08G08FANA2 JS29F04G08AANC1

FLASH厂商

容量

2Gb 2Gb 1Gb 1Gb 64Gb 64Gb 32Gb 32Gb 32Gb 32Gb 32Gb 16Gb 16Gb 16Gb 16Gb 16Gb 16Gb 16Gb 8Gb 8Gb 8Gb 8Gb 8Gb 8Gb 8Gb 8Gb 8Gb 4Gb

FLASH类型

SLC SLC SLC SLC MLC MLC MLC MLC MLC MLC SLC MLC MLC MLC SLC SLC SLC SLC MLC MLC SLC SLC SLC SLC SLC SLC SLC SLC

MICRON

MT29F4G08AAB MT29F4G08AAA MT29F2G08AAD MT29F2G08AAB MT29F2G08AAC MT29F2G08AAA K9HCG08U1M K9HCG08U5M K9LBG08U0M K9LBG08U1M K9HBG08U1M K9WBG08U1M K9GAG08U0M K9GAG08U0D K9LAG08U0M

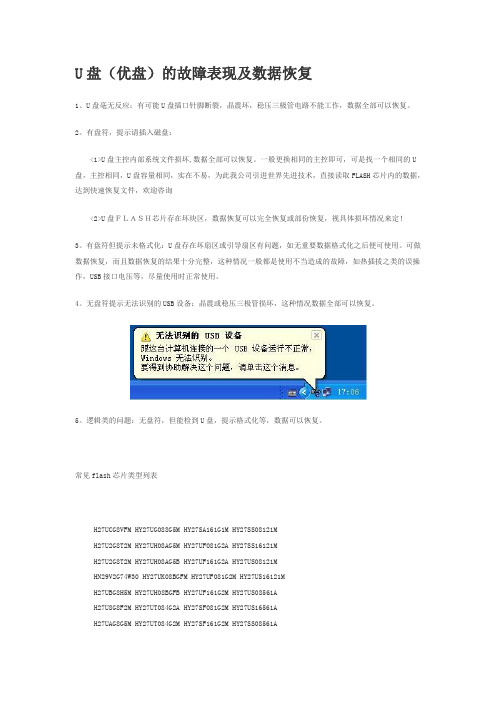

U盘 维修

U盘(优盘)的故障表现及数据恢复1、U盘毫无反应:有可能U盘插口针脚断裂,晶震坏,稳压三极管电路不能工作,数据全部可以恢复。

2。

有盘符,提示请插入磁盘:<1>U盘主控内部系统文件损坏,数据全部可以恢复。

一般更换相同的主控即可,可是找一个相同的U 盘,主控相同,U盘容量相同,实在不易,为此我公司引进世界先进技术,直接读取FLASH芯片内的数据,达到快速恢复文件,欢迎咨询<2>U盘FLASH芯片存在坏块区,数据恢复可以完全恢复或部份恢复,视具体损坏情况来定!3。

有盘符但提示未格式化:U盘存在坏扇区或引导扇区有问题,如无重要数据格式化之后便可使用。

可做数据恢复,而且数据恢复的结果十分完整,这种情况一般都是使用不当造成的故障,如热插拔之类的误操作,USB接口电压等,尽量使用时正常使用。

4。

无盘符提示无法识别的USB设备:晶震或稳压三极管损坏,这种情况数据全部可以恢复。

5。

逻辑类的问题:无盘符,但能检到U盘,提示格式化等,数据可以恢复。

常见flash芯片类型列表H27UCG8VFM HY27UG088G5M HY27SA161G1M HY27SS08121MH27U2G8T2M HY27UH08AG5M HY27UF081G2A HY27SS16121MH27U2G8T2M HY27UH08AG5B HY27UF161G2A HY27US08121MHN29V2G74W30 HY27UK08BGFM HY27UF081G2M HY27US16121MH27UBG8H5M HY27UH08BGFB HY27UF161G2M HY27US08561AH27U8G8F2M HY27UT084G2A HY27SF081G2M HY27US16561AH27UAG8G5M HY27UT084G2M HY27SF161G2M HY27SS08561AH27UBG8T5M HY27UU088G5M HY27UF082G2A HY27SS16561AHY27US08281A HY27UT088G2M HY27UF162G2A HY27US08561MHY27US08561A HY27UT088G2A HY27UF082G2B HY27US16561MHY27US08561M HY27UV08AG5M HY27UF162G2B HY27SS08561MHY27US08121A HY27UV08BG5M HY27UF084G2B HY27SS16561MHY27US08121M HY27UV08BGFM HY27UF164G2B HY27US08281AHY27UA081G1M HY27UV08BGFA HY27UF082G2M HY27US16281AHY27UA081G4M HY27UU08AG5M HY27UF162G2M HN29W12811T-60HY27UB082G4M HY27UU08AG5A HY27UH088G2M HN29V25691BTHY27UF081G2A HY27UW08BGFM HY27UH088GDM HN29V51211T-50HY27UF081G2M HY27UW08CGFM HY27UG088G5B HN29V1G91T-30HY27UF082G2A Hynix InkDie HY27UG088G5M HY27UF164G2B(x16)HY27UF082G2M H27UAG8T2M HY27UH08AG5M HYF33DS512804(5)BTC HY27UF082G2B H27UCG8V5M HY27UK08BGFM HYF33DS512804(5)BTC HY27UF084G2B HY27SF082G2B HY27US081G1M HYF33DS512804(5)BTC HY27UG088G5B HY27SF162G2B HY27US161G1M HYF33DS512804(5)BTC HY27UF084G2M HY27SF081G2A HY27US08121A HYF33DS1G800CTIHY27UG084G2M HY27SF161G2A HY27US16121A HYF33DS1G800CTIHY27UH084G2M HY27U(s)A081G1M HY27SS08121A HY27US16562AHY27UH088G2M HY27UA161G1M HY27SS16121A HY27SS081G1XI29F04G08AAA I29F32G08CAMCI FTGM40A2GK3WG FTNL41B8GK3PGI29F08G08AAMB2 I29F64G08FAMC1 FBNL41B32K3P4 FTNL41B8GK3PGI29F08G08AAMBI PF79BL1208BSG FBNL41B8GK3P2 FTNL41B8GK3PGI29F16G08AAMCI PF79AL1208BS FTNL41BHGK3W4 R1FV04G13RSA-3I29F16G08MAA DFT512W08B-P1 FBNL41B8GK3W3 R1FV04G13RSA-3_2ASU4GA30GT K9F2G08U0M K9WBG08U1M K9L8G08U0MASU2GA30GT K9F2G08U0M K9NBG08U5A K9LAG08U0MK9F2808U0B K9K2G08U0M K9NCG08U5M K9LAG08U0A_BK9F5608U0B K9GAG08U0A K9G2G08U0M K9HBG08U1AK9F1208U0A K9GAG08U0D K9G4G08U0A K9LBG08U0MK9F1208U0B K9K4G08U0M K9G8G08U0A K9HAG08U1MK9F1208U0C K9F4G08U0A K9G8G08U0M K9HBG08U1MK9K1G08U0M K9F8G08U0M K9L8G08U1M K9HCG08U1MK9E2G08U1M K9K8G08U0A K9LBG08U0D K9MDG08U5MK9F1G16U0M K9KAG08U0M K9HCG08U1M K9MBG08U5MK9F1G08U0A K9W8G08U1M K9HCG08U1D K9MCG08U5MK9F1G08U0B K9WAG08U1A K9LAG08U1M K9GAG08U0MK9F1G08U0M K9LBG08U1M K9HCG08U5M K9F5616U0C(x16)K9F2G08U0A K9F1208U0M K9F5616U0C K9K4G16Q0MK9F1G16Q0M K9F2808U0 K9G8G08U0M K9XXG08UXMK9F1G08 K9F5608U0B K9LAG08U0M K9K4G16U0MK9F1G16U0M K9F5616U0B K9HBG08U1M K9K8G08U0MK9F2G08U0A K9F5608D0C K9MCG08U5M K9WAG08U1MK9F2G16U0M K9F5616D0C K9K1G08U0M K9K2G08Q0MK9F2G08U0M K9F5608U0C K9K4G08Q0M K9K2G16Q0MK9XXG08UXM K9XXG16UXM K9K2G08U0M K9F1G08Q0MNAND128W3A2BN6E NAND08GW3C2B NAND512R3A NAND04GW4B2DNAND256W3A2BN6E NAND16GW3C4B NAND512W3A NAND08GW3B2CNAND512W3A0AN6 NAND01GW3B2B NAND512R4A NAND08GR4B2CNAND01GW3A0AN6 NAND01GR4B2B NAND512W4A NAND08GW4B2CNAND01GW3B2AN6 NAND01GW4B2B NAND01GR3A NAND08GW3C2ANAND01GW3B2BN6 NAND02GW3B2C NAND01GW3A NAND16GW3C4ANAND02GW3B2AN6 NAND02GR4B2C NAND01GR4A NAND08GW3C2BNAND02GW3B2D NAND02GW4B2C NAND01GW4A NAND08GW3D2ANAND02GW3B2CN6 NAND01GW3B2C NAND02GW3B2D NAND512R3A2DNAND04GW3B2DN6 NAND01GR4B2C NAND02GR4B2D NAND512W3A2DNAND04GW3B2BN6 NAND01GW4B2C NAND02GW4B2D NAND512R4A2DNAND08GW3B2CN6 NAND128R3A NAND04GW3C2A NAND512W4A2DNAND08GW3B2AN6 NAND128W3A NAND04GA3C2A NAND01GR3A2CNAND04GW3C2AN1 NAND256R3A NAND04GW3B2B NAND01GW3A2CNAND08GW3C2AN1 NAND256W3A NAND08GW3B2A NAND01GR4A2CNAND08GW3B2CN6 NAND256R4A NAND04GW3B2D NAND01GW4A2CNAND04GW3C2B NAND256W4A NAND04GR4B2D NAND04GW3C2BNAND08GW3F2A NAND16GW3F2A NAND08GW3C2BMT29F8G08MAA MT29F64G08TAA MT29F4G08ABC MT29F4G08BABMT29F8G16MAA MT29F32G08BAAA MT29F32G08FAA MT29F8G08FABMT29F16G08QAA MT29F64G08CFAAA MT29F8G08BAA MT29F4G16BABMT29F2G08AAC MT29F4G08ABC MT29F8G08DAA MT29F16G08QAA(DUAL) MT29F32G08TAA MT29F2G08AAA MT29F16G08FAA MT29F2G08ABCMT29F2G16AAC MT29F2G16ABD MT29F4G08MAA MT29F32G08TAA-BMT29F2G16ABC MT29F2G08AAB_C MT29F4G08MAA_2 MT29F128G08CJAAA MT29F4G08BBC MT29F4G08AAA_C MT29F8G08MAD MT29F4G08BACMT29F8G08MBD MT29F4G08BAB_C MT29F8G08MAD MT29F8G08FACMT29F4G08AAA MT29F8G08FAB_C MT29F2G08AAD MT29F16G08CBABAMT29F8G08DAA MT29F8G08MAD MT29F2G08AAB MT29F32G08CBABAMT29F16G08MAA MT29F8G08AAA MT29F2G08ABB MT29F8G08BAAMT29F16G08MAA MT29F16G08DAA MT29F2G16AAB MT29F16G08FAAMT29F32G08QAA MT29F2G08ABC MT29F2G16ABBSDTNFCH-512 SDTNKGHSM-8192 SDMLC-1GB-I SDUNIHHSM-8192(16bit)SDTNFCH-1024 SDMLC-16384-I SDTNLLBHSM-32768 SDTNIHHSM-4096(16Bit)SDTNKGHSM-1024 SDTNKHHSM-16384 SANDISK-16384(43nm) SDTNKGHSM-4096(16bit) SDTNGBHE0-2048-I SDTNKHHSM-32768 SDTNIGHE0-4096 SDTNKHHSM-32768(16bit)SDTNGFHE0-2048 SDTNLJCHSM-2048 Sandisk-4GB(43nm) SDTNLLAHSM-1024(16bit) SDTNKGHSM-2048 SDTNLJCHSM-4096 SDTNLMBHSM-4096 SDTNKGHSM-2048(16bit)SDMLC-4GB-I SM90-256MB SDTNKLBHSM-2048 SDTNKJBHSM-8192(16bit)SDTNKGHSM-4096 SM90-256MB SDTNLLCHSM-1024 SDTNKGHSM-8192(16bit)SDTNLJCHSM-1024 SDTNIGHSM-2048 SDTNLLBHSM-4096 SDTNIGHSM-4096(16bit)SDUNIHHSM-8192 SDTNIGHSM-2048(16bit) SDMLC-1GB-I SDTNKHHSM-16384(16bit) SDTNIHHSM-4096 SDMLC-2GB-I SDTNKHHSM-16384(16bit)TC58NVG4D1DTG00 TC58NVG3D4CTG00 TC58DVG14B1FT00 TC58DVG02ATC58NVG4D2ETA00 TC58DVM72A1FT00 TC58NVG1D4BTG00 TC58DVM92ATH58NVG4D6CTG00 TC58DVM82A1FT00 TH58DVG24B1FT00 TC58NVG0S3CTA00TH58NVG6D1DTG20 TC58DVM92A1FT00 TC58NVG2D4BFT00 TC58NVM9S3BTG00TH58NVG5D2ETA20 TC58DVG02A1FT00 TH58NVG3D4BTG00 TC58NVG3D1DTG00(S)TH58NVG6D2ETA20 TC58NVG02A2FT00 TC58NVG3D4CTG10 TC58NVG6D1DTG00TH58NVG4T2DTG00 TC58NVG0S3BTG00 TH58NVG4D4CTG00 TC58NVG7D1DTG20TH58NVG6T2DTG20 TC58NVG1S3BTG00 TH58NVG5D4CTG20 TC58NVG2D1DTG00TH58NVG5D2ETA00 TH58NVG2S3BFT00 TC58NVG3D1DTG00 TC58NVG2D1DTG00TH58NVG5D1DTG00 TC58DVM94B1FT00 TH58NVG6D1DTG80 TC58NVG5D1DTG20TC58512FT TC58DVG04B1FT00 TC58NVG4D1DTG00工厂级U盘维修很多人打电话咨询U盘故障及数据恢复问题,现在把U盘的一些故障及排除方法归类一、硬件故障故障现象:U盘插在电脑里面什么反应都没有或是插上去在设备管理器的“通用串行总线控制器”里面能看到有新设备,但是我的电脑里面没有出现新盘符此类故障必须要懂电子的人才能搞定,至少要懂得焊接故障排除:重新焊好FLASH和主控,如果有新晶振也可以换掉试下,如果还不行就只有换主控IC了,总之,至少插在电脑里面要有新的盘符显示才算硬件基本正常(不是完全正常哦)。

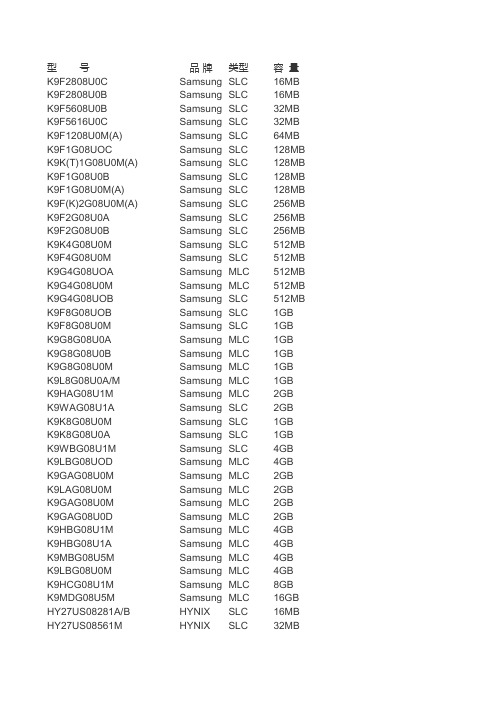

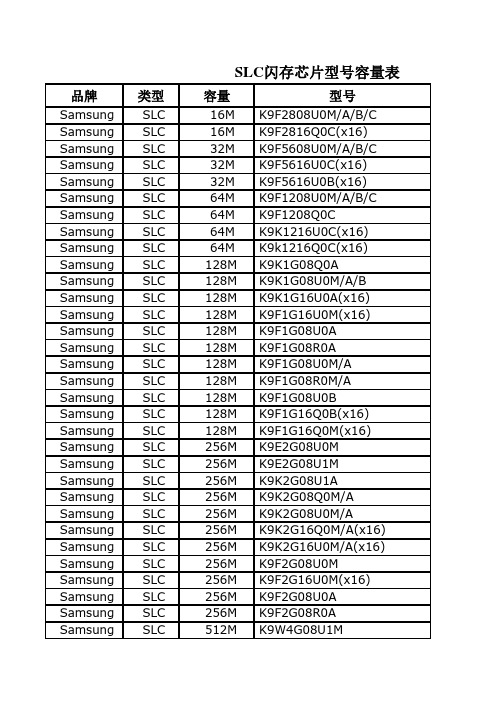

闪存型号容量对照

Toshiba

TC58512(A)FT

Toshiba

TC58DVM92A1FT

Toshiba

SLC SLC SLC MLC MLC MLC MLC SLC MLC SLC MLC MLC MLC MLC MLC MLC MLC SLC MLC MLC MLC SLC MLC MLC MLC MLC MLC MLC SLC MLC MLC MLC MLC MLC MLC MLC MLC SLC SLC SLC SLC SLC

HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX HYNIX Micron Micron Micron Micron Micron Micron Micron

容量 16MB 16MB 32MB 32MB 64MB 128MB 128MB 128MB 128MB 256MB 256MB 256MB 512MB 512MB 512MB 512MB 512MB 1GB 1GB 1GB 1GB 1GB 1GB 2GB 2GB 1GB 1GB 4GB 4GB 2GB 2GB 2GB 2GB 4GB 4GB 4GB 4GB 8GB 16GB 16MB 32MB

MLC SLC MLC SLC SLC MLC MLC MLC SLC SLC MLC MLC MLC MLC MLC MLC MLC MLC MLC MLC MLC

K9K8G08U0B-PCBO

K9K8G08U0BK9WAG08U1BINFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE.NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDEDON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.1. For updates or additional information about Samsung products, contact your nearest Samsung office.2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where Product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.* Samsung Electronics reserves the right to change products or specification without notice.Document Title1G x 8 / 2G x 8 Bit NAND Flash Memory Revision HistoryThe attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the rightto change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have any questions, please contact the SAMSUNG branch office near your office.Revision No0.00.1RemarkAdvance AdvanceHistory 1. Initial issue1. K9K8G08U0B-P is added.Draft DateJun. 11, 2008Jul. 10, 2008GENERAL DESCRIPTIONFEATURES• Voltage Supply- 3.3V (2.70V ~ 3.60V)• Organization- Memory Cell Array :- K9K8G08U0B : (1G + 32M) x 8bit - K9WAG08U1B : (2G + 64M) x 8bit - Data Register : (2K + 64) x 8bit • Automatic Program and Erase - Page Program : (2K + 64)Byte - Block Erase : (128K + 4K)Byte • Page Read Operation- Page Size : (2K + 64)Byte - Random Read : 25µs(Max.) - Serial Access : 25ns(Min.)1G x 8 / 2G x 8 Bit NAND Flash Memory• Fast Write Cycle Time- Page Program time : 200µs(Typ.) - Block Erase Time : 1.5ms(Typ.)• Command/Address/Data Multiplexed I/O Port • Hardware Data Protection- Program/Erase Lockout During Power Transitions • Reliable CMOS Floating-Gate Technology- Endurance : 100K Program/Erase Cycles (with 1bit/528Byte ECC)- Data Retention : 10 Years • Command Driven Operation• Unique ID for Copyright Protection • Package :- K9K8G08U0B-PCB0/PIB048 - Pin TSOP I (12 x 20 / 0.5 mm pitch) - K9WAG08U1B-PCB0/PIB048 - Pin TSOP I (12 x 20 / 0.5 mm pitch) - K9WAG08U1B-ICB0/IIB052 - Pin ULGA (12 x 17 / 1.0 mm pitch)Offered in 1G x 8bit, the K9K8G08U0B is a 8G-bit NAND Flash Memory with spare 256M-bit. And the K9WAG08U1B is a 16G-bit NAND Flash Memory with spare 512M-bit. Its NAND cell provides the most cost-effective solution for the solid state application mar-ket. A program operation can be performed in typical 200µs on the (2K+64)Byte page and an erase operation can be performed in typical 1.5ms on a (128K+4K)Byte block. Data in the data register can be read out at 25ns cycle time per Byte. The I/O pins serve as the ports for address and data input/output as well as command input. The on-chip write controller automates all program and erase functions including pulse repetition, where required, and internal verification and margining of data. Even the write-intensive systems can take advantage of the K9K8G08U0B/K9WAG08U1B ′s extended reliability of 100K program/erase cycles by providing ECC(Error Correcting Code) with real time mapping-out algorithm. The K9K8G08U0B/K9WAG08U1B is an optimum solution for large nonvola-tile storage applications such as solid state file storage and other portable applications requiring non-volatility.PRODUCT LISTPart Number Vcc RangeOrganizationPKG Type K9K8G08U0B-P 2.70 ~ 3.60VX8TSOP1K9WA G08U1B-P K9WA G08U1B-I52ULGA1.001.001.001.002.007 6 5 4 3 2 11.001.001.0012.00±0.10#A117.00±0.1017.00±0.10BA12.00±0.10(Datum B)(Datum A)12.0010.002.502.502.000.501.30A B C DEF GHJ K L M N12-∅1.00±0.0541-∅0.70±0.05Side View1.0(M a x .)0.10 C17.00±0.10Top ViewBottom ViewABC D EF G H J KL M N7654321K9WAG08U1B-ICB0/IIB052ULGA (measured in millimeters)NCNCNCNCNCNCNCNCNC NCNCNCNCNCNC NCVccVcc VssVssVss /RE1/RE2/CE1/CE2CLE1CLE2ALE1ALE2/WE1/WE2/WP1/WP2R/B1R/B2VssIO0-1IO0-2IO1-1IO1-2IO2-1IO3-1IO2-2IO3-2IO4-1IO4-2IO5-1IO5-2IO6-1IO6-2IO7-1IO7-2∅ABC M 0.1∅ABC M 0.1PACKAGE DIMENSIONSPIN DESCRIPTIONNOTE : Connect all V CC and V SS pins of each device to common power supply outputs. Do not leave V CC or V SS disconnected.Pin Name Pin FunctionI/O 0 ~ I/O 7DATA INPUTS/OUTPUTSThe I/O pins are used to input command, address and data, and to output data during read operations. The I/O pins float to high-z when the chip is deselected or when the outputs are disabled.CLECOMMAND LATCH ENABLEThe CLE input controls the activating path for commands sent to the command register. When active high, commands are latched into the command register through the I/O ports on the rising edge of the WE signal.ALEADDRESS LATCH ENABLEThe ALE input controls the activating path for address to the internal address registers. Addresses are latched on the rising edge of WE with ALE high.CE / CE1CHIP ENABLEThe CE / CE1 input is the device selection control. When the device is in the Busy state, CE / CE1 high is ignored, and the device does not return to standby mode in program or erase operation.Regarding CE / CE1 control during read operation , refer to ’Page Read’ section of Device operation. CE2CHIP ENABLEThe CE2 input enables the second of K9WAG08U1B.REREAD ENABLEThe RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE which also increments the internal column address counter by one.WEWRITE ENABLEThe WE input controls writes to the I/O port. Commands, address and data are latched on the rising edge of the WE pulse.WPWRITE PROTECTThe WP pin provides inadvertent program/erase protection during power transitions. The internal high volt-age generator is reset when the WP pin is active low.R/B / R/B1READY/BUSY OUTPUTThe R/B / R/B1 output indicates the status of the device operation. When low, it indicates that a program, erase or random read operation is in process and returns to high state upon completion. It is an open drain output and does not float to high-z condition when the chip is deselected or when outputs are disabled.Vcc POWERV CC is the power supply for device. Vss GROUNDN.CNO CONNECTIONLead is not internally connected.Product IntroductionThe K9K8G08U0B has a 8,448Mbit(8,858,370,048 bit) memory organized as 524,288 rows(pages) by 2,112x8 columns. Spare 64x8 columns are located from column address of 2,048~2,111. A 2,112-byte data register is connected to memory cell arrays accommo-dating data transfer between the I/O buffers and memory during page read and page program operations. The memory array is made up of 32 cells that are serially connected to form a NAND structure. Each of the 32 cells resides in a different page. A block consists of two NAND structured strings. A NAND structure consists of 32 cells. Total 1,081,344 NAND cells reside in a block. The program and read operations are executed on a page basis, while the erase operation is executed on a block basis. The memory array con-sists of 8,192 separately erasable 128K-byte blocks. It indicates that the bit by bit erase operation is prohibited on the K9K8G08U0B. The K9K8G08U0B has addresses multiplexed into 8 I/Os. This scheme dramatically reduces pin counts and allows system upgrades to future densities by maintaining consistency in system board design. Command, address and data are all written through I/O's by bringing WE to low while CE is low. Those are latched on the rising edge of WE. Command Latch Enable(CLE) and Address Latch Enable(ALE) are used to multiplex command and address respectively, via the I/O pins. Some commands require one bus cycle. For example, Reset Command, Status Read Command, etc require just one cycle bus. Some other commands, like page read and block erase and page program, require two cycles: one cycle for setup and the other cycle for execution. The 1,056M byte physical space requires 31 addresses, thereby requiring five cycles for addressing : 2 cycles of column address, 3 cycles of row address, in that order. Page Read and Page Program need the same five address cycles following the required command input. In Block Erase oper-ation, however, only the three row address cycles are used. Device operations are selected by writing specific commands into the command register. Table 1 defines the specific commands of the K9K8G08U0B.In addition to the enhanced architecture and interface, the device incorporates copy-back program feature from one page to another page without need for transporting the data to and from the external buffer memory. Since the time-consuming serial access and data-input cycles are removed, system performance for solid-state disk application is significantly increased.The K9WAG08U1B is composed of two K9K8G08U0B chips which are selected separately by each CE1 and CE2.Table 1. Command SetsFunction1st Cycle2nd Cycle Acceptable Command during Busy Read 00h30hRead for Copy Back00h35hRead ID90h-Reset FFh-OPage Program80h10hTwo-Plane Page Program(3)80h---11h81h---10hCopy-Back Program85h10hTwo-Plane Copy-Back Program(3)85h---11h81h---10hBlock Erase60h D0hTwo-Plane Block Erase60h---60h D0hRandom Data Input(1)85h-Random Data Output(1)05h E0hRead Status70h OChip1 Status(2)F1h OChip2 Status(2)F2h ONOTE : 1. Random Data Input/Output can be executed in a page.2. Interleave-operation between two chips is allowed.It’s prohibited to use F1h and F2h commands for other operations except interleave-operation.3.Any command between 11h and 81h is prohibited except 70h, F1h, F2h and FFh .Caution : Any undefined command inputs are prohibited except for above command set of Table 1.DC AND OPERATING CHARACTERISTICS (Recommended operating conditions otherwise noted.)NOTE : 1. V IL can undershoot to -0.4V and V IH can overshoot to V CC +0.4V for durations of 20 ns or less. 2. Typical value is measured at Vcc=3.3V, T A =25°C. Not 100% tested.3. The maximum value of K9K8G08U0B -P’s I LI and I LO is ±40µA , the maximum value of K9K8G08U0B -I’s I LI and I LO is ±20µA .ParameterSymbol Test ConditionsMinTypMaxUnitOperating CurrentPage Read withSerial Access I CC 1tRC=25nsCE=V IL, I OUT =0mA-2535mAProgramI CC 2-EraseI CC 3-Stand-by Current(TTL)I SB 1CE=V IH , WP=0V/V CC --1Stand-by Current(CMOS)I SB 2CE=V CC -0.2, WP=0V/V CC -40200µAInput Leakage Current I LI V IN =0 to Vcc(max)--±40Output Leakage Current I LO V OUT =0 to Vcc(max)--±40Input High VoltageV IH (1)-0.8xVcc -Vcc+0.3V Input Low Voltage, All inputs V IL (1)--0.3-0.2xVccOutput High Voltage Level V OH I OH =-400µA 2.4--Output Low Voltage Level V OL I OL =2.1mA --0.4Output Low Current(R/B)I OL (R/B)V OL =0.4V810-mA RECOMMENDED OPERATING CONDITIONS(Voltage reference to GND, K9XXG08UXB-XCB0 :T A =0 to 70°C, K9XXG08UXB-XIB0:T A =-40 to 85°C)ParameterSymbol Min Typ.Max Unit Supply Voltage V CC 2.7 3.3 3.6V Supply VoltageV SSVABSOLUTE MAXIMUM RATINGSNOTE :1. Minimum DC voltage is -0.6V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <30ns. Maximum DC voltage on input/output pins is V CC +0.3V which, during transitions, may overshoot to V CC +2.0V for periods <20ns.2. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.ParameterSymbol Rating Unit Voltage on any pin relative to VSSV CC -0.6 to +4.6VV IN -0.6 to +4.6V I/O-0.6 to Vcc+0.3 (<4.6V)Temperature Under Bias K9XXG08UXB-XCB0T BIAS -10 to +125°C K9XXG08UXB-XIB0-40 to +125Storage Temperature K9XXG08UXB-XCB0T STG-65 to +150°CK9XXG08UXB-XIB0Short Circuit CurrentI OS5mACAPACITANCE (T A =25°C, V CC =3.3V, f=1.0MHz)NOTE : Capacitance is periodically sampled and not 100% tested. K9WAG08U1B-IXB0’s capacitance(I/O, Input) is 20pF.ItemSymbol Test ConditionMin MaxUnitK9K8G08U0BK9WAG08U1B*Input/Output Capacitance C I/O V IL =0V -2040pF Input CapacitanceC INV IN =0V-2040pF VALID BLOCKNOTE :1. The device may include initial invalid blocks when first shipped. Additional invalid blocks may develop while being used. The number of valid blocks is presented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits. Do not erase or pro-gram factory-marked bad blocks. Refer to the attached technical notes for appropriate management of invalid blocks.2. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block up to 1K program/erase cycles with 1bit/528Byte ECC.3. The number of valid block is on the basis of single plane operations, and this may be decreased with two plane operations.* : Each K9K8G08U0B chip in the K9WAG08U1B has Maximun 160 invalid blocks.Parameter Symbol Min Typ.Max Unit K9K8G08U0B N VB8,028-8,192BlocksK9WAG08U1B16,064*-16,384*AC TEST CONDITION(K9XXG08UXB-XCB0: T A =0 to 70°C, K9XXG08UXB-XIB0:T A =-40 to 85°C ,K9XXG08UXB: Vcc=2.7V~3.6V unless otherwise noted)ParameterK9WAG08U1B Input Pulse Levels 0V to Vcc Input Rise and Fall Times 5ns Input and Output Timing Levels Vcc/2Output Load1 TTL GATE and CL=50pF (K9K8G08U0B-P/K9WAG08U1B-I)1 TTL GATE and CL=30pF (K9WAG08U1B-P)MODE SELECTIONNOTE : 1. X can be V IL or V IH.2. WP should be biased to CMOS high or CMOS low for standby.CLE ALE CE WERE WP ModeH L L H X Read Mode Command Input L H L H X Address Input(5clock)H L L H H Write Mode Command Input L H L H H Address Input(5clock)L L L HH Data Input L L L H X Data Output X X X X H X During Read(Busy)X X X X X H During Program(Busy)X X X X X H During Erase(Busy)X X (1)X X X L Write Protect XXHXX0V/V CC (2)Stand-byProgram / Erase CharacteristicsParameter Symbol Min Typ Max Unit Program Time t PROG-200700µs Dummy Busy Time for Two-Plane Page Program t DBSY-0.51µs Number of Partial Program Cycles Nop--4cycles Block Erase Time t BERS- 1.52msNOTE : 1. Typical value is measured at Vcc=3.3V, T A=25°C. Not 100% tested.2. Typical program time is defined as the time within which more than 50% of the whole pages are programmed at3.3V Vcc and 25°C tempera-ture.AC Timing Characteristics for Command / Address / Data InputParameter Symbol Min Max UnitCLE Setup Time t CLS(1)12-nsCLE Hold Time t CLH5-nsCE Setup Time t CS(1)20-nsCE Hold Time t CH5-nsWE Pulse Width t WP12-nsALE Setup Time t ALS(1)12-nsALE Hold Time t ALH5-nsData Setup Time t DS(1)12-nsData Hold Time t DH5-nsWrite Cycle Time t WC25-nsWE High Hold Time t WH10-nsAddress to Data Loading Time t ADL(2)70-nsNOTES : 1. The transition of the corresponding control pins must occur only once while WE is held low.2. tADL is the time from the WE rising edge of final address cycle to the WE rising edge of first data cycle.AC Characteristics for OperationParameter Symbol Min Max Unit Data Transfer from Cell to Register t R-25µs ALE to RE Delay t AR10-ns CLE to RE Delay t CLR10-ns Ready to RE Low t RR20-ns RE Pulse Width t RP12-ns WE High to Busy t WB-100ns Read Cycle Time t RC25-ns RE Access Time t REA-20ns CE Access Time t CEA-25ns RE High to Output Hi-Z t RHZ-100ns CE High to Output Hi-Z t CHZ-30ns RE High to Output hold t RHOH15-ns RE Low to Output hold t RLOH5-ns CE High to Output hold t COH15-ns RE High Hold Time t REH10-ns Output Hi-Z to RE Low t IR0-ns RE High to WE Low t RHW100-ns WE High to RE Low t WHR60-ns Device Resetting Time(Read/Program/Erase)t RST-5/10/500(1)µs NOTE: 1. If reset command(FFh) is written at Ready state, the device goes into Busy for maximum 5µs.NAND Flash Technical NotesIdentifying Initial Invalid Block(s)Initial Invalid Block(s)Initial invalid blocks are defined as blocks that contain one or more initial invalid bits whose reliability is not guaranteed by Samsung.The information regarding the initial invalid block(s) is called the initial invalid block information. Devices with initial invalid block(s)have the same quality level as devices with all valid blocks and have the same AC and DC characteristics. An initial invalid block(s)does not affect the performance of valid block(s) because it is isolated from the bit line and the common source line by a select tran-sistor. The system design must be able to mask out the initial invalid block(s) via address mapping. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block up to 1K program/erase cycles with 1bit /528Byte ECC.All device locations are erased(FFh) except locations where the initial invalid block(s) information is written prior to shipping. The ini-tial invalid block(s) status is defined by the 1st byte in the spare area. Samsung makes sure that either the 1st or 2nd page of every initial invalid block has non-FFh data at the column address of 2,048. Since the initial invalid block information is also erasable in most cases, it is impossible to recover the information once it has been erased. Therefore, the system must be able to recognize the initial invalid block(s) based on the original initial invalid block information and create the initial invalid block table via the following suggested flow chart(Figure 3). Any intentional erasure of the original initial invalid block information is prohibited.*Check "FFh" at the column address 2,048 Figure 3. Flow chart to create initial invalid block table.StartSet Block Address = 0Check "FFh"Increment Block AddressLast Block ?EndNoYesYesCreate (or update)NoInitialof the 1st and 2nd page in the blockInvalid Block(s) TableNAND Flash Technical Notes (Continued)Program Flow ChartStartI/O 6 = 1 ?I/O 0 = 0 ?No*Write 80hWrite AddressWrite DataWrite 10hRead Status RegisterProgram Completedor R/B = 1 ?Program ErrorYesNoYes: If program operation results in an error, map out the block including the page in error and copy thetarget data to another block.*Error in write or read operationWithin its life time, additional invalid blocks may develop with NAND Flash memory. Refer to the qualification report for the actual data.The following possible failure modes should be considered to implement a highly reliable system. In the case of status read fail-ure after erase or program, block replacement should be done. Because program status fail during a page program does not affect the data of the other pages in the same block, block replacement can be executed with a page-sized buffer by finding an erased empty block and reprogramming the current target data and copying the rest of the replaced block. In case of Read, ECC must be employed. To improve the efficiency of memory space, it is recommended that the read or verification failure due to single bit error be reclaimed by ECC without any block replacement. The said additional block failure rate does not include those reclaimed blocks.Failure ModeDetection and Countermeasure sequenceWrite Erase Failure Status Read after Erase --> Block Replacement Program Failure Status Read after Program --> Block Replacement ReadSingle Bit FailureVerify ECC -> ECC CorrectionECC: Error Correcting Code --> Hamming Code etc. Example) 1bit correction & 2bit detectionInterleave Page ProgramK9WAG08U1B is composed of two K9K8G08U0Bs. And K9K8G08U0B also is composed of two K9F4G08U0Bs. K9K8G08U0B pro-vides interleaving operation between two K9F4G08U0Bs.This interleaving page program improves the system throughput almost twice compared to non-interleaving page program.At first, the host issues page program command to one of the K9F4G08U0B chips, say K9F4G08U0B(chip #1). Due to this K9K8G08U0B goes into busy state. During this time, K9F4G08U0B(chip #2) is in ready state. So it can execute the page program command issued by the host.After the execution of page program by K9F4G08U0B(chip #1), it can execute another page program regardless of the K9F4G08U0B(chip #2). Before that the host needs to check the status of K9F4G08U0B(chip #1) by issuing F1h command. Only when the status of K9F4G08U0B(chip #1) becomes ready status, host can issue another page program command. If the K9F4G08U0B(chip #1) is in busy state, the host has to wait for the K9F4G08U0B(chip #1) to get into ready state.Similarly, K9F4G08U0B chip(chip #2) can execute another page program after the completion of the previous program. The host can monitor the status of K9F4G08U0B(chip #2) by issuing F2h command. When the K9F4G08U0B(chip #2) shows ready state, host can issue another page program command to K9F4G08U0B(chip #2).This interleaving algorithm improves the system throughput almost twice. The host can issue page program command to each chip individually. This reduces the time lag for the completion of operation.NOTES : During interleave operations, 70h command is prohibited.R / B (#1)b u s y o f C h i p #1I /O X80h10h C o m m a n d A 30 : L o w A d d & D a t a80h 10h A 30 : H i g h A d d & D a t ab u s y o f C h i p #2i n t e r n a l o n l yR /B (#2)i n t e r n a l o n l yR /BI n t e r l e a v e P a g e P r o g r a m≈≈≈F 1h o r F 2h A B CDa n o t h e r p a g e p r o g r a m o n C h i p #1S t a t e A : C h i p #1 i s e x e c u t i n g a p a g e p r o g r a m o p e r a t i o n a n d c h i p #2 i s i n r e a d y s t a t e . S o t h e h o s t c a n i s s u e a p a g e p r o g r a m c o m m a n d t o c h i p #2.S t a t e B : B o t h c h i p #1 a n d c h i p #2 a r e e x e c u t i n g p a g e p r o g r a m o p e r a t i o n .S t a t e C : P a g e p r o g r a m o n c h i p #1 i s t e r m i n a t e d , b u t p a g e p r o g r a m o n c h i p #2 i s s t i l l o p e r a t i n g . A n d t h e s y s t e m s h o u l d i s s u e F 1h c o m m a n d t o d e t e c t t h e s t a t u s o f c h i p #1. I f c h i p #1 i s r e a d y , s t a t u s I /O 6 i s "1" a n d t h e s y s t e m c a n i s s u e a n o t h e r p a g e p r o g r a m c o m m a n d t o c h i p #1.S t a t e D : C h i p #1 a n d C h i p #2 a r e r e a d y .A c c o r d i n g t o t h e a b o v e p r o c e s s , t h e s y s t e m c a n o p e r a t e p a g e p r o g r a m o n c h i p #1 a n d c h i p #2 a l t e r n a t e l y .S t a t u sO p e r a t i o nS t a t u s C o m m a n d / D a t aF 1hF 2hAC h i p 1 : B u s y , C h i p 2 : R e a d y8x hC x hBC h i p 1 : B u s y , C h i p 2 : B u s y8x h8x hCC h i p 1 : R e a d y , C h i p 2 : B u s yC x h8x hDC h i p 1 : R e a d y , C h i p 2 : R e a d yC x hC x hR / B (#1)b u s y o f C h i p #1I /O X60hD 0h C o m m a n d A 30 : L o w A d d60h D 0h A 30 : H i g h A d db u s y o f C h i p #2i n t e r n a l o n l yR /B (#2)i n t e r n a l o n l yR /BI n t e r l e a v e B l o c k E r a s e≈≈≈F 1h o r F 2h A B CDa n o t h e r B l o c k E r a s e o n C h i p #1S t a t e A : C h i p #1 i s e x e c u t i n g a b l o c k e r a s e o p e r a t i o n , a n d c h i p #2 i s i n r e a d y s t a t e . S o t h e h o s t c a n i s s u e a b l o c k e r a s e c o m m a n d t o c h i p #2.S t a t e B : B o t h c h i p #1 a n d c h i p #2 a r e e x e c u t i n g b l o c k e r a s e o p e r a t i o n .S t a t e C : B l o c k e r a s e o n c h i p #1 i s t e r m i n a t e d , b u t b l o c k e r a s e o n c h i p #2 i s s t i l l o p e r a t i n g . A n d t h e s y s t e m s h o u l d i s s u e F 1h c o m m a n d t o d e t e c t t h e s t a t u s o f c h i p #1. I f c h i p #1 i s r e a d y , s t a t u s I /O 6 i s "1" a n d t h e s y s t e m c a n i s s u e a n o t h e r b l o c k e r a s e c o m m a n d t o c h i p #1.S t a t e D : C h i p #1 a n d C h i p #2 a r e r e a d y .A c c o r d i n g t o t h e a b o v e p r o c e s s , t h e s y s t e m c a n o p e r a t e b l o c k e r a s e o n c h i p #1 a n d c h i p #2 a l t e r n a t e l y .S t a t u sO p e r a t i o nS t a t u s C o m m a n d / D a t aF 1hF 2hAC h i p 1 : B u s y , C h i p 2 : R e a d y8x hC x hBC h i p 1 : B u s y , C h i p 2 : B u s y8x h8x hCC h i p 1 : R e a d y , C h i p 2 : B u s yC x h8x hDC h i p 1 : R e a d y , C h i p 2 : R e a d yC x hC x hR /B (#1)I /O XC o m m a n dt B E R S o f c h i p #1i n t e r n a l o n l yR /B (#2)i n t e r n a l o n l yR /B60h D 0h A 30 :L o w A d d 60hA 30 : L o wA d d F 1h o r F 2h *60h D 0hA 30 :H i g h A d d60h A 30 : H i g h A d d t B E R S o f c h i p #2t B E R S o f c h i p #211I n t e r l e a v e T w o -P l a n e B l o c k E r a s eR /B (#1)I /O Xi n t e r n a l o n l yR /B (#2)i n t e r n a l o n l yR /B≈≈≈ABCS t a t e A : C h i p #1 i s e x e c u t i n g a b l o c k e r a s e o p e r a t i o n , a n d c h i p #2 i s i n r e a d y s t a t e . S o t h e h o s t c a n i s s u e a b l o c k e r a s e c o m m a n d t o c h i p #2.S t a t e B : B o t h c h i p #1 a n d c h i p #2 a r e e x e c u t i n g b l o c k e r a s e o p e r a t i o n .S t a t e C : B l o c k e r a s e o n c h i p #1 i s c o m p l e t e d a n d c h i p #1 i s r e a d y f o r t h e n e x t o p e r a t i o n . C h i p #2 i s s t i l l e x e c u t i n g b l o c k e r a s e o p e r a t i o n .S t a t e D : B o t h c h i p #1 a n d c h i p #2 a r e r e a d y .N o t e : *F 1h c o m m a n d i s r e q u i r e d t o c h e c k t h e s t a t u s o f c h i p #1 t o i s s u e t h e n e x t b l o c k e r a s e c o m m a n d t o c h i p #1. F 2h c o m m a n d i s r e q u i r e d t o c h e c k t h e s t a t u s o f c h i p #2 t o i s s u e t h e n e x t b l o c k e r a s e c o m m a n d t o c h i p #2.A s t h e a b o v e p r o c e s s , t h e s y s t e m c a n o p e r a t e t w o -p l a n e b l o c k e r a s e o n c h i p #1 a n d c h i p #2 a l t e r n a t i v e l y .DRead ID OperationCECLEWEALERE90hRead ID CommandMaker Code Device Code00h ECht REAAddress 1cycleI/Oxt ARDevice Device Code(2nd Cycle)3rd Cycle 4th Cycle 5th Cycle K9K8G08U0B DCh51h95h58hK9WAG08U1BSame as K9K8G08U0BDevice 4th cyc.Code3rd cyc.5th cyc.。

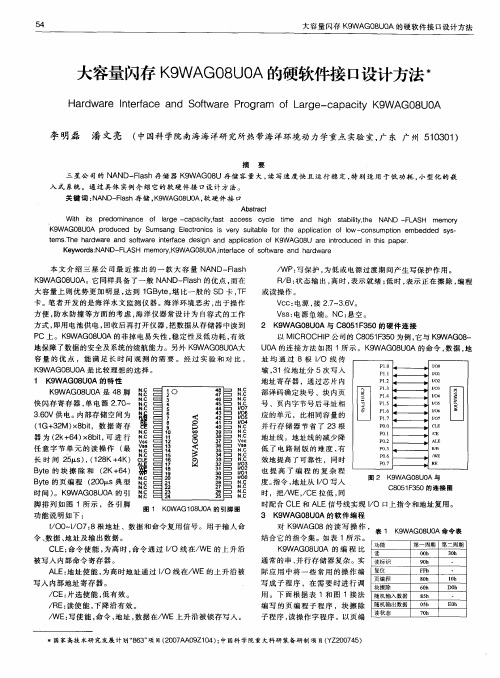

大容量闪存K9WAG08U0A的硬软件接口设计方法

/ P写保护 , W : 为低 或 电源 过 渡 期 间产 生写 保 护 作 用 。 R B: 态 输 出 , 时 , 示 就 绪 ; 时 , 示 正 在 擦 除 , 程 / 状 高 表 低 表 编

.

糟

Ke wor : y dsNAND—F ASH L memor , W AGO8U0 it ra fs t y K9 A. e fce o of n war d ar e an h dwar e

般 隧

陡隧

本 文 介 绍 三 星 公 司 最 近 推 出 的 一 款 大 容 量 N D— l h AN F s a

李 明磊 潘 文 亮 ( 中国科 学院南海海洋研 究所热带海洋环境动力学重点实验 室, 广东 广州 5 00 ) 13 1

摘 要

三 星公 司 的 N D- ls AN F h存 储 器 K WA 8 存 储 容 量 大 , 写 速 度 快 且 运 行 稳 定 , 别 适 用 于 低 功 耗 , 型 化 的 嵌 a 9 G0 U 读 特 小

大 容量 闪存 K W A 0 U A 的 硬软 件 接 口设 计方 法 9 G8O

大容量闪存 K WA 0 U A的硬软件接 I设计方法 9 G 8O : 1

Ha d r wa e It r c n o t r o a r nef e a d S f a wa e Pr gr m f L r e — a a i W AG0 UO o a g — p ct K9 c y 8 A

K9F4G08U0M中文资料

NC

NC

NC

NC

NC

NC

7

NC

/RE1 R/B2 IO7-2 IO6-2 IO5-2

NC

6

Vcc

/RE2 Vss

IO7-1 IO5-1

Vcc

5

4

/CE1 /CE2

R/B1 /WP2 IO6-1

IO4-1 IO4-2

3

CLE1 CLE2 /WE1

IO0-1 IO2-1

A B

0.65(Max.)

12-∅1.00±0.05

∅0.1 M C AB

Side View

17.00±0.10

41-∅0.70±0.05

∅0.1 M C AB

0.10 C

4

元器件交易网

K9K8G08U1M K9F4G08U0M

Advance FLASH MEMORY

K9K8G08U1M-ICB0/IIB0

12.00±0.10

#A1

17.00±0.10

(Datum A)

A B C D (Datum B) E F G H J K L M N

Bottom View

12.00±0.10

2.00

10.00

1.00

1.00

7 6 54 3 2 1

1.00

1.00

1.00

0.50

1.00

1.00

1.30

2.00 2.50 2.50

1

元器件交易网

K9K8G08U1M K9F4G08U0M

512M x 8 Bit / 1G x 8 Bits NAND Flash Memory

SMI主控FLASH支持列表

64Gbit 128Gbit 32Gbit 64Gbit

32Gbit

8G bit

32G bit 16G bit 16G bit 32Gbit 64Gbit 32Gbit 64Gbit 128Gbit 32G bit 64G bit 128G bit 32GB 128G bit 64G bit 128G bit 64G bit 64G bit 64G bit 64G bit 32G bit 32G bit 32G bit 32G bit 32G bit 32G bit 16G bit 16G bit 16G bit 16G bit 16G bit 16G bit 16G bit 8G bit 8G bit 8G bit 8G bit 8G bit 4G bit 4G bit 4G bit 2G bit 64G bit 32G bit 32G bit 32G bit 16G bit 16G bit 16G bit

Y

Y

Y

1CE 4b/512B

60nm

Y

Y

Y

2CE 4b/512B

90nm

Y

Y

Y

M 1CE 4b/512B

59nm

Y

Y

Y

S1CE 4b/512B

51nm

Y

Y

Y

Y

Y

Y

Y

N

N

N

N

N

N

N

Y

N

Y

N

Y

N

Y

N

N

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

K9WAG08U1M中文资料

K9XXG08UXMINFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE.NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDEDON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.1. For updates or additional information about Samsung products, contact your nearest Samsung office.2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where Product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.* Samsung Electronics reserves the right to change products or specification without notice.Document Title1G x 8 Bit / 2G x 8 Bit NAND Flash Memory Revision HistoryThe attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the rightto change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have any questions, please contact the SAMSUNG branch office near your office.Revision No0.00.10.2RemarkAdvance Advance PreliminaryHistory1. Initial issue1. Technical note is changedDraft DateMar. 1st. 2005Apr. 1st. 2005May 3rd. 2005GENERAL DESCRIPTIONFEATURES• Voltage Supply - 2.70V ~ 3.60V • Organization- Memory Cell Array : (1G + 32M) x 8bit - Data Register : (2K + 64) x 8bit • Automatic Program and Erase - Page Program : (2K + 64)Byte - Block Erase : (128K + 4K)Byte • Page Read Operation- Page Size : (2K + 64)Byte - Random Read : 20µs(Max.) - Serial Access : 25ns(Min.)1G x 8 Bit / 2G x 8 Bit NAND Flash Memory• Fast Write Cycle Time- Page Program time : 200µs(Typ.) - Block Erase Time : 1.5ms(Typ.)• Command/Address/Data Multiplexed I/O Port • Hardware Data Protection- Program/Erase Lockout During Power Transitions • Reliable CMOS Floating-Gate Technology- Endurance : 100K Program/Erase Cycles (with 1bit/512Byte ECC)- Data Retention : 10 Years • Command Driven Operation• Intelligent Copy-Back with internal 1bit/528Byte EDC • Unique ID for Copyright Protection • Package :- K9K8G08U0M-YCB0/YIB048 - Pin TSOP I (12 x 20 / 0.5 mm pitch)- K9K8G08U0M-PCB0/PIB0 : Pb-FREE PACKAGE 48 - Pin TSOP I (12 x 20 / 0.5 mm pitch) - K9WAG08U1M-YCB0/YIB048 - Pin TSOP I (12 x 20 / 0.5 mm pitch)- K9WAG08U1M-PCB0/PIB0 : Pb-FREE PACKAGE 48 - Pin TSOP I (12 x 20 / 0.5 mm pitch) - K9WAG08U1M-ICB0/IIB052 - Pin TLGA (12 x 17 / 1.0 mm pitch)Offered in 1G x 8bit, the K9K8G08U0M is a 8G-bit NAND Flash Memory with spare 256M-bit. Its NAND cell provides the most cost-effective solution for the solid state application market. A program operation can be performed in typical 200µs on the (2K+64)Byte page and an erase operation can be performed in typical 1.5ms on a (128K+4K)Byte block. Data in the data register can be read out at 25ns cycle time per Byte. The I/O pins serve as the ports for address and data input/output as well as command input. The on-chip write controller automates all program and erase functions including pulse repetition, where required, and internal verification and margining of data. Even the write-intensive systems can take advantage of the K9K8G08U0M ′s extended reliability of 100K program/erase cycles by providing ECC(Error Correcting Code) with real time mapping-out algorithm. The K9K8G08U0M is an optimum solu-tion for large nonvolatile storage applications such as solid state file storage and other portable applications requiring non-volatility. An ultra high density solution having two 8Gb stacked with two chip selects is also available in standard TSOPI package.PRODUCT LISTPart NumberVcc RangeOrganizationPKG Type K9K8G08U0M-Y ,P 2.70 ~ 3.60VX8TSOP1 K9WA G08U1M-Y ,P K9WA G08U1M-I52TLGA1.001.001.001.002.007 6 5 4 3 2 11.001.001.0012.00±0.10#A117.00±0.1017.00±0.10BA12.00±0.10(Datum B)(Datum A)12.0010.002.502.502.000.501.30A B C DEF GHJ K L M N12-∅1.00±0.0541-∅0.70±0.05Side View1.0(M a x .)0.10 C17.00±0.10Top ViewBottom ViewABC D EF G H J KL M N7654321K9WAG08U1M - ICB0 / IIB052-TLGA (measured in millimeters)NCNCNCNCNCNCNCNCNC NCNCNCNCNCNC NCVccVcc VssVssVss /RE1/RE2/CE1/CE2CLE1CLE2ALE1ALE2/WE1/WE2/WP1/WP2R/B1R/B2VssIO0-1IO0-2IO1-1IO1-2IO2-1IO3-1IO2-2IO3-2IO4-1IO4-2IO5-1IO5-2IO6-1IO6-2IO7-1IO7-2∅ABC M 0.1∅ABC M 0.1PACKAGE DIMENSIONSPIN DESCRIPTIONNOTE : Connect all V CC and V SS pins of each device to common power supply outputs. Do not leave V CC or V SS disconnected.Pin Name Pin FunctionI/O 0 ~ I/O 7DATA INPUTS/OUTPUTSThe I/O pins are used to input command, address and data, and to output data during read operations. The I/O pins float to high-z when the chip is deselected or when the outputs are disabled.CLECOMMAND LATCH ENABLEThe CLE input controls the activating path for commands sent to the command register. When active high, commands are latched into the command register through the I/O ports on the rising edge of the WE signal.ALEADDRESS LATCH ENABLEThe ALE input controls the activating path for address to the internal address registers. Addresses are latched on the rising edge of WE with ALE high.CE / CE1CHIP ENABLEThe CE / CE1 input is the device selection control. When the device is in the Busy state, CE / CE1 high is ignored, and the device does not return to standby mode in program or erase operation.Regarding CE / CE1 control during read operation , refer to ’Page Read’ section of Device operation. CE2CHIP ENABLEThe CE2 input enables the second K9K8G08U0MREREAD ENABLEThe RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE which also increments the internal column address counter by one.WEWRITE ENABLEThe WE input controls writes to the I/O port. Commands, address and data are latched on the rising edge of the WE pulse.WPWRITE PROTECTThe WP pin provides inadvertent program/erase protection during power transitions. The internal high volt-age generator is reset when the WP pin is active low.R/B / R/B1READY/BUSY OUTPUTThe R/B / R/B1 output indicates the status of the device operation. When low, it indicates that a program, erase or random read operation is in process and returns to high state upon completion. It is an open drain output and does not float to high-z condition when the chip is deselected or when outputs are disabled.Vcc POWERV CC is the power supply for device. Vss GROUNDN.CNO CONNECTIONLead is not internally connected.Product IntroductionThe K9K8G08U0M is a 8,448Mbit(8,858,370,048 bit) memory organized as 524,288 rows(pages) by 2,112x8 columns. Spare 64x8 columns are located from column address of 2,048~2,111. A 2,112-byte data register is connected to memory cell arrays accommo-dating data transfer between the I/O buffers and memory during page read and page program operations. The memory array is made up of 32 cells that are serially connected to form a NAND structure. Each of the 32 cells resides in a different page. A block consists of two NAND structured strings. A NAND structure consists of 32 cells. Total 1,081,344 NAND cells reside in a block. The program and read operations are executed on a page basis, while the erase operation is executed on a block basis. The memory array con-sists of 8,192 separately erasable 128K-byte blocks. It indicates that the bit by bit erase operation is prohibited on the K9K8G08U0M. The K9K8G08U0M has addresses multiplexed into 8 I/Os. This scheme dramatically reduces pin counts and allows system upgrades to future densities by maintaining consistency in system board design. Command, address and data are all written through I/O's by bringing WE to low while CE is low. Those are latched on the rising edge of WE. Command Latch Enable(CLE) and Address Latch Enable(ALE) are used to multiplex command and address respectively, via the I/O pins. Some commands require one bus cycle. For example, Reset Command, Status Read Command, etc require just one cycle bus. Some other commands, like page read and block erase and page program, require two cycles: one cycle for setup and the other cycle for execution. The 1056M byte physical space requires 31 addresses, thereby requiring five cycles for addressing : 2 cycles of column address, 3 cycles of row address, in that order. Page Read and Page Program need the same five address cycles following the required command input. In Block Erase oper-ation, however, only the three row address cycles are used. Device operations are selected by writing specific commands into the command register. Table 1 defines the specific commands of the K9K8G08U0M.In addition to the enhanced architecture and interface, the device incorporates copy-back program feature from one page to another page without need for transporting the data to and from the external buffer memory. Since the time-consuming serial access and data-input cycles are removed, system performance for solid-state disk application is significantly increased.The K9WAG08U1M is composed of two K9K8G08U0M chips which are selected separately by each CE1 and CE2. Therefore, in terms of each CE, the basic operation of K9WAG08U1M is same with K9K8G08U0M except some AC/DC charateristics.Table 1. Command SetsFunction1st Cycle2nd Cycle Acceptable Command during Busy Read 00h30hRead for Copy Back00h35hRead ID90h-Reset FFh-OPage Program80h10hTwo-Plane Page Program(4)80h---11h81h---10hCopy-Back Program85h10hTwo-Plane Copy-Back Program(4)85h---11h81h---10hBlock Erase60h D0hTwo-Plane Block Erase60h---60h D0hRandom Data Input(1)85h-Random Data Output(1)05h E0hRead Status70h ORead EDC Status(2)7Bh OChip1 Status(3)F1h OChip2 Status(3)F2h ONOTE : 1. Random Data Input/Output can be executed in a page.2. Read EDC Status is only available on Copy Back operation.3. Interleave-operation between two chips is allowed.It’s prohibited to use F1h and F2h commands for other operations except interleave-operation.4.Any command between 11h and 81h is prohibited except 70h, F1h, F2h and FFh .Caution : Any undefined command inputs are prohibited except for above command set of Table 1.DC AND OPERATING CHARACTERISTICS (Recommended operating conditions otherwise noted.)NOTE : 1. V IL can undershoot to -0.4V and V IH can overshoot to V CC +0.4V for durations of 20 ns or less. 2. Typical value is measured at Vcc=3.3V, T A =25°C. Not 100% tested.3. The typical value of the K9WAG08U1M’s I SB 2 is 40µA and the maximum value is 200µA.4. The maximum value of K9WAG08U1M-Y ,P’s I LI and I LO is ±40µA , the maximum value of K9WAG08U1M-I’s I LI and I LO is ±20µA .ParameterSymbol Test ConditionsMinTypMaxUnitOperating CurrentPage Read withSerial Access I CC 1tRC=25nsCE=V IL, I OUT =0mA-1530mAProgramI CC 2-EraseI CC 3-Stand-by Current(TTL)I SB 1CE=V IH , WP=0V/V CC --1Stand-by Current(CMOS)I SB 2CE=V CC -0.2, WP=0V/V CC -20100µAInput Leakage Current I LI V IN =0 to Vcc(max)--±20Output Leakage Current I LO V OUT =0 to Vcc(max)--±20Input High VoltageV IH (1)-0.8xVcc -Vcc+0.3V Input Low Voltage, All inputs V IL (1)--0.3-0.2xVccOutput High Voltage Level V OH I OH =-400µA 2.4--Output Low Voltage Level V OL I OL =2.1mA --0.4Output Low Current(R/B)I OL (R/B)V OL =0.4V810-mA RECOMMENDED OPERATING CONDITIONS(Voltage reference to GND, K9XXG08UXM-XCB0 :T A =0 to 70°C, K9XXG08UXM-XIB0:T A =-40 to 85°C)ParameterSymbol Min Typ.Max Unit Supply Voltage V CC 2.7 3.3 3.6V Supply VoltageV SSVABSOLUTE MAXIMUM RATINGSNOTE :1. Minimum DC voltage is -0.6V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <30ns. Maximum DC voltage on input/output pins is V CC +0.3V which, during transitions, may overshoot to V CC +2.0V for periods <20ns.2. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.ParameterSymbol Rating Unit Voltage on any pin relative to VSSV CC -0.6 to +4.6VV IN -0.6 to +4.6V I/O-0.6 to Vcc+0.3 (<4.6V)Temperature Under Bias K9XXG08UXM-XCB0T BIAS -10 to +125°C K9XXG08UXM-XIB0-40 to +125Storage Temperature K9XXG08UXM-XCB0T STG-65 to +150°CK9XXG08UXM-XIB0Short Circuit CurrentI OS5mACAPACITANCE (T A =25°C, V CC =3.3V, f=1.0MHz)NOTE : Capacitance is periodically sampled and not 100% tested. K9WAG08U1M-IXB0’s capacitance(I/O, Input) is 20pF.ItemSymbol Test ConditionMin MaxUnit K9K8G08U0MK9WAG08U1M*Input/Output Capacitance C I/O V IL =0V -2040pF Input CapacitanceC INV IN =0V-2040pFVALID BLOCKNOTE :1. The device may include initial invalid blocks when first shipped. Additional invalid blocks may develop while being used. The number of valid blocks is presented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits. Do not erase or pro-gram factory-marked bad blocks. Refer to the attached technical notes for appropriate management of invalid blocks.2. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block up to 1K program/erase cycles with 1bit/512Byte ECC.3. The number of valid block is on the basis of single plane operations, and this may be decreased with two plane operations.* : Each K9K8G08U0M chip in the K9WAG08U1M has Maximun 160 invalid blocks.ParameterSymbol Min Typ.Max Unit K9K8G08U0M N VB 8,032-8,192Blocks K9WAG08U1MN VB16,064*-16,384*BlocksAC TEST CONDITION(K9XXG08UXM-XCB0: T A =0 to 70°C, K9XXG08UXM-XIB0:T A =-40 to 85°C ,K9XXG08UXM: Vcc=2.7V~3.6V unless otherwise noted)ParameterK9XXG08UXM Input Pulse Levels 0V to Vcc Input Rise and Fall Times 5ns Input and Output Timing Levels Vcc/2Output Load1 TTL GATE and CL=50pF (K9K8G08U0M-Y ,P/K9WAG08U1M-I) 1 TTL GATE and CL=30pF (K9WAG08U1M-Y ,P)MODE SELECTIONNOTE : 1. X can be V IL or V IH.2. WP should be biased to CMOS high or CMOS low for standby.CLE ALE CE WERE WP ModeH L L H X Read Mode Command Input L H L H X Address Input(5clock)H L L H H Write Mode Command Input L H L H H Address Input(5clock)L L L HH Data Input L L L H X Data Output X X X X H X During Read(Busy)X X X X X H During Program(Busy)X X X X X H During Erase(Busy)X X (1)X X X L Write Protect XXHXX0V/V CC (2)Stand-byProgram / Erase CharacteristicsParameter Symbol Min Typ Max Unit Program Time t PROG-200700µs Dummy Busy Time for Two-Plane Page Program t DBSY-0.51µs Number of Partial Program Cycles Nop--4cycles Block Erase Time t BERS- 1.52msNOTE : 1. Typical value is measured at Vcc=3.3V, T A=25°C. Not 100% tested.2. Typical program time is defined as the time within which more than 50% of the whole pages are programmed at3.3V Vcc and 25°C tempera-ture.AC Timing Characteristics for Command / Address / Data InputParameter Symbol Min Max UnitCLE Setup Time t CLS(1)12-nsCLE Hold Time t CLH5-nsCE Setup Time t CS(1)20-nsCE Hold Time t CH5-nsWE Pulse Width t WP12-nsALE Setup Time t ALS(1)12-nsALE Hold Time t ALH5-nsData Setup Time t DS(1)12-nsData Hold Time t DH5-nsWrite Cycle Time t WC25-nsWE High Hold Time t WH10-nsAddress to Data Loading Time t ADL(2)70-nsNOTES : 1. The transition of the corresponding control pins must occur only once while WE is held low2. tADL is the time from the WE rising edge of final address cycle to the WE rising edge of first data cycleAC Characteristics for OperationParameter Symbol Min Max Unit Data Transfer from Cell to Register t R-20µs ALE to RE Delay t AR10-ns CLE to RE Delay t CLR10-ns Ready to RE Low t RR20-ns RE Pulse Width t RP12-ns WE High to Busy t WB-100ns Read Cycle Time t RC25-ns RE Access Time t REA-20ns CE Access Time t CEA-25ns RE High to Output Hi-Z t RHZ-100ns CE High to Output Hi-Z t CHZ-30ns RE High to Output hold t RHOH15-ns RE Low to Output hold t RLOH5-ns CE High to Output hold t COH15-ns RE High Hold Time t REH10-ns Output Hi-Z to RE Low t IR0-ns RE High to WE Low t RHW100-ns WE High to RE Low t WHR60-ns Device Resetting Time(Read/Program/Erase)t RST-5/10/500(1)µs NOTE: 1. If reset command(FFh) is written at Ready state, the device goes into Busy for maximum 5µs.NAND Flash Technical NotesIdentifying Initial Invalid Block(s)Initial Invalid Block(s)Initial invalid blocks are defined as blocks that contain one or more initial invalid bits whose reliability is not guaranteed by Samsung.The information regarding the initial invalid block(s) is called the initial invalid block information. Devices with initial invalid block(s)have the same quality level as devices with all valid blocks and have the same AC and DC characteristics. An initial invalid block(s)does not affect the performance of valid block(s) because it is isolated from the bit line and the common source line by a select tran-sistor. The system design must be able to mask out the initial invalid block(s) via address mapping. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block up to 1K program/erase cycles with 1bit /512Byte ECC.All device locations are erased(FFh) except locations where the initial invalid block(s) information is written prior to shipping. The ini-tial invalid block(s) status is defined by the 1st byte in the spare area. Samsung makes sure that either the 1st or 2nd page of every initial invalid block has non-FFh data at the column address of 2048. Since the initial invalid block information is also erasable in most cases, it is impossible to recover the information once it has been erased. Therefore, the system must be able to recognize the initial invalid block(s) based on the original initial invalid block information and create the initial invalid block table via the following suggested flow chart(Figure 3). Any intentional erasure of the original initial invalid block information is prohibited.*Check "FFh" at the column address 2048 Figure 3. Flow chart to create initial invalid block table.StartSet Block Address = 0Check "FFh"Increment Block AddressLast Block ?EndNoYesYesCreate (or update)NoInitialof the 1st and 2nd page in the blockInvalid Block(s) TableNAND Flash Technical Notes (Continued)Program Flow ChartStartI/O 6 = 1 ?I/O 0 = 0 ?No*Write 80hWrite AddressWrite DataWrite 10hRead Status RegisterProgram Completedor R/B = 1 ?Program ErrorYesNoYes: If program operation results in an error, map out the block including the page in error and copy thetarget data to another block.*Error in write or read operationWithin its life time, additional invalid blocks may develop with NAND Flash memory. Refer to the qualification report for the actual data.The following possible failure modes should be considered to implement a highly reliable system. In the case of status read fail-ure after erase or program, block replacement should be done. Because program status fail during a page program does not affect the data of the other pages in the same block, block replacement can be executed with a page-sized buffer by finding an erased empty block and reprogramming the current target data and copying the rest of the replaced block. In case of Read, ECC must be employed. To improve the efficiency of memory space, it is recommended that the read or verification failure due to single bit error be reclaimed by ECC without any block replacement. The said additional block failure rate does not include those reclaimed blocks.Failure ModeDetection and Countermeasure sequenceWrite Erase Failure Status Read after Erase --> Block Replacement Program Failure Status Read after Program --> Block Replacement ReadSingle Bit FailureVerify ECC -> ECC CorrectionECC: Error Correcting Code --> Hamming Code etc. Example) 1bit correction & 2bit detectionNAND Flash Technical Notes (Continued)Copy-Back Operation with EDC & Sector Definition for EDCGenerally, copy-back program is very powerful to move data stored in a page without utilizing any external memory. But, if the source page has one bit error due to charge loss or charge gain, then without EDC, the copy-back program operation could also accumulate bit errors.K9K8G08U0M supports copy-back with EDC to prevent cumulative bit errors. To make EDC valid, the page program operation should be performed on either whole page(2112byte) or sector(528byte). EDC status bits are not available for sectors within which some bits or bytes are modified by Random Data Input operation. However, in case of the one time 528 byte sector unit modification at the same address, EDC status bits are available.A 2,112-byte page is composed of 4 sectors of 528-byte and each 528-byte sector is composed of 512-byte main area and 16-byte spare area."A" area 512 Byte(1’st sector)"H" area (4’th sector)Main Field (2,048 Byte)16 Byte"G" area (3’rd sector)16 Byte "F" area (2’nd sector)16 Byte "E" area (1’st sector)16 Byte "B" area 512 Byte(2’nd sector)"C" area 512 Byte(3’rd sector)"D" area 512 Byte(4’th sector)Spare Field (64 Byte)Table 2. Definition of the 528-Byte SectorSector Main Field (Column 0~2,047)Spare Field (Column 2,048~2,111)Area NameColumn AddressArea NameColumn Address 1’st 528-Byte Sector "A"0 ~ 511"E"2,048 ~ 2,0632’nd 528-Byte Sector "B"512 ~ 1,023"F"2,064 ~ 2,0793’rd 528-Byte Sector "C"1,024 ~ 1,535"G"2,080 ~ 2,0954’th 528-Byte Sector"D"1,536 ~ 2,047"H"2,096 ~ 2,111Within a block, the pages must be programmed consecutively from the LSB (least significant bit) page of the block to MSB (most sig-nificant bit) pages of the block. Random page address programming is prohibited.From the LSB page to MSB page DATA IN: Data (1)Data (64)(1)(2)(3)(32)(64)Data register Page 0Page 1Page 2Page 31Page 63Ex.) Random page program (Prohibition)DATA IN: Data (1)Data (64)(2)(32)(3)(1)(64)Data registerPage 0Page 1Page 2Page 31Page 63Addressing for program operation::::Interleave Page ProgramK9K8G08U0M is composed of two K9F4G08U0Ms. K9K8G08U0M provides interleaving operation between two K9F4G08U0Ms. This interleaving page program improves the system throughput almost twice compared to non-interleaving page program.At first, the host issues page program command to one of the K9F4G08U0M chips, say K9F4G08U0M(chip #1). Due to this K9K8G08U0M goes into busy state. During this time, K9F4G08U0M(chip #2) is in ready state. So it can execute the page program command issued by the host.After the execution of page program by K9F4G08U0M(chip #1), it can execute another page program regardless of the K9F4G08U0M(chip #2). Before that the host needs to check the status of K9F4G08U0M(chip #1) by issuing F1h command. Only when the status of K9F4G08U0M(chip #1) becomes ready status, host can issue another page program command. If the K9F4G08U0M(chip #1) is in busy state, the host has to wait for the K9F4G08U0M(chip #1) to get into ready state.Similarly, K9F4G08U0M chip(chip #2) can execute another page program after the completion of the previous program. The host can monitor the status of K9F4G08U0M(chip #2) by issuing F2h command. When the K9F4G08U0M(chip #2) shows ready state, host can issue another page program command to K9F4G08U0M(chip #2).This interleaving algorithm improves the system throughput almost twice. The host can issue page program command to each chip individually. This reduces the time lag for the completion of operation.NOTES : During interleave operations, 70h command is prohibited.R / B (#1)b u s y o f C h i p #1I /O X80h10h C o m m a n d A 30 : L o w A d d & D a t a80h 10h A 30 : H i g h A d d & D a t ab u s y o f C h i p #2i n t e r n a l o n l yR /B (#2)i n t e r n a l o n l yR /BI n t e r l e a v e P a g e P r o g r a m≈≈≈F 1h o r F 2h A B CDa n o t h e r p a g e p r o g r a m o n C h i p #1S t a t e A : C h i p #1 i s e x e c u t i n g a p a g e p r o g r a m o p e r a t i o n a n d c h i p #2 i s i n r e a d y s t a t e . S o t h e h o s t c a n i s s u e a p a g e p r o g r a m c o m m a n d t o c h i p #2.S t a t e B : B o t h c h i p #1 a n d c h i p #2 a r e e x e c u t i n g p a g e p r o g r a m o p e r a t i o n .S t a t e C : P a g e p r o g r a m o n c h i p #1 i s t e r m i n a t e d , b u t p a g e p r o g r a m o n c h i p #2 i s s t i l l o p e r a t i n g . A n d t h e s y s t e m s h o u l d i s s u e F 1h c o m m a n d t o d e t e c t t h e s t a t u s o f c h i p #1. I f c h i p #1 i s r e a d y , s t a t u s I /O 6 i s "1" a n d t h e s y s t e m c a n i s s u e a n o t h e r p a g e p r o g r a m c o m m a n d t o c h i p #1.S t a t e D : C h i p #1 a n d C h i p #2 a r e r e a d y .A c c o r d i n g t o t h e a b o v e p r o c e s s , t h e s y s t e m c a n o p e r a t e p a g e p r o g r a m o n c h i p #1 a n d c h i p #2 a l t e r n a t e l y .S t a t u sO p e r a t i o nS t a t u s C o m m a n d / D a t aF 1hF 2hAC h i p 1 : B u s y , C h i p 2 : R e a d y8x hC x hBC h i p 1 : B u s y , C h i p 2 : B u s y8x h8x hCC h i p 1 : R e a d y , C h i p 2 : B u s yC x h8x hDC h i p 1 : R e a d y , C h i p 2 : R e a d yC x hC x hR / B (#1)b u s y o f C h i p #1I /O X60hD 0h C o m m a n d A 30 : L o w A d d60h D 0h A 30 : H i g h A d db u s y o f C h i p #2i n t e r n a l o n l yR /B (#2)i n t e r n a l o n l yR /BI n t e r l e a v e B l o c k E r a s e≈≈≈F 1h o r F 2h A B CDa n o t h e r B l o c k E r a s e o n C h i p #1S t a t e A : C h i p #1 i s e x e c u t i n g a b l o c k e r a s e o p e r a t i o n , a n d c h i p #2 i s i n r e a d y s t a t e . S o t h e h o s t c a n i s s u e a b l o c k e r a s e c o m m a n d t o c h i p #2.S t a t e B : B o t h c h i p #1 a n d c h i p #2 a r e e x e c u t i n g b l o c k e r a s e o p e r a t i o n .S t a t e C : B l o c k e r a s e o n c h i p #1 i s t e r m i n a t e d , b u t b l o c k e r a s e o n c h i p #2 i s s t i l l o p e r a t i n g . A n d t h e s y s t e m s h o u l d i s s u e F 1h c o m m a n d t o d e t e c t t h e s t a t u s o f c h i p #1. I f c h i p #1 i s r e a d y , s t a t u s I /O 6 i s "1" a n d t h e s y s t e m c a n i s s u e a n o t h e r b l o c k e r a s e c o m m a n d t o c h i p #1.S t a t e D : C h i p #1 a n d C h i p #2 a r e r e a d y .A c c o r d i n g t o t h e a b o v e p r o c e s s , t h e s y s t e m c a n o p e r a t e b l o c k e r a s e o n c h i p #1 a n d c h i p #2 a l t e r n a t e l y .S t a t u sO p e r a t i o nS t a t u s C o m m a n d / D a t aF 1hF 2hAC h i p 1 : B u s y , C h i p 2 : R e a d y8x hC x hBC h i p 1 : B u s y , C h i p 2 : B u s y8x h8x hCC h i p 1 : R e a d y , C h i p 2 : B u s yC x h8x hDC h i p 1 : R e a d y , C h i p 2 : R e a d yC x hC x h。

K9W8G08U1M 512内存

1

K9W8G08U1M K9K4G08Q0M K9K4G08U0M

K9K4G16Q0M K9K4G16U0M

FLASH MEMORY

512M x 8 Bit / 256M x 16 Bit NAND Flash Memory

PRODUCT LIST

Part Number K9K4G08Q0M-Y K9K4G16Q0M-Y K9XXG08UXM-Y K9K4G16U0M-Y 2.7 ~ 3.6V Vcc Range 1.70 ~ 1.95V Organization X8 X16 X8 X16 TSOP1 PKG Type

K9W8G08U1M K9K4G08Q0M K9K4G08U0M

K9K4G16Q0M K9K4G16U0M

FLASH MEMORY

Document Title

512M x 8 Bit / 256M x 16 Bit NAND Flash Memory

Revision History

Revision No

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you have any questions, please contact the SAMSUNG branch office near your office.

K9WAG08U1A-PCB0中文资料