基于单片机和FPGA简易数字存储示波器

基于单片机的简易数字示波器设计-电子信息

摘要示波器是设计制造和维修电子设备必不可少的一种硬件设施,在多个领域都有广泛的应用。

近年来微型集成电路和计算机信息都有着稳固的发展和提升,也就使得示波器也有了一定技术层次上的提高,逐渐开始被应用到了很多领域。

本次的设计方案主要是制作一个简易的数字示波器,主要研究的方向是硬件设施的选用以及有效构成,配合的软件程序的编写这两大部分。

硬件设施主要选用的是A/D转换设备,运行时间短,设备准确程度高,选用的是单片机at89c52和At89c51,有效的提高设备的运行速率,在同等状态的工作时间下,能够高质量高速度的完成作业。

数据最终的呈现效果选用液晶设备,能够有效地展现呈现效果,并且简单易识别,数据频率的显示设备也非常便捷。

有效的实现了数据的采集和读取,提高准确程度。

AbstractOscilloscope is an indispensable hardware facility for the design, manufacture and maintenance of electronic equipment, which is widely used in many fields. In recent years, micro-integrated circuits and computer information have developed and improved steadily, which makes the oscilloscope have also improved at a certain technical level, and gradually began to be applied to many fields.The design of this project is mainly to make a simple digital oscilloscope, the main research direction is the choice of hardware facilities and effective composition, with the compilation of software program these two parts. Hardware facilities mainly choose A/D conversion equipment, which has short running time and high accuracy. The micro-integrated circuits connected with AT89c52 and AT89c51 are selected to effectively improve the operation speed of the equipment. Under the same working time, it can complete the operation with high quality and high speed. The final display effect of data is LCD device, which can effectively show the presentation effect, and is easy to identify, and the display device of data frequency is also very convenient. Effective realization of data acquisition and reading, improve accuracy.Key Words: SCM ; Real-time sampling; Waveform; Frequency关键词:单片机;实时采样;波形;频率目录前言 (6)1.1选题的背景意义和研究现状 (6)1.1.1选题的背景和意义 (6)1.1.2国内外研究现状 (6)1.2 本设计所要实现的目标 (6)1.3 设计内容 (7)1.4 本章小结 (7)第二章单片机简易数字示波器的系统设计 (8)2.1简易数字示波器的基本原理 (8)2.1.1 简易数字示波器的组成 (8)2.2简易数字示波器的运作方式 (8)2.2.1简易数字示波器的功能 (8)2.2.2简易数字示波器驱动方式 (8)2.3简易数字示波器的特点 (9)2.4本章小结 (9)第三章单片机简易数字示波器硬件设计与实现 (7)3.1 频率测量及显示电路的硬件设计 (7)3.1.1 测频电路总体构成 (7)3.1.2 信号调理电路设计 (7)3.1.3 数码管显示模块 (9)3.1.4 数码管显示驱动模块 (9)3.2 幅度测量及显示模块的硬件设计 (10)3.2.1 显示电路总体结构 (15)3.2.2 单片机外围电路设计 (16)3.2.3 信号波形采集模块 (17)3.2.4 显示模块 (17)3.2.5 电源设计 (18)3.3 本章小结 (10)第四章系统软件设计 (39)4.1 测频系统软件设计 (39)4.2 显示系统软件设计 (40)4.3 信号采集系统软件设计 (41)4.4 本章小结 (41)第五章调试及仿真 (42)结论 (43)致谢 (44)参考文献 (45)附录 (46)1 前言1.1选题的背景意义和研究现状1.1.1选题的背景和意义世界上第一台示波器是阴极射线管示波器,他诞生于1897年,至今还被许多德国人称为布朗管。

基于单片机的数字存储式示波器设计与实现

基于单片机的数字存储式示波器设计与实现摘要本文介绍了基于单片机的数字存储式示波器的设计与实现。

数字存储式示波器是一种用于观察电信号波形的测量仪器,具有易于操作、灵敏度高以及方便存储和分析数据等特点。

文章首先介绍了数字存储式示波器的工作原理和基本组成部分,然后详细描述了单片机的选择和其在示波器中的应用。

接着,给出了数字存储式示波器的电路设计和PCB布局设计,并介绍了常见的示波器控制算法的实现方法。

最后,通过实际测试和验证,验证了数字存储式示波器的性能和准确度。

引言数字存储式示波器是一种用于测量和观察电信号波形的仪器,它通过将模拟信号转换为数字信号,并存储在存储器中进行处理和显示。

相比于模拟示波器,数字存储式示波器具有许多优势,如灵敏度高、易于操作以及能够方便存储和分析数据等。

本文将介绍基于单片机的数字存储式示波器的设计与实现。

首先,我们将详细介绍数字存储式示波器的工作原理和基本组成部分。

接着,我们将选择适合示波器设计的单片机并介绍其在示波器中的应用。

然后,我们将给出数字存储式示波器的电路设计和PCB布局设计,并介绍常见的示波器控制算法的实现方法。

最后,我们将通过实际测试和验证,验证数字存储式示波器的性能和准确度。

数字存储式示波器的工作原理和基本组成部分数字存储式示波器主要由以下几部分组成:模拟前端、A/D转换、存储器、信号处理和显示等。

•模拟前端:模拟前端用于对输入的模拟信号进行条件处理和放大,保证信号能够适合于A/D转换。

•A/D转换:A/D转换将模拟信号转换为数字信号,该数字信号将被存储在存储器中进行后续的处理和显示。

•存储器:存储器用于存储A/D转换后的数字信号,存储的容量决定了可存储的波形数据长度。

•信号处理:信号处理主要包括波形处理、触发处理和数据分析等。

波形处理用于对存储的数字信号进行加权平均和去噪处理,以提高显示效果;触发处理用于选择合适的触发条件,确保波形的稳定显示;数据分析用于对存储的波形数据进行进一步的分析和处理。

基于单片机和FPGA的数字示波器的设计

co k g n rt n,s mp i g c n r l r q e c a u e n n ai r t n sg a e e ao d l.Me s r b e fe u n y lc e e a i o a l o to ,f u n y me s r me t d c l ai in l n r trmo u e n e a b o g a u a l q e c r

中图 分 类 号 : M9 53 T 3. 7 文献 标 识 码 : A 文 章 编 号 :1 7 — 2 6 2 1 ) 8 0 7 — 4 6 4 6 3 (0 1 1— 0 8 0

De i n o i ia s il s o e b s d o m ir c n r l r a d sg fd g t lo clo c p a e n c o o t o l n FPG A e

比较 该 图 可 知 , 要 采 集 起 始 点 和 时 间 相 同 , 出 样 值 与 只 输

基于单片机的简易数字示波器

本科生课程设计题目:基于单片机的简易数字示波器题目来源:□省部级以上□市厅级□横向□自选题目性质:□理论研究□应用与理论研究□实际应用研究学院:信息工程学院系:自动化专业班级:学生姓名:学号:起讫日期:指导教师:职称:指导教师所在单位:学院审核(签名):审核日期:二0 年制目录1、设计原理概述.................................................1.1设计背景.....................................................1.2设计原理框图..................................................2 硬件的设计.....................................................................2.1.最小系统的设计.........................................2.1.1最小系统的电路设计................................2.1.2单片机STC89c52介绍........................................2.2 采样设计2.2.1 采样电路设计.......................................2.2.2 ADC0809介绍....................................2.3显示设计2.3.1 显示电路设计。

....................................2.3.2 12864液晶介绍..........................................3.软件设计..................................3.1程序流程图...............................3.2 采样程序设计与分析................3.3显示程序设计与分析...................4.仿真............................4.1 Proteus仿真软件介绍..........................4.2 矩形波仿真.....................................4.2三角波仿真....................................4.3正弦波仿真.............................5.设计总结................................6.参考文献...........................................7.附录......................................1设计原理概述1.1、设计背景示波器被广泛应用于各个领域。

基于单片机的简易示波器设计报告

基于单片机的简易示波器设计报告

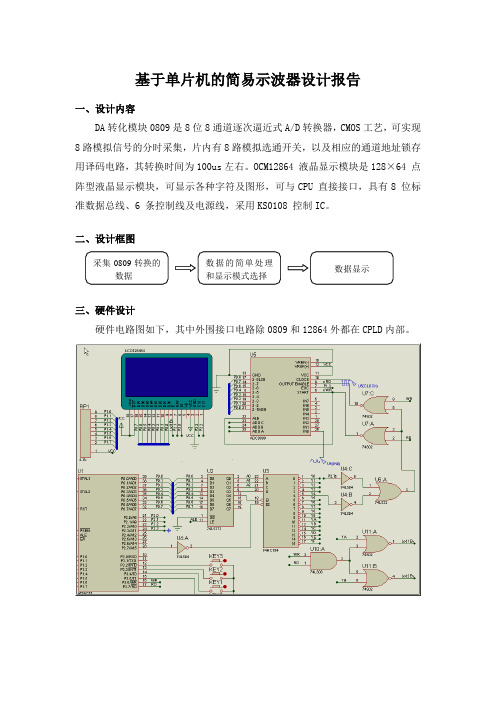

一、设计内容

DA 转化模块0809是8位8通道逐次逼近式A/D 转换器,CMOS 工艺,可实现8路模拟信号的分时采集,片内有8路模拟选通开关,以及相应的通道地址锁存用译码电路,其转换时间为100us 左右。

OCM12864 液晶显示模块是128×64 点阵型液晶显示模块,可显示各种字符及图形,可与CPU 直接接口,具有8 位标准数据总线、6 条控制线及电源线,采用KS0108 控制IC 。

二、设计框图

三、硬件设计

硬件电路图如下,其中外围接口电路除0809和12864外都在CPLD 内部。

采集0809转换的

数据 数据的简单处理和显示模式选择 数据显示

四、软件设计

软件设计采用KEIL编译器,用C语言编写,较汇编语言,C51可读性好,便于模块化。

简易多功能数字存储示波器(蔡天 林立 苏鑫)

简易多功能数字示波器参赛学校:武汉大学参赛队员:蔡天林立苏鑫时间:2007-7-27赛前辅导教师:黄根春张望先文稿辅导教师:黄根春徐大敏摘要本系统基于数字示波器基本原理,以8051单片机和FPGA组成的最小系统为控制核心;系统的频率范围为1Hz~2.8MHz,使用高速ADC芯片对任意波形信号进行采样量化,并在模拟示波器上显示,同时能对信号的基本参数进行数字测量,其中频率误差优于0.1%,幅度误差优于5%;通过FPGA对量化值进行FFT运算,实现了对输入信号的频谱分析;此外,本系统还可以利用傅立叶变换的性质对双通道输入的两路信号进行相位差测量,误差小于0.5o;实现周期信号的失真度测量,误差小于1%;系统的显示输出采用模拟示波器和128*64点阵液晶相结合的方式,连续可调电位器和3*8键盘为输入接口,故系统波形显示清晰,操作简单,界面友好。

关键词:示波器FFT 失真度测相AbstractThe system, mainly controlled by the combination of MCU 8051and ALTEA’s Cyclone FPGA, is based on the elements of Digital Oscillograph. All kinds of signal with the frequency fewer than 2.8MHz can be sampled by ADC chip AD9051 and AD197. The data of sampling is operated under FFT, with a result of the frequency spectrum of the input signal. Addition, the system also can measure the phasic difference, with the precision fewer than. We adopt the analog oscillograph and 128*64 dot-matrix LCD screens as export equipment, 3*8 keyboards and adjustable resistance as import equipment. People will find easy to handle the system with clear display and friendly interface.Keyword: oscillograph FFT Audibility of Distortion目录摘要 (1)Abstract (1)目录 (2)一、方案论证与选择 (3)1.题目任务要求及相关指标的分析 (3)2.方案的比较与选择 (3)二、系统总体设计方案及实现方框图 (5)三、理论分析与计算 (5)1、采样速率 (5)2、幅度控制 (5)3、波形的数据处理及相关参数测量 (5)4、快速傅立叶变换及误差 (6)四、主要功能电路的设计 (6)1、输入信号放大与采样量化电路 (6)2、同步采样时钟产生电路 (7)3、水平垂直div调节电路 (7)4、模拟示波器显示电路 (7)五、系统软件的设计 (7)六、测试数据与分析 (8)1.使用仪器及型号 (8)2.测试方案 (8)3.测量数据及结果分析 (8)七、总结分析与结论 (9)1、题目要求完成情况 (9)2、调试总结 (9)八、附录 (10)1、电路原理图 (10)2、参考文献 (11)一、方案论证与选择1.题目任务要求及相关指标的分析(1)题目要求仪器的输入阻抗大于100kΩ,我们可以使用一级射级跟随器或者同相放大器来实现;垂直刻度为8div,分辨率为32级/div,要求设置0.01V/div、0.1V/div、1V/div三档垂直灵敏度,误差≤5%,即直流档时输入信号电压范围为-4V~+4V,交流档时输入信号峰峰值范围为0V~8V,但为了能使用0.01V/div和0.1V/div档来清晰的观察小信号波形,所以需要根据输入信号的电压幅度的大小来对其进行适当放大或缩小,以适合ADC的采样和量化;水平刻度为10div,分辨率为20点/div,要求设置0.2s/div、0.2ms/div、20μs/div三档扫描速度,仪器的频率范围为DC~50kHz,误差≤5%,考虑极限情况,使用20μs/div档,采样周期为1μs,即此时采样频率为1MHz,对于0.2s/div和0.2ms/div,我们可以使用1MHz的采样频率,然后在下抽样,也可以分别使用100Hz和100KHz的采样频率。

基于FPGA技术的数字存储示波器设计

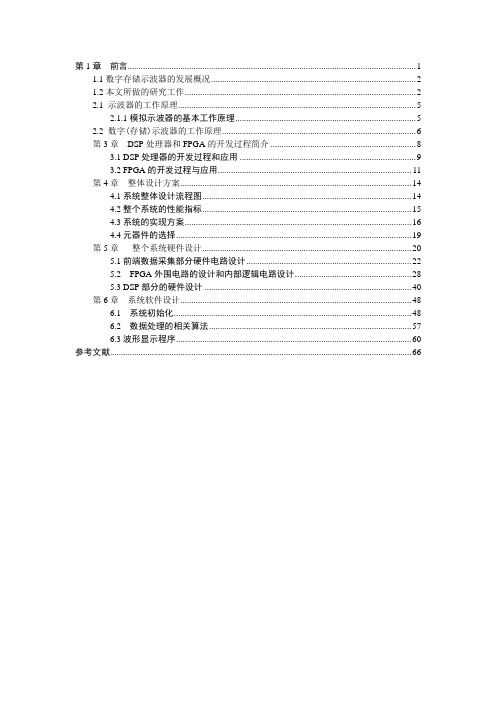

第1章前言 (1)1.1数字存储示波器的发展概况 (2)1.2本文所做的研究工作 (2)2.1示波器的工作原理 (5)2.1.1模拟示波器的基本工作原理 (5)2.2数字(存储)示波器的工作原理 (6)第3章DSP处理器和FPGA的开发过程简介 (8)3.1 DSP处理器的开发过程和应用 (9)3.2 FPGA的开发过程与应用 (11)第4章整体设计方案 (14)4.1系统整体设计流程图 (14)4.2整个系统的性能指标 (15)4.3系统的实现方案 (16)4.4元器件的选择 (19)第5章整个系统硬件设计 (20)5.1前端数据采集部分硬件电路设计 (22)5.2 FPGA外围电路的设计和内部逻辑电路设计 (28)5.3 DSP部分的硬件设计 (40)第6章系统软件设计 (48)6.1 系统初始化 (48)6.2 数据处理的相关算法 (57)6.3波形显示程序 (60)参考文献 (66)摘要数字存储示波器在仪器仪表领域中占有重要的地位,应用范围相当广泛,所以对示波器的研制有重要的理论和实际意义。

本文针对数字存储示波器的设计进行了深入的研究,旨在研制出100MHz带宽的数字存储示波器。

从各个方面考虑,选用了DSP、FPGA和单片机的方案来设计整个系统。

整个系统采用单通道的方式。

信号进来首先经过前端的调节电路把信号电压调整到AD的输入电压范围之内,这里调节电路主要是由信号衰减电路和信号放大电路所组成。

调节后的信号再送到AD变换电路里面完成信号的数字化。

然后把AD转换后的数据送到FPGA中,并把数据保存到FPGA中的FIFO中,FPGA中的电路主要包括有FIFO、触发系统、峰值检测、时基电路等。

由于本文采用FPGA,使得数字存储示波器的设计比较灵活,容易升级。

可以根据自己的需要进行相关的改进,例如对外围电路做进一步地扩展。

关键词:DSP;FPGA;LCD;单片机;数字存储示波器ABSTRACTDigital storage oscilloscopes play an important role in the field of instrumentation,it has a wide range of applications,the development of the oscilloscope has a very important theoretical and practical significance.In this paper, we have do a lot of work to the design of digltal storage oscilloscope.The goal is aimed at the development of the repeat 100MHz bandwidth digital storage oscilloscope.Considereing from various aspects,we select DSP,FPGA and microcontroller to design the whole system.The whole system is single channel.The signa that come in from the first front-end have been changed a fit voltage which put into a voltage signal AD.Front-end circmts here mainly are composed of by signal attenuation and signal amplifier circuit.After the front-end,the signals have changes the digital signal the by AD circuit.This data has been sent to FPGA,the data is saved to the FIFO in theFPGA.The main circuit in the FPGA,including FIFO,the trigger system,the peak detection circuit,time-ased circuit,and so on.At the same time,the use of FPGA makes the design more flexible,and easier to upgrade,for example,it is possible to expand extemal circuit of oscilloscopes.KEY WORDS:DSP,FPGA,LCD ,microcontroller,digital storage oscilloscope第1章前言示波器应用非常广泛,包括工业、军事、科研、教育领域都有很大的应用。

基于单片机的简易数字存储示波器

目录摘要 (I)Abstract (II)1 绪论 (1)1.1示波器发展简史与现状 (1)1.2 示波器原理概述 (3)1.3 模拟示波器与数字示波器 (5)1.4 设计任务与目标 (9)2.数字示波器总体设计 (10)2.1数字示波器总体结构 (10)2.2数字示波器采样速率 (11)2.3数字示波器采样原理 (12)3 数字示波器硬件设计 (15)3.1信号调理电路 (15)3.1.1输入衰减电路 (15)3.1.2程控放大电路 (17)3.1.3电平移位电路 (19)3.1.4硬件触发电路 (20)3.1.5 AD转换电路 (21)3.2数字处理电路 (24)3.2.1 CPLD电路 (24)3.2.2 MCU电路 (25)4.数字示波器软件设计 (29)4.1同步触发 (30)4.2串行通信 (32)4.3 波形显示 (34)4.4峰峰值计算 (35)5 数字示波器的调试和测试 (37)5.1硬件安装调试和软件调试 (37)5.2测试方案 (37)5.3性能测试 (38)参考文献 (39)致谢........................................................................................ 错误!未定义书签。

摘要本文对示波器的工作原理进行了介绍,提出一种基于单片机和CPLD的20M 数字存储示波器设计方案。

FPGA通过控制高速A/D转换器ADS831采样输入信号,信号输入频率低于4MHz时进行实时采样,高于4MHz时进行等效采样。

等效采样是对多个信号周期连续采样来复现一个信号波形,采样系统能以扩展的方式复现频率大大超过奈奎斯特极限频率的信号波形。

通过等效采样可以使用较低的采样频率获得较高信号的输入采集,从而降低了对A/D速度的要求,降低了示波器的硬件成本。

本文所设计制作的示波器对于示波器的发展与制造具有一定的指导意义。

基于单片机的数字示波器设计

基于单片机的数字示波器设计摘要示波器是电子测量中一种最常用的仪器,被广泛应用于各个领域。

随着微电子技术和计算机技术的飞速发展,示波器也从模拟示波器向数字示波器发展。

同模拟示波器相比,数字示波器具有很多优点,并开始逐步取代模拟示波器,成为市场上的主流。

基于单片机的数字示波器充分发挥了单片机的性能优势,它与传统的模拟示波器相比有许多优点,它易操作、体积小、精度高、可永久存储波形数据、反复重现波形数据等。

它特别适合一些电子DIY群体,故其使用面更加广。

本文提出了一种简易数字示波器的设计方案,以AT89C52单片机作为控制核心,通过高速A/D器件ADC0809采集信号,实现信号的存储与测量。

测试结果证明本设计提出的数字示波器可以实现波形的采集、存储、波形参数的测量,稳定性高,具有较高的实用价值。

关键词:单片机;AT89C52;ADC0809;数字示波器Design Of Digital Oscilloscope Based OnSingle-chip microcontrollerAbstractOscilloscope is an electronic measurement instrument.It is widely applied in various fields.With the rapid development of microelectronics and computer technology, oscilloscope has been changed from analogue oscilloscope to digital oscilloscope. Compared with analogue oscilloscope,digital oscilloscope has many advantages, and gradually replaces analogue oscilloscope, which becomes the mainstream in the market.The digital oscilloscope based on SCM has made most use of pared with analogue oscilloscope,many advantages can be listed,such as, easy to operate,small size,high accuracy, permanently store and repeatedly reproduce waveform data,etc.It is particularly suitable for DIY groups.Therefore,it is more widely used.This paper proposes a design of simple digital oscilloscope , of which AT89C52 microcontroller works as the control core, collecting signal by high-speed A/D device ADC0809 and reaching the signal storage and measurement. Test results show the digital oscilloscope proposed by this design can realize the acquisition and storage of waveform,and measure waveform parameter.At the same time,the digital oscilloscope owns advantages of high stability and practical value.Key words: Single-chip microcontroller;AT89C52;ADC0809;Digital Oscilloscope目录第一章绪论 (1)1.1 课题背景与实际意义 (1)1.2 国内外研究现状 (1)1.3 设计目标和设计内容 (2)第二章硬件电路设计 (3)2.1 总体研究思路 (3)2.2 AT89C52单片机简介 (3)2.3 数字示波器原理 (7)2.4 A/D转换及ADC0809的基本介绍 (8)2.4.1 A/D转换 (8)2.4.2 模/数转换器ADC0809 (8)2.5 系统各模块设计方案 (11)2.6 硬件电路设计 (13)2.6.1 电源模块 (13)2.6.2 串口通讯模块 (13)2.6.3 数据采集模块 (14)2.6.4 存储模块及液晶显示模块 (14)第三章软件设计 (17)3.1 设计思路 (17)3.2 主程序设计 (17)3.3 A/D转换子程序 (18)3.4 LCD液晶显示子程序 (19)3.5 EEPROM读写子程序 (20)3.6 按键处理子程序 (21)3.7 串口通讯子程序 (22)3.8 测试结果 (22)第四章结语 (25)致谢 (26)参考文献 (27)附录A (28)附录B (29)第一章绪论1.1 课题背景与实际意义近年来,随着电子技术与计算机技术的发展,对数据检测仪表的数据采集速度、精度及其智能化提出了更高的要求。

基于51单片机 简易存储示波器的设计

单片机方式原理框图

电路设计(硬件电路设计) 电路设计(硬件电路设计)

• • • • 硬件电路存储控制芯片的设计 外围电路A/D A/D模块设计 外围电路A/D模块设计 外围电路D/A D/A模块设计 外围电路D/A模块设计 外围电路键盘输入模块设计

硬件电路存储控制芯片的设计

存储器的位宽根据 A/D转换器的位宽来选取, 对于该课题选用8位的RAM。而控制芯片是选用单片 机里的80C51来实现对整个系统的控制。

方案二: 方案二:单片机方式

即使用单片机,A/D转换器,D/A转换器以及存 储器等组成系统。对输入信号用外接触发电路产生 触发信号,通过A/D转换将模拟信号转换成数字信号, 再通过单片机将数据锁存至外部RAM,然后由单片机 控制将数据送至D/A输出。它的优点是系统规模小, 有一定的灵活性,但是不适宜于观察高速信号或者 复杂信号。

80C51的引脚 80C51的引脚

本课题使用的是P89V51RB2FN芯片,其总线引脚图为:

80C51的内部结构 80C51的内部结构

80C51单片机由微处理器(含运算器和控制器)、 存储器、I/O接口以及特殊功能寄存器SFR等构成。

•80C51的微处理器 •80C51的片内存储器 •80C51的I/O口及功能单元 •80C51的特殊功能寄存器(SFR)

A/D模块-转换器的主要技术指标2 A/D模块-转换器的主要技术指标2 模块

(2) 水平分辨率 在数字存储示波器中,水平系统的作用是确保对输入 信号采集足够数量的采样值,并且每个采样值取自正确的 时刻,数字存储示波器的水平分辨率与存储器的存储深度 也即是容量,扫描速度和采样率有关。 存储器用来存储 A/D 转换器输出的数据,存储器的容 量决定了可以存储的取样点的数目。一般认为,存储容量 越大越好,但是由于存储容量是随着成本而增加的,因此 需要在两者中作权衡。 通常数字示波器技术指标是在最大扫描速率下给出的。 在给定扫描速度时,随着存储容量的增加,采样率也增加, 采样率越高,则信号重建的精度也越高;当给定采样速率 的时候,示波器记录时间的时间长度也将呈线性递增,时 间长度越长,对时间的观察也就也完整和精细。

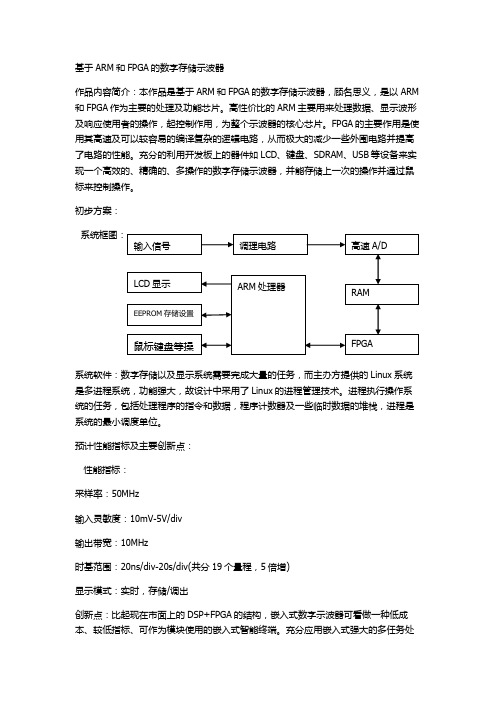

基于ARM和FPGA的数字存储示波器

基于ARM和FPGA的数字存储示波器

作品内容简介:本作品是基于ARM和FPGA的数字存储示波器,顾名思义,是以ARM 和FPGA作为主要的处理及功能芯片。

高性价比的ARM主要用来处理数据、显示波形及响应使用者的操作,起控制作用,为整个示波器的核心芯片。

FPGA的主要作用是使用其高速及可以较容易的编译复杂的逻辑电路,从而极大的减少一些外围电路并提高了电路的性能。

充分的利用开发板上的器件如LCD、键盘、SDRAM、USB等设备来实现一个高效的、精确的、多操作的数字存储示波器,并能存储上一次的操作并通过鼠标来控制操作。

初步方案:

系统软件:数字存储以及显示系统需要完成大量的任务,而主办方提供的Linux系统是多进程系统,功能强大,故设计中采用了Linux的进程管理技术。

进程执行操作系统的任务,包括处理程序的指令和数据,程序计数器及一些临时数据的堆栈,进程是系统的最小调度单位。

预计性能指标及主要创新点:

性能指标:

采样率:50MHz

输入灵敏度:10mV-5V/div

输出带宽:10MHz

时基范围:20ns/div-20s/div(共分19个量程,5倍增)

显示模式:实时,存储/调出

创新点:比起现在市面上的DSP+FPGA的结构,嵌入式数字示波器可看做一种低成本、较低指标、可作为模块使用的嵌入式智能终端。

充分应用嵌入式强大的多任务处

理能力,我们在此基础上增加了一些功能,比如鼠标操作、设置存储等功能,界面更加人性化。

而且用于逻辑电路的FPGA不用太高端,加上性价比高的ARM处理器,故整个系统的成本不高。

基于FPGA的数字存储示波器设计

基于FPGA的数字存储示波器设计耿新力;王中训【期刊名称】《电视技术》【年(卷),期】2013(37)9【摘要】An optimized method of data collection is proposed to complete the digital storage oscilloscope,which is supported by FPGA as its controller platform and the necessary peripheral circuits.The system uses FPGA high-speed digital signal processing and embedded of many modular circuits and soft-core characteristics,reducing the cost and difficulty of development.The combination of the basic principles of digital storage oscilloscope and signal source with new data acquisition and processing method and the optimization at analog signal preprocessing,data multi-faceted storage,trigger mode,and equal precision frequency measurement.After testing,the system has excellent performance,and all this provides new ideas for the development of new simple digital storage oscilloscope.%提出一个经过优化的数据采集方法,辅以FPGA(Field-Programmable Gate Array)主控制器和必备的外围电路完成了基于FPGA的数字存储示波器的设计.系统最大限度地利用了FPGA的高速数字信号处理能力以及众多硬核和软核内嵌的特性,降低了成本和开发难度.将数字存储示波器及信号源的基本原理和经过优化的数据采集方法相结合,分别在模拟信号预处理、数据多方位存储、触发方式、等精度测频等环节进行创新性优化,经测试,系统性能良好,各项指标均能较好满足要求,为新型简易数字存储示波器的发展提出了新思路.【总页数】4页(P218-221)【作者】耿新力;王中训【作者单位】烟台大学光电信息科学技术学院,山东烟台264005;烟台大学光电信息科学技术学院,山东烟台264005【正文语种】中文【中图分类】TN948【相关文献】1.基于FPGA和单片机的简易数字存储示波器设计 [J], 谭本军2.基于 FPGA 的数字存储示波器对外围芯片的控制设计 [J], 林盛鑫;钟惠球;黄丁香3.基于FPGA的虚拟简易数字存储示波器设计 [J], 雷贵;胡福云4.基于FPGA的手持式数字存储示波器显示驱动设计 [J], 石明江;张禾;河道清5.基于FPGA的数字存储示波器设计 [J], 苏建加;廖聪裕;鲁锦涛因版权原因,仅展示原文概要,查看原文内容请购买。

基于ARM FPGA结构的便携式数字存储示波器硬件平台设计

设计摘要便携式数字存储示波器是现代示波器发展的方向之一,但由于其技术含量及高,尚无本国产品上市,属于测试仪表方面众目交注的领域。

ARM是32位的RISC 处理器,高性能、低功耗是其显著特点,已被广泛应用与各种潜入式领域。

在便携式电子产品的设计中,采用FPGA器件可以将原来的电路板级产品集成为芯片级产品,做到功耗低、可靠性高。

本文提出了一种基于ARM+FPGA结构的便携式数字存储示波器硬件平台设计方案,FPGA主要用于大量的数据存储,ARM则负责数据的进一步处理和控制波形的重建、显示和数据永久存储。

系统的前端芯片选用Altera公司最新一代的MAX Ⅱ系列高性能、低功耗FPGA芯片,系统后端ARM处理器则选用三星公司基于ARM7TDMI-S内核的多功能、低功耗ARM单片机——LPC2210,系统利用彩色LCD作为终端显示设设备,利用其基于自带的存储器存储永久波形数据,且自带有JTAG调试接口,便于设计。

ABSTRACTIt is one of the directions of modern oscilloscope development that the portable digital storage oscilloscope, because its technological content is extremely high, there are no national products to go on the market, It is a field concerned by a lot of eyes in testing the instrument. ARM is 32 bits RISC processor, high performance, low consumption are its remarkable characteristic, have already widely used in various kinds of embedded fields. In portable electronic product design, using FPGA may upgrade printed circuit product to integration circuit, depress power consumption and enhance reliability.The paper has proposed a kind of hardware platform design plan of the portable digital storage oscilloscope based on ARM+FPGA structure. FPGA is used as data memory, ARM is responsible for the back end waveform rebuilding, displaying and the data storing for ever. The chip of the systematic front, we select Altera Company’s MAX Ⅱseries for use that is the most new generation high performance, lowconsumption FPGA chip, the ARM processor of the systematic back end, we select Samsung Company’s the multi-functional、low consumption ARM chip based on ARM7TDMI-S kernel ——lpc2210, the system utilizes multicolor LCD as the terminal display device, to utilize the memory of lpc2210 to store the waveform data for ever, the JTAG debugging interface of lpc2210 make it convenient for design. Key words ARM Embedded Monitoring System, Portable Digital Storage Oscilloscope, Redundant date lost by hardware, LCD目录摘要 (I)ABSTRACT (I)1 绪论 (3)2 设计要求 (3)2.1 方案设计 (3)2.2 实现的功能和技术指标 (4)3 单片机LPC2210简介 (5)3.1 ARM处理器核简介 (5)3.1.1 ARM嵌入式系统 (5)3.1.2 ARM处理器介绍 (6)3.1.3程序状态寄存器 (6)3.2 单片32位微控制器-LPC2210 (7)3.2.1 LPC2210介绍 (7)3.2.2特性 (7)3.2.3结构框图 (7)3.2.4管脚信息 (8)3.2.5功能描述 (8)4 硬件平台的模块介绍 (10)4.1信号调理电路 (10)4.1.1 输入信号保护和衰减电路的设计 (10)4.1.2 信号放大电路的设计 (11)4.2 A/D转换模块 (12)4.2.1特性 (12)4.2.2描述 (12)4.2.3操作 (14)4.3 显示模块 (14)4.4键盘输入模块 (15)4.4.1 ZLG7290芯片描述 (15)4.4.2 I2C接口 (18)5软件开发环境介绍 (22)5.1 ADS 1.2 集成开发环境的组成 (23)5.2 CodeWarrior IDE 简介 (23)5.3 Easy JTAG防真器的安装与运用 (23)5.4 安装EasyJTAG仿真器 (23)5.5 使用EasyJTAG仿真器 (24)6系统软件设计 (24)6.1 硬件丢失和软件丢失 (25)6.2 程序设计的方案选择 (26)6.3 数字存储示波器的实际性能指标 (26)6.4 应用程序 (27)结论 (27)参考文献 (28)附录A: 液晶模块驱动程序 (29)附录B: 液晶模块驱动程序头文件 (30)附录C: I2C中断服务程序 (36)附录D: I2C中断程序头文件 (41)致谢 ·········································································错误!未定义书签。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于单片机和FPGA简易数字存储示波器

2008/11/24/14:00 来源:电子产品世界作者:郭小虎,陈鹏鹏

l 引言

与传统模拟示波器相比.数字存储示波器不仅具有可存储波形、体积小、功耗低,使用方便等优点,而且还具有强大的信号实时处理分析功能。

在电子测量领域,数字存储示波器正在逐渐取代模拟示波器。

但目前我国使用高性能数字存储示波器主要依靠国外产品,而且价格昂贵。

因此研究数字存储示波器具有重要价值。

借于此,提出了一种简易数字存储示波器的设计方案,经测试,性能优良。

2 数字存储示波器基本工作原理

数字存储示波器与模拟示波器不同在于信号进入示波器后立刻通过高速A

/D转换器将模拟信号前端快速采样,存储其数字化信号。

并利用数字信号处理技术对所存储的数据进行实时快速处理,得到信号的波形及其参数,并由示波器显示,从而实现模拟示波器功能,而且测量精度高。

还可存储信号,因而,数字存储示波器可以存储和调用显示特定时刻信号。

3 系统分析论证

3.1 A/D实时采样

根据奈奎斯特采样定理,采样速率必须高于2倍的信号最高频率分量。

对于正弦信号,一周期内应有2个采样点。

为了不失真恢复被测信号,通常一周期内需要采样8个点以上。

为了配合高速模数转换器,采用FPGA控制M/D转换器的采样速率,以实现高速实时采样。

实时采样可以实现整个频段的全速采样,本系统设计选用ADI公司的12位高速A/D转换器AD9220,其最高采样速率可达10 MHz。

3.2 双踪显示

本系统设计的双踪显示模块是以高速切换模拟开关选通两路信号进入采样电路,两路波形存储在同一个存储器的奇、偶地址位。

双踪显示时,先扫描奇地址数据位,再扫描偶地址数据位。

采用模拟开关代替一个模数转换器,避免两片高速A/D转换器相互干扰,降低系统调试难度,并且实现系统功能。

3.3 触发方式

采用FPGA内部软件触发方式,通过软件设置触发电平,所设置的施密特触发器参数易于修改,从而抑制比较器产生的毛刺。

当采样值大于触发电平,则产生一次触发。

该方式充分利用了FPGA的资源,减少外围电路,消除硬件毛刺产生的干扰,易于调整触发电压。

3.4 波形显示位置的调节

3.4.1 行扫描调节

通过控制FPGA内部双口RAM(1 KB)的起始地址的偏移量确定来控制波形的移动。

其具体方法是将滑动变阻器R上的电平通过模数转换器转换为数字信号传输给FPGA,再与初始电平数字信号(显示位置复位时,滑动变阻器R的电平采样值)相比较决定起始地址ADR0的偏移量。

该方法可易于实现波形满屏和自动显示功能。

3.4.2 列扫描调节

MAXl97采样A、B通道的Position电位器值,所得采样值经FPGA送至16

位串行D/A转换器,MAX542产生直流电平,该直流电平与列扫描波形相加送至模拟示波器显示,实现波形上下移动。

为分离A、B通道,在读A通道波形数据时,FPGA必须将Position A电位器的值送至D/A转换器;而在读B通道波形数据时,也必须将Position B电位器的值送至D/A转换器,这样可在调节某一电位器时,实现相应通道波形上下移动。

3.5 波形数据存储

数字示波器存储波形数据可采用外接的双口RAM或通用静态RAM,同时FPGA 可控制RAM的地址线,从而实现波形数据的存储。

双口RAM可同时进行读写操作,由于本系统设计采用FPGA,因此可充分利用FPGA的逻辑阵列和嵌入式阵列,可将双口RAM写入FPGA内部,从而无需外接RAM,减少硬件电路,提高简易数字示波器的可靠性。

4 系统设计方案

本系统设计框图如图1所示。

整个系统是以FPGA为核心,包括前端模拟信号处理模块、单片机模块、显示模块和键盘输入模块。

而信号的前级处理模块又包括射级跟随器、程控放大电路、整形电路。

A、B通道的信号经前级处理变为O~4 V,AD9220对其采样。

波形存储控制模块将其采样数据写入FPGA内部RAM,再由波形显示控制模块进行显示。

FPGA通过编程设置实现测频、键盘扫描、显示驱动、波形存储控制等功能。

单片机AT89S52控制整个系统键盘和点阵液晶模块实现人机交互。

通过面板按键可方便调整波形显示方式。

5 硬件电路设计

5.1 程控放大电路

采用模拟开关CD4051、宽带运算放大器AD844及精密电位器实现10 mV/div~2 V/div的多档垂直分辨率。

FPGA含有通道选择寄存器模块,通过单片机

写入通道号控制模拟开关以选通不同的反馈电阻,实现不同放大倍数,将信号调理在满足AD9220的0~4 V的范围内,具体电路如图2所示。

5.2 数据采集模块

本系统设计采用ADI公司的高速模数转换器AD9220实现波形信号的采集,AD9220最高采样速率可达10 MHz,采用外部晶体振荡器8 MHz,FPGA内部通过采样实现波形存储。

AD9220有直流耦合和交流耦合两种输入方式。

本系统设计采用直流耦合,0~5 V的输入方式。

采用内部2.5 V参考电压。

由于系统垂直分辨率只需255级,故采用AD9220的高8位。

数据采集电路如图3所示。

5.3FPGA设计

系统采用Verilog HDL语言,在QuartusII软件下对FPGA进行逻辑电路的描述编程,可灵活实现系统所需电路和控制模块。

5.3.1 触发模块

单片机先向FPGA模块写入设置的触发电压,FPGA内部相比较后,当采样值大于该触发电压时,则产生一次触发。

图4为触发模块。

5.3.2 程控放大控制模块

单片机首先以100 mv/div的档位对信号采样,通过比较与该信号最近的模拟开关的通道号,然后写入控制字,产生相应通道号,实现垂直分辨率的调整。

5.3.3 波形存储控制模块

该模块为RAM模块的写地址累加器,可控制波形的存储。

H_sering为单次和多次触发控制引脚,当为高电平时,单次触发,停止向RAM写入数据,所显示波形为存储波形;为低电平时,多次触发,当检测到一次触发时,即向RAM写一次数据,共l K个点,并在写操作时屏蔽触发。

写地址先写奇地址,存入通道一采样后的波形数据,后写偶地址,存入通道二采样后的波形数据。

如果连续多次检测不到触发时,向RAM中写入全0,显示一条直线,即实现自动捕捉功能。

波形存储控制模块如图5所示。

5.3.4 波形显示控制模块

该模块为读地址累加器,从RAM中读取数据,并产生行扫描和列扫描数据。

通过单片机写入累加器基地址,改变读取数据的起始位,实现波形的平移。

该模块还可计算波形的峰峰值、平均值,单片机可直接读回数值。

波形显示控制模块如图6所示。

6 系统软件设计

系统软件设计实现人机交互、信息提示、系统启动与复位等功能。

首先系统初始化,显示默认通道波形,再等待按键按下。

当按键按下后,完成相应功能,显示相应波形,然后循环等待。

系统软件设计流程如图7所示。

7 测试结果

使用自制的数字存储示波器和tektronix TDSl002型数字示波器测量输入信号,其中部分测量数据如表1所列。

通过对比测试和结??精确显示波形,并且实现波形的双踪显示及波形水平、垂直平移,频率、平均值、峰峰值的测量,误差小,达到一定的精度要求。

8 结语

本系统设计采用单片机作为核心控制器,充分利用FPGA的可编程逻辑功能,完成相关电路设计。

软硬件有机结合实现简易数字存储示波器的设计,系统总体功能完善,稳定性高,使用方便。