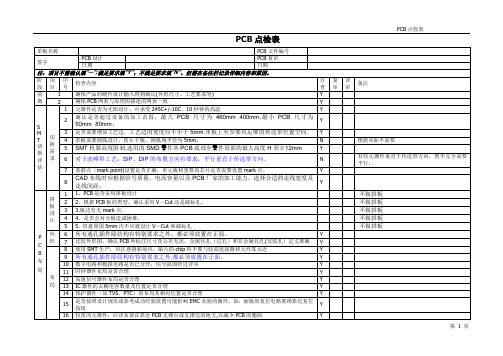

PCB评审表

PCB设计输入审查表

PCB设计输入审查表

PCB型号:

序号 內容 排板定位孔直徑Φ4mm,定位孔中心離板邊距離為5mm,PCB板同一邊 至少有2個定位孔 十字mark點:線寬1mm,長度5×5mm;圓形mark點:直徑2mm, Note:mark中心離板邊5mm,MAKR點表面裸銅,mark點周圍1mm區域內無干擾 點 同面mark點不能中心對稱。雙面板時,兩邊MARK點不可在同一位置

审核:

设计目的

日期:

符合性 符合 不符合 更改状况

1

SMT设备需求 SMT设备需求

2

3

防止TOP/BOT面SMT打件放PCB放错面,或 进板方向错误 SMT打件进板标准化,库存目视管理 减少变形对元件产生应力 防止过孔漏锡造成PAD少锡 PCB防焊后,无架桥PAD因工艺问题会比 有架桥PAD大0.1mm,焊盘大小不一,造成 立碑 防止连板分板应力 目视化管理 防止生产PCB时捞伤线路 防止弯折时应力造成元件锡裂 以免組裝時在尖角處“應力集中”導致 線路破損 防止SMT生产时锡珠,立碑,少锡的产生

10 PCB板邊到走線的距離不能小於1.0mm 11 FPCB板需折叠位元件下需有補強板 12 FPCB Layout時避免出現尖角 13 SMT元件layout設計;PAD设计需依据IPC标准设计 14 15 16 17 18 19

其它问题点:

Байду номын сангаас

4 5 6 7 8 9

PCB板邊必須有進板方向箭頭及PCB料号標記 雙面板正反兩面覆銅尽量保持一致,防止由於热膨脹係數不一致而變形 PCB板上元件PAD上不允許有過孔 FPCB板的接地PAD需用架橋形式,防止防焊工藝後PAD大小不一導致立碑 距板邊2mm以内不可有元件. 極性元件必須在PCB上標示極性點或者標示線.

印制板(PCB)自查与审核列表(EMC版本)

时钟线、高速信号线、控制线、复位线是否加跟随地线或包地

同层或相邻布线层的数字信号布线是否没有穿越模拟部分,反之亦然

分 层

主电源平面(板上功率最大的那种电源)是否与地平面相邻★

元件面下面(第二层或倒数第二层)是否有相对完整的参考平面★

时钟发生器是否靠近用到该时钟的器件★

逻辑电路(时钟驱动、缓存等)与晶体相连,是否扩大敷铜地平面包围住这些时钟附属电路★

时钟产生电路附近是否有与底板、机壳搭接的焊盘

电 源

电源线,尤其地线是否粗、短★

单层板的电源线、地线是否就近平行布线★

电源的输入输出线是否隔离,是否避免交叉★

隔离变压器、光电耦合器下面的电源层、地层是否挖空

PCB上的敷铜、局部接地面等接地过孔之间的物理距离是否小于最高频率波长的1/20

连 接 器

连接器是否避免跨越平面层的开槽★

金属外壳连接器,其周围15mm以内的地方,是否没有布置敏感器件★

是否选用具有更多地针的连接器,是否每根信号针都有相应的地针

审核意见及建议

EMC设计师(签名):年月日

印制板自查与审核列表

表单编号:NO:

产品名称

产品代号

设计师

印制板名称

版本号

图号

填表日期

本表使用说明:

1.设计师开始设计印制板之前,先应当熟悉公司《印制电路板电磁兼容设计规范》相关内容,当印制板设计完成后,

设计师首先应按照本检查表核对设计结果,进行设计师自查,最后提交审核;

2.“设计自查”及“EMC审核”分别由设计师本人和电磁兼容设计师在需要检查的项目填写“Y”、“N”或空白,

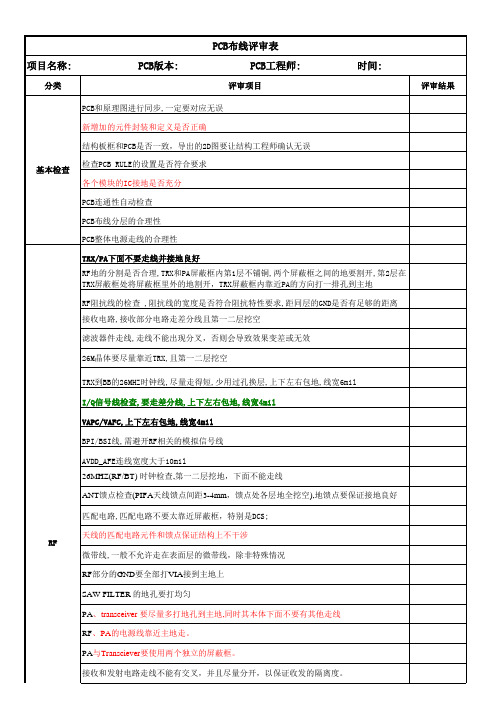

PCB设计评审表范例

PCB设计评审表

用的设计要求

●同一产品上使用的相似物料(如:按键、LED灯、插座、连接线、电解、保险管、插片、压敏/高压电容等),设计需防错(可以从跨距、颜色、安装的PIN脚、成型方向等方面考虑)。

1

●结构件设计需考虑色差、尺寸、安装、强度、外观等方面评估可行性。

1●LCD、背光源的设计是否密封,以免生产过程中进入灰尘、杂物。

1

●对温度/静电/湿度敏感的器件,需分析制造的可行性及防护措施,如双面板上安装的LED灯贴板安装要求改为单面焊盘,通孔不沉铜,如果高度不能满足要求,也可以加支架;蓝色LED灯抗静电能力差,要求增加反向二极管(内置有二极管的除外),湿度及温度保险丝高温焊接会脱落等。

1

●同一块板同一面的贴装电阻电容尽量采用同一尺寸的,以便生产设备相关参数的设定。

1各项得分

119

评审提出问题(含改善建议)

综合评分:A×B×C =

PCB评审组会签: 日期:

综合评分子项说明:

1.元器数量对应系数A:<45=0.7,46~60=0.8,61~120= 0.9,121~200=1.0,>200=1.1;

2.技术难度对应系数B: 双面板/碳桥板=1,单面板=1.05,镀金邦定板=1.1,多层板=1.2评审结论

3.工艺难度对应系数C:普通结构=1, PCB间装配型结构/超重结构=1.05, 结构紧凑型=1.1

20.器件选型及安装

评审输出

评审通过,不修改

条件通过,局部修改

不通过,重新设计评审。

PCB设计评审表

35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 65 66 67 68 69 70 71

ESD,防雷击器件走线时先经过元件 电源线,音频走线先经过电容 重要信号线,对线包地 注意阻抗线的设置是否能满足阻抗要求 相邻层布线方向互为垂直 板上无多余过孔及浮空的布线 没有过孔与焊盘重叠 高频、高速、时钟及其他脆弱信号线, 模块下无大于0.5MM的过孔,模块下加白油 RF模块焊盘下1MM内无过孔 RF模块的供电线和地线足够宽

结论说明

备注

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 21 22 23 24 25 26 27 28 29 30 31 32 33 34

结 构 检 查 封 装 检 查

板框尺寸无误 定位孔数量,孔径与机械图一致 螺丝孔加摆件,布线禁止区(≥螺丝帽直径的4MM) 定位元件定位无误,位置及所在元件层 元件与机壳无干涉 接插件(排线,金手指)检查:位置,排序 结构图与板是否对应 新设计器件是否已选用最新封装 封装工艺要求高的及新增关键元件给到工程检查工艺时需特别指出 封装形式,引脚间距,外形尺寸,焊盘尺寸,元件脚序是否正确 极性器件有方向标示 发热IC中间焊盘是否接地 DIP元件孔径是否大于对应元件插脚0.3MM以上 DIP元件焊盘外边对其它焊盘外边缘间距大于0合理 高器件之间尽量避免矮小器件 是否有1.0mm的Make 晶体、晶振等靠近相关器件,多负载时应平衡放置; 退耦电容靠近相关器件放置,匹配电阻位置适宜 滤波电容数量,容量及分布合理

发热元件及外壳裸露器件不能紧邻导线和热敏元件,其他器件也应适当远离;

PCB点检表(增加工艺审查)

PCB点检表

设计规范的附录A

公司对元器件文字符号(REFDES)的统一规定

器件间距要求

设计规范的附录C

内外层线路及铜箔到板边、非金属化孔壁的尺寸要求单位:mm(mil)

PCB布线最小间距

丝印字符大小(参考值)

器件封装制作要求

器件封装制作要求:

a。

器件在极限尺寸时,应该还能保证:尺寸a(toesolderfillet)=0。

4~0。

6mm且大于1/3引脚厚度H.器件引脚中心距<=0.5mm时,取0。

4mm.

b.器件在极限尺寸时,应该还能保证:尺寸b(heelsolderfillet)=0。

4~0.6mm.器件引脚中心距<=0.5mm时,取0。

4mm。

c.器件在极限尺寸时,应该还能保证:尺寸c(sidesolderfillet)=0~0。

2mm。

设计规范的附录G

通孔制作要求

一般通孔直接大于管脚直径0。

2~0.5mm,考虑公差适当增加,确保透锡量好.

PCB点检表设计规范的附录H

SMD贴片元件工艺要求。

PCB设计任务工作评审表

PCB设计任务工作评审流程表

1.本表格为跟进确认工作任务用,不作为工作任务单

2.工作任务单下达后,作为工作任务单的附件

3.后一步骤责任人作为前一步骤工作的审核人,前一步骤工作完成审核后接口人在接收到资料后签字确认,工作任务实际执行人转移,任务跟进人继续跟进

4.本表中的工作任务某步骤出现问题无法继续下一步骤时,本表自行终止,除任务临时结束外,重新填写新的表格,之前的表格作为附件,序号随之加1,编号维持前一表格

5.当一个工作任务评审流程表结束后即为一个工作任务的结束

6.任何一个工作步骤结束都应该有相应的证明文件存在,证明文件作为此表的附件

7.本表一式两份,一份交负责人,一份作为研发任务表的附件存档,当任务完成时以完成的表格作为结项表格替换任务下发时的存档表格,证明任务关闭。

8.本表格作为研发绩效考核和考评的依据,也是工作成果的体现

任务负责人:审核:批准:。

PCB投板评审要素表(硬件)2010

PCB 投板评审要素表(硬件)分钟评审花费设计者项目经理产品经理评审日期主审人 所处评审点所处阶段所属产品或版本评审对象 注: 评审结论为“否”需在“结论说明”中注明内容实例,结论为“免”需在“结论说明”中注明理由。

是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]匹配电阻位置适宜是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]退耦电容靠近相关器件放置是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]晶体、晶振等靠近相关器件放置,多负载时应平衡放置布局的电气4是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]波峰焊接面的贴片器件的方向、重量、pin 间距符合要求是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]压接件在元件面距高于它的器件大于5mm ,焊接面压接件贯通区域无任何器件是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]器件布局间距,表面贴装器件大于0.7mm 、IC 大于2mm 、BGA 大于5mm是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]高器件之间无矮小器件,且高度≥10mm 器件之间5mm 内不能放置贴片器件和矮、小的插装器件是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]同类型有极性插装元器件X 、Y 向各自方向相同是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]发热元件及外壳裸露器件不能紧邻导线和热敏元件,其他器件也应适当远离;是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]拨码开关、复位器件,指示灯等位置合适,不与拉手条冲突,且放在元件面布局设计3是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]普通板有5mm 工艺边,射频板至少有0.5mm 工艺边是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]板外框平滑弧度5mm ,或者按结构尺寸图设计是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]各种需加的附加孔无遗漏,且设置正确;是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]PCB 实际尺寸、定位器件位置等与工艺结构要素图吻合结构设计2是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]定位光标设置正确,中心距边大于6mm是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]所有器件均有明确标识,且字体大小整齐是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]极性器件有方向标示是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]新设计器件已选用最新封装器件封装1备注结论说明结论自评结果评审要素是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]没有锐角和90 °布线是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]线间距≥6mil ,线宽≥6mil ,走线宽度没有跳变是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]相邻层布线方向互为垂直是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]空白区域铺网格铜箔,网格的线宽和间隔设置正确是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]已经使用20H 规则是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]高速线圆弧过渡并且不跨相邻层地平面分割,或有平行地网络线作回流地是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]重要信号线用平行地线隔离,屏蔽地线每75mm 不少于1个过孔到地平面层是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]高速信号线、时钟信号线遵循回路面积最小原则是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]接插件管脚间没有有较长的信号线穿行是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]没有过孔与焊盘重叠是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]所有网络已完成布线是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]色码电阻、电感下没有过孔是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]电源和高热器件,安装面没有其他布线穿越是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]走线,铜皮到板边不得已最小也要保证大于20mils ,一般应大于2mm ;孔到板边(含开窗部分)最小距离3mm 是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]布线在空间没有形成闭环是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]屏蔽盒、屏蔽线已连接到对应的地网络是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]螺钉紧固件周围的禁布区符合相应的要求是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]电源、地Fanout ≤200mil ,尽可能加粗,电阻、电容的FANOUT 线尽量平行器件长度方向打出是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]电源地分割是否考虑了高速信号线的布线至少有一个完整的参考层是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]分割区连续,没有无花盘(热焊盘)的分割区,没有满铺的分割区,所有花盘均应打在相应的分割区内是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]PCB 层次是否满足芯材厚度对称、半固化片厚度对称、铜对称等原则是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]电源、地分割简捷,正确、分割线线宽合适,地汇接正确,且与光绘文件一致布线设计5是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]滤波电容数量、容量及分布合理考虑是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]安装孔、定位孔、椭圆孔、拉手条孔、ICT 孔、小背板固定孔、支架孔、导销孔、穿越孔等等非器件自带的孔,是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]丝印归属明确,无歧义是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]丝印未覆盖焊盘,避免与过孔重叠是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]丝印方向为从左到右、或者从下到上是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]母板已标注Front 、Back 是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]需拼版的已经正确拼板,且在装配图中注明拼版方式是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]焊接面及其相关层的光绘文件已镜像是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]异形孔、槽等已在DRILL 层中注明是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]尺寸标注完整、准确、没有封闭尺寸标注;尺寸推导参考点选取合理是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]特殊层厚、阻抗表述规范是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]光绘文件名称及图纸标注正确是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]板名正确,开发版本、生产版本已加是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]压缩文件名称正确,已加设计次数(投板)与版本信息(归档)文档规范性7是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]距BGA 器件2mm 以内区域无测试孔,过孔的元件面和焊接面阻焊都为0是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]测试孔间距≥50mil ,测试点上无丝印是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]测试孔与过孔已区分;且设置正确是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]测试孔已加,符合ICT 测试的规定,测试孔优选器件孔布线可测试性设计6是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]卧装晶体、卧装TO220封装三极管下,铺铜箔、开阻焊窗,接地或低电平,旁边走线尽量远离是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]焊接面贴片电阻、电容、电感焊盘间区域没有过孔是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]过孔间距≥8mil ,过孔与焊盘间距≥12mil是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]0805、0603、0402元件焊盘两端热容量一致是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]各个布线层的特征阻抗是否比较平滑是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]没有未被确认的开路线是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]总体布线均匀,布线尽可能短,且少过孔。

PCB SMT工艺评审要素表

素表

不满足的原因说明 工程部复核

2.屏蔽框的焊盘边缘离0402,0603阻容件的丝印框边缘不小于0.3mm,射频 部分不小于0.4mm 3.屏蔽框的边缘离射频部分天线开关,0805或更大尺寸电容等较高器件不小 于0.4mm (待定,暂不做为评审项) 4.屏蔽框的SOLDER MASK全开窗 1.注意后焊件的摆放方向,方向上要便于烙铁头下焊 2.注意后焊件的摆放位置,要考虑到焊接后是否容易处理好多余的线材,位 置上尽量不要太靠近PCB边角,防止装配中PCB将线材压断 3.手工焊接的PAD周边尽量为空,或空间尽量大,远离其它器件,避免焊接 时容易和其它器件连锡 (待定义出标准距离尺寸,可列为评审内容) 1.走线距离无焊盘、无电镀的孔的距离在0.3mm以上 2.镙钉孔离屏蔽框内边缘不小于 ??mm(距离标准定义后,可列为评审内 容) 3.丝印,SOLDER MASK的最小间距为0.2mm 1.SIM卡座定位PAD接地 2.芯片中心接地大于PAD接地 1.屏蔽框或所有元件需上锡膏焊接的PAD过孔是否合理,以免锡膏渗透(孔 距待定) 1.SMT元件及插脚元件的PAD铺铜连接方式设为十字形焊盘连接,不作为强制 评审项(RF和大功率例外) 1.是否有漏开窗的(如屏蔽框和特殊、异型PIN脚) 2.是否有位置不对的 3.沿板边框的GND开窗,注意不能开到线路上或元件PAD上 1.参照PCB 逐项检查是否有漏开窗的 2.注意跑道型孔/TFLASH是否增加开窗、手焊元件的开窗是否过大,是否需 要手动修改 3.是否有漏开窗的(如屏蔽框和特殊、异型PIN脚),屏蔽筐的钢网开窗应 比实际的屏蔽框宽0.4mm,但要距其他元件及其焊盘0.3mm 4.钢网的开孔不要有内角 5.碰触式元件的PAD,测试点,ESD PAD,不开钢网 6.屏蔽框的钢网开孔间距大于0.4mm 屏蔽框线条设计为0.8mm的宽度时,钢网开窗宽度的尺寸也按0.8mm宽度,不 能大于0.8mm,否则会锡膏过量,导致屏蔽罩难以装配,当屏蔽框线条小于 0.8mm时,钢网开窗适当加大 7.设计屏蔽罩的开窗时,在拐角处不需要开窗,因为拐角出屏蔽支架是避空 的,无法焊接 1.日期,版本号(阻焊层或丝印层)是否标识在可视区域,日期,版本是否 正确、应与所设计的文件名相符合,字符不能ONPAD 2.测试点是否有描述字符,极性元件是否有描述字符,是否摆放在合适位 置,不能ONPAD 3.底层的描述字符(版本号,测试点描述等)需作镜像处理 4.Drilldrawing层添加尺寸标注,若有添加叠构和PCB制作说明,需检查是 否为最新, 5.SIM卡座的外形和卡的外形需同时画出 6.丝印未上焊盘 7.丝印方向为从左到右、或者从下到上 8.丝印归属明确,无歧义 9.单板上已经放置了防静电标识 10.元件标注、丝印检查 11.板上面位号是否明确无重叠,遗漏 12.极性标注的完整性,检查有极性元件的极性标识是否清楚;列:二极 管,RF测试座,钽电容,滤波器,低噪声管,纽扣电池,LED,三极管等器件

PCB工艺设计评审表

结论说明

10 元件孔径是否符合设计要求(双引脚元件脚直径 d+0.2mm,多引脚 d+0.3mm )。 11 脚距偏差较大的器件,必须开椭圆孔。 12 波峰焊接工艺时散热器、变压器下方不允许开散热孔。 13 背光片、液晶、数码屏不允许设计成单端引脚,必须设计为两端引脚。 14 元件间距是否合理,有无影响其它元件插件。 15 元件丝印位置合理、清晰,无重叠、遮挡。 16 波峰工艺边设计是否合理,元件脚中心离板边最小为5mm。 17 波峰方向设计是否合理,是否有方向标识。 18 过波峰焊接时,PCB不规则时中间不允许有缺口,拼板用邮票孔保留PCB板材。 19 拼板对插件,过波峰是否有影响。 20 焊盘设计是否合理,(焊盘大小,泪滴焊盘)。 21 焊盘与焊盘间距小于1mm要加阻焊膜,减少连焊。 22 有后焊器件是否开了C形槽,使过波峰不堵孔。 23 单面板背焊插座,不允许开C槽过波峰,应贴美纹纸过波峰。 24 DIP芯片空脚可不放置焊盘,减少连焊。 散热面积如果太大,易产生锡尖不良和吃锡不均匀,建议采用1*4mm小块拼和结构或 25 用1mm宽的绿漆隔开 过波峰焊接的双面板,若板面有贴片IC,其引脚底部不能有过孔或者过孔一定要盖 26 绿油。 27 QFP封装元件必须波峰焊的话,QFP必须与进板方向呈45度,其4角必须有拖锡焊盘。 28 单个焊盘无连接,四周必须布铜,防止焊盘脱落。 29 PCB须预留三个以上的4mm测试定位孔,并且不能对称放置。 注: 请在对应的 中打“√”。 评审结论为“否”需在“结论说明”中注明内容实例,结论为“免”则PCB不需审核此项。

OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK OK

PCB设计评审表20090523

两个射频屏蔽框的接地应直接通过过孔打到主地,不与第一层的地相连,接地需要良好。 从电池连接器到PA、RF的LDO(低压差线性稳压器)和6305(6318)的线应按星型布线, 避免各电路通过电源系统相互干扰。 MT6139的26MHz晶体下面挖空,走线尽量细。 RF的LDO(低压差线性稳压器)要紧靠6319放。 MT6139的PIN10 和PIN14先连在一起,然后下主地。 将天线开关和 Transciever的地隔离开,分别与主地相连。 MT6139 的PIN1和 PIN40要单独接地,不要相互连接 除以上要求外,按照对应厂家提供的Layout guide检查,看是否有特殊要求 BB芯片的地脚要接地良好 BB 32KHZ晶体尽量靠近BB芯片,走线尽量短,其下面不要有走线特别是高速数字信号线 RECN/RECP,差分走线,上下左右包地,注意线宽 MICN0/MICP0,MICBIASP/MICBIASN,MICN1/MICP1,差分走线,上下左右包地 音频功放的接地要充分 AUDIO MP3_OUTL/MP3_OUTR,上下左右包地,注意线宽 注意音频功放的电源线和音频输出线的线宽 speaker/receiver磁珠,不要紧靠并排放置 PMIC下面尽量不要走线,并接地良好 给PA 供电的电源检查,注意线宽 电源跟电源之间最好有地线保护,电源跟地之间间距大于12mil以保证ESD性能. BYPASS电容的放置要尽量靠近IC管脚,容值越小的电容要越靠近,走线尽量短,电容的地脚 要直接打孔接到主地 电源 VCORE,VDD,AVDD,VMEM,线宽至少10mil 10mil PMIC_VTCXO,VISM线宽至少8mil 8mil VUSB,线宽至少15mil 充电线宽至少30mil BT及其周边元件下面L1/L2不要走其他部分的线,特别是高速数字信号线. BT天线信号线要走的尽量短,要走阻抗线 CHG_PUMP,VREF_CAP,MCG_CHG,TX_OUT旁的电容尽量靠近相应管脚,电容接地要好 TX_OUT线宽要大于10mil 模拟地和数字地要在第1层和第2层都割开,并都良好接地 BT 电源线要尽量远离天线信号线,1.8V电源要从电容C712分开走线到各个管脚,线宽都要大 于10mil 蓝牙环路滤波器:紧贴IC引脚布局和接地,下面不能走线,尤其是数字信号线 蓝牙晶体要尽量靠近6601,且第一二层挖空 1.8V电源要星型到各相关引脚;C711紧靠E1脚放防止DH1偏移。 FM及其周边元件下面L1/L2不要走其他部分的线,特别是高速数字信号线.

PCB设计评审检查清单(总表)

PCB设计检查清单(总表)一、资料输入阶段1.在流程上接收到的资料是否齐全(包括:原理图、*.brd文件、料单、PCB设计说明以及PCB设计或更改要求、标准化要求说明、工艺设计说明文件)2.确认PCB模板是最新的3. 确认模板的定位器件位置无误4.PCB设计说明以及PCB设计或更改要求、标准化要求说明是否明确5.确认外形图上的禁止布放器件和布线区已在PCB模板上体现6.比较外形图,确认PCB所标注尺寸及公差无误, 金属化孔和非金属化孔定义准确7.确认PCB模板准确无误后最好锁定该结构文件,以免误操作被移动位置二、布局后检查阶段a.器件检查8, 确认所有器件封装是否与公司统一库一致,是否已更新封装库(用viewlog检查运行结果)如果不一致,一定要Update Symbols9, 母板与子板,单板与背板,确认信号对应,位置对应,连接器方向及丝印标识正确,且子板有防误插措施,子板与母板上的器件不应产生干涉10, 元器件是否100% 放置11, 打开器件TOP和BOTTOM层的place-bound,查看重叠引起的DRC是否允许12, Mark点是否足够且必要13, 较重的元器件,应该布放在靠近PCB支撑点或支撑边的地方,以减少PCB的翘曲14, 与结构相关的器件布好局后最好锁住,防止误操作移动位置15, 压接插座周围5mm范围内,正面不允许有高度超过压接插座高度的元件,背面不允许有元件或焊点16, 确认器件布局是否满足工艺性要求(重点关注BGA、PLCC、贴片插座)17, 金属壳体的元器件,特别注意不要与其它元器件相碰,要留有足够的空间位置18, 接口相关的器件尽量靠近接口放置,背板总线驱动器尽量靠近背板连接器放置19, 波峰焊面的CHIP器件是否已经转换成波峰焊封装,20, 手工焊点是否超过50个21, 在PCB上轴向插装较高的元件,应该考虑卧式安装。

留出卧放空间。

并且考虑固定方式,如晶振的固定焊盘22, 需要使用散热片的器件,确认与其它器件有足够间距,并且注意散热片范围内主要器件的高度b.功能检查23, 数模混合板的数字电路和模拟电路器件布局时是否已经分开,信号流是否合理24, A/D转换器跨模数分区放置。

PCB图设计评审表

编号:

项目名称

产品型号

评审人员

评审日期

完整性评审

判断是否具备以下设计输出:

□PCB Layout图

□技术规格书

□电路原理图

□PCB板结构尺寸图(含限高图)

□该芯片方案的LAYOUT GUIDELINE资料

□此类型产品的LAYOUT规范

□所使用元器件的封装尺寸图

□连板图(含V-CUT方式尺寸)

□PCB制作规范

□其它:

总结:□本次设计输出完整□本次设计输出不完整

说明:

符合性评审

下列设计要求是否得到满足

□设计的PCB图是否符合和满足技术规格书的要求

□PCB设计是否正确

□PCB设计是否符合结构尺寸要求

□PCB设计是否符合该芯片方案的LAUOUT指引

□PCB设计是否符合该系列产品的LAYOUT规范

□PCB设计是否符合通用的LAYOUT规范

□上次评审须改进的缺陷得到纠正

□PCB板设计的成本可行性

□PCB板设计的生产可行性

□可检验性□产品可维修性□环境适应性□采购可行性

□元器件的封装尺寸是否正确

□连板图和PC工艺要求是否合理

□其他:

设计的缺陷/改进建议/总结:

结

论

该次评审是否通过

□YES设计总结:

□NO改进建议:

会签单位

硬件开发部/工业设计部/测试认证部/项目管理部/中试部

会签

研发总监

日期:

保存期:长期

电路板产前评审表格

测试考虑

合格/不合格

如测试点的布置,是否方便调试等

这个表格可以根据你的具体需求进行修改或扩展。例如,你可以添加额外的检查项,如耐久性测试、成本分析等。同时,你可以根据项目的具体情况,调整各项的检查侧重点。

电路板产前评审是一项重要的质量控制过程,它可以在生产前检查电路板设计的完整性,以减少潜在的错误和问题。以下是一个基本的电路板产前评审表格模板:

序号

评审项目

检查结果

备注

1

设计文件完整性

完整/不完整

包括原理图、BOM、PCB布局等

2

元器件选择

合适/不合适

可用性、适用性、规格等

3

布线规则遵守

是/否

如线宽、间距、层次设置等

4

功率和热设计

合格/不合格

考虑散热,热分布等

5

电源设计

合格/不合格

电源电压、电流、稳定性、噪声等

6

接口和连接器

合格/不合格

是否容易接入,标准化接口等

7

贴片和焊盘设计

合格/不合格

考虑元器件大小,焊盘大小、形状等

8

EMC/EMI设计

合格/不合格

如地层设计Hale Waihona Puke 滤波等9机械尺寸和位置

合格/不合格

是否满足封装需求,固定孔位置等

PCB评审要素表模板

发到加工厂进行工 艺审核 单板尺寸 单板设计 单板层数 单板设计 单板厚度 单板设计 单板设计 导线尺寸 单板设计 导线间距 定位孔位置及大小 单板设计 导通孔的最下尺寸 单板设计 埋孔、盲孔 单板设计 位置、尺寸 槽和缺口的尺寸 单板设计 通孔与焊盘的连接 单板设计 焊盘外形、尺寸 单板设计 单板设计 工艺边 2 单板设计 表面镀(涂)层 器件布局 单板设计 功能要求和加工工 艺角度 元器件体之间的布 单板设计 局距离 焊接方向和元器件 单板设计 排向 PCB与各种线缆的焊 单板设计 接 单板设计 插头插座的选择 单板设计 元器件封装尺寸 单板设计 丝印字体一致性 3 可安装性 便于安装、组合 DSP芯片选择 关键器件选型是 4 FPGA芯片选择 否符合系统要求 《TR3控制硬件评审要素表》

IPER

PCB评审要素表 PCB评审要素表

产品名称: ×××× 评审阶段 文件编号 版 本 号 研发TR■ 实 施 日 期 yyyy-mm-dd 序号 1 评审要素大类 加工厂审核 要素点 是否适用本项目 产品升级□ 保 密 等 级 □秘密 ■机密 □绝密 评审操作指导 加工工艺、可加工性 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 PCB设计要求 符合组装要求 重要程度 (ABC) ABC) 评审意见 评审结论 备 注 编 制 产品型号 审 核 总页数 批准

Page 1 of 3

HW-TR3-A

IPER

序号 AD芯片选择 电源模块 DSP模块 FPGA模块 AD模块 单板功能模块划 AD信号调理模块 分是否合理 数据RAM模块 电源故障检测模块 DA模块 光纤通讯模块 电源接口 电压采样接口 单板的外部接口 电流采样接口 设计是否合理 光纤通讯接口 232和485通讯接口 I/O接口 DSP与FPGA 单板的内部接口 DSP与RAM 设计是否合理 DSP与AD芯片 DSP与DA芯片 DSP JTAG 单板的调测接口 FPGA TTAG 设计是否合理 信号测试点 电源测试点 主电源芯片选择 电源设计 核心芯片电源选择 单板的安规,EMC PCB层数及定义 接地设计 设计是否合理 高热器件位置 散热设计 高热器件操作安装 散热片选择、安装 开发工具可操作 主控芯片 可编程逻辑门芯片 性是否容易 方便测试程度 可测试性 单板关键器件是 进行关键器件验证 否验证 器件选择采购评 可购买性、可替换 估 性 评审要素大类 否符合系统要求 要素点 是否适用本项目 评审操作指导 重要程度 ABC) (ABC) 评审意见 评审结论 备 注

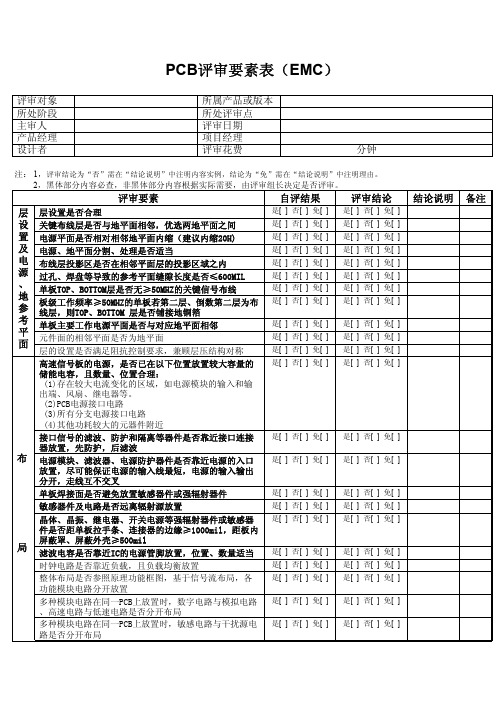

PCB评审要素表(EMC)

PCB 评审要素表(EMC )分钟评审花费设计者项目经理产品经理评审日期主审人 所处评审点所处阶段所属产品或版本评审对象 注: 1,评审结论为“否”需在“结论说明”中注明内容实例,结论为“免”需在“结论说明”中注明理由。

2,黑体部分内容必查,非黑体部分内容根据实际需要,由评审组长决定是否评审。

是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]多种模块电路在同一PCB上放置时,敏感电路与干扰源电路是否分开布局是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]多种模块电路在同一PCB上放置时,数字电路与模拟电路、高速电路与低速电路是否分开布局是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]整体布局是否参照原理功能框图,基于信号流布局,各功能模块电路分开放置是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]时钟电路是否靠近负载,且负载均衡放置是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]滤波电容是否靠近IC的电源管脚放置,位置、数量适当是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]晶体、晶振、继电器、开关电源等强辐射器件或敏感器件是否距单板拉手条、连接器的边缘≥1000mil,距板内屏蔽罩、屏蔽外壳≥500mil是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]敏感器件及电路是否远离辐射源放置是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]单板焊接面是否避免放置敏感器件或强辐射器件是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]电源模块、滤波器、电源防护器件是否靠近电源的入口放置,尽可能保证电源的输入线最短,电源的输入输出分开,走线互不交叉是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]接口信号的滤波、防护和隔离等器件是否靠近接口连接器放置,先防护,后滤波是[ ] 否[ ] 免[ ]是[ ] 否[ ] 免[ ]高速信号板的电源,是否已在以下位置放置较大容量的储能电容,且数量、位置合理:(1)存在较大电流变化的区域,如电源模块的输入和输出端、风扇、继电器等。

华为PCB设计评审要素表

14

是否针对PCB进行了DRC检查?

是[ ]否[ ]免[ ]

15

是否针对PCB进行了规范性检查?

是[ ]否[ ]免[ ]

16

是否进行了布线检视?是否有相关的检视记录?

是[ ]否[ ]免[ ]

17

PCB是否经过了工艺审查和装备审查?

是[ ]否[ ]免[ ]

18

是否用AVP或者其他工具进行了原理图验是否提供新器件、关键器件资料?

是[ ]否[ ]免[ ]

9

是否提供了BOM清单?

是[ ]否[ ]免[ ]

10

硬件经理是否指定了适当的测试经理、器件经理、成本经理、结构经理、EMC经理、热设计经理、BOM经理、工艺经理、装备经理等对投板申请进行审核,且各经理是否有意见反馈?PCB投板申请是否通过了总体组的审批?

是[ ]否[ ]免[ ]

19

是否用BOMStar或者其他工具进行了BOM检查?

是[ ]否[ ]免[ ]

20

《单板硬件调试和单元测试计划》是否更新并经过了检视?是否有相关的检视记录?

是[ ]否[ ]免[ ]

21

《单板硬件调试和单元测试计划》是否通过了评审?且参与评审是否涉及以下人员:单板硬件工程师、硬件测试工程师、CAD/SI工程师?

是[ ]否[ ]免[ ]

3

是否有原理图检视记录并且相关问题得到解决?

是[ ]否[ ]免[ ]

4

是否提供《单板SI工程设计方案》?

是[ ]否[ ]免[ ]

5

是否提供了《单板驱动规则设计要求表单》?

是[ ]否[ ]免[ ]

6

是否提供结构要素图?

是[ ]否[ ]免[ ]

PCB产品设计审核报告表

PCB产品设计审核报告产品型号:版本号:项目负责人: PCBLAYOUT:审核类别:□第一版的审核□第二版的审核□MP的审核□其他:PCB在服务器上的路径名说明:评审时需提供以下资料:1、PCB的客户结构图。

2、该PCB对应的原理图。

3、先一版本的PCBA。

(从第二版开始以后的版本)序号评审内容layout工程师项目工程师备注1 PCB文件结构与客户提供的结构图是否保持一致□OK □NG□OK □NG2 板卡命名是否为工程部授予的名字,设计日期及版本是否规范□OK □NG□OK □NG3 PCB设计是否标识好测试点□OK □NG□OK □NG4 测试点中心间距的最小距离大于2.0MM □OK □NG□OK □NG5 有高压输出是否标识清楚(),高压部分安全距离是否大于240Mil,开槽≥1.0MM。

高压输出电容为贴片封装时,电容两焊盘之间须开槽宽度不小于60MIL□OK □NG□OK □NG6 变压器下面禁止铺铜□OK □NG□OK □NG7 有金属与PCB接触的元件,元件与PCB(可铺白油)接触处禁止走线类如:SD卡座,GPS模块,电池区域等□OK □NG□OK □NG8 固定器件的连接座PIN1,是否特别注明,方向是否正确□OK □NG□OK □NG9 固定器件是否有放反,如该放TOP层的而放到了BOTTOM层□OK □NG□OK □NG10 PCB板上须卧倒的元件须标识卧倒方向□OK □NG□OK □NG11 不同的NET之间铺铜的间距最小为8Mil □OK □NG□OK □NG12 元件的接地焊盘禁止大面积铺铜(即"热焊盘"或"花孔") □OK □NG□OK □NG13 模拟地与数字地是否分开铺铜,所有的地线连接性是否足够强□OK □NG□OK □NG14 相邻PIN不允许垂于引脚相连□OK □NG□OK □NG15 走线不允许“┑”(直角)型或锐角走线□OK □NG□OK □NG16 是否有MARK点,且80mil范围内无走线、VIA及丝印□OK □NG□OK □NG17 贴片元件距板边间距:垂直时>60MIL;平行时>40Mil □OK □NG□OK □NG18 线路距板边距是否≥15Mil □OK □NG□OK □NG19 定位孔距器件或线路的安全距离是否大于15Mil,禁止布线□OK □NG□OK □NG20 过孔与焊盘相邻处最小间距边沿相距3MIL □OK □NG□OK □NG21 主电源线的宽度和其他网络间距是否足够宽□OK □NG□OK □NG22 过孔、焊盘最小内径8Mil,过孔的外径16Mil. □OK □NG□OK □NG23 主电源的滤波电容在电气上是否考虑充分利用,要靠近被滤波的元件摆放.□OK □NG□OK □NG24 Component place outline and silkscreen >=Component body□OK □NG□OK □NG25 元件丝印方向是否一致,由上向下,由左向右看□OK □NG□OK □NG26 PCB板丝印的字体是否一致□OK □NG□OK □NG27 字体大小不得小于Height:28Mil;Width:4Mil □OK □NG□OK □NG28 元件布局是否具有可维修性□OK □NG□OK □NG29 座子、定位孔是否依据客户结构要求,摆放位置是否正确□OK □NG□OK □NG30 座子第一脚与最后一脚是否正确,PIN1是否有特别表明□OK □NG□OK □NG31 保险管焊盘是否考虑散热□OK □NG□OK □NG32 测试点是否移动(已做测试架测试点不能移动)□OK □NG□OK □NG33 镙丝孔是否有遗失或是位置有改动, □OK □NG□OK □NG34 屏蔽罩的定位孔是否有遗失或是位置有改动□OK □NG□OK □NG35 定位孔和定位元件的定位脚是否有接地□OK □NG□OK □NG36 散热IC是否有加散热管脚□OK □NG□OK □NG37 散热器的放置是否有考虑利于对流□OK □NG□OK □NG38 温度敏感器是否有考虑远离热源□OK □NG□OK □NG 39元件是否方便生产(元件与元件的间距大小)□OK □NG□OK □NG40 元件封装有改动,PCB的元件库是否有更新□OK □NG□OK □NG41 PCB上元件管脚有更新,对应的原理图是否有更新□OK □NG□OK □NG42 PCB板边是否有包地和打过孔,防止EMI干扰□OK □NG□OK □NG43 PCB上元件是否有考虑机构的限高□OK □NG□OK □NG44 外接天线和差分信号线是否有做阻抗匹配的计算□OK □NG□OK □NG45 CPU输出的数据总线是否有做等长□OK □NG□OK □NG46 时钟信号线是否有包地处理□OK □NG□OK □NG47 声音信号线和视屏信号线是否有屏蔽□OK □NG□OK □NG48 声音信号线和视屏信号线旁是否有走高速数字信号线□OK □NG□OK □NG49 电源部分的信号线是否有加粗,有没有多打过孔连接. □OK □NG□OK □NG50 元件是否有叠加放置□OK □NG□OK □NG51 GND网络是否有多打过孔连接,减少信号的回路. □OK □NG□OK □NG52 网络是否有与前一个版本做比较(针对POWERPCB版本) □OK □NG□OK □NG53 是否有做DRC检查报告表□OK □NG□OK □NG54 高速信号线是否有走内层□OK □NG□OK □NG55 高速信号线是否有和普通的I/O线并走□OK □NG□OK □NG56 屏蔽罩外是否有走高速信号线□OK □NG□OK □NG57 开关电源的开关脚信号线是否走的太长□OK □NG□OK □NG58 高速信号线走线是否有考虑走线的合理性□OK □NG□OK □NG59 板边需加工艺边的方向,是否留了3毫米的没有放置元件□OK □NG□OK □NG60 工艺文件是否都按要求做了,阻抗控制的特殊信号是否有贴图?电池和SD卡座及其他特殊要求的丝印是否有贴图特别标明做黑油处理□OK □NG□OK □NG存在问题及改进的建议layout工程师:存在问题及改进的建议Layout主管:存在问题及改进的建议项目工程师:存在问题及改进的建议项目组长:评审结论:□通过□不通过,需再评审□修改后通过,无需再评审如果有问题需要修改,需对问题的处理结果给出解决方案后再对评审下结论评审组长:。

PCB评审表及Gerber文件生产资料规范v1[1]

![PCB评审表及Gerber文件生产资料规范v1[1]](https://img.taocdn.com/s3/m/bea3343e366baf1ffc4ffe4733687e21af45ff27.png)

LCD 焊盘要加长

核对结果

8

侧按键用PCB来做的时候,为了便于PCB焊接于主板上,主板上焊接 的PAD必须露铜直到靠近板边框

9

FM 2.2uH的封装为0806

10

6188的焊盘突出外形0.1-0.15mm

11

FPC侧按键

焊盘间距设计大于1.0mm,加定位焊盘,加丝印框辅助焊接定位

12

异形的PIN脚焊盘,采用PAD和SHAPE结合时,注意加铜皮的区域要 完整为整个异形焊盘形状,避免出现SOLDER或PASTE层不完整

3.SLOT槽尽量设计为包含于板框之内,避免板厂制作时引起铜翘

4.边框的格点最小为0.05mm,线宽0.01mm

1.测试座位置是否便于结构工程师设计壳料上的测试孔

4

GSM天线测试座,天线馈点 2.馈点位置尽量靠近板边框放置,馈点和GND盘的相对位置要便于

设计天线,馈点PAD的边缘距地的距离保持2.5mm以上

检查所有元件是否有正确的外 注意蓝牙滤波器的1脚标识(主料和替代料)

形边框,SMT方向标记或1脚标

记

注意射频部分天线测试座的SMT方向标识

注意触摸IC的1脚标识

检查有极性元件是否有正确极 二极管,RF测试座,钽电容,MIC,纽扣电池,喇叭,LED,三极管,霍尔

性标识

开关

手焊元件的PAD间距

PAD距PAD边缘间距尽量设计大于0.5mm,避免手工焊接时连锡

作去除绿油桥处理

1.0805的焊盘要兼容0603的焊盘,0603的焊盘要兼容0402的焊盘

评审结果及改进建议

元件的封装兼容性

2.射频部分PA的供电滤波电容尽量使用B SIZE,兼容0805封装

3.在结构和板空间允许的情况下,考虑纽扣电池和33uF电容封装的 兼容性

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCB设计评审记录表

项目名评审日期项目负责人

电子工程师结构工程

师PCB设计工程师

说明:

电子部分

评审内容评审意见确认人

封装

网表

网络表与原理图是否相符,元

件封装尺寸与实物是否相符

布局

元件布局是否疏密有序,满足

电气安全间距;同面元件无重

叠,异面元件无干涉

布线

关键信号线处理:

大电流信号线有足够的线宽

线距,敏感信号线远离干扰源

结构部分板框

板框与结构提供的板框一致,

定位孔尺寸、位置无偏差

元件

布局

禁布区无元件摆放,限高局域

按要求摆放,接插件定位元件

与结构提供的位置一致

生产工艺

S

M

T

元件摆放是否满足SMT工艺

要求

拼板方式

后焊

焊接点摆放位置方便焊接,周

边有足够距离方便焊接操作;

焊接点避免大面积铜皮导致

散热过快不易上锡

评审结论:□通过□修改后通过□严重缺陷评审员:

审核:。