04-Day1-Persistence-1.5h

nVent ERICO PlusCU 2L 6V 电源控制器操作指南说明书

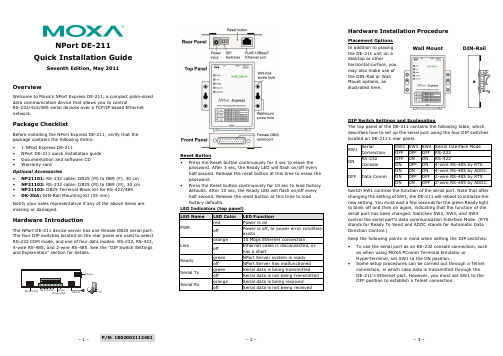

C o u n t -u p I g n i t i o n I n d i c a t o rT r i g g e r G u a r dT r i g g e rB a t t e r y D o o rB a t t e r y I n d i c a t o rC a d w e l d P l u s C u p C o n n e c t o rP L U S C U 2L 6P L U S C U 2L 15P L U S C U 2L 6N B P B P L U S C U 2L 6P B P L U S C U 2L 15P L U S C U 2R L D 6P L U S C U 2R L D 15L e a d C o n n e c t o rIndicator lights are flashing:The PlusCU uses an internal charging mechanism that sends an electric current to the Cadweld Plus cup. If the trigger on the control unit is pulled before the internal charging mechanism resets, the lights will flash. Wait 5 seconds and try again.If the error message persists, contact your nVent ERICO representative.PlusCU does not respond when trigger is pulled:If the unit does not respond, check battery status to determine if new batteries are needed.Cadweld Plus cup does not ignite:Disconnect the PlusCU lead from the PlusCU then re-examine your mold, weldmetal cup, ignition strip, and other Cadweld equipment to verify proper setup.If this issue persists, contact your nVent ERICO representative.PlusCU does not function properly at temperatures below 0° F [-18°C]:Alkaline batteries are not intended for extreme cold temperatures. nVent ERICOrecommends the use of lithium-ion batteries at temperatures below 0° F [-18°C].WARNING:nVent products shall be installed and used only as indicated in nVent product instruction sheets and training materials. Instruction sheets are available at and from your nVent customer service representative. nVent products must never be used for a purpose other than the purpose for which they were designed or in a manner that exceeds specified load ratings.2.All instructions must be completely followed to ensure proper and safe installation and performance.3.Improper installation, misuse, misapplication or other failure to completely follow nVent's instructions and warnings may cause product malfunction, property4.damage, serious bodily injury and/or death, and void your warranty.SAFETY INSTRUCTIONS:All governing codes and regulations and those required by the job site must be observed.Always use appropriate safety equipment such as eye protection, hard hat, and gloves as appropriate to the application.nVent, nVent CADDY, nVent ERICO Cadweld, nVent ERICO Critec, nVent ERICO, nVent ERIFLEX, and nVent LENTON are owned byHigh voltage electrical shock hazard. Keep hands and body clear of the cord(leads) while operating. Failure to do so can result in death or serious injury.Safety First!Personal SafetyWhen working with nVent ERICO Cadweld Plus, always use appropriate safety equipment suchas eye protection, heat-resistant gloves, and other PPE as appropriate to the application and required by local safety codes.Avoid contact with hot materials. Maintain safe working distance and secure footing whilewelding or working with hot materials.Welding material is a mixture of oxides and metal which react to produce hot molten materialwith temperatures in excess of 1400° C [2500° F] and a localized release of smoke. Thesereactions are not explosive and not known to be toxic. Ignition temperatures of weldingmaterial are in excess of 900° C [1650° F] and will not ignite under ambient conditions.For reduced or eliminated smoke options, contact nVent ERICO.。

JUMO 温度传感器说明书

Page 1/11Data Sheet 702040Blocks tructureFeature sk S tructured operating and programming layout k S elf-optimi s ation k Ramp functionk Timer functionk Digital input filter withprogrammable filter time con s tant k 1 limit comparator k limit s witchJUMO iTRON 04/08/16/32Compact microproce ss or controller sHou s ing for flu s h-panel mounting to DIN IEC 61554Brief de s criptionThe JUMO iTRON controller s erie s compri s e s univer s al and freely programmable com-pact in s trument s for a variety of control ta sks . It con s i s t s of five model s , with the bezel s ize s 96mm x 96mm, 96mm x 48mm in portrait and land s cape format, 48mm x 48mm and 48mm x 24mm.The controller s feature a clearly readable 7-s egment di s play which, depending on the ver-s ion, i s 10 or 20 mm high, for proce ss value and s etpoint indication or for dialog s . Only three k ey s are needed for configuration. Parameter s etting i s arranged dynamically, and after two operation-free s econd s the value i s accepted automatically. S elf-optimi s ation,which i s provided a s s tandard, e s tabli s he s the optimum controller parameter s by a k ey s tro k e. The ba s ic ver s ion al s o include s a ramp function with adju s table gradient s . A timer function ha s been integrated a s an extra.All controller s can be employed a s s ingle-s etpoint controller s with a limit comparator, or as double-s etpoint controller s . The lineari s ation s of the u s ual tran s ducer s are stored. Pro-tection i s IP66 at the front and IP20 at the bac k . The electrical connection i s by a plug-in connector with s crew terminal s .The input s and output s are s hown in the bloc k s tructure below.JUMO iTRON 08Type 702042JUMO iTRON 04Type 702044JUMO iTRON 08Type 702043JUMO iTRON 32Type 702040JUMO iTRON 16Type 702041Approval s /approval mark s (s ee "Technical data")Data Sheet 702040Page 2/11Technical dataThermocouple inputRe s i s tance thermometer inputStandard s ignal inputMea s urement circuit monitoring 1De s ignation Range 1Mea s urement accuracy Ambienttemperature error Fe-Con L Fe-Con J EN 60584Cu-Con U Cu-Con T EN 60584NiCr-Ni K EN 60584NiCr S i-Ni S i N EN 60584Pt10Rh-Pt S EN 60584Pt13Rh-Pt R EN 60584Pt30Rh-Pt6Rh BEN 60584-200to +900°C -200to +1200°C -200to +600°C -200to +400°C -200to +1372°C -100to +1300°C0— 1768°C 0—1768°C +300— 1820°C≤0.4%≤0.4%≤0.4%≤0.4%≤0.4%≤0.4%≤0.4%≤0.4%≤0.4%100 ppm/°C 100 ppm/°C 100 ppm/°C 100 ppm/°C 100 ppm/°C 100 ppm/°C 100 ppm/°C 100 ppm/°C 100 ppm/°CCold junctionPt 100 internal1. The s e range s refer to the ambient temperature of 20°CDe s ignation Connection type RangeMea s urement accuracy Ambienttemperature error Pt 100 EN 607512-/3-wire -200to +850°C ≤0.1%50 ppm/°C Pt 1000 EN 607512-/3-wire -200to +850°C ≤0.1%50 ppm/°C K TY11-62-wire-50to +150°C≤1.0%50 ppm/°CS en s or lead re s i s tance 20Ω max. per lead for 2- and 3-wire circuitMea s urement current 250µALead compen s ationNot required for 3-wire circuit. For 2-wire circuit, lead compen s ation can be implemented in s oftware through proce ss value correction.De s ignation RangeMea s urement accuracy Ambienttemperature error Voltage0—10V , input re s i s tance R E > 100k Ω2—10V , input re s i s tance R E > 100k Ω0—1V , input re s i s tance R E > 10M Ω10,2—1V , input re s i s tance R E > 10M Ω1≤0.1%≤0.1%≤0.1%≤0.1%100 ppm/°C 100 ppm/°C 100 ppm/°C 100 ppm/°C Current4—20mA, voltage drop 3V max.0—20mA, voltage drop 3V max.≤0.1%≤0.1%100 ppm/°C 100 ppm/°C1. for Type 702040/41 with 2 relay output s (option)Tran s ducer Overrange/underrangeProbe /lead s hort-circuit 1Probe/lead breakThermocouple•-•Re s i s tance thermometer •••Voltage 2—10V / 0.2—1V0—10V/ 0—1V •••-•-Current4—20mA 0—20mA•••-•-1. In the event of a fault, the output s move to a defined s tatu s (configurable).= factory s etting •recogni s ed-not recogni s edData Sheet 702040Page 3/11Output sControllerTimerElectrical dataHou s ingA ss ignment Type 702040/41Type 702042/43/44Output 1relayrelay Output 2logic 0/5V or logic input logic 0/5V Output 2 (option)logic 0/12V or logic input logic 0/12V Output 2 (option)relay not po ss ible Output 3not availablerelayTechnical data Relay ratingcontact life n.o. (ma k e) contact 3A at 250VAC re s i s tive load 150 000 operation s at rated loadLogiccurrent limiting load re s i s tance 0/5V 20mAR load 250Ω min .Logiccurrent limiting load re s i s tance 0/12V 20mAR load 600Ω min.= factory s ettingController types ingle-s etpoint controller with limit comparator, double-s etpoint controllerController s tructure s P/PD/PI/PIDA/D converter re s olution better than 15 bitS ampling time210m s ec/250m s ec with activated timer functionAccuracy0.7% ± 10ppm/°CS upply (s witch-mode power s upply)110—240V -15/+10%AC 48—63Hz, or 20—30V AC/DC 48—63Hz, or10—18V DC (Connection to S ELV or PELV)Te s t voltage s (type te s t)to EN 61010, Part 1, March 1994,overvoltage category II, pollution degree 2, for Type 702040/41overvoltage category III, pollution degree 2, for Type 702042/43/44Power con s umption max. 7VA Data bac k upEEPROMElectrical connectionat the rear, via plug-in s crew terminal s ,conductor cro ss -s ection up to 1.5mm 2 (1.0mm 2 for Type 702040/41) or2x 1.5mm 2 (1.0mm 2 for Type 702040/41) with ferrule sElectromagnetic compatibility interference emi ss ion interference immunity EN 61 326Cla ss Bto indu s trial requirement sS afety regulationto EN 61010-1In s tallation height maximum 2000 m above s ea levelCa s e typePla s tic ca s e for panel mounting acc to. IEC 61554 (indoor u s e)Dimen s ion s in mm (for Type)702040702041702042702043702044Bezel s ize48x 2448x 4848x 96(portrait)96x 48(land s cape)96x 96Depth behind panel100100707070Panel cut-out45+0.6x 22.2+0.345+0.6x 45+0.645+0.6x 92+0.892+0.8x 45+0.692+0.8x 92+0.8Ambient/s torage temperature range 0—55°C /-40 to +70°CData Sheet 702040Page 4/11Approval s /approval mark sDi s play and control sSelf-optimi s ation (SO)The s tandard s elf-optimi s ation facility produce s an automatic adju s tment of the controller to the proce ss .S elf-optimi s ation determine s the controller parameter s for PI and PID controller s (proportional band, re s et time, derivative time), a s well a s the cycle time and the filter time con s tant of the digital input filter.Ramp functionClimatic condition s not exceeding 75% rel. humidity, no conden s ationOperating po s ition unre s tricted Protection to EN 60529,IP66 at the front, IP20 at the bac kWeight75g approx.95g approx.145g approx.160g approx.200g approx.Approval mark Te s ting agencyCertificate/certification numberIn s pection ba s i sValid forUL Underwriter Laboratorie s E201387UL 61010-1all device s C S A C S A-Approval232831CAN/C S A-C22.2No. 61010.1-04all device sData Sheet 702040Page 5/11Limit comparatorLimit s witch (extra code)If the limit comparator function i s active, then the s witched s tate will have to be re s et by hand.Precondition: the condition that cau s ed the alarm i s no longer pre s ent (for l k 8: proce ss value < AL). The di s play s how s the alarm s tatu s .The alarm s tatu s will be retained after a power failure.Timer function (extra code)U s ing the timer function, the control action can be influenced by mean s of the adju s table time t i 0. After the timer ha s been s tarted by power ON, by pre ss ing the k ey or via the logic input, the timer s tart value t i 0 i s counted down to 0, either in s tantly or after the proce ss value ha s gone above or below a programmable tolerance limit. When the timer ha s run down, s everal event s are triggered, s uch a s control s witch-off (output 0%) and s etpoint s witching. Furthermore, it i s po ss ible to implement timer s ignalling during or after the timer count, via an output.The timer function can be u s ed in conjunction with the ramp function and s etpoint s witching.Table: Timer function s (u s ing the example of a rever s ed s ingle-s etpoint controller)Data Sheet 702040Page 6/11Tolerance limitThe po s ition of the tolerance limit depend s on the controller type:- S ingle-s etpoint controller (rever s ed, heating): Tolerance limit i s below the s etpoint - S ingle-s etpoint controller (direct, cooling): Tolerance limit i s above the s etpoint - Double-s etpoint controller: Tolerance limit i s below the s etpointIf, during the control proce ss , the proce ss value goe s above/below the tolerance limit, then the timer will be s topped for the duration of the infringement.Di s play and operationThe timer value i s di s played at the operating level and remain s s o permanently (no time-out).Operation i s from the k eypad, when the timer value i s vi s ible in the di s play, or via the logic input. The operating option s compri s e s tart,s top, continue and cancel timer function, and are s hown differently in the di s play.The current timer value and the timer s tart value are acce ss ible and adju s table at any time at a s eparate timer level.Data Sheet 702040Page 7/11Parameter and configurationOperating levelParameter levelConfiguration levelDe s ignation Di s play Factory s ettingValue range S etpointSP /SP1/SP20S PL—S PH Ramp s etpointSPr 0S PL—S PH Timer value/timer s tart valuet i /t i 00 —999.9hDe s ignation Di s play Factory s ettingValue range S etpoint 1SP 10S PL—S PH S etpoint 2SP 20S PL—S PH Limit value for limit comparator AL 0-1999to +9999digit Proportional band 1Pb:100—9999digit Proportional band 2Pb:200—9999digit Derivative time dt 80s ec 0—9999s ec Re s et time rt 350s ec 0—9999s ec Cycle time 1CY 120.0s ec 1.0—999.9s ec Cycle time 2CY 220.0s ec1.0—999.9s ec Contact s pacingdb 00—1000digit Differential (hy s tere s i s ) 1HYS.110—9999digit Differential (hy s tere s i s ) 2HYS.210—9999digit Wor k ing point Y:00%-100to +100%Maximum output Y:1100%0to 100%Minimum output Y:2-100%-100to +100%Filter time con s tant dF 0.6s ec 0.0—100.0s ec Ramp s loperASd—999digitDe s ignation Di s play Factory s etting Value range/s electionTran s ducerC111Pt100Pt100, Pt1000, K TY11-6, T, J, U, L, K , S ,R, B, N, 0 (4)—20mA, 0 (2)—10VDecimal place/unitC112none/°C none, one, two/°C, FController type/output s C113s ee table on next pageLimit comparator function C114no function no function, l k 1—8Ramp functionC115no function no function, °C/min, °C/h Output s ignal on overrange/ underrange C1160% output limit comparator off 0%, 100%, -100% limit comparator on/offLogic inputC117no function k ey / level inhibit,ramp s top, s etpoint s witchingOutput s 1, 2 and 3(only Type 702042/43/44)C118function s a s defined under C113freely configurable(s ee table on next page)Timer functionC120no function s ee de s cription “Timer function”S tart condition for timerC121from k eypad/logic input - power ON - k eypad/logic input- tolerance limitTimer s ignalling C122no function - timer s tart to timer run-down- after run-down for 10s ec - after run-down for 1 min.- after run-down until ac k nowledgementUnit of time (timer)C123mm.ss - mm.ss- hh.mm - hhh.hS tart value of value range SCL0-1999 to +9999 digitData Sheet 702040Page 8/11Controller type/output s (C 113)Expanded configuration option s for the output s on Type 702043/44 (C118)End value of value range SCH 100-1999 to +9999 digit Lower s etpoint limit SPL -200-1999 to +9999 digit Upper s epoint limitSPH 850-1999 to +9999 digit Proce ss value correction OFFS 0-1999 to +9999 digit Differential (hy s tere s i s )HySt 1 0—9999 digitController typeOutput 1Output 2 + 3S ingle s etpoint rever s ed controller limit comparator/timer s ignalling S ingle s etpoint direct controllerlimit comparator/timer s ignallingDouble s etpointcontroller rever s edcontroller direct S ingle s etpoint rever s ed limit comparator/timer s ignalling controller S ingle s etpoint direct limit comparator/timer s ignallingcontrollerDouble s etpoint controller directcontroller rever s ed= factory s ettingOutput 1: Relay (K1)Output 2: Logic (K2)Output 3: Relay 1-s e t p o i n t c o n t r o l l e rFunction s of the output s a s defined under C 113controller output limit comparator timer s ignalling controller output timer s ignalling limit comparator limit comparator controller output timer s ignalling limit comparator timer s ignalling controller output timer s ignalling controller output limit comparator timer s ignalling limit comparator controller output 2-s e t p t .c o n t r o l l e rcontroller output 1controller output 2limit comparator/timer controller output 1limit comparator/timer controller output 2controller output 2controller output 1limit comparator/timer controller output 2limit comparator/timer controller output 1limit comparator/timer controller output 1controller output 2limit comparator/timercontroller output 2controller output 1Data Sheet 702040Page 9/11Dimen s ion sType 702040 / …Type 702043/...Type 702041 / …Type 702044/...Type 702042 / …Typehorizontal vertical 70.2040/418mm min.8mm min.70.2042/43/4410mm min.10mm min.Edge-to-edge mounting(minimum s pacing s of the panel cut-out s)Data Sheet 702040Page 10/11Connection diagram sJUMO iTRON 32, Type 702040, 48mm x 24mm format JUMO iTRON 16, Type 702041, 48mm x 48mm formatJUMO iTRON 08, Type 702042, 48mm x 96mm format (portrait)JUMO iTRON 08, Type 702043. 96mm x 48mm format (land s cape)JUMO iTRON 04, Type 702044, 96mm x 96mm formatStandard ver s ion / Ver s ion with 12V logic outputVer s ion with 2 relay outputs2014-09-01/00357838Data Sheet 702040Page 11/11Order detail sExtra order code s for cu s tomized configuration(2)Ba s ic type exten s ion(3)Input s(1)(2)(3)(4)(5)(6)Type de s ignation 7020../..-...-...-../...,...** Li s t extra code s in s equence, s eparated by comma s(1)Ba s ic type(bezel s ize in mm)40=48x 24, 41 = 48x 48, 42 = 48x 96 (portrait), 43 = 96x 48 (land s cape), 44 = 96x 96(2)Ba s ic typeexten s ion 8899==controller type configurable 1controller type configured to cu s tomer s pecification 2(3)Input s 888999==input s configurable 1input s configured to cu s tomer s pecification 2(4)Output s000=S tandardType 702040/41Type 702042/43/44Output 1relay (n.o. ma k e)relay (n.o. ma k e)Output 2logic 0/5V , optionally configurable a s logic input logic 0/5V Output 3not available relay (n.o. ma k e)Option sType 702040/41Type 702042/43/44113=Output 2(output s 1+3 a s for S tandard)logic 0/12V , optionally configurable a s logic input logic 0/12V 101=Output 2(output 1 a s for S tandard)relay (n.o. ma k e)(logic input i s alway s available)not po ss ible(5)Supply162523===10—18V DC20—30V AC/DC 48—63Hz110—240V AC -15/+10% 48—63Hz (6)Extra code069=UL and C S A approval 210=Timer function220=Timer function + limit s witch 3Delivery package ex-factory for Type 702040/41Type 702042/43/441 mounting frame2 mounting brac k et s1 s eal, 1 Operating In s truction s 70.20401. s ingle-s etpoint with limit comparator, s ee factory s etting s under configuration and parameter level2. s ee extra order code s (below) or factory s etting s under configuration and parameter level3. The linearization s for K TY11-6 and thermocouple B have been deletedController typeOutput 1Output 2 and 310=s ingle s etpoint rever s ed 1controller limit comparator/timer s ignalling 11=s ingle s etpoint direct 2controllerlimit comparator/timer s ignalling 30=double s etpoint controller rever s edcontroller direct 20=s ingle s etpoint rever s ed 1limit comparator/timer s ignalling controller 21=s ingle s etpoint direct 2limit comparator/timer s ignalling controller33=double s etpointcontroller directcontroller rever s ed1. controller output i s active when proce ss value i s below s etpoint, e. g. heating2. controller output i s active when proce ss value i s above s etpoint, e. g. cooling001=Pt1003-wire 040=Fe-Con J 045=Pt13 Rh-Pt R 063=0—10V 003=Pt1002-wire041=Cu-Con U 046=Pt30 Rh-PtRh B 071=2—10V 005=Pt1000 2-wire 042=Fe-Con L 048=NiCr S i-Ni S i N601=K TY11-6 (PTC)006=Pt1000 3-wire 043=NiCr-Ni K 052=0—20mA 039=Cu-Con T044=Pt10Rh-PtS053=4—20mA= factory-s et。

ecl-学习

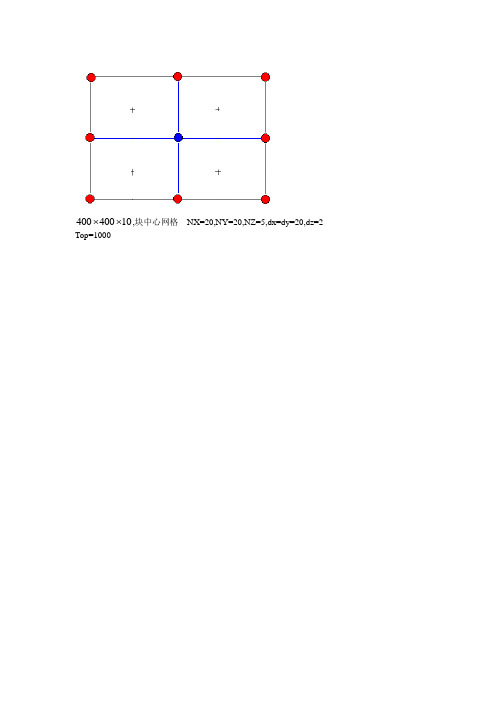

⨯⨯,块中心网格NX=20,NY=20,NZ=5,dx=dy=20,dz=2 40040010Top=1000E和F为什么是这样的?1、用Schedule建立一个基本的Project1.建立一个基本工程(Project)并保存生产数据:后缀为*.VOL or *.vol井的参数:后缀为*.EV or *.ev,包括射孔(perforation)、堵孔(well squeeze)、酸化(acidise)等。

井的几何参数:后缀为*.TRJ or *.trj;*.CNT or *.cnt;*.NET or *.net;*.LYR or *.lyr;网格参数:后缀为*.*GR* or *.*gr*地层特性:后缀为*.*IN* or *.*in*2.输入井的生产历史(Production History)加载后缀为*.vol的数据文件3.输入井的事件数据(Events Data)加载后缀为*.ev数据文件,包括射孔(perforation)、堵孔(well squeeze)、酸化(acidise)等。

4.输入控制网络数据(Control Network)加载后缀为*.net的数据文件5.输入网格参数(Importing a Grid)加载后缀为*.*gr*即.fgrid的数据文件6.定义井的轨迹(Trajectories)(1) 通过输入井的井斜检测(Deviation Survey)数据计算井的轨迹Schedule加载的这些网格特性数据是由INIT文件提供的,INIT数据文件是通过Eclipse非模拟(NOSIM)数据设置运行而产生的,有两种方式:一种是在GRID部分用INIT关键字运行而产生的;另一种是在RUNSPEC部分运用NOSIM关键字运行而产生的。

在加载数据以前,必须有以下资料:•加载的网格文件(这些网格文件由Eclipse或者GRID软件或其它相关软件运行产生的);•读入的网格特性文件(Eclipse INIT文件);•所要输入的井斜检测数据(由Eclipse 产生的后缀为*.cnt的文件)。

USB Mass Storage Class Bulk Only Transport

Universal Serial Bus Mass Storage Class Bulk-Only TransportRevision 1.0September 31, 1999Change HistoryRevision Issue Date Comments0.7September 23, 1998Initial draft, pre-release0.8October 6, 1998Revisions made at the Mass Storage DWG review – Irvine, CA0.9October 21, 1998Revisions made at the Mass Storage DWG review – Plano, TX0.9a January 5, 1999Revisions made at the Mass Storage DWG review – Tigard, OR0.9b February 1, 1999Additions of LUN support - Milpitas, CA1.0[RC1]March 5, 1999RR review - Midway, UT1.0[RC2]March 23, 1999Revisions from reflector review comments1.0[RC3]March 29, 1999Specification line by line review – Milpitas, CA1.0[RC4]June 21, 1999Specification line by line review – RR21 – Milpitas, CA1.0September 31, 1999Final Revision edits for Released Document – SLC, UTUSB Device Class Definition for Mass Storage DevicesCopyright © 1998, 1999, USB Implementers Forum.All rights reserved.INTELLECTUAL PROPERTY DISCLAIMERTHIS SPECIFICATION IS PROVIDED “AS IS” WITH NO WARRANTIES WHATSOEVER INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE.A LICENSE IS HEREBY GRANTED TO REPRODUCE AND DISTRIBUTE THIS SPECIFICATION FOR INTERNAL USE ONLY. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY OTHER INTELLECTUAL PROPERTY RIGHTS IS GRANTED OR INTENDED HEREBY.AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF PROPRIETARY RIGHTS, RELATING TO IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. AUTHORS OF THIS SPECIFICATION ALSO DO NOT WARRANT OR REPRESENT THAT SUCH IMPLEMENTATION(S) WILL NOT INFRINGE SUCH RIGHTS.ContributorsAl Rickey, Phoenix TechnologiesAlan Haffner, Lexar MediaBill Stanley, AdaptecCalaimany Bhoopathi, Shuttle TechnologyCurtis E. Stevens, Phoenix TechnologiesDarrell Redford , Iomega CorporationDave Gilbert, In-System DesignDavid G. Lawrence, Global Technology Development David L. Jolley, Iomega CorporationDavid Luke, In-System DesignEric Luttman, In-System DesignGlen Slick, Microsoft CorporationHiromichi Oribe, Hagiwara Sys-ComCoJan Matejica, PIMC/PhilipsJim Blackson, Y-E Data, IncJim Quigley, Iomega CorporationJohan Craeybeckk, PIMC/PhilipsJordan Brown, Sun MicrosystemsKenny Chu, Hagiwara Sys-ComCoKenichi Hamada, Y-E Data, IncMark Williams, Microsoft CorporationMasayuki Kitagawa, MitsumiMike Chen, CMD Technology Mike Glass, Microsoft Corporation Mike Liebow, eTEK LabsMike Nguyen, TEACMike Poulsen, Iomega Corporation Moto Watanabe, HagiwaraN.R. Devanathan, Shuttle Technology Paramita Das, Sun MicrosystemsPat LaVarre, Iomega Corporation Peter S'Heeren, PIMC/PhilipsRyota Okazaki, NEC Corporation Sadao Yabuki, TEACShigeyoshi Hashi, NEC Corporation Shing F. Lin, AdaptecSteve Bayless, Hewlett-Packard Steve Kolokowsky, Anchor Chips Steven Smith, eTEK LabsTerry Moore, MCCITim Bradshaw, Iomega Corp Toyoko Shimizu, Y-E Data, Inc Trenton Henry, SMSCTroy Davidson, Iomega Corporation Tsuyoshi Osawa, TEACYuji Oishi, Hagiwara Sys-Com Co LtdTable of Contents1Specification Overview and Scope (5)1.1Scope (5)2Terms and Abbreviations (6)2.1Conventions (6)2.2Definitions (6)3Functional Characteristics (7)3.1Bulk-Only Mass Storage Reset (class-specific request) (7)3.2Get Max LUN (class-specific request) (7)3.3Host/Device Packet Transfer Order (8)3.4Command Queuing (8)3.5Bi-Directional Command Protocol (8)4Standard Descriptors (9)4.1Device Descriptor (9)4.1.1Serial Number (9)4.1.2Valid Serial Number Characters (10)4.2Configuration Descriptor (10)4.3Interface Descriptors (11)4.4Endpoint Descriptors (11)4.4.1Bulk-In Endpoint (11)4.4.2Bulk-Out Endpoint (12)5Command/Data/Status Protocol (13)5.1Command Block Wrapper (CBW) (13)5.2Command Status Wrapper (CSW) (14)5.3Data Transfer Conditions (15)5.3.1Command Transport (15)5.3.2Data Transport (15)5.3.3Status Transport (16)5.3.4Reset Recovery (16)6Host/Device Data Transfers (17)6.1Overview (17)6.2Valid and Meaningful CBW (17)6.2.1Valid CBW (17)6.2.2Meaningful CBW (17)6.3Valid and Meaningful CSW (17)6.3.1Valid CSW (17)6.3.2Meaningful CSW (17)6.4Device Error Handling (17)6.5Host Error Handling (18)6.6Error Classes (18)6.6.1CBW Not Valid (18)6.6.2Internal Device Error (18)6.6.3Host/Device Disagreements (18)6.6.4Command Failure (18)6.7The Thirteen Cases (18)6.7.1H n - Host expects no data transfers (19)6.7.2H i - Host expects to receive data from the device (20)6.7.3H o - Host expects to send data to the device (21)List of TablesTable 3.1 – Bulk-Only Mass Storage Reset (7)Table 3.2 –Get Max LUN (7)Table 4.1 - Device Descriptor (9)Table 4.2 - Example Serial Number Format (10)Table 4.3 - Valid Serial Number Characters (10)Table 4.4 - Configuration Descriptor (10)Table 4.5 – Bulk-Only Data Interface Descriptor (11)Table 4.6 - Bulk-In Endpoint Descriptor (11)Table 4.7 – Bulk-Out Endpoint Descriptor (12)Table 5.1 - Command Block Wrapper (13)Table 5.2 - Command Status Wrapper (14)Table 5.3 - Command Block Status Values (15)Table 6.1 - Host/Device Data Transfer Matrix (19)List of FiguresFigure 1 - Command/Data/Status Flow (13)Figure 2 - Status Transport Flow (15)1 Specification Overview and Scope1.1ScopeA familiarity with the USB1.0 and 1.1Specifications and the USB Mass Storage Class Specification Overview is assumed.This specification addresses Bulk-Only Transport, or in other words, transport of command, data, and status occurring solely via Bulk endpoints (not via Interrupt or Control endpoints). This specification only uses the default pipe to clear a STALL condition on the Bulk endpoints and to issue class-specific requests as defined below. This specification does not require the use of an Interrupt endpoint.This specification defines support for logical units that share common device characteristics. Although this feature provides the support necessary to allow like mass storage devices to share a common USB interface descriptor, it is not intended to be used to implement interface bridge devices.2 Terms and Abbreviations2.1ConventionsNumbers without annotation are decimal -----------------------------------------------1, 17, 23Hexadecimal numbers are followed by an ‘h’-------------------------------------------1Fh, FCh, 38hBinary numbers are followed by a ‘b’----------------------------------------------------011b, 101b, 01110010b Words in italics indicate terms defined by USB or by this specification-----------bRequest, dCSWTag2.2DefinitionsCommand Block Wrapper (CBW)A packet containing a command block and associated information.Command Status Wrapper (CSW)A packet containing the status of a command block.Data-InIndicates a transfer of data IN from the device to the host.Data-OutIndicates a transfer of data OUT from the host to the device.Device RequestRequests from the host to the device using the default pipe.Phase ErrorAn error returned by the device indicating that the results of processing further CBWs will beindeterminate until the device is reset.ProcessedData received and controlled internally by the device to the point that the host need no longer beconcerned about it.RelevantThe amount of the data sent to the host by the device that is significant.Reset RecoveryAn error recovery procedure by which the host prepares the device for further CBWs.Thin DiagonalCases where the host and device are in complete agreement about the data transfer. See Chapter 6 -Host/Device Data Transfers, for additional information regarding error cases and the "thin diagonal."3 Functional Characteristics3.1Bulk-Only Mass Storage Reset (class-specific request)This request is used to reset the mass storage device and its associated interface.This class-specific request shall ready the device for the next CBW from the host.The host shall send this request via the default pipe to the device. The device shall preserve the value of its bulk data toggle bits and endpoint STALL conditions despite the Bulk-Only Mass Storage Reset.The device shall NAK the status stage of the device request until the Bulk-Only Mass Storage Reset is complete. To issue the Bulk-Only Mass Storage Reset the host shall issue a device request on the default pipe of:•bmRequestType: Class, Interface, host to device•bRequest field set to 255 (FFh)•wValue field set to 0•wIndex field set to the interface number•wLength field set to 0Table 3.1 – Bulk-Only Mass Storage ResetbmRequestType bRequest wValue wIndex wLength Data00100001b11111111b0000h Interface0000h none3.2Get Max LUN (class-specific request)The device may implement several logical units that share common device characteristics. The host uses bCBWLUN (see 5.1 Command Block Wrapper (CBW)) to designate which logical unit of the device is the destination of the CBW. The Get Max LUN device request is used to determine the number of logical units supported by the device. Logical Unit Numbers on the device shall be numbered contiguously starting from LUN 0 to a maximum LUN of 15 (Fh).To issue a Get Max LUN device request, the host shall issue a device request on the default pipe of:•bmRequestType: Class, Interface, device to host•bRequest field set to 254 (FEh)•wValue field set to 0•wIndex field set to the interface number•wLength field set to 1Table 3.2 –Get Max LUNbmRequestType bRequest wValue wIndex wLength Data10100001b11111110b0000h Interface0001h 1 byteThe device shall return one byte of data that contains the maximum LUN supported by the device. For example, if the device supports four LUNs then the LUNs would be numbered from 0 to 3 and the return value would be 3. If no LUN is associated with the device, the value returned shall be 0. The host shall not send a command block wrapper (CBW) to a non-existing LUN.Devices that do not support multiple LUNs may STALL this command.3.3Host/Device Packet Transfer OrderThe host shall send the CBW before the associated Data-Out, and the device shall send Data-In after the associated CBW and before the associated CSW. The host may request Data-In or CSW before sending the associated CBW.If the dCBWDataTransferLength is zero, the device and the host shall transfer no data between the CBW and the associated CSW.3.4Command QueuingThe host shall not transfer a CBW to the device until the host has received the CSW for any outstanding CBW. If the host issues two consecutive CBWs without an intervening CSW or reset, the device response to the second CBW is indeterminate.3.5Bi-Directional Command ProtocolThis specification does not provide for bi-directional data transfer in a single command.4 Standard DescriptorsThe device shall support the following standard USB descriptors:•Device. Each USB device has one device descriptor (per USB Specification).•Configuration. Each USB device has one default configuration descriptor, which supports at least one interface.•Interface. The device shall support at least one interface, known herein as the Bulk-Only Data Interface. Some devices may support additional interfaces, to provide other capabilities.•Endpoint. The device shall support the following endpoints, in addition to the default pipe that is required of all USB devices:(a)Bulk-In endpoint(b)Bulk-Out endpointSome devices may support additional endpoints, to provide other capabilities. The host shall use thefirst reported Bulk-In and Bulk-Out endpoints for the selected interface.•String. The device shall supply a unique serial number as detailed in 4.1.1 - Serial Number.This specification defines no class-specific descriptors.The rest of this section describes the standard USB device, configuration, interface, endpoint, and string descriptors for the device. For superseding information about these and other standard descriptors, see Chapter 9, “USB Device Framework,” of the USB Specification.4.1Device DescriptorEach USB device has one device descriptor (per USB Specification). The device shall specify the device class and subclass codes in the interface descriptor, and not in the device descriptor.Table 4.1 - Device DescriptorOffset Field Size Value Description0bLength Byte12h Size of this descriptor in bytes.1bDescriptorType Byte01h DEVICE descriptor type.2bcdUSB Word????h USB Specification Release Number in Binary-Coded Decimal(i.e. 2.10 = 210h). This field identifies the release of the USBSpecification with which the device and is descriptors arecompliant.4bDeviceClass Byte00h Class is specified in the interface descriptor.5bDeviceSubClass Byte00h Subclass is specified in the interface descriptor.6bDeviceProtocol Byte00h Protocol is specified in the interface descriptor.7bMaxPacketSize0Byte??h Maximum packet size for endpoint zero. (only 8, 16, 32, or 64are valid (08h, 10h, 20h, 40h)).8idVendor Word????h Vendor ID (assigned by the USB-IF).10idProduct Word????h Product ID (assigned by the manufacturer).12bcdDevice Word????h Device release number in binary-coded decimal.14iManufacturer Byte??h Index of string descriptor describing the manufacturer.15iProduct Byte??h Index of string descriptor describing this product.16iSerialNumber Byte??h Index of string descriptor describing the device’s serial number.(Details in 4.1.1 below)17bNumConfigurations Byte??h Number of possible configurations.NOTE:Information in this table is from the USB Specification version 1.1 table 9-7. Bold text has been added for clarifications when using these descriptors with this specification.4.1.1Serial NumberThe iSerialNumber field shall be set to the index of the string descriptor that contains the serial number. The serial number shall contain at least 12 valid digits, represented as a UNICODE string. The last 12 digits of the serial number shall be unique to each USB idVendor and idProduct pair.The host may generate a globally unique identifier by concatenating the 16 bit idVendor, the 16 bit idProduct and the value represented by the last 12 characters of the string descriptor indexed by iSerialNumber.The field iSerialNumber is an index to a string descriptor and does not contain the string itself. An example format for the String descriptor is shown below.Table 4.2 - Example Serial Number FormatOffset Field Size Value Description0bLength Byte??h Size of this descriptor in bytes - Minimum of 26 (1Ah)1bDescriptorType Byte03h STRING descriptor type2wString1Word00??h Serial number character 14wString2Word00??h Serial number character 26wString3Word00??h Serial number character 3: :Word: :: :Word: :n x 2wStringn Word00??h Serial number character nShall be at least 12 characters long4.1.2Valid Serial Number CharactersThe following table defines the valid characters that the device shall use for the serial number.Table 4.3 - Valid Serial Number CharactersNumeric ASCII0030h through 0039h"0" through "9"0041h through 0046h"A" through "F"4.2Configuration DescriptorTable 4.4 - Configuration DescriptorOffset Field Size Value Description0bLength Byte09h Size of this descriptor in bytes.1bDescriptorType Byte02h CONFIGURATION Descriptor Type.2wTotalLength Word????h Total length of data returned for this configuration. Includesthe combined length of all descriptors (configuration, interface,endpoint, and class- or vendor-specific) returned for thisconfiguration.4bNumInterfaces Byte??h Number of interfaces supported by this configuration. Thedevice shall support at least the Bulk-Only Data Interface.5bConfigurationValue Byte??h Value to use as an argument to the SetConfiguration() requestto select this configuration.6iConfiguration Byte??h Index of string descriptor describing this configuration.7bmAttributes Byte?0h Configuration characteristics:Bit Description7Reserved (set to one)6Self-powered5Remote Wakeup4..0Reserved (reset to zero)Bit 7 is reserved and must be set to one for historical reasons.For a full description of this bmAttributes bitmap, see theUSB 1.1 Specification.8MaxPower Byte??h Maximum power consumption of the USB device from the busin this specific configuration when the device is fullyoperational. Expressed in 2mA units (i.e. 50 = 100mA) NOTE:Information in this table is from the USB Specification version 1.1 table 9-8. Bold text has been added for clarifications when using these descriptors with this specification.4.3Interface DescriptorsThe device shall support at least one interface, known herein as the Bulk-Only Data Interface. The Bulk-Only Data Interface uses three endpoints.Composite mass storage devices may support additional interfaces, to provide other features such as audio or video capabilities. This specification does not define such interfaces.The interface may have multiple alternate settings. The host shall examine each of the alternate settings to look for the bInterfaceProtocol and bInterfaceSubClass it supports optimally.Table 4.5 – Bulk-Only Data Interface DescriptorOffset Field Size Value Description0bLength Byte09h Size of this descriptor in bytes.1bDescriptorType Byte04h INTERFACE Descriptor Type.2bInterfaceNumber Byte0?h Number of interface. Zero-based value identifying the indexin the array of concurrent interfaces supported by thisconfiguration.3bAlternateSetting Byte??h Value used to select alternate setting for the interfaceidentified in the prior field.4bNumEndpoints Byte??h Number of endpoints used by this interface (excludingendpoint zero). This value shall be at least 2.5bInterfaceClass Byte08h MASS STORAGE Class.6bInterfaceSubClass Byte0?h Subclass code (assigned by the USB-IF). Indicates whichindustry standard command block definition to use.Does not specify a type of storage device such as a floppydisk or CD-ROM drive.(See USB Mass Storage Overview Specification) 7bInterfaceProtocol Byte50h BULK-ONLY TRANSPORT.(See USB Mass Storage Overview Specification) 8iInterface Byte??h Index to string descriptor describing this interface.NOTE:Information in this table is from the USB Specification version 1.1 table 9-9. Bold text has been added for clarifications when using these descriptors with this specification.4.4Endpoint DescriptorsThe device shall support at least three endpoints: Control, Bulk-In and Bulk-Out.Each USB device defines a Control endpoint (Endpoint 0). This is the default endpoint and does not require a descriptor.4.4.1Bulk-In EndpointThe Bulk-In endpoint is used for transferring data and status from the device to the host.Table 4.6 - Bulk-In Endpoint DescriptorOffset Field Size Value Description0bLength Byte07h Size of this descriptor in bytes.1bDescriptorType Byte05h ENDPOINT Descriptor Type.2bEndpointAddress Byte8?h The address of this endpoint on the USB device. The address isencoded as follows.Bit Description3..0The endpoint number6..4Reserved, set to 071=In3bmAttributes Byte02h This is a Bulk endpoint.4wMaxPacketSize Word00??h Maximum packet size. Shall be 8, 16, 32 or 64 bytes (08h,10h, 20h, 40h).6bInterval Byte00h Does not apply to Bulk endpoints.4.4.2Bulk-Out EndpointThe Bulk-Out endpoint is used for transferring command and data from the host to the device.Table 4.7 – Bulk-Out Endpoint DescriptorOffset Field Size Value Description0bLength Byte07h Size of this descriptor in bytes.1bDescriptorType Byte05h ENDPOINT descriptor type.2bEndpointAddress Byte0?h The address of this endpoint on the USB device. This address isencoded as follows:Bit Description3..0Endpoint number6..4Reserved, set to 070=Out3bmAttributes Byte02h This is a Bulk endpoint.4wMaxPacketSize Word00??h Maximum packet size. Shall be 8, 16, 32 or 64 bytes (08h,10h, 20h, or 40h).6bInterval Byte00h Does not apply to Bulk endpoints.5 Command/Data/Status ProtocolFigure 1 - Command/Data/Status Flow shows the flow for Command Transport, Data-In, Data-Out and Status Transport.The following sections define Command and Status Transport.Figure 2 - Status Transport Flow shows a detailed diagram of Status Transport. The following sections outline the various conditions for host/device communication, possible errors, and recovery procedures.5.1 Command Block Wrapper (CBW)The CBW shall start on a packet boundary and shall end as a short packet with exactly 31 (1Fh) bytes transferred. Fields appear aligned to byte offsets equal to a multiple of their byte size. All subsequent data and the CSW shall start at a new packet boundary. All CBW transfers shall be ordered with the LSB (byte 0) first (little endian). Refer to the USBSpecification Terms and Abbreviations for clarification.Table 5.1 - Command Block Wrapperbit Byte 76543210-3dCBWSignature 4-7dCBWTag8-11(08h-0Bh)dCBWDataTransferLength12(0Ch)bmCBWFlags13(0Dh)Reserved (0)bCBWLUN14(0Eh)Reserved (0)bCBWCBLength15-30(0Fh-1Eh)CBWCBdCBWSignature:Signature that helps identify this data packet as a CBW. The signature field shall contain the value 43425355h (little endian), indicating a CBW.dCBWTag:A Command Block Tag sent by the host. The device shall echo the contents of this field back to the host in the dCSWTag field of the associated CSW. The dCSWTag positively associates a CSW with the corresponding CBW.dCBWDataTransferLength:The number of bytes of data that the host expects to transfer on the Bulk-In or Bulk-Out endpoint (as indicated by the Direction bit) during the execution of this command. If this field is zero, the device and the host shall transfer no data between the CBW and the associated CSW, and the device shall ignore the value of the Direction bit in bmCBWFlags .Figure 1 - Command/Data/Status FlowReady Command Transport(CBW)Data - Out(from host)Data - In(to host)Status Transport(CSW)bmCBWFlags:The bits of this field are defined as follows:Bit 7Direction - the device shall ignore this bit if the dCBWDataTransferLength field iszero, otherwise:0 = Data-Out from host to the device,1 = Data-In from the device to the host.Bit 6Obsolete. The host shall set this bit to zero.Bits 5..0 Reserved - the host shall set these bits to zero.bCBWLUN:The device Logical Unit Number (LUN) to which the command block is being sent. For devices thatsupport multiple LUNs, the host shall place into this field the LUN to which this command block isaddressed. Otherwise, the host shall set this field to zero.bCBWCBLength:The valid length of the CBWCB in bytes. This defines the valid length of the command block. Theonly legal values are 1 through 16 (01h through 10h). All other values are reserved.CBWCB:The command block to be executed by the device. The device shall interpret the first bCBWCBLength bytes in this field as a command block as defined by the command set identified by bInterfaceSubClass.If the command set supported by the device uses command blocks of fewer than 16 (10h) bytes inlength, the significant bytes shall be transferred first, beginning with the byte at offset 15 (Fh). Thedevice shall ignore the content of the CBWCB field past the byte at offset (15 + bCBWCBLength - 1). 5.2Command Status Wrapper (CSW)The CSW shall start on a packet boundary and shall end as a short packet with exactly 13 (0Dh) bytes transferred. Fields appear aligned to byte offsets equal to a multiple of their byte size. All CSW transfers shall be ordered with the LSB (byte 0) first (little endian). Refer to the USB Specification Terms and Abbreviations for clarification.Table 5.2 - Command Status WrapperbitByte765432100-3dCSWSignature4-7dCSWTag8-11dCSWDataResidue(8-Bh)12bCSWStatus(Ch)dCSWSignature:Signature that helps identify this data packet as a CSW. The signature field shall contain the value53425355h (little endian), indicating CSW.dCSWTag:The device shall set this field to the value received in the dCBWTag of the associated CBW.dCSWDataResidue:For Data-Out the device shall report in the dCSWDataResidue the difference between the amount of data expected as stated in the dCBWDataTransferLength, and the actual amount of data processed by the device. For Data-In the device shall report in the dCSWDataResidue the difference between theamount of data expected as stated in the dCBWDataTransferLength and the actual amount of relevant data sent by the device. The dCSWDataResidue shall not exceed the value sent in thedCBWDataTransferLength.bCSWStatus:bCSWStatus indicates the success or failure of the command. The device shall set this byte to zero if the command completed successfully. A non-zero value shall indicate a failure during commandexecution according to the following table:Table 5.3 - Command Block Status ValuesValue Description00h Command Passed ("good status")01h Command Failed02h Phase Error03h and 04h Reserved (Obsolete)05h to FFh Reserved5.3Data Transfer ConditionsThis section describes how the host and device remainsynchronized.The host indicates the expected transfer in the CBW using the Direction bit and the dCBWDataTransferLength field. The device then determines the actual direction and data transfer length. The device responds as defined in 6 - Host/Device Data Transfers by transferring data, STALLing endpoints when specified, and returning the appropriate CSW. 5.3.1Command TransportThe host shall send each CBW, which contains a command block, to the device via the Bulk-Out endpoint. The CBW shall start on a packet boundary and end as a short packet with exactly 31 (1Fh) bytes transferred.The device shall indicate a successful transport of a CBW by accepting (ACKing) the CBW. If the CBW is not valid see 6.6.1 - CBW Not Valid. If the host detects a STALL of the Bulk-Out endpoint during command transport, the host shall respond with a Reset Recovery (see 5.3.4 - Reset Recovery).5.3.2Data TransportAll data transport shall begin on a packet boundary. The host shall attempt to transfer the exact number of bytes to or from the device as specified by the dCBWDataTransferLength and the Direction bit. The device shall respond as specified in 6 - Host/Device Data Transfers.Attempt to read CSWfrom Bulk-In endpointSTALL Bulk-In- OR -Bulk Error?Clear the STALLconditionYesAttempt to read CSWfrom Bulk-In endpointBulk-IN endpointSTALLed?CSW Valid?NoPhase Error Status?Perform Reset RecoveryYesNoYesYesDevice ready toprocess next CBWNoEnterNoFigure 2 - Status Transport FlowTo report an error before data transport completes and to maximize data integrity, the device may terminate the command by STALLing the endpoint in use (the Bulk-In endpoint during data in, the Bulk-Out endpoint during data out).5.3.3 Status TransportThe device shall send each CSW to the host via the Bulk-In endpoint. The CSW shall start on a packet boundary and end as a short packet with exactly 13 (Dh) bytes transferred. Figure 2 - Status Transport Flow defines the algorithm the host shall use for any CSW transfer.The CSW indicates to the host the status of the execution of the command block from the corresponding CBW. The dCSWDataResidue field indicates how much of the data transferred is to be considered processed or relevant. The host shall ignore any data received beyond that which is relevant.5.3.3.1Phase ErrorThe host shall perform a Reset Recovery when Phase Error status is returned in the CSW.5.3.4Reset RecoveryFor Reset Recovery the host shall issue in the following order: :(a) a Bulk-Only Mass Storage Reset(b) a Clear Feature HALT to the Bulk-In endpoint(c) a Clear Feature HALT to the Bulk-Out endpoint。

A8293

DescriptionIntended for analog and digital satellite receivers, this single low noise block converter regulator (LNBR) is a monolithic linear and switching voltage regulator, specifically designed to provide the power and the interface signals to an LNB down converter via coaxial cable. The A8293 requires few external components, with the boost switch and compensation circuitry integrated inside of the device. A high switching frequency is chosen to minimize the size of the passive filtering components, further assisting in cost reduction. The high levels of component integration ensure extremely low noise and ripple figures. The A8293 has been designed for high efficiency, utilizing the Allegro ® advanced BCD process. The integrated boost switch has been optimized to minimize both switching and static losses. To further enhance efficiency, the voltage drop across the tracking regulator has been minimized.For DiSEqC™ communications, several schemes are available for generating tone signals, all the way down to no-load, and using either the internal clock or an external time source.Features and Benefits▪ 2-wire serial I 2C™ -compatible interface: control (write) and status (read)▪ LNB voltages (7 programmable levels) compatible with all common standards▪ Tracking switch-mode power converter for lowest dissipation ▪ Integrated converter switches and current sensing ▪ Provides up to 700 mA load current▪ Static current limit circuit allows full current at startup and 13→18 V output transition; reliably starts wide load range ▪ Push-pull output stage minimizes 13→18 V and 18→13 V output transition times for highly capacitive loads▪ Adjustable rise/fall time via external timing capacitor ▪ Built-in tone oscillator, factory-trimmed to 22 kHz facilitates DiSEqC™ tone encoding, even at no-load ▪ Four methods of 22 kHz tone generation, via I 2C™ data bits and/or external pin ▪ Auxiliary modulation input ▪ LNB overcurrent with timer▪Diagnostics for output voltage level, input supply UVLOSingle LNB Supply and Control V oltage RegulatorContinued on the next page…Functional Block DiagramA8293L1Packages:20-contact, 4 × 4 mmMLP/QFN (suffix ES)28 contact, 5 × 5 mm MLP/QFN (suffix ET)Package Thermal Characteristics*Package R θJA (°C/W)PCB ES 37 (estimated)4-layer ET324-layer* Additional information is available on the Allegro website.Selection GuidePart Number Packing 1DescriptionA8293SESTR-T 27 in. reel, 1500 pieces/reel12 mm carrier tape ES package, MLP/QFN surface mount 4 mm × 4 mm × 0.75 mm nominal height A8293SETTR-T 2,37 in. reel, 1500 pieces/reel12 mm carrier tapeET package, MLP/QFN surface mount 5 mm × 5 mm × 0.90 mm nominal height1Contact Allegro for additional packing options.2Leadframe plating 100% matte tin.3This variant is in production but has been determined to be NOT FOR NEW DESIGN. This classi fi cation indicates that saleof this device is currently restricted to existing customer applications. The variant should not be purchased for new design ap-plications because obsolescence in the near future is probable. Status date change September 21, 2010.A comprehensive set of fault registers are provided, which comply with all the common standards, including: overcurrent, thermal shutdown, undervoltage, and power not good.The device uses a 2-wire bidirectional serial interface, compatible with the I 2C™ standard, that operates up to 400 kHz.The A8293 is supplied in two lead (Pb) free MLP/QFN packages: ES, 20-contact, 4 mm × 4 mm, 0.75 nominal overall height, and ET, 28-contact, 5 mm × 5 mm, 0.90 nominal overall height.Description (continued)Absolute Maximum RatingsCharacteristic SymbolConditionsRating UnitsLoad Supply Voltage, VIN pin V IN 30V Output Current*I OUTInternally Limited A Output Voltage; LNB and BOOST pins –1 to 33 V Output Voltage; LX pin –1 to 30V Output Voltage; VCP pin –1 to 41 V Logic Input Voltage, EXTM pin –0.3 to 5 V Logic Input Voltage, other pins –0.3 to 7 V Logic Output Voltage–0.3 to 7 V Operating Ambient Temperature T A –20 to 85 °C Junction Temperature T J (max) 150°C Storage TemperatureT stg –55 to 150°C*Output current rating may be limited by duty cycle, ambient temperature, and heat sinking. Under any set of conditions, do not exceed thespecified current ratings, or a junction temperature, T J , of 150°C.PAD1514131211123456789102019181716L N BG N DL XV I NN CN CG N DV R E GS D A A D D FLOAT GND NC SCL IRQBOOST VCP TCAP FLOAT EXTMTerminal List TableName Number FunctionES ET ADD 1011Address selectFLOAT 4, 155, 22These pins must not be connected to anything; do not ground these pins BOOST 11Tracking supply voltage to linear regulator EXTM 56External modulation input GND 7, 148, 19Signal ground GNDLX 1927Boost switch ground IRQ 1114Interrupt request LNB 2028Output voltage to LNB LX 1826Inductor drive point NC 6, 13, 164, 7, 13, 15-18, 20, 21, 23, 24No connectionPAD Pad PadExposed pad; connect to the ground plane, for thermal dissipation SCL 1212I 2C™-compatible clock input SDA 910I 2C™-compatible data input/outputTCAP 33Capacitor for setting the rise and fall time of the LNB output VCP 22Gate supply voltage VIN 1725Supply input voltage VREG89Analog supplyDevice Pin-out Diagram(Top View)PAD 21201918171615123456789101112131428272625242322L N BG N D L XL XV I N N C N CF L O A TG N DV R E GS D A A D D S C L N C I R Q NC NC GND NC NC NC NC BOOST VCP TCAP NC FLOAT EXTM NCES PackageET PackageELECTRICAL CHARACTERISTICS at TA= 25°C, V IN = 9 to 16 V, unless noted otherwise1Characteristics Symbol Test Conditions Min.Typ.Max.Units GeneralSet-Point Accuracy, Load and Line Regulation Err Relative to selected V LNB target level,I LOAD = 0 to 450 mA–3.0–+3.0%Supply Current I IN(Off)ENB bit = 0, LNB output disabled, V IN = 12 V––10.0mA I IN(On)ENB bit = 1, LNB output enabled,I LOAD = 0 mA, V IN = 12 V––19.0mABoost Switch On Resistance R DS(on)BOOST I LOAD = 450 mA–300–mΩSwitching Frequency f SW320352384kHz Switch Current Limit I LIMSW V IN = 9 V, V OUT = 19.0 V– 2.7–ALinear Regulator Voltage Drop∆V REG V BOOST – V LNB, no tone signal,I LOAD = 450 mA–800–mVTCAP Pin CurrentI CHG TCAP capacitor (C7) charging–12.5–10–7.5μA I DISCHG TCAP capacitor (C7) discharging7.51012.5μAOutput Voltage Rise Time2t r(VLNB)For V LNB 13 →18 V; C TCAP = 5.6 nF,I LOAD = 450 mA–500–μsOutput Voltage Pull-Down Time2t f(VLNB)For V LNB 18 →13 V; C LOAD = 100 μF,I LOAD = 0 mA–12.5–msOutput Reverse Current I RLNB ENB bit = 0, V LNB = 33 V , BOOST capacitor(C5) fully charged–15mARipple and Noise on LNB Output3V rip,n(pp)20 MHz BWL; reference circuit shown inFunctional Block diagram; contact Allegro foradditional information on application circuitboard design–30–mV PPProtection CircuitryOutput Overcurrent Limit4I LIMLNB V BOOST – V LNB = 800 mV–700800mA Overcurrent Disable Time t DIS–48–ms VIN Undervoltage Lockout Threshold V UVLO V IN falling7.057.357.65V VIN Turn On Threshold V IN(th)V IN rising7.407.708.00V Undervoltage Hysteresis V UVLOHYS–350–mV Thermal Shutdown Threshold2T J–165–°C Thermal Shutdown Hysteresis2∆T J–20–°C Power Not Good Flag Set PNG SET With respect to V LNB778593% Power Not Good Flag Reset PNG RESET With respect to V LNB829098% Power Not Good Hysteresis PNG HYS With respect to V LNB–5–% ToneTone Frequency f TONE202224kHz Tone Amplitude, Peak-to-Peak V TONE(pp)I LOAD = 0 to 450 mA, C LOAD = 750 nF400620800mVContinued on the next page…Tone Duty Cycle DC TONE I LOAD = 0 to 450 mA, C LOAD = 750 nF 405060%Tone Rise Time t rTONE I LOAD = 0 to 450 mA, C LOAD = 750 nF 51015μs Tone Fall Time t fTONE I LOAD = 0 to 450 mA, C LOAD = 750 nF51015μs EXTM Logic Input V EXTM(H) 2.0––VV EXTM(L)––0.8V EXTM Input Leakage I EXTMLKG–1–1μAI 2C™-Compatible Interface Logic Input (SDA,SCL) Low Level V SCL(L)––0.8V Logic Input (SDA,SCL) High Level V SCL(H) 2.0––V Logic Input Hysteresis V I2CIHYS –150–mV Logic Input CurrentI I2CI V I2CI = 0 to 7 V –10<±1.010μA Logic Output Voltage SDA and IRQ V t2COut(L)I LOAD = 3 mA ––0.4V Logic Output Leakage SDA and IRQ V t2CLKG V t2COut = 0 to 7 V––10μA SCL Clock Frequency f CLK ––400kHz Output Fall Timet fI2COut V t2COut(H) to V t2COut(L)––250ns Bus Free Time Between Stop/Start t BUF 1.3––μs Hold Time Start Condition t HD:STA 0.6––μs Setup Time for Start Condition t SU:STA 0.6––μs SCL Low Time t LOW 1.3––μs SCL High Time t HIGH 0.6––μs Data Setup Timet SU:DAT 100––nsData Hold Timet HD:DAT For t HD:DAT (min) , the master device must provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the SCL signal falling edge 0–900ns Setup Time for Stop Condition t SU:STO 0.6––μs I 2C™ Address SettingADD Voltage for Address 0001,000Address10–0.7V ADD Voltage for Address 0001,001Address2 1.3– 1.7V ADD Voltage for Address 0001,010Address3 2.3– 2.7V ADD Voltage for Address 0001,011Address43.3–5.0V1Operation at 16 V may be limited by power loss in the linear regulator.2Guaranteed by worst case process simulations and system characterization. Not production tested.3LNB output ripple and noise are dependent on component selection and PCB layout. Refer to the Application Schematic and PCB layoutrecommendations. Not production tested.4Current from the LNB output may be limited by the choice of Boost components.ELECTRICAL CHARACTERISTICS (continued) at T A = 25°C, V IN = 9 to 16 V, unless noted otherwise 1CharacteristicsSymbol Test ConditionsMin.Typ.Max.Units I 2C™ Interface Timing DiagramHIGH LOW SDA SCLProtectionThe A8293 has a wide range of protection features and fault diag-nostics which are detailed in the Status Register section.Boost Converter/Linear RegulatorThe A8293 solution contains a tracking current-mode boost converter and linear regulator. The boost converter tracks the requested LNB voltage to within 800 mV, to minimize power dissipation. Under conditions where the input voltage, V BOOST , is greater than the output voltage, V LNB, the linear regulator must drop the differential voltage. When operating in these conditions, care must be taken to ensure that the safe operating temperature range of the A8293 is not exceeded.The boost converter operates at 352 kHz typical: 16 times the internal 22 kHz tone frequency. All the loop compensation, current sensing, and slope compensation functions are provided internally.The A8293 has internal pulse-by-pulse current limiting on the boost converter and DC current limiting on the LNB output to protect the IC against short circuits. When the LNB output is shorted, the LNB output current is limited to 700 mA typical, and the IC will be shut down if the overcurrent condition lasts for more than 48 ms. If this occurs, the A8293 must be reenabled for normal operation. The system should provide sufficient time between successive restarts to limit internal power dissipation; a minimum of 2 s is recommended.At extremely light loads, the boost converter operates in a pulse-skipping mode. Pulse skipping occurs when the BOOST voltage rises to approximately 450 mV above the BOOST target output voltage. Pulse skipping stops when the BOOST voltage drops 200 mV below the pulse skipping level.In the case that two or more set top box LNB outputs are con-nected together by the customer (e.g., with a splitter), it is pos-sible that one output could be programmed at a higher voltage than the other. This would cause a voltage on one output that is higher than its programmed voltage (e.g., 19 V on the output of a 13 V programmed voltage). The output with the highest voltage will effectively turn off the other outputs. As soon as this voltage is reduced below the value of the other outputs, the A8293 output will auto-recover to their programmed levels.Charge Pump.Generates a supply voltage above the internal tracking regulator output to drive the linear regulator control. Slew Rate Control. During either start-up, or when the output voltage at the LNB pin is transitioning, the output voltage rise and fall times can be set by the value of the capacitor connected from the TCAP pin to GND (C TCAP or C7 in the Applications Schematic). Note that during start-up, the BOOST pin is pre-charged to the input voltage minus a voltage drop. As a result, the slew rate control for the BOOST pin occurs from this voltage.The value of C TCAP can be calculated using the following for-mula:C TCAP = (I TCAP × 6) / SR ,where SR is the required slew rate of the LNB output voltage,in V/s, and I TCAP is the TCAP pin current specified in the data sheet. The recommended value for C TCAP, 10 nF, should provide satisfactory operation for most applications. However, in some cases, it may be necessary to increase the value of C TCAP to avoid activating the current limit of the LNB output. One such situa-tion is when two set-top boxes are connected in parallel. If this is the case, the following formula can be used to calculate C TCAP:C TCAP≥ (I TCAP × 6)(2 × C BOOST) / I LIMLNB ,C TCAP≥ (10 μA × 6)(2 × 100 μF) / 500 mA = 24 nF .The minimum value of C TCAP is 2.2 nF. There is no theoretical maximum value of C TCAP however too large a value will prob-ably cause the voltage transition specification to be exceeded. Tone generation is unaffected by the value of C TCAP .Pull-Down Rate Control.In applications that have to operate at very light loads and that require large load capacitances (in the order of tens to hundreds of microfarads), the output linear stage provides approximately 40 mA of pull-down capability. This ensures that the output volts are ramped from 18 V to 13 V in a reasonable amount of time.ODT (Overcurrent Disable Time)If the LNB output current exceeds 700 mA, typical, for more than 48 ms, then the LNB output will be disabled and the OCP bit will be set.Short Circuit HandlingIf the LNB output is shorted to ground, the LNB output current will be clamped to 700 mA, typical. If the short circuit condition lasts for more than 48 ms, the A8293 will be disabled and the OCP bit will be set.Auto-RestartAfter a short circuit condition occurs, the host controller should periodically reenable the A8293 to check if the short circuit hasFunctional Descriptionbeen removed. Consecutive startup attempts should allow at least 2 s of delay between restarts.In-Rush CurrentAt start-up or during an LNB reconfiguration event, a tran-sient surge current above the normal DC operating level can be provided by the A8293. This current increase can be as high as 700 mA, typical, for as long as required, up to a maximum of48 ms.Tone GenerationThe A8293 solution offers four options for tone generation, providing maximum flexibility to cover every application. The EXTM pin (external modulation), in conjunction with the I2C™ control bits: TMODE (tone modulation) and TGATE (tone gate), provide the necessary control. The TMODE bit controls whether the tone source is either internal or external (via the EXTM pin). Both the EXTM pin and TGATE bit determine the 22 kHz con-trol, whether gated or clocked.Four options for tone generation are shown in figure 1. Note that when using option 4, when EXTM stops clocking, the LNB volts park at the LNB voltage, either plus or minus half the tone signal amplitude, depending on the state of EXTM. For example, if the EXTM is held low, the LNB DC voltage is the LNB pro-grammed voltage minus 325 mV (typical).EXTM TMODE TGATE ToneEXTM TMODETGATE ToneEXTM TMODE TGATE ToneEXTM TMODE TGATE ToneOption 1 – Use internal tone, gated by the TGATE bit. Option 2 – Use internal tone, gated by the EXTM pin. Option 3 – Use external tone, gated by the TGATE bit. Figure 1. Options for tone generationI 2C™-Compatible InterfaceThis is a serial interface that uses two bus lines, SCL and SDA,to access the internal Control and Status registers of the A8293.Data is exchanged between a microcontroller (master) and theA8293 (slave). The clock input to SCL is generated by the master,while SDA functions as either an input or an open drain output,depending on the direction of the data.Timing ConsiderationsThe control sequence of the communication through the I 2C™-compatible interface is composed of several steps in sequence: 1. Start Condition. Defined by a negative edge on the SDA line,while SCL is high.2. Address Cycle. 7 bits of address, plus 1 bit to indicate read (1)or write (0), and an acknowledge bit. The first five bits of the address are fixed as: 00010. The four optional addresses, de-fined by the remaining two bits, are selected by the ADD input. The address is transmitted MSB first.3. Data Cycles. Write – 6 bits of data and 2 bits for addressing four internal control registers, followed by an acknowledge bit. See Control Register section for more information. Read – Two status registers, where register 1 is read first, followed by register 2, then register 1, and so on. At the start of any read sequence, register 1 is always read first. Data is transmitted MSB first.4. Stop Condition. Defined by a positive edge on the SDA line,while SCL is high. Except to indicate a Start or Stop condi-tion, SDA must be stable while the clock is high. SDA canonly be changed while SCL is low. It is possible for the Start or Stop condition to occur at any time during a data transfer. The A8293 always responds by resetting the data transfer sequence. The Read/Write bit is used to determine the data transfer direc-tion. If the Read/Write bit is high, the master reads the contents of 1 2 3 4 5 6 7 8 9SCL1 2 3 4 5 6 7 8 9SCL1 2 3 4 5 6 7 8 9SCL Write to RegisterRead One Byte from RegisterRead Multiple Bytes from RegisterFigure 2. I 2C™ Interface. Read and write sequences.register 1, followed by register 2 if a further read is performed. If the Read/Write bit is low, the master writes data to one of the two Control registers. Note that multiple writes are not permitted. All write operations must be preceded with the address.The Acknowledge bit has two functions. It is used by the mas-ter to determine if the slave device is responding to its address and data, and it is used by the slave when the master is reading data back from the slave. When the A8293 decodes the 7-bit ad-dress field as a valid address, it responds by pulling SDA low during the ninth clock cycle.During a data write from the master, the A8293 also pulls SDA low during the clock cycle that follows the data byte, in order to indicate that the data has been successfully received. In both cas-es, the master device must release the SDA line before the ninth clock cycle, in order to allow this handshaking to occur.During a data read, the A8293 acknowledges the address in the same way as in the data write sequence, and then retains control of the SDA line and send the data from register 1 to the master. On completion of the eight data bits, the A8293 releases the SDA line before the ninth clock cycle, in order to allow the master to acknowledge the data. If the master holds the SDA line low dur-ing this Acknowledge bit, the A8293 responds by sending the data from register 2 to the master. Data bytes continue to be sent to the master until the master releases the SDA line during the Acknowledge bit. When this is detected, the A8293 stops sending data and waits for a stop signal. Interrupt RequestThe A8293 also provides an interrupt request pin, IRQ, which is an open-drain, active-low output. This output may be connect-ed to a common IRQ line with a suitable external pull-up and can be used with other I 2C™-compatible devices to request attention from the master controller.The IRQ output becomes active when either the A8293 first recognizes a fault condition, or at power-on, when the main sup-ply, V IN , and the internal logic supply, V REG , reach the correct operating conditions. It is only reset to inactive when the I 2C™ master addresses the A8293 with the Read/Write bit set (caus-ing a read). Fault conditions are indicated by the TSD, VUV , and OCP bits, and are latched in the Status register. See the Status register section for full description.The DIS and PNG status bits do not cause an interrupt. The PNG bit is continually updated, apart from the DIS bit, which changes when the LNB is either disabled, faulted, or is enabled. When the master recognizes an interrupt, it addresses allslaves connected to the interrupt line in sequence, and then reads the status register to determine which device is requesting atten-tion. The A8293 latches all conditions in the Status register until the completion of the data read. The action at the resampling point is further defined in the Status Register section. The bits in the Status register are defined such that the all-zero condition in-dicates that the A8293 is fully active with no fault conditions. When V IN is initially applied, the I 2C™-compatible interface does not respond to any requests until the internal logic supply V REG has reached its operating level. Once V REG has reached this point, the IRQ output goes active, and the VUV bit is set. After the A8293 acknowledges the address, the IRQ flag is reset. After the master reads the status registers, the registers are updated with the VUV reset.Status Register 1Address Start R Stop1 2 3 4 5 6 7 8 9SCL IRQFaultEventReloadStatus RegisterRead after InterruptFigure 3. I 2C™ Interface. Read sequences after interrupt request.Control Registers (I2C™-Compatible Write Register) All main functions of the A8293 are controlled through the I2C™-compatible interface via the 8-bit Control registers. As the A8293 contains numerous control options, it is necessary to have two control registers. Each register contains up to 6 bits of data (bit 0 to bit 5), followed by 2 bits for the register address (bit 6 and bit 7). The power-up states for the control functions are all 0s.The following tables define the control bits for each address and the settings for output voltage:Table 1. Control Register Address (I1, I0) = 00 Bit Name Function0VSEL0See table 3, Output Voltage Amplitude Selection 1VSEL12VSEL23VSEL30: LNB = Low range1: LNB = High range4ODT 1 (recommended): The ODT functions are always enabled, but setting 1 recommended at all times.5ENB0: Disable LNB Output1: Enable LNB Output6I0Address Bit: 07I1Address Bit: 0Bit 0 VSEL0 These three bits provide incremental control over the voltage on the LNB output.Bit 1 VSEL1 The available voltages provide the necessary levels for all the common standards Bit 2 VSEL2 plus the ability to add line compensation in increments of 333 mV. The voltage levels are defined in table 3, Output V oltage Amplitude Selection.Bit 3 VSEL3 Switches between the low level and high level output voltages on the LNB output.0 selects the low level voltage and 1 selects the high level. The low-level center voltageis 12.709 V nominal and the high level is 18.042 V nominal. These may be increasedin steps of 333 mV using the VSEL2, VSEL1 and VSEL0 control register bits.Bit 4 ODT The overcurrent disable timer is always enabled.Bit 5 ENB Enables the LNB output. When set to 1 the LNB output is switched on. When set to 0, the LNB output is disabled.Bit 6 I0 AddressBit 7 I1 AddressTable 2. Control Register Address (I1, I0) = 10 and 11Bit Name Function0: External Tone0TMODE1: Internal Tone0: Tone Gated Off1TGATE1: Tone Gated On2-Not Used (0 recommended)3-Not Used4-Not Used5-Not Used6I0Address Bit: 07I1Address Bit: 1Bit 0 TMODE Tone Mode. Selects between the use of an external 22 kHz logic signal or the use of the internal 22 kHz oscillator to control the tone generation on the LNB output. A 0selects the external tone and a 1 selects the internal tone. See the Tone Generationsection for more informationBit 1 TGATE Tone Gate. Allows either the internal or external 22 kHz tone signals to be gated, unless the EXTM is selected for gating. When set to 0, the selected tone (viaTMODE) is off. When set to 1, the selected tone is on. See Tone Generation Sectionfor more information.Bit 2 – Not Used.Bit 3 – Not Used.Bit 4 – Not Used.Bit 5 – Not Used.Bit 6 I0 Address.Bit 7 I1 Address.Table 3. Output Voltage Amplitude Selection VSEL3VSEL2VSEL1VSEL0LNB (V) 000012.709 000113.042 001013.375 010014.042 100018.042 101018.709 101119.042Status Registers (I2C™-Compatible Read Register)The main fault conditions: overcurrent (OCP), undervoltage (VUV) and overtemperature (TSD), are all indicated by setting the relevant bits in the Status registers. In all fault cases, once the bit is set, it remains latched until the A8293 is read by the I2C™ master, assuming the fault has been resolved.The current status of the LNB output is indicated by the dis-able bit, DIS. The DIS bit is set when either a fault occurs or if the LNB is disabled intentionally. This bit is latched, and is reset when the LNB is commanded on again. The power not good (PNG) is the only bit which may be reset without an I2C™ read sequence. Table 4 summarizes the condition of each bit when set and how it is reset.As the A8293 has a comprehensive set of status reporting bits, it is necessary to have two Status registers. When performing a multiple read function, register 1 is read followed by register 2, then register 1 again and so on. Whenever a new read function is performed, register 1 is always read first.The normal sequence of the master in a fault condition will be to detect the fault by reading the Status registers, then rereading the Status registers until the status bit is reset indicating the fault condition is reset. The fault may be detected either by continuously polling, by responding to an interrupt request (IRQ), or by detect-ing a fault condition externally and performing a diagnostic poll of all slave devices. Note that the fully-operational condition of the Status registers is all 0s, to simplify checking of the Status bit.Table 4. Status Register Bit SettingStatus Bit Function SetReset Condition–Not used–Not usedDIS LNB disabled, either intentionally ordue to faultLatched LNB enabled and no faultOCP Overcurrent Latched I2C™ read and fault removed PNG Power not good Non-latched LNB volts in range–Not used–Not usedTSD Thermal shutdown Latched I2C™ read and fault removed VUV Undervoltage Latched I2C™ read and fault removedTable 5. Status Register 1Bit Name Function0DIS LNB output disabled1–Not Used2OCP Overcurrent3–Not Used4PNG Power Not Good5–Not Used6TSD Thermal Shutdown7VUV V IN UndervoltageBit 0 DIS LNB Output Disabled. DIS is used to indicate the current condition of the LNB output. At power-on, or if a fault condition occurs, DIS will be set. This bit changingto 1 does not cause the IRQ to activate because the LNB output may be disabled in-tentionally by the I2C™ master. This bit will be reset at the end of a write sequenceif the LNB output is enabled.Bit 1 – Not used.Bit 2 OCP Overcurrent. If the LNB output detects an overcurrent condition, for greater than48 ms, the LNB output will be disabled. The OCP bit will be set to indicate that anovercurrent has occurred and the disable bit, DIS, will be set. The Status register isupdated on the rising edge of the 9th clock pulse in the data read sequence, where theOCP bit is reset in all cases, allowing the master to reenable the LNB output.If the overcurrent timer is not enabled, the device operate in current limit indefinitelyand the OCP bit will be set. If the overcurrent condition is removed, the OCP bit willautomatically be reset. Note that if the overcurrent operates long enough, and a ther-mal shutdown occurs, the LNB output will be disabled and the TSD bit will be set.Bit 3 – Not used.Bit 4 PNG Power Not Good. Set to 1 when the LNB output is enabled and the LNB voltage is below 85% of the programmed voltage. The PNG is reset when the LNB volts arewithin 90% of the programmed LNB voltage.Bit 5 – Not used.Bit 6 TSD Thermal Shutdown. 1 indicates that the A8293 has detected an overtemperature condition and has disabled the LNB output. The disable bit, DIS, will also be set.The status of the overtemperature condition is sampled on the rising edge of the 9thclock pulse in the data read sequence. If the condition is no longer present, then theTSD bit will be reset, allowing the master to reenable the LNB output if required. Ifthe condition is still present, then the TSD bit will remain at 1.Bit 7 VUV Undervoltage Lockout. 1 indicates that the A8293 has detected that the input sup-ply, V IN is, or has been, below the minimum level and an undervoltage lockout hasoccurred disabling the LNB outputs. The disable bit, DIS, will also be set and theA8293 will not reenable the output until so instructed by writing the relevant bit intothe control registers. The status of the undervoltage condition is sampled on the risingedge of the 9th clock pulse in the data read sequence. If the condition is no longerpresent, then the VUV bit will be reset allowing the master to reenable the LNB out-put if required. If the condition is still present, then the VUV bit will remain at 1.。

正常循环前缀-概述说明以及解释

正常循环前缀-概述说明以及解释1.引言1.1 概述正常循环前缀是一种在计算机科学领域中常见的概念,它可以帮助我们更好地理解和优化算法的性能。

在算法设计中,循环前缀通常用于描述循环过程中的一组操作或指令的组合。

正常循环前缀则是指在循环执行过程中,这些操作按照指定的次序和规律依次执行,且不会出现死循环或执行顺序混乱的情况。

本文将详细探讨正常循环前缀的概念、特征以及其在算法设计和优化中的应用。

通过深入理解正常循环前缀,我们可以更好地把握算法执行的逻辑和效率,提高代码的可读性和可维护性。

在接下来的篇章中,我们将逐步展开对正常循环前缀的探讨,希望读者能够通过本文的学习,对这一概念有更加清晰的认识。

1.2 文章结构本文分为引言、正文和结论三个部分。

在引言部分,将对正常循环前缀的概念、文章结构和目的进行简要介绍,为读者提供整体的把握。

在正文部分,将详细探讨正常循环前缀的概念、特征和应用,对该概念进行深入解析,并分析其在实际应用中的意义和价值。

最后,在结论部分,将对本文进行总结,展望正常循环前缀未来可能的发展方向,并给出一些结束语,为读者留下深刻印象。

整体结构清晰,层次分明,希望能够为读者提供全面的了解和思考。

1.3 目的本文旨在探讨正常循环前缀在计算机科学领域中的重要性和应用。

通过对正常循环前缀的概念、特征和应用进行深入分析和讨论,旨在帮助读者更好地理解和运用正常循环前缀技术。

同时,通过本文的撰写,也旨在促进对正常循环前缀的研究和探讨,为相关领域的学术进步和技术发展提供有益的参考和启示。

希望读者能够通过本文的阅读,对正常循环前缀有更深入的了解,并能够将其运用到实际问题的解决中,从而提升工作和学习的效率和质量。

2.正文2.1 正常循环前缀的概念:正常循环前缀是指在一个给定的循环中,首先具有某个长度的前缀,并且该前缀不会在循环的其余部分中再次出现。

换句话说,正常循环前缀是不重复出现的、与循环其他部分不同的序列。

这种特殊的前缀在循环中起着重要的作用,可以帮助我们更好地理解循环的结构和特征。

Java Runtime Systems Characterization and Architectural Implications