在 系 统 可 编 程 模 拟 器 件

在系统可编程模拟器件(ispPAC)及其应用

在系统可编程模拟器件(ispPAC)及其应用余三同【摘要】在系统可编程模拟器件(ispPAC)的出现,改变了传统的模拟电路的设计思想,他具有在系统可编程的特点,无需外围元器件可以灵活地实现信号放大、滤波、D/A转换等,利用他设计电路方便、快捷.介绍在系统可编程模拟器件(ispPAC)的结构、功能与特点,利用可编程模拟器件ispPAC10,ispPAC20,借助于PACDesigner 软件,分别设计并实现了滤波器、数控振荡器等电路,并给出仿真结果.实践证明isp 技术有广阔的应用前景.【期刊名称】《现代电子技术》【年(卷),期】2007(030)022【总页数】3页(P140-142)【关键词】可编程模拟电路;PAC-Designer软件;滤波器;压控振荡器【作者】余三同【作者单位】江苏大亚集团,江苏,丹阳,212300【正文语种】中文【中图分类】TN713模拟电路的设计和调试对一个人的理论基础、经验、耐心要求很高,尤其是采用传统的分立元件搭建模拟电路,电路的精度、稳定度很难实现,而且功耗也比较大。

集成模拟可编程电路的出现将对相应电路的开发起到积极的促进作用,尤其是对初学者或者经验不足的工程师有较大的帮助。

本文介绍了美国Lattice公司新推出的在系统可编程模拟电路(In System Programmability Programmable Analog Circuits,ispPAC)及其应用。

在系统可编程模拟器件ispPAC具有在系统可编程技术的优势和特点。

该技术可以弥补传统模拟电路实践采用分立元件搭接各种电路的不足,将极大改善模拟电路实践的成效和创新.他允许设计者使用开发软件在计算机中设计,并进行电路特性功能仿真,检查是否有错误,以及所设计的功能是否与题目要求的功能一致,如发现问题应对设计进行检查,找出错误并加以修改,而且能够通过编程电缆最终将设计方案下载至芯片中,实现一个芯片完成一个系统的功能,满足高集成度的要求。

在系统可编程模拟器件在教学实验中的设计和应用

平 台 。设 计 了一 个 电源 转 换 、 控 和 保 护 的 电 路 实 验 , 综 合 了 模 拟 可 编 程 和 逻 辑 可 编 程 技 术 , 有 设 计 新 监 它 具 颖 、 识 面 广 、 合 性 强 等 特 点 , 够 充 分 培 养 学 生 的实 践 能 力 和 创 造 能 力 。 知 综 能

兰 墨

二兰 !

实

验

技

术

与

管

理

第 2 6卷

第 8期

2 0 年 8月 09

CNl — 2 3 / 1 0 4 T

Ex e i n a c no o y a d M a a e n p rme t lTe h lg n n g me t

Hale Waihona Puke Vo . 6 No. Au . 2 0 12 8 g 0 9

( u ngx o a i a G a iV c ton lCole fM e ha c la e t ia e hn og lge O c nia nd El c rc lT c ol y,N a ni 0 7,Chia) n ng 5 00 3 n

A b ta t Th p ri r du e he s r t r nd f a ur sofip src : e pa e nto c s t tuc u ea e t e s PA C30,a pr r m mab ea l vie Ba e og a l naog de c . sd on t lc r ct c olgy t a hng e e i e t ltor ,a cr ui e pe i e orp he ee toni e hn o e c i xp rm n alp a f m ic t x rm ntf owe o e son,s e — rc nv r i up r v so nd p ot c in i e i e ii n a r e to s d sgn d. I e r tn b h pr gr m m a e a a o e hnoog n o a m a e l c l nt g a ig ot o a bl n l g t c l y a d pr gr m bl ogia t c no o e h l gy,t i ic i xp rm e ih isne y d sgn, wi l ow ld nd s r gl om p e e i ec r hs cr ute e i ntw t t wl e i dey kn e gea ton y c r h nsv ha —

在系统可编程模拟器件的结构及原理11.4

上页

下页

返回

模拟电子技术基础

11.4.2

PAC-Designer软件的几个重要的功能 - 软件的几个重要的功能 Run Macro菜单 菜单

1.Tools .

上页

下页

返回

模拟电子技术基础

2.File .

Browse Library菜单 菜单

可调用这些文件, 可调用这些文件,并在此基础上修改从而方 便地完成自己的设计。 便地完成自己的设计。 3.Edit . Security菜单 菜单

该菜单可以用来选择下载至ispPAC器件后能 器件后能 该菜单可以用来选择下载至 否允许被读出,起加密保护作用。 否允许被读出,起加密保护作用。

上页

下页

返回

上页 下页 返回

模拟电子技术基础

2.设计仿真 . (1) 设置仿真参数 软件主窗口中按Operations 在PAC-Designer软件主窗口中按 - 软件主窗口中按 Simulator菜单 菜单 在该对话框中 确定仿真频率 的起始值和终 止值、 止值、仿真点 数、输入节点 和输出节点。 和输出节点。

上页 下页 返回

模拟电子技术基础

(2) 执行仿真操作 完成参数设置后, 完成参数设置后,按ToolsRun 单进行仿真。 单进行仿真。 Simulator菜 菜

上页

下页

返回

模拟电子技术基础

3.器件编程 . 通过编程电缆给器件下载,执行Tools 通过编程电缆给器件下载,执行 Download菜单即可。执行 菜单即可。执行Tools 菜单即可 原理图所示一致。执行 原理图所示一致。执行Tools 在原理图中。 在原理图中。 Verify Upload菜 菜 菜单可验证ispPAC中已编程的内容是否与 中已编程的内容是否与 菜单可验证 单可将ispPAC中已编程的内容读出来显示 中已编程的内容读出来显示 单可将

在系统可编程模拟器件ispPAC30及其应用

分 输 入 仪 表 放 大 器 I 两 个 双 端 口复 用 器 、 个 可 A、 两 配 置 输 出放 大 器 O A、 两 个 数 / 相 乘 变 换 器 模

MD AC、两 个 独 立 的 可 编 程 精 密 参 考 电 压 VR F及 E 非 易 失 配 置信 息 存储 器 、 自校 正 电 路 等 。 如 图 1 所

1 Ip AC3 sP 0结 构 与 特 性 Ip AC 0器 件 主 要 包 括 四 个 可 编 程 增 益 的 差 sP 3

19 9 2年 美 国 L t c at e半 导 体 公 司 发 明 了 在 系 统 i 可 编 程 技 术 (n S s m P o a I — yt rg mma it )彻 底 改 变 e r bly , i

fre e r d.

Ke r s I- y tm p o a y wo d : sse rg mma it( P ; iee t lip to tu ftr n r bl yI )df rni n u/ up ; l i S f a ie

O 引 言

和 具 有 动 态 可 重构 功 能 的模 拟 集 成 电路 。 因此 本 文 主 要 介 绍 i P C 0器 件 及 其 应 用 。 s A 3 p

了传 统 数 字 电子 系 统 的设 计 和实 现 方 法 ,开 创 了数 字 系 统 设 计 的 里 程 碑 。 9 9年 1 19 1月 , 国 L t c 公 美 a te i

司 又 推 出 了 在 系 统 可 编 程 模 拟 电 路 ( p AC I— i P " n s S se P o rmma l ao i ut) 翻 开 了 模 拟 ytm rga be An lg Cr i , c s

在系统可编程模拟器件(ispPAC)及其应用

( y r u f in s , n a g, 1 3 0 C ia Da aG o p o a g u Da y n 2 2 0 , h n ) J

A sr c : e c e t n o n—Sy t m r g a b ta t Th r a i f o I s e P o r mma l a o r u t ip b e An lg Ci i c s( s PAC)h sc a g d t e t a ii n li e f h e a h n e h r d t a d a o e d — o t

统 的 AS C所 实 现 的 电路 功 能 。 本 文 首 先 介 绍 ip I s PAC的 特 点 及 功 能 , 后 以 实 现 二 阶 滤 波 器 和 压 控 振 荡 电 路 为 然 例 , 绍 了他 们 的设 计 过 程 , 出 了其 仿 真结 果 。 介 给

f trn n A o v rin wi o tp r h r l o o e t n e ie . ti c n e in n a tt s s PAC t e incr i eiga d D/ c n e so t u ei ea mp n n sa dd vcs I s o v ne t d fs o u eip l h p c a od sg i—

维普资讯

余 三 同 : 系统 可编 程模 拟器件 (s P ) 在 i AC 及其 应用 p

ቤተ መጻሕፍቲ ባይዱ

在系统可编程模拟器件( p A ) i P C 及其应用 s

余三 同

( 苏 大 亚 集 团 江苏 丹 阳 江 摘 220 ) 1 3 0

要 : 系统 可 编 程 模 拟 器件 ( p AC 的 出现 , 变 了传 统 的 模 拟 电路 的 设 计 思 想 , 具 有 在 系统 可 编 程 的 特 点 , 在 iP ) s 改 他 无

编程软件ispLEVER与原理图输入详解

双击原理图的资源文件demo.sch,把它打开。 在原理图编辑器中,选择File菜单。 从下拉菜单中,选择Matching Symbol命令。 关闭原理图。 至此,这张原理图的宏元件符号已经建立完毕,并且被加到元件 表中。你可以在下一步中调用这个元件。

编程软件ispLEVER

ispLEVER编程软件 在系统可编程器件设计步骤 ISP器件的三种逻辑设计方法 编译、模拟、器件适配与下载

在系统可编程器件设计步骤

在系统可编程器件设计步骤

对一个可编程器件的设计大致经过以下步骤:创 建新设计项目,选择器件,输入源文件,编译与优 化,功能模拟或者时序模拟,连接与器件适配,下 载。

在系统可编程器件设计步骤

6.连接与器件适配 连接将编译后的各模块连接成一个文件。器件适配则把 设计放进目标器件中。 7.下载 通过下载电缆,将生成的JED数据文件下载到电路板上 的ISP器件中。下载又称为编程。一个ISP器件只有经过下载 这一步骤,才能将设计成果转化为该器件的功能,在电路板 上发挥应有的作用。

整个设计工作流程大致分为创建新设计项目,选择器件,输 入源文件,编译与优化,逻辑模拟,连接和器件适配,下载等 若干过程。

ispLEVER编程软件

2.项目导航器

ispLEVER使 用了项目的概念。 一个项目代表一 个设计。一个项 目所用的全部文 件应放在一个单 独的目录中。项 目导航器保存项 目设计中每一部 分的过程及状态。

②项目源文件:用户能够用不同的方式描述设计,这些描述 就是源文件。每个源文件是设计中的一个部件。

ispLEVER编程软件

(2)进程窗口

右半部分是进程窗口,该窗口显示源文件窗口中所选中文件 能进行的所有操作。这些操作包括:编译,逻辑化简,生成测 试模块,连接,器件适配,下载等,完成从设计输入到下载的 每一步骤。 ①源文件级进程:包括源文件输入,编译,优化等。在源文 件窗口单击一个源文件,进程窗口中将出现指示处理此源文件 的源文件级进程。 ②项目级进程:包括连接,器件适配,编译时序报告,下载 等。在源文件窗口中单击器件图标,进程窗口中将出现指示该 器件处理的项目级进程。

在系统可编程模拟器件(ispPAC)

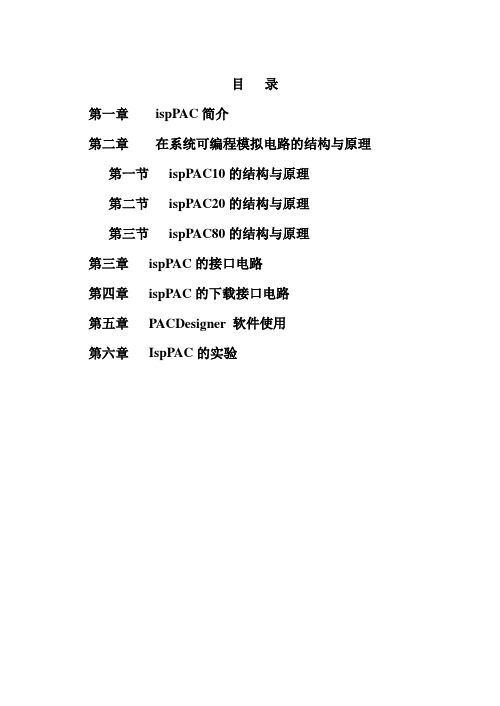

目录第一章ispPAC简介第二章在系统可编程模拟电路的结构与原理第一节ispPAC10的结构与原理第二节ispPAC20的结构与原理第三节ispPAC80的结构与原理第三章ispPAC的接口电路第四章ispPAC的下载接口电路第五章PACDesigner 软件使用第六章IspPAC的实验第一章ispPAC简介1992年美国Lattice公司发明了在系统可编程技术(In-System Programmability),彻底改变了传统数字电子系统的设计和实现方法,开创了数字系统设计的里程碑。

在21世纪来临的前夕,1999年11月,Lattice 公司又推出了在系统可编程模拟电路(In-System Programmability Programmable Analog Circuits),翻开了模拟电路设计方法的新篇章,为电子系统设计自动化(EDA)技术的应用开拓了更广阔的前景。

与数字的在系统可编程大规模集成电路(ispLSI)一样,在系统可编程模拟器件允许电路设计者使用开发软件在计算机中设计、修改模拟电路,进行电路特性模拟,最后通过编程电缆将设计方案下载至芯片中,在系统可编程器件可实现三种功能:(1)信号调理(2)信号处理(3)信号转换。

信号调理主要是能够对信号进行放大、衰减、滤波;信号处理是指对信号进行求和、求差、积分运算;信号转换是指能把数字信号转换成模拟信号。

目前已推出了三种器件:ispPAC10和ispPAC20和ispPAC80。

IspPAC的开发软件为PACDesigner,对计算机的软、硬件配置要求如下:(1)Windows 95,98,NT(2)16MB RAM(3)10MB 硬盘(4)Pentium CPU软件主要特征(1)设计输入方式:原理图输入(2)模拟可观测电路的幅频和相频特性(3)支持的器件:ispPAC10、ispPAC20、ispPAC80(4)内含用于低通滤波器设计的宏(5)能将设计直接下载第二章在系统可编程模拟电路的结构与原理在系统可编程模拟电路提供三种可编程性能:(1)可编程功能:具有对模拟信号进行放大、转换、滤波的功能;(2)可编程互连:能把器件中的多个功能块进行互连,能对电路进行重构,具有百分之百的电路布通率;(3)可编程特性:能调整电路的增益、带宽和阈值。

基于可编程模拟器件的精密整流电路设计

1引 言 .

本低,可靠性高与保密型强的特点 。

输 出放大 器组成 、配 以 电阻 p A 其 开发 软件 是基 于W n o s 台 的 构 成一个 真正 的差分输入 、差 分输 PC s id w 平

( n s s e r g a m b e A a o PC D s ge , 目前版本为6 0 i — y t m P o r m a 1 n l g A e in r . ,提 出的基本单元 电路 ,如2 图所示 。其

…

…

…

…

…

…

…

…

…

…

一

鳗 廑 __ (- ( ( (

基于可编程模拟器件 的精密整流 电路设计

中州大学工程技术 学院 时 伟 陈 良

【 摘要 】介绍了一种基于在系统可编程模拟器件i P C 精密整流电 sA p 路设计方法,在i P C0 s A 2 ̄片上实现,将整个电 p 路集成

于一块芯片 中,提高 了电路的集成度和可靠性。可对 目标芯片重新编程 以升级 电路结构,缩短 了研制周期,降低 了设计成本。

【 关键词 】可编程模拟器件;整流电路;模拟

Absr c :A sg eh d o ci e ic i wi i h p e ii n i l me t d o ・y t m r g a ta t De in m to f e t r r u t t h g r cso r f c i h mp e n e n i - se p o r mma l n l g c ru ti i t ・ ns b ea a o ic i s n r ・ o d c d i ep p r l h at r tg ae i g ec i oi r v e i tg a i n a d r l b l y o t ecr u t h o l h p c n b u e t a e . ep rsa ei e td i a s l h p t n h Al t n r n n mp o et e to n i i t f h i i T eg a i a e h n r ea i c . c

在系统可编程模拟器件的结构及原理11.3

11.3 在系统可编程模拟器件的应用电路

11.3.1 放大电路设计 1.信号耦合方式 .

上页

下页

返回

模拟电子技术基础

(1) 简单的直接耦合 +5V R1 R2 + R3 RX _ IA OA + _

ispPAC10

上页 下页 返回

模拟电子技术基础

(2) 外接偏置电路的直接耦合 VREF R1 + uI _ R1 R2 VREF ispPAC10

上页

U3 (s)

–1

下页

返回

模拟电子技术基础

由传递函数得三运放组成的双二阶滤波器 R3 C1 R4 + uI _ C2

_ R1 +

R6 R5 u2

_ +

A1

R2 u1

_ +

A2

A3

u3

上页

下页

返回

模拟电子技术基础

2.用ispPAC器件实现双二阶滤波器 . 器件实现双二阶滤波器 uI k11

IA1 1

上页 下页 返回

R2 + _ IA OA + _

模拟电子技术基础

(3) 阻容耦合 C + uI _ C R + _ R VREFout ispPAC10 IA OA + _

上页

下页

返回

模拟电子技术基础

VREFout 缓冲电路

上页

下页

返回

模拟电子技术基础

2.增益设置方法 . (1) 整数倍增益的设置方法 + 4 PAC Block1 IA1 _

1

+ OA1

2.5 V

IA2

在系统可编程器件ispPAC及其应用

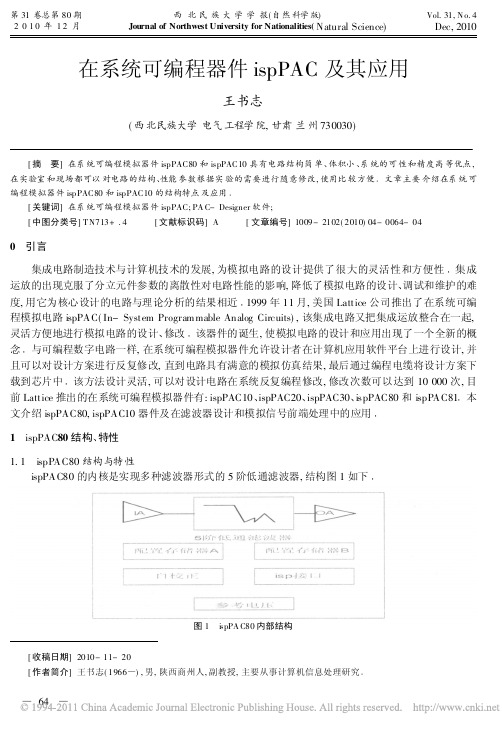

第31卷总第80期 西北民族大学学报(自然科学版)Vol.31,N o.4 2010年12月 Journal of Northwest University for Nationalities(Natural Science)Dec,2010在系统可编程器件ispPAC及其应用王书志(西北民族大学电气工程学院,甘肃兰州730030)[摘 要]在系统可编程模拟器件ispPAC80和ispPAC10具有电路结构简单、体积小、系统的可性和精度高等优点,在实验室和现场都可以对电路的结构、性能参数根据实验的需要进行随意修改,使用比较方便 文章主要介绍在系统可编程模拟器件ispPAC80和ispPAC10的结构特点及应用[关键词]在系统可编程模拟器件ispPAC;PA C-Designer软件;[中图分类号]T N713+.4 [文献标识码]A [文章编号]1009-2102(2010)04-0064-040 引言集成电路制造技术与计算机技术的发展,为模拟电路的设计提供了很大的灵活性和方便性 集成运放的出现克服了分立元件参数的离散性对电路性能的影响,降低了模拟电路的设计、调试和维护的难度,用它为核心设计的电路与理论分析的结果相近 1999年11月,美国Lattice公司推出了在系统可编程模拟电路ispPAC(In-System Program mable Analog Circuits),该集成电路又把集成运放整合在一起,灵活方便地进行模拟电路的设计、修改 该器件的诞生,使模拟电路的设计和应用出现了一个全新的概念 与可编程数字电路一样,在系统可编程模拟器件允许设计者在计算机应用软件平台上进行设计,并且可以对设计方案进行反复修改,直到电路具有满意的模拟仿真结果,最后通过编程电缆将设计方案下载到芯片中 该方法设计灵活,可以对设计电路在系统反复编程修改,修改次数可以达到10000次,目前Lattice推出的在系统可编程模拟器件有:ispPAC10、ispPAC20、ispPAC30、ispPAC80和ispPAC81 本文介绍ispPAC80,ispPAC10器件及在滤波器设计和模拟信号前端处理中的应用1 ispPAC80结构、特性1.1 ispPAC80结构与特性ispPAC80的内核是实现多种滤波器形式的5阶低通滤波器,结构图1如下图1 i spPA C80内部结构[收稿日期]2010-11-20[作者简介]王书志(1966 ),男,陕西商州人,副教授,主要从事计算机信息处理研究图2为简化的5阶低通滤波器的原理图,分析传递函数可知,滤波器的性能和类型由C1,C2,C3, C4,C5,L2,L4个电容共同来决定,改变其值,可以获得不同幅频特性和相频特性的滤波器,其滤波范围宽:50kH z~750kH z,可以实现如:Chebyshev(切比雪夫)、Bessel(贝赛尔)、Butterw orth(巴特沃斯)等多种类型的滤波器,开发工具PAC-Designer的库中提供了8000多种滤波器参数供选择 在ispPAC80器件结构中,包含同时存贮两组不同参数的五阶滤波器,配置存储器CfgA和CfgB用E2CMOS单元,通过8位SPI寄存器不同位的组合来选择A组或者B组,并且通过Bit7和Bit6两位的4种组合来决定滤波器的增益,其分别为:0dB,6dB,14dB,20dB图2 ispPA C80实现滤波器原理图1.2 ispPAC80的管脚表1 ispPAC80的管脚12345678910111213141516T SM T CK T DI T DO CS CA L EN SP I G ND V ERF(o)IN-IN+T EST OU T-OU T+T EST VSispPAC80是16管脚的集成电路,有PDIP和SOIC两种封装形式 从表1可以看出,ispPAC80有一对模拟输入管脚IN+/IN-,和一对模拟输出管脚OUT+/OUT- 两个测试管脚TEST,参考电压输出管脚VREFOUT,自校正输入管脚CAL,SPI模式使能管脚ENSPI,片选端CS和isp接口电路输入、输出管脚TMS、TCK、TDI、TDO管数字信号输入、输出管脚 电源管脚VS、接地管脚GND1.3 用ispPAC80设计滤波器启动PAC-Designer软件,在文件菜单里选择new,在出现的对话框中选择ispPAC80,就会出现其内部模拟电路,它包含一个输入仪器放大器IA、一个输出放大器OA和一个5阶低通滤波器,IA的增益只能设置为1、2、5、10 两个配置存储器cfgA、cfgB用来存放各种类型的5阶低通滤波器参数 两个配置存储器存放的滤波器参数经过一个多路选择器送给5阶低通滤波器,由设计者通过开发软件编程选择决定,如要设计一个截止频率为170.17kHz的bessel滤波器,选择ID=165,其参数送给5阶低通滤波器,仿真波形如图3,若仿真结果与设计要求有所偏差,可以调整滤波器7个电容参数图3 滤波器仿真波形从仿真图可以读出,-3.00DB点的频率为170kHz,对应的相频特性点为-137.90Deg,完全满足设计要求2 ispPAC 10的应用2.1 ispPAC10在信号基本处理中的应用用ispPAC10设计一个放大倍数为3的放大电路,直流耦合的接口电路见图4图4 ispPAC10的模拟信号接口电路以上电路R 1=R 2=R 3=R 4=R ,均为200 ,根据叠加原理,V IN+=V SE1R 2R 1+R 2+VREF OUT R 1R 1+R 2,V IN-=V SE2R 4R 3+R 4+VREF OUT R 3R 3+R 4,当输入差分信号时,V IN =V IN+-V IN-=12V SE1-V SE2,设计一个增益为3的放大电路,在PAC-Designer 软件平台上,把IN7设置为3,点击菜单栏tools,dow nload,确保下载电路正常,用并口进行下载,在硬件上测试,数据表2 ispPA C10下载测试数据输入差分信号0.200.400.600.80 1.00 1.20 1.40 1.60 1.80 2.00 2.20输出0.300.600.90 1.21 1.52 1.81 2.11 2.42 2.73 3.00 3.33增益333 3.01 3.04 3.01 3.01 3.02 3.0333产生的误差主要有测量仪表的系统误差、接口电路的电阻误差以及测量过程中的偶然误差等2.2 ispPAC10在小信号测量系统中的应用ispPAC10基本单元是PACBLOCK 块,它由两个具有差分输入,增益为到整数步进可调的仪用放大器和差分输出的求和放大器组成,反馈网络由一个电阻和电容构成,电阻由可编程开关控制其通与断,电容回路提供了128个可编程电容,大小从1.07PF 到61.59PF,根据电路设计需要由开发软件确定其大小值单片机构成的智能测量系统已经应用在很多领域,在该系统中,传感器给出的模拟信号前端处理十分重要,它的功能是把含有噪声的微弱电信号进行选择,滤波,放大后送给ADC,如果这些环节由独立的运放实现,需要的运放数量为7至8个,而且还需要大量电阻和电容,设计出的电路结构复杂,测量精度不高,电路调试不变 如果采用可编程模拟器件,只需要一片ispPAC10即可完成模拟信号的前端处理,图4是利用ispPAC10构建的小信号测量系统原理结构图,CD4052是一个差分4通道数字控制模拟开关,有A 、B 两个二进制控制输入端和INH 输入,具有低的导通阻抗和截止漏电流 用该芯片设计出的电路结构简单,测量精度高,调试方便在由核技术实现的非接触式流体管道密度测量仪表中,传感器给出的信号在送进ADC 和单片机以前也需要进行相应的处理,在可编程模拟器件问世以前,由运放组成的庞大处理前端电路,干扰大、精度不高 如果利用可编程模拟器构建前端模拟信号的处理,具有电路结构简单,运行稳定,抗干扰,测量精度高等优点3 结语在系统可编程模拟芯片的问世,使模拟电子电路的设计以及实现方法与以前相比发生了比较大的变革,运用PAC-Designer开发工具及ispPAC80、ispPAC10芯片设计滤波器和小信号采集前端电路,在实验室和在现场都可以对电路的结构、性能参数根据实际的需要进行随意修改,使用方便,能缩短产品的开发周期,节约了成本 用该系列器件设计的产品,电路结构简单,体积小,系统的可靠性和精度高图5 小信号测量原理图参考文献:[1]华成英等 模拟电子技术基础[M].北京:高等教育出版社,2007[2]赵曙光等 可编程模拟器件原理、开发及应用[M].西安:西安电子科技大学出版社,2002[3]刘笃仁 用I SP器件设计现代电路与系统[M].西安:西安电子科技大学出版社,2002[4]张洪瑞等 FPGA/CPLD应用设计200例[M].北京:北京航空航天大学出版社,2009(上接第23页)该软件的SIMA TIC指令集包含三种语言,即语句表(STL)语言、梯形图(LAD)语言、功能块图(FWD)语言 PLC控制程序由一个主程序和若干子程序构成,程序的编制在计算机上完成,编译后通过PC/PPI 电缆把程序下载到PLC 控制任务的完成,是通过在RUN模式下主机循环扫描并连续执行用户程序来实现的1)控制系统主程序设计 PLC主程序主要由系统初始化程序、水泵电机起动程序、小功率水泵电机变频/工频切换程序、水泵电机换机程序、阀门开启关闭程序、模拟量(压力、频率)比较计算程序、停机程序和报警程序等构成2)控制系统子程序设计 PLC子程序设计共包括四个子程序,分别是模拟量初始化子程序、模拟量数据处理子程序、自由通信初始化子程序、自由数据通信子程序4 改造后达到的效果经过改造,整个系统由水压传感器反馈信号与水压设定值在控制器内形成闭环,根据压力与流量优化控制泵组的调速运行,并自动调整泵组的运行台数,实现了不论用水量如何改变都可保持管网压力基本恒定,达到了稳压、节能的目的,实现了用变频器对电机进行软启软停,减少了设备损耗,延长了电机寿命,同时消除了水泵启动和停止时的水锤 经过一年多的运行统计,月均节电27%左右,月均节水35%左右,节能效果显著参考文献:[1]陈伯时,陈敏逊 交流调速系统[M] 北京:机械工业出版社,1998[2]王涛,王爱国 PL C及变频技术实现的恒压供水系统[J] 自动化博览,2004[3]侯存玉,马维明 变频器在恒压供水系统中的应用[J] 河北省科学院学报,2000。

在系统可编程模拟器件ispPAC80及其应用

Abs r c t a t:

M ana e te t rs a d fau e ft eI—y tm r g a i rhteu e n e tr so h I s se p o r mma l n lg cr ut s PAC8 I b ea ao ic i.ip 0.a e d r e

s rb d i h a e I l me t to 。 i e e t5 h o d r l we a s f t r t n ip AC8 y me n f e e c i e n t e p p r mp e n a in f f r n t r e o r p s i e s wih a P d f l s 0b a so v l d o me t s fwa e P p n o t r AC D sg e s a s r s n e Th e h i u se p d t h e i n p o e s i l y n r t — — e t n r i lo p e e t d e t c nq e x e ie t e d sg r c s ,s mp i i g p o o f t p ic i i lme t to n o i c to . y e cr u t mp e n a i n a d m d f a i n i Ke r y wo ds: ip AC {An l g cr u t Fi e ;EDA sP a o ic is; l r t 。

EEACC . 1 7 0 2

1 在 系统 可编 程 技 术 的特 点

2 世 纪9 年 代 , 国 L ti 0 0 美 at e半导 体公 司推 出了 c 在 系统 可 编程器 件 及 在系 统 可编 程技 术 。 系统 可 在 编 程器 件是 一种 提 供 可组 态 结构 的器 件 。 系统 可 在 编 程技术 是一种 在计算 机上 用相应 的开 发软件进 行 电路方案 设计 、 拟仿真 后 , 模 将设计 方案下 载至 在系 统 可编 程器 件 , 在 系统可 编 程器 件 实现 既定 功 能 使 的 技术 , 许用 户对 已装配 在 系 统 中的在 系统 可 编 允 程 器件 进行 功能 重 新 设置 l 次 以上 。 万 因而 , 以缩 可 短开发周期、 降低 开 发成 本 , 方便 地 “ 重构 ” 电路 功 能。 近年来 , 系统可编程 技 术得到 了越来越 广 泛的 在

在系统可编程模拟器件(ispPAC)离散性探讨

S s e Pr g a y t m o r mm a i t o r mm a l a o r u t b i Pr g a l y b e An l g Cic is

Z HOU Ho g o W ANG e2 n-u, W i YU n - h n , Mi g s e g

0c 2 ( L o) 6

在 系统可编程模拟器 件 ( p A 离散性探讨 i P C) s

周 红 鸥 , 王 伟 , 明生 余

( . 南民族 大学 , 1西 成都 6 0 4 ; . 10 1 2吉林航 空工程 学校 , 吉林 吉林 1 2 0 ) 3 1 2

摘 要 :p A i P C的 出现 使得模 拟 电路设 计 中在信 号 的调理 、 s 信号处 理及 信号 的转换 方 面可 采 用 图形结 构语 言 实现计 算 机编 程设 计 , 此外 软 件 的仿 真 功能 . 使 得对 设 计结 果验 证 更 具 有直 观性 和便 捷性 , 大大 减化 了许 多模 拟 电路 设计 和检 测 中费时 费力 的工 作 。但 是 . 结果 的仿 真 , 计 算机 对理 想 电路特 性 的模 拟 , 是 同具 体 电路 的实际 情况究 竟 存 在多 大差 距 ? 由于 在厂 家提供 的 资料 和相关 文献 中未 见报道 。 者就此 问题进 行 了探讨 。 作 关键 词 : p A 微 电子结 构 ; 编程 模 拟单元 ; i P C; s 可 电阻阵列 ; 离散性 ; 回归分 析

(. uh etU iesyf ai aie, hnd 10 1 hn; 1 otw s nvrt o N tnli C egu6 0 4, ia S i r o ts C 2 in ArE g er g Sho, in 12 ,l ,hn) .l i ni e n c olJi 2 inC ia Ji n i l 3 1 Ji 0

在系统可编程模拟器件ispPAC20及其应用

维普资讯

第 8期 20 0 2年 8月

电

子

Hale Waihona Puke 元 件 与

材

料

). l No 8 12 .

A ug. 0 2 2 0

E LEC TRONI COM P C ONE 1 & M ATER ALS J. s I

在 系统 可 编 程 模 拟 器 件 i P 2 s AC 0及 其 应 用 p

tc nq e frma i g v l g o to ld o cl t r VCO) a e n ip AC2 d t p rto rn i l ft eVCO.T e h iu o kn ot e c nr l s il o s( a e a b sd o s P 0 a heo eai np cp eo n i h he

Ab t a t s r c :Di c s e r h i tu t r d f a u e f ip AC2 - a i — y t m r g a s u s d a e t e ma n sr c u e a e t r s o s P n 0 n s se p o r mm a l n l g c r u t h b e a a o ic i,t e

ipP s AC2 nd IsAp i a i 0 a t plc ton

J N G a g , ANG u . u , ANG ng , a . a I Li n W G oy W Ya LIXi o y n

( _ l tc l n fr t nE gn e n l g , J g uUnv ri , h ni g J gu 2 2 1 ; . a ut f cec , 1 Ee r a a dI o mai n ier gCol e i s iesy Z eja i s 1 0 3 2 F c l o ine ci n o i e n a t n n a y S Ja guU iest, h nin Ja gu 2 2 1 ) i s nv ri Z eja g i s 10 3 n y n

ispPAC简介

第一章 ispPAC简介1999年11月,Lattice公司推出了在系统可编程模拟电路(In-System -Programmability Programmable Analog Circuits,以下简称ispPAC),为电子设计自动化(EDA)技术的应用开拓了广阔的前景。

与数字在系统可编程大规模集成电路(ispLSI)一样,ispPAC允许设计者使用开发软件通过计算机对模拟电路进行设计、修改、仿真,最后通过编程电缆将设计方案下载至芯片中。

ispPAC可实现以下三种功能:(1)信号调理:对信号进行放大、衰减、滤波。

(2)信号处理:对信号进行求和、求差、积分运算。

(3)信号转换:把数字信号转换成模拟信号。

目前已推出了五种芯片:ispPAC10,ispPAC20,ispPAC30,ispPAC80和ispPAC81。

ispPAC的开发软件为PACDesigner,软件主要特征:(1)设计输入方式:原理图输入;(2)模拟仿真:测试电路的幅频和相频特性;(3)支持器件:ispPAC10、ispPAC20、ispPAC30、ispPAC80、ispPAC81;(4)内含用于低通滤波器设计的宏;(5)能将设计直接下载;一、ispPAC20的结构在系统可编程模拟电路提供三种可编程性能:(1)可编程功能:具有对模拟信号进行放大、转换、滤波的功能。

(2)可编程互联:能把器件中的多个功能块进行互联,能对电路进行重构,具有百分之百的电路布通率。

(3)可编程特性:能调整电路的增益、带宽和阈值。

ispPAC器件可反复编程,编程次数可达1万次以上。

高集成度、高精确度的设计集于一片ispPAC器件中,取代了由许多分立元件组成所实现的电路功能。

ispPAC20器件由两个基本单元电路PAC块、两个比较器、一个8位的D/A转换器、配置存储器、参考电压、自动校正单元和isp接口所组成。

其内部结构框图和内部电路如下图1.1、1.2所示。

EDA常用术语及英文缩写

EDA常用术语及英文缩写电子设计自动化:EDA

片上系统:SOC

专用集成电路:ASIC

印制电路板:PCB

可编程逻辑器件:PLD

可编程模拟器件:PAC

在系统可编程模拟器件:ispPAC

复杂可编程逻辑器件:CPLD

现场可编辑门阵列:FPGA

硬件描述语言:HDL

可编程只读存储器:PROM

紫外线可擦除只读存储器:EPROM

电可擦除只读存储器:EEPROM

可编程阵列逻辑:PAL

通用阵列逻辑:GAL

可编程逻辑阵列:PLA

可编程逻辑阵列宏单元:LMC

输出逻辑宏单元:OLMC

可编程I/O单元:IOC

可编程内部连线:PIA

可编程逻辑块:CLB

输入/输出模块:IOB

可编程互连资源:PIR

数据选择器:MUX

在系统编程技术,在器件编程时,所用的无根信号线:(1):ispEN’:编程使能信号。

(2):SDO:数据输出线。

(3):SLCK:串行时钟线。

(4):SDI:向串行移位寄存器提供编程数据和其他命令。

(5):MODE:编程状态机的控制线。

全局布线区:GRP

输出布线区:ORP

逻辑阵列块:LAB

嵌入式阵列块:EAB

逻辑单元:LE

输入/输出单元:IOE

嵌入式系统块:ESB

边界扫描测试技术:BST

数字信号的硬件语言:VHDL Verilog HDL

模拟信号的硬件语言:AHDL

微波信号的硬件描述语言:MHDL。

在系统可编程模拟器件的结构及原理11.2

上页

下页

返回

上页

下页

返回

模拟电子技术基础

ispPAC10的PAC模块输出级 的 模块输出级 uI – gm1

IAF

CF +

_ uI

gm3 + _

a _ A+ _ a' + CF

uO+ + uO _ uO–

gm1

上页

下页

返回

模拟电子技术基础

PAC模块的有耗积分器等效电路 模块的有耗积分器等效电路 k1

IA1

CF RF

IA2

uI+

IA1

CF

IAFBiblioteka +_gm3 + _

_ A+ _ + CF

uO+ + uO _ uO –

输出相加放大器

上页 下页 返回

模拟电子技术基础

差分输入差分输出的OTA电路 电路 差分输入差分输出的 iO – uI+ + _ gm uI _ + uI– iO+ 图中

电路将差模输入电压转换为差模输入电流

模拟电子技术基础

构成一个等效电阻R 构成一个等效电阻 2.跨导运放(OTA)的基本应用电路 .跨导运放( ) ,实现电流电压变换 (1) OTA电压放大器 电压放大器 uI1 uI2 _

gm1

+

OTA1

_ iO1 i R

gm2

+

OTA2

iO2

uO

实现电压电流转换

上页

下页

返回

模拟电子技术基础

ispPAC10内部电路示意图 内部电路示意图

OTA1 C

可编程模拟器件ispPAC20在SoC系统中的应用

1 实例

圈 匝圈

图 1 i P C 0内部 结 构 框 图 s 输 出脚 都 标 了正 负 号 , ()所 只

1 1 i DeinE p r介 绍 . s s x et p g

是用作极性参考 , 连接时可 以互换连接。( ) 2 所有 的差

电阻有效 , 将其开关闭和 , 使其与 电容并联 , 为了比较 C P 比较器输 出, C 将 P比较器的正端连接在 O T U 2端 , P C

比较器的负端提供一个 15 的电压 , . V 所设计 的电路如

《 计量与飘试技术》o 8年第 3 2O 5誊 第 1 2期

尚风晗等 : 可编程模 拟器件 i P 2 s AC 0在 s c系统 中的应 用 p o

可编 程 模 拟 器 件 i P 2 s AC 0在 S C 系统 中的应 用 p o

Ap l ain o rg a p i t fP o r mma l ao rut i P c o beAn lgCi i p AC2 nS s m na C i c ss 0 i yt o hp e

端输入 、 单端输 出、 大倍 数为 2 的电路。因为 i — 放 倍 s p

P C 0精密滤波器范 围 1 一10 H , 10K z A2 O 0 K z在 0 H 以下

编程 电缆将设计方案下载到芯片中。同时还可以对 已装

配在 印制 板上 的 i P C进 行校 验 、 改 或重新设 计 。 s A p 修 12 i P C 0结 构及设 计 注意事 项 . s A 2 p

i D s n x e 是一套完整的 E D软件。设计输 s ei pr p gE t A 人可采用原理图、 硬件描述语言、 混合输人三种方式。能

在系统可编程模拟电路构成的测量电桥

全桥差动电桥

� � � � � 0 = 1 2 = � 如果 在差动电桥中正确连接传感器和补偿器 件,可有效地补偿非线性误差和温度等诸如此类环 境因素产生的影响,提高测量精度。

4

图2 典型的电桥电路

测量放大 器电路

采用 A 10 和各种电桥连接的电路的原理

图如图 5 所示。在电路设计中主要考虑以下 3 点: 输入,3 、4 端接 5 � 直流电源,第一桥臂接电阻 � � ( 1 )输入接口。注意直流电桥在 0 = 1 - 2 = 0 时,仍有 2 的共模电压,因此将电桥工作电 型传感器 1 (力敏、压敏、光敏、热敏等) ,其他 � 压设置为 5 ,使共模电压约为 2 .5 ,电桥差动 三臂为固定电阻,构成一个不平衡直流电桥。电桥 � � � � 输出便可直接与 A 10 差动输入方式匹配。 的初始平衡条件为: 1 4 = 2 3 。当 1 受到外界 因素 � � 作用时,其电阻值产生 � 1 = 的变 1� ( 2 )电路增益。为了使测量电路能配合多种传 感器,考虑到各种传感器的灵敏度,需要将放大电 化,电桥处于不平衡状态,其输出电压为: � � � � � 路增益设计为多段调节。利用一片 A 10 可以非 3 4 = = ( 0 14 2 4 � � � � 常方便地实现 2 0 B、40 B、60 B、80 B 四段调 1 - � 1 + 3 2 + 4 � � � 节,使 0 从 0.5 500 都能达到满幅输出。 � 1 2 � � � � � � ( 3 )抗干扰。在 A 10 在线编程中,将 (1 + ) � 1 � � � � � � � 设为最 大值, 四个 A B 构 成 3 B 带宽 为 5 式中,由电桥的初始平衡条件,设 = =

ZH O U H (S U

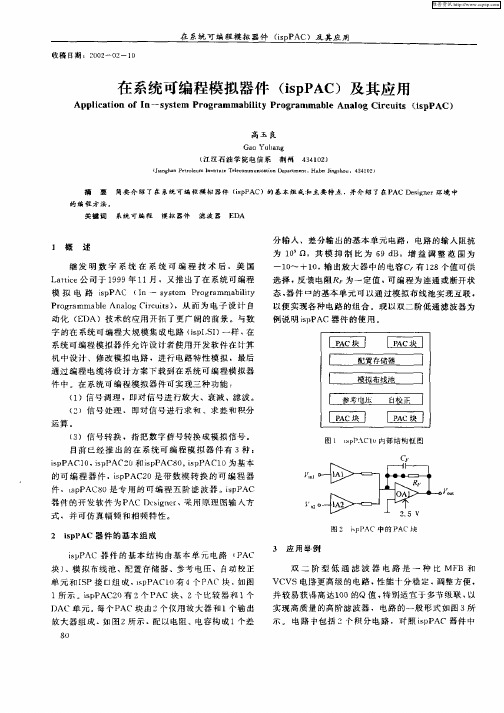

在系统可编程模拟器件(ispPAC)及其应用

动化 ( DA)技 术 的应用 开拓 了更广 阔的前 景 与数 E 字 的在 系统 可编程 大 规模集 成 电路 ( p I 一样 , iI ) s S 在 系统 可编 程模 拟器件 允许 设计 者使用 开 发软 件在计算 机 中设 计、修 改模 拟 电路 ,进 行 电路 特 性模 拟 ,最后

8 0

维普资讯

( 现代 电子技 术》 0 2 第4期 总第 1 5期 20 年 3

P C 块 的 结 构 . 2个 P A 用 AC 块 即 可 构 成 1个 双 二 阶 低

开 发软 件 P sg e AC Dein r中的模 拟器 对 所设 计 的 滤波 器 进行仿 真, 如频率 特性 与设 计要 求相 符 . 即可对P C A 器 件进 行 鳊程 ,编程是 通过 编程 电缆将 计算 机 的并行

。 一

圈2 i P s AC 中 的 P C块 p A

‘

3 应 用 举 例

块) 、模拟 布线 池 、配 置存 储 器、参考 电压 、自动校 正

单 元 和 IP 接 口组 成 , s P S i AC1 p 0有 4个 P C 块 , 图 A 如

双 二 阶 型 低 通 滤 波 器 电 路 是 一 种 比 MF 和 B VC VS电路更 高级 的 电路 , 能十分 稳定 ,调整方便 , 性 并 较 易获得 高达 1 0的Q值 , 0 特别适 宜于 多节 级联 , 以 实 现高 质量 的高 阶滤波 器 , 电路 的 一般形 式 如图 3所

为 l n,共 模 抑 制 比 为 6 B,增 益 调 整 范 围为 O 9d

在系统可编程模拟器件(ispPAC)基本原理与应用

① 为所要输入的电路图建立一个新文档

图4-33PAC-Designer主界面

选择了ispPAC10器件

图4-34 电路图设计输入界面

②编辑电路图连线;③配置增益

双二阶节滤波器(Biquad Filter)的实现

k11k12

V02

(CF1RF1)(CF 2 RF 2 )

VIN1 S 2

增益可微调的放大器

VOUT1=VIN1*k1+VIN1*k2/10 (4—5)

电压增益为: KV= VOUT1/ VIN1=k1+k2/10

(4—6)

KV =VOUT1/VIN1= k1 / k2 (4-7)

用 PAC-Designer 进行 设计输入与编辑的步骤:

① 为所要输入的电路图建立一个新文档 ② 编辑电路图连线 ③ 配置增益

参考电压 自校正

PAC 块

PAC 块

ispPAC10 内 部 结 构 框 图

ispPAC20

PAC 块

比较器

PAC 块

比较器

模 拟布线池

参考电压

DAC

自 校 正 配置存储器

ispPAC20 内 部 结 构 框 图

应用举例

(1)ispPAC的增益配置方法 (2)双二阶节滤波器 (Biquad Filter)的实现 (3)非线性电路的实现

ispPAC10、ispPAC20的共性结构

• PAC块(PAC block); •模拟布线池; •配置(组构)存储器; •参考电压和自动校正单元; • ISP接口。

PAC块

VOUT=VIN1*k1+VIN2*k2 (4 - 4)

ispPAC10

PAC 块

PAC 块

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在系统可编程模拟器件(ispPAC)原理及应用

•概述

•结构与性能简介—(1)共性结构与性能;(2) ispPAC10、ispPAC20、ispPAC80的结构和性能•应用举例(a)信号调理—放大、衰减与滤波;(b)信号运算—求和、求差和积分;(c)信号转换D A。

(1)ispPAC的增益配置方法;(2)双二阶节滤波器(Biquad Filter)的实现;(3)非线性电路的实现

•其它类型的可编程模拟器件

Lattice 1992年发明ispPLD,1999年又推出在系统可编程模拟电路ispPAC 开发软件:

设计输入方式:

原理图

支持“宏”设

计

提供:与

OrCAD

PAC-Designer可对电路的幅频和相频特性直接进行模拟分析,但不能进行时域模拟分析。

如需进行时域模拟分析,可利用PAC-Designer(1.21版以上)与Pspice/OrCAD的接口将所设计的PAC电路转到Pspice/OrCAD中去进行时域模拟分析。

ispPAC10、ispPAC20的共性结构

•PAC块(PAC block);

•模拟布线池;

•配置(组构)存储器;

•参考电压和自动校正单元;•ISP接口。

PAC块

V OUT=V IN1*k1+V IN2*k2(4 -4)

ispPAC10

PAC块PAC块配置存储器

模拟布线池

参考电压自校正

PAC块PAC块

ispPAC10 内部结构框图

ispPAC20

PAC块PAC块比较器比较器

模拟布线池

参考电压DAC 自校正配置存储器ispPAC20 内部结构框图

应用举例

(1)ispPAC的增益配置方法

(2)双二阶节滤波器(Biquad Filter)的实现(3)非线性电路的实现

增益可微调的放大器

V OUT1=V IN1*k1+V IN1*k2/10

(4—5)电压增益为:

K V=V OUT1/V IN1=k1+k2/10

(4—6)

K V =V OUT1/V IN1= k1 / k2 (4-7)

用PAC-Designer 进行设计输入与编辑的步骤:

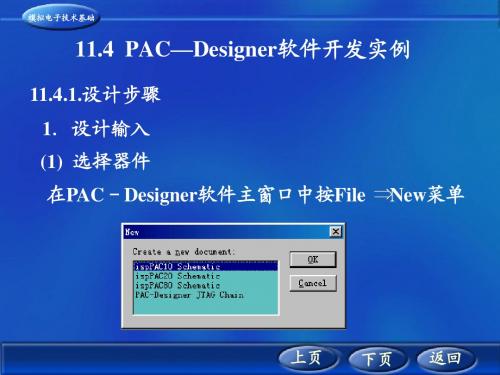

①为所要输入的电路图建立一个新文档

②编辑电路图连线

③配置增益

①为所要输入的电路图建立一个新文档

图4-33PAC-Designer主界面

选择了ispPAC10器件

图4-34 电路图设计输入界面

②编辑电路图连线;③配置增益

双二阶节滤波器(Biquad Filter)的实现

)

)(()()

)((221121

12112221112

11102F F F F F F F F F F IN R C R C k k R C S S R C R C k k V V +

+=20220ω+ω+ω=Q S S )

)(()(221121

111121

11111F F F F F F F F IN O R C R C k k R C S S R C S

k V V +

+=

2020ω+ω+ω=Q S S Q S ))((221121

110F F F F R C R C k k =ω21

122

1

k k C C Q F F =低通滤波器(4-9)高通滤波器(4-10)式中:

使用宏设计双二阶节滤波器

的步骤

•①打开电路图设计窗口依次点击主窗口的菜单File → New → ispPAC10 Schematic;

•②启动宏依次点击电路图设计窗口的菜单Tools → Run Macro…→ ispPAC10Biquad.exe;•③为模拟设置有关参数点击电路图设计窗口主菜单的Options→Simulator…;

•④启动模拟点击电路图设计窗口主菜单的Tools→Run Simulator。

图4-37启动设计双二阶节滤波器的宏

图4-38 滤波器宏设计输入窗口

其它类型的可编程模拟器件

Zetex公司

Microchip公司

PAC-Designer 2.0

THE END

THANKS FOR WATCHING

2002/10/9。