EMC Design Considerations for PSoC CapSense(TM) Applications - AN2318 (ZH)

《EMC 设计分析方法与风险评估技术》读书笔记模板

读书笔记

读书笔记

这本书拓宽了我的眼界,EMC不再是神秘而不可捉摸的,同时也让我对EMC有更深入的了解。 强烈建议硬件工程师看几遍,注意不是一遍,是反复结合项目中的EMI问题是读去思考。

目录分析

1

第1章 EMC与 EMC设计基础

第2章共模电流 2

的形成与EMC 问题实质解读

3

第3章 EMC风 险评估

第12章 EMC风险管理与产品研发

12.1 EMC设计技术与管理的发展现状 12.2 EMC风险管理的定义 12.3 EMC风险管理的重要性 12.4 EMC风险管理原则 12.5 EMC风险管理过程

精彩摘录

精彩摘录

这是《EMC 设计分析方法与风险评估技术》的读书笔记模板,可以替换为自己的精彩内容摘录。

第5章滤波、去耦、旁路设计

5.1电容器 5.2 RC电路 5.3再谈LC电路 5.4滤波器和滤波电路的设计分析 5.5常用信号接口电路的滤波电路设计原理 5.6滤波器或滤波电路的安装与放置 5.7滤波器与共模电流分析 5.8 PCB中的去耦设计 5.9电容旁路的设计方法

第6章 PCB布局布线EMC设计

第12章 EMC风 险管理与产品 研发

第1章 EMC与EMC设计基础

1.1什么是EMC和EMC设计 1.2产品的EMC性能是设计赋予的 1.3 EMC是常规设计准则的例外情况 1.4 EMC理论基础

第2章共模电流的形成与EMC问题实质解读

2.1 EMC测试与共模电流分析 2.2产品电路中的共模和差模信号 2.3 EMC测试的实质与共模电流 2.4典型共模干扰在产品内部传输的机理 2.5共模干扰电流影响电路工作的机理 2.6电路的干扰承受能力分析 2.7 EMI共模电流的产生机理

赛普拉斯 PSoC 4000S 系列数据手册说明书

请注意赛普拉斯已正式并入英飞凌科技公司。

此封面页之后的文件标注有“赛普拉斯”的文件即该产品为此公司最初开发的。

请注意作为英飞凌产品组合的部分,英飞凌将继续为新的及现有客户提供该产品。

文件内容的连续性事实是英飞凌提供如下产品作为英飞凌产品组合的部分不会带来对于此文件的任何变更。

未来的变更将在恰当的时候发生,且任何变更将在历史页面记录。

订购零件编号的连续性英飞凌继续支持现有零件编号的使用。

下单时请继续使用数据表中的订购零件编号。

PSoC 4:PSoC 4000S 系列数据手册可编程片上系统(PSoC)概述PSoC ® 4是一个可扩展和可重配置的平台架构,用于基于Arm ® Cortex ®-M0+ CPU 的可编程嵌入式系统控制器系列。

它集成了可编程和可重新配置的模拟和数字模块,并且能够灵活自动地路由资源。

PSoC 4000S 产品系列是PSoC 4平台架构的一个成员。

该产品系列集成了下列四项:拥有标准通信和时序外设的微控制器、具有一流性能的电容式触摸感应(CapSense )系统、可编程的通用、连续和带有开关电容的模拟模块以及可编程接口。

针对新应用和设计的要求,PSoC 4000S 产品与PSoC 4平台系列产品向上兼容。

特性32位MCU 子系统■48 MHz Arm Cortex-M0+ CPU,配置单周期倍频 ■包含读取加速器的闪存容量可达32 KB ■SRAM 的容量高达4 KB可编程模拟资源■由电容式感应模块提供的单斜10位ADC 功能■可用在任意引脚上的两个电流DAC (IDAC ),用于通用目的或电容式感应应用■可在深度睡眠模式下工作的两个低功耗比较器可编程数字资源可编程逻辑模块支持在输入和输出端口上执行Boolean (布尔)操作低功耗操作模式的电压范围:1.71 V ~ 5.5 V■在深度睡眠模式下,模拟系统可正常工作,并且数字系统仅消耗2.5 μA 的电流电容式感应■赛普拉斯的CapSense Sigma-Delta (CSD )模块提供了一流的信噪比(SNR > 5:1)和防水功能■赛普拉斯提供的软件组件使电容式感应设计变为更加简单■自动硬件调校(SmartSense™)串行通信■两个运行时可重新配置的独立串行通信模块(SCB ),可配置为I2C 、SPI 或UART 功能LCD 驱动能力■GPIO 上的LCD segment 驱动能力定时和脉冲宽度调制器■五个16位定时器/计数器/脉冲宽度调制器(TCPWM )模块■支持中心对齐、边沿对齐和伪随机模式■基于比较器触发的“Kill ”信号,适用于电机驱动和其它高可靠性数字逻辑的应用多达36个可编程的GPIO 引脚■48-TQFP 、40-pin QFN ,32-pin QFN 、24-pin QFN ,32-pin TQFP 和25-ball WLCSP 封装■任何GPIO 引脚都可用作CapSense 、模拟或数字引脚■可编程驱动模式、强度和转换速率时钟源■32-kHz 监视晶振 (WCO)■±2%精度内部主振荡器(IMO)■32-kHz I 内部低速振荡器 (ILO)ModusToolbox™ 软件■多平台工具和软件库的综合集合。

emc正向设计及流程 -回复

emc正向设计及流程-回复什么是EMC正向设计及流程?EMC 正向设计是一种跨学科的设计方法,旨在确保电子产品的电磁兼容性(Electromagnetic Compatibility,简称EMC)。

它着重于电子产品设计的早期阶段,以确保在产品完成后,能够满足或超越所有的电磁兼容性要求。

EMC 正向设计流程是逐步地将EMC 相关活动纳入到产品设计阶段的过程。

它包括了以下几个主要步骤:需求分析、电磁环境分析、电磁噪声控制、电磁屏蔽设计以及电磁兼容性测试。

首先,需求分析是确定产品EMC 目标的重要步骤。

在这一步骤中,设计团队将与客户进行沟通,理解产品将被使用的环境以及使用者的需求。

这有助于建立一个明确的EMC 目标,并确保设计团队了解产品在不同情况下需要满足的EMC 要求。

接下来,电磁环境分析是为了确定产品将面临的电磁环境条件。

这包括接收和传输可能导致想要设计的产品产生电磁干扰的电磁场。

设计团队需要了解这些环境并确定可能会干扰产品正常运行的电磁源。

在确定了产品可能面临的电磁环境后,设计团队将采取各种措施来控制电磁噪声。

这包括选择合适的电磁屏蔽材料、设计适当的排线和接地系统、减少器件之间的干扰等。

这些措施旨在降低电磁干扰的风险,确保产品正常运行。

随着设计团队采取控制措施,他们还将采用电磁屏蔽设计来进一步减少电磁干扰。

电磁屏蔽的目的是以物理方式阻挡电磁辐射的传输,使其不能干扰其他电子设备。

设计团队将选择合适的材料和设计方法来实现电磁屏蔽,同时确保产品的其他关键功能不受影响。

最后,为了确保产品满足EMC 相关要求,设计团队将进行电磁兼容性测试。

这些测试旨在验证产品在现实环境中的电磁性能。

测试过程通常包括辐射测试、传导测试、灵敏性测试等。

总结起来,EMC 正向设计及其流程是一种早期阶段的电子产品设计方法,旨在确保产品在不同电磁环境下具有良好的电磁兼容性。

通过需求分析、电磁环境分析、电磁噪声控制、电磁屏蔽设计以及电磁兼容性测试等步骤,设计团队能够识别和控制电磁干扰的风险,并确保产品满足EMC 相关要求。

电气设备的EMC设计、测试和整改

目录

• 引言 • EMCC设计 • EMC测试 • EMCC整改 • 案例分析

01

引言

目的和背景

01

随着电子技术的飞速发展,电气 设备在各个领域得到广泛应用, EMC问题逐渐凸显。

02

本文旨在探讨电气设备的EMC设 计、测试和整改,以提高设备电 磁兼容性,降低电磁干扰对设备 性能的影响。

小电磁干扰的影响。

接地方式

02

常见的接地方式包括单点接地、多点接地和混合接地等,应根

据设备的工作频率和接地需求选择合适的接地方式。

接地电阻

03

接地电阻的大小直接影响到接地的效果,应确保接地电阻值小

于规定的限值。

05

案例分析

设计案例

案例一

案例二

案例三

案例四

某电动工具的EMC设计

某智能家居系统的EMC 设计

滤波器的作用

滤波器可以滤除信号中的 噪声和干扰,提高信号的 纯净度。

滤波器的种类

常见的滤波器包括电容器、 电感器和RC电路等,应根 据需要选择合适的滤波器。

滤波器的安装

滤波器应安装在设备的电 源线和信号线上,尽量靠 近干扰源或敏感元件,以 减小干扰的影响。

接地整改

接地的作用

01

接地可以将设备与大地连接起来,形成一个等电位体,从而减

详细描述

辐射发射测试包括对设备在各个频段的电磁辐射进行测量, 以评估其对周围电子设备和通信系统的影响。测试方法包括 场地测试和暗室测试,其中暗室测试可以模拟无外界干扰的 环境。

传导发射测试

总结词

传导发射测试用于测量电气设备在电源线上产生的电磁干扰,以评估其对电源 系统的干扰程度。

EMC Considerations on PCB Design for a High-Power Converter Control System

In the development process, modem PCB design software was used. The whole process can be divided into two parts: schematic and layout design. First, the schematic was created. The circuit schematic serves as a basis for the layout design. It insures that the layout and design are consistent. Today's powerful tool of the PCB design software is an autorouter. It means that the software can route the whole PCB automatically, following the routing rules specified by the user. Autorouting has many advantages, e.g. it is much faster than manual routing, it takes EMC rules into account, autorouter always optimizes track lengths and avoids sharp windings. The disadvantages are that it takes some time to set up the routing rules and the expected result may not be ensured. Sometimes, when the PCB is too complicated, the autorouter is not able to route all the tracks. Thus, you still have to route some tracks manually. In the current project, a combination of manual routing and autorouter was applied. [1]

电磁兼容设计参考电路

电磁兼容设计参考电路EMC设计参考电路是为了解决设备在工作过程中的电磁兼容性问题而设计的电路。

下面将介绍一些常见的EMC设计参考电路。

1.滤波器:滤波器用于消除电源或信号线上的高频噪声。

常见的滤波器包括LC 滤波器和RC滤波器。

LC滤波器通过串联电感和并联电容来实现高频噪声的滤波。

而RC滤波器则通过串联电阻和并联电容来实现滤波效果。

在设计EMC参考电路时,需要根据设备的工作频率选择合适的滤波器。

2.接地:接地是EMC设计中非常关键的一环。

正确的接地可以减小电磁辐射和抑制外界电磁干扰。

在EMC设计中,常用的接地方法包括单点接地、分布式接地和屏蔽接地。

单点接地是将所有接地点连接到一个公共的接地点,分布式接地是利用多个接地点来减小接地电阻,而屏蔽接地则是使用金属屏蔽来隔离电磁噪声。

3.屏蔽:屏蔽是EMC设计的重要手段之一、通过在电路板或设备上加装金属屏蔽罩,可以阻挡外界的电磁辐射和干扰。

屏蔽的材料可以选择导电性能较好的金属材料,如铁、铜、铝等。

在设计屏蔽时,还需要注意屏蔽的接地问题,以确保其有效性。

4.增加衰减元件:在电路中添加合适的衰减元件,可以有效地减小电磁辐射和干扰。

常见的衰减元件有抑制电流的电阻、吸收电磁波的衰减器等。

选择合适的衰减元件,可以根据电路的特点和工作频率进行。

5.管理信号布线:在EMC设计中,合理的信号布线也非常重要。

信号线的布置和长度应该尽量减小对其他电路的干扰。

可以通过使用差分信号布线、降低信号线长度、使用屏蔽线等方法来管理信号布线。

EMC设计参考电路不仅可以减小电磁辐射和干扰,还可以提高设备的抗干扰能力,确保设备的正常工作。

在实际设计中,还应该根据具体的项目需求进行进一步的优化。

an2318应用中EMC设计要考虑的问题

应用手册AN2318 PSoC CapSense™应用中EMC设计要考虑的问题作者:Mark Lee相关项目:无相关器件系列:CY8C21x34PSoC Designer Version:4.2相关应用手册:AN2155、AN2292摘要用PSoC CapSense设计符合EMC标准的电容式触摸传感系统,有助于新设计容易通过资格鉴定,并提高系统的稳定性,降低成本。

我们将给出符合标准的带有检测结果的实例。

引言各电子器件都必须符合发射能量的特定要求,并对外部干扰有一定的抗扰度。

美国FCC及其他国家类似的监管机构制定了有关标准,确保电子器件不会彼此干扰。

因此,您的计算机不会干扰您的电视,还有更糟糕的情况下医院的X光机或通风设备不会破坏重要的医疗监视器的工作。

现代高速数字电子设备能生成极高速的信号,该信号可能发出大量噪音。

CMOS模拟电路和数字电路本身具有无限的输入阻抗。

因此,其对外部的电场、磁场相当敏感,我们必须采取适当的预防措施,确保存在大量的辐射和传导干扰能量的情况下能正常工作。

本应用手册将概述有关基本规范,提供符合标准的安全设计指南,并给出成功的PSoC CapSense设计的检测结果。

规范美国FCC关于无意辐射体的第15部分的B子部分规定了计算设备的标准。

欧洲和世界其他地区的标准基本依据CENELEC而有所调整。

这些都包含在CISPR发射标准(也称ENxxxx标准)和IEC抗扰度和安全问题标准(也称ENxxxx标准)中。

计算设备的一般发射规范为EN55022,该标准涵盖了传导发射和辐射发射。

在美国,医疗设备不受FCC管制,而受FDA法规管制,该法规包含了欧洲对医疗设备标准EN55011的要求。

这些设备中,电动机控制设备包含在EN55014标准中;照明设备包含在EN50015标准中。

上述规范对辐射发射和传导发射有着基本相似的性能要求。

辐射和传导抗干扰度(耐受性)性能要求由EN61000-4标准和EN55024标准的有关章节作了规定。

电气设备的EMC设计测试和整改

电气设备的EMC设计测试和整改一、EMC设计的重要性二、EMC设计的基本原则1.电路设计方面(1)合理选择元器件和材料,例如使用具有良好抗干扰性能的元器件和材料。

(2)合理布置元器件的位置和线路的走向,避免相互之间的电磁干扰。

(3)合理设计电路的接地,保证接地系统的连续性,同时减小接地回路的干扰。

2.线路布局方面(1)避免平行线路的交叉走向,减小电磁干扰。

(2)避免信号线与电源线同侧布局,以减小互相干扰的可能性。

3.外壳设计方面(1)合理选择外壳的设计材料和结构,提高其电磁屏蔽性能。

(2)合理设计外壳的接地,保证外壳的接地良好,减小外壳对电磁波的反射和散射。

三、EMC测试的目的和方法EMC测试主要是为了验证电气设备的EMC性能是否满足法规和标准的要求,以及检测设备之间是否存在电磁干扰的问题。

主要的测试项目包括:1.电气设备的辐射发射测试:通过测量电气设备在正常工作状态下发送的电磁波,判断其辐射发射是否满足法规和标准的要求。

2.电气设备的敏感度测试:通过模拟实际环境,测试电气设备在电磁干扰环境下的性能,判断其是否能够正常工作。

3.电气设备的抗扰度测试:通过模拟各种干扰源,测试电气设备在不同干扰环境下的性能,判断其是否能够抵御干扰。

EMC测试的方法主要包括:专业EMC测试仪器的使用、电磁暴露实验室的环境搭建、射频测量技术等。

通过测试数据的分析和判断,可以评估电气设备的EMC性能,从而进一步提升设备的抗干扰能力。

四、EMC整改的方法和措施如果在测试中发现电气设备的EMC性能不符合要求,需要进行整改。

EMC整改的方法和措施主要包括:1.重新设计电路:优化电路的布局,选择具有良好抗干扰性能的元器件,改进接地系统等,从根源上减小电磁干扰。

2.优化线路布局:调整线路的走向和布局,避免平行线路的交叉,减小电磁干扰的可能性。

3.增强外壳的屏蔽性能:优化外壳的设计材料和结构,增强外壳的屏蔽性能,减小对外界电磁波的反射和散射。

EMC电磁兼容设计与案例分析

输入输出耦合

输入输出耦合

➢ 内部空 间电磁环 境复杂, 给设备稳 定运行带 来隐患;

➢ RE102预测试:环境底噪声较大,测试值(比如工作频率谐 波)应淹没在底噪声之下;

➢ CE106预测试:测试谐波抑制。

电磁兼容设计与控制

EMC概述 EMC认证测试 整机EMC设计与案例 PCB板EMC设计与案例

如何保证产品EMC性能

电磁兼容设计与控制

整机EMC设计与案例

(一)CE101设计与案例 (二)CE102设计与案例 (三)RE102设计与案例

CE101测试案例

150Hz超标5dBuA 250Hz超标1dBuA

3A标准线

谐波怎么产生?

谐波问题怎么解决?

解决谐波问题需要改善输入电流的波形,使之尽量接近

正弦波。需要进行无源或有源功率因数校正。

电容滤波电路

整流后的滤波平滑电容 越大越好???

谐波问题怎么解决?

LC滤波电路:单硅钢片电感的滤波电路,需要的电感量很

➢ 由设备 因。

共模干扰电流

➢ 外界电磁场感应; ➢ 电缆两端设备所接的地电位不同; ➢ 设备上电缆与大地之间有电位差。

主电源板设计要求

主电源板采用“浮地”设计,即采用“双线进、双线出,正负 线与地隔离”的布线方法。

电源 + 输入 -

输入 滤波

DC/DC 或

AC/DC

输出 滤波

PGND 电源模块

+ 后级 - 电路

电磁兼容设计与控制

EMC概述 EMC认证测试 整机EMC设计与案例 PCB板EMC设计与案例

赛盛技术产品原理图EMC设计检查要点

产品原理图EMC 设计检查列表 保密文件

此版权归深圳市赛盛技术有限公司 侵权必究 共1页 第1页

产品原理图EMC 设计检查列表

产品名称 产品型号

产品原理图名称 产品类型 【 】盒式产品【 】机架产品的模块板 【 】系统单板

EMC 检视人

检查日期 产品负责人

备注

说明:此checklist 只是作为单板在原理图设计完成后进行EMC 设计评审时候使用,具体使用方法是根据企业内部规范通过检视来填写,目的是通过检视的项目以提示检视人关注产品原理图EMC 设计的关键要点。

评审要素

是否满足要求

结论说明

主芯片的滤波设计方案 是【】否【】免【】 单板级电源输入滤波方案 是【】否【】免【】 电源接口的滤波设计方案 是【】否【】免【】 电源滤波器件选型方案 是【】否【】免【】 面板指示灯电路设计方案 是【】否【】免【】 板间连接器针定义方案 是【】否【】免【】 电源接口的滤波设计方案 是【】否【】免【】 时钟芯片的滤波设计方案 是【】否【】免【】 时钟电路的滤波设计方案 是【】否【】免【】 晶体的电路设计方案 是【】否【】免【】 接口电路滤波设计方案

是【】否【】免【】 复位以及看门狗电路滤波处理方案 是【】否【】免【】 连接器选择方案 是【】否【】免【】 原 理 图E

M C 设 计 检 查 要 点 其他部分

是【】否【】免【】。

Cypress Psoc CSD触摸功能调试文档

应当使滑条中的传感器电容均衡。 根据传感器或 PCB 设计,某些传感器对可能需要更长的路由。 当选择 双工时,双工传感器索引表由 CSD 向导自动生成。 下表列出的是不同滑条部分计数的双工序列。

Table 1. 不同滑条部分计数的双工序列

滑条段总计数

段序列

10

0,1,2,3,4,0,3,1,4,2

CSD UM 具有两个支持辐射滑条的 API 功能。 第一个功能 CSD_wGetRadiaPos() 返回质心位置,第二个 CSD_wGetRadialInc() 通过分辨部件返回手指的移动情况。 当手指顺时针方向移动时,它是正偏量。

参考点 (0) 位于第一个传感器的中心。 线性滑条和辐射滑条的分辨率都受到限制,数值为 3000。

[+] Feedback

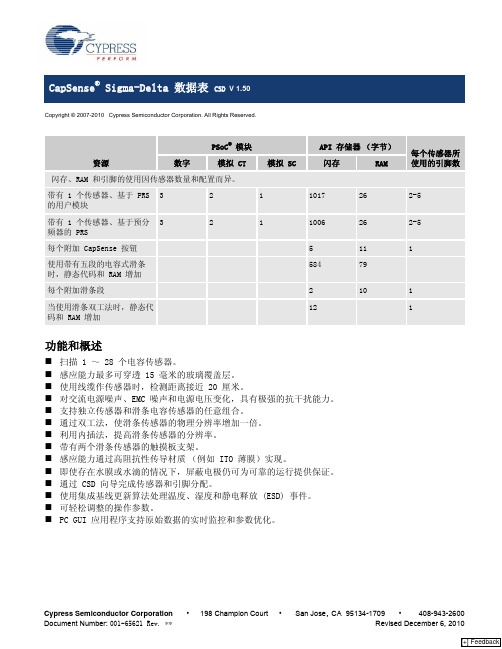

CapSense Sigma-Delta

CSD(使用 sigma delta 调制器的电容式感应技术)通过开关电容技术提供 CapSense® 功能,该技术通过 sigma-delta 调制器可以将感应开关电容电流转换为数字代码。

Figure 1. CSD 应用图

快速启动

1. 如果使用,选择并放置需要专用引脚 (例如 I2C 和 LCD)的用户模块。 根据需要分配端口和引脚。 2. 选择并放置 CSD 用户模块。 3. 在工作区浏览器中右键单击 CSD 用户模块,以访问 CSD 向导 (数据表中稍后将介绍该向导)。 4. 设置所需的传感器、滑条或旋转滑条的数量。 5. 设置每个传感器的传感器设置。 6. 设置引脚和全局参数。 阅读所有参数说明,遵守各种要求和相关指南。 7. 生成应用,并切换到应用编辑器。 8. 根据需要调整采样代码,以部署独立传感器、滑条传感器或触摸板。 9. 将 I2C-USB 桥连接至目标电路板,并观察信号。 10. 更改 CSD 参数以优化设置和重建应用。

电磁兼容性质量保证计划

电磁兼容性质量保证计划英文回答:Quality Assurance Plan for Electromagnetic Compatibility.Introduction.Electromagnetic compatibility (EMC) is the ability of a device or system to function satisfactorily in its intended electromagnetic environment without introducing intolerable electromagnetic disturbances to other devices or systems in that environment. EMC is a critical aspect of product design and development, as it ensures that devices and systems can operate reliably and safely in the presence of electromagnetic interference (EMI).Purpose.The purpose of this Quality Assurance Plan (QAP) is todefine the requirements for an EMC quality assurance program. This QAP establishes the procedures and processes that will be used to ensure that EMC requirements are met throughout the product lifecycle.Scope.This QAP applies to all products that are subject to EMC regulations. This includes products that are intended for use in commercial, industrial, and residential environments.Definitions.Electromagnetic compatibility (EMC) is the ability of a device or system to function satisfactorily in its intended electromagnetic environment without introducing intolerable electromagnetic disturbances to other devices or systems in that environment.Electromagnetic interference (EMI) is any electromagnetic disturbance that can cause unwanted effectsin a device or system.Quality assurance is the process of ensuring that products and services meet or exceed customer requirements.Requirements.The following requirements shall be met in order to ensure EMC compliance:Design and development.Products shall be designed and developed in accordance with applicable EMC standards.EMC considerations shall be integrated into all phases of product development, from concept design to final production.Testing.Products shall be tested to ensure that they meetapplicable EMC standards.Testing shall be performed in an accredited laboratory.Documentation.EMC test reports shall be generated and maintained.EMC compliance statements shall be included in product documentation.Training.Personnel involved in EMC activities shall be trained on EMC requirements and testing procedures.Auditing.EMC quality assurance activities shall be audited on a regular basis.Organization and Responsibilities.The following organization and responsibilities shall be established to implement this QAP:EMC Manager.The EMC Manager is responsible for the overall implementation and maintenance of the EMC quality assurance program.EMC Team.The EMC Team is responsible for conducting EMC testing and ensuring that products meet EMC requirements.Quality Assurance Department.The Quality Assurance Department is responsiblefor auditing EMC quality assurance activities.Procedures.The following procedures shall be followed to implement this QAP:Design and development review.EMC considerations shall be reviewed during all phases of product development.EMC testing.Products shall be tested to ensure that they meet applicable EMC standards.Documentation review.EMC test reports and compliance statements shall be reviewed and approved.Training.Personnel involved in EMC activities shall betrained on EMC requirements and testing procedures.Auditing.EMC quality assurance activities shall be audited on a regular basis.Continuous Improvement.The EMC quality assurance program shall be reviewed and updated on a regular basis to ensure that it remains effective. Feedback from customers, regulatory agencies,and other stakeholders shall be used to improve the program.中文回答:电磁兼容性质量保证计划。

电磁兼容性(EMC)设计需要考虑的问题

电磁兼容性(EMC)设计需要考虑的问题

Atmel Inc.

【期刊名称】《电子质量》

【年(卷),期】2002(000)005

【摘要】阐述了电磁兼容(EMC)设计的原则,指出了产品EMC现象的若干主要原因,提出了相应的方法和措施%The paper expounds the principle of EMC design, main cause of EMC phenomenaand proposes a few of solution for EMC

【总页数】7页(P131-137)

【作者】Atmel Inc.

【作者单位】无

【正文语种】中文

【中图分类】TN03

【相关文献】

1.系统内电磁兼容性(EMC)问题的建模及其优化设计 [J], 姜晓鸿;邱扬

2.水面舰船电磁兼容性数字化设计方法——舰船EMC辅助量化设计平台 [J], 刘相春;奚秀娟

3.电子镇流器电磁兼容性(EMC)技术方案探讨--SY/EMC203A厚膜集成电路(IC)简介 [J], 邓树兴

4.高频电路设计中电磁干扰(EMI)和电磁兼容性(EMC)研究 [J], 水恒春;赵小珍;刘

同旵

5.结构设计中的电磁兼容性(EMC)设计 [J], 陈玮敏

因版权原因,仅展示原文概要,查看原文内容请购买。

EMC设计规范

印制电路板的电磁兼容性设计规范序言自己结合自己在军队参加的电磁兼容设计工作实践,空军系统关于电子抗衡进行的两次培训(雷达系统防雷、电子信息防泄露)及入司后参加706所杨继深主讲的 EMC培训、 701所周开基主讲的 EMC培训、自己在地方电磁兼容实验室参加 EMC整改的工作体验、特别是国际 IEEE委员宣告的关于EMC有关文章、与地方同行的交流领悟,并结合公司的实验状况,对印制电路板的电磁兼容性设计进行了一下小结,希望对印制电路板的设计有所作用。

需要提示注意的是:总结中可是供应了一些最基础的结论,对详尽频率信号的走线长度计算、应试虑的谐波频率、波长、电路板级障蔽、障蔽体腔的设计、障蔽体孔径的大小、数目、进出导线的办理、截止导波管直径、长度的计算及静电防范,雷电防范等知识没有进行描述。

或许有些结论不用然正确,还需各位指正,自己将不胜感谢。

一、元器件布局印刷电路板进行EMC 设计时,第一要考虑布局,PCB 工程师必定和结构工程师、 EMC 工程师一起协调进行,做到两者兼顾,才能达到事半倍。

第一要考虑印刷电路板的结构尺寸大小,考虑如何对器件进行部署。

若是器件分布很散,器件之间的传输线可能会很长,印制线路长,阻抗增加,抗噪声能力下降,成本也会增加。

若是器件分布过于集中,则散热不好,且周边线条易受耦合、串扰。

因此依照电路的功能单元,对电路的所有元器件进行整体布局。

同时考虑到电磁兼容性、热分布、敏感器件和非敏感器件、I/O 接口、复位电路、时钟系统等因素。

一般来说,整体布局时应遵守以下基根源则:1、当线路板上同时存在高、中、低速电路时,应该按逻辑速度切割:部署迅速、中速和低速逻辑电路时,高速的器件(快逻辑、时钟振荡器等) 应部署在凑近连接器范围内,减少天线效应、低速逻辑和积蓄器 ,应部署在远离连接器范围内。

这样对共阻抗耦合、辐射和交扰的减小都是有利的。

高速电路中速电路(如低速电路接(如大规模数字控制电(如低频模口集成电路)路)拟电路)2、在单面板或双面板中,若是电源线走线很长,应每隔3000mil 对地加去耦合电容,电容取值为 10uF +1000pF ,滤除电源线上高频噪声。

EMC Part IX: EMC Design for PCB

EMC Part IX: EMC Design for PCBJohn;Wong【期刊名称】《变频器世界》【年(卷),期】2005(000)010【摘要】1. Introduction The EMC design for the Printed Circuit Board has been a popular topic. Guidelines and tips for high-speed PCB designs could be found from numerous resources. When investigating EMI issues associated with circuit boards, many details such as clock frequencies, switching rates, rise/fall times, signal harmonics, data transfer rates, impedances, trace loading, and types and values of the various circuit components, should be taken into considerations. The physical layout of the PC board and its associated metallic components are important considerations. Special attention should be given to the placement and characteristics of signal source components, vias,【总页数】4页(P132-135)【作者】John;Wong【作者单位】无【正文语种】中文【中图分类】TN41【相关文献】1.EMC为什么银行需要EMC:EMC在金融领域捷报频传 [J],2.PCB板中的EMC设计技术 [J], 赵哲懿3.关于电源和接地设计对EMC在PCB中的影响探讨 [J], 智秀杰4.开关电源PCB的近场EMC预测优化设计 [J], 汶涛;张超;诸文智;殷万君5.基于EMC技术的PCBA板级可靠性测试案例分析 [J], 江徽;马勇;解维坤;张凯红因版权原因,仅展示原文概要,查看原文内容请购买。

EMC项目建议书

EMC项目建议书EMC项目建议书1. 项目背景EMC(电磁兼容)是指无线电发射设备在使用中正常工作时,不产生对周围电子设备和系统的干扰,并且它应该具有抗电磁干扰的能力。

保证设备或系统在电磁环境下的正常运行,对于现代社会的发展和智能化的进步至关重要。

因此,为了提高电磁兼容性能,我们建议开展EMC项目。

2. 项目目标本项目的主要目标是通过针对电磁兼容性的研究与探索,提出一些在设计、制造和使用过程中可以被采纳的具体建议措施,从而提高设备和系统的电磁兼容性。

具体目标包括:- 分析并总结现有设备和系统在电磁兼容性方面存在的问题;- 研究国内外相关标准和技术规范,了解最新的电磁兼容性要求;- 提出一些针对电磁兼容性问题的解决方案,包括技术手段和设计原则;- 开展相关实验和测试,验证提出的解决方案的有效性;- 撰写并发布一份EMC项目建议书,供各行各业参考和借鉴。

3. 项目内容本项目的主要内容包括以下几个方面:3.1. 现有设备和系统问题的分析对现有设备和系统在电磁兼容性方面存在的问题进行分析,重点关注电磁辐射和电磁感应对设备和系统造成的干扰和损害。

3.2. 国内外标准和技术规范的研究调研国内外有关电磁兼容性的标准和技术规范,包括但不限于中国国家标准、国际电工委员会(IEC)标准等,以了解电磁兼容性要求的最新发展和应用情况。

3.3. 解决方案的提出基于现有设备和系统问题的分析以及对标准和技术规范的研究,提出一些具体的解决方案,包括技术手段和设计原则。

这些方案旨在提高设备和系统的电磁兼容性能,减少电磁干扰的产生和传播。

3.4. 实验和测试的开展为了验证提出的解决方案的有效性,开展相关实验和测试。

通过实验和测试,可以评估解决方案在不同情况下的适用性和可行性,从而为设备和系统的设计和制造提供科学依据。

3.5. EMC项目建议书的撰写与发布在完成以上各项内容后,撰写一份完整的EMC项目建议书。

该建议书将包括项目背景、目标、内容、方法和结果等部分,详细介绍整个项目的过程和重要成果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 [+] Feedback

AN2318 (ZH)

EN55022 包括“预扫描”检测和开放空间测试场所 (OATS) 检测。预扫描检测的目的是找到器件发射出最大能量的频 率。我们在检测室中进行预扫描检测。OATS 检测可对发 射进行更精确的测量。OATS 检测在较大空间里进行(10 米长或露天)。对大多数 PSoC® 应用(B 类—家用较低的 阈值)来说,30 MHz 到 230 MHz 之间的通过/未通过阈值 为 30 dBuV/m,230 MHz 到 1 GHz 之间为 37 uV/m。 下图给出了 EN55022 预扫描测试的结果。从该图中,我们 找到一组在更精确的 OATS 检测中研究的频率。

辐射和传导抗干扰度(耐受性)性能要求由 EN61000-4 标 准和 EN55024 标准的有关章节作了规定。ESD 测试包含 在 EN55024 标准中。

发射

辐射:辐射发射主要来自输入和输出的数字瞬态。应尽可能 限制数字输出的带宽。PSoC® 器件的 I/O 被全局总线结构 限制于 12.0MHz。这一定时频率限制为抵制辐射发射提供了 第一重保护。PSoC® 器件 CY8C21xxx、CY8C24xxxA、 CY8C27xxx、CY8C29xxx 和所有计划中的未来系列产品都 提供了启用较慢上升和下降时间的选择,能限制数字输出的 谐波能量。CY8C25xxx 和 CY8C26xxx 等较早系列的部件没 有此功能。电路板上的高速布线要尽可能的短。如果信号离 开电路板去驱动外部负载,那么芯片应具备串联端接的电阻 来提供必要的带宽。对高速线路而言,15 到 50 欧姆的电阻 通常就足够了。请注意,逻辑上的数字输出直接连接到(通 过输出 P 通道 FET 的 RDS(ON) )Vdd 上。这样,Vdd 总线实 际上直接连接到输出上,因而 Vdd 上出现的任何高频噪声都 会出现在输出上。我们应在 PSoC® 芯片上在 Vdd 和 VSS 之 间提供良好耦合的高频旁路电容。该电容旁路线迹应非常 短;尽可能地采用接地层和电源层。本应用笔记稍后部分给 出了 CapSense 的辐射发射设计实例。

引言

各电子器件都必须符合发射能量的特定要求,并对外部干扰 有一定的抗扰度。美国 FCC 及其他国家类似的监管机构制 定了有关标准,确保电子器件不会彼此干扰。因此,您的计 算机不会干扰您的电视,还有更糟糕的情况下医院的 X 光 机或通风设备不会破坏重要的医疗监视器的工作。

现代高速数字电子设备能生成极高速的信号,该信号可能发 出大量噪音。CMOS 模拟电路和数字电路本身具有无限的 输入阻抗。因此,其对外部的电场、磁场相当敏感,我们必 须采取适当的预防措施,确保存在大量的辐射和传导干扰能 量的情况下能正常工作。本应用笔记将概述有关基本规范, 提 供 符 合 标 准 的 安 全 设 计 指 南 , 并 给 出 成 功 的 PSoC® CapSense 设计的检测结果。

图 2. 通讯接口原理图

2005 年 8 月 29 日,我们在位于华盛顿州舒顿的西北 EMC 实验室检测该系统。CapSense 按钮根据 EN55022 标准 (Amds.A1:2001、A2:2003) Class B:1998 的要求进行 检测。

2008 年 12 月 17 日

文件编号 001-50403 版本 **

抗扰度

辐射:辐射电能会影响系统测量并可能会影响处理器内核的 工作。干扰通过引脚在印制电路板 (PCB) 级进入 PSoC® 芯 片。为避免辐射能干扰,我们应认真设计电路板的布局,做 好 PSoC® 项目的设计。有关方法如下:

1. 尽可能减小到达芯片的信号源源阻抗。

2. 尽量缩小化输入信号线迹的环路面积。

传导:传导发射是相对较低频的 RF 传导进入电源系统造成 的。PSoC® 电源引脚上的高频旁路电容和大型旁路电容可 满足巨大的瞬时负载要求并能有效消除 PSoC® 芯片的耦合 效果及电源系统的直接负载。开关电源瞬态不是 PSoC® 芯 片本身的问题,而是大量传导发射的问题。降低这一噪声的 标准设计做法是在输入电源连接上采用差模和共模电感器,

设计实例-辐射发射

用 CY8C21534-24PVXI 芯片来组装一个电路,执行 8 个按 钮的简单 CapSense 项目。在设计 PCB 时采用应用笔记 AN2292 中的总体布局指南。如欲了解以下功能原理,请参 见 AN2292。电路被组装在 0.062 英寸厚的 FR4 双面 PCB 上。CapSense 接地层仅位于电路板的最上面,部分地线填 充率为 60%。电路板的底部没有接地层。出于评估目的,测 试板上 4 个按钮的直径为 1.0 cm,其他四个直径为 1.2 cm。 按钮和接地之间的间距为 0.020 英寸。对 4 个一组两组不同 大小的按钮而言,各有 2 个按钮的垫片为实心导体,另 2 个

4. 天线馈电和 RS232 延伸线缆通过检测室中小型的电磁 隔离孔连通。

5. 执行测试的技术人员在频率为 80 MHz 至 1 GHz 之 间,采用 3V/m 的对数扫描对器件扫描。

6. 负责检测的技术人员进入检测室,将天线从水平极化变 为垂直极化,反之亦然。

7. 技术人员密闭检测室,在进行一次扫描。

静电放电 (ESD)

接触表面时,该表面上的电荷积累突然转移到另一表面,这 就会造成静电放电或 ESD。这时的放电电压通常会达到几 千伏特。易受 ESD 影响的系统根据各种不同因素,会对静 电放电做出不同反应。有关因素包括:在检测器件外壳上的 放电位置、放电的电压电平以及发生 ESD 事件的环境等。 本应用笔记稍后部分将给出 CapSense 的 ESD 实例。

通过 EN55024 辐射抗扰度测试的要求是,系统能在存在辐 射干扰条件下正常工作。就 CapSense 按钮而言,正常工 作是指测量出的灵敏度要大于给定应用较低灵敏度的要求。 按钮的灵敏度是指手指接触和没有接触按钮时的计数值 之差。

按钮灵敏度=(手指接触时的计数)-(手指不接触时的 计数)

以下两图显示了当在 80 MHz 至 1 GHz 之间扫描到 RF 源 时按钮的灵敏度。按钮 #5 显示了整组按钮的典型测试结 果。按钮 #6 显示了整组按钮的最差的测试结果。

图 3. EN55022 预扫描检测结果

PSoC® CapSense 8 按钮电路板大大超出了 EN55022 的要 求,比标准高 出 10 dB。OATS 检测结果见下图。负责进 行检测的技术人员指出:“这是我们做过的最无聊的 OATS 检测。”如此说来,最无聊的就是最好的结果。

图 4.“无聊的”OATS 检测结果

1. 待测器件位于在检测室中,一部天线发射 RF 干扰,另 一天线监视干扰频率。

2. RF 信号生成器和功率放大器位于检测室外,控制 PC 通过 GPIB 使其自动工作。RF 源生成抗扰度检测的 干扰。

3. 监视 PC 也位于检测室外,观察待测器件的工作。检测 室外的频率计数器连接到室内的监视天线上。计数器还 通过 RS232 延长线缆用 GPIB 连接到监视 PC 上。计 数器数据用于关联干扰频率和待检器件的反应。

重复第 5 步到第 7 步,直到下述八种位置连接和极化组合 所需频率都扫描到,编号 001-50403 版本 **

3 [+] Feedback

表 1. 辐射抗扰度检测组合

极 水平 水平 水平 水平 垂直 垂直 垂直 垂直

位置 前 右 后 左 前 右 后 左

设计实例—辐射抗扰度

上节中的辐射发射测试的 8 按钮电路和 EMC 测试实验室再 次用来进行了辐射抗扰度检测。

根据 EN55024 的要求检测 CapSense 按钮。EN55024 辐 射抗扰度检测的目的是找到器件在检测时受辐射干扰最严重 的频率。我们在电磁封闭的无回声检测室中进行辐射抗扰度 检测。检测程序如下:

规范

美国 FCC 关于无意辐射体的第 15 部分的 B 子部分规定了 计算设备的标准。欧洲和世界其他地区的标准基本依据 CENELEC 而有所调整。这些都包含在 CISPR 发射标准 (也称 ENxxxx 标准)和 IEC 抗扰度和安全问题标准(也 称 ENxxxx 标准)中。

计算设备的一般发射规范为 EN55022,该标准涵盖了传导 发射和辐射发射。在美国,医疗设备不受 FCC 管制,而受 FDA 法 规 管 制 , 该 法 规 包 含 了 欧 洲 对 医 疗 设 备 标 准 EN55011 的要求。这些设备中,电动机控制设备包含在 EN55014 标准中;照明设备包含在 EN50015 标准中。上 述规范对辐射发射和传导发射有着基本相似的性能要求。

图 5. EN55024 抗扰度检测图

AN2318 (ZH)

图显示出,在 80 MHz 到 1 GHz 的测试频谱内,按钮灵敏 度至少比设计要求高出 10 个计数值。根据上述测试结果, PSoC® CapSense 8 按钮电路板顺利通过了 EN55024 辐射 抗扰度测试。

设计实例-ESD

我 们 在 ESD 设 计 实 例 中 采 用 目 前 包 括 一 组 PSoC® CapSense 按 钮 的 消 费 产 品 。 本 例 中 的 PSoC® 是 CY8C21434-24LFXI。我们在设计本产品的 PCB 时采用应 用笔记 AN2292 的一般布局方法。如欲了解下述功能原 理,请参见 AN2992。电路组装在加固的聚酰亚胺有弹性的 四层 PCB 板上。包括顶层和底屏蔽层在内的电路板的总厚 度为 0.014 英寸。顶层有一组 3 x 3 个按钮阵列,大小约为 1.5 英寸 x 1 英寸。接地层位于 PCB 的底部,部分地线填充 率为 40%。铜线迹环绕 PCB 四周,形成接地环,提高了 CapSense 电路的性能。按钮阵列嵌入产品内部。外壳为丙 烯酸树脂材料,作为按扭上 1.0 mm 厚的覆盖层。

AN2318 (ZH)

为交叉梳状。该 PCB 的照片见下。赛普拉斯设计的电路板用 于内部测试目的,不对外提供。

图 1.内部测试用 CapSense PCB