verilog数字钟代码

数字闹钟的FPGA实现(Verilog)

闹钟的FPGA实现一.设计目的及总述:本次实验选择用FPGA实现一个闹钟。

它的功能有:1.时钟2.可以用按键快慢调整时钟时间3.可以设定闹钟并在时间到达设定闹钟时间时响起卡农音乐一分钟4.整点报时,响一声来报时系统一共有五个按键,分别命名为switch_mode,switch_enter,switch_pick,switch_down,switch_up。

时钟,调时,设定闹钟通过LCD1602进行显示,整点报时声和闹钟声通过蜂鸣器发出。

其中:本次实验的闹钟用Verilog语言进行设计,由于实验在Xilinx开发板上LCD1602显示模块几经调试显示都有问题,而实验的截止日期又极其接近了故最后选择在我购买的Altera 开发板上进行实现。

由于Altera公司FPGA使用Quartus II软件进行编译下载,所以把原来在ISE软件上以schematic方式实现的顶层原理图对应自动生成的verilog代码更改后添加进Quartus工程中使用。

所需要的修改仅为将顶层原理图中的OR2例化语句改为or(输出,输入1,输入2),并把系统时钟设为50MHZ,其他各模块代码不需进行更改。

二.仿真过程在几经更改之下,更由于在两种系统下的调试,使得仿真变得难以进行,此次试验针对各模块(不包括分频模块:fre_divider)的仿真结果难以找到了而且ISE9.1i十分难用,经常报各种错,因此在这里只选择其中比较重要的控制模块(controller)和时钟模块(timer),调时(快慢)模块(time_adjust)的仿真结果以说明本实验的仿真过程。

Controller:Timer:Time_adjust:三.系统总图即各模块Verilog代码和说明(参考对代码的详细注释):1.各模块之间连线图和对应的Verilog代码:Clock.v:module clock(clk_50m, //在本次实验所用的Altera开发版上,系统时钟为50MHZ rst, //复位键switch_down, //向下调整,设定switch_enter, //确认完成调整,设定switch_mode, //选择系统出于何种模式:时钟,调时,设定闹钟switch_pick, //选择调整,设定的对象:时,分,秒// switch_up, //向上调整,设定beep, //蜂鸣器lcd_d, //lcd1602 d7-d0管脚lcd_e, //lcd1602 en管脚lcd_rs, //lcd1602 rs管脚lcd_rw); //lcd1602 rw管脚input clk_50m;input rst;input switch_down;input switch_enter;input switch_mode;input switch_pick;//input switch_up;output beep;output [7:0] lcd_d;output lcd_e;output lcd_rs;output lcd_rw;//以下声明的线型量用于连接系统各模块 wire [7:0] XLXN_4;wire [7:0] XLXN_5;wire [7:0] XLXN_6;wire [7:0] XLXN_7;wire [7:0] XLXN_8;wire [7:0] XLXN_9;wire [7:0] XLXN_10;wire [7:0] XLXN_11;wire [2:0] XLXN_14;wire XLXN_15;wire XLXN_16;wire XLXN_17;wire XLXN_19;wire [5:0] XLXN_20;wire [5:0] XLXN_21;wire [5:0] XLXN_22;wire XLXN_24;wire [5:0] XLXN_33;wire [5:0] XLXN_34;wire XLXN_36;wire [5:0] XLXN_37;wire [5:0] XLXN_39;wire [5:0] XLXN_40;wire XLXN_50;wire XLXN_51;reg clk_25m;wire switch_up;assign switch_up=1;//由于系统本身是设计在实验室的板子上(25MHZ)上,所以现在把50MHZ系统时钟//二分频得到25MHZ时钟,这样就不用更改各子模块always@(posedge clk_50m)beginif(!rst)clk_25m<=0;elseclk_25m<=~clk_25m;end//控制模块,控制系统出于三种状态之一:时钟,调时,设定闹钟。

用Verilog语言编写的多功能数字钟

这次的闹钟电路设计和多功能数字钟有一些相似的地方,不同在于整体构思和细

节上要求的差异。

构思根据要求采用的是状态机设计方法。从一个状态进入另一个状态最适合这个

设计了。细节上和数字钟也有很大的差异。中间的控制逻辑有时候需要反馈。前

后都是有联系的,并不是独立存在的。

本次设计基本上完成的所以的要求,但是由于时间紧急,一些细节并不是很完美,

分频器的作用是对 50Mhz 的系统时钟信号进行分频,得到频率为 1hz 的信号,

作为时钟的输入信号。

2

2.控制器和计数器 控制器的作用是,调整小时和分钟的值,并能实现清零功能。计数器的

作用是实现分钟和秒钟满 60 进 1,小时则由 23 跳到 00。当到达 59 分 55 秒的时 候,LED 灯会闪烁来进行报时。

end 2:

begin state<=2; s=1;

end 3:

begin s=0; if(k1==0) //时调整

7

begin

if(nz_h_l==3)

begin

nz_h_l=0;

if(nz_h_h==2)nz_h_h=0;

else nz_h_h=nz_h_h+1;

end

else nz_h_l=nz_h_l+1;

end

else if(k3==0) finish=1;

//设置完成

else if(k4==0) spker_en=1; //停止声响

end

8

4: begin s=0; if(k4==0) begin on_off<=!on_off;state=0;end end

endcase end end endmodule 3.显示器 显示器的作用是将时:分的值在数码管上依次显示出来。从分频器输出的 1Khz 的信号作为数码管的扫描信号。SEL 表示 6 个数码管选择位,它的取值表示八个 数码管,从左至右依次是 111~000。seg 表示七段数码管,它的取值决定特定位 数上显示的数字。

Verilog 电子时钟 (分、秒)

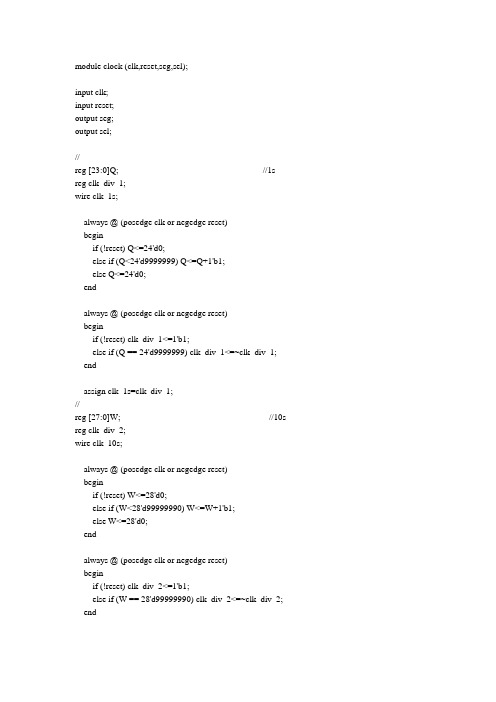

module clock (clk,reset,seg,sel);input clk;input reset;output seg;output sel;//-----------------------------------------reg [23:0]Q; //1s reg clk_div_1;wire clk_1s;always @ (posedge clk or negedge reset)beginif (!reset) Q<=24'd0;else if (Q<24'd9999999) Q<=Q+1'b1;else Q<=24'd0;endalways @ (posedge clk or negedge reset)beginif (!reset) clk_div_1<=1'b1;else if (Q == 24'd9999999) clk_div_1<=~clk_div_1; endassign clk_1s=clk_div_1;//----------------------------------------------reg [27:0]W; //10s reg clk_div_2;wire clk_10s;always @ (posedge clk or negedge reset)beginif (!reset) W<=28'd0;else if (W<28'd9*******) W<=W+1'b1;else W<=28'd0;endalways @ (posedge clk or negedge reset)beginif (!reset) clk_div_2<=1'b1;else if (W == 28'd9*******) clk_div_2<=~clk_div_2; endassign clk_10s=clk_div_2;//-----------------------------------------------------reg [29:0]E; //60sreg clk_div_3;wire clk_60s;always @ (posedge clk or negedge reset)beginif (!reset) E<=30'd0;else if (E<30'd599999940) E<=E+1'b1;else E<=30'd0;endalways @ (posedge clk or negedge reset)beginif (!reset) clk_div_3<=1'b1;else if (E == 30'd599999940) clk_div_3<=~clk_div_3;endassign clk_60s=clk_div_3;//------------------------------------------------------reg [33:0]R; //600s reg clk_div_4;wire clk_600s;always @ (posedge clk or negedge reset)beginif (!reset) R<=34'd0;else if (R<34'd5999999400) R<=R+1'b1;else R<=34'd0;endalways @ (posedge clk or negedge reset)beginif (!reset) clk_div_4<=1'b1;else if (R == 24'd5999999400) clk_div_4<=~clk_div_4;endassign clk_600s=clk_div_4;//--------------------------------------------------------------reg [16:0]A;reg clk_div_r;wire clk_div;always @ (posedge clk or negedge reset)//freq_division 30*4=120beginif (!reset) A<=17'd0;else if (A<17'd83334) A<=A+1'b1;//20000000/2/120=83334 [0-83334]else A<=17'd0;endalways @ (posedge clk or negedge reset)beginif (!reset) clk_div_r<=1'b1;else if (A == 17'd83334) clk_div_r<=~clk_div_r;endassign clk_div=clk_div_r;//------------------------------------------------------------reg [2:0]T;always @ (posedge clk_div or negedge reset)//six circlebeginif (!reset) T<=3'd0;else if (T<3'd3) T<=T+1'b1;//[0-3]else T<=3'd0;end//-------------------------------------------------reg [3:0]sel; //scan seg,selreg [7:0]seg;always @ (T)beginif (T<=3'b000) sel<=4'b1110;else if (T<=3'b001) sel<=4'b1101;else if (T<=3'b010) sel<=4'b1011;else if (T<=3'b011) sel<=4'b0111;else sel<=4'b1110;endalways @ (T)beginif (T<=3'b000) seg<=Y1;else if (T<=3'b001) seg<=Y2;else if (T<=3'b010) seg<=Y3;else if (T<=3'b011) seg<=Y4;else seg<= Y1;end//-----------------------------------------------parameter seg0 = 8'b11000000, //seg 0-9seg1 = 8'b11001111,seg2 = 8'b10100100,seg3 = 8'b10110000,seg4 = 8'b10011001,seg5 = 8'b10010010,seg6 = 8'b10000010,seg7 = 8'b11111000,seg8 = 8'b10000000,seg9 = 8'b10011000;//----------------------------------------------reg [3:0]Q1;reg [7:0]Y1;always @ (posedge clk_1s or negedge reset)//Asy_rst beginif (!reset) Q1<=4'd0;else if (Q1<4'd9) Q1<=Q1+1'b1;//[0-9]else Q1<=4'd0;endalways @ (Q1)//circlebeginif (Q1<=4'd0) Y1<=seg0;else if (Q1<=4'd1) Y1<=seg1;else if (Q1<=4'd2) Y1<=seg2;else if (Q1<=4'd3) Y1<=seg3;else if (Q1<=4'd4) Y1<=seg4;else if (Q1<=4'd5) Y1<=seg5;else if (Q1<=4'd6) Y1<=seg6;else if (Q1<=4'd7) Y1<=seg7;else if (Q1<=4'd8) Y1<=seg8;else if (Q1<=4'd9) Y1<=seg9;else Y1<=seg0;end//--------------------------------------------------reg [2:0]Q2;reg [7:0]Y2;always @ (posedge clk_10s or negedge reset)//Asy_rst beginif (!reset) Q2<=3'd0;else if (Q2<3'd5)Q2<=Q2+1'b1; //[0-5]else Q2<=3'd0;endalways @ (Q2)//circlebeginif (Q2<=3'd0) Y2<=seg0;else if (Q2<=3'd1) Y2<=seg1;else if (Q2<=3'd2) Y2<=seg2;else if (Q2<=3'd3) Y2<=seg3;else if (Q2<=3'd4) Y2<=seg4;else if (Q2<=3'd5) Y2<=seg5;else Y2<=seg0;end//---------------------------------------------------reg [3:0]Q3;reg [7:0]Y3;always @ (posedge clk_60s or negedge reset)//Asy_rst beginif (!reset) Q3<=4'd0;else if (Q3<4'd9) Q3<=Q3+1'b1;//0-9else Q3<=4'd0;endalways @ (Q3)//circlebeginif (Q3<=4'd0) Y3<=seg0;else if (Q3<=4'd1) Y3<=seg1;else if (Q3<=4'd2) Y3<=seg2;else if (Q3<=4'd3) Y3<=seg3;else if (Q3<=4'd4) Y3<=seg4;else if (Q3<=4'd5) Y3<=seg5;else if (Q3<=4'd6) Y3<=seg6;else if (Q3<=4'd7) Y3<=seg7;else if (Q3<=4'd8) Y3<=seg8;else if (Q3<=4'd9) Y3<=seg9;else Y3<=seg0;end//----------------------------------------------reg [2:0]Q4;reg [7:0]Y4;always @ (posedge clk_600s or negedge reset)//Asy_rst beginif (!reset) Q4<=3'd0;else if (Q4<3'd5) Q4<=Q4+1'b1;//[0-5]else Q4<=3'd0;endalways @ (Q4)//circlebeginif (Q4<=3'd0) Y4<=seg0;else if (Q4<=3'd1) Y4<=seg1;else if (Q4<=3'd2) Y4<=seg2;else if (Q4<=3'd3) Y4<=seg3;else if (Q4<=3'd4) Y4<=seg4;else if (Q4<=3'd5) Y4<=seg5;else Y4<=seg0;end//--------------------------------------------------endmodule。

数字时钟的Verilog代码

数字时钟的Verilog代码一、功能说明:1.可准确计时2.可按键复位3.可模式切换是正常计数还是调整秒位,或调整分位或小时位,再按置数键可调整4.切换为调整模式时,相应的被调整位会2Hz的闪烁注:我的FPGA开发板时钟为33.8688Mhz我的主体代码里的信号都是1有效,但开发板按键按下去时是置0,所以我在主体代码的前面都使用了反相器。

代码均调试成功,没有任何问题,同学们可以放心复制粘贴。

二、模块说明1.主体代码2.按键消抖模块3.分频器模块我的主题代码中嵌入了按键消抖模块,按键消抖中又嵌入了分频器。

请阅读此文档的同学不要漏加,否则不能正常工作三、代码(1)主体代码module clock(seg7,scan,clk,clr1,mode2,inc2);output[7:0] seg7;output[5:0] scan;input clk; //时钟输入20MHzinput clr1; //清零端input mode2; //控制信号,用于选择模式input inc2; //置数信号//按键全部反逻辑wire clr,mode,inc;assign clr=~clr1;wire mode1,inc1;assign mode=~mode1;assign inc=~inc1;reg[7:0] seg7; //8段显示控制信号(abcdefg.dp)reg[5:0] scan; //数码管地址选择信号reg[1:0] state; //定义4种状态reg[3:0] qhh,qhl,qmh,qml,qsh,qsl; //小时、分、秒的高位和低位reg[3:0] data;reg[2:0] cnt; //扫描数码管的计数器reg clk1khz,clk1hz,clk2hz; //1kHz、1Hz、2Hz的分频信号reg[2:0] blink; //闪烁信号reg inc_reg;//按键置数寄存器reg[7:0] sec,min;//定义按键置数时的时分秒寄存器reg[7:0] hour;parameter state0=2'b00,state1=2'b01,state2=2'b10,state3=2'b11;//状态0-3定义reg[14:0] n1;reg[24:0] n2;reg[23:0] n3;//----------------------按键消抖-----------------------------IP_ButtonDebounce m1(.clk(clk),.rst(clr),.BTN0(mode2),.BTN_DEB(mode1));IP_ButtonDebounce m2(.clk(clk),.rst(clr),.BTN0(inc2),.BTN_DEB(inc1));assign mode=~mode1;assign inc=~inc1;//-----------------------------800Hz分频,用于扫描数码管地址--------always@(posedge clk or posedge clr)beginif(clr) beginclk1khz<=0;n1<=0;endelse if(n1==42336/2-1) beginclk1khz<=~clk1khz;n1<=0;endelse n1<=n1+1;end//---------------------- 1Hz分频,用于计时-----------------------------always@(posedge clk or posedge clr)beginif(clr) beginclk1hz<=0;n2<=0;endelse if(n2==33868800/2-1) beginclk1hz<=~clk1hz;n2<=0;endelse n2<=n2+1;end//---------------------- 2Hz分频,用于闪烁----------------------------- always@(posedge clk or posedge clr)beginif(clr) beginclk2hz<=0;n3<=0;endelse if(n3==16934400/2-1) beginclk2hz<=~clk2hz;n3<=0;endelse n3<=n3+1;end//-------------------------模式转换-------------------------always @(posedge mode or posedge clr)beginif(clr) beginstate<=2'b00;endelse beginif(state==2'b11) beginstate<=2'b00;endelse beginstate<=state+1;endendend//-------------------------状态控制-----------------------------always @(posedge clk1hz or posedge clr)beginif(clr) beginhour<=7'b0000000;min<=7'b0000000;sec<=7'b0000000;inc_reg<=0;endelse begincase(state)state0:begin //模式0,正常计时if(sec==8'd59)beginsec<=8'd0;if(min==8'd59) beginmin<=8'd0;if(hour==8'd23) beginhour<=8'd0;endelse beginhour<=hour+1;endendelse beginmin<=min+1;endendelse beginsec<=sec+1;endendstate1:begin //模式1,设定小时时间if(inc)b egin//如果置数键按下if(!inc_reg) begin //如果置数寄存器值为0inc_reg<=1;//置数寄存器值置1if(hour==8'd23) beginhour<=8'd0;endelse beginhour<=hour+1;endendendelse begin//如果置数键未按下inc_reg<=0; //置数寄存器还是为0endendstate2:begin //模式2,设定分钟时间if(inc) beginif(!inc_reg) begininc_reg<=1;if(min==8'd59) beginmin<=8'd0;endelse beginmin<=min+1;endendendelse begininc_reg<=0;endendstate3:begin //模式3,设定秒钟时间if(inc) beginif(!inc_reg) begininc_reg<=1;if(sec==8'd59) beginsec<=8'd0;endelse beginsec<=sec+1;endendendelse begininc_reg<=0;endendendcaseendend//--------------------------------当进行时间设定时,令数码管闪烁----------------------- always @(state,clk2hz,clr) beginif(clr) beginblink[2:0]<=3'b111;endelse begincase(state)state0:blink[2:0]<=3'b111;//正常计数时,闪烁信号全为1state1:blink[2]<=clk2hz;state2:blink[1]<=clk2hz;state3:blink[0]<=clk2hz;default:blink[2:0]<=3'b111;//默认为1endcaseendend//--------------------------秒计数的十进制转BCD码---------------------------always @(sec,clr) beginif(clr) beginqsh[3:0]<=4'b0000;qsl[3:0]<=4'b0000;endelse begincase(sec[7:0])8'd0:begin qsh[3:0]<='b0000;qsl[3:0]<='b0000; end 8'd1:begin qsh[3:0]<='b0000;qsl[3:0]<='b0001; end 8'd2:begin qsh[3:0]<='b0000;qsl[3:0]<='b0010; end 8'd3:begin qsh[3:0]<='b0000;qsl[3:0]<='b0011; end 8'd4:begin qsh[3:0]<='b0000;qsl[3:0]<='b0100; end 8'd5:begin qsh[3:0]<='b0000;qsl[3:0]<='b0101; end 8'd6:begin qsh[3:0]<='b0000;qsl[3:0]<='b0110; end 8'd7:begin qsh[3:0]<='b0000;qsl[3:0]<='b0111; end 8'd8:begin qsh[3:0]<='b0000;qsl[3:0]<='b1000; end 8'd9:begin qsh[3:0]<='b0000;qsl[3:0]<='b1001; end 8'd10:begin qsh[3:0]<='b0001;qsl[3:0]<='b0000; end 8'd11:begin qsh[3:0]<='b0001;qsl[3:0]<='b0001; end 8'd12:begin qsh[3:0]<='b0001;qsl[3:0]<='b0010; end 8'd13:begin qsh[3:0]<='b0001;qsl[3:0]<='b0011; end 8'd14:begin qsh[3:0]<='b0001;qsl[3:0]<='b0100; end 8'd15:begin qsh[3:0]<='b0001;qsl[3:0]<='b0101; end 8'd16:begin qsh[3:0]<='b0001;qsl[3:0]<='b0110; end 8'd17:begin qsh[3:0]<='b0001;qsl[3:0]<='b0111; end 8'd18:begin qsh[3:0]<='b0001;qsl[3:0]<='b1000; end 8'd19:begin qsh[3:0]<='b0001;qsl[3:0]<='b1001; end 8'd20:begin qsh[3:0]<='b0010;qsl[3:0]<='b0000; end 8'd21:begin qsh[3:0]<='b0010;qsl[3:0]<='b0001; end 8'd22:begin qsh[3:0]<='b0010;qsl[3:0]<='b0010; end 8'd23:begin qsh[3:0]<='b0010;qsl[3:0]<='b0011; end 8'd24:begin qsh[3:0]<='b0010;qsl[3:0]<='b0100; end 8'd25:begin qsh[3:0]<='b0010;qsl[3:0]<='b0101; end 8'd26:begin qsh[3:0]<='b0010;qsl[3:0]<='b0110; end 8'd27:begin qsh[3:0]<='b0010;qsl[3:0]<='b0111; end 8'd28:begin qsh[3:0]<='b0010;qsl[3:0]<='b1000; end 8'd29:begin qsh[3:0]<='b0010;qsl[3:0]<='b1001; end 8'd30:begin qsh[3:0]<='b0011;qsl[3:0]<='b0000; end 8'd31:begin qsh[3:0]<='b0011;qsl[3:0]<='b0001; end 8'd32:begin qsh[3:0]<='b0011;qsl[3:0]<='b0010; end 8'd33:begin qsh[3:0]<='b0011;qsl[3:0]<='b0011; end 8'd34:begin qsh[3:0]<='b0011;qsl[3:0]<='b0100; end 8'd35:begin qsh[3:0]<='b0011;qsl[3:0]<='b0101; end 8'd36:begin qsh[3:0]<='b0011;qsl[3:0]<='b0110; end 8'd37:begin qsh[3:0]<='b0011;qsl[3:0]<='b0111; end 8'd38:begin qsh[3:0]<='b0011;qsl[3:0]<='b1000; end 8'd39:begin qsh[3:0]<='b0011;qsl[3:0]<='b1001; end 8'd40:begin qsh[3:0]<='b0100;qsl[3:0]<='b0000; end 8'd41:begin qsh[3:0]<='b0100;qsl[3:0]<='b0001; end 8'd42:begin qsh[3:0]<='b0100;qsl[3:0]<='b0010; end8'd44:begin qsh[3:0]<='b0100;qsl[3:0]<='b0100; end8'd45:begin qsh[3:0]<='b0100;qsl[3:0]<='b0101; end8'd46:begin qsh[3:0]<='b0100;qsl[3:0]<='b0110; end8'd47:begin qsh[3:0]<='b0100;qsl[3:0]<='b0111; end8'd48:begin qsh[3:0]<='b0100;qsl[3:0]<='b1000; end8'd49:begin qsh[3:0]<='b0100;qsl[3:0]<='b1001; end8'd50:begin qsh[3:0]<='b0101;qsl[3:0]<='b0000; end8'd51:begin qsh[3:0]<='b0101;qsl[3:0]<='b0001; end8'd52:begin qsh[3:0]<='b0101;qsl[3:0]<='b0010; end8'd53:begin qsh[3:0]<='b0101;qsl[3:0]<='b0011; end8'd54:begin qsh[3:0]<='b0101;qsl[3:0]<='b0100; end8'd55:begin qsh[3:0]<='b0101;qsl[3:0]<='b0101; end8'd56:begin qsh[3:0]<='b0101;qsl[3:0]<='b0110; end8'd57:begin qsh[3:0]<='b0101;qsl[3:0]<='b0111; end8'd58:begin qsh[3:0]<='b0101;qsl[3:0]<='b1000; end8'd59:begin qsh[3:0]<='b0101;qsl[3:0]<='b1001; enddefault: begin qsh[3:0]<=4'b0000;qsl[3:0]<='b0; endendcaseendend//---------------------------分计数的十进制转BCD码-------------------- always @(min,clr)beginif(clr) beginqmh[3:0]<='b0000;qml[3:0]<='b0000;endelse begincase(min[7:0])8'd0:begin qmh[3:0]<='b0000;qml[3:0]<='b0000; end8'd1:begin qmh[3:0]<='b0000;qml[3:0]<='b0001; end8'd2:begin qmh[3:0]<='b0000;qml[3:0]<='b0010; end8'd3:begin qmh[3:0]<='b0000;qml[3:0]<='b0011; end8'd4:begin qmh[3:0]<='b0000;qml[3:0]<='b0100; end8'd5:begin qmh[3:0]<='b0000;qml[3:0]<='b0101; end8'd6:begin qmh[3:0]<='b0000;qml[3:0]<='b0110; end8'd7:begin qmh[3:0]<='b0000;qml[3:0]<='b0111; end8'd8:begin qmh[3:0]<='b0000;qml[3:0]<='b1000; end8'd9:begin qmh[3:0]<='b0000;qml[3:0]<='b1001; end8'd10:begin qmh[3:0]<='b0001;qml[3:0]<='b0000; end8'd11:begin qmh[3:0]<='b0001;qml[3:0]<='b0001; end8'd12:begin qmh[3:0]<='b0001;qml[3:0]<='b0010; end8'd13:begin qmh[3:0]<='b0001;qml[3:0]<='b0011; end8'd15:begin qmh[3:0]<='b0001;qml[3:0]<='b0101; end 8'd16:begin qmh[3:0]<='b0001;qml[3:0]<='b0110; end 8'd17:begin qmh[3:0]<='b0001;qml[3:0]<='b0111; end 8'd18:begin qmh[3:0]<='b0001;qml[3:0]<='b1000; end 8'd19:begin qmh[3:0]<='b0001;qml[3:0]<='b1001; end 8'd20:begin qmh[3:0]<='b0010;qml[3:0]<='b0000; end 8'd21:begin qmh[3:0]<='b0010;qml[3:0]<='b0001; end 8'd22:begin qmh[3:0]<='b0010;qml[3:0]<='b0010; end 8'd23:begin qmh[3:0]<='b0010;qml[3:0]<='b0011; end 8'd24:begin qmh[3:0]<='b0010;qml[3:0]<='b0100; end 8'd25:begin qmh[3:0]<='b0010;qml[3:0]<='b0101; end 8'd26:begin qmh[3:0]<='b0010;qml[3:0]<='b0110; end 8'd27:begin qmh[3:0]<='b0010;qml[3:0]<='b0111; end 8'd28:begin qmh[3:0]<='b0010;qml[3:0]<='b1000; end 8'd29:begin qmh[3:0]<='b0010;qml[3:0]<='b1001; end 8'd30:begin qmh[3:0]<='b0011;qml[3:0]<='b0000; end 8'd31:begin qmh[3:0]<='b0011;qml[3:0]<='b0001; end 8'd32:begin qmh[3:0]<='b0011;qml[3:0]<='b0010; end 8'd33:begin qmh[3:0]<='b0011;qml[3:0]<='b0011; end 8'd34:begin qmh[3:0]<='b0011;qml[3:0]<='b0100; end 8'd35:begin qmh[3:0]<='b0011;qml[3:0]<='b0101; end 8'd36:begin qmh[3:0]<='b0011;qml[3:0]<='b0110; end 8'd37:begin qmh[3:0]<='b0011;qml[3:0]<='b0111; end 8'd38:begin qmh[3:0]<='b0011;qml[3:0]<='b1000; end 8'd39:begin qmh[3:0]<='b0011;qml[3:0]<='b1001; end 8'd40:begin qmh[3:0]<='b0100;qml[3:0]<='b0000; end 8'd41:begin qmh[3:0]<='b0100;qml[3:0]<='b0001; end 8'd42:begin qmh[3:0]<='b0100;qml[3:0]<='b0010; end 8'd43:begin qmh[3:0]<='b0100;qml[3:0]<='b0011; end 8'd44:begin qmh[3:0]<='b0100;qml[3:0]<='b0100; end 8'd45:begin qmh[3:0]<='b0100;qml[3:0]<='b0101; end 8'd46:begin qmh[3:0]<='b0100;qml[3:0]<='b0110; end 8'd47:begin qmh[3:0]<='b0100;qml[3:0]<='b0111; end 8'd48:begin qmh[3:0]<='b0100;qml[3:0]<='b1000; end 8'd49:begin qmh[3:0]<='b0100;qml[3:0]<='b1001; end 8'd50:begin qmh[3:0]<='b0101;qml[3:0]<='b0000; end 8'd51:begin qmh[3:0]<='b0101;qml[3:0]<='b0001; end 8'd52:begin qmh[3:0]<='b0101;qml[3:0]<='b0010; end 8'd53:begin qmh[3:0]<='b0101;qml[3:0]<='b0011; end 8'd54:begin qmh[3:0]<='b0101;qml[3:0]<='b0100; end 8'd55:begin qmh[3:0]<='b0101;qml[3:0]<='b0101; end 8'd56:begin qmh[3:0]<='b0101;qml[3:0]<='b0110; end 8'd57:begin qmh[3:0]<='b0101;qml[3:0]<='b0111; end8'd59:begin qmh[3:0]<='b0101;qml[3:0]<='b1001; enddefault:begin qmh[3:0]<='b0;qml[3:0]<='b0; endendcaseendend//----------------------------小时计数的十进制转BCD码------------------------ always @(hour,clr)beginif(clr) beginqhh[3:0]<='b0000;qhl[3:0]<='b0000;endelse begincase(hour)8'd0:begin qhh[3:0]<='b0000;qhl[3:0]<='b0000; end8'd1:begin qhh[3:0]<='b0000;qhl[3:0]<='b0001; end8'd2:begin qhh[3:0]<='b0000;qhl[3:0]<='b0010; end8'd3:begin qhh[3:0]<='b0000;qhl[3:0]<='b0011; end8'd4:begin qhh[3:0]<='b0000;qhl[3:0]<='b0100; end8'd5:begin qhh[3:0]<='b0000;qhl[3:0]<='b0101; end8'd6:begin qhh[3:0]<='b0000;qhl[3:0]<='b0110; end8'd7:begin qhh[3:0]<='b0000;qhl[3:0]<='b0111; end8'd8:begin qhh[3:0]<='b0000;qhl[3:0]<='b1000; end8'd9:begin qhh[3:0]<='b0000;qhl[3:0]<='b1001; end8'd10:begin qhh[3:0]<='b0001;qhl[3:0]<='b0000; end8'd11:begin qhh[3:0]<='b0001;qhl[3:0]<='b0001; end8'd12:begin qhh[3:0]<='b0001;qhl[3:0]<='b0010; end8'd13:begin qhh[3:0]<='b0001;qhl[3:0]<='b0011; end8'd14:begin qhh[3:0]<='b0001;qhl[3:0]<='b0100; end8'd15:begin qhh[3:0]<='b0001;qhl[3:0]<='b0101; end8'd16:begin qhh[3:0]<='b0001;qhl[3:0]<='b0110; end8'd17:begin qhh[3:0]<='b0001;qhl[3:0]<='b0111; end8'd18:begin qhh[3:0]<='b0001;qhl[3:0]<='b1000; end8'd19:begin qhh[3:0]<='b0001;qhl[3:0]<='b1001; end8'd20:begin qhh[3:0]<='b0010;qhl[3:0]<='b0000; end8'd21:begin qhh[3:0]<='b0010;qhl[3:0]<='b0001; end8'd22:begin qhh[3:0]<='b0010;qhl[3:0]<='b0010; end8'd23:begin qhh[3:0]<='b0010;qhl[3:0]<='b0011; enddefault:begin qhh[3:0]<='b0;qhl[3:0]<='b0; endendcaseendend//------------------------------数码管动态扫描-------------------------------------always @(posedge clk1khz or posedge clr) beginif(clr) begincnt<=3'b000;scan<=6'b111111;data<=4'b0000;endelse if(clk1khz) beginif(cnt==3'b101) cnt<=3'b000;else cnt<=cnt+1;case(cnt)3'b000:begin data[3:0]<=qsl[3:0];scan[5:0]<=6'b000001&{6{blink[0]}}; end3'b001:begin data[3:0]<=qsh[3:0];scan[5:0]<=6'b000010&{6{blink[0]}}; end3'b010:begin data[3:0]<=qml[3:0];scan[5:0]<=6'b000100&{6{blink[1]}}; end3'b011:begin data[3:0]<=qmh[3:0];scan[5:0]<=6'b001000&{6{blink[1]}}; end3'b100:begin data[3:0]<=qhl[3:0];scan[5:0]<=6'b010000&{6{blink[2]}}; end3'b101:begin data[3:0]<=qhh[3:0];scan[5:0]<=6'b100000&{6{blink[2]}}; endendcaseendend//-----------------------------------7段译码----------------------------------------always @(data)begincase(data[3:0])4'b0000:seg7[7:0]=8'b00111111; //04'b0001:seg7[7:0]=8'b00000110; //14'b0010:seg7[7:0]=8'b01011011; //24'b0011:seg7[7:0]=8'b01001111; //34'b0100:seg7[7:0]=8'b01100110; //44'b0101:seg7[7:0]=8'b01101101; //54'b0110:seg7[7:0]=8'b01111101; //64'b0111:seg7[7:0]=8'b00000111; //74'b1000:seg7[7:0]=8'b01111111; //84'b1001:seg7[7:0]=8'b01101111; //9default:seg7[7:0]=8'b00111111; //0endcaseendendmodule(2)按键消抖模块module IP_ButtonDebounce( clk,rst,BTN0,BTN_DEB );input clk;input rst;input BTN0;output BTN_DEB;//分频得200HZ,5ms时钟wire clk_169344;IP_1Hz #(169344) U1(.clk(clk),.rst(rst),.clk_N(clk_169344));reg BTN_r,BTN_rr,BTN_rrr;always@(posedge rst,posedge clk_169344 ) beginif(rst) beginBTN_rrr<=1'b1;BTN_rr<=1'b1;BTN_r<=1'b1;endelse beginBTN_rrr<=BTN_rr;BTN_rr<=BTN_r;BTN_r<=BTN0;endendassign BTN_DEB=BTN_r&BTN_rr&BTN_rrr;endmodule(3)分频器模块module IP_1Hz(clk,rst,clk_N); //clk=33.8688MHz,N分频模块input clk;input rst;output reg clk_N;parameter N=4;integer count;always@(posedge clk or posedge rst)beginif(rst) beginclk_N<=0;count<=0;endelse if(count==N/2-1) beginclk_N<= ~clk_N;count<=0;end。

Verilog--数字钟设计代码

数字钟一、简介此数字钟为时分秒可调,带有闹钟设置。

各引脚功能入下:clk: 输入时钟信号,为50mhz;(clk1k:产生闹铃音、报时音的时钟信号,)mode:功能控制信号;为0:计时功能;为1:闹钟功能;为2:手动校时功能;turn:接按键,在手动校时功能时,选择是调整小时,还是分钟;若长时间按住该键,还可使秒信号清零,用于精确调时;change:接按键,手动调整时,每按一次,计数器加1;如果长按,则连续快速加1,用于快速调时和定时;seg:此信号分别输出显示数据;采用BCD码计数,分别驱动6个数码管显示时间;scan:数码管位选择信号输出alert:输出到扬声器的信号,用于产生闹铃音和报时音;闹铃音为持续20秒的急促的“嘀嘀嘀”音,若按住“change”键,则可屏蔽该音;整点报时音为“嘀嘀嘀嘀—嘟”四短一长音;LD_alert:接发光二极管,指示是否设置了闹钟功能;LD_hour:接发光二极管,指示当前调整的是小时信号;LD_min:接发光二极管,指示当前调整的是分钟信号。

二、程序如下moduleshuzizhong(clk,mode,change,turn,alert,seg,scan,LD_alert,LD_hour,LD_min);input clk,mode,change,turn;output alert,LD_alert,LD_hour,LD_min;output[7:0] scan,seg;reg[7:0] scan,seg;reg[7:0] hour,min,sec,hour1,min1,sec1,ahour,amin;reg[1:0] m,fm,num1,num2,num3,num4;reg[1:0] loop1,loop2,loop3,loop4,sound;reg LD_hour,LD_min;reg clk1hz,clk4hz,clk2hz,clk1khz,minclk,hclk;reg alert1,alert2,ear;reg count1,count2,counta,countb;reg [3:0] data;reg [2:0] cnt8;reg [14:0] count3;reg [6:0] count4;wire ct1,ct2,cta,ctb,m_clk,h_clk;//-------------------1khz, 2hz--,1hz------------------------------------ always @(posedge clk)beginif(count3=='d25000)begin clk1khz<=~clk1khz;count3<=0;endelsebegin count3<=count3+1'b1;endendalways @(posedge clk1khz) //4hzbeginif(count4=='d125)begin clk4hz<=~clk4hz;count4<=0;endelsebegin count4<=count4+1'b1;endendalways @(posedge clk4hz) //2hzbeginclk2hz<=~clk2hz;endalways @(posedge clk2hz) //1hzbeginclk1hz<=~clk1hz;end//-----------------------------------------------------------always @(posedge clk4hz)beginif(sound==3)begin sound<=0; ear<=1;endelsebegin sound<=sound+1'b1; ear<=0;endendalways @(negedge mode)beginif(m==2) m<=0;else m<=m+1'b1;endalways @(negedge turn)beginfm<=~fm;end//----------------------------------------------------------------alwaysbegincase(m)2: begin if(fm)begin count1<=change; {LD_min,LD_hour}<=2; endelsebegin counta<=change; {LD_min,LD_hour}<=1; end{count2,countb}<=2'b11;end1: begin if(fm)begin count2<=change; {LD_min,LD_hour}<=2; endelse begin countb<=change; {LD_min,LD_hour}<=1; end{count1,counta}<=2'b11;enddefault: {count1,count2,counta,countb,LD_min,LD_hour}<=6'b111111;endcaseendalways @(negedge clk4hz)beginif(!count2)beginif(loop1==3) num1<=1;elsebegin loop1<=loop1+1'b1; num1<=0;endendelsebegin loop1<=0; num1<=0;endendalways @(negedge clk4hz)beginif(!countb)beginif(loop2==3) num2<=1;elsebegin loop2<=loop2+1'b1; num2<=0;endendelsebegin loop2<=0; num2<=0;endendalways @(negedge clk4hz)beginif(!count1)beginif(loop3==3) num3<=1;elsebegin loop3<=loop3+1'b1; num3<=0;endendelsebegin loop3<=0; num3<=0;endendalways @(negedge clk4hz)beginif(!counta)beginif(loop4==3) num4<=1;elsebegin loop4<=loop4+1'b1; num4<=0;endendelsebegin loop4<=0; num4<=0;endendassign ct1=(num3&clk)|(!num3&m_clk);assign ct2=(num1&clk)|(!num1&(!count2));assign cta=(num4&clk)|(!num4&h_clk);assign ctb=(num2&clk)|(!num2&(!countb));//-----------------------------------------------------------------------------always @(posedge clk1hz)beginif(!(sec1^8'h59)|(!turn)&(!m))begin sec1<=0;if(!((!turn)&(!m)))minclk<=1;endelsebeginif(sec1[3:0]==4'b1001)begin sec1[3:0]<=4'b0000; sec1[7:4]<=sec1[7:4]+1'b1;endelse sec1[3:0]<=sec1[3:0]+1'b1; minclk<=0;endendassign m_clk=minclk||(!count1);always @(posedge ct1)beginif(min1==8'h59)begin min1<=0; hclk<=1;endelsebeginif(min1[3:0]==9)begin min1[3:0]<=0; min1[7:4]<=min1[7:4]+1'b1;endelse min1[3:0]<=min1[3:0]+1'b1; hclk<=0;endendassign h_clk=hclk||(!counta);always @(posedge cta) //Сʱ¼ÆʱºÍСʱµ÷Õû½ø³Ìif(hour1==8'h23) hour1<=0;elseif(hour1[3:0]==9)begin hour1[7:4]<=hour1[7:4]+1'b1; hour1[3:0]<=0;endelse hour1[3:0]<=hour1[3:0]+1'b1;always @(posedge ct2)if(amin==8'h59) amin<=0;elseif(amin[3:0]==9)begin amin[3:0]<=0; amin[7:4]<=amin[7:4]+1'b1;endelse amin[3:0]<=amin[3:0]+1'b1;always @(posedge ctb)if(ahour==8'h23) ahour<=0;else if(ahour[3:0]==9)begin ahour[3:0]<=0; ahour[7:4]<=ahour[7:4]+1'b1;endelse ahour[3:0]<=ahour[3:0]+1'b1;//---------------------------------------------------------------------------alwaysif((min1==amin)&&(hour1==ahour)&&(amin|ahour)&&(change)) if(sec1<8'h20) alert1<=1;else alert1<=0;else alert1<=0;alwaysbegincase(m)3'b00: begin hour<=hour1; min<=min1; sec<=sec1; end3'b01: begin hour<=ahour; min<=amin; sec<=8'bx; end3'b10: begin hour<=hour1; min<=min1; sec<=8'bx; enddefault : begin hour<=8'bx; min<=8'bx; sec<=8'bx; endendcaseendassign LD_alert=(ahour|amin)?1'b1:1'b0;assign alert=((alert1)?clk1khz&clk4hz:1'b0)|alert2;alwaysbeginif((min1==8'h59)&&(sec1>8'h54)||(!(min1|sec1)))if(sec1>8'h54) alert2<=ear&clk1khz;else alert2<=!ear&clk1khz;else alert2<=0;end//-------------------------------------------------------------always @(posedge clk1khz)begincnt8<=cnt8+1'b1;endalwaysbegincase(cnt8[2:0])3'b000 : begin scan<=8'b01111111;data[3:0]<=hour[7:4];end3'b001 : begin scan<=8'b10111111;data[3:0]<=hour[3:0];end3'b010 : begin scan<=8'b11011111;data[3:0]<=min[7:4];end3'b011 : begin scan<=8'b11101111;data[3:0]<=min[3:0];end3'b100 : begin scan<=8'b11110111;data[3:0]<=sec[7:4];end3'b101 : begin scan<=8'b11111011;data[3:0]<=sec[3:0];end//3'b110 : begin scan<='b11111101;data[3:0]<=4'b1011;end//3'b111 : begin scan<='b11111110;data[3:0]<=4'b1010;enddefault : begin scan<=8'b11111111;data[3:0]<=4'bx;endendcasecase(data[3:0])4'b0000 : seg[7:0]<=8'b11000000;4'b0001 : seg[7:0]<=8'b11111001;4'b0010 : seg[7:0]<=8'b10100100;4'b0011 : seg[7:0]<=8'b10110000;4'b0100 : seg[7:0]<=8'b10011001;4'b0101 : seg[7:0]<=8'b10010010;4'b0110 : seg[7:0]<=8'b10000010;4'b0111 : seg[7:0]<=8'b11111000;4'b1000 : seg[7:0]<=8'b10000000;4'b1001 : seg[7:0]<=8'b10010000;4'b1010 : seg[7:0]<=8'b10001000;4'b1011 : seg[7:0]<=8'b10000011;4'b1100 : seg[7:0]<=8'b11000110;4'b1101 : seg[7:0]<=8'b10100001;4'b1110 : seg[7:0]<=8'b10000110;4'b1111 : seg[7:0]<=8'b10001110;default : seg[7:0]<=8'bx;endcaseendendmodule三、框图。

电子钟(FPGA设计verilog代码)

电子钟(FPGA设计verilog代码)//*****************************************//电子钟:24小时制时分秒////作者:yotain////clk 50M时钟 CP 1Hz输出可接LED指示灯//nCR 清零(必须接低电平异步清零)//Adj_Min (分校正低电平计时必须接)//Adj_Hour (时校正低电平计时必须接)//dataout (数码管输出)//en (数码管使能端)//(Hour Minute Second 可以不接也可以单独接数码管一位的) //修改bcd_decoder 即可修改显示////*****************************************//************ timeclock top block*************module top_clock ( Hour, Minute, Second, CP, nCR, EN, Adj_Min, Adj_Hour,clk,dataout,en) ;input clk, nCR, EN, Adj_Min, Adj_Hour;output CP;output [7:0] Hour, Minute, Second,dataout;output [3:0] en;wire [7:0] Hour, Minute, Second, dataout;supply1 Vdd;wire MinL_EN, MinH_EN, Hour_EN;//**************Hour, Minute, Second counter************counter10 U1 ( Second[3:0], nCR, EN, CP);counter6 U2 ( Second[7:4], nCR, ( Second[3:0]==4'h9), CP);assign MinL_EN = Adj_Min? Vdd : (Second==8'h59);assign MinH_EN = ( Adj_Min &&( Minute [3:0] ==4'h59))|| ( Minute[3:0]==4'h9)&& (Second == 8'h59);counter10 U3 ( Minute[3:0], nCR, MinL_EN,CP);counter6 U4 ( Minute[7:4], nCR, MinH_EN,CP);assign Hour_EN = Adj_Hour ? Vdd: ((Minute == 8'h59)&&(Second == 8'h59));counter24 U5 ( Hour[7:4], Hour[3:0], nCR, Hour_EN,CP);bcd_decoder U6 (clk,nCR,Hour[7:4],Hour[3:0],Minute[7:4],Minute[3:0],dataout,en);PULSE U7(clk,CP);endmodule//**************counter10 ( BCD 0~9 )*************module counter10 ( Q, nCR, EN, CP);input CP, nCR, EN;output [3 : 0] Q;reg [3 : 0] Q;always @ (posedge CP or negedge nCR)beginif( !nCR ) Q<=4'b0000;else if ( !EN ) Q<=Q;else if ( Q ==4'b1001) Q <= 4'b0000;else Q <= Q+1'b1;endendmodule//**************counter6 ( BCD 0~5 )************ module counter6 ( Q, nCR, EN, CP);input CP, nCR, EN;output [3:0] Q;reg [3:0] Q;always @ (posedge CP or negedge nCR ) beginif(!nCR) Q<= 4'b0000;else if (!EN) Q<=Q;else if (Q == 4'b0101) Q<=4'b0000;else Q <= Q + 1'b1;endendmodule//***************counter24 ( 0~23 )************** module counter24 ( CntH, CntL, nCR, EN, CP); input CP, nCR, EN;output[3:0] CntH,CntL;reg [3:0] CntH,CntL;reg CO;always @ (posedge CP or negedge nCR)if(!nCR) {CntH,CntL} <=8'h00;else if(!EN) {CntH,CntL} <= {CntH,CntL};else if ( (CntH>2)||(CntL>9) || ( (CntH==2)&&(CntL>=3) ) ) {CntH,CntL} <=8'h00;else if((CntH==2)&&(CntL<3))beginCntH<=CntH;CntL<=CntL+1'b1;endelse if (CntL==9)beginCntH=CntH+1'b1;CntL=4'b0000;endelse beginCntH<=CntH;CntL<=CntL+1'b1;endendendmodule//*************cnt_1Hz*****************module PULSE ( clk, clk_1Hz);input clk;output clk_1Hz;reg [24:0] cnt_1Hz;reg R_clk=0;assign clk_1Hz=R_clk;always @ (posedge clk)if (cnt_1Hz==50000000) cnt_1Hz<=0;else cnt_1Hz<=cnt_1Hz+1;endalways @ (posedge clk)beginif(cnt_1Hz<=25000000) R_clk<=1;else R_clk<=0;endendmodule//*************bcd_decoder*************module bcd_decoder (clk,nCR,A,B,C,D,dataout,en);input clk; //system clockinput nCR; //system reset,low is activeinput [3:0] A,B,C,D;output[7:0] dataout;output[3:0] en; //enable high is activereg[7:0] dataout;reg[4:0] en;reg[15:0] cnt_scan;reg[3:0] dataout_buf;always@(posedge clk or negedge nCR)beginif(!nCR) begincnt_scan<=0;endelse begincnt_scan<=cnt_scan+1; endendalways@(cnt_scan) begincase(cnt_scan[15:14]) 2'b00:en=4'b0001;2'b01:en=4'b0010;2'b10:en=4'b0100;2'b11:en=4'b1000; default:en=4'b1111; endcaseendalways@(en)begincase(en)4'b0001:dataout_buf=A;4'b0010:dataout_buf=B;4'b0100:dataout_buf=C;dataout_buf=D; default:dataout_buf=4'b0000; endcaseendalways@(dataout_buf) begincase(dataout_buf)4'b0000:dataout=8'b1111_1100; 4'b0001:dataout=8'b0110_0000; 4'b0010:dataout=8'b1101_1010; 4'b0011:dataout=8'b1111_0010; 4'b0100:dataout=8'b0110_0110; 4'b0101:dataout=8'b1011_0110; 4'b0110:dataout=8'b1011_1110; 4'b0111:dataout=8'b1110_0000; 4'b1000:dataout=8'b1111_1110; 4'b1001:dataout=8'b1110_0110;dataout=8'b1110_1110; 4'b1011:dataout=8'b0011_1110; 4'b1100:dataout=8'b1001_1100; 4'b1101:dataout=8'b0111_1010; 4'b1110:dataout=8'b1001_1110; 4'b1111:dataout=8'b1000_1110; default :dataout=8'b0000_0010; endcaseendendmodule//End of RTL code。

简单的数字时钟(verilog设计)

else begin if(ss1==1) begin if (hour_1<2'b10) begin if(hour_0<4'b1001) hour_0<=hour_0+4'b1; else begin hour_0<=4'b0; hour_1<=hour_1+2'b1;end end if(hour_1==2'b10) begin if (hour_0<4'b0011) hour_0<=hour_0+4'b1; else begin hour_0<=4'b0; hour_1<=2'b0; end end end if(ss2==1) begin if (hour_1>2'b0) begin if (hour_0>4'b0) hour_0<=hour_0-4'b1; else begin hour_0<=4'b1001; hour_1<=hour_1-2'b1;end end if (hour_1==2'b00) begin if (hour_0>4'b0) hour_0<=hour_0-4'b1; else begin hour_1<=4'b0010; hour_0<=4'b0011;end end end

三、闹钟部分

1、设置闹铃

if (sh==1) begin if (ss1==1) begin if (minute_0<4'b1001) minute_0<=minute_0+4'b1; else begin minute_0<=4'b0; if(minute_1<4'b0101) minute_1<=minute_1+4'b1; else minute_1<=4'b0; end end if (ss2==1) begin if (minute_0>4'b0000) minute_0<=minute_0-4'b1; else begin minute_0<=4'b1001; if (minute_1>4'b0000) minute_1<=minute_1-4'b1; else minute_1<=4'b0101;end end end

产生时钟门控的verilog写法

一、产生时钟门控的verilog写法在数字电路设计中,时钟门控是一种重要的设计概念。

它通常用于控制某个电路部分在特定时钟脉冲下的工作。

在Verilog中,我们可以通过设计适当的逻辑来实现产生时钟门控的功能。

下面我们将介绍如何在Verilog中实现产生时钟门控的写法,以及对其深入的讨论和理解。

二、Verilog中产生时钟门控的基本方法在Verilog中,产生时钟门控通常使用always块来实现。

下面是一个简单的示例代码:```verilogmodule clock_gate(input wire clk,input wire reset,output reg gate);always @(posedge clk or posedge reset)beginif (reset)gate <= 1'b0;elsegate <= 1'b1;endendmodule```在这个例子中,我们定义了一个模块clock_gate,它包含了一个时钟输入clk、一个复位信号reset和一个时钟门控输出gate。

在always块中,我们使用了posedge关键字来表示在时钟信号的上升沿触发,当reset信号为1时,gate输出为0,否则输出为1。

这样就实现了时钟门控的功能。

三、对Verilog时钟门控的深入理解和讨论产生时钟门控的Verilog写法看似简单,但其中蕴含了许多深层次的设计思考。

我们需要考虑时钟门控的灵活性和稳定性。

在实际设计中,时钟门控往往需要满足一些特定的时序要求,例如保持时间、设置时间等。

我们需要对时钟门控的功能和时序要求有深入的理解,以确保设计的稳定性和可靠性。

另外,Verilog中产生时钟门控的写法还需要考虑到时序约束和时钟域的问题。

在复杂的数字电路设计中,不同的模块通常处于不同的时钟域,因此对时钟门控的设计需要满足时序约束,以保证信号的正确传输和处理。

为了避免时钟域之间的异步问题,我们还需要考虑时钟和复位信号的同步问题,以确保时钟门控的稳定性和可靠性。

verilog实时可调时钟代码

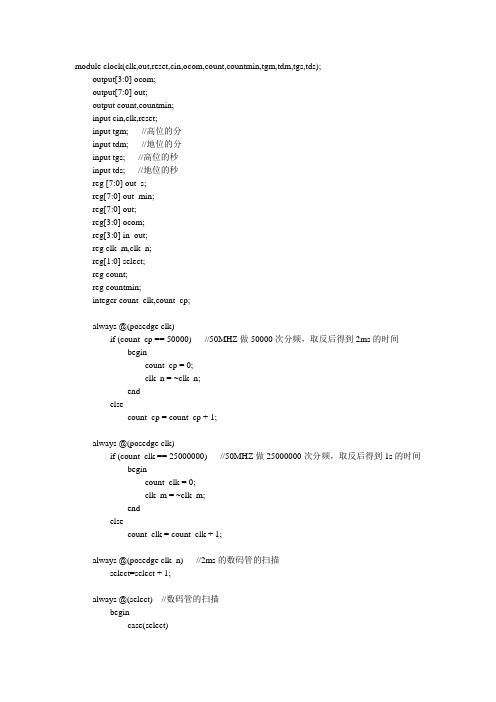

module clock(clk,out,reset,cin,ocom,count,countmin,tgm,tdm,tgs,tds);output[3:0] ocom;output[7:0] out;output count,countmin;input cin,clk,reset;input tgm; //高位的分input tdm; //地位的分input tgs; //高位的秒input tds; //地位的秒reg [7:0] out_s;reg[7:0] out_min;reg[7:0] out;reg[3:0] ocom;reg[3:0] in_out;reg clk_m,clk_n;reg[1:0] select;reg count;reg countmin;integer count_clk,count_cp;always @(posedge clk)if (count_cp == 50000) //50MHZ做50000次分频,取反后得到2ms的时间begincount_cp = 0;clk_n = ~clk_n;endelsecount_cp = count_cp + 1;always @(posedge clk)if (count_clk == 25000000) //50MHZ做25000000次分频,取反后得到1s的时间begincount_clk = 0;clk_m = ~clk_m;endelsecount_clk = count_clk + 1;always @(posedge clk_n) //2ms的数码管的扫描select=select + 1;always @(select) //数码管的扫描begincase(select)2'b00 : begin ocom[3:0]=4'b1110;in_out = out_s[3:0]; end2'b01 : begin ocom[3:0]=4'b1101;in_out = out_s[7:4]; end2'b10 : begin ocom[3:0]=4'b1011;in_out = out_min[3:0]; end2'b11 : begin ocom[3:0]=4'b0111;in_out = out_min[7:4]; end endcaseendalways @(posedge clk_m)beginif(!reset) //如果reset为低电平,秒清零beginout_s <= 0;endelse if(!tds) //如果tds为低电平,秒调整beginout_s[3:0]<=out_s[3:0]+1;if(out_s[3:0]==9)out_s[3:0]<=0;endelse if(!tgs) //如果tgs为低电平,秒调整beginout_s[7:4]<=out_s[7:4]+1;if(out_s[7:4]==5)out_s[7:4]<=0;endelse if(cin) //秒计数,60进制计数器beginif(out_s[3:0]==9)beginout_s[3:0] <= 0;if(out_s[7:4]==5)out_s[7:4] <= 0;elseout_s[7:4] <= out_s[7:4]+1;endelseout_s[3:0] <= out_s[3:0]+1;endendalways @(out_s) //秒的进位if ((out_s == 8'h59) & cin)count = 1;else#1 count = 0;always @(posedge clk_m)beginif(!reset) //reset低电平,分清零beginout_min <= 0;endelse if(!tdm) //tdm低电平,分调整beginout_min[3:0]<=out_min[3:0]+1;if(out_min[3:0]==9)out_min[3:0]<=0;endelse if(!tgm) //tgm低电平,分调整beginout_min[7:4]<=out_min[7:4]+1;if(out_min[7:4]==5)out_min<=0;endelse if(count) //分计数,60进制计数器if(out_min[3:0]==9)beginout_min[3:0] <= 0;if(out_min[7:4]==5)out_min[7:4] <= 0;elseout_min[7:4] <= out_min[7:4]+1;endelseout_min[3:0] = out_min[3:0] + 1;endalways @(out_min) //分进位if ((out_min == 8'h59) & cin)countmin = 1;else#1 countmin = 0;always @(in_out) //数码管的绑定,输出响应begincase(in_out)4'b0000 : out[7:0]=8'b1001_0000;4'b0001 : out[7:0]=8'b1001_1111;4'b0010 : out[7:0]=8'b0101_1000;4'b0011 : out[7:0]=8'b0001_1001;4'b0100 : out[7:0]=8'b0001_0111;4'b0101 : out[7:0]=8'b0011_0001;4'b0110 : out[7:0]=8'b0011_0000;4'b0111 : out[7:0]=8'b1001_1101;4'b1000 : out[7:0]=8'b0001_0000;4'b1001 : out[7:0]=8'b0001_0001;default : out[7:0]=8'bx;endcaseendendmodule。

verilog语言实现时钟功能

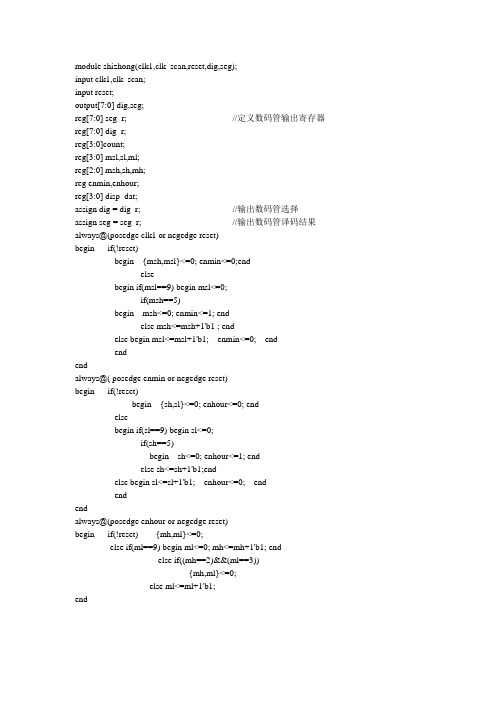

module shizhong(clk1,clk_scan,reset,dig,seg);input clk1,clk_scan;input reset;output[7:0] dig,seg;reg[7:0] seg_r; //定义数码管输出寄存器reg[7:0] dig_r;reg[3:0]count;reg[3:0] msl,sl,ml;reg[2:0] msh,sh,mh;reg enmin,enhour;reg[3:0] disp_dat;assign dig = dig_r; //输出数码管选择assign seg = seg_r; //输出数码管译码结果always@(posedge clk1 or negedge reset)begin if(!reset)begin {msh,msl}<=0; enmin<=0;endelsebegin if(msl==9) begin msl<=0;if(msh==5)begin msh<=0; enmin<=1; endelse msh<=msh+1'b1 ; endelse begin msl<=msl+1'b1; enmin<=0; endendendalways@( posedge enmin or negedge reset)begin if(!reset)begin {sh,sl}<=0; enhour<=0; endelsebegin if(sl==9) begin sl<=0;if(sh==5)begin sh<=0; enhour<=1; endelse sh<=sh+1'b1;endelse begin sl<=sl+1'b1; enhour<=0; endendendalways@(posedge enhour or negedge reset)begin if(!reset) {mh,ml}<=0;else if(ml==9) begin ml<=0; mh<=mh+1'b1; endelse if((mh==2)&&(ml==3)){mh,ml}<=0;else ml<=ml+1'b1;endalways @(posedge clk_scan) //定义上升沿触发进程beginif(count==8) count<=0;elsecount <= count + 1'b1;endalways @(posedge clk_scan)begincase(count) //选择扫描显示数据3'd0:begin disp_dat= msl; dig_r = 8'b11111110; end //第一个数码管3'd1:begin disp_dat =msh; dig_r = 8'b11111101;end //第二个数码管3'd2:begin disp_dat =4'ha; dig_r = 8'b11111011;end//第三个数码管3'd3:begin disp_dat =sl; dig_r = 8'b11110111; end//第四个数码管3'd4:begin disp_dat =sh; dig_r = 8'b11101111; end //第五个数码管3'd5:begin disp_dat =4'ha; dig_r = 8'b11011111; end//第六个数码管3'd6:begin disp_dat =ml; dig_r = 8'b10111111; end //第七个数码管3'd7:begin disp_dat =mh; dig_r = 8'b01111111; end//第八个数码管endcaseendalways @(disp_dat)begincase(disp_dat) //七段译码4'h0:seg_r = 8'hc0; //显示04'h1:seg_r = 8'hf9; //显示14'h2:seg_r = 8'ha4; //显示24'h3:seg_r = 8'hb0; //显示34'h4:seg_r = 8'h99; //显示44'h5:seg_r = 8'h92; //显示54'h6:seg_r = 8'h82; //显示64'h7:seg_r = 8'hf8; //显示74'h8:seg_r = 8'h80; //显示84'h9:seg_r = 8'h90; //显示94'ha:seg_r = 8'hbf; //显示-default seg_r=8'hff;endcaseendendmodule。

verilog实现简易数字钟设计

V e r i l o g实现简易数字钟设计(总2页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--module ly2(clock,sec1,sec2,min1,min2,hou1,hou2);input clock;output sec1,sec2,min1,min2,hou1,hou2;reg[5:0] sec,min,hou;reg tun,mod;reg[3:0] sec1,sec2,min1,min2,hou1,hou2;wire mt,nt;initialbegintun=1;mod=1;min=0;hou=0;sec=0;sec1=0;sec2=0;min1=0;min2=0;hou1=0;hou2=0;endalways @(posedge clock) \\clock 标准1HZ时钟信号beginif(sec==59)beginsec<=0; \\秒为60进制计数器tun<=1; \\每60秒产生一个进位信号tun。

endelsebeginsec<=sec+1;tun<=0; \\进位信号置0。

endendassign mt=tun; \\生成分的控制信号,always@(posedge mt)beginif(min==59) \\分钟为60进制计数器 beginmin<=0;mod<=1; \\每60分产生一个小时的进位。

endelsebeginmin<=min+1;mod<=0; \\分钟向小时的进位信号置0。

endendassign nt=mod; \\生成时的控制信号,always@(posedge nt)beginif(hou==23) \\小时为24进制计数器 hou<=0;elsehou<=hou+1;endalways@(sec)beginsec1<=sec%10; \\sec1为秒个位sec2<=sec/10; \\sec2为秒十位endalways@(min)beginmin1<=min%10; \\min1为分个位min2<=min/10; \\min2为分十位endalways@(hou)beginhou1<=hou%10; \\hou1为时个位 hou2<=hou/10; \\hou2为时十位 endendmodule。

基于verilogHDL的数字时钟

*****顶层模块信号定义:clk : 基准时钟信号输入;keysel : 校时状态/正常计时状态选择键输入;key_s : 校秒信号选择键输入;key_m : 校分信号选择键输入;key_h : 校时信号选择键输入;keyclr : 计时清零键;keyen : 计时开始键;buzzout : 声响输出;sled : 4位数码管段码输出;sl : 4位数码管位码输出;seg : 单个数码管输出;********************************************************* ******/moduleclock(clk,keysel,key_s,key_m,key_h,keyen,keyclr,sled,sl,seg,buzzout);output[7:0] sled;output[3:0] sl;output[7:0] seg;output buzzout;input clk;input keysel,key_s,key_m,key_h,keyen,keyclr;reg[24:0] count;wire[23:0] min;wire sec;wire sec_s,sec_m,sec_h,sec_narmal;divclk Q1(clk,sec_narmal,sec_s,sec_m,sec_h);modifyQ2(clk,keysel,key_s,key_m,key_h,sec,sec_narmal,sec_s,sec_m,sec_h);counttime Q3(sec,keyclr,keyen,min);display Q4(clk,sec,min,sled,sl,seg);music Q5(clk,min,buzzout,sec_narmal);endmodule*****分频模块信号定义:clk : 基准时钟信号输入;sec_narmal : 周期为1的信号输出;sec_s : 周期为0.5s的信号输出;sec_m : 周期为0.05s的信号输出;sec_h : 周期为0.0005s的信号输出;********************************************************* ******/module divclk(clk,sec_narmal,sec_s,sec_m,sec_h);input clk;output sec_narmal,sec_s,sec_m,sec_h;reg[23:0] count1;reg[22:0] count2;reg[19:0] count3;reg[12:0] count4;reg sec_narmal,sec_s,sec_m,sec_h;always@(negedge clk)begincount1=count1+1'b1;if(count1==24'd1*******)begincount1=24'h0;sec_narmal=~sec_narmal;endendalways@(negedge clk)begincount2=count2+1'b1;if(count2==23'd6000000)begincount2=23'h0;sec_s=~sec_s;endendalways@(negedge clk)begincount3=count3+1'b1;if(count3==20'd600000)begincount3=20'h0;sec_m=~sec_m;endendalways@(negedge clk)begincount4=count4+1'b1;if(count4==13'd6000)begincount4=13'h0;sec_h=~sec_h;endendendmodule/********************************************************* *****计时处理模块信号定义:sec : 计时信号输入;keyclr : 计时清零键;keyen : 计时开始键;min : 计时结果输出;********************************************************* ******/module counttime(sec,keyclr,keyen,min);input sec;input keyclr,keyen;output[23:0] min;reg[23:0] min;always@(posedge sec)beginif(!keyclr)beginmin=24'h0;endelseif(!keyen)beginmin=min+1'b1;if(min[3:0]==4'ha)beginmin[3:0]=4'h0;min[7:4]=min[7:4]+1'b1;if(min[7:4]==4'h6)beginmin[7:4]=4'h0;min[11:8]=min[11:8]+1'b1;if(min[11:8]==4'ha)beginmin[11:8]=4'h0;min[15:12]=min[15:12]+1'b1;if(min[15:12]==4'h6)beginmin[15:12]=4'h0;min[19:16]=min[19:16]+1'b1;if(min[19:16]==4'ha)beginmin[19:16]=4'h0;min[23:20]=min[23:20]+1'b1;endif(min[23:16]==8'h24)min[23:16]=0;endendendendendendendmodule/********************************************************* *****校时模块信号定义:clk : 基准时钟信号输入;keysel : 校时状态/正常计时状态选择键输入key_s : 校秒信号选择键输入key_m : 校分信号选择键输入key_h : 校时信号选择键输入sec_narmal : 周期为1的信号输出;sec_s : 周期为0.5s的信号输出;sec_m : 周期为0.05s的信号输出;sec_h : 周期为0.0005s的信号输出;sec : 计时信号输出;********************************************************* ******/modulemodify(clk,keysel,key_s,key_m,key_h,sec,sec_narmal,sec_s,sec_m,sec _h);input clk;input keysel;input key_s,key_m,key_h;input sec_narmal,sec_s,sec_m,sec_h;output sec;reg sec;always@(negedge clk)beginif(!keysel)beginif(!key_s)sec=sec_s;if(!key_m)sec=sec_m;if(!key_h)sec=sec_h;endelsesec=sec_narmal;endendmodule/********************************************************* *****报时模块信号定义:clk : 基准时钟信号输入;min : 当前计时结果输入;buzzout : 声响输出;********************************************************* ******/module music(clk,min,buzzout,sec_narmal);input clk,sec_narmal;input[23:0] min;output buzzout;reg[3:0] high,med,low;reg buzzout_reg;reg[24:0] count1,count2;reg[15:0] count_end,count_now;reg[7:0] counter;reg clk_4HZ;always@(posedge clk)beginif(count1<22'd3000000)count1=count1+1'b1;elsebegincount1=0;clk_4HZ=~clk_4HZ;endendalways@(posedge clk)beginif(count_now!=count_end)begincount2=25'h0;count_now=count_end;endcount2=count2+1'b1;if((min[15:0]>=16'h5945)&&(min[15:0]<=16'h5959))beginif((count2==count_end)&&(min[23:16]==8'h11))begincount2=25'h0;buzzout_reg=!buzzout_reg;endendif((min[15:0]>=16'h5950)&&(min[15:0]<=16'h5959)) beginif(min[23:16]!=8'h11)beginbuzzout_reg=!(count2[10]&sec_narmal);endendendalways@(posedge clk_4HZ)begincase({high,med,low})9'b000000001:count_end=16'hbb9a;9'b000000010:count_end=16'ha72f;9'b000000011:count_end=16'h94f2;9'b000000100:count_end=16'h8e78;9'b000000101:count_end=16'h7d63;9'b000000110:count_end=16'h6fb5;9'b000000111:count_end=16'h637f;9'b000001000:count_end=16'h5dfb;9'b000010000:count_end=16'h53bb;9'b000011000:count_end=16'h4a95;9'b000100000:count_end=16'h4651;9'b000101000:count_end=16'h3eb1;9'b000110000:count_end=16'h37da;9'b000111000:count_end=16'h31bf;9'b001000000:count_end=16'h2ef2;9'b010000000:count_end=16'h29d4;9'b011000000:count_end=16'h2543;9'b100000000:count_end=16'h232f;9'b101000000:count_end=16'h1f58;9'b110000000:count_end=16'h1bed;9'b111000000:count_end=16'h18df;endcaseendalways@(posedge clk_4HZ)beginif(counter==57)counter=0;elsecounter=counter+1'b1;case(counter)0:{high,med,low}=9'b000001000;1:{high,med,low}=9'b000001000;2:{high,med,low}=9'b000001000;3:{high,med,low}=9'b000001000;4:{high,med,low}=9'b000010000;5:{high,med,low}=9'b000010000;6:{high,med,low}=9'b000010000;7:{high,med,low}=9'b000010000;8:{high,med,low}=9'b000011000;9:{high,med,low}=9'b000011000;10:{high,med,low}=9'b000011000;11:{high,med,low}=9'b000011000;12:{high,med,low}=9'b000001000;13:{high,med,low}=9'b000001000;14:{high,med,low}=9'b000001000;15:{high,med,low}=9'b000001000;16:{high,med,low}=9'b000001000;17:{high,med,low}=9'b000001000;19:{high,med,low}=9'b000001000; 20:{high,med,low}=9'b000010000; 21:{high,med,low}=9'b000010000; 22:{high,med,low}=9'b000010000; 23:{high,med,low}=9'b000010000; 24:{high,med,low}=9'b000011000; 25:{high,med,low}=9'b000011000; 26:{high,med,low}=9'b000011000; 27:{high,med,low}=9'b000011000; 28:{high,med,low}=9'b000001000; 29:{high,med,low}=9'b000001000; 30:{high,med,low}=9'b000001000; 31:{high,med,low}=9'b000001000; 32:{high,med,low}=9'b000011000; 33:{high,med,low}=9'b000011000; 34:{high,med,low}=9'b000011000; 35:{high,med,low}=9'b000011000; 36:{high,med,low}=9'b000100000; 37:{high,med,low}=9'b000100000; 38:{high,med,low}=9'b000100000; 39:{high,med,low}=9'b000100000; 40:{high,med,low}=9'b000101000; 41:{high,med,low}=9'b000101000; 42:{high,med,low}=9'b000101000; 43:{high,med,low}=9'b000101000; 44:{high,med,low}=9'b000001000; 45:{high,med,low}=9'b000001000; 46:{high,med,low}=9'b000001000; 47:{high,med,low}=9'b000011000; 48:{high,med,low}=9'b000011000; 49:{high,med,low}=9'b000011000; 50:{high,med,low}=9'b000011000; 51:{high,med,low}=9'b000100000; 52:{high,med,low}=9'b000100000; 53:{high,med,low}=9'b000100000; 54:{high,med,low}=9'b000100000;56:{high,med,low}=9'b000101000;57:{high,med,low}=9'b000101000;endcaseendassign buzzout=buzzout_reg;endmodule/********************************************************* *****显示模块信号定义:clk : 基准时钟信号输入;min : 当前计时结果输入;sec : 计时的秒信号输入;sled_reg : 数码管短码输出;sl_reg : 数码管位码输出;seg_reg : 单个数码管输出;********************************************************* ******/module display(clk,sec,min,sled_reg,sl_reg,seg_reg);input clk;input sec;input[23:0] min;output[7:0] sled_reg;output[3:0] sl_reg;output[7:0] seg_reg;reg[7:0] sled_reg;reg[3:0] sl_reg;reg[7:0] seg_reg;reg[15:0] count;reg[3:0] ledbuf;always@(negedge clk)begincount=count+1'b1;endalways@(count[11:10])begincase(count[11:10])2'h0:ledbuf=min[3:0];2'h1:ledbuf=min[7:4];2'h2:ledbuf=min[11:8];2'h3:ledbuf=min[15:12];endcasecase(count[11:10])2'h0:sl_reg=4'b0111;2'h1:sl_reg=4'b1011;2'h2:sl_reg=4'b1101;2'h3:sl_reg=4'b1110;endcaseendalways@(ledbuf)begincase(ledbuf)4'h0:sled_reg=8'hc0;4'h1:sled_reg=8'hf9;4'h2:sled_reg=8'ha4;4'h3:sled_reg=8'hb0;4'h4:sled_reg=8'h99;4'h5:sled_reg=8'h92;4'h6:sled_reg=8'h82;4'h7:sled_reg=8'hf8;4'h8:sled_reg=8'h80;4'h9:sled_reg=8'h90;4'ha:sled_reg=8'h88;4'hb:sled_reg=8'h83;4'hc:sled_reg=8'hc6;4'hd:sled_reg=8'ha1;4'he:sled_reg=8'h86;4'hf:sled_reg=8'h8e;endcaseif((count[11:10]==2'b10)&sec)sled_reg=sled_reg&8'h7f; endalways@(min[23:16])begincase(min[23:16])8'h0:seg_reg=8'h3f;8'h1:seg_reg=8'h06;8'h2:seg_reg=8'h5b;8'h3:seg_reg=8'h4f;8'h4:seg_reg=8'h66;8'h5:seg_reg=8'h6d;8'h6:seg_reg=8'h7d;8'h7:seg_reg=8'h07;8'h8:seg_reg=8'h7f;8'h9:seg_reg=8'h6f;8'h10:seg_reg=8'h77;8'h11:seg_reg=8'h7c;8'h12:seg_reg=8'hbf;8'h13:seg_reg=8'h86;8'h14:seg_reg=8'hdb;8'h15:seg_reg=8'hcf;8'h16:seg_reg=8'he6;8'h17:seg_reg=8'hed;8'h18:seg_reg=8'hfd;8'h19:seg_reg=8'h87;8'h20:seg_reg=8'hff;8'h21:seg_reg=8'hef;8'h22:seg_reg=8'hf7;8'h23:seg_reg=8'hfc;endcaseendendmodule。

实现数字时钟设计的Verilog代码

下面给出实现数字时钟设计的Verilog代码module top(inc_hour,sub_hour,inc_min,sub_min,rst,clk,sel,q); input inc_hour,sub_hour,inc_min,sub_min;input rst,clk;output reg [2:0] sel;output reg [6:0] q;reg [9:0] scan;reg [2:0] scan_clk;reg div_clk;reg [19:0] counter_clk;reg [3:0] sec_counter1,sec_counter2;reg [3:0] min_counter1,min_counter2;reg [3:0] hour_counter1,hour_counter2;always @ (negedge rst or posedge clk)beginif(~rst)begincounter_clk<=20'h00000;div_clk<=1'b0;endelsebeginif(counter_clk==20'h7a11f)begincounter_clk<=20'h00000;div_clk<=~div_clk;endelse counter_clk<=counter_clk+1;endendalways @(negedge rst or posedge div_clk)beginif(~rst)beginsec_counter1<=4'h0;sec_counter2<=4'h0;min_counter1<=4'h0;min_counter2<=4'h0;hour_counter1<=4'h0;hour_counter2<=4'h0;endelseif(inc_min==1'b0) beginif(min_counter1==4'h9) begin min_counter1<=4'h0;if(min_counter2==4'h5)min_counter2<=4'h0;elsemin_counter2<=min_counter2+1; endelsemin_counter1<=min_counter1+1; endelse if(sub_min==4'b0) beginif(min_counter1==4'h0) begin min_counter1<=4'h9;if(min_counter2==4'h0)min_counter2<=4'h5;elsemin_counter2<=min_counter2-1; endelsemin_counter1<=min_counter1-1; endelse if(inc_hour==4'b0) beginif(hour_counter2==4'h2) beginif(hour_counter1==4'h3) begin hour_counter2<=4'h0;hour_counter1<=4'h0;endelsehour_counter1<=hour_counter1+1; endelse beginif(hour_counter1==4'h9) begin hour_counter1<=4'h0;hour_counter2<=hour_counter2+1; endelsehour_counter1<=hour_counter1+1; endendelse if(sub_hour==1'b0) beginif(hour_counter1==1'b0) beginif(hour_counter2==1'b0) beginhour_counter1<=4'h3;hour_counter2<=4'h2;endelse beginhour_counter2<=hour_counter2-1; hour_counter1<=4'h9;endendelsehour_counter1<=hour_counter1-1; endelse beginif(sec_counter1>=4'h9) beginsec_counter1<=4'h0;if(sec_counter2>=4'h5) beginsec_counter2<=4'h0;if(min_counter1>=4'h9) begin min_counter1<=4'h0;if(min_counter2>=4'h5) begin min_counter2<=4'h0;if(hour_counter2==4'h2) beginif(hour_counter1==4'h3) begin hour_counter1<=4'h0;hour_counter2<=4'h0;endelsehour_counter1<=hour_counter1+1; endelse beginif(hour_counter1==4'h9) begin hour_counter1<=4'h0;hour_counter2<=hour_counter2+1; endelsehour_counter1<=hour_counter1+1; endendmin_counter2<=min_counter2+1; endmin_counter1<=min_counter1+1; endsec_counter2<=sec_counter2+1; endsec_counter1<=sec_counter1+1;endendalways @(negedge rst or posedge clk) beginif(~rst) scan_clk<=3'b000;elsebeginif(scan_clk==3'b101) scan_clk<=3'b000; else scan_clk<=scan_clk+1;endendalways @(scan_clk)begincase (scan_clk)3'b000 :beginq<=disp(sec_counter1);sel<=3'b000;end3'b001 :beginq<=disp(sec_counter2);sel<=3'b001;end3'b010 :beginq<=disp(min_counter1);sel<=3'b010;end3'b011 :beginq<=disp(min_counter2);sel<=3'b011;end3'b100 :beginq<=disp(hour_counter1);sel<=3'b100;end3'b101 :beginq<=disp(hour_counter2);sel<=3'b101;enddefault : ;endcaseendfunction[6:0] disp;input[3:0] a;case (a)4'h0 : disp=7'b0111111; 4'h1 : disp=7'b0000110; 4'h2 : disp=7'b1011011; 4'h3 : disp=7'b1001111; 4'h4 : disp=7'b1100110; 4'h5 : disp=7'b1101101; 4'h6 : disp=7'b1111101; 4'h7 : disp=7'b0000111; 4'h8 : disp=7'b1111111;4'h9 : disp=7'b1101111; default : disp=7'b1111111; endcaseendfunction endmodule。

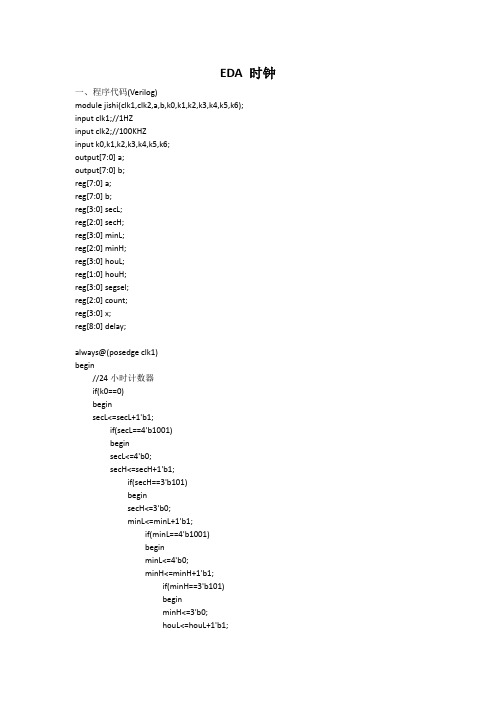

EDA时钟Verilog代码

EDA 时钟一、程序代码(Verilog)module jishi(clk1,clk2,a,b,k0,k1,k2,k3,k4,k5,k6);input clk1;//1HZinput clk2;//100KHZinput k0,k1,k2,k3,k4,k5,k6;output[7:0] a;output[7:0] b;reg[7:0] a;reg[7:0] b;reg[3:0] secL;reg[2:0] secH;reg[3:0] minL;reg[2:0] minH;reg[3:0] houL;reg[1:0] houH;reg[3:0] segsel;reg[2:0] count;reg[3:0] x;reg[8:0] delay;always@(posedge clk1)begin//24小时计数器if(k0==0)beginsecL<=secL+1'b1;if(secL==4'b1001)beginsecL<=4'b0;secH<=secH+1'b1;if(secH==3'b101)beginsecH<=3'b0;minL<=minL+1'b1;if(minL==4'b1001)beginminL<=4'b0;minH<=minH+1'b1;if(minH==3'b101)beginminH<=3'b0;houL<=houL+1'b1;if(houL==4'b1001)beginhouL<=4'b0;houH<=houH+1'b1;endendendendendelse if(houH==2'b10)beginif(houL==4'b0100)beginhouL<=4'b0;houH<=2'b0;endendendx=4'b1010;if(k0==1)begin//调秒if(k1==1)//++beginsecL<=secL+1'b1;if(secL==4'b1001)beginsecL<=4'b0;secH<=secH+1'b1;if(secH==3'b101)beginsecH<=3'b0;endendendif(k2==1)//--beginsecL<=secL-1'b1;if(secL==4'b0)beginsecL<=4'b1001;secH<=secH-1'b1;beginsecH<=3'b101;endendend//调分if(k3==1)//++beginminL<=minL+1'b1;if(minL==4'b1001)beginminL<=4'b0;minH<=minH+1'b1;if(minH==3'b101)beginminH<=3'b0;endendendif(k4==1)//--beginminL<=minL-1'b1;if(minL==4'b0)beginminL<=4'b1001;minH<=minH-1'b1;if(minH==3'b0)beginminH<=3'b101;endendend//调时if(k5==1)//++beginhouL<=houL+1'b1;if(houL==4'b1001)beginhouL<=4'b0;houH<=houH+1'b1;endbeginif(houL==4'b0100)beginhouL<=4'b0;houH<=2'b0;endendendif(k6==1)//--beginhouL<=houL-1'b1;if(houL==4'b0)beginhouL<=4'b1001;houH<=houH-1'b1;endelse if(houH==2'b0)beginif(houL==4'b0)beginhouL<=4'b0011;houH<=2'b01;endendendendendalways@(posedge clk2)begincount<=count+1'b1;delay<=delay+1'b1;case(count)3'b000:begin a=8'b00000001;segsel=houH; end 3'b001:begin a=8'b00000010;segsel=houL; end3'b010:begin a=8'b00000100;segsel=x; end3'b011:begin a=8'b00001000;segsel=minH; end 3'b100:begin a=8'b00010000;segsel=minL; end3'b101:begin a=8'b00100000;segsel=x; end3'b110:begin a=8'b01000000;segsel=secH; end3'b111:begin a=8'b10000000;segsel=secL; endendcasecase(segsel)//循环显示4'b0000:b=8'b00111111;4'b0001:b=8'b00000110;4'b0010:b=8'b01011011;4'b0011:b=8'b01001111;4'b0100:b=8'b01100110;4'b0101:b=8'b01101101;4'b0110:b=8'b01111101;4'b0111:b=8'b00000111;4'b1000:b=8'b01111111;4'b1001:b=8'b01101111;4'b1010:b=8'b01000000;endcaseendendmodule二、仿真结果:三、硬件结果:。

Verilog HDL实现数字钟 西交

数字钟设计程序代码`timescale 1ns / 1ps////////////////////////////////////////////////////////////////////////////////// // Company:// Engineer://// Create Date: 10:05:58 05/07/2016// Design Name:// Module Name: shuzizhong// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments:////////////////////////////////////////////////////////////////////////////////////module shuzizhong(input wire clk,input wire clr,input [2:0] button,input wire Adjust,input wire Counter,output Second_Flash,output LED_Counter,output LED_Adjust,output reg[6:0] a_to_g,output reg[3:0] an);模块变量声明时钟,清零,按键,校时reg[3:0] LED0_num,LED1_num,LED2_num,LED3_num;reg[1:0] s;reg[3:0] digit;reg[16:0] clkdiv;reg[100:0] q1;reg sec;reg[3:0]Minute_L;reg[3:0]Minute_H;reg[3:0]hour_L;reg[3:0]hour_H;reg[5:0]n;reg[3:0]M_L;reg[3:0]M_H;reg[3:0]h_L;reg[3:0]h_H;reg[3:0]CM_L;reg[3:0]CM_H;reg[3:0]Ch_L;reg[3:0]Ch_H;初始化initial beginMinute_L=0;Minute_H=0;hour_L=0;hour_H=0;LED3_num=Minute_L;LED2_num=Minute_H;LED1_num=hour_L;LED0_num=hour_H;M_L=0;M_H=0;h_L=0;h_H=0;n=0;CM_L=0;CM_H=0;Ch_L=0;Ch_H=0;end数码管显示always@(*)beginan=4'b1111;s<=clkdiv[16:15];an[s]=0;case(s)0:digit<=LED0_num[3:0];1:digit<=LED1_num[3:0];2:digit<=LED2_num[3:0];3:digit<=LED3_num[3:0];default:digit<=LED3_num[3:0];endcasecase(digit)0:a_to_g=7'b0000001;1:a_to_g=7'b1001111;2:a_to_g=7'b0010010;3:a_to_g=7'b0000110;4:a_to_g=7'b1001100;5:a_to_g=7'b0100100;6:a_to_g=7'b0100000;7:a_to_g=7'b0001111;8:a_to_g=7'b0000000;9:a_to_g=7'b0000100;'hA:a_to_g=7'b0001000;'hB:a_to_g=7'b1100000;'hC:a_to_g=7'b0110001;'hD:a_to_g=7'b1000010;'hE:a_to_g=7'b0110000;'hF:a_to_g=7'b0111000;default:a_to_g=7'b0000001;endcaseendalways@(posedgeclk)beginclkdiv<=clkdiv+1;end判断校时功能是否打开,如果是则显示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

module digclk(clk,en,rst,dula,wela,s1,s2,s3,led,flag1,start1,flag2,start2,aled,s6,s4,s5); //s1调时s2调分s3调秒wela位码dula段码en使能clk时钟,flag1是跑表标志(拨上去就是显示跑表),置一为跑表功能,start1为跑表开始停止//flag2为闹钟标志(拨上去就是设置闹钟时间)start2为闹钟开关aled闹钟提示灯input clk,rst,en,s1,s2,s3,flag1,start1,flag2,start2,s6,s4,s5;output [2:0] wela;output [7:0] dula;output led;output aled;reg led;reg aled;reg [7:0] cnt,dula;reg [2:0] wela;reg[7:0] hourh,hourl,minh,minl,sech,secl;reg[7:0] phourh,phourl,pminh,pminl,psech,psecl;reg[7:0] ahourh,ahourl,aminh,aminl,asech,asecl;reg[3:0] a; //a用于数码管显示的临时变量(* synthesis, keep *) reg clk1;always @(posedge clk1)beginif(start2)beginif(hourh==ahourh&&hourl==ahourl&&minh==aminh&&minl==aminl&&sech==asech&&secl ==asecl) aled=1'b1;else aled=1'b0;endendalways @(posedge clk1) //闹钟功能beginif(flag2)beginif(!s4) //调节小时begin/*if(ahourl==9)begin ahourl<=0;ahourh<=ahourh+1;endif(ahourh==2&&ahourl==3)begin ahourh<=0;ahourl<=0; endelse ahourl<=ahourl+1;*/ahourl<=ahourl+1;if(ahourl==3&&ahourh==2)begin ahourl<=0;ahourh<=0;endif(ahourl==9) begin ahourl<=0;ahourh<=ahourh+1;end;endelse if(!s5) //调节分钟beginif(aminl==9)beginaminl<=0;if(aminh==5) aminh<=0;else aminh<=aminh+1;endelse aminl<=aminl+1;endelse if(!s6) //调节秒钟(调节都是在暂停的前提下)beginif(asecl==9)beginasecl<=0;if(asech==5) asech<=0;else asech<=asech+1;endelse asecl<=asecl+1;endendendalways @(posedge clk1)//用于跑表beginif(flag1&&start1)beginif(psecl==9) //时钟正常跳动状态beginpsecl<=0;if(psech==5)beginpsech<=0;if(pminl==9)beginpminl<=0;if(pminh==5)beginpminh<=0;if(phourl==9) beginphourl<=0;phourh<=phourh+1;endelse if(phourh==2&&phourl==3) begin phourl<=0; phourh<=0;endelse phourl<=phourl+1;endelse pminh<=pminh+1;endelse pminl<=pminl+1;endelse psech<=psech+1;endelse psecl<=psecl+1;endelse if(!flag1) begin psecl<=0;psech<=0;pminl<=0;pminh<=0;phourl<=0;phourh<=0; end endalways @(posedge clk)//用于分频begincnt=cnt+1;if(cnt==200) begin clk1=1'b1; cnt=0; endelse clk1=1'b0; //200分频,CLK为数码管扫描频率,CLK1为计数频率if(wela<7) wela=wela+1; else wela=0;endalways @(posedge clk1)//整点报时beginif(minh==0&&minl==0&&sech==0&&secl==0) led=1'b1;else led=1'b0;endalways @(posedge clk1 or negedge rst) //这里负责处理使能和复位暂停调时使能处于开的时候则是正常显示beginif(!rst) begin secl<=0;sech<=0;minl<=0;minh<=0;hourl<=0;hourh<=0; endelse if(!en) //时钟暂停,开始调时beginif(!s1) //调节小时begin/*if(hourh==2&&hourl==4)begin hourl<=0;hourh<=0; endelse if(hourl==9)begin hourl<=0;hourh<=hourh+1;endelse hourl<=hourl+1;*/hourl<=hourl+1;if(hourl==3&&hourh==2)begin hourl<=0;hourh<=0;endif(hourl==9) begin hourl<=0;hourh<=hourh+1;end;endelse if(!s2) //调节分钟beginif(minl==9)beginminl<=0;if(minh==5) minh<=0;else minh<=minh+1;endelse minl<=minl+1;endelse if(!s3) //调节秒钟(调节都是在暂停的前提下)beginif(secl==9)beginsecl<=0;if(sech==5) sech<=0;else sech=sech+1;endelse secl<=secl+1;endendelse if(secl==9) //时钟正常跳动状态beginsecl<=0;if(sech==5)beginsech<=0;if(minl==9)beginminl<=0;if(minh==5)beginminh<=0;if(hourl==9) begin hourl<=0;hourh<=hourh+1;endelse if(hourh==2&&hourl==3) begin hourl<=0; hourh<=0;endelse hourl<=hourl+1;endelse minh<=minh+1;endelse minl<=minl+1;endelse sech<=sech+1;endelse secl<=secl+1;endalways @(wela)//用于数码管显示beginif(flag1&&!flag2)begincase(wela)0:a=phourh;1:a=phourl;2:a=12;3:a=pminh;4:a=pminl;5:a=12;6:a=psech;7:a=psecl;default: a=0;endcasecase(a)0:dula<=8'b00111111; 1:dula<=8'b00000110;2:dula<=8'b01011011; 3:dula<=8'b01001111;4:dula<=8'b01100110; 5:dula<=8'b01101101;6:dula<=8'b01111101; 7:dula<=8'b00000111;8:dula<=8'b01111111; 9:dula<=8'b01101111; //8段译码值是倒着看的12:dula<=8'b01000000;default:dula<=8'b11111111;endcaseendelse if(flag2&&!flag1)begincase(wela)0:a=ahourh;1:a=ahourl;2:a=12;3:a=aminh;4:a=aminl;5:a=12;6:a=asech;7:a=asecl;default: a=0;endcasecase(a)0:dula<=8'b00111111; 1:dula<=8'b00000110;2:dula<=8'b01011011; 3:dula<=8'b01001111;4:dula<=8'b01100110; 5:dula<=8'b01101101;6:dula<=8'b01111101; 7:dula<=8'b00000111;8:dula<=8'b01111111; 9:dula<=8'b01101111; //8段译码值12:dula<=8'b01000000;default:dula<=8'b11111111;endcaseendelsebegincase(wela)0:a=hourh;1:a=hourl;2:a=12;3:a=minh;4:a=minl;5:a=12;6:a=sech;7:a=secl;default: a=0;endcasecase(a)0:dula<=8'b00111111; 1:dula<=8'b00000110;2:dula<=8'b01011011; 3:dula<=8'b01001111;4:dula<=8'b01100110; 5:dula<=8'b01101101;6:dula<=8'b01111101; 7:dula<=8'b00000111;8:dula<=8'b01111111; 9:dula<=8'b01101111; //8段译码值12:dula<=8'b01000000;default:dula<=8'b11111111;endcaseendendendmodule。