FM25L256铁电存储器数据手册pdf

铁电存储器在仪表中的应用

摘要:FRAM是一种新型存贮器,最大特点是可以随总线速度无限次的擦写,而且功耗低。

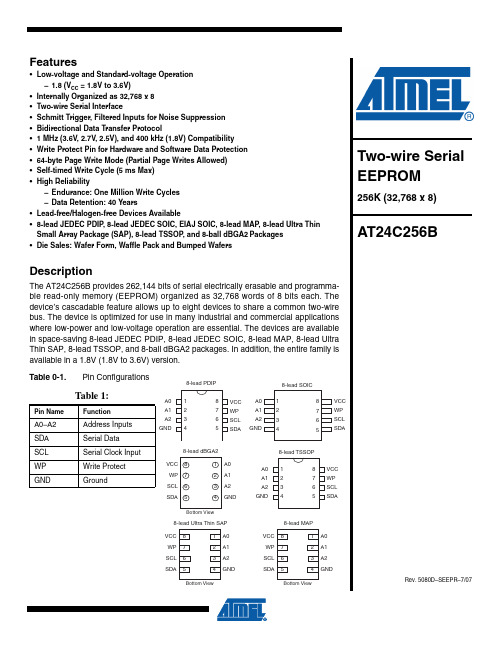

FRAM 性能优越于EEPROMAT24C256。

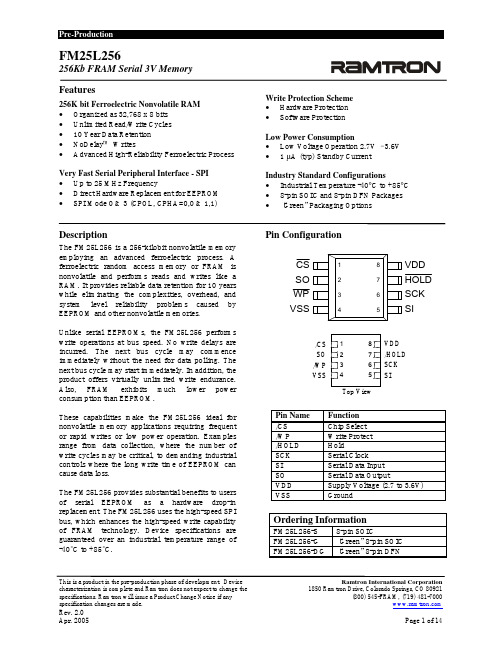

关键词:存贮器;FM24C256;AT24C256;EEPROM一.概述:FRAM是最近几年由RAMTRON公司研制的新型存贮器,它的核心技术是铁电晶体材料,拥有随即存取记忆体和非易失性存贮产品的特性。

FM24C256是一种铁电存贮器(FRAM),容量为256KBIT存贮器,它和AT24C256容量等同,总线结构兼容,但FM24C256的性能指标远大于AT24C256。

在存贮器领域中,FM24C256应用逐渐被推广和认可,尤其是大容量存贮器,它的优良特性远高于同等容量的EEPROM。

在电子式电能表行业中,数据安全保存是最重要的。

随着电子表功能的发展,保存的数据量越来越大,这就需要大容量的存储器,而大容量的EEPROM性能指标不是很高,尤其是擦写次数和速度影响电能表自身的质量。

FM24C256在电能表中的使用,会提高电能表的数据安全存贮特性。

二.铁电存贮器(FRAM)FM24C256的特性:传统半导体记忆体有两大体系:易失性记忆体(volatilememory)和非易失性记忆体(non-volatilememory)。

易失性记忆体像SRAM和DRAM在没有电源的情况下都不能保存数据。

但这种存贮器拥有高性能、易用等优点。

非易失性记忆体像EPROM,EEPROM和FLASH能在断电后仍保存数据。

但由于所有这些记忆体均起源自ROM技术,所以不难想象得到他们都有不易写入的缺点:写入缓慢、读写次数低、写入时工耗大等。

FM24C256是一个256Kbit的FRAM,总线频率最高可达1MHz,10亿次以上的读写次数,工耗低。

与典型的EEPROMAT24C256相比较,FM24C256可跟随总线速度写入,无须等待时间,而AT24C256必须等待几毫秒(ms)才能进行下一步写操作。

FM24C256可读写10亿次以上,几乎无限次读写。

fm25256

This is a product in the pre-production phase of development. Device Ramtron International Corporationcharacterization is complete and Ramtron does not expect to change the 1850 Ramtron Drive, Colorado Springs, CO 80921FM25256256Kb FRAM Serial 5V MemoryFeatures256K bit Ferroelectric Nonvolatile RAM • Organized as 32,768 x 8 bits • Unlimited Read/Write Cycles • 10 Year Data Retention • NoDelay™ Writes• Advanced High-Reliability Ferroelectric ProcessVery Fast Serial Peripheral Interface - SPI • Up to 25 MHz Frequency• Direct Hardware Replacement for EEPROM • SPI Mode 0 & 3 (CPOL, CPHA=0,0 & 1,1)Write Protection Scheme • Hardware Protection • Software ProtectionWide Operating Range• Wide Voltage Operation 4.0V – 5.5VIndustry Standard Configurations• Industrial Temperature -40°C to +85°C •8-pin SOIC (-S)• “Green” 8-pin SOIC (-G)DescriptionThe FM25256 is a 256-kilobit nonvolatile memory employing an advanced ferroelectric process. A ferroelectric random access memory or FRAM is nonvolatile and performs reads and writes like a RAM. It provides reliable data retention for 10 years while eliminating the complexities, overhead, and system level reliability problems caused by EEPROM and other nonvolatile memories.Unlike serial EEPROMs, the FM25256 performs write operations at bus speed. No write delays are incurred. The next bus cycle may commence immediately without the need for data polling. The next bus cycle may start immediately. In addition, the product offers virtually unlimited write endurance. Also, FRAM exhibits much lower power consumption than EEPROM.These capabilities make the FM25256 ideal for nonvolatile memory applications requiring frequent or rapid writes or low power operation. Examples range from data collection, where the number of write cycles may be critical, to demanding industrial controls where the long write time of EEPROM can cause data loss.The FM25256 provides substantial benefits to users of serial EEPROM as a hardware drop-in replacement. The FM25256 uses the high-speed SPI bus, which enhances the high-speed write capability of FRAM technology. Device specifications are guaranteed over an industrial temperature range of -40°C to +85°C.Pin ConfigurationPin Name Function/CS Chip Select /WP Write Protect /HOLD Hold SCK Serial Clock SI Serial Data Input SO Serial Data Output VDD Supply Voltage (4.0 to 5.5V) VSS GroundOrdering InformationFM25256-S 8-pin SOIC FM25256-G “Green” 8-pin SOICFigure 1. Block DiagramPin DescriptionsPin Name I/O Description/CS Input Chip Select: This active low input activates the device. When high, the device enters low-power standby mode, ignores other inputs, and all outputs are tri-stated. Whenlow, the device internally activates the SCK signal. A falling edge on /CS must occurprior to every op-code.SCK Input Serial Clock: All I/O activity is synchronized to the serial clock. Inputs are latched on the rising edge and outputs occur on the falling edge. Since the device is static, theclock frequency may be any value between 0 and 25 MHz and may be interrupted atany time./HOLD Input Hold: The /HOLD pin is used when the host CPU must interrupt a memory operation for another task. When /HOLD is low, the current operation is suspended. The deviceignores any transition on SCK or /CS. All transitions on /HOLD must occur whileSCK is low./WP Input Write Protect: This active low pin prevents write operations to the status register only.A complete explanation of write protection is provided on pages 6 and 7.SI Input Serial Input: All data is input to the device on this pin. The pin is sampled on the rising edge of SCK and is ignored at other times. It should always be driven to a validlogic level to meet I DD specifications.* SI may be connected to SO for a single pin data interface.SO Output Serial Output: This is the data output pin. It is driven during a read and remains tri-stated at all other times including when /HOLD is low. Data transitions are driven onthe falling edge of the serial clock.* SO may be connected to SI for a single pin data interface.VDD Supply Power Supply (4.0V to 5.5V)GroundVSS SupplyOverviewThe FM25256 is a serial FRAM memory. The memory array is logically organized as 32,768 x 8 and is accessed using an industry standard Serial Peripheral Interface or SPI bus. Functional operation of the FRAM is similar to serial EEPROMs. The major difference between the FM25256 and a serial EEPROM with the same pinout is the FRAM’s superior write performance and power consumption. Memory ArchitectureWhen accessing the FM25256, the user addresses 32K locations of 8 data bits each. These data bits are shifted serially. The addresses are accessed using the SPI protocol, which includes a chip select (to permit multiple devices on the bus), an op-code, and a two-byte address. The upper bit of the address range is a “don’t care” value. The complete address of 15-bits specifies each byte address uniquely.Most functions of the FM25256 either are controlled by the SPI interface or are handled automatically by on-board circuitry. The access time for memory operation is essentially zero, beyond the time needed for the serial protocol. That is, the memory is read or written at the speed of the SPI bus. Unlike an EEPROM, it is not necessary to poll the device for a ready condition since writes occur at bus speed. So, by the time a new bus transaction can be shifted into the device, a write operation will be complete. This is explained in more detail in the interface section. Users expect several obvious system benefits from the FM25256 due to its fast write cycle and high endurance as compared to EEPROM. In addition there are less obvious benefits as well. For example in a high noise environment, the fast-write operation is less susceptible to corruption than an EEPROM since it is completed quickly. By contrast, an EEPROM requiring milliseconds to write is vulnerable to noise during much of the cycle.Note that the FM25256 contains no power management circuits other than a simple internal power-on reset. It is the user’s responsibility to ensure that V DD is within datasheet tolerances to prevent incorrect operation. It is recommended that the part is not powered down with chip enable active.Serial Peripheral Interface – SPI BusThe FM25256 employs a Serial Peripheral Interface (SPI) bus. It is specified to operate at speeds up to 25 MHz. This high-speed serial bus provides high performance serial communication to a host microcontroller. Many common microcontrollers have hardware SPI ports allowing a direct interface. It is quite simple to emulate the port using ordinary port pins for microcontrollers that do not. The FM25256 operates in SPI Mode 0 and 3.The SPI interface uses a total of four pins: clock, data-in, data-out, and chip select. A typical system configuration uses one or more FM25256 devices with a microcontroller that has a dedicated SPI port, as Figure 2 illustrates. Note that the clock, data-in, and data-out pins are common among all devices. The Chip Select and Hold pins must be driven separately for each FM25256 device.For a microcontroller that has no dedicated SPI bus, a general purpose port may be used. To reduce hardware resources on the controller, it is possible to connect the two data pins together and tie off the Hold pin. Figure 3 shows a configuration that uses only three pins.Protocol OverviewThe SPI interface is a synchronous serial interface using clock and data pins. It is intended to support multiple devices on the bus. Each device is activated using a chip select. Once chip select is activated by the bus master, the FM25256 will begin monitoring the clock and data lines. The relationship between the falling edge of /CS, the clock and data is dictated by the SPI mode. The device will make a determination of the SPI mode on the falling edge of each chip select. While there are four such modes, the FM25256 supports only modes 0 and 3. Figure 4 shows the required signal relationships for modes 0 and 3. For both modes, data is clocked into the FM25256 on the rising edge of SCK and data is expected on the first rising edge after /CS goes active. If the clock starts from a high state, it will fall prior to the first data transfer in order to create the first rising edge.The SPI protocol is controlled by op-codes. These op-codes specify the commands to the device. After /CS is activated the first byte transferred from the bus master is the op-code. Following the op-code, any addresses and data are then transferred. Note that the WREN and WRDI op-codes are commands with no subsequent data transfer.Important: The /CS must go inactive after an operation is complete and before a new op-code can be issued. There is one valid op-code only per active chip select.SS : Slave SelectFigure 2. System Configuration with SPI portFigure 3. System Configuration without SPI portSPI Mode 0: CPOL=0, CPHA=0SPI Mode 3: CPOL=1, CPHA=1Figure 4. SPI Modes 0 & 3Power Up to First AccessThe FM25256 is not accessible for a period of time (10 ms) after power up. Users must comply with the timing parameter t PU , which is the minimum time from V DD (min) to the first /CS low.Data TransferAll data transfers to and from the FM25256 occur in 8-bit groups. They are synchronized to the clock signal (SCK), and they transfer most significant bit (MSB) first. Serial inputs are registered on the rising edge of SCK. Outputs are driven from the falling edge of SCK.Command StructureThere are six commands called op-codes that can be issued by the bus master to the FM25256. They are listed in the table below. These op-codes control the functions performed by the memory. They can be divided into three categories. First, there are commands that have no subsequent operations. They perform a single function such as to enable a write operation. Second are commands followed by one byte, either in or out. They operate on the status register. The third group includes commands for memory transactions followed by address and one or more bytes of data.Table 1. Op-code Commands Name Description Op-codeWREN Set Write Enable Latch00000110b WRDIWrite Disable 0000 0100b RDSRRead Status Register 0000 0101b WRSRWrite Status Register 0000 0001b READRead Memory Data 0000 0011b WRITE Write Memory Data 0000 0010bWREN - Set Write Enable LatchThe FM25256 will power up with writes disabled. The WREN command must be issued prior to any write operation. Sending the WREN op-code will allow the user to issue subsequent op-codes for write operations. These include writing the status register and writing the memory.Sending the WREN op-code causes the internal Write Enable Latch to be set. A flag bit in the status register, called WEL, indicates the state of the latch. WEL=1 indicates that writes are permitted. Attempting to write the WEL bit in the status register has no effect on the state of this bit. Completing any write operation will automatically clear the write-enable latch and prevent further writes without another WREN command. Figure 5 illustrates the WREN command bus configuration.WRDI - Write DisableThe WRDI command disables all write activity by clearing the Write Enable Latch. The user can verify that writes are disabled by reading the WEL bit in the status register and verifying that WEL=0. Figure 6 illustrates the WRDI command bus configuration.Hi-Z0 1 2 3 4 5 6 7CSSCKSI SOFigure 5. WREN Bus ConfigurationCSSCKSI SO0 1 2 3 4 5 6 7Figure 6. WRDI Bus ConfigurationRDSR - Read Status RegisterThe RDSR command allows the bus master to verify the contents of the Status register. Reading Status provides information about the current state of the write protection features. Following the RDSR op-code, the FM25256 will return one byte with the contents of the Status register. The Status register is described in detail in a later section. WRSR – Write Status RegisterThe WRSR command allows the user to select certain write protection features by writing a byte to the Status register. Prior to issuing a WRSR command, the /WP pin must be high or inactive. Prior to sending the WRSR command, the user must send a WREN command to enable writes. Note that executing a WRSR command is a write operation and therefore clears the Write Enable Latch.Figure 7. RDSR Bus ConfigurationFigure 8. WRSR Bus ConfigurationStatus Register & Write ProtectionThe write protection features of the FM25256 are multi-tiered. Taking the /WP pin to a logic low state is the hardware write protect function. All write operations are blocked when /WP is low. To write the memory with /WP high, a WREN op-code must first be issued. Assuming that writes are enabled using WREN and by /WP, writes to memory are controlled by the Status register. As described above, writes to the status register are performed using the WRSR command and subject to the /WP pin. The Status register is organized as follows.Table 2. Status RegisterBit 76 5 4 321 0NameWPEN 0 0 0 BP1BP0 WEL 0Bits 0 and 4-6 are fixed at 0 and cannot be modified. Note that bit 0 (Ready in EEPROMs) is unnecessary as the FRAM writes in real-time and is never busy. The BP1 and BP0 control software write protection features. They are nonvolatile (shaded yellow). The WEL flag indicates the state of the Write Enable Latch. Attempting to directly write the WEL bit in the status register has no effect on its state. This bit is internally set by the WREN command and clearedby terminating a write cycle (/CS high) or by using the WRDI command.BP1 and BP0 are memory block write protection bits. They specify portions of memory that are write protected as shown in the following table.Table 3. Block Memory Write ProtectionBP1 BP0 Protected Address Range0 0 None0 1 6000h to 7FFFh (upper ¼)1 0 4000h to 7FFFh (upper ½)1 1 0000h to 7FFFh (all)The BP1 and BP0 bits and the Write Enable Latch are the only mechanisms that protect the memory from writes. The remaining write protection features protect inadvertent changes to the block protect bits. The WPEN bit controls the effect of the hardware /WP pin. When WPEN is low, the /WP pin is ignored. When WPEN is high, the /WP pin controls write access to the status register. Thus the Status register is write protected if WPEN=1 and /WP=0. This scheme provides a write protection mechanism, which can prevent software from writing the memory under any circumstances. This occurs if the BP1 and BP0 are set to 1, the WPEN bit is set to 1, and /WP is set to 0. This occurs because the block protect bits prevent writing memory and the /WP signal in hardware prevents altering the block protect bits (if WPEN is high). Therefore in this condition, hardware must be involved in allowing a write operation. The following table summarizes the write protection conditions.Table 4. Write ProtectionWEL WPEN /WP Protected Blocks Unprotected Blocks Status RegisterXXProtected Protected Protected1 0 XProtected Unprotected Unprotected1 1 0Protected Unprotected Protected1 1 1Protected Unprotected UnprotectedMemory OperationThe SPI interface, which is capable of a relatively high clock frequency, highlights the fast write capability of the FRAM technology. Unlike SPI-bus EEPROMs, the FM25256 can perform sequential writes at bus speed. No page register is needed and any number of sequential writes may be performed. Write OperationAll writes to the memory array begin with a WREN op-code. The next op-code is the WRITE instruction. This op-code is followed by a two-byte address value. The upper bit of the address is a “don’t care”. In total, 15-bits specify the address of the first data byte of the write operation. Subsequent bytes are data and they are written sequentially. Addresses are incremented internally as long as the bus master continues to issue clocks. If the last address of 7FFFh is reached, the counter will roll over to 0000h. Data is written MSB first. A write operation is shown in Figure 9.Unlike EEPROMs, any number of bytes can be written sequentially and each byte is written to memory immediately after it is clocked in (after the 8th clock). The rising edge of /CS terminates a WRITE op-code operation. Asserting /WP active in the middle of a write operation will have no effect until the next falling edge of /CS.Read OperationAfter the falling edge of /CS, the bus master can issue a READ op-code. Following this instruction is a two-byte address value. The upper bit of the address is a don’t care. In total, 15-bits specify the address of the first byte of the read operation. After the op-code and address are complete, the SI line is ignored. The bus master issues 8 clocks, with one bit read out for each. Addresses are incremented internally as long as the bus master continues to issue clocks. If the last address of 7FFFh is reached, the counter will roll over to 0000h. Data is read MSB first. The rising edge of /CS terminates a READ op-code operation.A read operation is shown in Figure 10.HoldThe /HOLD pin can be used to interrupt a serial operation without aborting it. If the bus master pulls the /HOLD pin low while SCK is low, the current operation will pause. Taking the /HOLD pin high while SCK is low will resume an operation. The transitions of /HOLD must occur while SCK is low, but the SCK and /CS pins can toggle during a hold state.Figure 9. Memory WriteFigure 10. Memory ReadElectrical SpecificationsAbsolute Maximum RatingsSymbol Description Ratings V DD Power Supply Voltage with respect to V SS-1.0V to +7.0VV IN Voltage on any pin with respect to V SS-1.0V to +7.0Vand V IN < V DD+1.0V T STG StorageTemperature -55°C to + 125°C T LEAD Lead Temperature (Soldering, 10 seconds) 300° CV ESD Electrostatic Discharge Voltage- Human Body Model (JEDEC Std JESD22-A114-B)- Charged Device Model (JEDEC Std JESD22-C101-A) - Machine Model (JEDEC Std JESD22-A115-A)3kV 1kV 100VPackage Moisture Sensitivity Level MSL-1Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stressrating only, and the functional operation of the device at these or any other conditions above those listed in the operationalsection of this specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affectdevice reliability.DC Operating Conditions(T A = -40°C to + 85°C, V DD = 4.0V to 5.5V unless otherwise specified)Symbol Parameter MinTypMaxUnitsNotes V DD Power Supply Voltage 4.0 - 5.5 VI DD Power Supply Current@ SCK = 1.0 MHz @ SCK = 5.0 MHz @ SCK = 25.0 MHz ---0.81.87.0mA 1I SB StandbyCurrent - 150 µA 2 I LI InputLeakageCurrent - ±1 µA 3 I LO Output Leakage Current - ±1 µA 3 V IH Input High Voltage 0.7 V DD V DD + 0.5 VV IL Input Low Voltage -0.3 0.3 V DD VV OH Output High Voltage@ I OH = -2 mAV DD – 0.8 - VV OL Output Low Voltage@ I OL = 2 mA - 0.4VV HYS Input Hysteresis 0.05 V DD- V 4 Notes1. SCK toggling between V DD-0.3V and V SS, other inputs V SS or V DD-0.3V.2. SCK = SI = /CS=V DD. All inputs V SS or V DD.3. V SS≤ V IN≤ V DD and V SS≤ V OUT≤ V DD.4. This parameter is characterized but not 100% tested.AC Parameters (T A = -40°C to + 85°C, V DD = 4.0V to 5.5V, C L = 30pF)Symbol Parameter Min Max Units Notesf CK SCK Clock Frequency 0 25 MHzt CH Clock High Time 18 ns 1LowTime 18 ns 1t CL Clockt CSU Chip Select Setup 10 nst CSH Chip Select Hold 10 nst OD Output Disable Time 15 ns 2t ODV Output Data Valid Time 15 nst OH Output Hold Time 0 nsTime 60 nst D Deselectt R Data In Rise Time 50 ns 1,3t F Data In Fall Time 50 ns 1,3t SU Data Setup Time 5 nst H Data Hold Time 5 nst HS/Hold Setup Time 10 nsTime 10 nst HH /HoldHoldt HZ/Hold Low to Hi-Z 20 ns 2t LZ/Hold High to Data Active 15 ns 2Notes1.t CH + t CL = 1/f CK.2.This parameter is characterized but not 100% tested.3.Rise and fall times measured between 10% and 90% of waveform.Power Cycle Timing (T A = -40° C to + 85° C, V DD = 4.0V to 5.5V)NotesUnitsSymbol Parameter MinMaxt PU Power Up (V DD min) to First Access (/CS low) 10 - mst PD Last Access (/CS high) to Power Down (V DD min) 0 - µst VR V DD Rise Time 50 µs/V 1,2t VF V DD Fall Time 100 - µs/V 1,2Capacitance (T A = 25° C, f=1.0 MHz, V DD = 5.0V)UnitsNotesMaxSymbol Parameter MinC O Output capacitance (SO) - 8 pF 1capacitance - 6 pF 1C I InputNotes1. This parameter is characterized and not 100% tested.2. Slope measured at any point on V DD waveform.AC Test ConditionsInput Pulse Levels 10% and 90% of V DDInput rise and fall times 5 nsInput and output timing levels 0.5 V DDOutput Load Capacitance 30 pFSerial Data Bus Timing/Hold TimingPower Cycle TimingV DDCSData Retention (V DD = 4.0V to 5.5V)Parameter Min Max Units NotesData Retention 10 - YearsMechanical Drawing8-pin SOIC (JEDEC MS-012 variation AA)Refer to JEDEC MS-012 for complete dimensions and notes.All dimensions in millimeters.Revision HistoryRevision Date Summary 0.1 9/9/03 Initial release. 0.11 12/9/03 Reduced I DD spec limits. 0.12 1/7/04 Added t VR spec, “green” package, and modified Power Cycling diagram. 0.13 4/28/04 Changed t OD , t ODV , and t LZ timing specs. Changed t VR and t VF conditions. 1.0 8/16/04 Changed V DD range in AC Parameters table. Changed I DD limits. Addedpackage marking scheme. Changed t ODV spec. New rev. number to comply with new scheme.1.1 3/14/05 New part number FM25256 replaces FM25W256 since operating voltage isno longer wide (2.7V – 5.5V). Added note about powering down with /CS active (pg 3). Added ESD and package MSL ratings. Changed I SB spec.2.0 4/5/05 Changed to Pre-Production status.。

MSP430 与FM25L256 铁电存储器SPI接口 原理与实现

SPI1Rxflg 变量为 1,就表示一个字节已经接收完毕。详细实现如下:

unsigned char RxTxSPI1(unsigned char c)

{

while(!(U1TCTL & TXEPT));

SPI1Rxflg=0;

TXBUF1=c;

网页: 电子邮件:xz_y2k@ 电话:0512-51621677 QQ:373506171 技术支持 QQ 群:13872234

始,下表示所有这些操作的代码:

名称

描述

操作码

WREN 设置写操作允许,每次写操作(写存储器数据或者状态寄存器)时,都必 0000 0110b 须首先使用这个命令,执行这个命令后,状态寄存器中WEL位被设置为1。

WRDI

写操作不允许,在每次写操作完成后,器件会自动改变为写操作不允许, 0000 0100b 用户也可使用这个命令,设置写操作不允许。执行这个命令后,状态寄存 器中的WEL位被清除。

2.3

FM25L256 的 SPI 通信..................................................................................................6

2.3.1 FM25L256 的访问操作..........................................................................................6

UTCTL1=SSEL1+STC;

//选择 SMCLK 为 SPI 时钟源

UBR11=0; UBR01=8;

//SPI 时钟频率为 1M @ 外部 8 MHz 晶振

FM25F02.04使用说明手册

FM25F04/02使用手册1.产品概述FM25F04/02为4M/2M位的串行Flash存储器,内部组织为524,288个字节(FM25F04)/262144个字节(FM25F02),另外还有一个256字节的OTP扇区,每个字节8位。

芯片接口为兼容SPI协议(模式3/0)的串行接口总线,广泛应用于消费类电子市场。

主要用于存储固件和配置、设置信息。

产品的基本性能如下:✧工作电压:2.3V - 3.6V✧统一扇区架构:-128个4-Kbyte扇区(FM25F04),64个4-Kbyte扇区(FM25F02)-8个64K-byte区块(FM25F04),4个64K-byte区块(FM25F02)-任意扇区或区块都可以被单独擦除✧可锁定的256 byte OTP安全扇区✧SPI串行接口(模式0及模式3)✧支持Dual Output Fast Read操作✧支持Dual I/O Fast Read操作,在此操作下也支持Continuous Read✧支持软/硬件写保护✧支持256字节页编程模式Manu ID:A1JEDEC ID:A13112(FM25F02),A13113(FM25F04)2.引脚定义FM25F04/023.直流参数(TA=-40℃~85℃,Vcc=2.3V~3.6V)f CLK=100MHZ时CL=20 pF, f CLK=75MHZ时CL=30 pF5.上电时序上电时序及写禁止电压FM25F04/02状态寄存器定义注意:1.在OTP模式下,SRP位定义为OTP_LOCK位2.见"保护区域表”7.操作命令说明所有的命令、地址和数据都是移位进出芯片,最高位(MSB)在第一位。

DI在CS#为低后的第一个CLK的上升沿被采样,之后,一字节的命令码必须被移位输入芯片,最高位在第一位,每位都在时钟的上升沿被采样。

下表列出了命令集。

每种命令序列都由一个单字节命令码开始。

根据不同的命令,后面跟随的可能是地址字节或数据字节,或什么都不跟。

M95128.M95256--128k.256K存储芯片手册免费下载

1/39October 2004M95256M95128256Kbit and 128Kbit Serial SPI Bus EEPROMWith High Speed ClockFEATURES SUMMARY■Compatible with SPI Bus Serial Interface (Positive Clock SPI Modes)■Single Supply Voltage:– 4.5 to 5.5V for M95xxx – 2.5 to 5.5V for M95xxx-W – 1.8 to 5.5V for M95xxx-R ■High Speed–10MHz Clock Rate, 5ms Write Time ■Status Register■Hardware Protection of the Status Register ■BYTE and PAGE WRITE (up to 64 Bytes)■Self-Timed Programming Cycle■Adjustable Size Read-Only EEPROM Area ■Enhanced ESD Protection■More than 100000 Erase/Write Cycles ■More than 40-Year Data RetentionTable 1. Product ListReferencePart NumberM95256M95256M95256-W M95256-R M95128M95128M95128-W M95128-RM95256, M95128TABLE OF CONTENTSFEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1Table 1.Product List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Figure 1.Packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Figure 2.Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Figure 3.DIP, SO and TSSOP Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Table 2.Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5SIGNAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6Serial Data Output (Q). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Serial Data Input (D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Serial Clock (C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Chip Select (S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Hold (HOLD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Write Protect (W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6CONNECTING TO THE SPI BUS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7Figure 4.Bus Master and Memory Devices on the SPI Bus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 SPI Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Figure 5.SPI Modes Supported . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8OPERATING FEATURES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9Power-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 Power On Reset: VCC Lock-Out Write Protect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 Power-down. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 Active Power and Standby Power Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 Hold Condition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 Figure 6.Hold Condition Activation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 WIP bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 WEL bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 BP1, BP0 bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 SRWD bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Table 3.Status Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Data Protection and Protocol Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Table 4.Write-Protected Block Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10MEMORY ORGANIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Figure 7.Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12Table 5.Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 Write Enable (WREN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 Figure 8.Write Enable (WREN) Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132/39M95256, M95128Write Disable (WRDI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 Figure 9.Write Disable (WRDI) Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 Read Status Register (RDSR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 WIP bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 WEL bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 BP1, BP0 bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 SRWD bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Figure 10.Read Status Register (RDSR) Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Write Status Register (WRSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Table 6.Protection Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Figure 11.Write Status Register (WRSR) Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 Read from Memory Array (READ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17 Figure 12.Read from Memory Array (READ) Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17 Write to Memory Array (WRITE). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18 Figure 13.Byte Write (WRITE) Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18 Figure 14.Page Write (WRITE) Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19POWER-UP AND DELIVERY STATE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20Power-up State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20 Initial Delivery State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21 Table 7.Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21DC AND AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22Table 8.Operating Conditions (M95xxx). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22 Table 9.Operating Conditions (M95xxx-W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22 Table 10.Operating Conditions (M95xxx-R). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22 Table 11.AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 Figure 15.AC Measurement I/O Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 Table 12.Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 Table 13.DC Characteristics (M95xxx, Device Grade 6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24 Table 14.DC Characteristics (M95xxx, Device Grade 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24 Table 15.DC Characteristics (M95xxx-W, Device Grade 6). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24 Table 16.DC Characteristics (M95xxx-W, Device Grade 3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25 Table 17.DC Characteristics (M95xxx-R). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25 Table 18.AC Characteristics (M95xxx, Device Grade 6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26 Table 19.AC Characteristics (M95xxx, Device Grade 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 Table 20.AC Characteristics (M95xxx-W, Device Grade 6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Table 21.AC Characteristics (M95xxx-W, Device Grade 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29 Table 22.AC Characteristics (M95xxx-R). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30 Figure 16.Serial Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31 Figure 17.Hold Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31 Figure 18.Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .333/39M95256, M951284/39Figure 19.PDIP8 – 8 pin Plastic DIP, 0.25mm lead frame, Package Outline . . . . . . . . . . . . . . . . .33 Table 23.PDIP8 – 8 pin Plastic DIP, 0.25mm lead frame, Package Mechanical Data. . . . . . . . . .33 Figure 20.SO8 narrow – 8 lead Plastic Small Outline, 150 mils body width, Package Outline . . . .34 Table 24.SO8 narrow – 8 lead Plastic Small Outline, 150 mils body width, Package Mechanical Data 34Figure 21.SO8 wide – 8 lead Plastic Small Outline, 200 mils body width, Package Outline. . . . . .35 Table 25.SO8 wide – 8 lead Plastic Small Outline, 200 mils body width, Package Mechanical Data 35Figure 22.TSSOP8 – 8 lead Thin Shrink Small Outline, Package Outline . . . . . . . . . . . . . . . . . . .36 Table 26.TSSOP8 – 8 lead Thin Shrink Small Outline, Package Mechanical Data. . . . . . . . . . . .36PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37 Table 27.Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38 Table 28.Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38M95256, M95128SUMMARY DESCRIPTIONThese electrically erasable programmable memo-ry (EEPROM) devices are accessed by a high speed SPI-compatible bus. The memory array is organized as 32768 x 8 bit (M95256) and 16384 x 8 bit (M95128).The device is accessed by a simple serial interface that is SPI-compatible. The bus signals are C, D and Q, as shown in Table 2. and Figure 2..The device is selected when Chip Select (S) is tak-en Low. Communications with the device can be interrupted using Hold (HOLD).sions, and how to identify pin-1.Table 2. Signal NamesC SerialClockD Serial Data InputQ Serial Data OutputS Chip SelectW WriteProtectHOLD HoldV CC Supply VoltageV SS Ground5/39M95256, M951286/39SIGNAL DESCRIPTIONDuring all operations, V CC must be held stable and within the specified valid range: V CC (min) to V CC (max).All of the input and output signals must be held High or Low (according to voltages of V IH , V OH , V IL or V OL , as specified in Table 13. to Table 17.).These signals are described next.Serial Data Output (Q).This output signal is used to transfer data serially out of the device.Data is shifted out on the falling edge of Serial Clock (C).Serial Data Input (D).This input signal is used to transfer data serially into the device. It receives in-structions, addresses, and the data to be written.Values are latched on the rising edge of Serial Clock (C).Serial Clock (C).This input signal provides the timing of the serial interface. Instructions, address-es, or data present at Serial Data Input (D) are latched on the rising edge of Serial Clock (C). Data on Serial Data Output (Q) changes after the falling edge of Serial Clock (C).When this input signal is High,the device is deselected and Serial Data Output(Q) is at high impedance. Unless an internal Write cycle is in progress, the device will be in the Stand-by Power mode. Driving Chip Select (S) Low se-lects the device, placing it in the Active Power mode.is required prior to the start of any instruction. pause any serial communications with the device without deselecting the device.During the Hold condition, the Serial Data Output (Q) is high impedance, and Serial Data Input (D)and Serial Clock (C) are Don’t Care.To start the Hold condition, the device must be se-The main purpose of this in-put signal is to freeze the size of the area of mem-ory that is protected against Write instructions (as specified by the values in the BP1 and BP0 bits of the Status Register).This pin must be driven either High or Low, and must be stable during all write instructions.M95256, M95128 CONNECTING TO THE SPI BUSThese devices are fully compatible with the SPI protocol.All instructions, addresses and input data bytes are shifted in to the device, most significant bit first. The Serial Data Input (D) is sampled on the first rising edge of the Serial Clock (C) after Chip All output data bytes are shifted out of the device, most significant bit first. The Serial Data Output (Q) is latched on the first falling edge of the Serial Clock (C) after the instruction (such as the Read from Memory Array and Read Status Register in-structions) have been clocked into the device. Figure 4. shows three devices, connected to an MCU, on a SPI bus. Only one device is selected at a time, so only one device drives the Serial Data Output (Q) line at a time, all the others being high impedance.7/39M95256, M951288/39SPI ModesThese devices can be driven by a microcontroller with its SPI peripheral running in either of the two following modes:–CPOL=0, CPHA=0–CPOL=1, CPHA=1For these two modes, input data is latched in on the rising edge of Serial Clock (C), and output data is available from the falling edge of Serial Clock (C).The difference between the two modes, as shown in Figure 5., is the clock polarity when the bus master is in Stand-by mode and not transferring data:– C remains at 0 for (CPOL=0, CPHA=0)– C remains at 1 for (CPOL=1, CPHA=1)M95256, M95128 OPERATING FEATURESPower-upWhen the power supply is turned on, V CC rises from V SS to V CC.During this time, the Chip Select (S) must be al-lowed to follow the V CC voltage. It must not be al-lowed to float, but should be connected to V CC via a suitable pull-up resistor.sensitive as well as level sensitive. After Power-up, the device does not become selected until a falling edge has first been detected on Chip Selectbeen High, prior to going Low to start the first op-eration.Power On Reset: V CC Lock-Out Write Protect In order to prevent data corruption and inadvertent Write instructions during Power-up, a Power On Reset (POR) circuit is included. The internal reset is held active until V CC has reached the Power On Reset (POR) threshold voltage, and all operations are disabled – the device will not respond to any instruction. In the same way, when V CC drops from the operating voltage, below the Power On Reset (POR) threshold voltage, all operations are dis-abled and the device will not respond to any in-struction.A stable and valid V CC must be applied before ap-plying any logic signal.Power-downAt Power-down, the device must be deselected.voltage applied on V CC.Active Power and Standby Power Modes When Chip Select (S) is Low, the device is select-ed, and in the Active Power mode. The device consumes I CC, as specified in Table 13. to Table 17..lected. If an Erase/Write cycle is not currently in progress, the device then goes in to the Standby Power mode, and the device consumption drops to I CC1.Hold ConditionThe Hold (HOLD) signal is used to pause any se-rial communications with the device without reset-ting the clocking sequence.During the Hold condition, the Serial Data Output (Q) is high impedance, and Serial Data Input (D) and Serial Clock (C) are Don’t Care.To enter the Hold condition, the device must be Normally, the device is kept selected, for the whole duration of the Hold condition. Deselecting the de-vice while it is in the Hold condition, has the effect of resetting the state of the device, and this mech-anism can be used if it is required to reset any pro-cesses that had been in progress.The Hold condition starts when the Hold (HOLD) signal is driven Low at the same time as Serial Clock (C) already being Low (as shown in Figure 6.).The Hold condition ends when the Hold (HOLD) signal is driven High at the same time as Serial Clock (C) already being Low.Figure 6. also shows what happens if the rising and falling edges are not timed to coincide with Serial Clock (C) being Low.9/39M95256, M9512810/39Status RegisterFigure 7. shows the position of the Status Register in the control logic of the device. The Status Reg-ister contains a number of status and control bits that can be read or set (as appropriate) by specific instructions.WIP bit.The Write In Progress (WIP) bit indicates whether the memory is busy with a Write or Write Status Register cycle.WEL bit.The Write Enable Latch (WEL) bit indi-cates the status of the internal Write Enable Latch.BP1, BP0 bits.The Block Protect (BP1, BP0) bits are non-volatile. They define the size of the area to be software protected against Write instructions. SRWD bit.The Status Register Write Disable (SRWD) bit is operated in conjunction with the Write Protect (W) signal. The Status Register signal allow the device to be put in the Hardware Protected mode. In this mode, the non-volatile bits of the Status Register (SRWD, BP1, BP0) become read-only bits.Table 3. Status Register FormatData Protection and Protocol ControlNon-volatile memory devices can be used in envi-ronments that are particularly noisy, and within ap-plications that could experience problems if memory bytes are corrupted. Consequently, the device features the following data protection mechanisms:■Write and Write Status Register instructionsare checked that they consist of a number of clock pulses that is a multiple of eight, before they are accepted for execution.■All instructions that modify data must bepreceded by a Write Enable (WREN) instruction to set the Write Enable Latch(WEL) bit. This bit is returned to its reset state by the following events:–Power-up–Write Disable (WRDI) instructioncompletion–Write Status Register (WRSR) instructioncompletion–Write (WRITE) instruction completion ■The Block Protect (BP1, BP0) bits allow part ofthe memory to be configured as read-only. This is the Software Protected Mode (SPM).■The Write Protect (W) signal allows the BlockProtect (BP1, BP0) bits to be protected. This is the Hardware Protected Mode (HPM).For any instruction to be accepted, and executed,Chip Select (S) must be driven High after the rising edge of Serial Clock (C) for the last bit of the in-struction, and before the next rising edge of Serial Clock (C).Two points need to be noted in the previous sen-tence:–The ‘last bit of the instruction’ can be theeighth bit of the instruction code, or the eighth bit of a data byte, depending on the instruction (except for Read Status Register (RDSR) and Read (READ) instructions).–The ‘next rising edge of Serial Clock (C)’ might(or might not) be the next bus transaction for some other device on the SPI bus.Table 4. Write-Protected Block Sizeb7 b0SRWD0 0 0 BP1 BP0 WEL WIPStatus Register Write ProtectBlock Protect Bits Write Enable Latch BitWrite In Progress BitStatus Register Bits Protected BlockArray Addresses Protected BP1 BP0M95256M951280 0 none none none 0 1 Upper quarter 6000h - 7FFFh 3000h - 3FFFh 1 0 Upper half 4000h - 7FFFh 2000h - 3FFFh 11Whole memory0000h - 7FFFh0000h - 3FFFhMEMORY ORGANIZATIONThe memory is organized as shown in Figure 7..11/39INSTRUCTIONSEach instruction starts with a single-byte code, as summarized in Table 5..If an invalid instruction is sent (one not contained in Table 5.), the device automatically deselects it-self.Table 5. Instruction SetInstructionDescriptionInstructionFormat WREN Write Enable0000 0110 WRDI Write Disable0000 0100 RDSR Read Status Register 0000 0101 WRSR Write Status Register 0000 0001 READ Read from Memory Array0000 0011 WRITE Write to Memory Array 0000 001012/39Write Enable (WREN)The Write Enable Latch (WEL) bit must be set pri-or to each WRITE and WRSR instruction. The only way to do this is to send a Write Enable instruction to the device.As shown in Figure 8., to send this instruction to the device, Chip Select (S) is driven Low, and the bits of the instruction byte are shifted in, on Serial Data Input (D). The device then enters a wait state. It waits for a the device to be deselected, by Chip Select (S) being driven High.One way of resetting the Write Enable Latch (WEL) bit is to send a Write Disable instruction to the device.As shown in Figure 9., to send this instruction to the device, Chip Select (S) is driven Low, and the bits of the instruction byte are shifted in, on Serial Data Input (D).The device then enters a wait state. It waits for a the device to be deselected, by Chip Select (S) be-ing driven High.The Write Enable Latch (WEL) bit, in fact, be-comes reset by any of the following events:–Power-up–WRDI instruction execution–WRSR instruction completion–WRITE instruction completion.13/39Read Status Register (RDSR)The Read Status Register (RDSR) instruction al-lows the Status Register to be read. The Status Register may be read at any time, even while a Write or Write Status Register cycle is in progress. When one of these cycles is in progress, it is rec-ommended to check the Write In Progress (WIP) bit before sending a new instruction to the device. It is also possible to read the Status Register con-tinuously, as shown in Figure 10..The status and control bits of the Status Register are as follows:WIP bit.The Write In Progress (WIP) bit indicates whether the memory is busy with a Write or Write Status Register cycle. When set to 1, such a cycle is in progress, when reset to 0 no such cycle is in progress.WEL bit.The Write Enable Latch (WEL) bit indi-cates the status of the internal Write Enable Latch. When set to 1 the internal Write Enable Latch is set, when set to 0 the internal Write Enable Latch is reset and no Write or Write Status Register in-struction is accepted.BP1, BP0 bits.The Block Protect (BP1, BP0) bits are non-volatile. They define the size of the area to be software protected against Write instructions. These bits are written with the Write Status Regis-ter (WRSR) instruction. When one or both of the Block Protect (BP1, BP0) bits is set to 1, the rele-vant memory area (as defined in Table 3.) be-comes protected against Write (WRITE) instructions. The Block Protect (BP1, BP0) bits can be written provided that the Hardware Protect-ed mode has not been set.SRWD bit.The Status Register Write Disable (SRWD) bit is operated in conjunction with the Write Protect (W) signal. The Status Register Write Disable (SRWD) bit and Write Protect (W) signal allow the device to be put in the Hardware Protected mode (when the Status Register Write Disable (SRWD) bit is set to 1, and Write Protect bits of the Status Register (SRWD, BP1, BP0) be-come read-only bits and the Write Status Register (WRSR) instruction is no longer accepted for exe-cution.14/39Write Status Register (WRSR)The Write Status Register (WRSR) instruction al-lows new values to be written to the Status Regis-ter. Before it can be accepted, a Write Enable (WREN) instruction must previously have been ex-ecuted. After the Write Enable (WREN) instruction has been decoded and executed, the device sets the Write Enable Latch (WEL).The Write Status Register (WRSR) instruction is by the instruction code and the data byte on Serial Data Input (D).The instruction sequence is shown in Figure 11.. The Write Status Register (WRSR) instruction has no effect on b6, b5, b4, b1 and b0 of the Status Register. b6, b5 and b4 are always read as 0. Chip Select (S) must be driven High after the rising edge of Serial Clock (C) that latches in the eighth bit of the data byte, and before the next rising edge of Serial Clock (C). Otherwise, the Write Status Register (WRSR) instruction is not executed. As soon as Chip Select (S) is driven High, the self-timed Write Status Register cycle (whose duration is t W) is initiated. While the Write Status Register cycle is in progress, the Status Register may still be read to check the value of the Write In Progress (WIP) bit. The Write In Progress (WIP) bit is 1 dur-ing the self-timed Write Status Register cycle, and is 0 when it is completed. When the cycle is com-pleted, the Write Enable Latch (WEL) is reset. The Write Status Register (WRSR) instruction al-lows the user to change the values of the Block Protect (BP1, BP0) bits, to define the size of the area that is to be treated as read-only, as defined in Table 3..The Write Status Register (WRSR) instruction also allows the user to set or reset the Status Register Write Disable (SRWD) bit in accordance with the Write Protect (W) signal. The Status Register Write Disable (SRWD) bit and Write Protect (W) signal allow the device to be put in the Hardware Protected Mode (HPM). The Write Status Register (WRSR) instruction is not executed once the Hard-ware Protected Mode (HPM) is entered.The contents of the Status Register Write Disable (SRWD) and Block Protect (BP1, BP0) bits are fro-zen at their current values from just before the start of the execution of Write Status Register (WRSR) instruction. The new, updated, values take effect at the moment of completion of the ex-ecution of Write Status Register (WRSR) instruc-tion.Table 6. Protection ModesNote: 1.As defined by the values in the Block Protect (BP1, BP0) bits of the Status Register, as shown in Table 6..The protection features of the device are summa-rized in Table 4..When the Status Register Write Disable (SRWD) bit of the Status Register is 0 (its initial delivery state), it is possible to write to the Status Register provided that the Write Enable Latch (WEL) bit has previously been set by a Write Enable (WREN) in-struction, regardless of the whether Write Protect (W) is driven High or Low.When the Status Register Write Disable (SRWD) bit of the Status Register is set to 1, two cases need to be considered, depending on the state of Write Protect (W):–If Write Protect (W) is driven High, it is possible to write to the Status Registerprovided that the Write Enable Latch (WEL) bit has previously been set by a Write Enable(WREN) instruction.–If Write Protect (W) is driven Low, it is not possible to write to the Status Register even if the Write Enable Latch (WEL) bit haspreviously been set by a Write Enable(WREN) instruction. (Attempts to write to the Status Register are rejected, and are notaccepted for execution). As a consequence,all the data bytes in the memory area that are software protected (SPM) by the Block ProtectW Signal SRWDBitModeWrite Protection of theStatus RegisterMemory ContentProtected Area1Unprotected Area110SoftwareProtected(SPM)Status Register is Writable(if the WREN instructionhas set the WEL bit)The values in the BP1 andBP0 bits can be changedWrite ProtectedReady to accept Writeinstructions00 1101HardwareProtected(HPM)Status Register isHardware write protectedThe values in the BP1 andBP0 bits cannot bechangedWrite ProtectedReady to accept Writeinstructions15/39。

FM25L256操作子程序

#include "FM25L256.h"//FM25L256数据读取子程序//参数: *pDestination要读入数据的主机内存地址指针; uiSourceAddress要读取的数据在FM25L256中的地址(整形); uiNum数据个数(整形)//参数条件: uiSourceAddress+(uiNum-1)不能大于器件的最高地址; uiNum必须>0;void ReadFM25L256(unsigned char *pDestination, unsigned int uiSourceAddress, unsigned int uiNum){unsigned char ucHighAddress = uiSourceAddress >> 8; //高位地址SPCR = (1<<SPE)|(1<<MSTR)|(0<<CPOL)|(0<<SPR0);EnableFM25256; //CS变低SPDR = 0x03; //写入读命令字while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕SPDR = ucHighAddress; //写入高位地址while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕SPDR = (unsigned char) (uiSourceAddress & 0x00FF); //写入低位地址while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕for(;uiNum > 0;uiNum--){SPDR = 0; //为了读取数据,需要写入数据,发送SCK,故写入0while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕*pDestination = SPDR; //从器件读出一个字节pDestination++;}DisableFM25256; //CS变高}//FM25L256数据读取并发送至串口子程序//参数: uiSourceAddress要读取的数据在FM25L256中的地址(整形); uiNum数据个数(整形) //参数条件: uiSourceAddress+(uiNum-1)不能大于器件的最高地址; uiNum必须>0;//返回值:所发送数据的检验和unsigned char ReadFM25L256SendToUsart(unsigned int uiSourceAddress, unsigned int uiNum) {unsigned char ucHighAddress = uiSourceAddress >> 8; //高位地址unsigned char ucTemp;EnableFM25256; //CS变低SPCR = (1<<SPE)|(1<<MSTR)|(0<<CPOL)|(0<<SPR0);SPDR = 0x03; //写入读命令字while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕SPDR = ucHighAddress; //写入高位地址while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕SPDR = (unsigned char) (uiSourceAddress & 0x00FF); //写入低位地址while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕for(;uiNum > 0;uiNum--){SPDR = 0; //为了读取数据,需要写入数据,发送SCK,故写入0while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕ucTemp = SPDR; //读取SPDRSendChar(ucTemp); //发送至串口}DisableFM25256; //CS变高return (1);}//FM25L256数据写入子程序//参数: *pSource要写入数据的主机内存地址指针; uiDestinationAddress要写入的数据在FM25L256中的地址(整形); uiNum数据个数(整形)void WriteFM25L256(unsigned char *pSource, unsigned int uiDestinationAddress, unsigned int uiNum){unsigned char ucHighAddress = uiDestinationAddress >> 8; //高位地址EnableFM25256; //CS变低SPCR = (1<<SPE)|(1<<MSTR)|(0<<CPOL)|(0<<SPR0);SPDR = 0x06; //写入写使能WREN命令while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕DisableFM25256; //CS变高_delay_us(50);EnableFM25256; //CS变低SPDR = 0x02; //写入写命令字while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕SPDR = ucHighAddress; //写入高位地址CI-FM25H20-DGwhile((SPSR&(1<<SPIF))==0); //等待SPI发送完毕SPDR = (unsigned char) (uiDestinationAddress & 0x00FF); //写入低位地址while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕for(;uiNum > 0;uiNum--){SPDR = *pSource; //发送要写入的数据while((SPSR&(1<<SPIF))==0); //等待SPI发送完毕pSource++;}DisableFM25256; //CS变高}//FM25L256自检子程序//返回值:0:自检成功,1:自检失败unsigned char FM25L256SelfTest(void){unsigned int uiTemp;uiTemp = ReadInt(FM25L256_CHECK_ADDRESS);if (uiTemp == 0xA55A) //判断是否存储器是否能读return (0);else{ //存储器不能读或未进行出厂设置SetDefault(); //出厂设置,函数定义在System.c WriteInt (0xA55A,FM25L256_CHECK_ADDRESS); //设置已出厂设置标志uiTemp = ReadInt(FM25L256_CHECK_ADDRESS);if (uiTemp == 0xA55A) //若读取正确返回0return (0);elsereturn (1); //若仍读取错误则返回1}}/*//测试FM25L256子程序void VerifyFM25L256(void){unsigned int uiCheckAddress = 0;unsigned int uiMemoryNum = ReadInt(MEMORY_ADDRESS);unsigned int uiOldData;unsigned char ucError = 0;unsigned char ucSendChkSum;unsigned char i;union tagSTOREINT siUsartDataInt; //整型共用体,将整形分解为字节型存取,在DataStore.h中定义for (;uiCheckAddress < uiMemoryNum;uiCheckAddress += 2){uiOldData = ReadInt(uiCheckAddress); //保存原有数据WriteInt (0xA55A,uiCheckAddress); //写入测试字// __delay_cycles(10);if (ReadInt(uiCheckAddress) != 0xA55A){WriteInt (uiOldData,uiCheckAddress); //写回原有数据SendChar(COMM_FRAME_START); //发送反馈帧头ucSendChkSum = COMM_FRAME_START; //计算反馈帧的校验和SendChar(VERIFY_FRAM_COMMAND); //发送命令字ucSendChkSum += VERIFY_FRAM_COMMAND; //计算反馈帧的校验和siUsartDataInt.uiStoreInt = uiMemoryNum; //发送地址总长for (i = 0;i <= 1;i++){SendChar(siUsartDataInt.ucStoreBuff[i]);ucSendChkSum += siUsartDataInt.ucStoreBuff[i];}siUsartDataInt.uiStoreInt = uiCheckAddress; //发送测试地址for (i = 0;i <= 1;i++){SendChar(siUsartDataInt.ucStoreBuff[i]);ucSendChkSum += siUsartDataInt.ucStoreBuff[i];}SendChar(FINISHED_SEND);ucSendChkSum += FINISHED_SEND; //发送结束上传标志SendChar(ucSendChkSum); //发送检验和SendChar(COMM_FRAME_END); //发送帧尾ucError = 1; //置错误标志break; //退出循环}else if ((((uiCheckAddress + 2) % 1024) == 0) && ((uiCheckAddress + 2) < uiMemoryNum)){WriteInt (uiOldData,uiCheckAddress); //写回原有数据SendChar(COMM_FRAME_START); //发送反馈帧头ucSendChkSum = COMM_FRAME_START; //计算反馈帧的校验和SendChar(VERIFY_FRAM_COMMAND); //发送命令字ucSendChkSum += VERIFY_FRAM_COMMAND; //计算反馈帧的校验和siUsartDataInt.uiStoreInt = uiMemoryNum; //发送地址总长for (i = 0;i <= 1;i++){SendChar(siUsartDataInt.ucStoreBuff[i]);ucSendChkSum += siUsartDataInt.ucStoreBuff[i];}siUsartDataInt.uiStoreInt = uiCheckAddress + 2; //发送测试完成地址for (i = 0;i <= 1;i++){SendChar(siUsartDataInt.ucStoreBuff[i]);ucSendChkSum += siUsartDataInt.ucStoreBuff[i];}SendChar(GO_ON_SEND);ucSendChkSum += GO_ON_SEND; //发送结束上传标志SendChar(ucSendChkSum); //发送检验和SendChar(COMM_FRAME_END); //发送帧尾// __watchdog_reset(); //复位看门狗}WriteInt (uiOldData,uiCheckAddress); //写回原有数据}if (ucError == 0){SendChar(COMM_FRAME_START); //发送反馈帧头ucSendChkSum = COMM_FRAME_START; //计算反馈帧的校验和SendChar(VERIFY_FRAM_COMMAND); //发送命令字ucSendChkSum += VERIFY_FRAM_COMMAND; //计算反馈帧的校验和siUsartDataInt.uiStoreInt = uiMemoryNum; //发送地址总长for (i = 0;i <= 1;i++){SendChar(siUsartDataInt.ucStoreBuff[i]);ucSendChkSum += siUsartDataInt.ucStoreBuff[i];}siUsartDataInt.uiStoreInt = uiCheckAddress; //发送测试完成地址for (i = 0;i <= 1;i++){SendChar(siUsartDataInt.ucStoreBuff[i]);ucSendChkSum += siUsartDataInt.ucStoreBuff[i];}SendChar(FINISHED_SEND);ucSendChkSum += FINISHED_SEND; //发送结束上传标志SendChar(ucSendChkSum); //发送检验和SendChar(COMM_FRAME_END); //发送帧尾}}*/。

FM25V02铁电存储器数据手册pdf格式