《数字电路-分析与设计》第十章习题及解答(部分)北京理工大学出版社

数字电路习题答案详解

受5号译码器输出控制。(1)当 CD=00时, 只1号译码器译码,其他译码器不译码。

当 CD=01时, 只2号译码器译码。(3)当 CD=10时, 只3号译码器译码。当 CD=11

时, 只4号译码器译码F1。0、F20、F30、F40

的逻辑函数表达式为:

第11页,共50页。

3-7 图示电路每一方框均为2线一4线译码器组成。其输出低电平有效。要求:

3-11

G AB

Y A BC

RC

G AB AB Y A BC ABC RC

需用七个与非门。而圈0则:

G A B AB

Y AB C ABC

R C

G AB

Y ABC RC

第25页,共50页。

3-11

试用六个与非门设计一个水箱控制电路。图为水箱示意图。A、B、C是三个电极。 当电极被水浸没时, 会有信号输出。水面在A,B间为正常状态,点亮绿灯G;水面在B、C间或在A以上为异常状态,点亮黄灯Y;水 面在C以下为危险状态.点亮红灯R。

其他电路:

第16页,共50页。

第17页,共50页。

第18页,共50页。

第19页,共50页。

3-10 试用与非门设计一个逻辑选择电路。S1、S0为

选择端,A、B为数据输入端。选择电路的 功能见下表。选择电路可以有反变量输入。

第20页,共50页。

3-10 F S1 AB S0 AB S0 A B S0 AB S1S0 A B F F S1 AB S0 AB S0 A B S0 AB S1S0 A B F S1S0 AB S1S0 ( A B) S1S0 ( A B AB) S1S0 ( A B AB )

择信号;比较结果F从74151 Y 反相输出端得到。

数字电子技术基础_北京理工大学中国大学mooc课后章节答案期末考试题库2023年

数字电子技术基础_北京理工大学中国大学mooc课后章节答案期末考试题库2023年1.逐次渐近型8位A/D转换器中的8位D/A转换器的Vomax=10.2V,若输入为3V,则转换后的数字输出D为:答案:010010112.用ROM设计逻辑电路实现两个两位二进数的全加运算,则需要ROM的地址线和数据线至少为:答案:5,33.存储容量为8k×16位的RAM,地址线有()根。

答案:134.静态RAM一般采用MOS管的栅极电容来存储信息,必须由刷新电路定期刷新。

答案:错误5.以下触发器电路中能够实现二进制计数器(对输入的时钟进行计数,辨识两个时钟周期)功能的电路有:答案:___6.ROM为只读存储器,因此不能对其进行写操作。

答案:错误7.施密特触发器具有两个稳定状态。

答案:正确8.由555定时器构成的电路如图所示,则此电路能够实现()功能。

【图片】答案:单稳态触发器9.555定时器构成电路如图所示,则此电路的功能为:【图片】答案:施密特触发器10.【图片】上图可以实现的逻辑功能为:答案:半减器11.下图所示74LS151为8选1数据选择器,当用此器件设计逻辑函数【图片】时,D0D1D2D3D4D5D6D7应分别连接到:【图片】答案:0100101012.如图所示74LS283为四位二进制加法计数器,如果要将输入的8421BCD码D3D2D1D1转换为余3码F3F2F1F0,并且把D3D2D1D1分别接到输入端A3A2A1A0上,则输入端B3B2B1B0和低位进位输入CI分别接到:【图片】答案:0010113.已知TTL反相器电路的参数如下:VOH/ VOL=3.6V/0.3V,IOH/IOL=0.2mA/8mA, IIH/ IIL=20uA/0.4mA ,则其驱动同类门的数量即其扇出系数为多少。

答案:1014.三位环形计数器的模为()?答案:315.如图所示电路输出信号为00110010。

【图片】答案:正确16.单稳态触发器输出信号的脉宽由输入的触发信号决定。

数字电路习题及答案

数字电路习题及答案项目一一.填空题1.电子电路中的信号可分为两类。

一类是时间的连续信号,称为__________,另一类是时间和幅度都是离散的(即不连续的信号),称为__________。

(模拟信号、数字信号)2.所谓数字信号,是指可以用两种逻辑电平__________和__________来描述的信号。

(0、1)3.在数字电路中,应用最为广泛的是__________集成门电路和__________集成门电路。

(TTL、CMOS)4.基本的逻辑关系有三种:__________、__________、__________。

(逻辑与、逻辑或、逻辑非)5.任何逻辑函数都可以用__________、__________、__________和__________四种形式来表示。

(逻辑表达式、逻辑图、真值表、卡诺图)6.常用的数制有__________、__________、__________和__________等。

(十进制、二进制、八进制、十六进制)7.BCD码有很多种形式,常用的有__________、__________、__________、__________、__________等。

(8421码、余3码、格雷码、2421码、5421码)8.在实践中最常用的逻辑函数的化简方法是__________法,它比较适用于__________变量以内的逻辑函数的化简。

(卡诺图化简、四)9.数字电路按逻辑功能和电路结构的不同特点可划分为两大类,一类称为__________,另一类称为__________。

(组合逻辑电路、时序逻辑电路)10.能实现基本和常用逻辑运算的电子电路称为__________。

(门电路)11.仿真软件__________是学习数字电路有效的辅助工具,它可以在计算机上完成电路的连接及测试,大大提高数字电路学习的效率。

(Multisim 10)二.简答题1.与模拟电路相比,数字电路具有哪些优点?答:与模拟电路相比,数字电路具有以下显著的优点:(1)结构简单,便于集成化、系列化生产,成本低廉,使用方便。

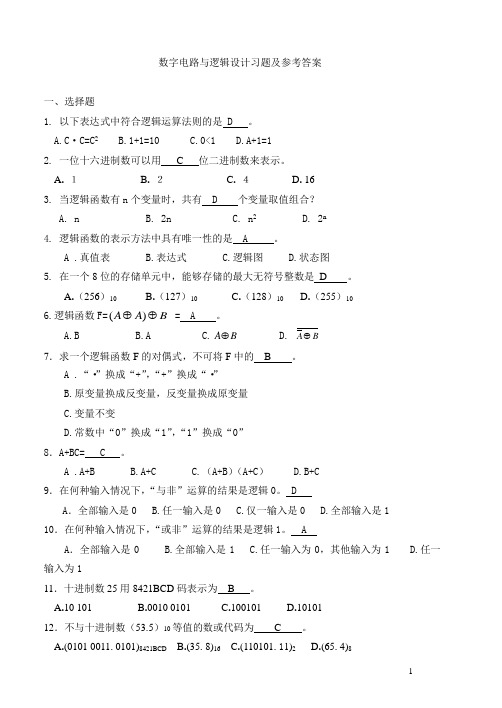

数字电路与逻辑设计习题及参考答案全套

数字电路与逻辑设计习题及参考答案一、选择题1. 以下表达式中符合逻辑运算法则的是 D 。

A.C ·C=C 2B.1+1=10C.0<1D.A+1=12. 一位十六进制数可以用 C 位二进制数来表示。

A . 1B . 2C . 4D . 163. 当逻辑函数有n 个变量时,共有 D 个变量取值组合?A. nB. 2nC. n 2D. 2n4. 逻辑函数的表示方法中具有唯一性的是 A 。

A .真值表 B.表达式 C.逻辑图 D.状态图5. 在一个8位的存储单元中,能够存储的最大无符号整数是 D 。

A .(256)10B .(127)10C .(128)10D .(255)106.逻辑函数F=B A A ⊕⊕)( = A 。

A.BB.AC.B A ⊕D. B A ⊕7.求一个逻辑函数F 的对偶式,不可将F 中的 B 。

A .“·”换成“+”,“+”换成“·”B.原变量换成反变量,反变量换成原变量C.变量不变D.常数中“0”换成“1”,“1”换成“0”8.A+BC= C 。

A .A+B B.A+C C.(A+B )(A+C ) D.B+C9.在何种输入情况下,“与非”运算的结果是逻辑0。

DA .全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是110.在何种输入情况下,“或非”运算的结果是逻辑1。

AA .全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为111.十进制数25用8421BCD 码表示为 B 。

A .10 101B .0010 0101C .100101D .1010112.不与十进制数(53.5)10等值的数或代码为 C 。

A .(0101 0011.0101)8421BCDB .(35.8)16C .(110101.11)2D .(65.4)813.以下参数不是矩形脉冲信号的参数 D 。

A.周期B.占空比C.脉宽D.扫描期14.与八进制数(47.3)8等值的数为: BA. (100111.0101)2B.(27.6)16C.(27.3 )16D. (100111.101)215. 常用的BCD码有 D 。

数字电路及系统设计课后习题答案

1.1 将下列各式写成按权展开式:2 1 0 -1(352.6 ) io=3X 102+5X 101+2X 10°+6X 10(101.101 ) 2=1 X 22+1x 2O+1X 2-1+1x 2-3( 54.6 )8=5X 81+54X 80+6X 8-12 1 0 -1 -2(13A.4F)16=1X162+3X161+10X 160+4X16-1+15X16-21.2 按十进制0~17 的次序,列表填写出相应的二进制、八进制、十六进制数。

解:略1.3 二进制数00000000~11111111 和0000000000~1111111111 分别可以代表多少个数?解:分别代表28=256和210=1024个数。

1.4 将下列个数分别转换成十进制数:1111101000)2,(1750) 8,( 3E8)16解:( 1111101000)2=( 1000)10( 1750)8= ( 1000)10(3E8)16=(1000)101.5 将下列各数分别转换为二进制数: ( 210)8,( 136)10,( 88)16解:结果都为:(10001000)21.6 将下列个数分别转换成八进制数:(111111)2,(63)10,(3F)16解:结果都为(77)81.7 将下列个数分别转换成十六进制数:(11111111)2,(377)8 ,(255)10 解:结果都为(FF)161.8 转换下列各数,要求转换后保持原精度:解:(1.125 )10=(1.0010000000 )10 ——小数点后至少取10 位(0010 1011 0010 )2421BCD= (11111100)2(0110.1010 )余 3 循环BC[M= ( 1.1110 ) 21.9 用下列代码表示(1 23)10,(1011.01 )2:解:(1) 8421BCD码:(123 )10= (0001 0010 0011 )8421BCD(1011.01 )2=(11.25)10=(0001 0001.0010 0101 )8421BCD(2) 余3 BCD码(123) io= (0100 0101 0110 )余3BCD(1011.01 ) 2=( 11.25 ) 10=(0100 0100.0101 1000 )余3BcD1.10 已知A=(1011010) 2,B=( 101111) 2,c=(1010100) 2,D=( 110) 2(1)按二进制运算规律求A+B, A-B, C X D, C一D,(2)将A B、C D转换成十进制数后,求A+B, A-B, C X D,C- D,并将结果与(1)进行比较。

数字集成电路设计与系统分析答案

懂得1、Please illustrate the meaning of its voltage transfer characteristic to a logic gate, and describe the static behaviors showed in the voltage transfer characteristic curves.The electrical function of a gate is best expressed by its voltage transfer characteristic (VTC),which plots the output voltage as a function of the input voltage Vout=f(Vin).The high and low nominal voltage Voh and Vol;The gate or switching threshold voltage Vm,that is define as Vm=f(Vm)(The gate threshold voltage presents the midpoint of the switching characteristics,which is obtained when the output of a gate is short circuited to the input);The high and low input voltage Vih and Vil are defined by the point where the gain (=dVout/dVin)of the VTC equals -12、Please draw the voltage transfer characteristic curve of the inverter and label the static operation points in the VTC.3、Please describe the definition of noise margin and its physical significance(物理意义), then draw the figure of definition of noise margins.The noise margins represent the levels of noise that can be sustained(所允许的) when gates are cascaded. A measure of the sensitivity of a gate to noise is given by the noise margins NML(noise margin low) and NMH(noise margin high), which quantize the size of the legal “0” and “1”, respectively, and set a fixed maximum threshold on the noise value4、Please describe the meaning of the regenerative property and the conditions of a gate with regenerative property.A gate with regenerative property ensures that a disturbed signal converges back to a nominal voltage level after passing through a number of logical stages. The VTC should have a transient region (or undefined region) with a gain greater than 1 in absolute value, bordered by the two legal zones, where the gain should be less than 1 in absolute value5、What are the definitions of the fan-out and fan-in properties?The number that can be driven is termed the fan-out of circuit, that denotes the number of load gates N that are connected to the output of the driving gate. The fan-in of a gate is defined as the number of independent input nodes to the gate.6、How to describe the performance of a digital IC? Please illustrate the parameters used to characterize the transient performance of a logic family, and draw the associated figure of the definition of these parP ropagation delay time and rise/fall time can be used to characterize the transient performance of a logic family .Propagation delay time of a gate expresses the delay experienced by a signal when passing through a gate,which represent how quickly the gate responds to the changes at its inputs.Rise/fall time express how fast a signal transits between the different levels. Propagation delay time is defined as the period between the 50%transition points of the input and output signals.Rise/fall time is defined as the period between the 10% and 90% points of the total voltage transition at the output waveforms.1、Illustrate the basic structure and simple operation principle of MOS transistor.Four terminals:source, drain, gate, body; Vertical Structure: gate electrode, insulator, semiconductor substrate; Horizontal Structure: source region, channel region, drain region2、Illustrate the basic function of each terminal of MOS device, and describe the general terminal connections of NMOS and PMOS transistor, respectively.The source and the drain are the electrodes conducting the current. The gate electrode is thecontrolling terminal. The function of the body is secondaryIn NMOS devices, the source is defined as the n+ region which has a lower potential(电势) than the other n+ region, the drain. The source is the terminal with the higher potential in PMOS devices, The body is generally connected to a DC supply that is identical for all devices of the same type (GND for NMOS, VDD for PMOS).3、What does the transition (or input) characteristic of MOS transistor mean? And what conclusions we can find from the characteristic curve?It describes the relationship between the gate-source voltage and the drain-source current with the certain drain-source voltage .When the gate-source voltage is less than the threshold voltage, the conducting current is zero, that is, the NMOS transistor is in cutoff operation. When is larger than, the NMOS transistor is on.4、What does the current-voltage (or output) characteristic of MOS transistor mean? And what conclusions we can find from the I-V characteristic curve?.It describes the relationship between the drain-source voltage and the drain-source current with a certain gate-source voltageVgs > Vt , 0<VDS <VGS -VT : Linear modeThe inversion layer forms a continuous current path between the source and the drain.A drain current proportional to Vds will flow from the drain to the source through the conducting channel. The channel region acts as a voltage-controlled linear resister.5、Describe the operation modes of NMOS and PMOS transistors respectively, and define the corresponding ideal current equations.1、Explain the channel-length modulation, sub-threshold conduction, short-channel effect and narrow-channel effect. And illustrate their corresponding chief impacts on the device.This simple current equation prescribes a linear drain-bias dependence for the current in MOS transistors, determined by the empirical model parameter λ, called the channel-length modulation coefficientOne typical condition, which is due to the two-dimensional nature of channel current flow, is the sub-threshold conduction in small-geometry MOS transistors.As a working definition, a MOS transistor is called a short-channel device if its channel length is on the same order of magnitude as the depletion region thicknesses of the source and drain junctions.The short-channel effects that arise in this case are attributed to two physical phenomena: the limitations imposed on electron drift characteristics in the channel; the modification of the threshold voltage due to the shortening channel lengthMOS transistor that have channel widths on the same order of magnitude as the maxium depletion region thickness are defined as narrow channel devices.For MOSFET with small channel widths,the actual threshold voltage increases as a result of this extra depletion charge of the fringe depletion region.This fact is called narrow channel effect.2、Describe the three main components of the load capacitanceCL, when a logic gate is driving other fan-out gates. And sketch the capacitance model of NMOS transistor.Gate capacitances (of other inputs connected to out)Diffusion(or junction) capacitances (of drain/source regions)Routing capacitances (output to other inputs)1,Describe the basic structure and operation of a static CMOS inverter. Then draw theassociated transistor schematicThis structure consists of an enhancement-type NMOS transistor and an enhancement-type PMOS transistor, operating in complementary mode. So this configuration is called Complementary MOS (CMOS). The gate terminals of the PMOS and NMOS transistors are connected to form the inverter input. The drain terminals of the PMOS and NMOS transistors are connected to form the inverter output. The source and the substrate of the NMOS transistor are connected to the ground, while the source and body of PMOS transistor are connected to VDD The circuit topology is complementary push-pull in the sense that: For high input the NMOS transistor drives (pulls down) the output node while the PMOS transistor acts as the load, and for low input the PMOS transistor drives (pulls up) the output node while the NMOS transistor acts as the load.When the input is at VDD: The NMOS is on (conducting) while the PMOS is off (cut-off). A direct path exists between Vout and the ground node, resulting in a steady-state value of 0V at the output. When the input is at ground:The NMOS is off while the PMOS is on. A direct path exists between VDD and Vout, yielding a high output voltage (equal to VDD).Static CMOS logic:structure:The static CMOS style is really an extension of the static CMOS inverter to multiple inputs. A logic function in static CMOS must be implemented in both NMOS and PMOS transistors. It is the combination of the pull-up network(PUN) and the pull-down network(PDN). Each input always connects to PUN and PDN simultaneously. The function of the PUN is to provide a connection between the output and VDD anytime the output of the logic gate is meant to be 1 (based on the inputs). The function of the PDN is to connect the output to VSS when the output of the logic gate is meant to be 0.Opreation: The pull-down net should be “on” when the pull-up net is “off” and vice versa. For any given input combination, the output is connected either to VDD or to ground via a low-resistance path. A DC current path between the VDD and ground is not established for any of the input combinations. With the complementary nature of NMOS and PMOS, the pull-up or the pull-down is “on” alternately to implement the logic operation.Discuss the main problems for high fan-in static CMOS gates and the associated techniques for fast complex gates.tpHL = 0.69 Reqn(C1+2C2+3C3+4CL); Propagation delay deteriorates(恶化) rapidly as a function of fan-in quadratically in the worst case, Gates with a fan-in greater than 4 become excessively slow and must be avoided.tPLH increases linearly due to the linearly increasing value of the diffusion capacitance;tPHL increase quadratically due to the simultaneous increase the resistance and internal capacitance in serial part.Transistor sizing: as long as fan-out capacitance dominatesProgressive transistor sizing: This approach reduces the dominant resistance, while keeping the increase in capacitance within boundsTransfer gate:Configuration:The source and drain nodes serve as inputs and outputs, while the gate node serves as the control input, the body node is connected to the power/ground Operation: For NMOS transfer gate,it turns on while the gate control terminal goes high, and the input signal will be delivered to the output node; it turns off while the gate control terminal goes low, and the output node will be impedance.CMOS transmission gate:Configuration: The CMOS transmission gate consists of one NMOS and one PMOS transistor, with the source and drain connected in parallel; The gate voltages appliedto these two transistors are also set to be complementary signals. The substrate terminal of the NMOS transistor is connected to ground and the substrate terminal of the PMOS transistor is connected to Vdd.Operation: If the control signal C is logic-high (equal to Vdd), then both transistors are turned on and provide a low-resistance current path between the input and output nodes. If the control signal C is logic-low, then both transistors will be off, and the path between the input and output nodes will be in the high-impedance state. The weakness of one device is overcome by the strength of the other device, whether the output is transmitting a high or low value. This is a clear advantage of the CMOS transfer gate over the single transistor counterpart.DCVLS:Operation: Assume now that, for a given set of inputs, PDN1 conducts while PDN2 does not, and that Out and out are initially high and low, respectively. Turning on PDN1: Causes Out to be pulled down (below VDD−|VTP |); Out is in a high impedance state, as M2 and PDN2 are both turned off. At the point M2 turns on and starts charging out非to VDD — eventually turning off M1; This in turn enables Out to discharge all the way to GND.XOR/XNOR: When the signals A and B have the same values, there is one conducting path either AB or A非B非; Then the output F is pulled down;At the same time, the other pull-down paths connected to the F非are both turned off. When F is pulled down below VDD−|VTP |, M2 t urns on and starts charging F非to VDD —eventually turning off M1 and pulling down F to Gnd. When the signals A and B have the different values, there is one conducting path either AB非or A非B; Then the output F非is pulled down; At the same time, the other pull-down paths connected to the F are both turned off. When F非is pulled down below VDD−|VTP |, M1 turns on and starts charging F to VDD —eventually turning off M2 and pulling down F非to Gnd.Precharge-Evaluate dynamic CMOS:Operation: Precharge (when the clock signal Φ= 0):The PMOS precharge transistor MP is conducting while the complementary NMOS transistor MN is off. The output load capacitance is precharged to VDD by MP, then VOH=VDD;The input voltages have no influence yet upon the output level since the complementary NMOS transistor MN is off. Evaluate (when the clock signal Φ=1):The precharge transistor MP turns off while the NMOS evaluate transistor MN turns on. The output node voltage may now remain at the logic-high level or drop to a logic low, depending on the input voltage levels: If the input signals create a conducting path between the output node and the ground, PDN is on, and the output capacitance will discharge toward VOL=0;Otherwise, when PDN is off, the output voltage remains at VOH= VDD.Domino dynamic CMOS logic:When Φ=0, during precharge: The output of the n-type dynamic gate is charged up to VDD, and the output of the inverter is set to 0. When Φ=1, during evaluation: The dynamic gate conditionally discharges, and there are two possibilities: The output node of the dynamic CMOS stage is either discharged to a low level through the NMOS circuitry (1 to 0 transition), or it remains high. Consequently, the inverter output voltage can also make at most one transition during the evaluation phase, from 0 to 1.TSPC dynamic CMOS logic:Configuration:If one constrains a NORA stage to have only n-precharge gates, and not static gates, then a p-channel transistor can be eliminated from the clocked latch; The dynamic circuit technique to be presented in that it uses only one-phase clock signal, so no clock skew problem exists. The NORA design style can be simplified so that a single clock is sufficient. For the doubled n-C2MOS latch, when φ= 1, the latch is in the transparent evaluate mode and corresponds to 2 cascaded inverters (non-inverting); For the doubled n-C2MOS latch, when φ= 0, both inverters are disabled (hold mode) -- only the pull-up network is still active.Pipelined NORA dynamic CMOS system:Configuration: Consists of an np-CMOS logic sequence and a clocked CMOS output buffer; A pipelined system can be constructed by simply cascading alternating φ-section and φ -section, meaning that evaluation occurs during active φ and φ respectively;Operation:φ=0, during hold mode :N block performs the precharge operation and pulls node Out1 up to VDD through the p-type device Mp1, while p block performs the discharge operation and pulls the node Out2 down to zero through the n-type device Mn2; The clocked CMOS latch will not be in operation and the previous output voltage will be stored on the output load capacitor CL. φ=1, during evaluate mode:All cascaded NMOS and PMOS blocks evaluate output levels one after the other, and then the signal Out2 will be inversed to the output node by the clocked CMOS latch in operation;Operation Mode: Evaluate―Hold: All logic stages perform the precharge-discharge operation when the clock is high, and all stages evaluate output levels when the clock is low. Therefore, wewill call this circuit a section, meaning that evaluation occurs during active .Clocked CMOS dynamic circuit:Basic Structure:A pair of PMOS and NMOS transistors controlled by the complementary clock signals are cascaded in the pullup and pulldown paths of the static CMOS gate, respectively, then a CMOS logic gate can be synchronized with a clock. Operation: φ=1, during evaluation mode:The transistors Mp1 and Mp2 are both turned on, then this gate can evaluate normally as a CMOS inverter to generate the logic output In非; φ=0 , during hold mode: Both transistors Mp1 and Mp2 are off, decoupling the output from the input. The CMOS circuit cannot conduct and evaluate, then the output Q retains its previous value stored on the output capacitor CL.Sequential logic:Virtually all useful systems require storage of state information, leading to another class of circuits called sequential logic circuits. In these circuits, the output not only depends upon the current values of the inputs, but also upon preceding output values. In other words, a sequential circuit remembers some of the past history of the system; A sequential circuit consists of a combinational circuit and a memory block in the feedback loop.Combination logic:In all logic circuits described so far, the output is directly related to the input. Typically, there are no feedback loops between the output and the input in these circuits (also classified as non-regenerative circuits), so the outputs are always a logical combination of the inputs. As a class, these circuits are known as combinational logic circuits. Combinational logic circuits, described earlier, have the property that the output of a logic block is only a function of the current input values, assuming that enough time has elapsed for the logic gates to settle. Static storage:preserve state as long as the power is on;are built using positive feedback or regeneration with an intentional connection between the output and the input;useful when updates are infrequent (clock gating)Dynamic storage:store state on parasitic capacitors;only hold state for short periods of time (milliseconds);require periodic refresh to annihilate charge leakage;usually simpler, so higher speed and lower power;useful in datapath circuits that require high performance levels and are periodically clockedLatch: level sensitive circuit that passes inputs to Q when the clock is high (or low);input sampledon the falling edge of the clock is held stable when clock is low (or high)Register or Flip-flops (edge-triggered): edge sensitive circuits that only sample the inputs on a clock transitionpositive edge-triggered: 0- 1negative edge-triggered: 1 -0built using latches (e.g., master-slave flip-flops)。

10级数字电路试题answer

第 1 页 共 4 页……………………………………………装………………………………订…………………………线………………………………………………此处不能书写此处不能书写此处不能书写 此处不能书写此处不能书写 此处不能书写此处不能书写北京理工大学珠海学院2010 ~ 2011学年第二学期《数字电路基础》期末试卷答案(A )一、填空题1、(28)D = ( 11100 )B =( 1C )H =( 34 )O 。

2、已知a=0,b=1,c=1,则逻辑表达式()c b a ⊕∙= 0 。

3、按逻辑功能划分,四种常用的时钟触发器是 RS 触发器 ,D 触发器 , T 触发器 , JK 触发器 。

4、脉冲形成电路的组成有两大部分,分别是 惰性电路 和 开关 。

二、单项选择题1、下列二进制代码的奇校验位为0的是( D ) A 、0101B 、11110C 、1010101D 、1001001002、能起定时作用的电路是 ( C )A 、多谐振荡器B 、施密特触发器C 、单稳态电路D 、译码器 3、逻辑函数F=AB+B C 的反函数F =( A ) A 、(A +B )(B +C ) B 、(A+B )(B+C ) C 、A +B +CD 、A B +B C 4、函数F=AB+BC ,使F=1的输入ABC 组合为( D ) A 、ABC=000 B 、ABC=010 C 、ABC=101D 、ABC=1105、在同步工作条件下,JK 触发器的现态Q n =0,要求Q n+1=0,则应使( B ) A 、J=×,K=0 B 、J=0,K=×C 、J=1,K=×D 、J=K=16、下列函数中,是最小项表达式形式的是(C ) A 、 Y=A+BC B 、Y =ABC+ACD C 、 C B A C AB Y += D 、C B A C AB Y +=7、对于四位二进制译码器,其相应的输出端共有( B )A .4个 B. 16个 C. 8个 D. 10个 8、用8421码表示的十进制数45,可以写成(C )A.45 B. [101101]BCD C. [01000101]BCD D. [101101]29、属于组合逻辑电路的是(B )A.触发器 B. 全加器 C. 移位寄存器 D. 计数器10、当TTL与非门的输入端悬空时相当于输入为( B )A、逻辑0 B. 逻辑1 C、不确定D、0.5V11、F=A(A+B)+B(B+C+D)=( A )A、BB、A+BC、1D、C12、同步时序电路和异步时序电路比较,其差异在于后者( B )A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关13、欲使D触发器按Q n+1=n Q工作,应使输入D=( D )A.0B.1C.QD.Q14、DAC电路的转换比例常数为0.01,输入代码为10010001时,输出电压为( B )A.1.28B.1.45C.1.57D.1.5415、一个3位的二进制加法计数器,由000状态开始,经过9个时钟脉冲后,此计数器的状态为( C )A.000 B.100 C.001 D.011三、第 3 页 共 4 页……………………………………………装………………………………订…………………………线………………………………………………此处不能书写此处不能书写此处不能书写 此处不能书写此处不能书写 此处不能书写此处不能书写C A AC BC F ++= 四、C B F = 五、六、激励方程:特征方程:状态表:状态图该电路为同步具有自启动能力的模四计数器。

《数字电路-分析与设计》第七章习题及解答(部分1) 北京理工大学出版社

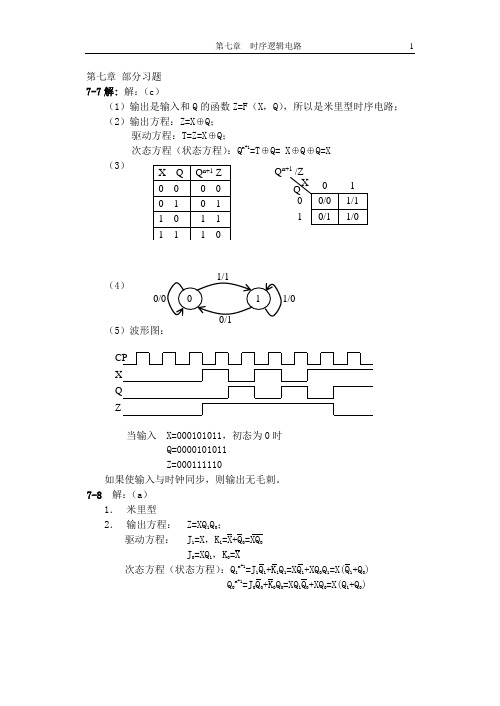

第七章 部分习题 7-7解: 解:(c )(1)输出是输入和Q 的函数Z=F (X ,Q ),所以是米里型时序电路; (2)输出方程:Z=X ⊕Q ;驱动方程:T=Z=X ⊕Q ;次态方程(状态方程):Q n+1=T ⊕Q= X ⊕Q ⊕Q=X(3)(4)(5)波形图:当输入 X=000101011,初态为0时 Q=0000101011 Z=000111110如果使输入与时钟同步,则输出无毛刺。

7-8 解:(a ) 1. 米里型2. 输出方程: Z=XQ 1Q 0;驱动方程: J 1=X ,K 1=X+Q 0=XQ 0J 0=XQ 1,K 0=X次态方程(状态方程):Q 1n+1=J 1Q 1+K 1Q 1=XQ 1+XQ 0Q 1=X(Q 1+Q 0)Q 0n+1=J 0Q 0+K 0Q 0=XQ 1Q 0+XQ 0=X(Q 1+Q 0)Q n+1CP X Q Z3.4.7-12某同步时序电路的逻辑方程如下:驱动方程:nQ X T 01⊕=,n Q X T 10=;输出方程:n Q X Z 1=。

要求: 解:1.同步时序电路的逻辑图示于图,这是米里型的状态机。

2.(a )状态方程: Q 1n+1=T 1⊕Q 1=X ⊕Q 0⊕Q 1Q 0n+1=T 0⊕Q 0=XQ 1⊕Q 0=XQ 1Q 0+XQ 0+Q 1Q 0(b )状态转换表: (c )状态转换图:(Q 1Q 0n+1Q7-15解:(a )“11”检测器,不重叠。

S 0:初始状态,输出0; S 1:输入一个“1”,输出0; S 2:输入两个“1”,输出1;(b ) “101”检测器,可重叠。

S 0:初始状态;S 1:输入序列为“1”;S 2:输入序列为“10”;S 3:输入序列为“101”;(c )(d )略7-34 “011”序列检测器,可重叠。

解:1.采用D(a ) 米里型状态图: S 0:初始状态;S 1:输入序列为“0”; S 2:输入序列为“01”;S 3:输入序列为“011”; (b ) 状态表(两种画法均可):(c ) 状态化简:由观察法知,S 0、S 3等价。

《数字电路-分析与设计》第三章习题及解答(部分)北京理工大学出版社

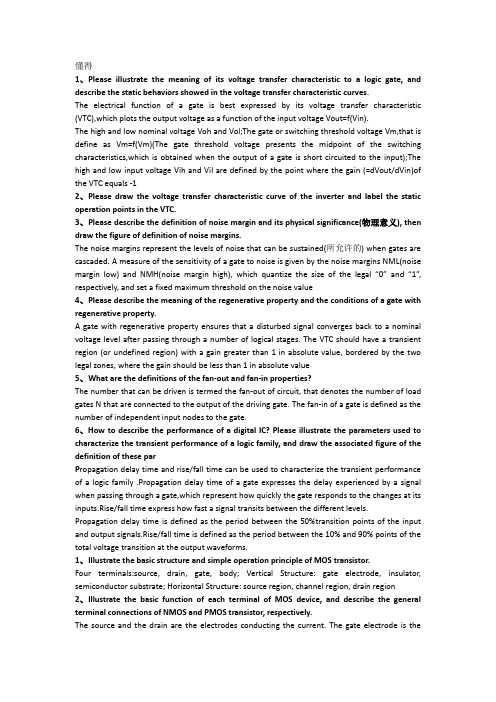

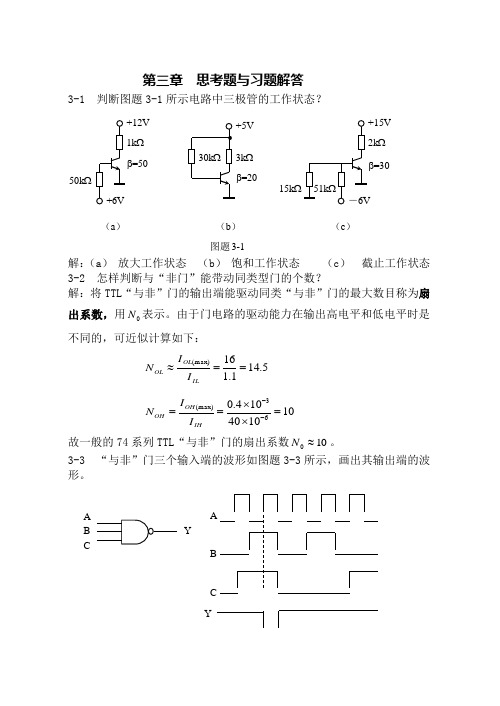

第三章 思考题与习题解答 3-1 判断图题3-1所示电路中三极管的工作状态?解:(a ) 放大工作状态 (b ) 饱和工作状态 (c ) 截止工作状态 3-2 怎样判断与“非门”能带动同类型门的个数?解:将TTL “与非”门的输出端能驱动同类“与非”门的最大数目称为扇出系数,用0N 表示。

由于门电路的驱动能力在输出高电平和低电平时是不同的,可近似计算如下:5.141.116(max)==≈IL OL OL I I N 101040104.063(max)=⨯⨯==--IHOH OH I I N 故一般的74系列TTL “与非”门的扇出系数100≈N 。

3-3 “与非”门三个输入端的波形如图题3-3所示,画出其输出端的波形。

Ω =5050k ΩΩ =20Ω =3015k (a )(b ) (c )图题3-1AC BB A CYY3-4 试分别指出TTL “与非”门的下列接法会造成什么后果,并说明原因:⑴ 输出端接地;⑵ 输出端接+5V 电源;⑶ 两个普通“与非”门的输出端短接。

解:⑴ 无论输出高、低电平,输出始终为低电平。

则无法实现“与非”逻辑功能。

⑵ 无论输出高、低电平,输出始终为高电平。

则无法实现“与非”逻辑功能。

⑶一般的TTL “与非”门是不允许将输出端直接连接在一起的。

因为,TTL “与非”门的输出电阻很小,不论在“与非”门导通还是截止状态,其输出电阻都在几欧姆到几十欧姆之间,若将它们的输出端直接相连,则当一个“与非”门输出高电平而另一个“与非”门输出低电平时,从电源CC U 到地之间则会形成一条低阻通路,将有一个很大的电流从截止“与非”门的4T 管流到导通“与非”门的5T 管,这个电流不仅会使导通“与非”门的输出低电平抬高,甚至会因功耗过大而把两个“与非”门都损坏。

3-5 有两个相同型号的TTL “与非”门,对它们进行测试的结果如下: ⑴ 甲的开门电平为1.4V ,乙的开门电平为1.5V ; ⑵ 甲的关门电平为1.0V ,乙的关门电平为0.9V 。

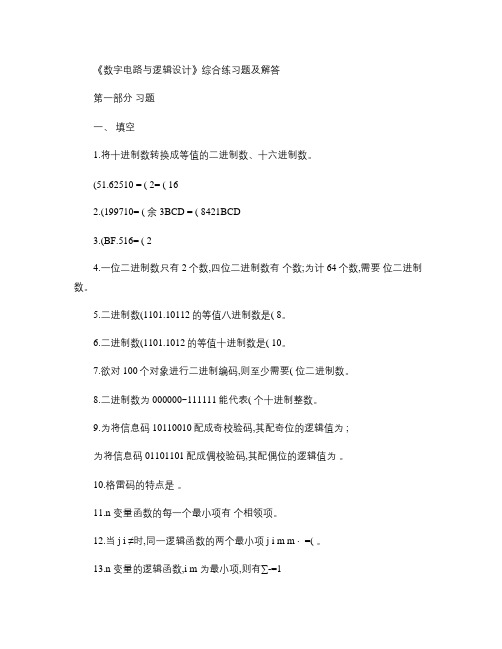

《数字电路与逻辑设计》综合练习题及解答

《数字电路与逻辑设计》综合练习题及解答第一部分习题一、填空1.将十进制数转换成等值的二进制数、十六进制数。

(51.62510 = ( 2= ( 162.(199710= ( 余3BCD = ( 8421BCD3.(BF.516= ( 24.一位二进制数只有2个数,四位二进制数有个数;为计64个数,需要位二进制数。

5.二进制数(1101.10112的等值八进制数是( 8。

6.二进制数(1101.1012的等值十进制数是( 10。

7.欲对100个对象进行二进制编码,则至少需要( 位二进制数。

8.二进制数为000000~111111能代表( 个十进制整数。

9.为将信息码10110010配成奇校验码,其配奇位的逻辑值为 ;为将信息码01101101配成偶校验码,其配偶位的逻辑值为。

10.格雷码的特点是。

11.n 变量函数的每一个最小项有个相领项。

12.当j i ≠时,同一逻辑函数的两个最小项j i m m ⋅=( 。

13.n 变量的逻辑函数,i m 为最小项,则有∑-=120n i i m =( 。

14.逻辑函数D C B A F ++=的反函数F = ( 。

15.逻辑函数(C B A F +=的对偶函数F '是 ( 。

16.多变量同或运算时, =0,则i x =0的个数必须为( 。

17.逻辑函数AB C B A F ⊕⊕=1,,(的最小项表达式为,,(C B A F =( 。

18. 逻辑函数14,12,0(10,8,4,3,2,1(,,,(∑∑Φ+=m D C B A F 的最简与或式为F =( 。

19.逻辑函数((,,(C B A C B A C B A F ++++=的最简与或式为( 。

20.巳知函数的对偶式BC D C B A D C B A F ++=',,,(,则它的原函数F =( 。

* * * * *21.正逻辑约定是( 、( 。

22.双极型三极管由截止状态过渡到饱和状态所需的过渡时间称为时间,它由时间和时间两部分组成,可用等式描述。

19春北理工《数字电子技术》在线作业答案

------------------------------------------------------------------------------------------------------------------------------ (单选题)1: 逐次逼近型A/D转换器转换开始时,首先应将()。

A: 移位寄存器最高位置1B: 移位寄存器的最低位置1C: 移位寄存器的所有位均置1D: 移位寄存器的所有位均置0正确答案:(单选题)2: 施密特触发器有()个稳定状态,多谐振荡器有()个稳定状态。

A: 2、0B: 0、2C: 1、0D: 0、1正确答案:(单选题)3: 若希望采用触发器设计一个六进制同步计数器,故需要()个触发器。

A: 3B: 2C: 6D: 4正确答案:(单选题)4: 可用于总线结构,分时传输的门电路是()。

A: 异或门B: 同或门C: OC门D: 三态门正确答案:(单选题)5: 逻辑式F=ABC可变换为()。

A: F=AB+CB: F=A+BCC: F=CBAD: F=A+B+C正确答案:(单选题)6: 欲使边沿JK触发器构成T’触发器,则只要使()。

A: JK=01B: JK=11C: JK=10D: JK=00正确答案:(单选题)7: 下列逻辑电路中为时序逻辑电路的是()。

A: 变量译码器B: 加法器C: 数码寄存器D: 数据选择器正确答案:(单选题)8: 由集成定时器555构成的单稳态触发器,加大定时电容C,则()。

------------------------------------------------------------------------------------------------------------------------------ A: 增大输出脉冲的幅度B: 增大输出脉冲的宽度C: 对输出脉冲无影响D: 减小输出脉冲的宽度正确答案:(单选题)9: n位的二进制加法计数器,能计数的最大十进制数是()。

《数字电路-分析与设计》第一章习题及解答 北京理工大学出版社

第一章习题1-1 例1.2.12中转换前后两个数的绝对值哪个大?为什么?答:转换前大。

因为转换后舍去了后边的小数位。

1-2 将下列二进制数分别转换为八进制数、十六进制数和十进制数。

11001101.101,10010011.1111解:(11001101.101)2 =(11 001 101.101)2= ( 315.5)8=(1100 1101.1010)2 =( CD.A)16=(128+64+8+4+1+0.5+0.125)10=(205.625)10(10010011.1111)2 =(1001 0011.1111)2= (93.F)16=(10 010 011.111 100)2 =( 223.74)8=(128+16+2+1+0.5+0.25+0.125+0.0625)10=(147.9375)101-3 将下列十进制数转换为二进制、八进制和十六进制数。

121.56,73.85解:1. 0Å1Å3Å7Å15Å30Å60Å121 0.56Æ0.12Æ0.24Æ0.48Æ0.96Æ0.921 1 1 1 0 0 1 1 0 0 0 1所以:(121.56)10=(1111001.10001)2=(171.42)8=(79.88)162. 0Å1Å2Å4Å9Å18Å36Å73 0.85Æ0.7Æ0.4Æ0.8Æ0.6Æ0.2Æ0.41 0 0 1 0 0 1 1 1 0 1 1 0(73.85)10=(1001001.11011)2=(111.66)8=(49.D8)161-4 将下列十六进制数转换为二进制、八进制和十进制数。

89.0F,E5.CD解:(89.0F)16=(10001001.00001111)2=(211.036)8=(8*16+9+15/256)10=(137. 0.05859375)10 1-5 试求例1.2.17的转换误差,比较例1.2.12的转换误差,哪个大?为什么?答:例1.2.12的误差大。

数字电路答案大全(DOC)

数字电路试卷答案大全试卷A一、选择题(从每小题的四个备选答案中,选出一个正确答案,并将其号码填在括号内,每小题2分,共20分)1.将十进制数(18)10转换成八进制数是 [ ]① 20 ② 22 ③ 21 ④ 23 2. 三变量函数()BC A C B A F+=,,的最小项表示中不含下列哪项 [ ]① m2 ② m5 ③ m3 ④ m7 3.一片64k ×8存储容量的只读存储器(ROM ),有 [ ]①64条地址线和8条数据线 ②64条地址线和16条数据线 ③16条地址线和8条数据线 ④16条地址线和16条数据线4.下列关于TTL 与非门的输出电阻描述中,正确的是 [ ] ①门开态时输出电阻比关态时大 ②两种状态都是无穷大输出电阻 ③门关态时输出电阻比开态时大 ④两种状态都没有输出电阻5.以下各种ADC 中,转换速度最慢的是 [ ]① 并联比较型 ② 逐次逼进型 ③ 双积分型 ④ 以上各型速度相同6. 关于PAL 器件与或阵列说法正确的是 [ ]① 只有与阵列可编程 ② 都是可编程的③ 只有或阵列可编程 ④ 都是不可编程的7. 当三态门输出高阻状态时,输出电阻为 [ ]① 无穷大 ② 约100欧姆 ③ 无穷小 ④ 约10欧姆8.通常DAC 中的输出端运算放大器作用是 [ ]① 倒相 ② 放大③ 积分 ④ 求和 9. 16个触发器构成计数器,该计数器可能的最大计数模值是 [ ]① 16 ② 32 ③ 162 ④ 216 10.一个64选1的数据选择器有( )个选择控制信号输入端。

[ ]① 6 ② 16 ③ 32 ④ 64 二、填空题(把正确的内容填在题后的括号内。

每空1分,共15分。

)1.已知一个四变量的逻辑函数的标准最小项表示为()()13,11,9,8,6,4,3,2,0,,,m d c b a F ∑=,那么用最小项标准表示=*F ,以及=F ,使用最大项标准表示F。

F,以及==2.具有典型实用意义的可编程逻辑器件包括,,,。

数字电路课后题参考答案

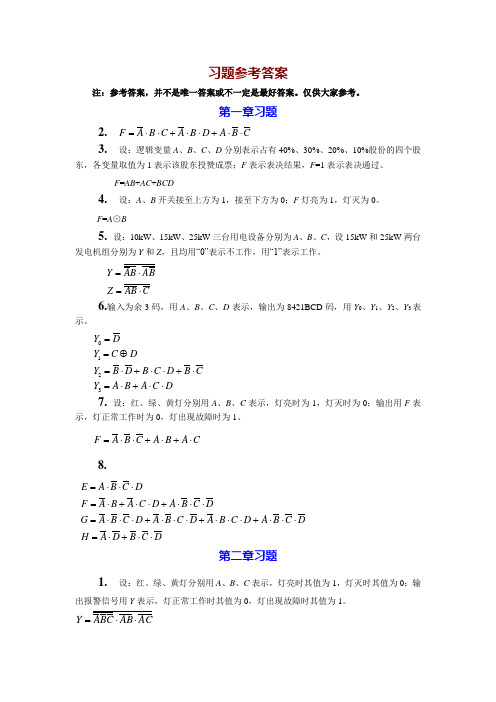

习题参考答案注:参考答案,并不是唯一答案或不一定是最好答案。

仅供大家参考。

第一章习题2. C B A D B A C B A F ⋅⋅+⋅⋅+⋅⋅=3. 设:逻辑变量A 、B 、C 、D 分别表示占有40%、30%、20%、10%股份的四个股东,各变量取值为1表示该股东投赞成票;F 表示表决结果,F =1表示表决通过。

F =AB +AC +BCD4. 设:A 、B 开关接至上方为1,接至下方为0;F 灯亮为1,灯灭为0。

F =A ⊙B5. 设:10kW 、15kW 、25kW 三台用电设备分别为A 、B 、C ,设15kW 和25kW 两台发电机组分别为Y 和Z ,且均用“0”表示不工作,用“1”表示工作。

C AB Z BA B A Y ⋅=⋅=6.输入为余3码,用A 、B 、C 、D 表示,输出为8421BCD 码,用Y 0、Y 1、Y 2、Y 3表示。

D C A B A Y CB DC BD B Y DC Y DY ⋅⋅+⋅=⋅+⋅⋅+⋅=⊕==32107. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时为1,灯灭时为0;输出用F 表示,灯正常工作时为0,灯出现故障时为1。

C A B A C B A F ⋅+⋅+⋅⋅=8. D C B D A H DC B AD C B A D C B A D C B A G DC B AD C A B A F DC B A E ⋅⋅+⋅=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=⋅⋅⋅+⋅⋅+⋅=⋅⋅⋅=第二章习题1. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时其值为1,灯灭时其值为0;输出报警信号用Y 表示,灯正常工作时其值为0,灯出现故障时其值为1。

AC AB C B A Y ⋅⋅=2. 设:烟、温度和有害气体三种不同类型的探测器的输出信号用A 、B 、C 表示,作为报警信号电路的输入,有火灾探测信号时用1表示,没有时用0表示。

报警信号电路的书躇用Y 表示,有报警信号时用1表示,没有时用0表示。

《数字电路-分析与设计》第五章习题及解答(部分) 北京理工大学出版社

5-15画出图题5-15所示电路在给定输入波形作用下的输出端Y的波形。设触发器的初始状态均为0。

解:先写出Q’和Y的状态方程:第一个触发器结成了T’触发器,Q’n+1=Q’;第二个触发器的K=1,所以Yn+1=Q’Y,再根据状态方程画波形即可.注意1.两个触发器的时钟;2.第一个触发器的清0信号;3.画时序图时,将Q’作为辅助变量画出。

第五章习题

5-1图题5-1所示为由或非门组成的基本R-S锁存器。试分析该电路,即写出它的状态转换表、状态转换方程、状态图、驱动转换表和驱动方程,并画出它的逻辑符号,说明S、R是高有效还是低有效。

解:状态转换表:

状态转换驱动表

5-2试写出主从式R-S触发器的状态转换表、状态转换方程、状态图、驱动转换表和驱动方程,注意约束条件。

解:略。

5-12用一个T触发器和一个2-1多路选择器构成一个JK触发器。

解:T=JQ+KQ

也Hale Waihona Puke 用Q作为选择输入。5-13试用一个D触发器、一个2-1多路选择器和一个反相器构成一个JK触发器。

解:D=JQ+KQ,用Q或Q做选择输入即可。参见5-12。

5-14设图题5-14中各触发器的初始状态均为0,试画出在CP信号作用下各触发器Q端的输出波形。

JKD, DT, TD, JKT, JKT’, DT’。

解:JKD:Qn+1=JQ+KQ,D:Qn+1=D=DQ+DQ。

令两个状态方程相等:D=DQ+DQ =JQ+KQ。

对比Q、Q的系数有:J=D,K=D

逻辑图略。

5-11试用驱动表法完成下列触发器功能转换:

数字电路习题参考答案详解

第27页,共29页。

4.24 判断用下列函数构成的电路是否存在冒险?冒险的类型?

(1)F=AB+ABC

AC

F

00

0

01

0

10

B

1 1 B+B

0型冒险

(4)F=AB+AB

11 0 0 1 1

10 1 0 0 1

D1 D3 D7 D5

10

D

第25页,共29页。

(3)三变量多数表决电路。

AB

D0 D2 D6 D4

C 00 01 11

0 100 0 1 0

1 0 1 01 1

D1 D3 D7 D5

10

第26页,共29页。

4.23 用数据选择器组成的电路如图所示,求输出Y 的表达式。

又Si m1 m2 m4 m7 Ai BiCi1 Ai BiCi1 Ai BiCi1 Ai BiCi1

比较得: D0=D3= Ci-1 D1=D2= Ci-1

且 Ci m3 m5 Ai Bi Ai BiCi1 Ai BiCi1 Ai Bi

Y m0 D0 m1D1 m2 D2 m3D3

D0 B 0 0 1 1 0 1 1111

D1 1

D2 B D3 1

A C

B1

第22页,共29页。

(4)二变量异或表达式。

A

B

0

00

1 AB

1

11 0

D0=0

AB

D3=0

数字电路分析与设计_浙江大学中国大学mooc课后章节答案期末考试题库2023年

数字电路分析与设计_浙江大学中国大学mooc课后章节答案期末考试题库2023年1.若对8个特定对象进行编制,应该选择位二进制编码器。

参考答案:32.使逻辑函数【图片】为1的最小项有个参考答案:7##%_YZPRLFH_%##七3.条件中不可能出现的组合称为任意项,条件中不允许出现的组合称为约束项,约束项和任意项统称为无关项。

参考答案:正确4.将逻辑函数L=AB+AC+BC用卡诺图表示为:【图片】参考答案:正确5.和逻辑式【图片】相等的是参考答案:B6.已知N的反码为10110011,则补码为01001101。

参考答案:错误7.十进制数(-10)10的二进制补码表示为:参考答案:(10110)28.判断对错:D/A转换器输出模拟量的大小只取决于输入的数字量。

参考答案:错误9.执行Quartus II的______命令,可以检查设计电路错误。

参考答案:Compiler10.CPLD和FPGA器件______。

参考答案:在系统加电时可以对器件的内容进行重构11.某中规模集成计数器74HCXX的功能表和简化逻辑符号如下所示。

【图片】用该集成计数器连接而成的电路如下图所示。

该电路是(同步/异步)、(加法/减法)计数器;其中74HCXX(I)片连接成进制计数器;整个电路是进制计数器。

(答案间用中文分号隔开)【图片】参考答案:异步;加法;10;4412.已知集成计数器74HC193的功能表和引脚图如下所示,若利用反馈置数法设计一个余3码编码的10进制加计数器,则需要在输出Q3Q2Q1Q0=()时使置数端【图片】置为(),并将数据输入端D3D2D1D0置为()。

(答案间用中文分号隔开)【图片】【图片】参考答案:1101;0;001113.下列A/D转换器速度最快的是()。

参考答案:并行比较型A/D转换器14.用4选一的数据选择器扩展成16选一的数据选择器,若不加其它门电路,则最少需要()片4选一数据选择器。

参考答案:515.用中规模集成计数器74LS192构成的电路如图所示,则该电路功能为进制法(加/减)计数器。

数字电路逻辑设计课后答案

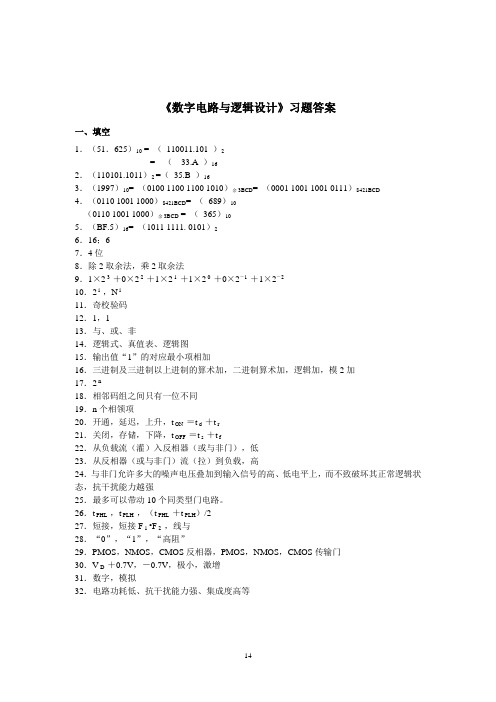

《数字电路与逻辑设计》习题答案一、填空1.(51.625)10 = (110011.101 )2= (33.A )162.(110101.1011)2 =(35.B )163.(1997)10= (0100 1100 1100 1010)余3BCD= (0001 1001 1001 0111)8421BCD 4.(0110 1001 1000)8421BCD= (689)10(0110 1001 1000)余3BCD = (365)105.(BF.5)16= (1011 1111. 0101)26.16;67.4位8.除2取余法,乘2取余法9.1×2 3 +0×2 2 +1×2 1 +1×2 0 +0×2-1 +1×2-210.2 i ,N i11.奇校验码12.1,113.与、或、非14.逻辑式、真值表、逻辑图15.输出值“1”的对应最小项相加16.三进制及三进制以上进制的算术加,二进制算术加,逻辑加,模2加17.2 n18.相邻码组之间只有一位不同19.n个相领项20.开通,延迟,上升,t ON =t d +t r21.关闭,存储,下降,t OFF =t s +t f22.从负载流(灌)入反相器(或与非门),低23.从反相器(或与非门)流(拉)到负载,高24.与非门允许多大的噪声电压叠加到输入信号的高、低电平上,而不致破坏其正常逻辑状态,抗干扰能力越强25.最多可以带动10个同类型门电路。

26.t PHL ,t PLH ,(t PHL +t PLH)/227.短接,短接F 1 •F 2 ,线与28.“0”,“1”,“高阻”29.PMOS,NMOS,CMOS反相器,PMOS,NMOS,CMOS传输门30.V D+0.7V,-0.7V,极小,激增31.数字,模拟32.电路功耗低、抗干扰能力强、集成度高等33.V NL= V iL(max) -V oL(max)34.电路任一时刻的输出仅取决于该时刻的输入状态,而与电路前一时刻的状态无关35.只包含门电路(无存储元件)36.37.确定它的逻辑功能,并加以改进38.两数的本位加,不带低位的进位加,带进位加39.16个,低电平“0”,高电平“1”40.它们都有两个稳态,可以触发翻转,故具有记忆能力41.特性表、特性方程、波形图42.D、T'、T、RS、JK43.可以用CP控制其翻转时刻,同步触发器、主从触发器、边沿触发器,电平触发、主从触发、边沿触发44.主从、边沿触发器可以克服空翻,而同步触发器不能克服空翻45.两门之间因交叉耦合而产生的自锁作用46.RS=0,R、S不能同时为“1”47.0,148.可控制的计数,计数翻转,保持原状态49.下降,上升,150.边沿触发方式51.同步时序电路,异步时序电路52.触发器53.统计计数脉冲个数54.Q i-1 Q i-2‥‥‥Q 1 Q 0 ,Q n-1 Q n-2 ‥‥‥Q 1Q 055.暂存,平移56.串/并转换57.16μS58.波形变换、整形、脉冲鉴幅二、选择题:1. A D2. B C D3. A B4. D5. C6. A B D7. D.8. C9. B10. D11. B12. A.13. B14. A B三、化简下列各题1.用代数法化简下列函数为最简与或表达式(1)F=A B+B C+AC=B(A+C)+AC=B AC+AC=B+AC(2)F=C D+CD+C D+C D=(C D+C D)+(CD+C D)=C+C=1(3)F=AB C+AB+B C+AC=AB+B C+AC=AB+B C(4)F=A+CDAD=A+BCD+AD+B+B+B=A+B2.将下列函数式化为最小项表达式(1)F=AB+BC+AC=AB(C+C)+(A+A)BC+A(B+B)C =ABC+AB C+A BC+A B C(2)F=BCAB =AB+BC=AB(C+C)+(A+A)BC=ABC+AB C+A BC3.用代数法证明下列等式(1)左式=(A B+B)+(A CD+C)+D=A+B+A D+C+D=A +B +D +C +D=1(2)A ⊕0=A ·0+A ·1=A(3)A ⊕1=A ·1+A ·1 =A(4)A ⊕A =A ·A +A ·A=A +A =14.直接写出下列各函数的对偶式F',并用反演规则写出其反演式F(1)F'=(A +B )(B +C )(C +A D )F =(A +B )(B +C )(C +A D )(2)F'=A ·)+(E D C BF =A ·)+(E D C B5.用对偶规划求下列各式的对偶等式(1)左式的对偶式为(A +B )(A +C )(B +C +D )右式的对偶式为(A +B )(A +C )∴其对偶等式为:(A +B )(A +C )(B +C +D )=(A +B )(A +C )(根据对偶规则两式相等,则其对偶式也相等)(2)左式的F'1 =C B A ⋅⋅右式的F'2 =A +B +C其对偶等式为:C B A ⋅⋅=A +B +C6.试写出下列卡诺图的最小项表达式,并用卡诺图法求其最简与或式(1)最小项表达式F (A 、B 、C )=∑),,,,(54310 或F =A B C +A B C +A BC +A B C +A B C 最简与或式F =A C +B(2)最小项表达式F (A 、B 、C 、D )=),,,,,(1086420∑或F =A B C D +A B C D +A B C D +A BC D +A B C D +A B C D ;最简与或式F =B D +A D7.用卡诺图法化简下列函数为最简与或式(1)F =A B C +AD +D (B +C )+A C +A D =A +B C +D(2)10157φ32869)+(,(11,,,,,,,=A B+A C+B D+CD9.(1)错(2) 错(3) 对10.⋅⋅=+F⋅BCBAC1⋅B=C+⊕F⋅BCA2+⋅=3⋅⋅BCF⋅ACBA11.当控制信号BC=00时,输出是输入变量的反码。