体系结构试验报告(cache存储过程)

计算机组成原理cache课程报告

计算机组成原理课程报告学号:班级:姓名:Cache的发展历程及应用在计算机组成原理课学过Cache之后我才发现原来我对Cache了解的如此之少,以前在买电脑时经常看到一级缓存、二级缓存和三级缓存,然而当时并不懂这是什么东西,现在学过Cache 之后才知道了缓存在电脑中的地位.原来Cache在提高计算机速度方面有如此大的作用。

那么就让我们来了解一下Cache的发展历程。

经过我查资料得知,Cache一词来源于法语,其原意是“藏匿处,隐秘的地方”,而自从被应用于计算机科学之后,就已经成为了英语中的一个计算机体系结构专有名词。

Sun Microsystems 的前首席科学家Billy Joy,作为BSD unix,csh,vi,NFS,java,TCP/IP等的发明者,他曾经说过,在计算机科学领域,如果没有了cache的发明,其他的一切发明都将失去意义。

而正是他,将给予分页的虚拟内存系统引入了Unix,影响了之后所有的新操作系统开发。

Cache的出现正是为了解决CPU日益增长的核心时钟频率以及系统主内存日益落后的速度之间的矛盾①。

这就是Cache解决的主要问题。

那么,这个问题是怎样显现出来以及Cache是如何出现的呢?纵观PC系统和CPU二十年的发展,随着半导体加工工艺水平的不断提高,集成电路技术的不断进步,导致生产成本不断降低,CPU的功能不断增强,运算速度越来越快,CPU和存储器的性能都有了很大的提高。

CPU频率的提高,必然要求系统中存储器的存取速度要提高,还要求其容量要增大。

主存储器DRAM容量的提高还是比较快的,但是DRAM读取时间的提高却很慢。

从而在速度上与CPU主频的提高产生了极不相配的情况,这样会影响整个系统的性能.二十年来,CPU 设计的问题之一就是解决高速CPU和低速DRAM之间的平衡或匹配问题,以求系统性能的整体提高。

在它们之间加入高速缓冲存储器Cache,就是这个问题的解决方案之一。

cache硬件设计实验总结

cache硬件设计实验总结

一、实验内容

本次实验主要是简单熟悉cache硬件设计的基础,以及学习cache在系统中的应用。

学习的主要内容有:

1、cache硬件结构,包括cache的分类、cache的结构及工作原理;

2、cache替换算法的概述;

3、cache的动态优化。

二、实验目的

通过本次实验,学生可以掌握cache的硬件结构,理解cache 的替换算法,以及cache的动态优化,为以后学习更深入的cache 知识打下扎实的基础。

三、实验过程

1、首先,学生阅读有关cache硬件结构的相关资料,理解cache的分类、结构及工作原理;

2、然后,学生学习cache的替换算法,如最近最久未使用(LRU)、先进先出(FIFO)、最佳置换(OPT)等;

3、接着,学生了解cache的动态优化,学习cache置换算法的变种,以及新型cache技术,如组织优化(Organize)、负载均衡(Load Balance)等;

4、最后,学生自己动手实现cache的编程,并用调试工具检测cache的程序是否正确。

四、实验总结

经过本次实验,我们对cache的硬件结构、替换算法、动态优化有了更加全面的认识,并且深入理解了cache在系统中的应用,锻炼了我们的编程能力。

同时,我们在实验中,也提升了自己的专业技能,为以后学习打下扎实的基础。

计算机组成原理实验报告_存储系统设计实验

实验四存储系统设计实验一、实验目的本实训项目帮助大家理解计算机中重要部件—存储器,要求同学们掌握存储扩展的基本方法,能设计MIPS 寄存器堆、MIPS RAM 存储器。

能够利用所学习的cache 的基本原理设计直接相联、全相联,组相联映射的硬件cache。

二、实验原理、内容与步骤实验原理、实验内容参考:1、汉字字库存储芯片扩展设计实验1)设计原理该实验本质上是8个16K×32b 的ROM 存储系统。

现在需要把其中一个(1 号)16K×32b 的ROM 芯片用4个4K×32b 的芯片来替代,实际上就是存储器的字扩展问题。

a) 需要4 片4个4K×32b 芯片才可以扩展成16K×32b 的芯片。

b) 目标芯片16K个地址,地址线共14 条,备用芯片12 条地址线,高两位(分线器分开)用作片选,可以接到2-4 译码器的输入端。

c) 低12 位地址直接连4K×32b 的ROM 芯片的地址线。

4个芯片的32 位输出直接连到D1,因为同时只有一个芯片工作,因此不会冲突。

芯片内数据如何分配:a) 16K×32b 的ROM 的内部各自存储16K个地址,每个地址里存放4个字节数据。

地址范围都一样:0x0000~0x3FFF。

b) 4个4K×32b 的ROM,地址范围分别是也都一样:0x000~0xFFF,每个共有4K个地址,现在需要把16K×32b 的ROM 中的数据按照顺序每4个为一组分为三组,分别放到4个4K×32b 的ROM 中去。

HZK16_1 .txt 中的1~4096个数据放到0 号4K 的ROM 中,4097~8192 个数据放到 1 号4K 的ROM 中,8193~12288 个数据放到2 号4K 的ROM 中,12289~16384个数据放到3 号4K 的ROM 中。

c) 注意实际给的16K 数据,倒数第二个4K(8193~12288 个数据)中部分是0,最后4K(12289~16384 数据)全都是0。

存储过程的使用 实验报告

USEypp7

--声明四个变量,用于保存输入和输出参数

DECLARE@KECHENGMINGvarchar(20)

DECLARE@AVGCHENGJI1tinyint

DECLARE@MAXCHENGJI1tinyint

DECLARE@MINCHENGJI1tinyint

--为输入参数赋值

SELECT@KECHENGMING='高等数学'

--声明四个变量,用于保存输入和输出参数

DECLARE@KECHENGMINGvarchar(20)

DECLARE@AVGCHENGJI1tinyint

DECLARE@MAXCHENGJI1tinyint

DECLARE@MINCHENGJI1tinyint

--为输入参数赋值

SELECT@KECHENGMING='计算机基础'

1.使用if exists语句,如果存储过程“单科成绩分析”存在,就将其删除;

2.使用create proc语句创建存储过程;

3.定义所需要的输入参数和输出参数;

4.声明4个变量来保存输入和输出参数;

5.执行存储过程并显示结果。

同时,值得注意的是,在创建存储过程时,应该注意一些细节,如单词的拼写要准确无误,程序中用的是单引号而不是双引号等等。

--执行存储过程

EXEC单科成绩分析@KECHENGMING,

@AVGCHENGJI1OUTPUT,

@MAXCHENGJI1OUTPUT,

@MINCHENGJI1OUTPUT

--显示结果

SELECT@KECHENGMINGAS课程名,@AVGCHENGJI1AS平均成绩,@MAXCHENGJI1AS最高成绩,

计算机系统结构实验2报告

实

验

内

容

、

步

骤

及

结

果

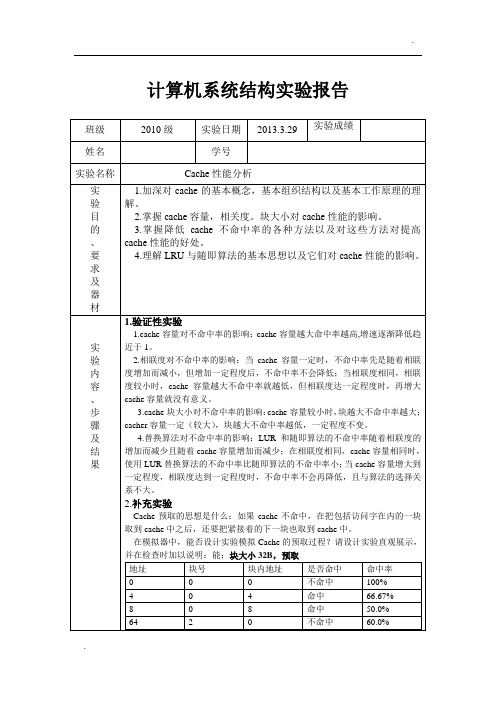

1.验证性实验

1.cache容量对不命中率的影响:cache容量越大命中率越高,增速逐渐降低趋近于1。

2.相联度对不命中率的影响:当cache容量一定时,不命中率先是随着相联度增加而减小,但增加一定程度后,不命中率不会降低;当相联度相同,相联度较小时,cache容量越大不命中率就越低,但相联度达一定程度时,再增大cache容量就没有意义。

计算机系统结构实验报告

班级

2010级

实验日期

2013.3.29

实验成绩

姓名

学号

实验名称

Cache性能分析

实

验

目

的

、

要

求

及

器

材

1.加深对cache的基本概念,基本组织结构以及基本工作原理的理解。

2.掌握cache容量,相关度。块大小对cache性能的影响。

3.掌握降低cache不命中率的各种方法以及对这些方法对提高cache性能的好处。

3.思考题(调研内容)

Intel 酷睿i7 3610QM:3层cache,一层128kb,二层512kb,三层6M(共享)AMD 羿龙II X4 N970:2层cache,1层128kb,2层2M.

都是分离cache。

4.探究性实验

块大小

统一cache

独立cache

64kb

0.89%

0.79%

128kb

100%

4

0

4

命中

66.67%

8

0

8

命中

计算机系统结构课程实验报告实验二:存贮层次模拟器

计算机系统结构课程实验报告2012—2013 学年第 1 学期学生姓名:学生班级:2011179学生学号:**********师:***教研室:计算机系统结构教研室2012年10月23日实验二:存贮层次模拟器一、实验目的与要求使学生清楚认识虚拟存贮层次结构,熟练掌握常用的几种存储地址映象与变换方法,以及FIFO、LRU等替换算法的工作全过程。

要求用程序实现任意地址流在存储层次上的命中情况,实验结束后提交源程序和实验说明书。

二、实验内容在模拟器上实现在任意地址流下求出在cache-主存—辅存三层存贮层次上的命中率。

三、实验步骤1.主存-辅存:映像方式可以选择组相联方式;替换算法可以使用LRU算法和FIFO算法。

2.要求主存容量、页大小以及组数等可以输入修改。

3.求出命中率;显示替换的全过程;任选一种高级语言来做。

4.要有简洁、易于操作的界面。

四、程序源代码#include<stdio.h>#include<string.h>#include <iostream.h>struct Fu{int gh;//组号int gnh;//组内块号int kd;//块内地址};Fu c[50];int count[50];//计数器int d[50];//地址流int Groupfind(int mainAddr,int FuSize,int bsINg){return mainAddr%FuSize/bsINg;}void InitFu(int bsINg,int FuSize){for(int i=0;i<FuSize;i++){c[i].kd=-1;//块内地址初始化为-1c[i].gnh=i%bsINg;//组内块号初始化为c[i].gh=i/bsINg;//组号count[i]=0;}int Find(int gh,int bsINg){int index=0+gh*bsINg;int max=count[index];for(int i=0+gh*bsINg;i<0+gh*bsINg+bsINg;i++){if(count[i]>max){max=count[i];index=i;}}return index;}int IsFull(int gh,int bsINg){for(int i=0+gh*bsINg;i<0+gh*bsINg+bsINg;i++){if(c[i].kd==-1)return i;}return -1;}void AddCount(int gh,int bsINg){for(int i=0+gh*bsINg;i<0+gh*bsINg+bsINg;i++)if (c[i].kd!=-1){count[i]++;}}int IsShoot(int mainAddr,int gh,int bsINg){for(int i=0+gh*bsINg;i<0+gh*bsINg+bsINg;i++)if (c[i].kd==mainAddr){return i;}return -1;}void LRU1(int mainAddr,int groups,int FuSize,char* src,int type,int bsINg,double &shoot)//kd地址流中的一个,int gh=Groupfind(mainAddr,FuSize,bsINg);//找到组号int i=-1;int j=-1;i=IsShoot(mainAddr,gh,bsINg);j=IsFull(gh,bsINg);if (i!=-1)//命中{//命中if(type==0){AddCount(gh,bsINg);count[i]=0;}c[i].kd=mainAddr;strcpy(src,"命中");shoot++;return;}if (j!=-1)//调进{AddCount(gh,bsINg);count[j]=0;c[j].kd=mainAddr;strcpy(src,"调进");return;}int k;k=Find(gh,bsINg);AddCount(gh,bsINg);count[k]=0;c[k].kd=mainAddr;strcpy(src,"替换");}void DisplayTitle(){cout<<"辅存-主存映像关系组相联方式"<<endl;}void Display(char* src,int cl){for (int i=0;i<cl;i++){cout<<c[i].kd<<"\t";cout<<src<<endl;}void DisplayHead(int cl){for (int i=0;i<cl;i++){cout<<i<<"\t";}cout<<endl;}void main(){char src[5];int type;int g,cl;int bsINg;int MainSize;int addr;int i=0;double shoot=0;DisplayTitle();cout<<"选择LRU(0)or FIFO(1):";cin>>type;cout<<"输入辅存大小:";cin>>MainSize;cout<<"输入主存大小:";cin>>cl;cout<<"输入组数:";cin>>g;bsINg=cl/g;cout<<"输入地址流(以-1结束):";cin>>addr;while(addr!=-1){d[i++]=addr;cin>>addr;}InitFu(g,cl);DisplayHead(cl);for (int j=0;j<i;j++){LRU1(d[j],g,cl,src,type,bsINg,shoot);Display(src,cl);cout<<"命中率:"<<shoot/i<<endl;}四、实验截图1、当替换算法采用FIFO,主存的组数为1,则结果如下图所示:2、当替换算法采用LRU,主存的组数为1,则结果如下图所示:3、当替换算法采用FIFO,主存的组数为2,则结果如下图所示:4、当替换算法采用FIFO,主存的组数为2,则结果如下图所示:五、实验总结通过本次实验我搞清楚了虚拟存贮层次结构,掌握了常用的几种存储地址映象与变换方法,以及FIFO、LRU等替换算法的工作全过程。

cache实验报告

cache实验报告Cache实验报告一、引言计算机系统中的缓存(Cache)是一种用于提高数据访问速度的技术。

通过在CPU与主存之间插入一个高速缓存存储器,可以减少CPU等待主存数据的时间,从而提高系统的整体性能。

本实验旨在通过实际操作,深入了解并掌握Cache的工作原理。

二、实验目的1. 了解Cache的基本概念和工作原理;2. 学习Cache的组织结构和映射方式;3. 掌握Cache的读写操作流程;4. 分析Cache的命中率和访问延迟。

三、实验环境本实验使用Intel Core i7处理器和8GB内存的计算机。

四、实验步骤1. 确定实验所需的Cache参数,包括Cache大小、Cache块大小和关联度等;2. 设计并编写测试程序,用于模拟不同的内存访问模式;3. 运行测试程序,并记录Cache的读写命中次数和访问延迟;4. 分析实验结果,计算Cache的命中率和平均访问延迟。

五、实验结果与分析1. Cache命中率根据实验数据统计,我们可以计算出Cache的命中率。

命中率是指在所有内存访问中,Cache能够直接从Cache中读取数据的比例。

通过调整Cache的大小和关联度等参数,可以观察到命中率的变化。

实验结果表明,增加Cache的大小和提高关联度可以显著提高命中率。

2. 访问延迟访问延迟是指从CPU发出内存读写请求到实际完成读写操作所需的时间。

通过实验测量,我们可以得到不同访问模式下的平均访问延迟。

实验结果显示,随着Cache大小的增加,访问延迟逐渐减少。

这是因为Cache能够更快地响应CPU的读写请求,减少了CPU等待主存数据的时间。

3. 性能优化通过实验结果的分析,我们可以发现一些性能优化的方法。

首先,合理设置Cache的大小和关联度,可以提高命中率和降低访问延迟。

其次,采用合适的替换算法(如LRU)可以减少缓存失效的次数,提高Cache的效率。

此外,程序的空间局部性和时间局部性对Cache的性能也有重要影响,优化算法和数据结构可以提高程序的局部性,从而提高Cache的命中率。

计算机体系结构cache模拟器实验报告

计算机体系结构——Cache模拟器实验实验报告姓名崔雪莹学号班级计科1202班老师董岚2015年 06月07日一、阅读分析附件模拟器代码...............................错误!未定义书签。

1、关键参数.......................................错误!未定义书签。

2、关键算法.......................................错误!未定义书签。

二、课后习题.............................................错误!未定义书签。

1、习题内容.......................................错误!未定义书签。

2、题目分析.......................................错误!未定义书签。

3、计算及结果.....................................错误!未定义书签。

4、模拟器上实验结果检验...........................错误!未定义书签。

三、整体分析.............................................错误!未定义书签。

1、三种映射方式对Cache效率的的影响...............错误!未定义书签。

2、block块大小与Cache容量对Cache效率的影响 .....错误!未定义书签。

3、Cache容量与相连度对Cache效率的影响...........错误!未定义书签。

4、三种失效类型影响因素...........................错误!未定义书签。

四、实验思考和感受.......................................错误!未定义书签。

1、关于模拟器的思考...............................错误!未定义书签。

存储过程实验报告_总结(3篇)

第1篇一、实验背景随着数据库技术的不断发展,存储过程在数据库管理中的应用越来越广泛。

存储过程是一组为了完成特定功能的SQL语句集合,它具有提高数据库性能、增强安全性、简化应用开发等优点。

为了更好地掌握存储过程的应用,我们进行了本次实验。

二、实验目的1. 理解存储过程的概念、特点和应用场景。

2. 掌握存储过程的创建、执行、修改和删除方法。

3. 学习使用存储过程实现常见的数据库操作,如数据插入、查询、更新和删除。

4. 熟悉存储过程中的流程控制语句、循环语句和游标操作。

三、实验环境1. 操作系统:Windows 102. 数据库:MySQL 5.73. 开发工具:MySQL Workbench四、实验内容1. 创建存储过程2. 执行存储过程3. 修改存储过程4. 删除存储过程5. 存储过程中的流程控制语句6. 存储过程中的循环语句7. 存储过程中的游标操作五、实验步骤1. 创建存储过程首先,我们创建一个简单的存储过程,用于查询特定部门的所有员工信息。

```sqlCREATE PROCEDURE GetEmployeeInfo(IN dept_id INT)BEGINSELECT FROM employees WHERE department_id = dept_id;END;```在此过程中,我们使用了`IN`参数,表示该参数在调用存储过程时传入。

2. 执行存储过程创建存储过程后,我们可以通过以下命令执行它:```sqlCALL GetEmployeeInfo(10);```这将查询部门ID为10的所有员工信息。

3. 修改存储过程如果需要修改存储过程,可以使用`ALTER PROCEDURE`语句。

例如,将查询条件修改为按姓名查询:```sqlALTER PROCEDURE GetEmployeeInfo(IN emp_name VARCHAR(50))BEGINSELECT FROM employees WHERE name = emp_name;END;```4. 删除存储过程删除存储过程可以使用`DROP PROCEDURE`语句。

cache硬件设计实验总结

cache硬件设计实验总结Cache硬件设计实验总结Cache是计算机系统中的一种高速缓存,用于存储最近被访问的数据,以提高计算机系统的性能。

在计算机系统中,CPU访问内存的速度比访问Cache的速度慢得多,因此,Cache的设计对于计算机系统的性能至关重要。

本文将对Cache硬件设计实验进行总结。

实验目的本次实验的目的是设计一个Cache硬件,实现Cache的读写操作,并测试Cache的性能。

具体实验要求如下:1. 设计一个Cache硬件,包括Cache的大小、块大小、组数、替换策略等参数的设置。

2. 实现Cache的读写操作,包括Cache的读取、写入和替换等操作。

3. 测试Cache的性能,包括Cache的命中率、访问时间等指标。

实验过程1. Cache硬件设计在本次实验中,我们设计了一个4KB大小的Cache,块大小为16B,共有256组。

采用的替换策略是LRU(Least Recently Used,最近最少使用)。

具体的Cache硬件设计如下:(1)Cache的地址结构Cache的地址结构包括标记位、组索引和块内偏移量。

在本次实验中,我们采用了直接映射的Cache结构,因此组索引的位数为8位,块内偏移量的位数为4位。

标记位的位数为16-8-4=4位。

(2)Cache的数据结构Cache的数据结构包括标记位、有效位、块内数据和LRU计数器。

标记位用于存储主存地址的高位,有效位用于表示Cache中的数据是否有效,块内数据用于存储主存地址对应的数据,LRU计数器用于记录Cache中每个块的使用情况。

2. Cache的读写操作Cache的读写操作包括Cache的读取、写入和替换等操作。

具体的操作流程如下:(1)Cache的读取操作当CPU需要读取主存中的数据时,首先会查询Cache中是否存在该数据。

如果存在,则直接从Cache中读取数据;如果不存在,则从主存中读取数据,并将数据存储到Cache中。

体系结构试验报告(cache存储过程)

体系结构实验报告实验目的通过程序,模拟cache存储过程,并通过控制变量法模拟分析Cache性能实验步骤:我们要通过老师所给程序进行模拟,并通过操作系统试验中老师所给算法生成出project.txt,并通过project.txt里面的数据来模拟程序的局部性等特性。

一、实验结果1、比较关联方式,控制blockSize, CacheSize不变:(1)、Direct_mapped:(2)、Set_associate:(3)、Fully_associate通过上述三个比较可以看出,各种映射有自己的优点。

但是不难看出,增大关联度会减小miss rate,但是增加到一定程度又会有抑制作用。

2.比较Cache大小对于性能的影响。

(1)、Direct_mapped,Cache容量为64时:(2)、Direct_mapped,Cache容量为128时:(3)、Direct_mapped,Cache容量为256时:对比实验结果,不难发现,随着Cache容量的增加,Cache的命中率一直在提升。

分析原因发现,虽然Cache容量大了,但并不等于其预存的内容增多,所以命中率会上升。

3、比较Cache大小对于性能的影响。

(1)、Direct_mapped,关联度为1时:(2)、Direct_mapped,关联度为2时:(3)、Direct_mapped,关联度为4时:(4)、Direct_mapped,关联度为8时:(5)、Direct_mapped,关联度为16时:可以看出,随着关联度的提高,命中率也有所增加。

4、比较block Number对于Cache性能影响。

(1)、Direct_mapped, block number为1时:(2)、Direct_mapped, block number为2时:(1)、Direct_mapped, block number为4时:通过以上三组数据不难看出,当block number增加时,命中率明显增高了。

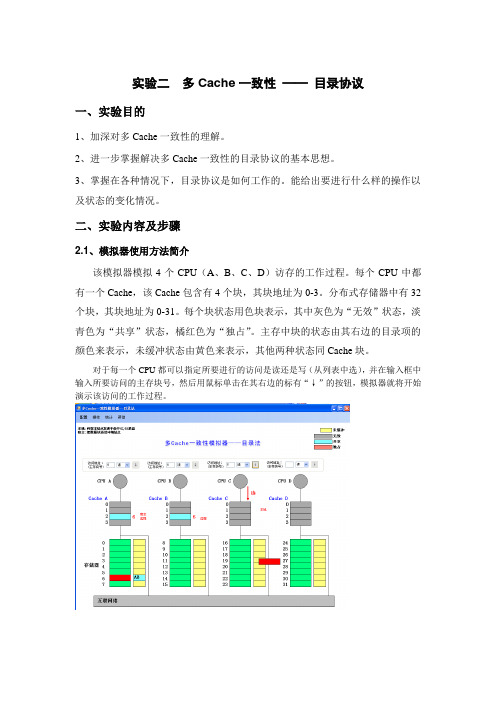

系统结构实验二报告 多Cache一致性 —— 目录协议

实验二多Cache一致性——目录协议一、实验目的1、加深对多Cache一致性的理解。

2、进一步掌握解决多Cache一致性的目录协议的基本思想。

3、掌握在各种情况下,目录协议是如何工作的。

能给出要进行什么样的操作以及状态的变化情况。

二、实验内容及步骤2.1、模拟器使用方法简介该模拟器模拟4个CPU(A、B、C、D)访存的工作过程。

每个CPU中都有一个Cache,该Cache包含有4个块,其块地址为0-3。

分布式存储器中有32个块,其块地址为0-31。

每个块状态用色块表示,其中灰色为“无效”状态,淡青色为“共享”状态,橘红色为“独占”。

主存中块的状态由其右边的目录项的颜色来表示,未缓冲状态由黄色来表示,其他两种状态同Cache块。

对于每一个CPU都可以指定所要进行的访问是读还是写(从列表中选),并在输入框中输入所要访问的主存块号,然后用鼠标单击在其右边的标有“↓”的按钮,模拟器就将开始演示该访问的工作过程。

2.2、目录协议基本思想(自己补充)2.3、实验步骤对于以下访问序列,写出目录协议所进行的操作。

实验二多Cache一致性——监听协议一、实验目的1、加深对多Cache一致性的理解。

2、进一步掌握解决多Cache一致性的监听协议的基本思想。

3、掌握在各种情况下,监听协议是如何工作的。

能给出要进行什么样的操作以及状态的变化情况。

二、实验内容及步骤2.1、模拟器简介该模拟器模拟4个CPU(A、B、C、D)访存的工作过程。

每个CPU中都有一个Cache,该Cache包含有4个块,其块地址为0-3。

集中共享存储器中有32个块,其块地址为0-31。

每个块状态用色块表示,其中灰色为“无效”状态,淡青色为“共享”状态,橘红色为“独占”。

对于每一个CPU都可以指定所要进行的访问是读还是写(从列表中选),并在输入框中输入所要访问的主存块号,然后用鼠标单击在其右边的标有“↓”的按钮,模拟器就将开始演示该访问的工作过程。

实验五:存储体系实验

深圳大学实验报告课程名称:计算机系统(3)实验项目名称:存储体系实验学院:计算机与软件学院专业:计算机与软件学院所有专业指导教师:*******报告人:***** 学号:******* 班级:******** 实验时间:2017年12月19日星期二实验报告提交时间:2017年12月21日星期四教务处制注:1、报告内的项目或内容设置,可根据实际情况加以调整和补充。

一、实验目的增进对cache工作原理的理解体验程序中访存模式变化是如何影响cache效率进而影响程序性能的过程;学习在X86真实机器上通过调整程序访存模式来探测多级cache结构以及TLB的大小。

二、实验内容按照下面的实验步骤及说明,完成相关操作记录实验过程的截图:(1)x86 cache 层次结构的测量(90分)首先,设计一个用于测量x86系统上的cache层次结构的方案,然后设计出相应的代码;然后,运行你的代码获得相应的测试数据。

最后,根据测试数据分析你的x86机器有几级cache,各自容量是多大。

(2)选做:尝试测量你L1 cache行的大小;(3)选做:尝试测量你的x86机器TLB有多大(报告撰写质量10分)三、实验环境硬件:桌面PC软件:Windows四、实验步骤及说明(1)x86 cache 层次结构的测量一个程序从存储系统中读取数据的速率为读吞吐量,或者有时称为读带宽。

如果一个程序在s秒的时间段内读n个字节,那么这段时间内的读吞吐量就等于n/s,典型的是以兆字节每秒(MB/s)为单位的。

如果我们要编写一个程序,它从一个紧密程序循环中发出一系列读请求,那么测量出的读吞吐量能让我们看到对于这个读序列来说的存储系统的性能。

关于这个测试,有两个基本的概念:时间局部性与空间局部性。

时间局部性:被引用过一次的存储器位置在未来会被多次引用(通常在循环中)。

空间局部性:如果一个存储器的位置被引用,那么将来他附近的位置也会被引用。

本实验使用的是x64位系统,配置如下图:注:1、报告内的项目或内容设置,可根据实际情况加以调整和补充。

cache实验报告

cache实验报告《cache实验报告》在计算机科学领域中,cache(缓存)是一种用于存储临时数据的高速存储器,用于加快数据访问速度。

在本次实验中,我们对cache进行了一系列的实验,以探究其对计算机系统性能的影响。

首先,我们设计了一个简单的计算机系统模型,包括CPU、内存和cache。

我们使用了不同大小和结构的cache,并对其进行了性能测试。

通过比较不同cache结构下的数据访问速度和命中率,我们发现了cache大小和关联度对性能的影响。

较大的cache和更高的关联度可以显著提高数据访问速度和命中率,从而提升整个系统的性能。

接着,我们对cache的替换策略进行了实验。

我们比较了最常见的替换策略,如LRU(最近最少使用)、FIFO(先进先出)和随机替换。

通过实验结果,我们发现不同的替换策略会对cache的性能产生显著影响。

在某些情况下,合适的替换策略可以提高cache的命中率,从而提高系统的整体性能。

最后,我们对cache的一致性和一致性维护进行了实验。

我们测试了不同的一致性协议,如MESI(修改、独占、共享、无效)协议和MOESI(修改、独占、共享、无效、所有者)协议。

通过实验,我们发现一致性协议的选择对cache的性能和系统的稳定性有着重要影响。

合适的一致性协议可以有效减少数据访问的冲突和错误,提高系统的可靠性和性能。

综上所述,本次实验对cache进行了全面的性能测试和分析,探究了cache对计算机系统性能的影响。

通过实验结果,我们得出了一些重要结论,为优化计算机系统性能提供了重要的参考和指导。

希望本次实验结果能够对相关领域的研究和应用产生积极的影响。

简述cache存储体系的结构原理

简述cache存储体系的结构原理Cache存储体系的结构原理一、引言随着计算机性能的不断提升,处理器的速度远远快于内存存取速度,这导致了处理器与内存之间的速度差异问题,从而限制了计算机整体性能的提升。

为了解决这一问题,Cache存储体系应运而生。

Cache存储体系作为一种高速缓存,位于处理器与内存之间,能够提供快速的数据读写,有效地缓解了处理器与内存之间的速度矛盾。

二、Cache存储体系的基本原理Cache存储体系的基本原理是通过在处理器与内存之间增加一层高速存储器,即Cache,来提高数据的访问速度。

Cache存储体系采用了局部性原理,即数据访问的局部性较高,即近期访问的数据很有可能在不久的将来再次被访问到。

基于这一原理,Cache存储体系将近期访问的数据存储在高速缓存中,以便快速响应处理器的读写请求。

三、Cache存储体系的组成结构Cache存储体系通常由三级结构组成,分别是L1 Cache、L2 Cache和L3 Cache。

1. L1 Cache(一级缓存)L1 Cache是位于处理器核心内部的一级缓存,与处理器核心紧密结合,速度非常快。

L1 Cache通常分为指令缓存和数据缓存,分别用于存储指令和数据。

由于L1 Cache与处理器核心距离近,因此可以快速响应处理器的读写请求。

2. L2 Cache(二级缓存)L2 Cache是位于处理器与内存之间的二级缓存,容量较大。

L2 Cache的读写速度相对于L1 Cache略慢一些,但仍然远快于内存。

处理器在访问数据时,首先会查找L1 Cache,如果没有找到,则会继续查找L2 Cache。

由于L2 Cache容量较大,可以存储更多的数据,因此命中率相对较高。

3. L3 Cache(三级缓存)L3 Cache是位于处理器与内存之间的三级缓存,容量最大。

L3 Cache的读写速度相对于L2 Cache略慢一些,但仍然比内存要快很多。

处理器在访问数据时,首先会查找L1 Cache,如果没有找到,则会继续查找L2 Cache,最后才会查找L3 Cache。

cache存储体系的结构原理

cache存储体系的结构原理

Cache存储体系的结构原理包括如下几个方面:

1. 层次结构:Cache存储体系一般由多级缓存组成,包括L1、L2、L3等多级缓存。

不同级别的缓存容量和访问速度各不相同,越靠近处理器的缓存级别容量越小、访问速度越快。

2. 局部性原理:Cache存储体系利用了程序运行过程中存在的

局部性原理,包括时间局部性和空间局部性。

时间局部性指的是一段时间内某个数据被访问的概率很高,而空间局部性指的是一次访问某个数据后,其附近的数据也有很大的可能性会被访问。

3. 缓存映射:Cache存储体系中的数据被映射到下一级的缓存

或主存中。

常见的映射方式有直接映射、全相联映射和组相联映射。

直接映射是指每个数据块只能映射到缓存中的某个固定位置,全相联映射是指缓存中每个位置都可以映射任意数据块,组相联映射是指将缓存分成若干组,每组中有若干个位置,每个数据块只能映射到该组中的某个位置。

4. 缓存一致性:当多个处理器共享同一个缓存时,需要保证缓存的一致性。

一致性协议(如MESI协议)用于解决多个处理

器同时对同一个数据进行读写操作时可能出现的数据不一致问题。

5. 替换策略:当缓存已满时,需要按照一定策略替换缓存中的数据。

常见的替换策略有最近最少使用(LRU)、先进先出

(FIFO)等。

以上是Cache存储体系的结构原理的一些基本概念和原则,实际实现中还有一些细节和技术,例如缓存预取、写缓冲区等。

简述cache存储体系的结构原理

简述cache存储体系的结构原理Cache存储体系的结构原理随着互联网的发展和数据量的不断增加,对于数据的访问速度和效率要求也越来越高。

为了提高数据的访问速度,减少对数据库等后端存储系统的压力,缓存技术应运而生。

Cache存储体系是一种常见的缓存技术,通过将数据存储在内存中,以提高数据的读取速度。

本文将从结构和原理两个方面对Cache存储体系进行简要的介绍。

一、Cache存储体系的结构Cache存储体系通常由三层结构组成:缓存层、数据库层和应用层。

1. 缓存层:缓存层是整个Cache存储体系的核心。

它由缓存服务器和缓存存储介质组成。

缓存服务器负责接收应用层的读请求,并根据缓存策略决定是否从缓存存储介质中读取数据。

缓存存储介质通常使用高速内存,如内存条或固态硬盘,以保证读取速度。

缓存层的设计要考虑数据一致性和可靠性,通常会采用缓存同步和缓存失效等机制。

2. 数据库层:数据库层是缓存层的下一层,负责存储和管理原始数据。

数据库层通常使用关系型数据库或分布式数据库,用于存储大量的数据。

在缓存层无法满足读取请求时,数据库层会被调用,从而保证数据的完整性和可靠性。

3. 应用层:应用层是整个Cache存储体系的最上层,负责接收用户的请求,并将读取到的数据返回给用户。

应用层可以是Web服务器、应用程序或其他数据访问接口。

应用层通常会通过缓存服务器来提高数据的读取速度,以提升用户体验。

二、Cache存储体系的原理Cache存储体系的原理主要包括缓存命中和缓存失效两个方面。

1. 缓存命中:当应用层发起读取请求时,缓存服务器会首先检查缓存层是否存在请求的数据。

如果数据在缓存层中存在,即发生了缓存命中,缓存服务器会立即将数据返回给应用层。

这样可以避免对数据库层的访问,大大提高了读取速度和系统的吞吐量。

2. 缓存失效:当缓存层无法命中请求的数据时,即发生了缓存失效。

缓存失效后,缓存服务器会向数据库层发起读取请求,获取数据并存储到缓存层中,以备下一次的读取请求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

体系结构实验报告

实验目的

通过程序,模拟cache存储过程,并通过控制变量法模拟分析Cache性能实验步骤:

我们要通过老师所给程序进行模拟,并通过操作系统试验中老师所给算法生成出project.txt ,并通过project.txt 里面的数据来模拟程序的局部性等特性。

实验结果

1、比较关联方式,控制blockSize, CacheSize 不变:

(1)、Direct_mapped

(2) 、Set_associate:

(3) 、Fully_associate

通过上述三个比较可以看出,各种映射有自己的优点。

但是不难看出,增大关联度会减小miss rate,但是增加到一定程度又会有抑制作用。

2.比较Cache大小对于性能的影响。

(1)、Direct_mapped,Cache容量为64 时:

(2r

Direcflmapped

〉Cache

朿*

R

128 手

(3r Direcflmapped

〉Cache

助*

R

256

口

F

一pwsef 峑

s 2O J I 0

\^J.e e K ^g 63-L w g <J g -f a

JnnnrEd

理"巧 nm

rMecIrlxML

H

肆

一

事

呼

LJw

匸

-dJ-LUf

J

F U »»

a i

B ci

n

IJr l

t

R

n x li 黑

鱼

*=£1

K s 1!蚯c a p w p llrt t M:C4mw J

L

l n rll n i H H

Hi L n h != l

£lx-瞌

忻恥f*<41.

匸

«

F 2

3L L

/2\.*X «礼 j !H F i <n

对比实验结果,不难发现,随着Cache容量的增加,Cache的命中率一直在提升。

分析原因发现,虽然Cache容量大了,但并不等于其预存的内容增多,所以命中率会上升。

3、比较Cache大小对于性能的影响。

(1)、Direct_mapped,关联度为 1 时:

(2)、Direct_mapped,关联度为2 时:

(3)、Direct_mapped,关联度为4 时:

(4) 、Direct mapped ,关联度为 8 时:

I ■ C -\LI wrs 1.11uwe

i mo\Dw_-m e ts'_Vi EUUI I ^tud o l£f Pre e-crE\tt. q\Dfft!uq\ti'g.-i-j r

IE Is-* -IrMHi

F OP n tiny Ret U <A lun f 1± fl

hiss

H41# a 聊

C4pnic4tv Conflict

nx5S

(5) 、Direct map ped ,关联度为 16 时:

可以看出,随着关联度的提高,命中率也有所增加

Canipuilsnry 1

XSE-

hH MuflfafiP = I44.MIUUM1

Ace R -S3 NumWr ■

寸

-F

口寸 灭 」

eqlunu

>loo-q

〈 p ①ddelu —10

①」一q <

(L)

S

33I

・

鹫

詡M u

s y u s L l

's

童wr

#*■

L 書

-E .f n -s

r e U F K e$u

s.H

92

m £百

1-

■

阿

*

E

戏

*%

贰

%

严一&丫

A

*u

-

u

k s ?

£

L

c 』 C

3"

f l a

毒* 1

和4£

s

E E *

B J W

11

v m 「>!5

q

言石-d ^l L l e l

迟

E n p xll -,.I 曰右号v d d -o'w -o M n 「口釜l Y ci

-te L ^R 」

eqlunu

>loo-q 〈 p ①

ddelu —10①」Q <

通过以上三组数据不难看出,当block number增加时,命中率明显增高了。

分析原因可知,这是由于程序局部性原理所造成的,当一次性多拿些附近的数据, 会有效的预测为下次用到的。

通过程序可以看出,这种方法会增加程序运行时间。

习题:利用Cache模拟器CacheSimulator 程序分析解决:

The followi ng C program is run (with no optimizatio ns) on a machi ne with a cache that has four-word(16-byte)blocks and holds 256 bytes of data:

int i, j, c, stride, array[256];

for (i=0; i<10000; i++)

for (j=0; j<256; j=j+stride)

c=array[j]+5;

if we con sider only the cache activity gen erated by refere nces to the array and we assume that in tegers are words, what is the expected miss rate when the cache is direct-mapped and stride=132? How about if stride=131? Would either of these cha nge if the cache were two-way set associative?

截取实验结果屏幕,分析实验结果,写出实验报告和实验心得。

1、当stride=132 时:

Cache容量大小为256B,每个块大小为16B,所以Cache blocks 一共有16 个。

当访问array[0]和array[132]时,分别映射到Cacheblock第0个和第1个块,因为(132/4)mod16=1。

所以当第一次方位array[0]时,它会产生一次miss,并将其从memory中取出放入cache,第一次访问array[132]时也会产生一次miss,并将其从memory中取出放入cache。

以后访问时都可从cache中找到,所以不论访问几次,都是2个miss。

1、当stride=131 时:

个。

当访问array[0] 和array[132] 时,都将映射到Cache block 第0 个块,因为(132/4)mod16=0 。

所以当第一次方位array[O]时,它会产生一次miss,将其从memory中取出存入cache,而当其第一次访问array[131]时又产生一次miss,又将memory中的存入到cache 中,所以之后每次都会miss。

实验总结:

通过此次实验,让我对Cache的原理有了更深的理解。

Cache性能的影响是综合性的,其大小,关联度,块大小都可能影响着其最终性能。

但是同时我们还发现这几种映射每个都有自己的优缺点,最终我们要通过实验证明权衡最好的组合。