DS90LV110_LVDS

DS90LV012中文资料

Connection Diagrams

Functional Diagram

DS90LV012A

20015026

(Top View) Order Number DS90LV012ATMF, DS90LT012ATMF

See NS Package Number MF05A

20015002

DS90LT012A

−40 25 +85 ˚C

Electrical Characteristics

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified. (Notes 2, 3)

Symbol

Parameter

VTH

OUTPUT TTL OUT

H L H

© 2002 National Semiconductor Corporation DS200150

元器件交易网

DS90LV012A/DS90LT012A

Absolute Maximum Ratings (Note 1)

The DS90LV012A and DS90LT012A, and companion LVDS line driver provide a new alternative to high power PECL/ ECL devices for high speed interface applications.

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

完整版)LVDS接口详解

完整版)LVDS接口详解LVDS输出接口是一种数字视频信号传输方式,它利用低压差分信号技术接口,在两条PCB走线或一对平衡电缆上通过差分进行数据的传输。

相比于TTL接口,LVDS输出接口具有高速率、低噪声、远距离、高准确度等优点,因此在17in及以上液晶显示器中得到了广泛的应用。

LVDS接口电路由驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)组成。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过柔性电缆传送到液晶面板侧的LVDS接收器。

LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

在数据传输过程中,LVDS接口采用差分信号对的形式进行传输,每个数据传输通道或时钟传输通道的输出都为两个信号(正输出端和负输出端)。

这种方式不仅可以提高数据传输速率,还可以减少电磁干扰和功耗,使得LVDS输出接口更加稳定可靠。

不同种类的液晶显示器的驱动板上的LVDS发送器并不相同。

有些LVDS发送器是一片或两片独立的芯片,例如DS90C383;而有些则是集成在主控芯片中,例如主控芯片gm5221内部集成了LVDS发送器。

LVDS输出接口也分为四种类型,其中第一种是单路6位LVDS输出接口。

这种接口电路采用单路方式传输,每个基色信号(即RGB三色中的其中任何一种颜色)采用6位数据(XOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-),共18位RGB(6bit X 3(RGB3色))数据,因此也被称为18位或18bit LVDS接口。

第二种是双路6位LVDS输出接口。

在这种接口电路中,两个基色信号(例如红色和绿色)共用一条传输线,而蓝色信号则使用另一条传输线,每个基色信号采用6位数据,因此也被称为双路18位或18bit LVDS接口。

DS91M125 125 MHz 1 4 M-LVDS Repeater with LVDS Inp

DS91M125 125 MHz 1:4 M-LVDS Repeater withLVDS Input Evaluation KitUSER MANUALPart Number: DS91M125EVK NOPBFor the latest documents concerning these products and evaluation kit, visit . Schematics andgerber files are also available at OverviewThe purpose of this document is to familiarize you with the DS91M125 evaluation board, suggest the test setup procedures and instrumentation, and to guide you through some typical measurements that will demonstrate the performance of the device. The board enables the user to examine performance and all functions of theDS91M125 as a standalone device.The DS91M125 is a high-speed 1:4 M-LVDS repeater with an LVDS input designed for multipoint applications with multiple drivers or receivers. The device conforms to TIA/EIA-899 standard. It utilizes M-LVDS technology for low power, high-speed and superior noise immunity.DescriptionFigure 1 below represents the top layer drawing of the board with the silkscreen annotations. It is a 2.5 x 3 inch 4 layer printed circuit board (PCB) that features a single DS91M125 (U2) device.Figure 1 -DS91M125EVK Top View DrawingDS91M125 Evaluation in a Point-to-Point LinkThe following is a recommended procedure for using and evaluating the DS91M125EVK. Figure 2 depicts a typical setup and instrumentation used.1. Select a single DS91M125 evaluation board.2. Apply the power to the board (3.3 V typical) between J3 and J4 power tabs, observe the value of I CC,and compare it with the expected value (refer to the datasheet) to ensure that the devices arefunctional.3. Enable one of the U2 driver outputs. This is accomplished by setting the DE0-3 pin to VDD (JP3-6).4. Connect a signal source to the driver input (DI+, DI-). The signal needs to be an LVDS/M-LVDS/CML/LVPECL compliant signal. Refer to the DS91M125 datasheet for the receiver inputcompatibility.5. Connect one of the U2 outputs (A0-3/B0-3) to an oscilloscope and observe the waveforms.Figure 2 – DS91M125 Test SetupFigure 3 shows an eye diagram acquired at the output of the DS91M125 driver loaded with a 100-ohm resistor. The generator connected to the driver input simulated a 100 Mbps PRBS-7 NRZ.Figure 3 – DS91M125 OutputIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connectivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated。

DS90LV019中文资料

Features

n LVDS Signaling n 3.3V or 5.0V operation n Low power CMOS design n Balanced Output Impedance n Glitch free power up/down (Driver disabled) n High Signaling Rate Capacity (above 100 Mbps) n Ultra Low Power Dissipation n ±1V Common-Mode Range n ±100 mV Receiver Sensitivity n Product offered in SOIC and TSSOP packages n Flow-Through Pin Out n Industrial Temperature Range Operation

IOS

Output Short Circuit Current

VOUT = 0V

VTH

Input Threshold High

VTH

Input Threshold Low

IIN

Input Current

VIN = +2.4V or 0V, VCC = 3.6V or 0V

DEVICE CHARACTERISTICS

> 2.0 kV > 200 V

Maximum Package Power Dissipation at 25˚C

LVDS驱动芯片

MS90C385SN75LVDS83十通道LVDS发送芯片DS90C365说明:4通道LVDS发送芯片主要用于驱动6bit液晶面板。

使用四通道LVDS发送芯片可以构成单路6bit LVDS接自电路和奇/偶双路6bit LVDS接口电路。

五通道LVDS发送芯片DS90C385十通道LVDS发送芯片DS90C3871.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS 发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

LVDS简介

LVDS原理与应用简介1 LVDS信号介绍LVDS:Low Voltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

IEEE在两个标准中对LVDS信号进行了定义。

ANSI/TIA/EIA-644中,推荐最大速率为655Mbps,理论极限速率为1.923Mbps。

1.1 LVDS信号传输组成TTL TTLLVDS差分接收器图1 LVDS信号传输组成图LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

通常由一个IC来完成,如:DS90C031差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成,如:DS90C032差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

按照IEEE规定,电阻为100欧。

我们通常选择为100,120欧。

1.2 LVDS信号电平特性LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV摆幅。

LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω 的匹配电阻,并在接收器的输入端产生大约350mV 的电压。

电流源为恒流特性,终端电阻在100――120欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420mV 。

下图为LVDS 与PECL (光收发器使用的电平)电平变化。

图2 LVDS 与PECL 电平图示由逻辑“0”电平变化到逻辑“1”电平是需要时间的。

LVDS驱动芯片

MS90C385SN75LVDS83十通道LVDS发送芯片DS90C365说明:4通道LVDS发送芯片主要用于驱动6bit液晶面板。

使用四通道LVDS发送芯片可以构成单路6bit LVDS接自电路和奇/偶双路6bit LVDS接口电路。

五通道LVDS发送芯片DS90C385十通道LVDS发送芯片DS90C3871.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS 发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

LVDS应用小结2021

LVDS简介LVDS(Low-Voltage Differential Signaling ,低电压差分信号)是美国国家半导体(National Semiconductor, NS,现TI)于1994年提出的一种信号传输模式的电平标准LVDS驱动器和接收器如图1-1所示的LVDS驱动器-接收器对的原理图。

驱动器中含有一个(标称值)3.5mA的电流源。

因为接收器输入阻抗很高,故整个电流实际上全部流过100Ω终接电阻,于是在接收器输入端产生了350mV(标称值)的电压。

接收器的阈值可以保证为100mV或更低;改变电流方向即可在接收器端形成幅值相同而极性相反的电压,以这种方式来产生0和1。

CML&LVPECL电流模式逻辑(Current-Mode Logic CML)和低压正发射极耦合逻辑(Low-Voltage Positive-Emitter-Coupled LVPECL)典型CML实现方案如图所示,CML技术有一个特点是在驱动器和接收器上均集成终接网络.CML使用一个无源的上拉电路(将电压拉升到正电压轨),其阻抗一般为50Ω。

大多数CML都采用了交流耦合的实现方案典型的LVPECL实现方案SerDes架构1.并行时钟SerDes并行-时钟-串化器编码示例目前TV方案使用均为此种形式的架构,从该架构图可以看出来在CLK一个周期内Data 传过7bit数据2.嵌入式时钟(起始/终止)位SerDes18bit时钟位嵌入式串化器编码示例时钟位嵌入式架构中的发送器将数据总线上的数据信号和时钟串行化,形成单路串行信号对。

两个时钟位,一路低而另一路高,被嵌入到串行流中,每隔一个周期放置一个,用于界定串化后每个字的起点和终点(因此又有另一个名称“起止位”SerDes)并在串行数据流中产生一个周期性的上升沿。

这种架构的一个好处是,数据有效负载的字宽度无需被限制为字节的倍数。

周期性嵌入时钟信号切换串化器在电路上电时就可以搜寻周期性出现的嵌入时钟信号的上升沿。

液晶屏LVDS,TTL,RSDS接口样式的区别方法

液晶屏LVDS,TTL,RSDS接口样式的区别方法2008-04-25 13:39很多初学者对于如何区分屏的接口类型很是头疼,是LVDS屏,TTL屏还是RSDS屏?总是很难搞清出。

如何快速识别出液晶屏的接口类型则需要一些经验的,下面从屏的屏线接口的样式来对接口类型做出分类的介绍,帮助大家快速识别屏的接口类型。

以下方法是个人认识,不足之处请大家谅解。

(1) TTL屏接口样式:D6T(单6位TTL):31扣针,41扣针。

对应屏的尺寸主要为笔记本液晶屏(8寸,10寸,11寸,12寸),还有部分台式机屏15寸为41扣针接口。

S6T(双6位TTL):30+45针软排线,60扣针,70扣针,80扣针。

主要为台式机的14寸,15寸液晶屏。

D8T(单8位TTL):很少见S8T(双8位TTL):有,很少见80扣针(14寸,15寸)2)LVDS屏接口样式:D6L(单6位LVDS):14插针,20插针,14片插,30片插(屏显基板100欧姆电阻的数量为4个)主要为笔记本液晶屏(12寸,13寸,14寸,15寸)D8L(单8位LVDS):20插针(5个100欧姆)(15寸)S6L(双6位LVDS):20插针,30插针,30片插(8个100欧姆)(14寸,15寸,17寸)S8L(双8位LVDS):30插针,30片插(10个100欧姆电阻)(17寸,18寸,19寸,20寸,21寸)(3)RSDS屏接口样式:50排线,双40排线,30+50排线。

主要为台式机(15寸,17寸)液晶屏。

常规LVDS接口液晶屏定义20PIN单6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16空 17空 18空 19 空 20空每组信号线之间电阻为(数字表120欧左右)20PIN双6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3- 18:RO3+ 19:CLK1- 20:CLK1+每组信号线之间电阻为(数字表120欧左右)20PIN单8定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16:R3- 17:R3+每组信号线之间电阻为(数字表120欧左右)30PIN单6定义:1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地20:空- 21:空 22:空 23:空 24:空 25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)30PIN单8定义:1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地20:R3- 21:R3+ 22:地 23:空 24:空 25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)30PIN双6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16:地 17:RS0- 18:RS0+ 19:地 20:RS1- 21:RS1+ 22:地 23:RS2- 24:RS2+ 25:地 26:CLK2- 27:CLK2+每组信号线之间电阻为(数字表120欧左右)30PIN双8定义:1:电源2:电源3:电源 4:空 5:空 6:空 7:地 8:R0- 9:R0+ 10:R1- 11:R1+ 12:R2- 13:R2+ 14:地 15:CLK- 16:CLK+ 17:地 18:R3- 19:R3+ 20:RB0-21:RB0+ 22:RB1- 23:RB1+ 24:地 25:RB2- 26:RB2+ 27:CLK2- 28:CLK2+ 29:RB3- 30:RB3+每组信号线之间电阻为(数字表120欧左右)一般14PIN、20PIN、30PIN为LVDS接口。

基于FPGA的LVDS学习报告讲解

3.4 不同总线结构的性能

点到点的连接结构可以在高达芯片组最大的性能指标的情 况下工作,这也取决于互联是否支持那么高的速度。

4、Spartan-6 系列FPGA 器件特点总结

From:Spartan-6 Family Overview, Table 1

Spartan-6 系列器件封装和最大可用I/O数

基于FPGA的LVDS 接口应用 学习汇报

汇报人:张兴

1、什么是差分信号?

差分信号利用两根导线来传输数据,我们 主要研究低压差分信号(Low Voltage Differential Signal,LVDS)。在正引线上, 电流正向流动,负引线构成电流的返回通 路,接收器仅仅给出两传输线上的信号差, 因此共模噪声信号将被抑制掉。LVDS一般 用恒流源驱动器,在接收侧一般是简单的 100 W电阻。

From:DS25BR110 3.125 Gbps LVDS Buffer with Receive Equalization

总结

DS25BR120 的特点是four levels of preemphasis(PE), 是最优的驱动设备 DS25BR110 的特点是four levels of receive equalization(EQ),是最理想的接收 设备

DS25BR100

DS25BR100的特点是both pre-emphasis(PE) and receive equalization(RE),是最理想的中继 设备(repeater device) The repeater device repeats a signal between the transmission device and the reception device, and includes an equalizer amplifier that amplifies a signal that is received from the transmission device or another repeater device.

LVDS介绍及详细原理说明

LVDSJawen_tao2011-05-09目录一、简介 (2)1、为何要用LVDS? (2)2、LVDS信号传输组成 (2)二、LVDS电气特性 (4)三、传输协议 (5)四、线路接法 (10)五、Layout (13)一、简介LVDS(Low Voltage Differential Signal)即低电压差分信号。

1、为何要用LVDS?LVDS接口又称RS644总线接口,1994年由美国国家半导体公司(NS)提出的为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种视频信号传输模式,是一种电平标准,广泛应用于液晶屏接口。

液晶显示器驱动板输出的数字信号是TTL信号,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,像素时钟信号的最高频率可超过28MHZ.采用TTL接口,数据传输速率不高(一个CLK周期只能传输1bit数据),传输距离较短,且抗电磁干扰能力比较差,会对RGB数据造成一定的影响。

另外,TTL 多路数据信号采用并行的传输方式,整个并口数量达几十路(RGB各8位,8x3=24,加 DE,HSYNC,VSYNC,至少27位),不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

2、LVDS信号传输组成最基本的LVDS器件就是LVDS驱动器和接收器。

LVDS的驱动器由驱动差分线对的电流源组成,电流通常为3.5 mA。

如下图,LVDS接收器具有很高的输入阻抗,因此驱动器输出的大部分电流都流过100 Ω的匹配电阻(R=100Ω),并在接收器的输入端产生大约350 mV的电压。

(电流源为恒流特性,终端电阻在100—120 欧姆之间,则电压摆动幅度为:3.5mA x 100=350Mv;3.5mA x 120=420mV。

)当驱动器(LVDS发送)翻转时,它改变流经电阻的电流方向,因此产生有效的逻辑“1”和逻辑“0”状态。

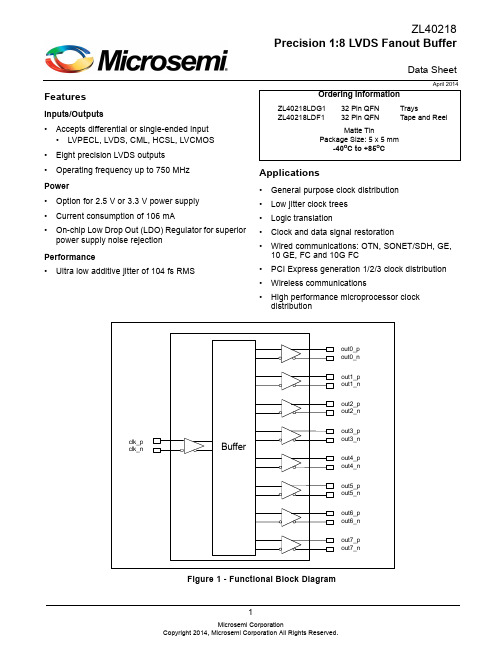

微光电子1 8精密LVDS缓冲器说明书

1FeaturesInputs/Outputs •Accepts differential or single-ended input •LVPECL, LVDS, CML, HCSL, LVCMOS •Eight precision LVDS outputs •Operating frequency up to 750 MHzPower •Option for 2.5 V or 3.3 V power supply •Current consumption of 106 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply noise rejectionPerformance •Ultra low additive jitter of 104 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration•Wired communications: OTN, SONET/SDH, GE, 10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40218Precision 1:8 LVDS Fanout BufferData SheetOrdering InformationZL40218LDG1 32 Pin QFN TraysZL40218LDF132 Pin QFNTape and ReelMatte TinPackage Size: 5 x 5 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .196.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .207.0 Package Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .218.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3 - LVPECL Input DC Coupled Thevenin Equivalent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 4 - LVPECL Input DC Coupled Parallel Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 5 - LVPECL Input AC Coupled Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 6 - LVDS Input DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 7 - LVDS Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 8 - CML Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 9 - HCSL Input AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 10 - CMOS Input DC Coupled Referenced to VDD/2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 11 - CMOS Input DC Coupled Referenced to Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 12 - Simplified LVDS Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 13 - LVDS DC Coupled Termination (Internal Receiver Termination). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 14 - LVDS DC Coupled Termination (External Receiver Termination) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 15 - LVDS AC Coupled Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 16 - LVDS AC Output Termination for CML Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 17 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 18 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 19 - Differential Voltage Parameter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 20 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18Change SummaryBelow are the changes from the February 2013 issue to the April 2014 issue:Page Item Change1Applications Added PCI Express clock distribution.6Pin Description Added exposed pad to Pin Description.7, 8Figure 3 and Figure 4Removed 22 Ohm series resistors from Figure 3 and 4. Theseresistors are not required; however there is no impact toperformance if the resistors are included.16Power supply filtering Corrected typo of 0.3 ohm to 0.15 ohm.18Figure 19Clarification of V ID and V OD.Below are the changes from the November 2012 issue to the February 2013 issue:Page Item Change8Figure 4Changed text to indicate the circuit is not recommended forVDD_driver=2.5V.8Figure 5Changed pull-up and pull-down resistors from 2kOhm to100 Ohm.12Figure 12Changed gate values to +/+ on the left and -/- on the right.1.0 Package DescriptionThe device is packaged in a 32 pin QFNFigure 2 - Pin Connections2.0 Pin DescriptionPin # Name Description3, 6clk_p, clk_n,Differential Input (Analog Input). Differential (or single ended) input signals.For all input configurations see section 3.1, “Clock Inputs“.30, 29, 28, 27, 26, 25, 24, 23, 18, 17, 16, 15, 14, 13, 12, 11 out0_p, out0_nout1_p, out1_nout2_p, out2_nout3_p, out3_nout4_p, out4_nout5_p, out5_nout6_p, out6_nout7_p, out7_nDifferential Output (Analog Output). Differential outputs.9, 19,22, 32vdd Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal. 1, 8vdd_core Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal. 2, 7,20, 21gnd Ground. 0 V.4, 510, 31NC No Connection. Leave unconnected.Exposed Pad Device GND.3.0 Functional DescriptionThe ZL40218 is an LVDS clock fanout buffer with eight identical output clock drivers capable of operating at frequencies up to 750MHz.Inputs to the ZL40218 are externally terminated to allow use of precision termination components and to allow full flexibility of input termination. The ZL40218 can accept DC coupled LVPECL or LVDS and AC coupled LVPECL, LVDS, CML or HCSL input signals; single ended input signals can also be accepted. A pin compatible device with internal termination is also available.The ZL40218 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe ZL40218 is adaptable to support different types of differential and singled-ened input signals depending on the passive components used in the input termination. The application diagrams in the following figures allow the ZL40218 to accept LVPECL, LVDS, CML, HCSL and single-ended inputs.Figure 3 - LVPECL Input DC Coupled Thevenin EquivalentFigure 4 - LVPECL Input DC Coupled Parallel TerminationFigure 5 - LVPECL Input AC Coupled TerminationFigure 6 - LVDS Input DC CoupledFigure 7 - LVDS Input AC CoupledFigure 8 - CML Input AC CoupledFigure 9 - HCSL Input AC CoupledFigure 10 - CMOS Input DC Coupled Referenced to VDD/2Figure 11 - CMOS Input DC Coupled Referenced to GroundVDD_driver R1 (kΩ)R2 (kΩ)R3 (kΩ)RA (kΩ) C (pF) 1.5 1.25 3.075open10101.81 3.8open10102.50.33 4.2open10103.30.75open4.21010Table 1 - Component Values for Single Ended Input Reference to Ground*For frequencies below 100 MHz, increase C to avoid signal integrity issues.3.2 Clock OutputsLVDS has lower signal swing than LVPECL which results in a low power consumption. A simplified diagram for the LVDS output stage is shown in Figure 12.Figure 12 - Simplified LVDS Output DriverThe methods to terminate the ZL40218 drivers are shown in the following figures.Figure 13 - LVDS DC Coupled Termination (Internal Receiver Termination)Figure 15 - LVDS AC Coupled TerminationFigure 16 - LVDS AC Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40218 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40218 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40218 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 17.Figure 17 - Additive Jitter3.4 Power SupplyThis device operates employing either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40218 is equipped with an on-chip linear power regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise.The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.3.4.2 Power supply filteringJitter levels may increase when noise is present on the power pins. For optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure . •10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating •0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating •Capacitors should be placed next to the connected device power pins •A 0.15 O hm resistor is recommendedZL402181891922320.1 µF 0.1 µFvdd_core10 µF 0.1 µF0.15 Ωvdd0.1 µF 10 µFFigure 18 - Decoupling Connections for Power Pins3.4.3 PCB layout considerationsThe power nets in Figure can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.4.0 AC and DC Electrical CharacteristicsAbsolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5V DD V 3Soldering temperature T260 °C 4Storage temperature T ST-55125 °C 5Junction temperature T j125 °C 6Voltage on input pin V input V DD V 7Input capacitance each pin C p500fF *Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.*Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units 1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V 2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V 3Operating temperature T A-402585°C*Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVDS drivers - loadedI dd_load106mA(all outputs are active)DC Electrical Characteristics - Inputs and Outputs - for 2.5/3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes 1Differential input common modeV ICM 1.1 1.6V for 2.5 V voltageV ICM 1.1 2.0V for 3.3 V 2Differential input common modevoltage3Differential input voltage difference V ID0.251V4Differential input resistance V IR80100120ohm5LVDS output differential voltage*V OD0.250.300.40V6LVDS Common Mode voltage V CM 1.1 1.25 1.375V*The VOD parameter was measured between 125 and 750 MHzAC Electrical Characteristics* - Inputs and Outputs (see Figure 20) - for 2.5/3.3 V supply.Characteristics Sym.Min.Typ.Max.Units Notes 1Maximum Operating Frequency1/t p750MHz2Input to output clock propagation delay t pd012ns3Output to output skew t out2out80150ps4Part to part output skew t part2part120300ps5Output clock Duty Cycle degradation t PWH/ t PWL-505Percent6LVDS Output slew rate r SL0.55V/nsFigure 19 - Differential Voltage Parameter* Supply voltage and operating temperature are as per Recommended Operating ConditionsInputt Pt PWL t pdt PWHOutputFigure 20 - Input To Output TimingAdditive Jitter at 2.5 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1482212.512 kHz - 20 MHz 1383311.0412 kHz - 20 MHz 121442512 kHz - 20 MHz 115550012 kHz - 20 MHz 1076622.0812 kHz - 20 MHz 107775012 kHz - 20 MHz105Additive Jitter at 3.3 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1502212.512 kHz - 20 MHz 1383311.0412 kHz - 20 MHz 120442512 kHz - 20 MHz 115550012 kHz - 20 MHz 1076622.0812 kHz - 20 MHz 106775012 kHz - 20 MHz1045.0 Performance Characterization*The values in this table were taken with a slew rate of approximately 0.8 V/ns.*The values in this table were taken with a slew rate of approximately 0.8 V/ns.Additive Jitter from a Power Supply Tone*Carrier frequencyParameterTypicalUnitsNotes125MHz 25 mV at 100 kHz 24fs RMS 750MHz25 mV at 100 kHz23fs RMS* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 3.3 V. The magnitude of the interfering tone is measured at the DUT.6.0 Typical BehaviorTypical Waveform at 155.52 MHzV OD vs FrequencyPower Supply Tone Frequency versus PSRRPower Supply Tone Magnitude versus PSRRPropagation Delay versus TemperatureNote:This is for a single device. For more details, see thecharacterization section.7.0 Package CharacteristicsThermal DataParameter Symbol Test Condition Value UnitJunction to Ambient Thermal Resistance ΘJA Still Air1 m/s2 m/s 37.433.131.5o C/WJunction to Case Thermal Resistance ΘJC24.4o C/W Junction to Board Thermal Resistance ΘJB19.5o C/W Maximum Junction Temperature*T jmax125o C Maximum Ambient Temperature T A85o C© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .Microsemi Corporate Headquarters One One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.For more information about all Microsemi productsvisit our website at TECHNICAL DOCUMENTATION – NOT FOR RESALE。

微塞米电子LVDS高速时钟转换器说明书

1FeaturesInputs/Outputs •Accepts differential or single-ended input •LVPECL, LVDS, CML, HCSL, LVCMOS •On-chip input termination and biasing for AC coupled inputs•Six precision LVDS outputs •Operating frequency up to 750 MHzPower •Option for 2.5 V or 3.3 V power supply •Current consumption of 97 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply noise rejectionPerformance •Ultra low additive jitter of 135 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration•Wired communications: OTN, SONET/SDH, GE, 10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40217Precision 1:6 LVDS Fanout Buffer with On-Chip Input TerminationData SheetOrdering InformationZL40217LDG1 32 Pin QFN TraysZL40217LDF132 Pin QFNTape and ReelMatte TinPackage size: 5 x 5 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .165.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .197.0 Package Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 Figure 3 - Simplified Diagram of input stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 4 - Clock Input - LVPECL - DC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 5 - Clock Input - LVPECL - AC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 6 - Clock Input - LVDS - DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 7 - Clock Input - LVDS - AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 8 - Clock Input - CML- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 9 - Clock Input - HCSL- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 10 - Clock Input - AC-coupled Single-Ended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 11 - Clock Input - DC-coupled 3.3V CMOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 12 - Simplified LVDS Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 13 - LVDS DC Coupled Termination (Internal Receiver Termination). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 14 - LVDS DC Coupled Termination (External Receiver Termination) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 15 - LVDS AC Coupled Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 16 - LVDS AC Output Termination for CML Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 17 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 18 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 19 - Differential Voltage Parameter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 20 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17Change SummaryBelow are the changes from the February 2013 issue to the April 2014 issue:Page Item Change1Applications Added PCI Express clock distribution.6Pin Description Added exposed pad to Pin Description.7Figure 4 and Figure 5Removed 22 ohm series resistors from Figure 4 and 5. Theseresistor are not required; however there is no impact toperformance if the resistors are included.15Power supply filtering Corrected typo of 0.3 ohm to 0.15 ohm.17Figure 19Clarification of V ID and V ODBelow are the changes from the November 2012 issue to the February 2013 issue:Page Item Change7Figure 4Changed text to indicate the circuit is not recommended forVDD_driver=2.5V.11Figure 12Changed gate values to +/+ on the left and -/- on the right.1.0 Package DescriptionThe device is packaged in a 32 pin QFNFigure 2 - Pin Connections2.0Pin # Name Description3, 6clk_p, clk_n,Differential Input (Analog Input). Differential (or single ended) input signals.For all input configurations see “Clock Inputs” on page 628, 27, 26, 25, 24, 23, 18, 17, 16, 15, 14, 13out0_p, out0_nout1_p, out1_nout2_p, out2_nout3_p, out3_nout4_p, out4_nout5_p, out5_nDifferential Output (Analog Output). Differential outputs.9, 19,22, 32vdd Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.1, 8vdd_core Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.2, 7,20, 21gnd Ground. 0 V.4vt On-Chip Input Termination Node (Analog). Center tap between internal 50 Ohmtermination resistors.The use of this pin is detailed in section 3.1, “Clock Inputs“, for various input signal types.5ctrl Digital Control for On-Chip Input Termination (Input). Selects differential input mode;0: DC coupled LVPECL or LVDS modes1: AC coupled differential modesThis pin are internally pulled down to GND. The use of this pin is detailed in section 3.1,“Clock Inputs“, for various input signal types.10, 11,12, 29,30, 31NC No Connection. Leave unconnected.Exposed Pad Device GND.Pin Description3.0 Functional Descriptionhe ZL40217 is an LVDS clock fanout buffer with six output clock drivers capable of operating at frequencies up to 750MHz.The ZL40217 provides an internal input termination network for DC and AC coupled inputs; optional input biasing for AC coupled inputs is also provided. The ZL40217 can accept DC coupled LVPECL or LVDS and AC coupled LVPECL and LVDS input signals, AC coupled CML or HCSL input signals, and single ended signals. A pin compatible device with external termination is also available.The ZL40217 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe device has a differential input equipped with two on-chip 50 Ohm termination resistors arranged in series with a center tap. The input can accept many differential and single-ended signals with AC or DC coupling as appropriate. A control pin is available to enable internal biasing for AC coupled inputs. A block diagram of the input stage is in Figure 3.Receiverclk_n 50clk_pVt 50BiasctrlFigure 3 - Simplified Diagram of Input StageThis following figures give the components values and configuration for the various circuits compatible with the input stage and the use of the Vt and ctrl pins in each case.In the following diagrams where the ctrl pin is "1" and the Vt pin is not connected, the Vt pin can be instead connected to V DD with a capacitor. A capacitor can also help in Figure 4 between Vt and V DD . This capacitor will minimize the noise at the point between the two internal termination resistors and improve the overall performance of the device.Clock Input - LVPECL - DC CoupledFigure 4 -Figure 6 - Clock Input - LVDS - DC CoupledFigure 7 - Clock Input - LVDS - AC CoupledFigure 8 - Clock Input - CML- AC CoupledFigure 9 - Clock Input - HCSL- AC CoupledFigure 10 - Clock Input - AC-coupled Single-EndedFigure 11 - Clock Input - DC-coupled 3.3V CMOS3.2 Clock OutputsLVDS has lower signal swing than LVPECL which results in a low power consumption. A simplified diagram for the LVDS output stage is shown in Figure 12.Figure 12 - Simplified LVDS Output DriverFigure 15 - LVDS AC Coupled TerminationFigure 16 - LVDS AC Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40217 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40217 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40217 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 17.Figure 17 - Additive Jitter3.4 Power SupplyThis device operates employing either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40217 is equipped with a low drop out (LDO) linear power regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.3.4.2 Power supply filteringJitter levels may increase when noise is present on the power pins. For optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure •. •10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating •0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating •Capacitors should be placed next to the connected device power pins •A 0.15 ohm resistor is recommendedZL402171891922320.1 µF 0.1 µFvdd_core10 µF 0.1 µF0.15 Ωvdd0.1 µF 10 µFFigure 18 - Decoupling Connections for Power Pins3.4.3 PCB layout considerationsThe power nets in Figure 18 can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.4.0 AC and DC Electrical CharacteristicsAbsolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5V DD V 3Soldering temperature T260 °C 4Storage temperature T ST-55125 °C 5Junction temperature T j125 °C 6Voltage on input pin V input V DD V 7Input capacitance each pin C p500fF * Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.* Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V3Operating temperature T A-402585°C* Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVDS drivers -I dd_load97mAloaded (all outputs are active)DC Electrical Characteristics - Inputs and Outputs - for 2.5/3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes 1CMOS control logic high-level input V CIH0.7*V DD V2CMOS control logic low-level input V CIL0.3*V DD VI IL1µA V I = V DD or 0 V3CMOS control logic Input leakagecurrentV ICM 1.1 1.6V for 2.5 V 4Differential input common modevoltageV ICM 1.1 2.0V for 3.3 V 5Differential input common modevoltage6Differential input voltage difference V ID0.251V7Differential input resistance V IR80100120ohm* The VOD parameter was measured between 125 and 750 MHzFigure 19 - Differential Voltage ParameterAC Electrical Characteristics* - Inputs and Outputs (see Figure 20) - for 2.5/3.3 V Supply.CharacteristicsSym.Min.Typ.Max.Units Notes1Maximum Operating Frequency 1/t p 750MHz 2Input to output clock propagation delay t pd 012ns 3Output to output skew t out2out 80150ps 4Part to part output skewt part2part 120300ps 5Output clock Duty Cycle degradation t PWH / t PWL-505%6LVDS Output slew rater SL0.55V/ns* Supply voltage and operating temperature are as per Recommended Operating ConditionsInputt Pt PWLt pdt PWHOutputFigure 20 - Input To Output Timing8LVDS output differential voltage*V OD 0.250.300.40V 9LVDS Common Mode voltageV CM1.11.251.375VDC Electrical Characteristics - Inputs and Outputs - for 2.5/3.3 V SupplyCharacteristicsSym.Min.Typ.Max.Units Notes5.0 Performance Characterization Additive Jitter at 2.5 V*Output Frequency (MHz)JitterMeasurementFilterTypicalRMS (fs)Notes112512 kHz - 20 MHz184 2212.512 kHz - 20 MHz174 3311.0412 kHz - 20 MHz157 442512 kHz - 20 MHz152 550012 kHz - 20 MHz139 6622.0812 kHz - 20 MHz138 775012 kHz - 20 MHz135 *The values in this table were taken with an approximate slew rate of 0.8 V/ns.Additive Jitter at 3.3 V*Output Frequency (MHz)JitterMeasurementFilterTypicalRMS (fs)Notes112512 kHz - 20 MHz1872212.512 kHz - 20 MHz1763311.0412 kHz - 20 MHz156442512 kHz - 20 MHz153550012 kHz - 20 MHz1406622.0812 kHz - 20 MHz139775012 kHz - 20 MHz137*The values in this table were taken with an approximate slew rate of 0.8 V/ns.Additive Jitter from a Power Supply Tone*CarrierfrequencyParameter Typical Units Notes125MHz25 mVat 100 kHz33fs RMS750MHz25 mVat 100 kHz33fs RMS* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 3.3 V. The magnitude of the interfering tone is measured at the DUT.6.0 Typical BehaviorTypical Waveform at 155.52 MHz V OD vs FrequencyPower Supply Tone Frequency versus PSRR Power Supply Tone Magnitude versus PSRRPropagation Delay versus TemperatureNote:This is for a single device. For more details, see thecharacterization section.7.0 Package CharacteristicsThermal DataParameter Symbol Test Condition Value UnitJunction to Ambient Thermal Resistance ΘJA Still Air1 m/s2 m/s 37.433.131.5o C/WJunction to Case Thermal Resistance ΘJC24.4o C/W Junction to Board Thermal Resistance ΘJB19.5o C/W Maximum Junction Temperature*T jmax125o C Maximum Ambient Temperature T A85o C8.0 Mechanical DrawingInformation relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any suchinformation, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.Purchase of Microsemi’s I 2C components conveys a license under the Philips I 2C Patent rights to use these components in an I 2C System, provided that the system conforms to the I 2C Standard Specification as defined by Philips.Microsemi, ZL, and combinations thereof, VoiceEdge, VoicePort, SLAC, ISLIC, ISLAC and VoicePath are trademarks of Microsemi Corporation.TECHNICAL DOCUMENTATION - NOT FOR RESALEFor more information about all Microsemi productsvisit our Web Site at。

lvds 电平标准

lvds 电平标准

LVDS(Low Voltage Differential Signaling)是一种低压差分信号传输技术,可用于高速数据传输和抗干扰能力较强的电路中。

LVDS电平标准是由美国电子工业协会(Electronic Industries Alliance,EIA)制定的。

LVDS信号需要使用特殊的发送和接收器件,常用的发送器件包括DS90LV011A和DS90LV019A等;常用的接收器件包括

DS90LV027A和DS90LV028A等。

LVDS电平标准规定了信号的电压范围、输出电阻、驱动电流等参数。

LVDS电平标准的电压范围为±350mV到±2V,输出电阻为100Ω,驱动电流为3.5mA。

LVDS电平标准的优点在于高速、低电平摆动、抗干扰能力强、适合远距离传输,适用于音视频传输、通信系统、计算机总线等领域。

与其他电平标准相比,LVDS电平标准可以在高速传输中保持较低的时钟抖动和数据失真。

需要注意的是,LVDS电平标准的信号必须传输在双绞线上,同时需要使用特殊的发送和接收器件,因此在实际应用中需要考虑成本和可行

性等因素。

总之,LVDS电平标准是一种高速、低电平摆动、抗干扰能力强、适合远距离传输的电平标准,适用于音视频传输、通信系统、计算机总线

等领域。

在实际应用中需要根据具体情况选择合适的发送和接收器件,并考虑成本和可行性等因素。

lvds 差分阻抗范围

lvds 差分阻抗范围

LVDS(低电压差分信号)是一种常用的高速串行通信接口标准,通常用于在PCB板上传输高速数字信号。

LVDS差分信号线路的阻抗

范围通常在90欧姆左右。

在设计LVDS差分信号线路时,确保差分阻抗匹配是非常重要的。

一般来说,差分阻抗的范围应该控制在85欧姆到100欧姆之间,以

确保信号的传输质量和稳定性。

对于PCB板上的差分信号线路,通

常会采用特殊的布线技术和材料来确保阻抗匹配,比如控制线宽、

线间距和层间距等参数。

另外,还需要注意信号线的走线路径、信号线与其他线路的交叉、信号线的终端匹配等因素,这些都会对差分信号线路的阻抗产

生影响。

因此,在设计LVDS差分信号线路时,需要综合考虑布线、

材料选择、信号完整性等多个因素,以确保差分阻抗在合适的范围内,从而保证信号的传输质量和稳定性。

ds90ur906解码原理

ds90ur906解码原理

DS90UR906是一种高速串行器件,主要用于将并行数据转换为串行数据进行传输。

它通常用于视频和图像传输领域,例如汽车摄像头系统、医疗成像设备等。

DS90UR906的解码原理涉及到串行器件的工作方式。

当并行数据输入到DS90UR906时,它会将这些数据转换为串行数据,并通过差分信号进行传输。

差分信号是通过两个相互补偿的信号来传输数据,可以减少传输过程中的干扰和噪音,提高数据传输的稳定性和可靠性。

在DS90UR906中,解码的过程主要涉及到将串行数据重新转换为并行数据。

这个过程包括解串、时钟恢复、数据解封装等步骤。

解串是将串行数据转换为并行数据,时钟恢复是通过接收到的时钟信号重新生成本地时钟,数据解封装是将数据按照原始格式重新排列组合。

除此之外,DS90UR906还可能涉及到一些特定的协议和信号处理技术,例如LVDS(低压差分信号)、8B/10B编码等。

这些技术和协议可以帮助DS90UR906更好地处理不同类型的数据,并确保数据

的完整性和准确性。

总的来说,DS90UR906的解码原理涉及到并行到串行和串行到并行的数据转换,以及与差分信号、时钟恢复、数据解封装等相关的技术和处理过程。

这些原理和技术的应用使得DS90UR906能够在高速数据传输中发挥重要作用。

LVDS接口标准

LVDS接口标准:LVDS接口是LCD Panel通用的接口标准,以8-bit Panel为例,包括5组传输线,其中4组是数据线,代表Tx0+/Tx0-... Tx3+/Tx3-。

还有一组是时钟信号,代表TxC+/TxC-。

相应的在Panel一端有5组接收线。

如果是6-bit Panel则只有3组数据线和一组时钟线。

LVDS接口又称RS-644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。

LVDS即低电压差分信号,这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。

LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。

目前,流行的LVDS技术规范有两个标准:一个是TIA/EIA(电讯工业联盟/电子工业联盟)的ANSI/TIA/EIA-644标准,另一个是IEEE 1596.3标准。

1995年11月,以美国国家半导体公司为主推出了ANSI/TIA/EIA-644标准。

1996年3月,IEEE公布了IEEE 1596.3标准。

这两个标准注重于对LVDS接口的电特性、互连与线路端接等方面的规范,对于生产工艺、传输介质和供电电压等则没有明确。

LVDS可采用CMOS、GaAs或其他技术实现,其供电电压可以从+5V到+3.3V,甚至更低;其传输介质可以是PCB连线,也可以是特制的电缆。

标准推荐的最高数据传输速率是655Mbps,而理论上,在一个无衰耗的传输线上,LVDS的最高传输速率可达1.923Gbps。

---- OpenLDI标准在笔记本电脑中得到了广泛的应用,绝大多数笔记本电脑的LCD显示屏与主机板之间的连接接口都采用了OpenLDI标准。

OpenLDI接口标准的基础是低压差分信号(Low Voltage Differential Signaling,LVDS)接口,它具有高效率、低功耗、高速、低成本、低杂波干扰、可支持较高分辨率等特点。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DS90LV110AT1to 10LVDS Data/Clock Distributor with FailsafeGeneral DescriptionDS90LV110A is a 1to 10data/clock distributor utilizing LVDS (Low Voltage Differential Signaling)technology for low power,high speed operation.Data paths are fully differential from input to output for low noise generation and low pulse width distortion.The design allows connection of 1input to all 10outputs.LVDS I/O enable high speed data transmis-sion for point-to-point interconnects.This device can be used as a high speed differential 1to 10signal distribution /fanout replacing multi-drop bus applications for higher speed links with improved signal quality.It can also be used for clock distribution up to 200MHz.The DS90LV110A accepts LVDS signal levels,LVPECL lev-els directly or PECL with attenuation networks.The LVDS outputs can be put into TRI-STATE by use of the enable pin.For more details,please refer to the Application Information section of this datasheet.Featuresn Low jitter 400Mbps fully differential data pathn 145ps (typ)of pk-pk jitter with PRBS =223−1data pattern at 400Mbps n Single +3.3V Supplyn Balanced output impedancen Output channel-to-channel skew is 35ps (typ)n Differential output voltage (V OD )is 320mV (typ)with 100Ωtermination load.n LVDS receiver inputs accept LVPECL signals n LVDS input failsafen Fast propagation delay of 2.8ns (typ)n Receiver open,shorted,and terminated input failsafe n 28lead TSSOP packagen Conforms to ANSI/TIA/EIA-644LVDS standardConnection Diagram 20098205Order Number DS90LV110ATMT See NS Package Number MTC28Block Diagram20098201October 2004DS90LV110AT 1to 10LVDS Data/Clock Distributor with Failsafe©2004National Semiconductor Corporation Absolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Supply Voltage (V DD -V SS )−0.3V to +4VLVCMOS/LVTTL Input Voltage (EN)−0.3V to (V CC +0.3V)LVDS Receiver Input Voltage (IN+,IN−)−0.3V to +4V LVDS Driver Output Voltage (OUT+,OUT−)−0.3V to +4VJunction Temperature +150˚CStorage Temperature Range −65˚C to +150˚CLead Temperature (Soldering,4sec.)+260˚C Maximum Package Power Dissipation at 25˚C 28L TSSOP1.209W Package Derating 28L TSSOP 9.67mW/˚C above +25˚CθJA28L TSSOP 103.4˚C/WattESD Rating:(HBM,1.5k Ω,100pF)>4kV (EIAJ,0Ω,200pF)>250VRecommended Operating ConditionsMin Typ Max UnitsSupply Voltage (V DD -V SS ) 3.0 3.33.6V Receiver Input Voltage0V DDV Operating Free Air Temperature-40+25+85˚CElectrical CharacteristicsOver recommended operating supply and temperature ranges unless otherwise specified Symbol ParameterConditionsMin TypMax Units LVCMOS/LVTTL DC SPECIFICATIONS (EN)V IH High Level Input Voltage 2.0V DD V V IL Low Level Input Voltage V SS0.8V I IH High Level Input Current V IN =3.6V or 2.0V;V DD =3.6V ±7±20µA I IL Low Level Input Current V IN =0V or 0.8V;V DD =3.6V ±7±20µA V CL Input Clamp Voltage I CL =−18mA −0.8−1.5V LVDS OUTPUT DC SPECIFICATIONS (OUT1,OUT2,OUT3,OUT4,OUT5,OUT6,OUT7,OUT8,OUT9,OUT10)V OD Differential Output VoltageR L =100Ω250320450mV R L =100Ω,V DD =3.3V,T A =25˚C260320425mV ∆V OD Change in V OD between Complimentary Output States 35|mV|V OS Offset Voltage (Note 3)1.1251.251.375V ∆V OS Change in V OS between Complimentary Output States 35|mV|I OZ Output TRI-STATE Current EN =0V,±1±10µA V OUT =V DD or GNDI OFF Power-Off Leakage Current V DD =0V;V OUT =3.6V or GND ±1±10µA I SA ,I SB Output Short Circuit Current V OUT+OR V OUT−=0V or V DD 1224|mA|I SAB Both Outputs Shorted (Note 4)V OUT+=V OUT−612|mA|LVDS RECEIVER DC SPECIFICATIONS (IN)V TH Differential Input High Threshold V CM =+0.05V or +1.2V or +3.25V,0+100mV V TL Differential Input Low Threshold V DD =3.3V−1000mVV CMR Common Mode Voltage Range V ID =100mV,V DD =3.3V 0.05 3.25V I INInput CurrentV IN =+3.0V,V DD =3.6V or 0V ±1±10µA V IN =0V,V DD =3.6V or 0V±1±10µAD S 90L V 110A T 2Electrical Characteristics(Continued)Over recommended operating supply and temperature ranges unless otherwise specifiedSymbol Parameter Conditions Min Typ Max Units SUPPLY CURRENTI CCD Total Supply Current R L=100Ω,C L=5pF,200MHz,125160mAEN=HighNo Load,200MHz,EN=High80125mA I CCZ TRI-STATE Supply Current EN=Low1529mANote1:“Absolute Maximum Ratings”are these beyond which the safety of the device cannot be guaranteed.They are not meant to imply that the device should be operated at these limits.The table of“Electrical Characteristics”provides conditions for actual device operation.Note2:All typical are given for V CC=+3.3V and T A=+25˚C,unless otherwise stated.Note3:V OS is defined as(V OH+V OL)/2.Note4:Only one output can be shorted at a time.Don’t exceed the package absolute maximum rating.AC Electrical CharacteristicsOver recommended operating supply and temperature ranges unless otherwise specified.Symbol Parameter Conditions Min Typ Max Units T LHT Output Low-to-High Transition Time,20%to80%,Figure4(Note5)390550psT HLT Output High-to-Low Transition Time,80%to20%,Figure4(Note5)390550psT DJ LVDS Data Jitter,Deterministic(Peak-to-Peak)(Note6)V ID=300mV;PRBS=223-1data;V CM=1.2V at400Mbps(NRZ)145psT RJ LVDS Clock Jitter,Random(Note6)V ID=300mV;V CM=1.2Vat200MHz clock2.8psT PLHD Propagation Low to High Delay,Figure5 2.2 2.8 3.6nsT PHLD Propagation High to Low Delay,Figure5 2.2 2.8 3.9nsT SKEW Pulse Skew|T PLHD-T PHLD|(Note5)20340psT CCS Output Channel-to-Channel Skew,Figure6(Note5)3591psT PHZ Disable Time(Active to TRI-STATE)High to Z,Figure1 3.0 6.0nsT PLZ Disable Time(Active to TRI-STATE)Low to Z,Figure1 1.8 6.0nsT PZH Enable Time(TRI-STATE to Active)Z to High,Figure110.023.0nsT PZL Enable Time(TRI-STATE to Active)Z to Low,Figure17.023.0nsNote5:The parameters are guaranteed by design.The limits are based on statistical analysis of the device performance over PVT(process,voltage and temperature)range.Note6:The measurement used the following equipment and test setup:HP8133A pattern/pulse generator),5feet of RG-142cable with DUT test board and HP83480A(digital scope mainframe)with HP83484A(50GHz scope module).The HP8133A with the RG-142cable exhibit a T DJ=26ps and T RJ=1.3psDS90LV110AT3AC Timing Diagrams20098204FIGURE 1.Output active to TRI-STATE and TRI-STATE to active output time20098215FIGURE 2.LVDS Driver TRI-STATE Circuit20098206FIGURE 3.LVDS Output Load20098209FIGURE 4.LVDS Output Transition TimeD S 90L V 110A T 4AC Timing Diagrams(Continued)20098207FIGURE 5.Propagation Delay Low-to-High and High-to-Low20098208FIGURE 6.Output 1to 10Channel-to-Channel SkewDS90LV110AT5DS90LV110A Pin DescriptionsPin Name#of PinInput/OutputDescriptionIN+1I Non-inverting LVDS inputIN -1I Inverting LVDS input OUT+10O Non-inverting LVDS Output OUT -10O Inverting LVDS OutputEN1IThis pin has an internal pull-down when left open.A logic low on the Enable puts all the LVDS outputs into TRI-STATE and reduces the supply current.V SS 3P Ground (all ground pins must be tied to the same supply)V DD2PPower Supply (all power pins must be tied to the same supply)Application InformationINPUT FAIL-SAFEThe receiver inputs of the DS90LV110A have internal fail-safe biasing for short,open,and teminated input conditions.LVDS INPUTS TERMINATIONThe LVDS Receiver input must have a 100Ωtermination resistor placed as close as possible across the input pins.UNUSED CONTROL INPUTSThe EN control input pin has internal pull down device.If left open,the 10outputs will default to TRI-STATE.EXPANDING THE NUMBER OF OUTPUT PORTSTo expand the number of output ports,more than one DS90LV110A can be used.Total propagation delay through the devices should be considered to determine the maxi-mum expansion.Adding more devices will increase the out-put jitter due to each pass.PCB LAYOUT AND POWER SYSTEM BYPASSCircuit board layout and stack-up for the DS90LV110A should be designed to provide noise-free power to the de-vice.Good layout practice also will separate high frequency or high level inputs and outputs to minimize unwanted stray noise pickup,feedback and interference.Power system per-formance may be greatly improved by using thin dielectrics (4to 10mils)for power/ground sandwiches.This increases the intrinsic capacitance of the PCB power system which improves power supply filtering,especially at high frequen-cies,and makes the value and placement of external bypass capacitors less critical.External bypass capacitors should include both RF ceramic and tantalum electrolytic types.RF capacitors may use values in the range 0.01µF to 0.1µF.Tantalum capacitors may be in the range 2.2µF to 10µF.Voltage rating for tantalum capacitors should be at least 5X the power supply voltage being used.It is recommended practice to use two vias at each power pin of the DS90LV110A as well as all RF bypass capacitor terminals.Dual vias reduce the interconnect inductance by up to half,thereby reducing interconnect inductance and extending the effective frequency range of the bypass components.The outer layers of the PCB may be flooded with additional ground plane.These planes will improve shielding and iso-lation as well as increase the intrinsic capacitance of the power supply plane system.Naturally,to be effective,these planes must be tied to the ground supply plane at frequent intervals with vias.Frequent via placement also improves signal integrity on signal transmission lines by providing short paths for image currents which reduces signal distor-tion.The planes should be pulled back from all transmission lines and component mounting pads a distance equal to the width of the widest transmission line or the thickness of the dielectric separating the transmission line from the internal power or ground plane(s)whichever is greater.Doing so minimizes effects on transmission line impedances and re-duces unwanted parasitic capacitances at component mounting pads.There are more common practices which should be followed when designing PCBs for LVDS signaling.Please see Appli-cation Note:AN-1108for additional information.D S 90L V 110A T 6Multi-drop Applications20098202Point-to-Point Distribution Applications20098203For applications operating at data rate greater than 400Mbps,a point-to-point distribution application should be used.This improves signal quality compared to multi-drop applications due to no stub PCB trace loading.The only load is a receiver at the far end of the transmission line.Point-to-point distribution applications will have a wider LVDS bus lines,but data rate can increase well above 400Mbps due to the improved signal quality.DS90LV110AT7Typical Performance CharacteristicsOutput Voltage (V OD )vs.Resistive Load (R L )Peak-to-Peak Output Jitter at V CM =+0.4V vs.VID2009821120098212Peak-to-Peak Output Jitter at V CM =+1.2V vs.VID Peak-to-Peak Output Jitter at V CM =+2.9V vs.VID2009821320098214D S 90L V 110A T 8Physical Dimensionsinches (millimeters)unless otherwise notedNS Package Number MTC28Order Number DS90LV110ATMT (Rail quantity of 48)DS90LV110ATMTX (2500piece Tape and Reel)National does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.For the most current product information visit us at .LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.BANNED SUBSTANCE COMPLIANCENational Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2)and the Banned Substances and Materials of Interest Specification (CSP-9-111S2)and contain no ‘‘Banned Substances’’as defined in CSP-9-111S2.National Semiconductor Americas Customer Support CenterEmail:new.feedback@ Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National Semiconductor Asia Pacific Customer Support CenterEmail:ap.support@National SemiconductorJapan Customer Support Center Fax:81-3-5639-7507Email:jpn.feedback@ Tel:81-3-5639-7560DS90LV110AT 1to 10LVDS Data/Clock Distributor with Failsafe。