基于Tsi148的PCI-VME总线接口设计

VME自定义总线接口设计精品资料

VME自定义总线是一条并行运行的总线,该总线采用数据广播的方式,可以方便各个板块同时接收同一个数据。其由同步控制卡提供5KHz时钟,每200us同步控制卡将数据锁存线拉高,向光栅译码卡发出一个脉冲,此时光栅译码卡和激光干涉仪等设备锁存该时刻的数据,其读数不再发生变化,然后同步控制卡产生一连串的读取信号,将各个光栅尺的数据读出。同时切换总线上的地址,并生成采样保持,读取和地址三个信号置于自定义总线,运动控制卡通过对自身所需的地址的识别在读信号低电平时获得相应位置传感器的信号。

关键词:

FPGA;VME;自定义总线;光栅译码卡

1引言

在光刻机双工件台控制系统中,VME总线使用了三个接口共430根线路接入,通过背板互联的有P1,P2两个接口320根线路接入。实际上VME标准协议并没有完全使用全部线路,而是为用户预留了部分自定义线路,增加了设计的灵活性[4]。由于VME总线主要用于工控机与各板卡的通信,同步控制卡与激光计数卡和光栅译码卡使用总线就会产生严重冲突,影响采用是实时性,因此这里将VME总线中未使用的管脚作为自定义总线管脚,这样避免了增加新的硬件接口,而且在硬件设计上可以和VME总线一起考虑。自定义同步总线数据传输完全根据主控总线提供的时序进行,地址线包含了对数据发送和接收方的定义。每个总线传输周期中,数据发送端和接收端的身份根据地址寻址关系自动切换,而避免了总线控制权更迭时的握手,及数据传输优先级或传输抢占等问题,总线控制信号来自同一个时钟域,从节点仅响应控制信号,可忽略节点间时钟相位差影响。在每个伺服周期,设计了一个数据传输序列来实现共享数据交互。数据传输序列由若干个总线传输周期构成,每个周期完成32bit的数据共享。通过设定总线地址来设置数据传输序列的传输内容,当所有的设定总线地址被遍历,则当前周期数据传输已经完成,所有被规划传输的数据都被所有的运动控制卡所共享[1]。

VME总线接口逻辑分析和电路设计

VME总线接口逻辑分析和电路设计

谢长生;徐睿

【期刊名称】《电子与封装》

【年(卷),期】2004(004)002

【摘要】本文介绍了VME总线接口逻辑芯片的逻辑分析和电路设计.通过这些工作,对用户利用CY7C964芯片构造通用的总线接口,或根据实际情况在CY7C964电路构成的基础上进行VME接口的简化或优化设计,以及对开发基于VME总线协议的接口芯片有所帮助.

【总页数】7页(P34-40)

【作者】谢长生;徐睿

【作者单位】中国电子科技集团公司第58研究所,江苏,无锡,214035;中国电子科技集团公司第58研究所,江苏,无锡,214035

【正文语种】中文

【中图分类】TN431.2

【相关文献】

1.VME总线接口逻辑的CPLD设计及试验 [J], 吴杰长;郭朝有;李雄涛

2.多处理器系统中基于FPGA的VME总线接口设计 [J], 杨亮亮;史伟民;汪立君;葛瑞广

3.基于FPGA的VME总线接口的设计与实现 [J], 邵文建;李超

4.基于FPGA的从设备VME总线接口设计 [J], 万勇利;魏凯;韩记晓;陈兴林

5.基于FPGA的VME自定义总线接口设计 [J], 韩记晓;万勇利;张常江;赵为志;陈兴林

因版权原因,仅展示原文概要,查看原文内容请购买。

基于PCI总线位置控制系统的接口卡的实现

为 电压 的模 拟 量 , 经 功放控 制 电机 的转 动 ; 再 电机 每转 动一 圈 , 电编 码器 输 出 5 0个 脉 冲 , 冲 数 ( 示 电 光 0 脉 表 机转 动 的距 离 ) 被接 口卡 计 数 , 后 被计 算 机 读 取 , 然 计 算机 从而 可 以控制 电机 转动 的位 置l 。 3]

墨 Q 兰 ! 曼 兰 二

CN¨ 一 2 3 / 0 4 T

实

验

技

术

与

管

理 ห้องสมุดไป่ตู้

第 2 7卷

第 5期

21 0 0年 5月

Ex e i e t lT e h o o y a d M a a e e t p rm n a c n l g n n g m n

Vo1 2 N o M a . 2 1 . 7 .5 y 00

Ab ta t o h u p s fma i g s u e t a d e t e t c n l g fc mp t rc n r l n , n i t ra e c r s r c :F r t e p r o e o k n t d n s h n l h e h o o y o o u e o to l g a e f c a d i n

计 算 机 技 术 应 用

基 于 P I 线位 置 控 制 系统 的接 口卡 的实现 O总

王 苑 , 景 新 , 长 德 董 赵

( 华 大 学 精 密 仪 器 与 机 械 学 系 ,北 京 1 0 8 ) 清 0 0 4

摘

要 : 了使 学 生 掌 握 计 算 机 控 制 技 术 , 合 计 算 机 控 制 系统 实验 课 , P I0 4 计 了 一 块 接 口卡 , 卡 为 结 用 C95 设 该

基于PCIe总线高速数据传输系统的设计与实现的开题报告

基于PCIe总线高速数据传输系统的设计与实现的开题报告一、选题背景随着现代科技的飞速发展,数据处理和传输变得越来越重要。

不仅需要高效的数据传输速度以满足现代大数据处理的需要,也需要高可靠性和兼容性以适应不同应用场景的需求。

PCI Express(PCIe)总线技术由于其高速、可靠和广泛的应用支持而成为了一种重要的数据传输标准。

本课题基于此,旨在设计和实现一个基于PCIe总线的高速数据传输系统。

二、研究目的和意义本课题主要研究基于PCIe总线的高速数据传输系统的设计和实现,旨在提供一个具有高速、可靠、兼容性好的数据传输方案,以满足现代数据处理需求。

其意义在于:1. 提高数据处理效率。

PCIe总线技术具有高速传输和低延迟的特点,在大数据处理和高性能计算中能够显著提高数据传输效率。

2. 提高数据传输可靠性。

PCIe总线技术具有高可靠性的特点,其锁定机制和CRC校验功能能够保证数据传输的准确性和完整性。

3. 提高数据传输兼容性。

PCIe总线技术是一种广泛应用的数据传输标准,被应用于各种不同的领域,能够实现不同设备之间的数据交换和共享。

三、研究内容和研究方法本课题的主要研究内容包括:1. 设计一个符合PCIe总线规范的高速数据传输系统。

包括硬件电路设计和软件控制程序设计。

2. 实现高速数据传输系统,采用HDL语言设计硬件电路,采用C++设计软件控制程序。

3. 测试和验证高速数据传输系统,包括性能测试、稳定性测试和兼容性测试等。

本课题研究采用的方法主要包括:1. 系统设计方法。

根据PCIe总线规范,设计一个符合标准的高速数据传输系统,保证系统的性能、稳定性和兼容性。

2. 硬件设计方法。

采用HDL语言设计系统的硬件电路,包括PCIe 总线接口电路、数据传输电路和控制逻辑电路等。

3. 软件设计方法。

采用C++设计软件控制程序,包括系统的控制逻辑和数据传输协议等。

4. 测试和验证方法。

对系统进行性能测试、稳定性测试和兼容性测试等,以验证系统的可靠性和兼容性。

计算机总线系统架构

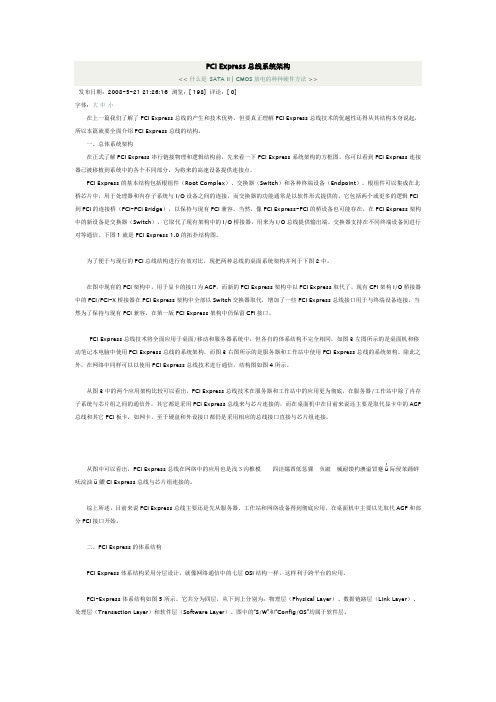

PCI Express总线系统架构<< 什么是SATA II | CMOS放电的种种硬件方法 >>发布日期:2008-5-21 21:26:16 浏览:[ 198] 评论:[ 0]字体:大中小在上一篇我们了解了PCI Express总线的产生和技术优势,但要真正理解PCI Express总线技术的优越性还得从其结构本身说起,所以本篇就要全面介绍PCI Express总线的结构。

一、总体系统架构在正式了解PCI Express串行链接物理和逻辑结构前,先来看一下PCI Express系统架构的方框图。

你可以看到PCI Express连接器已被移植到系统中的各个不同部分,为将来的高速设备提供连接点。

PCI Express的基本结构包括根组件(Root Complex)、交换器(Switch)和各种终端设备(Endpoint)。

根组件可以集成在北桥芯片中,用于处理器和内存子系统与I/O设备之间的连接,而交换器的功能通常是以软件形式提供的,它包括两个或更多的逻辑PCI 到PCI的连接桥(PCI-PCI Bridge),以保持与现有PCI兼容。

当然,像PCI Express-PCI的桥设备也可能存在。

在PCI Express架构中的新设备是交换器(Switch),它取代了现有架构中的I/O桥接器,用来为I/O总线提供输出端。

交换器支持在不同终端设备间进行对等通信。

下图1就是PCI Express 1.0的拓扑结构图。

为了便于与现行的PCI总线结构进行有效对比,现把两种总线的桌面系统架构并列于下图2中。

在图中现有的PCI架构中,用于显卡的接口为AGP,而新的PCI Express架构中以PCI Express取代了,现有CPI架构I/O桥接器中的PCI/PCI-X桥接器在PCI Express架构中全部以Switch交换器取代,增加了一些PCI Express总线接口用于与终端设备连接,当然为了保持与现有PCI兼容,在第一版PCI Express架构中仍保留CPI接口。

《2024年基于FPGA的PCIE总线接口和光纤通信模块设计》范文

《基于FPGA的PCIE总线接口和光纤通信模块设计》篇一一、引言随着信息技术的飞速发展,数据传输的速度和效率成为了系统性能的关键因素。

FPGA(现场可编程门阵列)以其高度的可定制性和并行处理能力,在高速数据传输和处理领域得到了广泛应用。

本文将详细介绍基于FPGA的PCIE总线接口和光纤通信模块设计,探讨其设计原理、实现方法和应用前景。

二、PCIE总线接口设计1. 设计原理PCIE(Peripheral Component Interconnect Express)总线是一种高速串行计算机扩展总线标准,具有高带宽、低延迟、支持即插即用等特点。

FPGA作为PCIE设备的核心控制器,需要设计相应的接口电路以实现与主机的通信。

2. 实现方法在FPGA中,PCIE总线接口的设计主要包括物理层设计、数据链路层设计和事务层设计。

物理层设计负责信号的收发和电气特性的匹配;数据链路层设计负责数据的封装、解封和流控制;事务层设计则负责处理数据传输过程中的各种事务请求。

3. 优势与挑战PCIE总线接口的设计具有高带宽、低延迟、可扩展性强等优势,能够满足高速数据传输的需求。

然而,设计过程中也面临着诸多挑战,如信号完整性问题、时钟同步问题、协议复杂性等。

需要采用先进的EDA工具和设计方法,以确保设计的可靠性和稳定性。

三、光纤通信模块设计1. 设计原理光纤通信模块是一种基于光纤的高速数据传输模块,具有传输距离远、传输速率高、抗干扰能力强等优点。

在FPGA系统中,光纤通信模块负责将数据通过光纤传输到其他设备或系统。

2. 实现方法光纤通信模块的设计主要包括光模块电路设计、光纤接口设计和FPGA控制逻辑设计。

光模块电路设计负责将电信号转换为光信号或将光信号转换为电信号;光纤接口设计负责实现光纤与光模块之间的物理连接;FPGA控制逻辑设计则负责控制光模块的发送和接收过程。

3. 关键技术光纤通信模块设计的关键技术包括光模块的选择与配置、光纤类型的选择、光信号的调制与解调、光纤接口的电气特性等。

PCIe的原理及体系架构_学习笔记

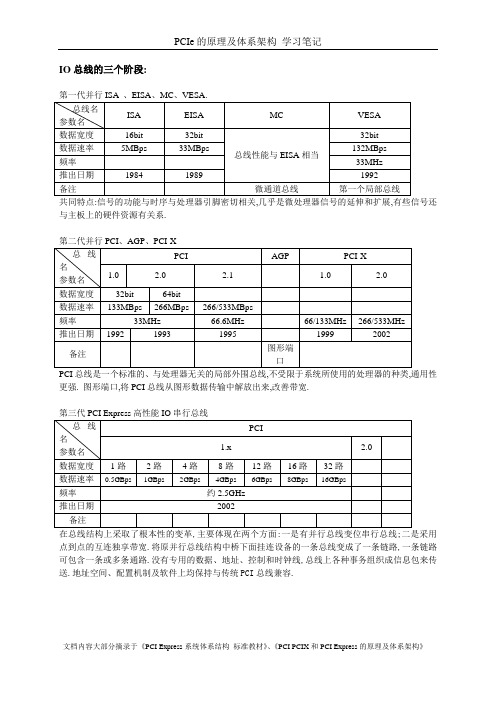

IO总线的三个阶段:第一代并行ISA 、EISA、MC、VESA.共同特点:信号的功能与时序与处理器引脚密切相关,几乎是微处理器信号的延伸和扩展,有些信号还与主板上的硬件资源有关系.第二代并行PCI、AGP、PCI-XPCI总线是一个标准的、与处理器无关的局部外围总线,不受限于系统所使用的处理器的种类,通用性更强. 图形端口,将PCI总线从图形数据传输中解放出来,改善带宽.第三代PCI Express高性能IO串行总线在总线结构上采取了根本性的变革,主要体现在两个方面:一是有并行总线变位串行总线;二是采用点到点的互连独享带宽.将原并行总线结构中桥下面挂连设备的一条总线变成了一条链路,一条链路可包含一条或多条通路.没有专用的数据、地址、控制和时钟线,总线上各种事务组织成信息包来传送.地址空间、配置机制及软件上均保持与传统PCI总线兼容.第一代和第二代都是并行总线,有多条地址线、数据线和控制线,挂接多个设备,称为下挂式总线(Multi-Drop),总线带宽由多个设备共享.通过提高数据宽度和频率来改善带宽的代价是挂接的电器负载减少(由于功耗增加和静态定时减少).PCIx与PCI相比:由于采用了PLL,频率更高性能更好;在地址和数据的基础上增加属性,从而可以高效管理缓冲区;分离事务协议相对延迟事务协议来说,提高了总线利用效率;可不需要中断引脚,改用消息信号中断(带内)体系结构,中断效率更高.基于PCI总线的结构最基本的PCI总线平台包含三级总线:FSB(Front-Side Bus)、PCI和ISA,FSB是处理器子系统的总线(Host总线),总线定义完全取决于系统所用的处理器;PCI局部总线是一个完全与处理器无关的总线,不受限微处理器的种类;ISA总线(IO扩展总线),也有采用EISA或MC总线的.不同的总线之间通过相应的桥芯片来连接.平台中两极桥是必须的,一是Host到PCI的(常称为主桥——Host桥),即北桥;另一个是PCI总线的桥(常称为扩展总线桥),即南桥.最基本的基于PCI总线的平台PCI地址空间映射x86 CPU的内存与I/O独立编址,I/O对应寄存器,内存对应RAM.因此,访问IO空间用IO读写指令,访问内存空间用内存读写指令.IO读写一般用于低速传输一些状态、控制寄存器的读写等。

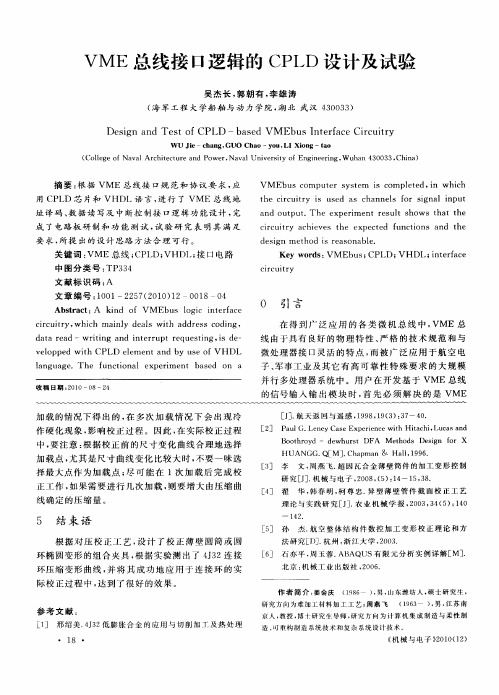

VME总线接口逻辑的CPLD设计及试验

中 图分 类 号 : TP3 4 3 文献标 识码 : A

文 章 编 号 :0 1 2 7 2 1 )2 O 1 0 1 0 —2 5 (0 0 1 O 8— 4

Ab ta t A k n o VM Eb s o i n e f c sr c : id f u l g c t ra e i

Pa ulG.Le yCa eExp re c t ia hi Luc s a d ne s e in e wih H t c , a n

中, 要注 意 : 根据 校正 前 的尺寸变 化 曲线 合理 地选择 加 载点 , 尤其是 尺寸 曲线 变化 比较大 时 , 不要 一味选 择 最大点 作为加 载 点 ; 可 能在 1次 加 载后 完 成校 尽

VME总 线接 口逻 辑 的 C L P D设 计及 试验

吴 杰 长 , 朝 有 , 雄 涛 郭 李 ( 军 工 程 大 学船 舶 与 动 力 学 院 , 北 武 汉 4 0 3 ) 海 湖 3 0 3

De i n a d Te to sg n s fCPLD — b s d VM Ebu n e f c r u t y — a e s I t ra e Cic ir

[]航 天返 回 与遥 感 ,9 8 1 ( )3 —4 . J. 19 ,9 3 :7 0

完整版PCIe总线基础及FPGA设计实战

PCI Express 总线基础及FPGA设计实战1. PCI Express基础PCIe总线是基于PCI总线发展起来的,很多基本概念都来自于PCI总线,有必要在介绍PCIe之前了解PCI总线。

1.1 PCI基础PCI总线作为处理器系统的局部总线,其主要目的是为了连接外部设备,而不是作为处理器系统的系统总线连接Cache和主存储器。

PCI总线作为系统总线的延伸,其设计考虑了许多与处理器相关的内容,孤立的研究PCI总线并不可取,因此需要将PCI作为存储器系统的一个部分来研究。

1.1.1几个重要概念1) PCI总线空间与处理器空间隔离PCI设备具有独立的地址空间,即PCI总线地址空间,该空间与存储器地址空间通过HOST主桥隔离。

处理器需要通过HOST主桥才能访问PCI设备,而PCI设备需要通过HOST主桥才能方位主存储器。

要注意区分存储器地址空间和PCI总线地址。

在一个处理器系统中,存储器域、线域与HOST主桥的关系如下图。

存储器域与PCI总线域的划分一个DRAM控制器和两个HOST主桥组成。

在这个处理存储器域和PCI总线域地址空间。

其中HOST主桥x和HOST主桥y分别管理PCI总线x域与PCI总线y域。

CPU访问PCI设备,必须通过HOST主桥进行地址转换,而PCI设备访问存储器设备,也需要HOST主桥进行地址转换。

HOST主桥PCI总疗fit證城「、CPU\ DRAM1控制誥图中的处理器系统由一个CPU器系统中,包含CPU域、DRAM域、DH.AMPCI设計I PCI邊彌II ]|Ki十一mn 城K I g畑I-■ I卩门总蛛y城的一个重要作用就是将存储器访问的存储器地址转换成 PCI 总线地址。

CPU 域地址空间是指CPU 所能直接访问的地址空间集合。

DRAM 域地址空间是指 DRAM 控制器所能访问的地址空间集合,又称为主主存储器域。

存储器域是CPU 域和DRAM 域的集合。

存储器域包括 CPU 内部的通用寄存器、存储器 映射寻址的寄存器、主存储器空间和外部设备空间。

一种PCI总线接口的设计

sr o t r Su e on u c insm ua in frt eh r wa ed sg f CIit ra e i s fwa ei s d d ig f n t i lto o h a d r e ino n e fe .Th i e o P esm—

两个值一致 , 偶校验没错 , 否则 , 在下一个时钟脉冲

设备 或 通 过 P RR#有 效 报 告 数 据 错 误 , 通 过 E 或 SR E R#有效报告 地址错 误 。

延时计数模块用来约束主设备对总线的占有时

第1 7卷 第 5期

金鹏 飞 , 毛永毅 , 张宏君 : 一种 P I C 总线接 口的设计

中 图分 类 号 : T 3 6 P 3 文 献 标 识 码 : A 文 章 编 号 : 10 —3 6 ( 0 20 —0 6 —0 0 7 24 2 1) 5 0 5 5

De i n o s g f PCI b s i e f c u nt r a e

JN e g e , MAO o g i, Z I P n fi Y n y HANG n j n Ho gu

随 着 密度 和 速 度 的提高 , 现 场可 编 程 门阵列 用 ( il P o rmma l GaeAra ,F GA)自行 设 Fed rga - be t ry P 计 P I 口变得容 易实 现 , 且许多 F GA制造 商 C接 而 P 都 提供 了 P I 口宏 核逻 辑 ( C P oe , C接 P IIC r) 降低 了 设 计难度 。该 设计 方 法具 有 较 强 的灵 活 性 , 以 自 可

.

Dl3 >= ^ - = T 二 ^ >

) )一 (

一

1 P I 口信 号及 总线 操 作 C 接

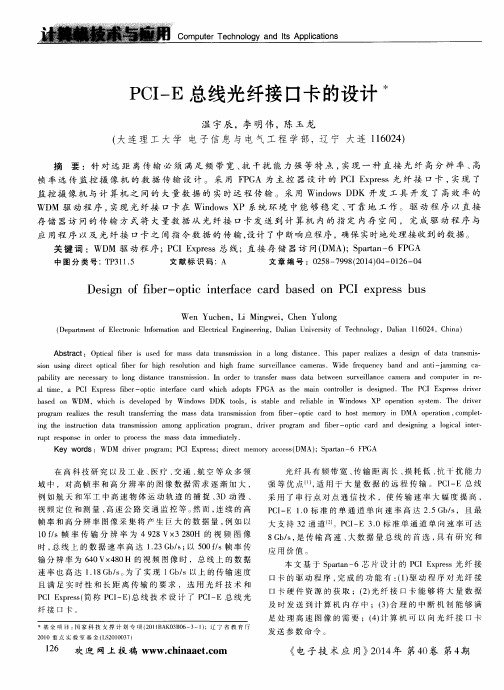

PCI—E总线光纤接口卡的设计

P C I — E总线光 纤接 口卡 的设计 : l :

温 宇 辰 ,李 明 伟 ,陈 玉 龙 ( 大 连 理 工 大 学 电 子 信 息 与 电 气 工 程 学 部 ,辽 宁 大 连 1 1 6 0 2 4 )

中图分 类号 : T P 3 1 1 . 5 文 献 标 识 码 :A 文 章 编 号 :0 2 5 8 — 7 9 9 8 ( 2 0 1 4 ) 0 4 — 0 1 2 6 — 0 4

De s i g n o f i f b e r -o p t i c i n t e r f a c e c a r d b a s e d o n PCI e x p r e s s b u s

摘 要 :针 对 远 距 离 传 输 必 须 满 足 频 带 宽 、 抗 干扰 能 力强 等 特 点 , 实现 一 种 直接 光 纤 高 分辨 率 、 高

帧 率远 传 监 控 摄 像 机 的 数 据 传输 设 计 。采 用 F P G A 为主 控 器设 计 的 P C I E x p r e s s光 纤 接 口 卡 , 实现 了

Ab s t r a c t : Op t i c a l i f b e r i s u s e d f o r ma s s d a t a t r a n s mi s s i o n i n a l o n g d i s t a n c e .T h i s p a p e r r e a l i z e s a d e s i g n o f d a t a t r a n s mi s —

监 控 摄 像 机 与 计 算 机 之 间 的 大 量 数 据 的 实 时 远 程 传 输 。采 用 Wi n d o w s D D K 开 发 工 具 开 发 了 高 效 率 的

机载恶劣环境下BGA芯片应用研究

机载恶劣环境下BGA芯片应用研究作者:李乔杨来源:《科学与财富》2018年第17期摘要:当前军用飞机的性能提高对机载计算机性能提出了更高的要求,为了提高性能、增加集成度,BGA芯片在机载领域应用非常广泛。

在机载恶劣环境中长时间使用,BGA芯片脱焊问题不断出现,严重影响到产品的可靠性。

本文对机载计算机中BGA芯片应用进行研究,以某型飞机任务计算机为例进行对比试验,并最终给出应用建议。

关键词:BGA芯片、陶瓷封装、散热1引言当前军用飞机的功能日益增多,飞机性能不断增强,机载计算机作为现代飞机的重要组成部分,要求其性能不断提高,计算机的集成度逐渐增加。

随着微电子技术发展,单个芯片的IC数量呈爆炸性增长。

与此同时,为了获得高集成度,在芯片封装领域BGA元件具有IO数量众多,信号传输路径短,信号衰减小的特点,在集成度增加的同时BGA元件拥有更小的体积,更好地散热性能和电性能。

为了增加计算机的集成度,BGA封装芯片已成为机载计算机工程师共同的选择。

机载计算机属于恶劣环境计算机,其工作环境苛刻,可靠性要求高。

BGA元件是一种温度和湿度敏感器件,对焊点的可靠性要求严格,出现故障后,维修起来比较困难。

BGA元件在恶劣环境使用易发生脱焊、鼓包等失效情况。

本文已某型任务显控计算机中处理器模块为例,对机载恶劣环境中BGA芯片应用进行研究。

2 事例概述该处理器模块包括两个独立的处理节点,主节点和从节点。

每个处理节点采用一片PC7447A处理器芯片和一片Tsi109-200IL桥接器芯片(D3、D4)组成核心电路,两个处理节点通过PCI总线进行互联,主单元作为PCI总线的主设备完成PCI总线的初始化和仲裁。

VME总线的主控制器Tsi148芯片和MBI子卡通过连接在PCI总线上,该模块作为整机中VME总线的主控制器,在系统中负责飞机任务管理和数据计算功能。

模块见图1。

通过对故障模块电装工艺流程、器件烘烤、焊盘尺寸、印刷网板、焊接温度清查,以及不同模块工艺、动力学仿真和热仿真对比分析,故障模块维修清查等几个方面的清查和分析,最终确认芯片脱焊的原因是:Tsi109-200IL为工业级塑封器件,长期在恶劣环境下受到热应力影响,由于塑封器件自身散热效果不好导致脱焊。

PCI-E总线设计总结_liguisheng_2013-11-08

PCI-E设计总结Name:liguishengDate:2013-11-08PCI-E的发展最初PCI总线是32bit,33Mhz,这样带宽为133Mbps;接着因为在服务器领域传输要求Intel把总线位数提高到64,这样又出现了2种PCI总线,分别为64bit/33Mhz和64bit/66Mhz,当然带宽分别翻倍了,为266Mbps和533Mbps,这个比较通常的名称应该是pci-64,但这好像是intel自己做的,没有行业标准。

同时服务器领域也没闲着,几家厂商联合制定了PCI-X,这个就是真正PCI下一代的工业标准了,其实也没什么新意,就是64bit,133Mhz版本的PCI,那这样带宽就为1Gbps,后来PCI-X 2.0,3.0又分别提升频率,经历过266Mhz,533Mhz,甚至1GMhz。

这个带宽可以说是非常足够的了,不过这个时候PCI也面临一些问题:一方面是频率提高造成的并行信号串扰,另一方面是共享式总线造成的资源争用,总之也就是说虽然规格上去了,但实际效果可能跑不了这些指标。

随着民用领域显卡带宽要求提升,服务器领域对pci-X感觉力不从心,pci-E真正显出了优势:PCI-E标准的最大特点就是串行总线与并行体系的PCI没有任何相似之处,它采用串行方式传输数据,而依靠高频率来获得高性能,因此PCI Express也一度被人称为“串行PCI”。

由于串行传输不存在信号干扰,总线频率提升不受阻碍,PCI Express很顺利就达到2.5GHz的超高工作频率。

其次,PCI Express采用全双工运作模式,最基本的PCI Express 拥有4根传输线路,其中2线用于数据发送,2线用于数据接收,也就是发送数据和接收数据可以同时进行。

相比之下,PCI总线和PCI-X总线在一个时钟周期内只能作单向数据传输,效率只有PCI Express的一半;加之PCI Express使用8b/10b编码的内嵌时钟技术,时钟信息被直接写入数据流中,这比PCI总线能更有效节省传输通道,提高传输效率。

基于PCIe总线的专用高速信号采集卡设计

基于PCIe总线的专用高速信号采集卡设计林连雷;易宇【摘要】In some radar countermeasure tests,a high-speed signal acquisition system was designed to assess the test re-sults accurately. This system has the maximum sampling rate of 500 MS/s,in which the cache in the card is 1 GB,and can pro-vide data transmission interface of high-speed storage system to expand the storage capacity. Two operation modes of the scope operating mode and the continuous acquisition mode are offered in this system,and users can use the different operating modes according to the requirements to process the collected data. This system has perfect trigger function,and is convenience for the users to analyze the data.%在某些雷达对抗试验中,为了精确地评估试验效果,设计了一个高速信号采集系统,该系统具有最高为500 MS/s的采样率,板上缓存为1 GB,同时提供与高速存储系统的数据传输接口以供外扩存储容量.该系统提供了示波器工作模式和连续采集工作模式两种工作模式,用户可根据需求使用不同的工作模式对采集到的数据进行处理,同时该系统具有完善的触发功能,以方便用户对数据进行分析.【期刊名称】《现代电子技术》【年(卷),期】2015(038)021【总页数】5页(P52-55,59)【关键词】PCIExpress;高速数据采集;模拟信号;同步脉冲信号【作者】林连雷;易宇【作者单位】哈尔滨工业大学自动化测试与控制系,黑龙江哈尔滨 150001;哈尔滨工业大学自动化测试与控制系,黑龙江哈尔滨 150001【正文语种】中文【中图分类】TN911.7-34在某些雷达对抗试验中,为了精确地评估试验效果,需要对雷达接收机产生的回波信号、同步脉冲信号等进行采集,通过对这些信号的分析得出试验结果,基于此目的,需要设计一个具有高速采集能力的系统,用于采集雷达接收机产生的回波信号、同步脉冲信号;同时该系统需要具备大容量存储能力,用于实时存储采集到的数据,为雷达对抗试验后续的数据分析提供数据来源;为了更好地捕捉雷达对抗试验中的关键信号,该系统应该具备完善的触发功能。

基于PCI总线的全闭环交流伺服的控制系统

基于PCI总线的全闭环交流伺服的控制系统2008-9-9 19:27:00 来源:中国自动化网摘要:基于PCI总线设计开放式交流伺服运动控制系统,具有模块化,智能化,柔性化的特点。

采用运动控制卡+PC作为上位控制单元,交流伺服驱动器和伺服电机作为执行机构,光栅尺+数据采集卡作为直线位移检测装置,设计出全闭环运动控制系统。

同时利用VC++编程实现对伺服电机高速、高精度的控制。

关键词:全闭环 PCI总线交流伺服运动控制卡Full-closed Loop AC Servo Control System Based On PCI BUSGUAN Jian, SHU Zhibing(Automation College, Nanjing University of Technology, Nanjing 210009, China)关键, 舒志兵(南京工业大学自动化学院运动控制研究所, 江苏南京210009)Abstract:The open servo motion control system based on PCI BUS is modular, intelligent, flexible. With motion controller and PC as high level control unit, AC servo driver and servo motor as execute component, the optical grating ruler and data collection as position examination part, a motion control system of full-closed loop is designed. And by VC++ the system can control servo motor with high speed and high precision.Keywords:Full-closed Loop PCI BUS AC Servo Motion Controller0 引言现代工业生产中,交流伺服控制系统已经被广泛使用。

基于PCI总线的直扩通信信号模拟信号源的设计的开题报告

基于PCI总线的直扩通信信号模拟信号源的设计的开题报告一、选题背景随着通信技术的不断发展,直扩通信技术在高速数据传输、射频信号处理和信道编解码等方面具有广泛的应用。

直扩通信技术的核心是信号源的设计,信号源能够产生带有特定性能参数的信号波形,如带宽、载频、数据速率等。

因此,设计一个基于PCI总线的直扩通信信号模拟信号源具有重要的意义。

基于PCI总线的直扩通信信号模拟信号源,不仅需要考虑实时性和稳定性,还需要充分考虑信号源的数据传输速率、信号源控制、外部接口等多方面的因素,是一个涉及多学科知识的复杂系统工程。

本文将着重探讨如何设计一个基于PCI总线的直扩通信信号模拟信号源,以满足实际的工程应用需求。

二、选题意义1.增强科技创新能力本研究通过对基于PCI总线的直扩通信信号模拟信号源的设计和开发,有助于提升国内通信技术领域的科技创新能力。

2.拓展技术应用领域直扩通信技术在高速数据传输、射频信号处理和信道编解码等方面具有广泛的应用,本研究可为这些应用领域的开发提供技术支持。

3.促进社会发展基于PCI总线的直扩通信信号模拟信号源的设计和开发,可以为相关领域提供可靠的技术设备和解决方案,促进社会经济的发展。

三、研究内容1.系统基础设计本系统的基础设计是通过PCI总线与上位机通信,实现直扩通信信号的采集、处理和输出。

设计基础部分的主要任务是建立合理的硬件、软件框架,保证系统的可靠性和高效性。

2.设备选型及供应商管理为确保系统正常运行,需要进行设备选型、制定供应商管理流程,推行可持续发展的设备资源管理。

3.系统功能设计系统功能设计是开发过程的核心,根据前期的设计需求,提出详细的功能设计方案,并进行软件编程、软硬件调试和性能测试等工作。

四、研究步骤本研究的具体研究步骤如下:1.资料查阅:对PCI总线、直扩通信技术等相关信息进行查阅和整理。

2.需求分析:分析直扩通信信号模拟信号源的应用需求,确定系统需求和性能指标。

3.系统方案设计:设计硬件和软件系统框架,选择系统中所需要的部件材料及供应商。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于Tsi148的PCI-VME总线接口设计作者:刘宝明阚丹丹史云辉来源:《现代电子技术》2010年第04期摘要:VME总线是一种开放式工业计算机总线,在VME总线多主处理计算机系统中,通常需要进行PCI总线与VME总线接口互连。

这里分析了业界最先进的PCI-VME总线互连芯片Tsi148的原理与功能,介绍Tsi148在VME总线智能模块中进行PCI-VME接口互连的方法,给出通过本地PCI总线接口进行Tsi148初始化和VME系统配置的软件流程。

实践表明,采用Tsi148进行PCI-VME互连设计,实现了VME总线的高速数据传输和控制功能,并在实际应用中取得了良好的效果。

关键词:Tsi148;PCI总线;VME总线;接口互连中图分类号:TP368文献标识码:B文章编号:1004-373X(2010)04-108-03Design of PCI-VME Bus Interface Based on Tsi148LIU Baoming,KAN Dandan,SHI Yunhui(Jiangsu Automation Research Insititute,China Shipbuilding Industry GroupCorporation,Lianyungang,222006,China)Abstract:VMEbus is an open standard industrial computer bus,in the multi-master computer system of VMEbus,the PCI and VME interface are needed to be interconnected.The principle and function of Tsi148,which is the most advanced device for PCI-VME are analysed.The method for PCI/X-VME interconnecting in intelligent board-based Tsi148 is introduced.The flow of software for initializing of Tsi148 and configuration of system from local PCI bus are brought forward.Practice indicates that the design of PCI-VME by Tsi148 has achieved the high speed data transmission and has bus function,and has achieved favorable purpose.Keywords:Tsi148;PCI Bus;VME Bus;interface interconnect0 引言VME(Versa Module Eurocard)总线是一种开放性工业标准计算机总线,支持32/64位总线宽度,采用主控/目标结构异步、复用/非复用方式;支持16/24/32/64位寻址和8/16/24/32/64位数据传送以及跨界数据传送;具有7条中断请求线、4条总线请求线,采用菊花链优先级队列;系统最多支持21个主处理模块,具有系统错误检测功能[1]。

VME总线是一种高可靠性和高兼容性的系统总线,广泛应用于嵌入式系统中,尤其是在多主处理系统中,它系统总线,可以实现多主控处理;PCI总线作为一种高性能32或64位地址数据复用的总线,具有性能高,成本低,适应性强,数据完整性及软件兼容性都好的特点,实现处理器和存储器系统以及各种接口系统的连接。

因此在VME总线的主控系统中,VME总线与PCI总线之间需要专门的桥接芯片进行互连,如早期Cypress公司的VIC068A,VIC64,CY7C960芯片,但目前均已停产,取而代之的是Tundra公司的Universe Ⅱ和Tsi148。

Tsi148是2004年Tundra公司推出的新一代PCI/X-VME互连芯片,是早期Universe Ⅱ的替代和升级产品,PCI总线接口可支持PCI-X 133 MHz,VME总线接口支持VME,2eVME,2eSST等传输协议,可以灵活实现Master,Slave,SCON系统控制器功能,专门为VME总线主处理模块、智能模块中的PCI-VME总线接口互连而设计。

1 Tsi148的工作原理1.1 Tsi148的功能Tsi148实质是一个PCI总线与VME总线地址空间转换与互连的非透明桥,实现了本地PCI 或PCI/X总线操作与系统VME总线操作的相互转换。

Tsi148的PCI/X总线接口可以全面兼容PCI或PCI/X。

PCI-X总线的工作频率介于50~133 MHz之间,PCI总线的工作频率介于33~66 MHz之间,两种模式下支持32位或64位寻址和数据;VME总线兼容传统VME32协议,支持VME64扩展和2eVME,2eSST协议,完备的总线系统控制器功能、中断和中断处理功能可通过PCI/X总线或VME总线进行初始化配置;两个可进行软件配置的DMA控制器,支持直接模式和链式模式的DMA操作,可以进行高速数据传输[4]。

1.2 Tsi148的组成Tsi148的内部功能框图如图1所示。

芯片内部主要由以下几个功能模块组成:PCI/X接口单元、VME接口单元、Linkage 模块单元、DMA单元、寄存器单元、中断寄存器单元。

PCI/X 接口单元分为PCI/X Master和PCI/X Target,VME总线接口分为VME Master,VME Slave和SCON单元。

Linkage Module为核心转换单元,负责两种总线操作的时序转换,实现PCI-VME和VME-PCI的互访转换;通过配置中断寄存器可以实现两种总线之间的中断映射。

图1 Tsi148内部组成框图2 VME与PCI总线互连Tsi148非常适合VME总线的主处理模块和智能处理模块。

一种VME总线智能处理模块主要组成框图见图2,系统主要由MPC8280处理器、存储器芯片、外围接口芯片、Tsi148、VME总线接口等其他电路和器件组成。

该智能模块可运行VxWorks操作系统,在VME系统中可以实现Master/Slave工作方式和SCON功能。

在智能模块上的MPC8280处理器片内集成了高效PCI Host接口,可以实现与Tsi148的无缝连接,同时通过模块本地PCI总线接口可以对Tsi148进行初始化配置,实现本地PCI地址空间与VME总线地址空间的映射。

2.1 PCI总线接口MPC8280的PCI接口支持PCI总线时钟最高为66 MHz,总线宽度为32位,Tsi148的PCI/X 接口时钟由MPC8280的PCLK提供,Tsi148工作模式由上电复位过程采集到的指定信号的电平状态决定,这些信号包括FRAME,IRDY,DEVSEL,STOP,TRDY,M66EN。

在该模块中,采用32 b/66 MHz PCI总线模式,没有用到高32位地址数据线。

为防止信号电平浮动造成漏电流过大引起的电平不稳,高32位地址数据线进行上拉,其他与64位操作相关的控制信号进行适当拉高或拉低处理,Tsi148的设备选择线IDSEL由PCI的地址数据线中的AD13实现。

图2 智能模块组成框图2.2 VME总线接口Tsi148的VME总线接口支持32/64位总线宽度,并且具有槽位自动识别功能,实现了VME64x规范中定义的CR/CSR功能,配合相应的软件工具可以实现通过VME总线进行模块配置和系统资源的初始化。

Tsi148中的CR/CSR的地址分配可设置为自动识别Auto ID和地理位置Geographical两种方法,通过设置数据线VD2,VD3的电平,在上电复位时即可决定ASIDEN,GSIDEN引脚的电平状态。

两种电平的组合方式如表1所示。

表1 CR/CSR分配机制ASIDEN[VD2]GSIDEN[VD3]描述00CR/CSR禁止01地理位置方式10Auto slot ID方式11如果GA[4:0]引脚为高,设为默认Auto slot ID2.3 地址空间转换智能模块中的PCI总线接口通过Tsi148的Outbound Windows实现VME总线空间的访问,最小地址空间为32 KB。

当该模块访问VME系统的某个地址空间时,它首先访问本地PCI地址空间。

当Tsi148的PCI Target单元收到访问命令后,加上预设的地址偏移量,通过PCI Target送给VME Master。

VME Master作为VME总线主控,发起地址空间访问,地址转换关系如图3所示。

图3 PCI/X到VME地址转换系统中其他主模块通过Tsi148的Inbound Windows访问智能模块的PCI空间。

主模块访问智能模块PCI总线的某个地址空间时,它首先访问VME地址空间。

当Tsi148的VME Slave单元收到访问命令后,加上预设的地址偏移量,通过VME Slave单元送给PCI Master,PCI Master作为本地PCI总线上的主控发起地址空间访问,VME总线地址宽度由主模块决定,地址转换如图4所示。

图4 VME到PCI/X地址转换两种总线之间是通过独立的读/写命令和数据缓冲器实现的,通过它可实现预取读和延时写功能。

除此之外,Tsi148还支持DMA数据传送,即支持直接模式DMA传输和链式DMA传输两种方式,可以实现数据量较大时的块传送,并且DMA控制器可实现VME-PCI,PCI-VME,PCI-PCI,VME-VME接口之间的数据传送。

3 Tsi148软件初始化智能模块在VME总线系统中需要进行资源配置对Tsi148初始化。

首先初始化Tsi148内部寄存器,初始化可由两种方式实现,一种是通过智能模块本地PCI总线接口操作进行;另一种是系统中主控板通过VME总线接口配置CR/CSR空间实现。

本文介绍通过本地PCI总线进行软件初始化的方法。

Tsi148内部的4 KB寄存器,分为PCFS,LCSR,GCSR,CSR。

其中,PCFS为256 B 的标准PCI头寄存器;LCSR 为本地控制与状态寄存器;GCSR 为全局控制与状态寄存器;CSR为VME总线控制与状态寄存器。

4 KB寄存器通过配置命令映射到智能模块上处理器内存地址空间,利用VxWorks环境下PCI读/写命令实现寄存器配置。

3.1 开放地址空间初始化之前,首先需要确定4 KB寄存器在系统中的内存空间,使能相应存储器读/写控制位MEMSP。

此时,可以通过存储器读/写的方式初始化Tsi148的内部寄存器。