计算机组成原理除法课程设计

计算机组成原理课程设计

计算机组成原理课程设计1. 引言计算机组成原理是计算机科学与技术专业中一门重要的基础课程。

通过学习计算机组成原理,可以了解计算机的基本组成结构、工作原理和性能提升方法。

为了更好地掌握和应用所学知识,本文将介绍一项针对计算机组成原理课程的设计任务。

2. 任务描述本次课程设计任务要求设计一个简单的单周期CPU,实现基本的指令执行功能。

具体要求如下:•CPU的指令集包括加载(Load)、存储(Store)和算术逻辑运算(ALU)指令,需要支持整数加法、减法、乘法和除法运算。

•CPU需要具备基本的流水线功能,包括取指(Instruction Fetch)、译码(Decode)、执行(Execute)和写回(Write Back)。

•CPU需要支持基本的寄存器操作,包括寄存器读取(Register Read)和寄存器写入(Register Write)。

•CPU的指令和数据存储器使用单端口RAM,指令和数据的访问都需要经过存储器。

3. 设计思路针对上述需求,我们可以采用以下设计思路:3.1 CPU总体设计•CPU采用单周期结构,即每个指令都在一个时钟周期内完成。

•CPU主要分为指令存储器、数据存储器、寄存器文件和控制逻辑四个部分。

3.2 指令存储器设计•指令存储器采用单端口RAM,每个指令的长度为固定的32位。

•指令存储器需要实现读取指令的功能,每次从内存中读取一个指令。

3.3 数据存储器设计•数据存储器也采用单端口RAM,每个数据的长度为固定的32位。

•数据存储器需要实现读取数据和写入数据的功能,执行指令时需要从存储器中读取数据,计算结果需要写回存储器。

3.4 寄存器文件设计•寄存器文件包含若干个通用寄存器,用于存储指令执行过程中的临时数据。

•寄存器文件需要实现读取寄存器和写入寄存器的功能,执行指令时需要读取和写入寄存器。

3.5 控制逻辑设计•控制逻辑负责根据当前指令的操作码和操作数生成控制信号,控制CPU的工作流程。

计算机组成原理课程设计

计算机组成原理课程设计

计算机组成原理课程设计是计算机科学与技术专业的一门核心课程,其目的是帮助学生更深入地理解计算机的组成原理和工作原理,培养学生分析和设计计算机硬件的能力。

在这个课程设计中,我选择了设计一个简单的单周期CPU。

首先,我会设计CPU的指令集,包括处理器指令的类型、指

令格式、寻址方式等。

然后,根据指令集的要求,设计并实现CPU的控制器,控制指令的执行流程。

接着,我会设计并实

现CPU的数据通路,包括寄存器、ALU、存储器等组件,实

现指令的操作。

在设计过程中,我会遵循计算机组成原理的基本原理和设计原则,如冯·诺伊曼体系结构、指令周期、数据通路和控制单元

的相互协调等。

我会使用硬件描述语言,如VHDL或Verilog,进行设计,通过仿真和验证来测试设计的正确性。

同时,我还会考虑CPU的性能和效率,尽量优化各个部分的设计,以提

高CPU的运行速度和处理能力。

在设计完成后,我还会进行性能测试和功能验证,测试CPU

在不同工作负载下的性能表现,并根据测试结果对设计进行优化。

最后,我会编写报告,详细介绍我的设计思路、实现过程和测试结果,以及可能存在的问题和改进的方向。

通过这个课程设计,我将深入理解计算机组成原理的相关知识,并掌握CPU设计的基本方法和技术。

这对于我今后的学习和

工作都具有重要意义,不仅可以加深我对计算机硬件的理解,

还可以提高我的问题分析和解决能力,为我未来的研究和工作奠定坚实的基础。

计算机组成原理除法课程设计

课程设计说明书题目: 设计指令系统院系:计算机科学与工程学院专业班级:计算机10-03班学号: 2010303089学生姓名:胡敬杰指导教师:刘向举2013年1 月10日安徽理工大学课程设计(论文)任务书计算机科学与工程学院监控与嵌入式技术系学号2010303089 学生姓名胡敬杰专业(班级)计算机10-3班设计题目设计指令系统设计技术参数1.本系统采用DJ-CPTH超强型计算机组成原理教学实验系统搭建电路图,在实验箱上实现指令系统。

2.利用软件工程中的可行性研究以及分析方法,进行系统分析。

设计要求1在基本模型机的基础上设计取数、存数、输入、输出、与、或、非、加法、减法、移位指令等,用这些指令的助记符不得与指导书上相同。

2.指令包括立即数寻址、寄存器直接寻址、存储器直接寻址三种寻址方式。

3.利用新构建的指令系统编程,分别实现求补、同或、异或、乘法、除法、两存储单元数据交换等功能。

工作量1.课程设计说明书2000字;2.画出流程图,编写微指令代码和程序。

工作计划1.首先认真研究老师所给的题目,了解题目要求做什么。

2.查阅资料,解决难题。

3.编写源程序并调试之。

4.写课程设计说明书参考资料[1] 蒋本珊.计算机组成原理(第2版).北京:清华大学出版社,2011[2] 白中英.计算机组成原理(第二版).北京:科学出版社,2008[3] DJ-CPTH超强型计算机组成原理与系统结构实验指导书[4] 沈美明.汇编语言程序设计北京:清华大学出版社指导教师签字教研室主任签字2012年 12月17日安徽理工大学课程设计(论文)成绩评定表指导教师评语:成绩:指导教师:年月日摘要本次计算机组成原理课程设计课题是基本模型机的设计与实现。

利用CPU与简单模型机来实现计算机组成原理课程设计,编写指令的应用程序,用微程序控制器实现一系列的指令功能,最终达到将理论与实践相联系。

本次设计完成了相关指令的格式以及编码的设计,实现了机器指令微代码,完成具有一定功能的程序。

计算机组成原理课程设计报告,乘法,除法,

成绩:课程设计报告课程名称:计算机组成原理课程设计实验项目:用微指令实现乘法和除法的程序姓名:专业:计算机科学与技术班级:计算机14-6班学号:计算机科学与技术学院实验教学中心2016年9 月1 日设计项目名称:用微指令实现乘法和除法的程序(2 学时)一.设计目的1、通过学习用微指令实现乘法和除法的程序,巩固课本知识,加深对所学知识的理解,综合理解计算机组成原理课程的核心知识并进一步建立整机系统的概念。

2、通过实际上机动手操作和亲自设计,锻炼自身的动手能力和实践能力,将课本的理论知识运用于实践,培养综合实践及独立分析、解决问题的能力,充分发挥理论联系实践的教学理念。

3、通过上机学习对微指令的设计,为以后走上工作岗位奠定一定的基础,同时也为以后学习其他相关的内容做铺垫。

4.在实验机上设计实现机器指令及对应的微指令(微程序)并验证,从而进一步掌握微程序设计控制器的基本方法并了解指令系统与硬件结构的对应关系。

二.设计内容针对COP2000实验仪,从详细了解该模型机的指令微指令系统入手,以实现乘法和除法运算功能为应用目标,在COP2000的集成开发环境下,设计全新的指令系统并编写对应的微程序,之后编写实现乘法和除法的程序进行设计的验证。

三.使用仪器cop2000计算机组成原理实验系统。

四.设计步骤1、理解试验系统自带的每一条微指令的含义和具体工作流程。

2、根据原有的微指令自己设计微指令。

3、微指令设计完成后调试所有的微指令确保没有错误。

4、用自己设计的微指令编写实现乘法和除法运算的程序。

5、编写程序完毕后调试并运行代码,观察是否能够满足需求。

五.微程序设计指令原理1.在微指令的控制字段中,每一位代表一个微命令,在设计微指令时,是否发出某个微命令,只要将控制字段中相应位置成"1"或"0",这样就可打开或关闭某个控制门。

2.详细了解并掌握COP 2000模型机的微程序控制器原理,通过综合实验来实现(1)该模型机指令系统的特点:①总体概述:COP2000模型机包括了一个标准CPU所具备所有部件,这些部件包括:运算器ALU、累加器A、工作寄存器W、左移门L、直通门D、右移门R、寄存器组R0-R3、程序计数器PC、地址寄存器MAR、堆栈寄存器ST、中断向量寄存器IA、输入端口IN、输出端口寄存器OUT、程序存储器EM、指令寄存器IR、微程序计数器uPC、微程序存储器uM,以及中断控制电路、跳转控制电路。

教案-计算机组成原理(DOC)

计算机组成原理教案(数字媒体专业)第一章计算机系统概论内容简介:计算机系统的层次结构,冯·诺伊曼计算机的硬件结构和主要功能,计算机的工作步骤以及计算机的主要技术指标。

教学目标:了解计算机系统的层次结构;了解冯·诺伊曼计算机的特点及硬件构成;理解计算机的工作步骤,了解计算机的主要技术指标的含义及其对计算机的影响。

教学重点和难点:虚拟机的概念;计算机的硬件构成;计算机的工作步骤。

教学媒体和教学方法:使用幻灯片在多媒体教室进行教学;教学中采用讲授与讨论相结合的方法。

教学过程:一、计算机系统简介1.计算机的软硬件概念(1)硬件(2)软件(3)软硬件的关系2.计算机系统的层次结构(1)虚拟机的概念(2)各层虚拟机及与真实机器的层次关系3.计算机的基本组成(1)冯·诺伊曼计算机的特点(2)计算机硬件结构,总线的构成。

讨论、分析直连结构的问题,提出总线思想,并简单介绍总线结构。

(3)计算机的工作步骤提出计算机解决问题的基本步骤计算机基本构成部件的介绍(运算器、存储器、控制器)以计算ax2+bx+c为例分析计算机工作的过程4.计算机的主要技术指标(1)机器字长计算机同时处理的二进制位机器字长与数据总线宽度、存储字长的关系(2)存储容量存储容量的单位主存容量辅存容量(3)运算速度几种计算运算速度的方法并对它们进行比较运算速度的表示单位第二章计算机的发展及应用内容简介:计算机的发展史;计算机的应用领域;计算机的发展展望。

教学目标:了解计算机的产生和发展以及发展思路;了解计算机的应用领域;了解计算机的发展趋势。

教学重点和难点:计算机的应用领域。

教学媒体和教学方法:使用幻灯片在多媒体教室进行教学;教学中采用讲授与讨论相结合的方法。

教学过程:一、计算机的发展史1.计算机的产生和发展现代计算机的研究工作第一台电子计算机的产生计算机的发展阶段计算机的发展规律计算机的发展趋势2.微型计算机的出现和发展微型计算机的发展阶段微型计算机的发展带来的工作、学习、生活方式的变化3.软件技术的兴起和发展软硬件的融合,简介嵌入式发展方向二、计算机的应用1.科学计算和数据处理通过ENIAC进行计算的一个案例,直观体会计算机的计算能力2.工业控制和实时控制3.网络技术应用4.虚拟现实介绍虚拟现实技术的一些应用5.办公自动化和管理信息系统6.多媒体技术7.人工智能三、计算机发展的展望第三章系统总线内容简介:总线的概念;总线的分类;总线的特性和性能指标;总线结构;总线控制。

计算机组成原理教案(第二章)

为便于软件移植,按照 IEEE754 标准,32位浮点数和 64位浮点数的标准格式为

浮点数 符号位

小数点 (隐含的)

阶符采用隐含方式,即采用移码方式来表示正负指数。

将浮点数的指数真值e 变成阶码E 时,应将指数 e 加上 一个固定的偏移值127(01111111),即 E=e+127.

不规格的例子:

2.1.5 校验码

最简单且应用广泛的检错码是采用一位校验位的奇校验或偶校验

设x=(x0x1…xn-1)是一个n位字,则奇校验位C定义为 C=x0⊕x1⊕…⊕xn-1

式中⊕代表按位加,表明只有当x中包含有奇数个1时,才使C=1, 即C=0。

同理,偶校验位C定义为

C=x0⊕x1⊕…⊕xn-1

即x中包含偶数个1时,才使C=0。

[例4]将十进制真值(-127,-1,0,+1,+127)列表表示成二进制数及原 码、反码、补码、移码值。

[例5]设机器字长16位,定点表示,尾数15位,数符1位,问: (1)定点原码整数表示时,最大正数是多少?最小负数是多少?

(2)定点原码小数表示时,最大正数是多少?最小负数是多少?;

(1)定点原码整数表示 最大正数值=(215-1)10=(+32767)10 0 111 111 111 111 111

0.1011

1.0101

10.0000 0.0000

对定点整数,补码表示的定义是 [x]补= {

x

2n>x≥0 (mod 2n+1)

2n+1+x=2n+1-|x| 0≥x≥-2n

3.反码表示法

我们比较定点小数反码与补码的公式 [x]反=(2-2-n)+x [x]补=2+x

[x]补=[x]反+2-n

计算机组成原理课程设计

计算机组成原理课程设计一、设计背景计算机组成原理是计算机科学与技术专业的一门基础课程,旨在培养学生对计算机硬件组成和工作原理的深刻理解。

通过课程设计,学生可以巩固和应用所学的知识,提高解决实际问题的能力。

二、设计目标本次计算机组成原理课程设计的目标是让学生通过实践,加深对计算机硬件组成和工作原理的理解,培养学生的设计和实现能力。

具体目标包括:1. 设计并实现一个简单的计算机系统,包括中央处理器(CPU)、存储器、输入输出设备等。

2. 熟悉计算机指令系统的设计与实现,包括指令的编码、解码和执行过程。

3. 学会使用硬件描述语言(如VHDL)进行计算机硬件的设计和仿真。

4. 掌握计算机系统的性能评估方法,包括指令周期、时钟频率等。

三、设计内容本次计算机组成原理课程设计的内容为设计并实现一个简单的基于冯·诺依曼结构的计算机系统。

具体设计内容包括以下几个方面:1. 计算机系统的总体设计根据冯·诺依曼结构的原理,设计计算机系统的总体框架。

包括中央处理器(CPU)、存储器、输入输出设备等。

2. 指令系统的设计与实现设计并实现一个简单的指令系统,包括指令的编码、解码和执行过程。

指令集可以包括算术运算、逻辑运算、数据传输等常见指令。

3. 中央处理器(CPU)的设计与实现设计并实现一个简单的中央处理器,包括指令寄存器、程序计数器、算术逻辑单元等。

通过对指令的解码和执行,实现计算机的基本功能。

4. 存储器的设计与实现设计并实现一个简单的存储器模块,包括指令存储器和数据存储器。

通过存储器的读写操作,实现程序的加载和数据的存储。

5. 输入输出设备的设计与实现设计并实现一个简单的输入输出设备,如键盘和显示器。

通过输入输出设备,实现用户与计算机系统的交互。

6. 系统性能评估对设计的计算机系统进行性能评估,包括指令周期、时钟频率等指标的测量和分析。

通过性能评估,优化计算机系统的性能。

四、设计步骤本次计算机组成原理课程设计的步骤如下:1. 确定设计的整体框架和目标,明确设计的内容和要求。

计算机组成原理课程设计课程设计

华东交大理工学院__2016-2017__学年第_一_学期课程设计安排计划班级:计算机科学与技术1-4班课程:计算机组成原理课程设计一、课程设计题目:1、16位全加器的设计2、补码乘法运算器设计3、具有先进进位功能的24位ALU电路设计二、设计内容及要求:选定三个题目之一作为设计目标。

了解计算机的硬件系统,了解一位全加器的组成原理,深入讨论计算机的组成原理,在熟悉常用的门电路的组成和工作过程的基础上,要求设计出一个16位全加器。

其中要求设计并写出产生求和结果的逻辑表达式,需要写出利用快速仅为链产生仅为的逻辑表达式,同时还要实现时需要用一个时钟信号控制运算的执行,如第一拍给出输入数据,第二拍给出运算控制信号,第三拍送输出数据,然后又回到第一拍,循环往复,知道运算全部结束。

根据要求设计出针对具体指令所对应的流程图;根据流程及门电路设计出相应的全加器。

编写出VHDL程序,在仿真软件上运行并检验所设计的微程序的正确性。

三、设计方法与步骤:(1)了解计算机的硬件基本组成。

(2)了解计算机中半加器的设计。

(3)熟悉74系列芯片的组成和工作过程。

(4)掌握全加器的组成、工作原理。

(5)掌握1位全加器的形成。

(6)掌握4位片SN74LS181的原理。

(7)掌握形成16位运算器数据通路结构。

(8)掌握快速进位链产生仅为的逻辑表达式。

(9)学会使用MAX-PLUS II软件设计电路原理图及功能模拟。

(Xilinx Foundation F3.1i)(10)熟悉常用的门电路,掌握快速进位链技术。

四、设计时间安排:第_16_周指导老师:王莉时间:联系电话:华东交通大学理工学院课程设计教学安排任课老师:王莉指导老师:王莉任课班级:15级计算机科学与技术课程名称:计算机组成原理课程设计次数年、月、日时间指导方式指导内容指导人数12345678。

计算机组成原理课程设计---简单计算机的设计

计算机组成原理课程设计(Ver 3.1)计算机科学与工程学院2007年7月1、课程设计目的 (3)2、仪器设备 (3)3、基于微控器的模型机设计部分 (3)3.1、设计步骤 (3)3.2、准备知识 (6)3.3、设计内容 (11)题目一:设计一个具有带进位加法和立即数寻址方式的模型机11题目二:设计一个具有带进位加法和条件跳转的模型机 (11)题目三:设计一个具有循环左移功能的模型机 (12)题目四:设计一个具有带借位减法和存储功能的模型机 (13)4、可编程逻辑器件设计部分 (14)4.1、设计步骤 (14)4.2、准备知识 (14)4.3、设计内容 (16)题目五:利用CPLD设计一个并行加法器 (16)题目六:阵列乘法器设计 (16)题目七:硬联控制器设计 (17)5、具有中断处理功能的模型机设计 (19)5.1、设计内容 (19)5.2、准备知识 (20)5.3、设计步骤 (23)6、课程设计任务及要求 (27)7、考核办法 (27)8、参考资料 (27)9、附录 (28)附录1(数据通路): (28)附录2(系统连线参考图) (29)附录3(实验系统主要单元电路) (30)附录4(ispDesignEXPERT软件使用) (35)VIII.把设计适配到Lattice器件中 (47)IX.层次化操作方法 (47)《计算机组成原理》课程设计1、课程设计目的通过对一个简单计算机的设计,对计算机的基本组成,部件的设计、部件间的连接、微程序控制器的设计、微指令和微程序的编制与调试等过程有更深的了解,在此基础上完成一台基本计算机的组成设计,从而加深对理论课程的理解,锻炼学生的独立思考和动手能力。

2、仪器设备硬件环境为PC-386以上微机,西安唐都科教仪器公司的TDN-CM+计算机组成原理实验台。

软件环境采用WINDOWS操作系统,西安唐都科教仪器公司的TDN-CM+计算机组成原理实验软件。

3、基于微控器的模型机设计部分3.1、设计步骤设计一台完整的计算机,大致需按如下的顺序来考虑:(1)确定设计目标确定所设计计算机的功能和用途。

《计算机组成原理》课程设计

课程设计说明书《计算机组成原理》算法实现(五)专业 计算机科学与技术学生夏晶晶 班级 M 计算机101 学号1051401122指导教师花小朋完成日期2013年6月21日目录1 课程设计目的 (2)2 课程设计容与要求 (2)2.1课程设计的容 (2)2.2 课程设计的要求 (2)3 实现方法 (2)3.1 系统目标 (2)3.2 主体设计 (4)3.2.1 主窗体的设计 (4)3.2.2 定点整数真值还原窗体的设计 (6)3.2.3 定点整数单符号位补码加减法 (9)3.2.4 定点整数的原码乘法 (11)3.2.5 浮点数的加减运算 (13)4 设计小结 (14)参考文献 (14)1 课程设计目的本课程设计是在学完本课程教学大纲规定的全部容、完成所有实践环节的基础上,旨在深化学生学习的计算机组成原理课程基本知识,进一步领会计算机组成原理的一些算法,并进行具体实现,提高分析问题、解决问题的综合应用能力。

2 课程设计容与要求2.1课程设计的容计算机组成原理算法实现(五)2.2 课程设计的要求能够实现机器数的真值还原(定点整数)、定点整数的单符号位补码加减运算、定点整数的原码乘法运算和浮点数的加减运算。

3 实现方法3.1 系统目标本程序含有以下几个功能模块,分别能够实现如设计容所设计的功能。

共有5个类,各类之间的关系如图3-1所示:系统流程图:3.2 主体设计3.2.1 主窗体的设计程序菜单需要在输入口令正确后方可使用,若口令输入错误需给出重新输入口令的提示,三次口令输入错误则禁止使用。

登陆算法的流程图:输入密码判断密码计数器减1激活菜单栏隐藏登陆显示欢迎界面弹出错误窗口判断计数器值是否大于零结束开始3.2.2 定点整数真值还原窗体的设计选择主窗体中“机器数的真值还原(定点整数)”时进入下图所示的窗体。

在上面的窗体中按“输入”按扭时,将输入焦点设置为最上面的一个文本框上。

输入一个机器数(如10001000)后,按“原->真值”、“反->真值”、“补->真值”或“移->真值”按扭中的任一个后,将在第二文本框中显示对应操作的结果。

计算机组成原理--除法器原理

计算机组成原理--除法器原理

除法器是计算机中的一种基本逻辑功能模块,用于实现除法运算。

除法器的实现原理与方法有很多种,以下是其中一种常见的实现原理:

1. 物理实现

除法器通常由大量的逻辑门电路组成,可以采用不同的实现方式,如串行除法器、并行除法器、移位除法器、余数-商除法器等。

其中,

移位除法器和余数-商除法器是最常用的两种。

2. 操作流程

以余数-商除法器为例,其操作流程如下:

(1)将除数和被除数输入除法器。

(2)将除法器初始化,即将商和余数的初始值设置为0。

(3)按照一定的算法,在每个时钟周期内进行一次除法运算。

(4)在计算过程中,如果余数小于除数,则商的相应位清零,

否则商的相应位为1,并将余数减去除数。

(5)在除法执行完毕后,商即为结果的整数部分,余数即为结

果的小数部分。

3. 特点

除法器的特点包括:

(1)实现较为复杂,需要大量的逻辑门电路,占用较多的芯片

面积和功耗。

(2)除法运算的速度相比加减乘运算较慢,需要多个时钟周期

才能计算完毕。

(3)除法器较为容易出错,需要考虑除法中各种特殊情况的处

理方法,如被除数为0、除数为0、商或余数超出范围等。

(4)除法器通常作为CPU中的一个模块存在,与其他逻辑电路

协同工作,在计算机系统中发挥重要作用。

计算机组成原理课程设计

计算机组成原理 课程设计一、课程目标知识目标:1. 让学生掌握计算机硬件的基本组成,包括CPU、内存、硬盘、输入输出设备等,并了解各部件的功能和工作原理。

2. 使学生了解并理解计算机的指令系统,包括指令的种类、格式和执行过程。

3. 帮助学生理解计算机的性能指标,如主频、缓存、运算速度等,并学会分析不同硬件配置对计算机性能的影响。

技能目标:1. 培养学生运用所学知识分析和解决实际问题的能力,例如根据需求选择合适的计算机硬件配置。

2. 提高学生的动手实践能力,通过组装和拆解计算机硬件,加深对计算机组成原理的理解。

3. 培养学生查阅资料、自主学习的能力,以便在课后拓展相关知识。

情感态度价值观目标:1. 培养学生对计算机科学的兴趣和热情,激发他们探索计算机技术发展的积极性。

2. 增强学生的团队合作意识,通过小组讨论和实践活动,学会与他人合作共同解决问题。

3. 引导学生关注计算机技术在生活中的应用,认识到科技对社会的推动作用,培养创新精神和责任感。

本课程针对高中年级学生,结合计算机组成原理的教学要求,将课程目标分解为具体的学习成果,以便进行后续的教学设计和评估。

课程性质为理论联系实践,注重培养学生的实际操作能力和创新思维。

在教学内容上,紧密联系课本知识,突出重点,使学生能够在实践中掌握计算机组成原理的相关知识。

二、教学内容1. 计算机硬件基本组成- 课本第二章:介绍CPU、内存、硬盘、输入输出设备等硬件的基本概念、功能及工作原理。

- 教学大纲:安排2课时,通过讲解、图示和实物展示,使学生了解各硬件部件的作用及相互关系。

2. 计算机指令系统- 课本第三章:讲解指令的种类、格式和执行过程,以及指令系统的发展。

- 教学大纲:安排2课时,通过实例分析、指令执行流程图解,帮助学生理解计算机指令系统的基本原理。

3. 计算机性能指标与硬件配置- 课本第四章:介绍计算机性能指标,分析不同硬件配置对计算机性能的影响。

- 教学大纲:安排2课时,结合实际案例,让学生学会分析硬件配置对计算机性能的影响,并能根据需求选择合适的硬件配置。

计算机组成原理课程设计

计算机组成原理课程设计计算机组成原理课程设计是一个重要的课程项目,旨在帮助学生深入理解计算机的基本组成和工作原理。

以下是一个可能的计算机组成原理课程设计的简要概述:1. 课程设计目标:- 理解计算机的基本组成和工作原理;- 掌握计算机的层次结构和指令执行过程;- 学习计算机的数据表示和存储方式;- 熟悉计算机的中央处理器和存储器的设计与实现;- 掌握计算机的输入输出系统和总线结构。

2. 课程设计内容:- 计算机层次结构和指令执行过程的介绍;- 数据表示和存储方式的学习;- 中央处理器和存储器的设计与实现;- 输入输出系统和总线结构的研究。

3. 课程设计步骤:- 第一阶段:理论学习和研究- 学习计算机组成原理的基本概念和理论知识;- 研究计算机的层次结构和指令执行过程;- 学习计算机的数据表示和存储方式;- 研究计算机的中央处理器和存储器的设计与实现;- 学习计算机的输入输出系统和总线结构。

- 第二阶段:实践设计和实现- 设计并实现一个简单的计算机系统,包括中央处理器、存储器、输入输出系统和总线结构;- 学习使用硬件描述语言(如Verilog或VHDL)进行计算机系统的设计和仿真;- 进行计算机系统的功能测试和性能评估;- 优化计算机系统的设计和实现。

- 第三阶段:课程设计报告和演示- 撰写课程设计报告,包括设计思路、实现过程和结果分析;- 准备课程设计演示,展示计算机系统的功能和性能;- 进行课程设计的答辩和评审。

4. 课程设计评估:- 课程设计报告的质量和完整性;- 计算机系统的功能和性能;- 课程设计演示的表现和效果;- 学生对计算机组成原理的理解和应用能力。

以上是一个可能的计算机组成原理课程设计的简要概述,具体的设计内容和步骤可以根据教学目标和学生能力进行调整和补充。

计算机组成原理课程设计

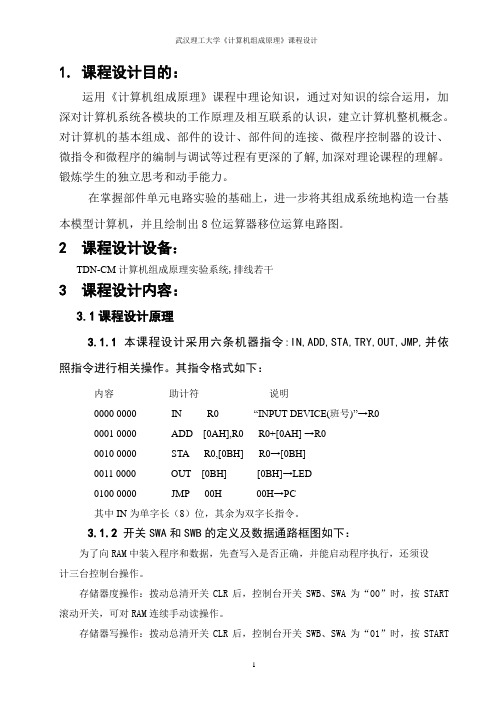

1. 课程设计目的:运用《计算机组成原理》课程中理论知识,通过对知识的综合运用,加深对计算机系统各模块的工作原理及相互联系的认识,建立计算机整机概念。

对计算机的基本组成、部件的设计、部件间的连接、微程序控制器的设计、微指令和微程序的编制与调试等过程有更深的了解,加深对理论课程的理解。

锻炼学生的独立思考和动手能力。

在掌握部件单元电路实验的基础上,进一步将其组成系统地构造一台基本模型计算机,并且绘制出8位运算器移位运算电路图。

2课程设计设备:TDN-CM计算机组成原理实验系统,排线若干3课程设计内容:3.1课程设计原理3.1.1本课程设计采用六条机器指令:IN,ADD,STA,TRY,OUT,JMP,并依照指令进行相关操作。

其指令格式如下:内容助计符说明0000 0000 IN R0 “INPUT DEVICE(班号)”→R00001 0000 ADD [0AH],R0 R0+[0AH] →R00010 0000 STA R0,[0BH] R0→[0BH]0011 0000 OUT [0BH] [0BH]→LED0100 0000 JMP 00H 00H→PC其中IN为单字长(8)位,其余为双字长指令。

3.1.2开关SWA和SWB的定义及数据通路框图如下:为了向RAM中装入程序和数据,先查写入是否正确,并能启动程序执行,还须设计三台控制台操作。

存储器度操作:拨动总清开关CLR后,控制台开关SWB、SWA为“00”时,按START 滚动开关,可对RAM连续手动读操作。

存储器写操作:拨动总清开关CLR后,控制台开关SWB、SWA为“01”时,按START滚动开关,可对RAM 连续手动写操作。

启动程序:拨动总清开关CLR 后,控制台开关SWB 、SWA 为“11”时,按START 滚动开关,即可转入到第01好“取址”微指令,启动程序运行。

上述三条控制台指令用到的两个开关SWB 、SWA 的状态设置,其定义如下:SWB SWA 控制台指令0 0 1 0 1 1 读内存(KRD ) 写内存(KWE ) 启动程序(RP )3.1.3设计用到的微指令的格式定义及微程序流程图如下:微指令格式定义3.1.4依照微程序流程图,生成如下指令代码表:微指令二进制代码表微地址S3S2S1S0M Cn W E A9A8 A B C μA5 ~μA0联机微地址微指令内容00Q 0 0 0 0 0 0 0 1 1 000 000 100 0 1 0 0 0 0 00H 018110H01Q 0 0 0 0 0 0 0 1 1 110 110 110 0 0 0 0 1 0 01H 01ED82H02Q 0 0 0 0 0 0 0 0 1 100 000 001 0 0 1 0 0 0 02H 00C048H03Q 0 0 0 0 0 0 0 0 1 110 000 000 0 0 0 1 0 0 03H 00E004H04Q 0 0 0 0 0 0 0 0 1 011 000 000 0 0 0 1 0 1 04H 00B005H05Q 0 0 0 0 0 0 0 1 1 010 001 000 0 0 0 1 1 0 05H 01A206H06Q 1 0 0 1 0 1 0 1 1 001 101 000 0 0 0 0 0 1 06H 959A01H07Q 0 0 0 0 0 0 0 0 1 110 000 000 0 0 1 1 0 1 07H 00E00DH10Q 0 0 0 0 0 0 0 0 0 001 000 000 0 0 0 0 0 1 08H 001001H11Q 0 0 0 0 0 0 0 1 1 110 110 110 0 0 0 0 1 1 09H 01ED83H12Q 0 0 0 0 0 0 0 1 1 110 110 110 0 0 0 1 1 1 0AH 01ED87H13Q 0 0 0 0 0 0 0 1 1 110 110 110 0 0 1 1 1 0 0BH 01ED8EH14Q 0 0 0 0 0 0 0 1 1 110 110 110 0 1 1 0 1 0 0CH 01ED9AH15Q 0 0 0 0 0 0 0 1 1 110 110 110 0 1 0 1 1 0 0DH 01ED96H16Q 0 0 0 0 0 0 0 0 1 110 000 000 0 0 1 1 1 1 0EH 00E00FH17Q 0 0 0 0 0 0 0 0 1 010 000 000 0 1 0 1 0 1 0FH 00A015H20Q 0 0 0 0 0 0 0 1 1 110 110 110 0 1 0 0 1 0 10H 01ED92H21Q 0 0 0 0 0 0 0 1 1 110 110 110 0 1 0 1 0 0 11H 01ED94H22Q 0 0 0 0 0 0 0 0 1 010 000 100 0 1 0 1 1 1 12H 00A117H23Q 0 0 0 0 0 0 0 1 1 000 000 000 0 0 0 0 0 1 13H 018001H24Q 0 0 0 0 0 0 0 0 0 010 000 000 0 1 1 0 0 0 14H 002018H25Q 0 0 0 0 0 1 1 1 0 000 101 000 0 0 0 0 0 1 15H 070A01H26Q 0 0 0 0 0 0 0 0 1 101 000 110 0 0 0 0 0 1 16H 00D181H27Q 0 0 0 0 0 1 1 1 0 000 101 000 0 1 0 0 0 0 17H 070A10H30Q 0 0 0 0 0 1 1 0 1 000 101 100 0 1 0 0 0 1 18H 068B11H31Q 0 0 0 0 0 0 0 0 0 000 000 000 0 0 0 0 0 0 19H 000000H32Q 0 0 0 0 0 0 0 0 1 110 000 000 0 1 1 0 1 1 1AH 00E01BH33Q 0 0 0 0 0 0 0 0 1 011 000 000 0 1 1 1 0 0 1BH 00B01CH34Q 0 0 0 0 0 0 0 1 1 010 001 000 0 1 1 1 0 1 1CH 01A21DH35Q 0 0 0 0 1 1 0 1 1 001 101 000 0 0 0 0 0 1 1DH 9D9A05H36Q 0 0 0 0 0 0 1 0 1 000 001 000 0 0 0 0 0 1 1EH 028201H3.1.5机器指令程序设计:机器指令程序序列地址内容助计符说明0000 0000 0000 0100 IN R0 “INPUT DEVICE(班号3)”→R0 0000 0001 0001 0000 ADD [0AH],R0 R0+[0AH] →R00000 0010 0000 10100000 0011 0010 0000 STA R0,[0BH] R0→[0BH]0000 0100 0000 10110000 0101 0011 0000 OUT [0BH] [0BH] →LED 0000 0110 0000 10110000 0111 0100 0000 JMP 00H 00H→ PC0000 1000 0000 00000000 10010000 1010 0010 0110 学号(20号同学) 0000 1011 求和结果(班号加学号) 3.2 实验步骤:3.2.1画出实验接线图如下:3.2.2 模型机实验预备操作步骤:3.2.2.1 按下图接线:按微程序控制器实验的步骤输入并检验上面的微指令代码表①将编程开关置为PROM(编程)状态。

计算机组成原理课程设计指导书1

《计算机组成原理》课程设计指导书一、课程设计目的通过该课程设计的学习,总结计算机组成原理课程的学习内容,利用TDN-CM++教学实验系统提供的软硬件操作平台掌握层次化设计方法、运用计算机原理知识,设计并实现一台完整的计算机,从而巩固课堂知识、深化学习内容、完成教学大纲要求,学好计算机科学与技术专业的专业基础课。

二、课程设计内容与要求要求每个学生(或小组)独立完成设计任务,在设计方案中可直接利用TDN-CM++ 教学实验系统提供的单元电路,如:运算器、数据通路、存储器、控制器、信号及时序控制、内总线、外总线、外围接口、输入/输出设备及大规模可编程逻辑器件等。

要充分利用所学知识设计出具有一定特色的模型计算机。

课程设计的时间为1周。

设计的最终作品包括硬件和软件两个部分,要求能够演示并达到设计指标的要求。

每个学生(或小组)在作品完成后,要经指导教师检查,同意拆除后方可拆卸,并分类放回元器件盒内。

课程设计报告每个学生一份,由课代表收齐后统一交给指导教师。

课程设计成绩评定由3部分组成:作品+出勤等40%;答辩30%;设计报告30%。

三、课程设计步骤设计一台完整的计算机,其设计过程可以归纳为以下七个步骤:.1、确定设计目标确定所设计计算机的功能和用途。

2、确定指令系统确定数据的表示格式、位数、指令的编码、类型、需要设计哪些指令及使用的寻址方式。

3、总体结构与数据通路总体结构设计包括确定各部件设置以及它们之间的数据通路结构。

在此基础上,就可以拟出各种信息传输路径,以及实现这些传输所需要的微命令。

对于部件设置时要确定运算器部件采用什么结构,控制器是微程序控制还是硬联控制等。

综合考虑计算机的速率、性能价格比、可靠性等要求,设计合理的数据通路结构,确定采用何种方案的内总线及外总线。

数据通路不同,执行指令所需要的操作就不同,计算机的结构也就不一样。

4、设计指令执行流程数据通路确定后,就可以设计指令系统中每条指令所需要的机器周期数。

计算机组成原理--除法器原理及c代码

计算机组成原理--除法器原理及c代码除法器是计算机中的一种重要的算术逻辑单元,用于实现除法运算。

除法器的设计是计算机组成原理中的重要内容之一,本文将从除法器的原理和相关的C代码实现两个方面进行介绍。

一、除法器原理除法器的原理主要包括除法算法和硬件实现两个方面。

1.除法算法在计算机中,除法可以采用多种算法实现,其中最常用的算法是连续除法和恢复余数法。

连续除法是将除数逐位地与被除数相减,判断余数的大小来进行下一步的操作。

具体操作如下:1)将被除数置于一边,余数和商置于另一边;2)被除数减去除数,得到当前位上的余数;3)余数进行左移,并加上下一位的被除数;4)重复上述操作直到计算完所有位。

恢复余数法是将除法过程中的余数加上除数,然后与被除数进行比较,得到商和下一位的余数。

具体操作如下:1)将被除数放在寄存器的高位,余数和商放在低位;2)将寄存器与除数进行比较,若寄存器大于等于除数,说明商的该位为1,余数等于当前寄存器减去除数;3)将寄存器进行左移,并加上下一位的被除数;4)重复上述操作直到计算完所有位。

2.硬件实现硬件实现除法器可以采用著名的Restoring、Non-Restoring和SRT 等算法。

其中Restoring算法是最常用的硬件实现方式。

Restoring算法中,通过比较、左移、减法等操作进行计算。

具体操作如下:1)将除数和被除数放入寄存器的高位和低位,商和余数置零;2)将寄存器与除数进行比较,若寄存器大于等于除数,说明商的该位为1,余数等于当前寄存器减去除数;3)将寄存器逻辑左移一位;4)循环执行2-3步,直到计算完所有位。

二、C代码实现以下是C语言中使用Restoring算法实现的除法器代码:```c#include <stdio.h>unsigned int divide(unsigned int dividend, unsigned int divisor)unsigned int quotient = 0;unsigned int remainder = 0;//32位无符号整数除法for (int i = 31; i >= 0; i--)remainder = (remainder << 1) , ((dividend >> i) & 1); // 将被除数逻辑左移一位,并加上下一位的被除数if (remainder >= divisor) // 判断余数是否大于等于除数remainder -= divisor; // 余数减去除数quotient ,= (1u << i); // 商的该位为1}}return quotient;int mainunsigned int dividend = 53;unsigned int divisor = 5;unsigned int result = divide(dividend, divisor);printf("%u / %u = %u\n", dividend, divisor, result);return 0;```以上的代码实现了一个32位无符号整数的除法操作,通过Restoring算法将除法运算转化为逐位比较、逻辑左移和减法等操作,最终得到商。

计算机组成原理课设 定点原码一位除法器的设计

沈阳航空航天大学课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:定点原码一位除法器的设计院(系):计算机学院专业:计算机科学与技术班级:94010101学号:2009040101013姓名:胡桂林指导教师:周大海完成日期:2012年1月13日沈阳航空航天大学课程设计报告目录第1章总体设计方案 (1)1.1设计环境 (1)1.2设计原理 (2)第2章详细设计方案 (4)2.1总流程图 (4)2.2上商置0模块流程图 (6)2.3上商置1模块流程图 (6)2.4商的符号流程图 (7)第3章测试结果 (9)3.1程序仿真 (9)3.2仿真测试一 (9)3.3仿真测试二 (10)附录 (11)参考文献 (14)第1章总体设计方案1.1 设计环境伟福COP2000实验箱,用汇编语言编程实现定点原码一位除法器COP2000 计算机组成原理实验系统由实验平台、开关电源、软件三大部分组成。

实验平台上有寄存器组R0-R3、运算单元、累加器A、暂存器W、直通/左移/右移单元、地址寄存器、程序计数器、堆栈、中断源、输入/输出单元、存储器单元、微地址寄存器、指令寄存器、微程序控制器、组合逻辑控制器、扩展座、总线插孔区、微动开关/指示灯、逻辑笔、脉冲源、20 个按键、字符式LCD、RS232 口。

COP2000集成调试软件(即仿真测试软件)共分为6部分:(1)主菜单区实现实验仪的各项功能的菜单,包括[文件][编辑][汇编][运行][帮助]五大项,各项线面做详细介绍。

(2)快捷图标区快速实现各项功能按键(3)源程序/机器码区在此区域有源程序窗口,反汇编窗口,EM程序代码窗口。

源程序用于输入,显示,编辑汇编源程序:反汇编窗口显示程序编译后的机器码及反汇编的程序;EM程序代码窗口用数据方式机器码。

(4)机构图/逻辑波形区结构图能结构化显示模型机的各部件,以及运行时数据走向寄存器值;逻辑波形图能显示模型机运行时所有信号的程序。

阵列除法器设计

课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:阵列除法器的设计院(系):计算机学院专业:计算机科学与技术班级:24010105学号:2012040101222姓名:孙洪宇指导教师:訾学博完成日期:2015年1月16日沈阳航空航天大学课程设计报告目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (3)1.3设计环境 (3)第2章详细设计方案 (5)2.1顶层方案图的设计与实现 (5)2.1.1顶层方案的设整体逻辑图 (5)2.1.2器件的选择与引脚锁定 (5)2.1.3编译、综合、适配 (7)2.2功能模块的设计与实现 (7)2.2.1细胞模块的设计与实现 (7)2.2.2除法器模块的设计与实现 (9)2.3仿真调试 (11)第3章编程下载与硬件测试 (13)3.1编程下载 (13)3.2硬件测试及结果分析 (13)参考文献 (15)附录(电路原理图) (16)第1章总体设计方案1.1 设计原理在原码除法中,原码除法符号位是单独处理的,商符由两数符号位进行异或运算求得,商值由两数绝对值相除求得。

原码除法中由于对余数的处理不同,又可分为恢复余数法和不恢复余数法(加减交替法)。

本设计采用加减交替法。

加减交替法的运算规则如下:(1)当余数为正时,上商1,余数左移一位后减去除数得下一位余数。

(2)当余数为负时,上商0,余数左移一位后加上除数得下一位余数。

阵列除法器是一种并行运算部件,采用大规模集成电路制造,与早期的串行除法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运算速度。

阵列除法器有多种形式,如不恢复余数阵列除法器、补码阵列除法器等等。

本实验设计的是加减交替阵列除法器。

本实验利用的细胞单元是一个可控加法/减法CAS单元,利用它组成的流水阵列来实现四位小数的除法。

CAS单元有四个输入端、四个输出端。

其中有一个控制输入端P,当P=0时,CAS作加法运算;当P=1时,CAS作减法运算。

现代计算机组成原理——除法器设计

数字系统组成原理和设计技术实验:除法器学号 1115108052姓名詹炳鑫班级电子2班华侨大学电子工程系一.程序LIBRARY IEEE;USE IEEE.std_logic_1164.ALL;USE IEEE.std_logic_unsigned.ALL;ENTITY devide ISPORT(reset, clock, start : IN STD_LOGIC;x : IN STD_LOGIC_VECTOR( 4 DOWNTO 0 );y : IN STD_LOGIC_VECTOR( 8 DOWNTO 0 ); done, overflow : OUT STD_LOGIC;q, r : OUT STD_LOGIC_VECTOR( 4 DOWNTO 0 ) );END devide;ARCHITECTURE behav OF devide ISSIGNAL rx : STD_LOGIC_VECTOR( 5 DOWNTO 0 ); SIGNAL ry : STD_LOGIC_VECTOR( 5 DOWNTO 0 ); SIGNAL rq : STD_LOGIC_VECTOR( 4 DOWNTO 0 );SIGNAL rmd : STD_LOGIC_VECTOR( 5 DOWNTO 0 ); SIGNAL flag_subadd : bit;SIGNAL state : integer RANGE 0 TO 6;BEGINPROCESS ( reset, clock )V ARIABLE sq : STD_LOGIC;BEGINIF reset = '0' THENrx <= ( OTHERS => '0' );ry <= ( OTHERS => '0' );rq <= ( OTHERS => '0' );state <= 0;ELSIF clock'event AND clock = '1' THENCASE STATE ISWHEN 0 =>rx( 5 DOWNTO 0 ) <= x(4) & x( 4 DOWNTO 0 ) ;ry( 5 DOWNTO 0 ) <= y(8) & y( 8 DOWNTO 4 ) ;rq( 4 DOWNTO 0 ) <= y( 3 DOWNTO 0 ) & '0';flag_subadd <= '1';done <= '0';overflow <= '0';IF start = '1' THENstate <= 1;END IF;WHEN 1 =>IF rmd(5) = '0' THENoverflow <= '1';state <= 0;done <= '1';ELSEstate <= state + 1;sq := '0';ry( 5 DOWNTO 0 ) <= rmd( 4 DOWNTO 0 ) & rq(4); rq( 4 DOWNTO 0 ) <= rq( 3 DOWNTO 0 ) & sq; flag_subadd <= '0';END IF;WHEN 5 =>IF rmd(5) = '0' THENsq := '1';flag_subadd <= '1';ELSEsq := '0';flag_subadd <= '0';END IF;ry( 5 DOWNTO 0 ) <= rmd( 4 DOWNTO 0 ) & rq(4); ry( 5 DOWNTO 0 ) <= rmd( 5 DOWNTO 0 );rq( 4 DOWNTO 0 ) <= rq( 3 DOWNTO 0 ) & sq; state <= state + 1;WHEN 6 =>IF rq(0) = '0' THENry <= rmd( 5 DOWNTO 0 );r <= rmd( 4 DOWNTO 0 );ELSEr <= ry( 4 DOWNTO 0);END IF;state <= 0;q <= rq;done <= '1' ;WHEN OTHERS =>IF rmd(5) = '0' THENsq := '1';flag_subadd <= '1';ELSEsq := '0';flag_subadd <= '0';END IF;ry( 5 DOWNTO 0 ) <= rmd( 4 DOWNTO 0 ) & rq(4);rq( 4 DOWNTO 0 ) <= rq( 3 DOWNTO 0 ) & sq;state <= state + 1;END CASE;END IF;END PROCESS;rmd <= ry + rx WHEN flag_subadd = '0' ELSEry + NOT rx + 1;END behav;-- Copyright (C) 1991-2011 Altera Corporation-- Your use of Altera Corporation's design tools, logic functions-- and other software and tools, and its AMPP partner logic-- functions, and any output files from any of the foregoing-- (including device programming or simulation files), and any-- associated documentation or information are expressly subject-- to the terms and conditions of the Altera Program License-- Subscription Agreement, Altera MegaCore Function License-- Agreement, or other applicable license agreement, including,-- without limitation, that your use is for the sole purpose of-- programming logic devices manufactured by Altera and sold by-- Altera or its authorized distributors. Please refer to the-- applicable agreement for further details.-- *************************************************************************** -- This file contains a Vhdl test bench template that is freely editable to-- suit user's needs .Comments are provided in each section to help the user-- fill out necessary details.-- *************************************************************************** -- Generated on "03/04/2014 15:45:59"-- Vhdl Test Bench template for design : devide---- Simulation tool : ModelSim-Altera (VHDL)--LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY devide_tb ISEND devide_tb;ARCHITECTURE devide_arch OF devide_tb IS-- constants-- signalsSIGNAL clock : STD_LOGIC:='0';SIGNAL done : STD_LOGIC:='0';SIGNAL overflow : STD_LOGIC:='0';SIGNAL q : STD_LOGIC_VECTOR(4 DOWNTO 0):="00000"; SIGNAL r : STD_LOGIC_VECTOR(4 DOWNTO 0):="00000"; SIGNAL reset : STD_LOGIC:='0';SIGNAL start : STD_LOGIC:='0';SIGNAL x : STD_LOGIC_VECTOR(4 DOWNTO 0); SIGNAL y : STD_LOGIC_VECTOR(8 DOWNTO 0); CONSTANT CLK_P : TIME :=10 ns;COMPONENT devidePORT (clock : IN STD_LOGIC;done : OUT STD_LOGIC;overflow : OUT STD_LOGIC;q : OUT STD_LOGIC_VECTOR(4 DOWNTO 0);r : OUT STD_LOGIC_VECTOR(4 DOWNTO 0);reset : IN STD_LOGIC;start : IN STD_LOGIC;x : IN STD_LOGIC_VECTOR(4 DOWNTO 0);y : IN STD_LOGIC_VECTOR(8 DOWNTO 0));END COMPONENT;BEGINi1 : devidePORT MAP (-- list connections between master ports and signalsclock => clock,done => done,overflow => overflow,q => q,r => r,reset => reset,start => start,x => x,y => y);PROCESSBEGINCLOCK<='0';W AIT FOR CLK_P;CLOCK<='1';W AIT FOR CLK_P;END PROCESS;reset <= '0','1' AFTER 10 ns;start <='0','1' AFTER 25 ns;x<="00000","01011"AFTER 60 ns,"00010"AFTER 120 ns;y<="000000000","010010000"AFTER 60 ns,"000001101"AFTER 120 ns; END devide_arch;二.仿真图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计说明书题目: 设计指令系统院系:计算机科学与工程学院专业班级:计算机10-03班学号:2010303089学生姓名:胡敬杰指导教师:刘向举2013年1 月10日安徽理工大学课程设计(论文)任务书计算机科学与工程学院监控与嵌入式技术系2012年12月17日安徽理工大学课程设计(论文)成绩评定表摘要本次计算机组成原理课程设计课题是基本模型机的设计与实现。

利用CPU与简单模型机来实现计算机组成原理课程设计,编写指令的应用程序,用微程序控制器实现一系列的指令功能,最终达到将理论与实践相联系。

本次设计完成了相关指令的格式以及编码的设计,实现了机器指令微代码,完成具有一定功能的程序。

在基本模型机的基础上构建一组能实现输入、输出、加、减、逻辑与、逻辑或、逻辑非、转移指令等8个功能的指令,这些指令的助记符不得与指导书上相同。

指令包括立即数寻址、寄存器直接寻址、存储器直接寻址三种寻址方式。

利用新构建的指令系统编程,实现交换两存储单元数据的功能。

关键字:指令系统,寻址方式,算术逻辑目录摘要 (1)目录 (2)1系统分析 (3)1.1 设计背景 (3)1.2 设计目标 (5)2系统设计 (6)2.1 模型机的指令系统设计 (6)2.2 模型机的微指令设计 (7)2.3实现除法功能的程序设计 (10)3系统实现 (13)4总结 (16)5参考文献 (17)1系统分析1.1 设计背景一台计算机所能执行的各种指令集合称为指令系统或指令集。

一台特定的计算机只能执行自己指令系统中的指令。

因此,指令系统就是计算机的机器语言。

指令系统表征着计算机的基本功能和使用属性,它是计算机系统设计中的核心问题。

指令系统的设计主要括指令功能、操作类型的设计,寻址方式和指令格式的设计。

计算机的性能与它所设置的指令系统有很大的关系,指令系统反映了计算机的主要属性,而指令系统的设置又与机器的硬件结构密切相关。

指令是计算机执行某种操作的命令,而指令系统是一台计算机中所有机器指令的集合。

通常性能较好的计算机都设置有功能齐全、通用性强、指令丰富的指令系统,而指令功能的实现需要复杂的硬件结构来支持。

本课程设计的模型机的指令码为8位,根据指令类型的不同,可以有0到2个操作数,指令码的最低两位用来选择R0-R3寄存器。

在微程序控制方式下,用指令码作为微地址来寻址微程序存储器,找到执行该指令的微程序。

在本模型机中,一条指令最多分为四个状态周期,一个状态周期为一个时钟脉冲,每个状态周期产生不同的控制逻辑,实现模型机的各种功能。

模型机有24位控制位以控制寄存器的输入输出,选择运算器的运算功能,存储器的读写。

简言之,这次设计,计算机数据通路的控制将由微程序控制器来完成,CPU从内存中取出一条机器指令到指令执行结束的一个指令周期,全部由微指令组成的序列来完成,即一条机器指令对应一条微程序,一条微程序又有若干微指令组成,一条微指令的功能由24位操作信号(即控制位)实现。

本设计是在DJ-CPT816计算机组成原理实验仪和仿真软件上进行的24位控制位分别介绍如下:XRD:外部设备读信号,当给出个外设的地址后,输出此信号,从指定外设读数据。

EMWR:程序存储器EM写信号EMRD:程序存储器EM读信号PCOE:将程序计数器PC的值送到地址总线ABUS上EMEN:将程序存储器EM与数据总线DBUS接通,有EMWR和EMRD决定是将DBUS 数据写入EM中,还是从EM读出数据到DBUSIREN:将程序存储器EM独处的数据打入指令寄存器IR和微指令计数器uPC EINT:中断返回时清除中断响应和中断请求标志,便于下次中断。

ELP:PC打入允许,与指令寄存器的IR2.,IR3位结合,控制程序跳转。

MAREN:将数据总线DBUS上数据打入地址寄存器MARMAROE:将地址寄存器MAR的值送到地址总线ABUS上OUTEN:将数据总线DBUS上数据送到输出端口寄存器OUT里STEN:将数据总线DBUS上数据存到堆栈寄存器里RRD:读寄存器组R0-R3,寄存器R?的选择由指令的最低两位决定RWR:写寄存器组R0-R3,寄存器R?的选择由指令的最低两位决定CN:决定运算器是否带进位移位,CN=1带进位,CN=0不带进位FEN:将标志位存入ALU内部的标志寄存器X2,X1,X0三位组合来译码选择将数据送到DBUS上的哪个寄存器,见表1 WEN:将数据总线DBUS的值打入工作寄存器W中AEN:将数据总线DBUS的值打入累加器A中S2,S1,S0三位组合决定ALU做何种运算,见表21.2 设计目标本课程设计要求实现机器指令:MOV(传送)、OUTE(输出)、AND(逻辑与)、ORE(逻辑或)、ADDE(不带进位算术加)、ADDCE(带进位算术加)、SUBE(不带进位算术减)、JCE、JZE、JMPE(转移指令)。

并且要包括立即数寻址,寄存器直接寻址,存储器直接寻址三种寻址方式。

最后要在设计的指令系统基础上,编写程序实现除法功能。

2系统设计2.1模型机的指令系统设计根据设计要求,设计出的指令要包括传送、逻辑与、逻辑或、算术加、减运算、输入、输出、转移这八种指令,且要运用立即数寻址、寄存器直接寻址、存储器直接寻址三种寻址方式。

由此设计出新的指令系统,如下截图图2.1新的指令系统2.2模型机的微指令设计(1)微指令的24位控制位如下:(2)设计出的微指令集如下表:助记符状态微地址微程序数据输出数据打入地址输出运算器uPC PC_FETCH_T000CBFFFF指令寄存器IR PC输出A输出写入101FFFFFF A输出102FFFFFF A输出103FFFFFF A输出1ADD A,#*T204C7FFEF存储器值EM寄存器W A输出11T105FFFE90ALU直通寄存器A,标志位C,ZPC输出加运算1T006CBFFFF指令寄存器IR PC输出A输出写入107FFFFFF A输出1SUB A,#*T208C7FFEF存储器值寄存器W PC输A输112.3实现除法功能的程序设计程序设计思路:先将两个立即数存入寄存器r0(被除数)和r1(除数),然后判断除数是否为零,是则输出结果为0,结束程序,否则继续第二步,将除数右移一位,再检查除数是否为零,是则输出结果r0中的数结束,否则进入第三步,将除数右移然后将被除数右移,检查被除数是否为零,是则输出0结束,否则调到第三步继续运行。

源程序截图如下:3系统实现1.按照系统分析中得到的指令集,在DJ-CPT816实验软件中新建指令系统,生成.mac 文件和.mic文件。

2.在DJ-CPT816实验软件中新建.asm文件,输入程序:MOV A,#00HMOV R0,#11HMOV R1,#07HAND R1,#01HJZ S1ADD A,#01S1:AND R1,0FHJZ S2RR R1AND R1,0FHJZ S3S5:RR R1RR R0AND R0,0FHJZ S2AND R1,0FHJZ S4JMP S5S2:MOV A,#00HJMP ES3:MOV A,R0JMP ES4:AND A,0FHJZ S6MOV A,R0SUB A,#01JMP ES6:MOV A,R0E:OUT AEND3.将程序另存为.asm文件,再汇编成机器码,调试窗口会显示出程序、机器码、反汇编指令,如图3.1图3.1程序、机器码、反汇编指令4.实验结果:使用DJ-CPTH运行此程序后得出了正确的结果,故实现了设计要求。

4总结通过本次课程设计,我巩固了所学的《计算机组成原理》中有关指令系统、总线系统等方面的知识,进一步加深了对计算机组成原理实验仪的使用方法的了解,能够更加熟练的使用计算机组成原理实验仪,同时还让我复习并运用了算法设计与分析和汇编语言的内容,此次课程设计进一步巩固和提高了自己的基础知识。

通过这次课程设计,既锻炼了我的动手能力,又锻炼了我的动脑能力,使我理论联系实际,使所学的知识不再枯燥无味,将所学的知识运用到实际,让我掌握这些知识更牢固。

在查找资料的同时也锻炼了自己的自学能力,还提高了获取有用信息的能力。

同时课程设计过程中与组内成员的积极合作培养了自己的团队意识,让自己再一次认识到了团队合作的重要性。

此次做课程设计也为自己积累了必要的经验,做课程设计或者以后做项目一定在最开始有个大体的设计思路,按照设计思路一步步的做,没有设计思路盲目做的话,会导致设计混乱,浪费大量时间。

而且在做课程设计的过程中需要查阅大量资料,积极与组员合作,选择方法时要严谨,如果遇到错误要尽快寻求到解决的办法,以防止影响以后的设计。

本次课程设计对我来说是一次很好的实践机会,锻炼了自己的动手能力,让我能够过活学活用知识,在实践中加深对所学课程的理解,让我充分认识到了理论与实践的重要性。

在以后的学习与生活中,要不断的把课本所学的知识与生活实际相结合,让自己知道自己所学知识的用处以及发现有待加强和学习的地方。

总之,此次课程设计,自己获益匪浅。

-------------精选文档-----------------5参考文献1. 白中英.《计算机组成原理(第二版)》.北京:科学出版社,19982. 平玲娣,潘雪增.《计算机组成与设计》浙江大学出版社,出版日期:20043. 裘雪红,李博成,车向全等.《计算机组成与系统结构》.北京:高等教育出版社,20094.《DJ-CPTH超强型计算机组成原理与系统结构实验指导书》可编辑。