STM32L4复位和时钟控制(RCC)介绍

STM32系统时钟RCC(基于HAL库)

STM32系统时钟RCC(基于HAL库)基础认识为什么要有时钟:时钟就是单⽚机的⼼脏,其每跳动⼀次,整个单⽚机的电路就会同步动作⼀次。

时钟的速率决定了两次动作的间隔时间。

速率越快,单⽚机在单位时间内所执⾏的动作将越多。

时钟是单⽚机运⾏的基础,时钟信号推动单⽚机内各个部分执⾏相应的指令。

时钟系统就是CPU的脉搏,决定cpu速率。

为什么这么多个时钟源:STM32系统是复杂的,⾼精度、低精度、⾼速、低速等,且可以对每个时钟源进⾏开关操作,可以把不需要使⽤的关闭掉。

这可以让单⽚机适⽤更多的环境中,把选择权利交个了开发者,开发者可以从精度、功耗、资源等多⽅⾯考虑。

STM32时钟:从时钟源的⾓度可分为:l 外部时钟(E)l 内部时钟(I)从时钟速率的⾓度分为:l ⾼速时钟(HS)l 低速时钟(LS)STM32在芯⽚复位后默认选⽤的是内部的⾼速时钟(HSI)进⾏⼯作,如果需要使⽤外部⾼速时钟(HSE)的话需要经过软件操作相关的寄存器配置。

外部时钟模式外部的⾼速和低速时钟均有这三个可选项⽬,图中是CubeMX提供的外部时钟选择:可选类型为l Disable(关闭,不使⽤外部时钟)l BYPASS Clock Source(旁路时钟源)l Crystal/Ceramic Resonator(外部晶体/陶瓷谐振器)外部晶体/陶瓷谐振器模式该模式较为常见,这可以为系统时钟提供较为精确的时钟源。

该时钟源是由外部⽆源晶体与MCU内部时钟驱动电路共同配合形成,有⼀定的启动时间,精度较⾼。

为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容必须尽可能地靠近振荡器引脚。

负载电容值必须根据所选择的晶体来具体调整。

整体上讲,陶瓷晶体和⽯英晶体的主要区别就在于精度和温度稳定性上。

⽯英晶体⽐陶瓷晶体精度要⾼,温度稳定性要好。

旁路时钟源模式该模式下必须提供外部时钟。

外部时钟信号(50%占空⽐的⽅波、正弦波或三⾓波)必须连到SOC_IN引脚,此时OSC_OUT引脚对外呈⾼阻态。

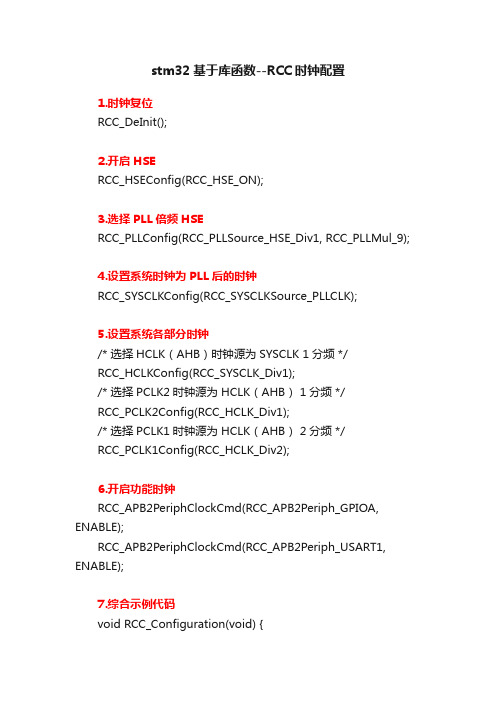

stm32基于库函数--RCC时钟配置

stm32基于库函数--RCC时钟配置1.时钟复位RCC_DeInit();2.开启HSERCC_HSEConfig(RCC_HSE_ON);3.选择PLL倍频HSERCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);4.设置系统时钟为PLL后的时钟RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);5.设置系统各部分时钟/* 选择HCLK(AHB)时钟源为SYSCLK 1分频 */RCC_HCLKConfig(RCC_SYSCLK_Div1);/* 选择PCLK2时钟源为 HCLK(AHB) 1分频 */RCC_PCLK2Config(RCC_HCLK_Div1);/* 选择PCLK1时钟源为 HCLK(AHB) 2分频 */RCC_PCLK1Config(RCC_HCLK_Div2);6.开启功能时钟RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA, ENABLE);RCC_APB2PeriphClockCmd(RCC_APB2Periph_USART1, ENABLE);7.综合示例代码void RCC_Configuration(void) {/* 定义枚举类型变量 HSEStartUpStatus */ErrorStatus HSEStartUpStatus;/* 复位系统时钟设置*/RCC_DeInit();/* 开启HSE*/RCC_HSEConfig(RCC_HSE_ON);/* 等待HSE起振并稳定*/HSEStartUpStatus = RCC_WaitForHSEStartUp();/* 判断HSE起是否振成功,是则进入if()内部 */if(HSEStartUpStatus == SUCCESS) {/* 选择HCLK(AHB)时钟源为SYSCLK 1分频 */RCC_HCLKConfig(RCC_SYSCLK_Div1);/* 选择PCLK2时钟源为 HCLK(AHB) 1分频 */RCC_PCLK2Config(RCC_HCLK_Div1);/* 选择PCLK1时钟源为 HCLK(AHB) 2分频 */RCC_PCLK1Config(RCC_HCLK_Div2);/* 设置FLASH延时周期数为2 */FLASH_SetLatency(FLASH_Latency_2);/* 使能FLASH预取缓存 */FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable); /* 选择锁相环(PLL)时钟源为HSE 1分频,倍频数为9,则PLL输出频率为 8MHz * 9 = 72MHz */RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);/* 使能PLL */RCC_PLLCmd(ENABLE);/* 等待PLL输出稳定 */while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET);/* 选择SYSCLK时钟源为PLL */RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);/* 等待PLL成为SYSCLK时钟源 */while(RCC_GetSYSCLKSource() != 0x08); }/* 打开APB2总线上的GPIOA时钟*/RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA|RCC_AP B2Periph_USART1, ENABLE);}2018-7-15 11:41:46 meetwit。

STM32中RCC的总结

一.时钟源在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。

倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

其中40kHz的LSI供独立看门狗IWDG使用,另外它还可以被选择为实时时钟RTC的时钟源。

另外,实时时钟RTC的时钟源还可以选择LSE,或者是HSE的128分频。

RTC的时钟源通过RTCSEL[1:0]来选择。

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz 的时钟源。

该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

另外,STM32还可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟。

系统时钟SYSCLK,它是供STM32中绝大部分部件工作的时钟源。

系统时钟可选择为PLL输出、HSI或者HSE。

系统时钟最大频率为72MHz,它通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。

其中AHB分频器输出的时钟送给5大模块使用:①、送给AHB总线、内核、内存和DMA使用的HCLK时钟。

②、通过8分频后送给Cortex的系统定时器时钟。

③、直接送给Cortex的空闲运行时钟FCLK。

④、送给APB1分频器。

APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给定时器(Timer)2、3、4倍频器使用。

STM32 RCC复位时钟配置寄存器

RCCSTM32 的RCC看起来还是蛮复杂的,英文全称是Reset Clock Config,复位时钟配置,以下基本网上贴的,整理了一下,非原创哈。

一、时钟概述STM32有多个时钟源,分别是:HSI: 内部高速时钟(上电默认启动),因精度不高所以先不采用,以后如果需要再使用LSI:内部低速时钟,精度不高,一般用于IWDGCLKHSE:外部高速时钟,系统时钟一般采用它,经过PLL倍频作为系统同时钟LSE:外部低速时钟,一般专门用于RTC,等到RTC模块时再使用二、配置流程1.将RCC寄存器重新设置为默认值RCC_DeInit(default 默认)2.打开外部高速时钟晶振HSE RCC_HSEConfig(RCC_HSE_ON);3.等待外部高速时钟晶振工作HSEStartUpStatus = RCC_WaitForHSEStartUp();4.设置AHB时钟RCC_HCLKConfig;5.设置高速APB2时钟 RCC_PCLK2Config;6.设置低速速APB1时钟RCC_PCLK1Config7.设置PLL RCC_PLLConfig8.打开PLL RCC_PLLCmd(ENABLE);9.等待PLL工作while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET)10.设置系统时钟RCC_SYSCLKConfig11.判断是否PLL是系统时钟while(RCC_GetSYSCLKSource() != 0x08)至此系统时钟已经配置完成,STM32的每个模块都有自己的时钟,如果要使用某个模块,必须使能这个模块的时钟。

使能对应模块的时钟,STM32有个库函数,RCC_APB2PeriphClockCmd(对应模块,ENABLE)(72MHZ)或者RCC_APB1PeriphClockCmd(对应模块,ENABLE)(36MHZ);其中不同的模块有不同的时钟源,下面列举各个模块的时钟源:AHB2 时钟用于以下资源:(APB2:72MHZ)RCC_APB2Periph_AFIO 功能复用 IO 时钟RCC_APB2Periph_GPIOA GPIOA 时钟RCC_APB2Periph_GPIOB GPIOB 时钟RCC_APB2Periph_GPIOC GPIOC 时钟RCC_APB2Periph_GPIOD GPIOD 时钟RCC_APB2Periph_GPIOE GPIOE 时钟RCC_APB2Periph_ADC1 ADC1 时钟RCC_APB2Periph_ADC2 ADC2 时钟RCC_APB2Periph_TIM1 TIM1 时钟RCC_APB2Periph_SPI1 SPI1 时钟RCC_APB2Periph_USART1 USART1 时钟RCC_APB2Periph_ALL 全部 APB2外设时钟AHB1 时钟用于以下资源:(APB1:36MHZ)RCC_APB1Periph_TIM2 TIM2 时钟RCC_APB1Periph_TIM3 TIM3 时钟RCC_APB1Periph_TIM4 TIM4 时钟RCC_APB1Periph_WWDG WWDG时钟RCC_APB1Periph_SPI2 SPI2 时钟RCC_APB1Periph_USART2 USART2 时钟RCC_APB1Periph_USART3 USART3 时钟RCC_APB1Periph_I2C1 I2C1 时钟RCC_APB1Periph_I2C2 I2C2时钟RCC_APB1Periph_USB USB 时钟RCC_APB1Periph_CAN CAN时钟RTC 时钟来源:RCC_RTCCLKSource_LSE 选择 LSE 作为RTC 时钟RCC_RTCCLKSource_LSI 选择 LSI 作为RTC 时钟RCC_RTCCLKSource_HSE_Div128 选择 HSE 时钟频率除以 128 作为 RTC时钟ADC 时钟来源:该时钟源自 APB2 时钟(PCLK2)RCC_PCLK2_Div2 ADC 时钟= PCLK / 2RCC_PCLK2_Div4 ADC 时钟= PCLK / 4RCC_PCLK2_Div6 ADC 时钟= PCLK / 6RCC_PCLK2_Div8 ADC 时钟= PCLK / 8USB 时钟来源:该时钟来源于PLLCLK时钟的预分频三、RCC配置实例代码,与解析void RCC_Configuration(void){ErrorStatus HSEStartUpStatus;RCC_DeInit();//复位RCC模块的寄存器,复位成缺省值RCC_HSEConfig(RCC_HSE_ON);//开启HSE时钟,咱是用HSE的时钟作为PLL的时钟源HSEStartUpStatus = RCC_WaitForHSEStartUp();//获取HSE启动状态if(HSEStartUpStatus == SUCCESS) //如果HSE启动成功{FLASH_PrefetchBufferCmd(ENABLE);//开启FLASH的预取功能FLASH_SetLatency(FLASH_Latency_2);//FLASH延迟2个周期,RCC_HCLKConfig(RCC_SYSCLK_Div1);//配置HCLK,PCLK2,PCLK1,PLLRCC_PCLK2Config(RCC_HCLK_Div1);RCC_PCLK1Config(RCC_HCLK_Div2);RCC_PLLConfig(RCC_PLLSource_HSE_Div1,RCC_PLLMul_9);RCC_PLLCmd(ENABLE);//启动PLLwhile(RCC_GetFlagStatus(RCC_FLAG_PLLRDY)==RESET){}//等待PLL启动完成RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);//配置系统时钟while(RCC_GetSYSCLKSource() !=0x80)//检查是否将HSE 9倍频后作为系统时钟{}}}和STM32超频比较相关,Ourdev上有个超频的帖蛮有意思的有兴趣的可以看看,附上网址:/bbs/bbs_content_all.jsp?bbs_sn=3554410总之,STM32的时钟看起来比较复杂,但是可以不用去深究,使用STM32的库函数还是很好用的,虽然效率低了点,但是其实只使用很少的次数,无所谓了,要想STM32跑起来,按照上述配置就好了,千万不要忘记为使用的模块分配时钟,不要像我,跑个LED,忘记给IO分配时钟,还在纳闷呢,为什么不亮.(摘自网络).总结:我比这位原作者好点,我第一次让STM32跑两个灯一下就顺利了.就是第一次KEIL联不上STM32有点郁闷,在网上升级了,STLINK还是不行.后来得知,原来STLINK升级版本好几个了,找了新的版本总算跟4.12联上了.我的STLINK版本号J1STM32有五个时钟源:HSI、HSE、LSI、LSE、PLL1.1HSI:高速内部时钟、RC振荡器、频率为8MHz、时钟精度较差(上电默认启动),可作为备用时钟源(时钟安全系统CSS)。

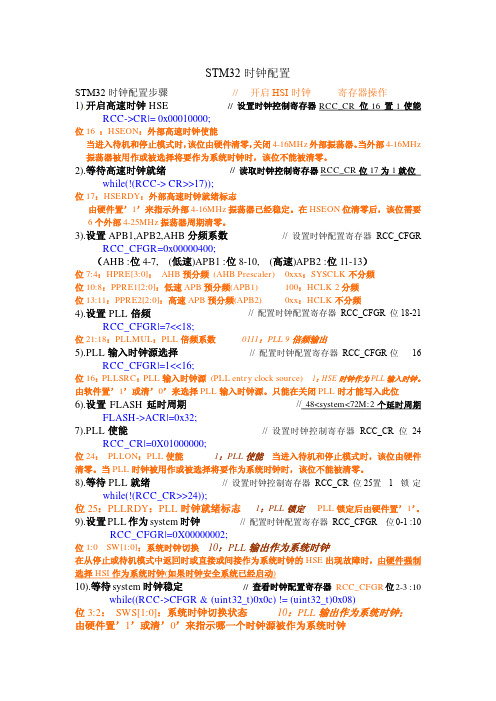

STM32RCC分析与使用

STM32RCC分析与使用STM32系列微控制器是意法半导体公司(STMicroelectronics)推出的一款32位嵌入式微控制器,广泛应用于各种各样的嵌入式应用中。

在STM32中,RCC(Reset and Clock Control)模块是用来控制系统复位和时钟的重要模块。

下面将对RCC模块进行分析与使用。

首先,RCC模块的主要功能是对系统时钟进行控制和配置。

在STM32中,系统时钟用于驱动处理器和外设,因此RCC模块的配置对整个系统的性能和功能都有着重要的影响。

RCC模块提供了多个时钟源和分频器来满足不同需求。

RCC模块主要包括以下功能:1.时钟源选择:RCC可以选择多个时钟源,包括内部和外部时钟源。

常见的时钟源包括内部高速时钟(HSI)、内部低速时钟(LSI)、外部高速时钟(HSE)和外部低速时钟(LSE)等。

通过选择不同的时钟源,可以满足不同的功耗和精度要求。

2.时钟分频:RCC模块提供了多个分频器,可以对系统时钟进行分频,以得到所需的时钟频率。

可以通过调整分频系数来满足不同的应用需求,例如减小系统时钟频率以降低功耗。

3.时钟输出:RCC模块还可以将系统时钟输出到特定的管脚,以供其他外设使用。

这对于一些需要同步时钟的应用非常有用。

在使用RCC模块时,一般需要进行以下几个步骤:1.使能对应的时钟源:根据实际需求选择合适的时钟源,并使能该时钟源。

对于外部时钟源,还需要设置相关的参数,如频率和稳定性。

2.配置时钟分频器:根据应用需求配置时钟分频器,以得到所需的时钟频率。

通常可以通过寄存器设置来完成。

3.选择系统时钟源:根据实际需求选择合适的系统时钟源。

一般可以选择内部高速时钟(HSI)、内部低速时钟(LSI)、外部高速时钟(HSE)或外部低速时钟(LSE)作为系统时钟源。

4.配置系统时钟分频器:根据应用需求配置系统时钟分频器,以得到所需的系统时钟频率。

通常可以通过寄存器设置来完成。

5.配置时钟输出:如果需要将系统时钟输出到特定的管脚,可以通过设置相应的寄存器来完成。

快速看懂STM32-电源、时钟、复位电路及 源代码

快速看懂STM32-电源、时钟、复位电路及源代码

STM32时钟分析

一、硬件上的连接问题

如果使用内部RC振荡器而不使用外部晶振,请按照如下方法处理:

1)对于100脚或144脚的产品,OSC_IN应接地,OSC_OUT应悬空。

2)对于少于100脚的产品,有2种接法:

i)OSC_IN和OSC_OUT分别通过10K电阻接地。

此方法可提高EMC性能。

ii)分别重映射OSC_IN和OSC_OUT至PD0和PD1,再配置PD0和PD1为推挽输出并输出0。

此方法可以减小功耗并(相对上面i)节省2个外部电阻。

对上图的分析如下:

重要的时钟:

PLLCLK,SYSCLK,HCKL,PCLK1,PCLK2之间的关系要弄清楚;

1、HSI:高速内部时钟信号STM32单片机内带的时钟(8M频率)精度较差

2、HSE:高速外部时钟信号精度高来源(1)HSE外部晶体/陶瓷谐振器(晶振)(2)HSE用户外部时钟

3、LSE:低速外部晶体32.768kHz主要提供一个精确的时钟源一般作为RTC时钟使用

在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。

倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

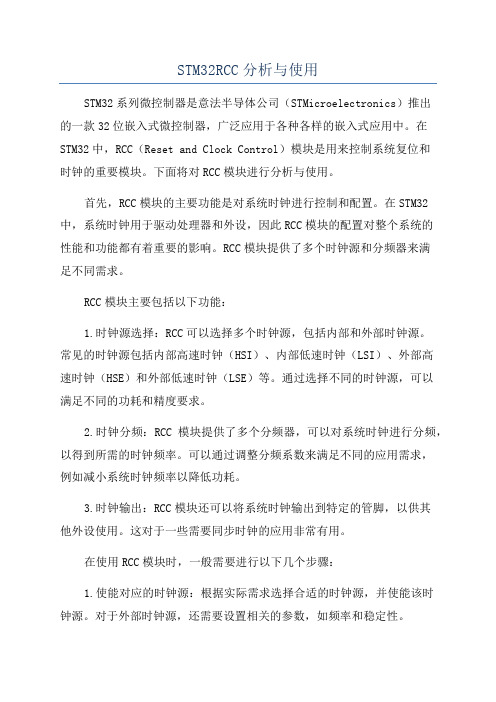

STM32时钟详细配置

STM32时钟配置STM32时钟配置步骤// 开启HSI时钟寄存器操作1).开启高速时钟HSE // 设置时钟控制寄存器RCC_CR 位16 置1使能RCC->CR|= 0x00010000;位16 :HSEON:外部高速时钟使能当进入待机和停止模式时,该位由硬件清零,关闭4-16MHz外部振荡器。

当外部4-16MHz 振荡器被用作或被选择将要作为系统时钟时,该位不能被清零。

2).等待高速时钟就绪// 读取时钟控制寄存器RCC_CR位17为1就位while(!(RCC-> CR>>17));位17:HSERDY:外部高速时钟就绪标志由硬件置’1’来指示外部4-16MHz振荡器已经稳定。

在HSEON位清零后,该位需要6个外部4-25MHz振荡器周期清零。

3).设置APB1,APB2,AHB分频系数// 设置时钟配置寄存器RCC_CFGRRCC_CFGR=0x00000400;(AHB :位4-7, (低速)APB1 :位8-10, (高速)APB2 :位11-13)位7:4:HPRE[3:0]:AHB预分频(AHB Prescaler)0xxx:SYSCLK不分频位10:8:PPRE1[2:0]:低速APB预分频(APB1) 100:HCLK 2分频位13:11:PPRE2[2:0]:高速APB预分频(APB2) 0xx:HCLK不分频4).设置PLL倍频// 配置时钟配置寄存器RCC_CFGR 位18-21RCC_CFGR|=7<<18;位21:18:PLLMUL:PLL倍频系数0111:PLL 9倍频输出5).PLL输入时钟源选择// 配置时钟配置寄存器RCC_CFGR 位16RCC_CFGR|=1<<16;位16:PLLSRC:PLL输入时钟源(PLL entry clock source) 1:HSE时钟作为PLL输入时钟。

由软件置’1’或清’0’来选择PLL输入时钟源。

stm32时钟初始化函数rcc_configuration(void)[指南]

![stm32时钟初始化函数rcc_configuration(void)[指南]](https://img.taocdn.com/s3/m/c93d9d02a9114431b90d6c85ec3a87c240288a1b.png)

E rrorStatus HSE StartUpStatus; //什么意思?格式?您好:您出现这个问题的原因可能是你的程序里调用了一些标准C的函数,但这些函数在嵌入式C语言里是没有定义的,你需要对你调用的这些函数进行重新定义。

举个例子,例如你调用了标准C里面的printf函数,就会出现在你所说的错误,你需要在程序里对这个函数进行重定义或者直接删除。

GPIO_InitTypeDef GPIO_InitStructure;这句话什么意思声明一个结构体,名字是GPIO_InitStructure,结构体原型由GPIO_InitTypeDef 确定,stm32里面初始化GPIO用的吧。

设置完了GPIO_InitStruc ture里面的内容后在GPIO_Init (GPIO_TypeDef *GPIOx, GPIO_InitTypeDef *GPIO_InitStruct)里面调用,比如初始化pa口,就是GPIO_Init (GPIOA, &GPIO_InitStructure),括号里后面那个就是你问题里面声明的那个结构体1.函数RCC_DeInitTable 338. 函数RCC_DeInit(1)(2)函数名RCC_DeInit函数原形void RCC_DeInit(void)功能描述将外设RCC寄存器重设为缺省值输入参数无输出参数无返回值无先决条件无被调用函数无2. 15.2.2 函数RCC_HSEConfigTable 339. 描述了函数RCC_HSEConfig函数名RCC_HSEConfig函数原形void RCC_HSEConfig(u32 RCC_HSE)功能描述设置外部高速晶振(HSE)输入参数RCC_HSE: HSE的新状态参阅Section:RCC_HSE 查阅更多该参数允许取值范围输出参数无返回值无先决条件如果HSE被直接或者通过PLL用于系统时钟,那么它不能被停振被调用函数无3.RCC_HSE该参数设置了HSE的状态(见Table 340.)Table 340. RCC_HSE定义RCC_HSE描述RCC_HSE_OFFHSE晶振OFFRCC_HSE_ONHSE晶振ONRCC_HSE_BypassHSE晶振被外部时钟旁路3.HSE或LSE晶振/时钟被旁路是什么意思?楼主可以仔细看芯片资料,只有在使用外部时钟的时候是被旁路,注意不是晶体振荡器,也就是说当使用外部提供的时钟时(如使用有源振荡器),必须设置这个控制位旁路上述内置振荡器;可以理解把内部时钟关闭,打开外部时钟。

STM32学习笔记之RCC

STM32学习笔记之RCC时钟三种不同的时钟源可被用来驱动系统时钟(SYSCLK):●HSI 振荡器时钟●HSE 振荡器时钟●PLL 时钟这些设备有以下2 种二级时钟源:●40kHz 低速内部RC,可以用于驱动独立看门狗和通过程序选择驱动RTC。

RTC 用于从停机/待机模式下自动唤醒系统。

●32.768kHz 低速外部晶体也可用来通过程序选择驱动RTC(RTCCLK)。

当不被使用时,任一个时钟源都可被独立地启动或关闭,由此优化系统功耗。

1.当HSI 被用于作为PLL 时钟的输入时,系统时钟能得到的最大频率是64MHz。

2.对于内部和外部时钟源的特性,请参考相应产品数据手册中电气特性章节。

用户可通过多个预分频器配置AHB、高速APB(APB2)和低速APB(APB1)域的频率。

AHB 和APB2 域的最大频率是72MHz。

APB1 域的最大允许频率是36MHz。

SDIO 接口的时钟频率固定为HCLK/2。

RCC 通过AHB 时钟(HCLK)8 分频后作为Cortex 系统定时器(SysTick)的外部时钟。

通过对SysTick 控制与状态寄存器的设置,可选择上述时钟或Cortex(HCLK)时钟作为SysTick 时钟。

ADC 时钟由高速APB2 时钟经2、4、6或8 分频后获得。

定时器时钟频率分配由硬件按以下2 种情况自动设置: 1.如果相应的APB 预分频系数是1,定时器的时钟频率与所在APB 总线频率一致。

2. 否则,定时器的时钟频率被设为与其相连的APB 总线频率的2 倍。

void RCC_Configuration(void){ SystemInit(); RCC_APB2PeriphClockCmd(USARTy_GPIO_CLK | USARTz_GPIO_CLK | RCC_APB2Periph_AFIO, ENABLE);#ifndef USE_STM3210C_EVAL RCC_APB2PeriphClockCmd(USARTy_CLK, ENABLE);#else RCC_APB1PeriphClockCmd(USARTy_CLK, ENABLE);#endif RCC_APB1PeriphClockCmd(USARTz_CLK, ENABLE);}tips:感谢大家的阅读,。

STM32F2系列之复位和时钟控制RCC详解

TIMxCLK TIM2..7,12..14

PCLK2 up to 60MHz VCO /P PLL48CLK (USB FS, SDIO & RNG) /Q xN /R APB2 Prescaler /1,2,4,8,16

If (APB2 pres =1)

x1

Else

x2

TIMxCLK TIM1,8..11

PLL

VCO

/P

HSI HSE MCO1 /1..5 PLLCLK LSE

/Q

Ext. Clock SPI2S_CKI N I2SCLK PLLI2SCLK MACTXCLK MACRXCLK MACRMIICL K

xN

/R

PLLI2S

USB HS ULPI clock

SYSCLK

MCO2 /1..5 PLLCLK / 2, 20 HSE

TIMxCLK TIM2..7,12..14

PCLK2 up to 60MHz VCO /P PLL48CLK (USB FS, SDIO & RNG) /Q xN /R APB2 Prescaler /1,2,4,8,16

If (APB2 pres =1)

x1

Else

x2

TIMxCLK TIM1,8..11

HSI RC 4 -26 MHz OSC_OUT OSC_IN

16MHz HSI

/M HSE PLLCLK

HSE Osc

SYSCLK AHB Prescaler 120 MHz max

/1,2…512

APB1 Prescaler /1,2,4,8,16

If (APB1 pres =1) Else

x1 x2

TB复位和时钟控制介绍(RCC)

TB复位和时钟控制介绍(RCC)STM32 RCC分析与使用由于STM32 系列微控制器系统比较复杂,时钟系统也相对于普通MCU 更多样化,这加大了我们设计程序和学习的难度.比如普通的MCU延时程序,我们直接可以使用“for 循环”或者“while”来轻易实现;而在Cortex 核的STM32 系列微控制器上则不行:因为无法判断当时的时钟频率,做不到精确的延时.如果详细地了解其时钟系统后,我们知道可以使用SYSCLK 来实现精确延时.RCC的学习可以说没有实验,但所有的模块都会用到时钟,我们进行I/O口的初始化,配置函数中第一行代码一般都是对时钟的初始化,足可见其重要性.一般而言,要是真正理解了STM32中所有的时钟,学习其他外设都是易如反掌了.[编辑] 实验要求深入理解STM32系统时钟和复位控制.[编辑] 实验目的学习STM32系列的时钟.[编辑] 硬件分析[编辑] 时钟树.在STM32 系统中,共有五个时钟源,分别为HSE、HSI、LSE、LSI、PLL.由图可以看出,HSI 和LSI 为片内RC 振荡器,HSI 为8MHz 而LSI 为32KHz;HSE 和LSE 为外部时钟源;PLL 则需要HSE 和HSI 来提供时钟.(1)HSE:高速外部时钟信号可以通过外部直接提供时钟,从OSC_IN 输入,或使用外部陶瓷/晶体谐振器.外部直接提供的时钟可以达到25MHz,用户可以通过设置时钟信号控制寄存器RCC_CR 中的HSEBYP 和HSEON 位来选择该模式.此时OSC_OUT 引脚为高阻状态.(2)HSI:高速内部时钟信号该时钟通过8MHz 的内部RC 振荡器产生,并且可被直接用做系统时钟,或者经过2 分频后作为PLL 的输入.它比HSE 有更快的启动时间,但频率精确度没有外部晶体振荡器高.而且根据制造工艺的不同,不同芯片之间的RC 振荡器频率也是不同.出厂时,每个设备频率已被校准至1%(25 摄氏度).出厂校验值被装载到时钟控制寄存器RCC_CR 的HSICAL [7:0] 位.在不同的电压或者温度下,可以通过RCC_CR 中的HSITRIM[4:0]位来调整HSI 的频率.并可以通过时钟控制寄存器RCC_CR 的HISON 位打开或者禁用.(3) LSE:低速外部时钟信号振荡器是一个32.768KHz 的低速外部晶体/陶瓷振荡器,它可以向RTC 提供高精准时钟.LSI:低速内部时钟信号振荡频率为32KHz 左右(30-60KHz 之间).(5)PLL:锁相环倍频输出其时钟输入源可选择为HSI/2、HSE 或者HSE/2.倍频可选择为2~16 倍,但是其输出频率最大不得超过72MHz.系统时钟(SYSCLK)系统时钟SYSCLK 是供STM32 中绝大部分部件工作的时钟源.系统时钟可选择为PLL 输出、HSI 或者HSE.HSI 与HSE 可以通过分频加至PLLSRC,并由PLLMUL 进行倍频后经选择直接充当SYSCLK.PLLCLK 经1.5 分频或1 分频后为USB 串行接口引擎提供一个48MHz 的振荡频率.即当需要使用USB 时,PLL 必须使能,并且时钟频率配置为48MHz 或者72MHz.但这并不意味着USB 模块工作时需要48MHz,48MHz 仅提供给USB 串行接口引擎(SIE),而USB 模块工作是由APBH1 提供的.系统时钟最大频率为72MHz,它通过AHB 分频器分频后送给各模块使用,AHB 分频器可选择1、2、4、8、16、64、128、256、512 分频.AHB 分频器输出的时钟送给5 大模块使用:(1)送给AHB 总线、内核、内存和DMA 使用的HCLK 时钟.(2)通过8 分频后送给Cortex 的系统定时器时钟.(3)直接送给Cortex 的空闲运行时钟FCLK.(4)送给APB1 分频器.APB1 分频器可选择为1、2、4、8、16 分频,其输出中一路供APB1 外设使用(PCLK1,最大频率36MHz);另一路送给定时器(Timer)2、3、4 的倍频器使用(TIMXCLK),该倍频器可选择1或者2 倍频,输出供定时器2、3、4 使用.(5)送给APB2 分频器.APB2 分频器可供选择为1、2、4、8、16 分频,其输出一路供APB2 外设使用(PCLK2,最大频率72MHz);一路送给定时器(Timer)1 的倍频器使用(TIM1CLK),该倍频器可选择1 或者2 倍频,输出供定时器1 使用;另外,APB2 分频器还有一路输出供ADC 分频器使用,分频后送给ADC 模块使用,ADC 分频器可选择为2、4、6、8 分频.时钟安全系统(CSS)图中在SYSCLK 选择端下方有个CSS 模块,CSS 是一个时钟安全系统,用来保证系统时钟在HSE 失效时能继续工作.时钟检测器在HSE 振荡器启动延时后被使能,并当振荡器停止时禁用.如果在HSE振荡器时钟上检测到一个失效,这个振荡器将被自动禁用;一个时钟失效事件打断TIM1 高级控制定时器的输入,并且产生一个中断来通知软件该次失效,使得MCU 能够进行补救措施.系统时钟输出(MCO)图的左下方为系统时钟输出(MCO)模块.使得时钟能够输出到外部MCO 引脚,相关的GPIO 端口的配置寄存器必须被编程为复用功能模式.下面4 个时钟的任意一个可被选作MCO 时钟:(1)SYSCLK(2)HIS(3)HSE(4)2 分频的PLLCLK可通过时钟配置寄存器RCC_CFGR 的MCO[2:0]位进行选择.几点说明:(1)在以上的时钟输出中,有很多是带使能控制端的(如图中的Peripheral Clock Enable),例如AHB 总线时钟、内核时钟、各种APB1外设、APB2 外设等等.当需要使用某模块时,记得一定要先使能对应的时钟.(2)需要注意的是定时器的倍频器,当APB 的分频为1 时,它的倍频值为1,否则它的倍频值就为2.(3)连接在APB1(低速外设)上的设备有:电源接口、备份接口、CAN、USB、I2C1、I2C2、UART2、UART3、SPI2、窗口看门狗、Timer2、Timer3、Timer4.(4)连接在APB2( 高速外设)上的设备有:UART1、SPI1、Timer1、ADC1、ADC2、所有普通IO 口(PA~PE)、第二功能IO 口.(5)如果独立的看门狗(IWDG)被硬件选项或者软件访问启动了,LSI 振荡器将被强制打开,并且不能被禁用,在LSI 振荡器开始工作后,它的时钟被提供给IWDG.[编辑] 复位STM32F10xxx支持三种复位形式,分别为系统复位、上电复位和备份区域复位.[编辑] 系统复位除了时钟控制器的RCC_CSR寄存器中的复位标志位和备份区域中的寄存器(见上图)以外,系统复位将复位所有寄存器至它们的复位状态.当发生以下任一事件时,产生一个系统复位:1. NRST引脚上的低电平(外部复位)2. 窗口看门狗计数终止(WWDG复位)3. 独立看门狗计数终止(IWDG复位)4. 软件复位(SW复位)5. 低功耗管理复位可通过查看RCC_CSR控制状态寄存器中的复位状态标志位识别复位事件来源.[编辑] 软件复位通过将Cortex?M3中断应用和复位控制寄存器中的SYSRESETREQ位置’1’,可实现软件复位.请参考Cortex?M3技术参考手册获得进一步信息.[编辑] 低功耗管理复位在以下两种情况下可产生低功耗管理复位:在进入待机模式时产生低功耗管理复位:通过将用户选择字节中的nRST_STDBY位置’1’将使能该复位.这时,即使执行了进入待机模式的过程,系统将被复位而不是进入待机模式.在进入停止模式时产生低功耗管理复位:通过将用户选择字节中的nRST_STOP位置’1’将使能该复位.这时,即使执行了进入停机模式的过程,系统将被复位而不是进入停机模式.[编辑] 电源复位当以下事件中之一发生时,产生电源复位:上电/掉电复位(POR/PDR复位)从待机模式中返回电源复位将复位除了备份区域外的所有寄存器.复位电路如下所示:..图中复位源将最终作用于RESET引脚,并在复位过程中保持低电平.复位入口矢量被固定在地址0x0000_0004.芯片内部的复位信号会在NRST引脚上输出,脉冲发生器保证每一个(外部或内部)复位源都能有至少20μs的脉冲延时;当NRST引脚被拉低产生外部复位时,它将产生复位脉冲.[编辑] 时钟详细分析三种不同的时钟源可被用来驱动系统时钟(SYSCLK):● HSI振荡器时钟● HSE振荡器时钟● PLL时钟这些设备有以下2种二级时钟源:● 40kHz低速内部RC,可以用于驱动独立看门狗和通过程序选择驱动RTC.RTC用于从停机/待机模式下自动唤醒系统.● 32.768kHz低速外部晶体也可用来通过程序选择驱动RTC(RTCCLK).当不被使用时,任一个时钟源都可被独立地启动或关闭,由此优化系统功耗.[编辑] HSE时钟高速外部时钟信号(HSE)由以下两种时钟源产生:● HSE外部晶体/陶瓷谐振器● HSE用户外部时钟为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容器必须尽可能地靠近振荡器引脚.负载电容值必须根据所选择的振荡器来调整..上图为外部时钟源的硬件配置在外部时钟源(HSE旁路)这个模式下,必须提供外部时钟.它的频率最高可达25MHz.用户可通过设置在时钟控制寄存器中的HSEBYP和HSEON位来选择这一模式.外部时钟信号(50%占空比的方波、正弦波或三角波)必须连到SOC_IN引脚,同时保证OSC_OUT引脚悬空.具体见上图.上图为晶体/陶瓷谐振器的硬件配置在外部晶体/陶瓷谐振器(HSE晶体)这个模式下 4~16Mz外部振荡器可为系统提供更为精确的主时钟.相关的硬件配置可参考上图,进一步信息可参考数据手册的电气特性部分.在时钟控制寄存器RCC_CR中的HSERDY位用来指示高速外部振荡器是否稳定.在启动时,直到这一位被硬件置’1’,时钟才被释放出来.如果在时钟中断寄存器RCC_CIR中允许产生中断,将会产生相应中断.HSE晶体可以通过设置时钟控制寄存器里RCC_CR中的HSEON 位被启动和关闭.[编辑] HSI时钟HSI时钟信号由内部8MHz的RC振荡器产生,可直接作为系统时钟或在2分频后作为PLL输入.HSI RC振荡器能够在不需要任何外部器件的条件下提供系统时钟.它的启动时间比HSE晶体振荡器短.然而,即使在校准之后它的时钟频率精度仍较差.校准制造工艺决定了不同芯片的RC振荡器频率会不同,这就是为什么每个芯片的HSI时钟频率在出厂前已经被ST校准到1%(25°C)的原因.系统复位时,工厂校准值被装载到时钟控制寄存器的HSICAL[7:0]位.如果用户的应用基于不同的电压或环境温度,这将会影响RC振荡器的精度.可以通过时钟控制寄存器里的HSITRIM[4:0]位来调整HSI频率.时钟控制寄存器中的HSIRDY位用来指示HSI RC振荡器是否稳定.在时钟启动过程中,直到这一位被硬件置’1’,HSI RC输出时钟才被释放.HSI RC可由时钟控制寄存器中的HSION位来启动和关闭.如果HSE晶体振荡器失效,HSI时钟会被作为备用时钟源.[编辑] PLL内部PLL可以用来倍频HSI RC的输出时钟或HSE晶体输出时钟.参考时钟树图和时钟控制寄存器.PLL的设置(选择HIS振荡器除2或HSE振荡器为PLL的输入时钟,和选择倍频因子)必须在其被激活前完成.一旦PLL被激活,这些参数就不能被改动.如果PLL中断在时钟中断寄存器里被允许,当PLL准备就绪时,可产生中断申请.如果需要在应用中使用USB接口,PLL必须被设置为输出48或72MHZ时钟,用于提供48MHz的USBCLK时钟.[编辑] LSE时钟LSE晶体是一个32.768kHz的低速外部晶体或陶瓷谐振器.它为实时时钟或者其他定时功能提供一个低功耗且精确的时钟源.LSE晶体通过在备份域控制寄存器(RCC_BDCR)里的LSEON位启动和关闭.在备份域控制寄存器(RCC_BDCR)里的LSERDY指示LSE晶体振荡是否稳定.在启动阶段,直到这个位被硬件置’1’后,LSE时钟信号才被释放出来.如果在时钟中断寄存器里被允许,可产生中断申请.外部时钟源(LSE旁路) 在这个模式里必须提供一个32.768kHz频率的外部时钟源.你可以通过设置在备份域控制寄存器(RCC_BDCR)里的LSEBYP和LSEON位来选择这个模式.具有50%占空比的外部时钟信号(方波、正弦波或三角波)必须连到OSC32_IN引脚,同时保证OSC32_OUT引脚悬空.[编辑] LSI时钟LSI RC担当一个低功耗时钟源的角色,它可以在停机和待机模式下保持运行,为独立看门狗和自动唤醒单元提供时钟.LSI时钟频率大约40kHz(在30kHz和60kHz之间).进一步信息请参考数据手册中有关电气特性部分.LSI RC可以通过控制/状态寄存器(RCC_CSR)里的LSION位来启动或关闭.在控制/状态寄存器(RCC_CSR)里的LSIRDY位指示低速内部振荡器是否稳定.在启动阶段,直到这个位被硬件设置为’1’后,此时钟才被释放.如果在时钟中断寄存器(RCC_CIR)里被允许,将产生LSI中断申请.LSI校准可以通过校准内部低速振荡器LSI来补偿其频率偏移,从而获得精度可接受的RTC时间基数,以及独立看门狗(IWDG)的超时时间(当这些外设以LSI为时钟源).校准可以通过使用TIM5的输入时钟(TIM5_CLK)测量LSI时钟频率实现.测量以HSE的精度为保证,软件可以通过调整RTC的20位预分频器来获得精确的RTC时钟基数,以及通过计算得到精确的独立看门狗(IWDG)的超时时间.LSI校准步骤如下:打开TIM5,设置通道4为输入捕获模式;设置AFIO_MAPR的TIM5_CH4_IREMAP位为’1’,在内部把LSI连接到TIM5的通道4;通过TIM5的捕获/比较4事件或者中断来测量LSI时钟频率;根据测量结果和期望的RTC时间基数和独立看门狗的超时时间,设置20位预分频器.系统时钟(SYSCLK)选择系统复位后,HSI振荡器被选为系统时钟.当时钟源被直接或通过PLL间接作为系统时钟时,它将不能被停止.只有当目标时钟源准备就绪了(经过启动稳定阶段的延迟或PLL稳定),从一个时钟源到另一个时钟源的切换才会发生.在被选择时钟源没有就绪时,系统时钟的切换不会发生.直至目标时钟源就绪,才发生切换.在时钟控制寄存器(RCC_CR)里的状态位指示哪个时钟已经准备好了,哪个时钟目前被用作系统时钟.[编辑] 时钟安全系统(CSS)在实际应用中,经常出现由于晶体振荡器在运行中失去作用,造成微处理器的时钟源丢失,从而出现死机的现象,导致系统出错.严重时,由于系统的死机造成监控失效,导致无法挽回的损失!STM32作为一个可靠稳定的微处理器,但是不能排除由于某些外界特殊因素可能造成STM32的外部振荡器失效,STM32内部的时钟安全系统(CCS)正是为解决出现这种问题而设计的.一旦外部晶体振荡器(HSE)失效,CCS系统将STM32的系统时钟源切换到一个稳定的时钟源,以保证STM32能够继续运行,并进行相应的保护操作..时钟安全系统可以通过软件被激活.一旦其被激活,时钟监测器将在HSE振荡器启动延迟后被使能,并在HSE时钟关闭后关闭.如果HSE时钟发生故障,HSE振荡器被自动关闭,时钟失效事件将被送到高级定时器(TIM1和TIM8)的刹车输入端,并产生时钟安全中断CSSI,允许软件完成营救操作.此CSSI中断连接到Cortex?M3的NMI中断(不可屏蔽中断).注意:一旦CSS被激活,并且HSE时钟出现故障,CSS中断就产生,并且NMI也自动产生.NMI将被不断执行,直到CSS中断挂起位被清除.因此,在NMI的处理程序中必须通过设置时钟中断寄存器(RCC_CIR)里的CSSC位来清除CSS中断.如果HSE振荡器被直接或间接地作为系统时钟,(间接的意思是:它被作为PLL输入时钟,并且PLL时钟被作为系统时钟),时钟故障将导致系统时钟自动切换到HSI振荡器,同时外部HSE振荡器被关闭.在时钟失效时,如果HSE振荡器时钟(被分频或未被分频)是用作系统时钟的PLL的输入时钟,PLL也将被关闭.应用举例启动时钟安全系统CSS:RCC_ClockSecuritySystemCmd(ENABLE);//NMI中断是不可屏蔽的!//外部振荡器实现时,产生中断,对应的中断程序:void NMIException(void){if (RCC_GetITStatus(RCC_IT_CSS) != RESET){ // HSE、PLL已被禁止(但是PLL设置未变)… … // 客户添加相应的系统保护代码处// 下面为HSE恢复后的预设置代码RCC_HSEConfig(RCC_HSE_ON); // 使能HSERCC_ITConfig(RCC_IT_HSERDY, ENABLE); // 使能HSE就绪中断RCC_ITConfig(RCC_IT_PLLRDY, ENABLE); // 使能PLL就绪中断RCC_ClearITPendingBit(RCC_IT_CSS); // 清除时钟安全系统中断的挂起位// 至此,一旦HSE时钟恢复,将发生HSERDY中断,在RCC中断处理程序里,系统时钟可以设置到以前的状态}}在RCC的中断处理程序中,再对HSE和PLL进行相应的处理[编辑] RTC时钟通过设置备份域控制寄存器(RCC_BDCR)里的RTCSEL[1:0]位,RTCCLK时钟源可以由HSE/128、LSE或LSI时钟提供.除非备份域复位,此选择不能被改变..LSE时钟在备份域里,但HSE和LSI时钟不是.因此:● 如果LSE被选为RTC时钟:─ 只要VBAT维持供电,尽管VDD供电被切断,RTC仍继续工作.● 如果LSI被选为自动唤醒单元(AWU)时钟:─ 如果VDD供电被切断, AWU状态不能被保证.有关LSI校准. ● 如果HSE时钟128分频后作为RTC时钟:─ 如果VDD供电被切断或内部电压调压器被关闭(1.8V域的供电被切断),则RTC状态不确定.─ 必须设置电源控制寄存器(见4.4.1节)的DPB位(取消后备区域的写保护)为’1’.[编辑] 看门狗时钟如果独立看门狗已经由硬件选项或软件启动,LSI振荡器将被强制在打开状态,并且不能被关闭.在LSI振荡器稳定后,时钟供应给IWDG.[编辑] 时钟输出在实际应用中,一些用户常常遇到某些外设需要对其输入外部时钟或方波,针对这一需求,常用的方法是使用软件模拟,或使用有源晶振为其提供时钟或方波.STM32的PA.8引脚具有复用功能——时钟输出(MCO),该功能能将STM32内部的时钟通过PA.8输出,这解决客户的问题,同时降低了硬件成本.微控制器允许输出时钟信号到外部MCO引脚.相应的GPIO端口寄存器必须被配置为相应功能.以下四个时钟信号可被选作MCO时钟:.● SYSCLK ● HSI ● HSE ● 除2的PLL时钟时钟的选择由时钟配置寄存器(RCC_CFGR)中的MCO[2:0]位控制.由于STM32 GPIO输出管脚的最大响应频率为50MHz,如果输出频率超过50MHz,则输出的波形会失真.应用举例//设置PA.8为复用Push-Pull模式.<br/>GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;GPIO_Init(GPIOA, &GPIO_InitStructure);//输出时钟:时钟的选择由时钟配置寄存器(RCC_CFGR)中的MCO[2:0]位控制.<br/>RCC_MCOConfig(RCC_MCO);参数RCC_MCO为要输出的内部时钟: RCC_MCO_NoClock --- 无时钟输出RCC_MCO_SYSCLK --- 输出系统时钟(SysCLK)RCC_MCO_HSI --- 输出内部高速8MHz的RC振荡器的时钟(HSI)RCC_MCO_HSE --- 输出高速外部时钟信号(HSE)RCC_MCO_PLLCLK_Div2 --- 输出PLL倍频后的二分频时钟(PLLCLK/2)[编辑] RCC寄存器分析[编辑] 时钟控制寄存器(RCC_CR)偏移地址: 0x00复位值: 0x0000 XX83 X代表未定义.位31:26 保留,始终读为0.位25 PLLRDY:PLL时钟就绪标志 (PLL clock ready flag) PLL锁定后由硬件置’1’.0:PLL未锁定;1:PLL锁定.位24 PLLON:PLL使能 (PLL enable) 由软件置’1’或清零. 当进入待机和停止模式时,该位由硬件清零.当PLL时钟被用作或被选择将要作为系统时钟时,该位不能被清零.0:PLL关闭;1:PLL使能.位23:20 保留,始终读为0.位19 CSSON:时钟安全系统使能(Clock security system enable)由软件置’1’或清零以使能时钟监测器.0:时钟监测器关闭;1:如果外部4-16MHz振荡器就绪,时钟监测器开启.位18 HSEBYP:外部高速时钟旁路 (External high-speed clock bypass)在调试模式下由软件置’1’或清零来旁路外部晶体振荡器.只有在外部4-16MHz振荡器关闭的情况下,才能写入该位.0:外部4-16MHz振荡器没有旁路;1:外部4-16MHz外部晶体振荡器被旁路.位17 HSERDY:外部高速时钟就绪标志(External high-speed clock ready flag)由硬件置’1’来指示外部4-16MHz振荡器已经稳定.在HSEON位清零后,该位需要6个外部4-25MHz振荡器周期清零.0:外部4-16MHz振荡器没有就绪;1:外部4-16MHz振荡器就绪.位16 HSEON:外部高速时钟使能(External high-speed clock enable) 由软件置’1’或清零.当进入待机和停止模式时,该位由硬件清零,关闭4-16MHz外部振荡器.当外部4-16MHz振荡器被用作或被选择将要作为系统时钟时,该位不能被清零.0:HSE振荡器关闭;1:HSE振荡器开启.位15:8 HSICAL[7:0]:内部高速时钟校准(Internal high-speed clock calibration)在系统启动时,这些位被自动初始化位7:3 HSITRIM[4:0]:内部高速时钟调整(Internal high-speed clock trimming)由软件写入来调整内部高速时钟,它们被叠加在HSICAL[5:0]数值上.这些位在HSICAL[7:0]的基础上,让用户可以输入一个调整数值,根据电压和温度的变化调整内部HSI RC振荡器的频率.默认数值为16,可以把HSI调整到8MHz±1%;每步HSICAL的变化调整约40kHz.位2 保留,始终读为0.位1 HSIRDY:内部高速时钟就绪标志(Internal high-speed clock ready flag)由硬件置’1’来指示内部8MHz振荡器已经稳定.在HSION位清零后,该位需要6个内部8MHz振荡器周期清零.0:内部8MHz振荡器没有就绪;1:内部8MHz振荡器就绪.位0 HSION:内部高速时钟使能(Internal high-speed clock enable)由软件置’1’或清零.当从待机和停止模式返回或用作系统时钟的外部4-16MHz振荡器发生故障时,该位由硬件置’1’来启动内部8MHz的RC振荡器.当内部8MHz振荡器被直接或间接地用作或被选择将要作为系统时钟时,该位不能被清零.0:内部8MHz振荡器关闭; 1:内部8MHz振荡器开启.[编辑] 时钟配置寄存器(RCC_CFGR)偏移地址: 0x04复位值: 0x0000 0000访问: 0到2个等待周期,字,半字和字节访问只有当访问发生在时钟切换时,才会插入1或2个等待周期..位31:27 保留,始终读为0.位26:24 MCO:微控制器时钟输出(Microcontroller clock output)由软件置’1’或清零.0xx:没有时钟输出;100:系统时钟(SYSCLK)输出;101:内部RC振荡器时钟(HSI)输出;110:外部振荡器时钟(HSE)输出;111:PLL时钟2分频后输出.注意:- 该时钟输出在启动和切换MCO时钟源时可能会被截断.- 在系统时钟作为输出至MCO引脚时,请保证输出时钟频率不超过50MHz (I/O口最高频率).位22 USBPRE:USB预分频(USB prescaler) 由软件置’1’或清’0’来产生48MHz的USB时钟.在RCC_APB1ENR寄存器中使能USB时钟之前,必须保证该位已经有效.如果USB时钟被使能,该位不能被清零.0:PLL时钟1.5倍分频作为USB时钟1:PLL时钟直接作为USB时钟位21:18 PLLMUL:PLL倍频系数 (PLL multiplication factor) 由软件设置来确定PLL倍频系数.只有在PLL关闭的情况下才可被写入.注意:PLL的输出频率不能超过72MHz0000:PLL 2倍频输出 1000:PLL 10倍频输出0001:PLL 3倍频输出 1001:PLL 11倍频输出0010:PLL 4倍频输出 1010:PLL 12倍频输出0011:PLL 5倍频输出 1011:PLL 13倍频输出0100:PLL 6倍频输出 1100:PLL 14倍频输出0101:PLL 7倍频输出 1101:PLL 15倍频输出0110:PLL 8倍频输出 1110:PLL 16倍频输出0111:PLL 9倍频输出 1111:PLL 16倍频输出位17 PLLXTPRE:HSE分频器作为PLL输入 (HSE divider for PLL entry)由软件置’1’或清’0’来分频HSE后作为PLL输入时钟.只能在关闭PLL时才能写入此位.0:HSE不分频1:HSE 2分频位16 PLLSRC:PLL输入时钟源 (PLL entry clock source)由软件置’1’或清’0’来选择PLL输入时钟源.只能在关闭PLL时才能写入此位.0:HSI振荡器时钟经2分频后作为PLL输入时钟1:HSE时钟作为PLL输入时钟.位15:14 ADCPRE[1:0]:ADC预分频 (ADC prescaler)由软件置’1’或清’0’来确定ADC时钟频率00:PCLK2 2分频后作为ADC时钟01:PCLK2 4分频后作为ADC时钟10:PCLK2 6分频后作为ADC时钟11:PCLK2 8分频后作为ADC时钟位13:11 PPRE2[2:0]:高速APB预分频(APB2) (APB high-speed prescaler (APB2))由软件置’1’或清’0’来控制高速APB2时钟(PCLK2)的预分频系数.0xx:HCLK不分频100:HCLK 2分频101:HCLK 4分频110:HCLK 8分频111:HCLK 16分频位10:8 PPRE1[2:0]:低速APB预分频(APB1) (APB low-speed prescaler (APB1))由软件置’1’或清’0’来控制低速APB1时钟(PCLK1)的预分频系数.警告:软件必须保证APB1时钟频率不超过36MHz.0xx:HCLK不分频100:HCLK 2分频101:HCLK 4分频110:HCLK 8分频111:HCLK 16分频位7:4 HPRE[3:0]: AHB预分频 (AHB Prescaler)由软件置’1’或清’0’来控制AHB时钟的预分频系数.0xxx:SYSCLK 不分频1000:SYSCLK 2分频1001:SYSCLK 4分频1010:SYSCLK 8分频1101:SYSCLK 16分频1100:SYSCLK 64分频1101:SYSCLK 128分频1110:SYSCLK 256分频1111:SYSCLK 512分频注意:当AHB时钟的预分频系数大于1时,必须开启预取缓冲器.位3:2 SWS[1:0]:系统时钟切换状态(System clock switch status)由硬件置’1’或清’0’来指示哪一个时钟源被作为系统时钟.00:HSI作为系统时钟;01:HSE作为系统时钟;10:PLL输出作为系统时钟;11:不可用.位1:0 SW[1:0]:系统时钟切换 (System clock switch)由软件置’1’或清’0’来选择系统时钟源.在从停止或待机模式中返回时或直接或间接作为系统时钟的HSE出现故障时,由硬件强制选择HSI作为系统时钟(如果时钟安全系统已经启动)00:HSI作为系统时钟;01:HSE作为系统时钟;10:PLL输出作为系统时钟;11:不可用.[编辑] 时钟中断寄存器 (RCC_CIR)偏移地址: 0x08复位值: 0x0000 0000访问:无等待周期, 字, 半字和字节访问.位31:24 保留,始终读为0.位23 CSSC:清除时钟安全系统中断(Clock security system interrupt clear)由软件置’1’来清除CSSF安全系统中断标志位CSSF.0:无作用;1:清除CSSF安全系统中断标志位.位22:21 保留,始终读为0.位20 PLLRDYC:清除PLL就绪中断 (PLL ready interrupt clear) 由软件置’1’来清除PLL就绪中断标志位PLLRDYF.0:无作用;1:清除PLL就绪中断标志位PLLRDYF.位19 HSERDYC:清除HSE就绪中断 (HSE ready interrupt clear) 由软件置’1’来清除HSE就绪中断标志位HSERDYF.0:无作用;1:清除HSE就绪中断标志位HSERDYF.位18 HSIRDYC:清除HSI就绪中断 (HSI ready interrupt clear) 由软件置’1’来清除HSI就绪中断标志位HSIRDYF.0:无作用;1:清除HSI就绪中断标志位HSIRDYF.位17 LSERDYC:清除LSE就绪中断 (LSE ready interrupt clear) 由软件置’1’来清除LSE就绪中断标志位LSERDYF.0:无作用;1:清除LSE就绪中断标志位LSERDYF.位16 LSIRDYC:清除LSI就绪中断 (LSI ready interrupt clear) 由软件置’1’来清除LSI就绪中断标志位LSIRDYF.0:无作用;1:清除LSI就绪中断标志位LSIRDYF.位15:13 保留,始终读为0.位12 PLLRDYIE:PLL就绪中断使能 (PLL ready interrupt enable) 由软件置’1’或清’0’来使能或关闭PLL就绪中断.0:PLL就绪中断关闭;1:PLL就绪中断使能.位11 HSERDYIE:HSE就绪中断使能(HSE ready interrupt enable)由软件置’1’或清’0’来使能或关闭外部4-16MHz振荡器就绪中断.。

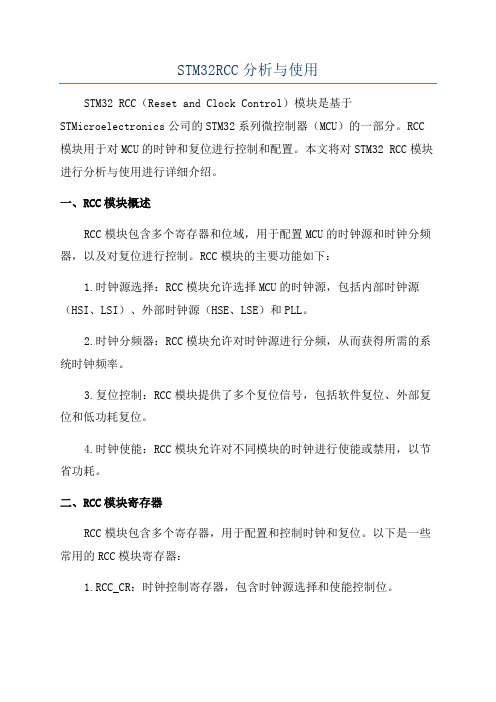

STM32RCC分析与使用

STM32RCC分析与使用STM32 RCC(Reset and Clock Control)模块是基于STMicroelectronics公司的STM32系列微控制器(MCU)的一部分。

RCC 模块用于对MCU的时钟和复位进行控制和配置。

本文将对STM32 RCC模块进行分析与使用进行详细介绍。

一、RCC模块概述RCC模块包含多个寄存器和位域,用于配置MCU的时钟源和时钟分频器,以及对复位进行控制。

RCC模块的主要功能如下:1.时钟源选择:RCC模块允许选择MCU的时钟源,包括内部时钟源(HSI、LSI)、外部时钟源(HSE、LSE)和PLL。

2.时钟分频器:RCC模块允许对时钟源进行分频,从而获得所需的系统时钟频率。

3.复位控制:RCC模块提供了多个复位信号,包括软件复位、外部复位和低功耗复位。

4.时钟使能:RCC模块允许对不同模块的时钟进行使能或禁用,以节省功耗。

二、RCC模块寄存器RCC模块包含多个寄存器,用于配置和控制时钟和复位。

以下是一些常用的RCC模块寄存器:1.RCC_CR:时钟控制寄存器,包含时钟源选择和使能控制位。

2.RCC_CFGR:时钟配置寄存器,包含PLL、时钟分频器和USBOTGFS时钟配置等。

3.RCC_APB1ENR/RCC_APB2ENR:外设时钟使能寄存器,用于使能或禁用不同外设的时钟。

4.RCC_AHB1RSTR/RCC_APB1RSTR/RCC_APB2RSTR:复位寄存器,用于控制不同外设的复位。

5.RCC_CSR:复位状态寄存器,用于读取和清除复位原因。

三、RCC模块的使用以下是一些常见的RCC模块的使用方法:1.时钟源选择:通过设置RCC_CR寄存器的位域,选择所需的时钟源。

例如,可以选择HSE作为系统时钟源。

2.时钟分频器配置:通过设置RCC_CFGR寄存器的位域,配置所需的时钟频率。

例如,可以将PLL分频系数设置为2,以获得系统时钟频率为HSE/23.外设时钟使能:通过设置RCC_APB1ENR/RCC_APB2ENR寄存器的位域,使能或禁用所需外设的时钟。

stm32复位和时钟控制

以下模块多个时钟源可选择

ADC模块

PCLK经过2或4分频,专用的14MHz-HSI 如果选择专用14MHz作为ADC时钟,可以配置是否由ADC自动开启/关闭14MHz RC

USART1

PCLK,系统时钟,HSI,LSE

I2C1

HSI,系统时钟

CEC

HSI/244,LSE

TI1_RMP @ TIM14_OR

TIM14

GPIO

TI1

RTCCLK HSE/32 MCO

7

低功耗模式下的时钟表现

睡眠模式

CPU时钟停止 用户可以设置是否也停止片上闪存和SRAM的接口时钟 如果所有连在APB总线上的外设的时钟都被用户关闭,则AHB到APB 桥的时钟也被硬件关闭

LSI

35~40~55 KHz

85 us

PLL

输入时钟频率 输出时钟频率

1~24 MHz 16~48 MHz

4

LSE起振能力动态可调

5

特殊外设时钟供给

片上闪存编程接口,HSI Option byte loader,HSI I2S1,系统时钟 IWWDG,LSI

由软件或硬件开启;一旦开启LSI就不能关闭

1

时钟树框图

OSC32_IN OSC32_OUT ~40kHz LSI RC 8MHz HSI RC /2 4 -32 MHz OSC_OUT OSC_IN /2, 4 [16MHz,48MHz] HSI14 RC ADC HSE Osc /2, 3, ..16 HSI IWWDGCLK CSS PCLK HCLK 32.768KHz LSE Osc HSE /32 RTCCLK /8 SysTick

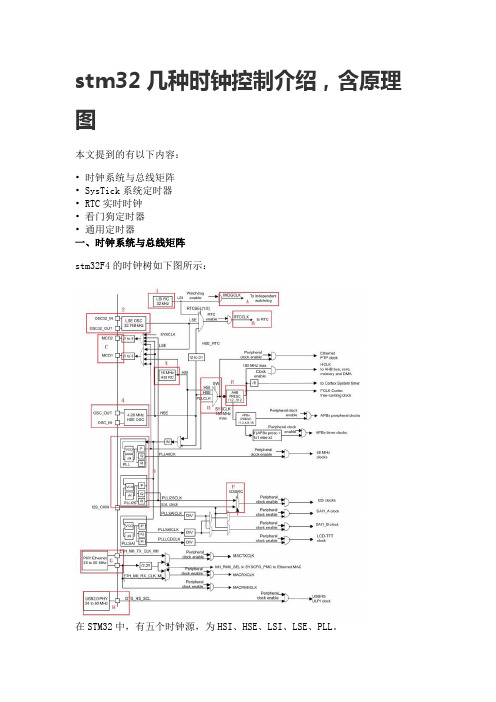

stm32几种时钟控制介绍,含原理图

stm32几种时钟控制介绍,含原理图本文提到的有以下内容:• 时钟系统与总线矩阵• SysTick系统定时器• RTC实时时钟• 看门狗定时器• 通用定时器一、时钟系统与总线矩阵stm32F4的时钟树如下图所示:在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

HSI是高速内部时钟,RC振荡器,频率为8MHz。

HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

LSI是低速内部时钟,RC振荡器,频率为40kHz。

LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。

倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

我们在学习51单片机的时候,其内部是没有晶振的,而stm32是有的。

stm32可以通过RCC(时钟控制寄存器)对时钟进行参数配置以及使能。

我们还可以通过修改system_stm32f4xx.c文件,来配置上述时钟树上的一些分频、倍频参数,得到理想的频率。

在单片机系统中,CPU和总线以及外设的时钟设置是非常重要的,因为没有时钟就没有时序,组合电路需要好好理解清楚。

我们先来看一下总线矩阵。

片上总线标准种类繁多,而由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。

AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。

二者分别适用于高速与相对低速设备的连接。

一般性的时钟设置需要先考虑系统时钟的来源,是内部RC还是外部晶振还是外部的振荡器,是否需要PLL。

然后考虑内部总线和外部总线,最后考虑外设的时钟信号。

遵从先倍频作为CPU时钟,然后在由内向外分频,下级迁就上级的原则。

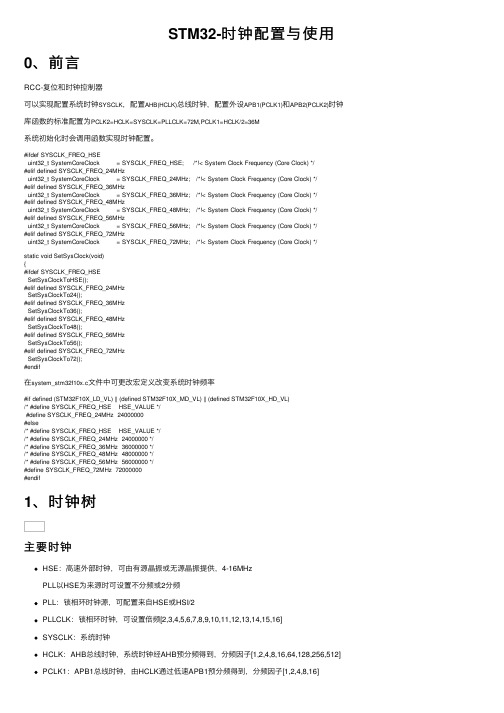

STM32-时钟配置与使用

STM32-时钟配置与使⽤0、前⾔RCC-复位和时钟控制器可以实现配置系统时钟SYSCLK,配置AHB(HCLK)总线时钟,配置外设APB1(PCLK1)和APB2(PCLK2)时钟库函数的标准配置为PCLK2=HCLK=SYSCLK=PLLCLK=72M,PCLK1=HCLK/2=36M系统初始化时会调⽤函数实现时钟配置。

#ifdef SYSCLK_FREQ_HSEuint32_t SystemCoreClock = SYSCLK_FREQ_HSE; /*!< System Clock Frequency (Core Clock) */#elif defined SYSCLK_FREQ_24MHzuint32_t SystemCoreClock = SYSCLK_FREQ_24MHz; /*!< System Clock Frequency (Core Clock) */#elif defined SYSCLK_FREQ_36MHzuint32_t SystemCoreClock = SYSCLK_FREQ_36MHz; /*!< System Clock Frequency (Core Clock) */#elif defined SYSCLK_FREQ_48MHzuint32_t SystemCoreClock = SYSCLK_FREQ_48MHz; /*!< System Clock Frequency (Core Clock) */#elif defined SYSCLK_FREQ_56MHzuint32_t SystemCoreClock = SYSCLK_FREQ_56MHz; /*!< System Clock Frequency (Core Clock) */#elif defined SYSCLK_FREQ_72MHzuint32_t SystemCoreClock = SYSCLK_FREQ_72MHz; /*!< System Clock Frequency (Core Clock) */static void SetSysClock(void){#ifdef SYSCLK_FREQ_HSESetSysClockToHSE();#elif defined SYSCLK_FREQ_24MHzSetSysClockTo24();#elif defined SYSCLK_FREQ_36MHzSetSysClockTo36();#elif defined SYSCLK_FREQ_48MHzSetSysClockTo48();#elif defined SYSCLK_FREQ_56MHzSetSysClockTo56();#elif defined SYSCLK_FREQ_72MHzSetSysClockTo72();#endif在system_stm32f10x.c⽂件中可更改宏定义改变系统时钟频率#if defined (STM32F10X_LD_VL) || (defined STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)/* #define SYSCLK_FREQ_HSE HSE_VALUE */#define SYSCLK_FREQ_24MHz 24000000#else/* #define SYSCLK_FREQ_HSE HSE_VALUE *//* #define SYSCLK_FREQ_24MHz 24000000 *//* #define SYSCLK_FREQ_36MHz 36000000 *//* #define SYSCLK_FREQ_48MHz 48000000 *//* #define SYSCLK_FREQ_56MHz 56000000 */#define SYSCLK_FREQ_72MHz 72000000#endif1、时钟树主要时钟HSE:⾼速外部时钟,可由有源晶振或⽆源晶振提供,4-16MHzPLL以HSE为来源时可设置不分频或2分频PLL:锁相环时钟源,可配置来⾃HSE或HSI/2PLLCLK:锁相环时钟,可设置倍频[2,3,4,5,6,7,8,9,10,11,12,13,14,15,16]SYSCLK:系统时钟PCLK2:APB2总线时钟,由HCLK通过⾼速APB2预分频得到,分频因⼦[1,2,4,8,16]其他时钟USB时钟:由PLLCLK通过USB预分频器得到,分频因⼦[1,1.5]Cortex系统时钟:由HCLK8分频得到,⽤来驱动内核的系统定时器SysTickADC时钟:由PCLK2经ADC预分频得到,分频因⼦[2,4,6,8]RTC时钟:由HSE/128或LSE或LSI得到MCO时钟:输出时钟,可由PLLCLK/2,HSI,HSE,SYSCLK配置2、时钟配置相关库函数配置函数/*将RCC外设初始化为复位状态*/void RCC_DeInit(void);/*使能HSE,可选参数RCC_HSE_OFF,RCC_HSE_ON,RCC_HSE_Bypass*/void RCC_HSEConfig(uint32_t RCC_HSE);/*等待时钟源启动稳定,返回SUCCESS,ERROR*/ErrorStatus RCC_WaitForHSEStartUp(void);/*配置PLL时钟源和PLL倍频因⼦RCC_RLLSource:RCC_PLLSource_HSE_Div1,RCC_PLLSource_HSE_Div2,RCC_PLLSource_HSI_Div2RCC_PLLMul:RCC_PLLMul_2 [2,3,4,5,6,7,8,9,10,11,12,13,14,15,16]*/void RCC_PLLConfig(uint32_t RCC_PLLSource, uint32_t RCC_PLLMul);/*配置系统时钟,可选参数RCC_SYSCLKSource_HSI,RCC_SYSCLKSource_HSE,RCC_SYSCLKSource_PLLCLK */void RCC_SYSCLKConfig(uint32_t RCC_SYSCLKSource);/*配置HCLK,可选参数RCC_SYSCLK_Div1 [1,2,4,8,16,64,128,256,512]*/void RCC_HCLKConfig(uint32_t RCC_SYSCLK);/*配置PCLK1,可选参数RCC_HCLK_Div1 [1,2,4,8,16]*/void RCC_PCLK1Config(uint32_t RCC_HCLK);/*配置PCLK2,可选参数RCC_HCLK_Div1 [1,2,4,8,16]*/void RCC_PCLK2Config(uint32_t RCC_HCLK);操作函数/*控制PLL开关,可选参数DISABLE,ENABLE*/void RCC_PLLCmd(FunctionalState NewState);/*获取状态,可选参数#define RCC_FLAG_HSIRDY ((uint8_t)0x21)#define RCC_FLAG_HSERDY ((uint8_t)0x31)#define RCC_FLAG_PLLRDY ((uint8_t)0x39)#define RCC_FLAG_LSERDY ((uint8_t)0x41)#define RCC_FLAG_LSIRDY ((uint8_t)0x61)#define RCC_FLAG_PINRST ((uint8_t)0x7A)#define RCC_FLAG_PORRST ((uint8_t)0x7B)#define RCC_FLAG_SFTRST ((uint8_t)0x7C)#define RCC_FLAG_IWDGRST ((uint8_t)0x7D)#define RCC_FLAG_WWDGRST ((uint8_t)0x7E)#define RCC_FLAG_LPWRRST ((uint8_t)0x7F)返回SET,RESET*/* - 0x08: PLL used as system clock*/uint8_t RCC_GetSYSCLKSource(void);使⽤HSE配置系统时钟1、开启HSE ,并等待 HSE 稳定2、设置 AHB、APB2、APB1的预分频因⼦3、设置PLL的时钟来源,和PLL的倍频因⼦,设置各种频率主要就是在这⾥设置4、开启PLL,并等待PLL稳定5、把PLLCK切换为系统时钟SYSCLK6、读取时钟切换状态位,确保PLLCLK被选为系统时钟/* 设置系统时钟:SYSCLK, AHB总线时钟:HCLK, APB2总线时钟:PCLK2, APB1总线时钟:PCLK1* PCLK2 = HCLK = SYSCLK* PCLK1 = HCLK/2,最⾼只能是36M* 参数说明:pllmul是PLL的倍频因⼦,在调⽤的时候可以是:RCC_PLLMul_x , x:[2,3,...16]* 举例:HSE_SetSysClock(RCC_PLLMul_9); 则设置系统时钟为:8MHZ * 9 = 72MHZ* HSE_SetSysClock(RCC_PLLMul_16); 则设置系统时钟为:8MHZ * 16 = 128MHZ,超频慎⽤** HSE作为时钟来源,经过PLL倍频作为系统时钟,这是通常的做法*/void HSE_SetSysClock(uint32_t pllmul){__IO uint32_t StartUpCounter = 0, HSEStartUpStatus = 0;// 把RCC外设初始化成复位状态,这句是必须的RCC_DeInit();//使能HSE,开启外部晶振,野⽕开发板⽤的是8MRCC_HSEConfig(RCC_HSE_ON);// 等待 HSE 启动稳定HSEStartUpStatus = RCC_WaitForHSEStartUp();// 只有 HSE 稳定之后则继续往下执⾏if (HSEStartUpStatus == SUCCESS){//----------------------------------------------------------------------//// 使能FLASH 预存取缓冲区FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);// SYSCLK周期与闪存访问时间的⽐例设置,这⾥统⼀设置成2// 设置成2的时候,SYSCLK低于48M也可以⼯作,如果设置成0或者1的时候,// 如果配置的SYSCLK超出了范围的话,则会进⼊硬件错误,程序就死了// 0:0 < SYSCLK <= 24M// 1:24< SYSCLK <= 48M// 2:48< SYSCLK <= 72MFLASH_SetLatency(FLASH_Latency_2);//----------------------------------------------------------------------//// AHB预分频因⼦设置为1分频,HCLK = SYSCLKRCC_HCLKConfig(RCC_SYSCLK_Div1);// APB2预分频因⼦设置为1分频,PCLK2 = HCLKRCC_PCLK2Config(RCC_HCLK_Div1);// APB1预分频因⼦设置为1分频,PCLK1 = HCLK/2RCC_PCLK1Config(RCC_HCLK_Div2);//-----------------设置各种频率主要就是在这⾥设置-------------------//// 设置PLL时钟来源为HSE,设置PLL倍频因⼦// PLLCLK = 8MHz * pllmulRCC_PLLConfig(RCC_PLLSource_HSE_Div1, pllmul);//------------------------------------------------------------------//// 开启PLLRCC_PLLCmd(ENABLE);// 等待 PLL稳定while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){}// 当PLL稳定之后,把PLL时钟切换为系统时钟SYSCLKRCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);// 读取时钟切换状态位,确保PLLCLK被选为系统时钟while (RCC_GetSYSCLKSource() != 0x08){}}else{// 如果HSE开启失败,那么程序就会来到这⾥,⽤户可在这⾥添加出错的代码处理// 当HSE开启失败或者故障的时候,单⽚机会⾃动把HSI设置为系统时钟,// HSI是内部的⾼速时钟,8MHZwhile (1){使⽤HSI配置系统时钟1、开启HSI ,并等待 HSI 稳定2、设置 AHB、APB2、APB1的预分频因⼦3、设置PLL的时钟来源,和PLL的倍频因⼦,设置各种频率主要就是在这⾥设置4、开启PLL,并等待PLL稳定5、把PLLCK切换为系统时钟SYSCLK6、读取时钟切换状态位,确保PLLCLK被选为系统时钟/* 设置系统时钟:SYSCLK, AHB总线时钟:HCLK, APB2总线时钟:PCLK2, APB1总线时钟:PCLK1* PCLK2 = HCLK = SYSCLK* PCLK1 = HCLK/2,最⾼只能是36M* 参数说明:pllmul是PLL的倍频因⼦,在调⽤的时候可以是:RCC_PLLMul_x , x:[2,3,...16]* 举例:HSI_SetSysClock(RCC_PLLMul_9); 则设置系统时钟为:4MHZ * 9 = 72MHZ* HSI_SetSysClock(RCC_PLLMul_16); 则设置系统时钟为:4MHZ * 16 = 64MHZ** HSI作为时钟来源,经过PLL倍频作为系统时钟,这是在HSE故障的时候才使⽤的⽅法* HSI会因为温度等原因会有漂移,不稳定,⼀般不会⽤HSI作为时钟来源,除⾮是迫不得已的情况* 如果HSI要作为PLL时钟的来源的话,必须⼆分频之后才可以,即HSI/2,⽽PLL倍频因⼦最⼤只能是16 * 所以当使⽤HSI的时候,SYSCLK最⼤只能是4M*16=64M*/void HSI_SetSysClock(uint32_t pllmul){__IO uint32_t HSIStartUpStatus = 0;// 把RCC外设初始化成复位状态,这句是必须的RCC_DeInit();//使能HSIRCC_HSICmd(ENABLE);// 等待 HSI 就绪HSIStartUpStatus = RCC->CR & RCC_CR_HSIRDY;// 只有 HSI就绪之后则继续往下执⾏if (HSIStartUpStatus == RCC_CR_HSIRDY){//----------------------------------------------------------------------//// 使能FLASH 预存取缓冲区FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);// SYSCLK周期与闪存访问时间的⽐例设置,这⾥统⼀设置成2// 设置成2的时候,SYSCLK低于48M也可以⼯作,如果设置成0或者1的时候,// 如果配置的SYSCLK超出了范围的话,则会进⼊硬件错误,程序就死了// 0:0 < SYSCLK <= 24M// 1:24< SYSCLK <= 48M// 2:48< SYSCLK <= 72MFLASH_SetLatency(FLASH_Latency_2);//----------------------------------------------------------------------//// AHB预分频因⼦设置为1分频,HCLK = SYSCLKRCC_HCLKConfig(RCC_SYSCLK_Div1);// APB2预分频因⼦设置为1分频,PCLK2 = HCLKRCC_PCLK2Config(RCC_HCLK_Div1);// APB1预分频因⼦设置为1分频,PCLK1 = HCLK/2RCC_PCLK1Config(RCC_HCLK_Div2);//-----------------设置各种频率主要就是在这⾥设置-------------------//// 设置PLL时钟来源为HSE,设置PLL倍频因⼦// PLLCLK = 4MHz * pllmulRCC_PLLConfig(RCC_PLLSource_HSI_Div2, pllmul);//------------------------------------------------------------------//// 开启PLLRCC_PLLCmd(ENABLE);// 等待 PLL稳定while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){}// 当PLL稳定之后,把PLL时钟切换为系统时钟SYSCLKRCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);// 读取时钟切换状态位,确保PLLCLK被选为系统时钟while (RCC_GetSYSCLKSource() != 0x08){}}else{// 如果HSI开启失败,那么程序就会来到这⾥,⽤户可在这⾥添加出错的代码处理// 当HSE开启失败或者故障的时候,单⽚机会⾃动把HSI设置为系统时钟,// HSI是内部的⾼速时钟,8MHZwhile (1){MCO输出MCO GPIO初始化/** 初始化MCO引脚PA8* 在F1系列中MCO引脚只有⼀个,即PA8,在F4系列中,MCO引脚会有两个*/void MCO_GPIO_Config(void){GPIO_InitTypeDef GPIO_InitStructure;// 开启GPIOA的时钟RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA, ENABLE);// 选择GPIO8引脚GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8;//设置为复⽤功能推挽输出GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;//设置IO的翻转速率为50MGPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;// 初始化GPIOA8GPIO_Init(GPIOA, &GPIO_InitStructure);}输出// MCO 引脚初始化MCO_GPIO_Config();// 设置MCO引脚输出时钟,⽤⽰波器即可在PA8测量到输出的时钟信号,// 我们可以把PLLCLK/2作为MCO引脚的时钟来检测系统时钟是否配置准确// MCO引脚输出可以是HSE,HSI,PLLCLK/2,SYSCLK//RCC_MCOConfig(RCC_MCO_HSE);//RCC_MCOConfig(RCC_MCO_HSI);//RCC_MCOConfig(RCC_MCO_PLLCLK_Div2);RCC_MCOConfig(RCC_MCO_SYSCLK);Systick系统定时器简介SysTick——系统定时器是属于 CM3 内核中的⼀个外设,内嵌在 NVIC 中。

STM32的时钟系统RCC详细整理

__IO uint32_t BDCR;

__IO uint32_t CSR;

#ifdef STM32F10X_CL

__IO uint32_t AHBRSTR;

__IO uint32_t CFGR2;

#endif /* STM32F10X_CL */

#if defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || defined (STM32F10X_HD_VL)

4、APB2外设复位寄存器 (RCC_APB2RSTR):(复位值: 0x0000 0000)

主要功能:AFIO、IOPA、IOPB、IOPC、IOPD、IOPE、IOPF、IOPG、ADC1、ADC2、TIM1、SPI1、TIM8、USART1、ADC3复位。

5、APB1外设复位寄存器 (RCC_APB1RSTR) :(复位值: 0x0000 0000)

打开外部高速时钟晶振 HSE : RCC_HSEConfig(RCC_HSE_ON);

等待外部高速时钟晶振工作: HSEStartUpStatus = RCC_WaitForHSEStartUp();

设置 AHB 时钟 (HCLK) : RCC_HCLKConfig(RCC_SYSCLK_Div1);

3、时钟中断寄存器 (RCC_CIR):(复位值: 0x0000 0000)

主要功能:LSI、LSE、HIS、HSE、PLL就绪中断标志,HSE时钟失效导致时钟安全系统中断标志,LSI、LSE、HIS、HSE、PLL就绪中断使能,清除LSI、LSE、HIS、HSE、PLL就绪中断,清除时钟安全系统中断。

__IO uint32_t CIR;

STM32L4实时时钟模块(RTC)介绍

68 68

• To unlock write protection on all RTC registers

No VBAT

YES

3 pins/ 3 events

Edge or Level Detection with Configurable filtering External interrupt and NO trigger with filtering 32-bit Backup registers 20 32

YES

RTC Block Diagram

RTC_TAMP1 RTC_TAMP2 RTC_TAMP3 RTC_TS RTC_REFIN

Backup Registers and RTC Tamper Control registers

67 67

Tamper Flag

TimeStamp Registers

YES YESΒιβλιοθήκη YES Resolution down to RTCCLK YES

2 w/ subseconds Calib window : 8s/16s/32s Calibration step: 3.81ppm/1.91ppm/0.95 ppm Range [-480ppm +480ppm]

RTC overview across families (2/2)

STM32L4

Real-Time Clock (RTC)

RTC Features (1/2)

STM32复位和时钟控制(RCC)

S T M32复位和时钟控制(R C C)-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN复位STM32F10xxx支持三种复位形式,分别为系统复位、电源复位和备份区域复位。

1、系统复位系统复位将所有寄存器设置成复位值,除了RCC_CSR(控制状态寄存器)中的相关复位标志位,通过查看RCC_CSR寄存器,可以识别复位源。

系统复位可由以下5种方式产生:1)外部引脚NRST复位(低电平触发);2)窗口看门狗(WWDG)计数终止3)独立看门狗(IDOG)计数终止4)软件复位(SW RESET),通过将中断应用和复位控制寄存器( Application Interrupt and Reset Control Register )中SYSRESETREQ位置1。

具体参考Cortex-M3 programmingmanual。

5)低功耗管理复位:①通过进入等待模式(StandBy)产生复位:通过User Option Bytes中设置nRST_STDBY位使能这种复位模式。

这时,即使执行了进入待机模式的过程,系统将被复位而不是进入待机模式。

②通过进入停止模式(STOP)产生复位:通过User Option Bytes中设置nRST_STOP位使能这种复位模式。

这时,即使执行了进入停止模式的过程,系统将被复位而不是进入停止模式。

2、电源复位电源复位设置所有寄存器置初始值,除了备份区域。

电源复位可由以下2种方式产生:1)上电复位和掉电复位(POR/PDR reset)2)退出等待(StandBy)模式这些复位源都作用在NRST引脚上,并且在复位延迟期间保持低电平。

提供给设备的系统复位信号都由NRST引脚输出,对每一个内部/外部复位源,脉冲发生器都将保证一个20us最小复位周期。

对于外部复位,当NRST位置低时,将产生复位信号。

3、备份区复位备份区复位仅仅影响被分区域,有以下两种产生方式:1)软件复位,设置备份区域控制寄存器RCC_BDCR BDRST=1;2)在V DD和V BAT两者掉电的前提下,V DD或V BAT上电。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Clocks: PLL

• 3 PLLs

• Each with 3 independent outputs • PLLs input frequency must be between 4 and 16 MHz • PLL input can be MSI/HSI or HSE f(VCO clock) = (f(PLL clock input)/PLLM) × PLLN f(PLL_P) = f(VCO clock) / PLLP f(PLL_Q) = f(VCO clock) / PLLQ f(PLL_R) = f(VCO clock) / PLLR PLLM from 1 to 8 PLLN from 8 to 86 PLLP = 7 or 17 PLLQ = 2, 4, 6, 8 PLLR = 2, 4, 6, 8

100 kHz, 200 kHz, 400 kHz, 800 kHz, 1 MHz, 2 MHz, 4 MHz (reset value), 8 MHz, 16 MHz, 24 MHz, 32 MHz, 48 MHz.

89

• After Reset and Shutdown, MSI frequency is 4 MHz, selected by MSISRANGE in RCC_CSR register • After Standby: Frequency selected from 1, 2, 4 or 8 MHz with MSISRANGE in RCC_CSR register. • MSIRGSEL must be set in RCC_CR to switch to the frequency selected by MSIRANGE

98

• Clock-out capability :

• MCO selected between :

• LSI • LSE • SYSCLK • • • HSI HSE PLLCLK • MSI

• LSCO selected between :

• LSI • LSE

Available in all modes except VBAT

• • • • • • • • Low level on the NRST pin (External Reset) WWDG event IWDG event Firewall event A software reset (through NVIC) Low-power mode security reset Option byte loader reset Brown-out Reset

87

• Backup domain RESET

• Resets in the Backup domain: RTC registers + Backup Registers + RCC BDCR register • Sources

• BDRST bit in RCC BDCR register • VDD or VBAT power on, if both supplies have previously been powered off

• Reset flag source can be found in RCC_CSR register

RESET Sources

• Power RESET

• Sources

• Brown-out reset BOR => reset all registers except those in Backup domain • Exit from STANDBY => all registers in VCORE domain are reset Registers outside the VCORE domain (RTC, WKUP, IWDG, and Standby/Shutdown modes control) are not impacted. • Exit from SHUTDOWN generates a BOR Reset.

• LSI 32kHz

Parameters Accuracy over parts Accuracy over temperature STM32L15x 26..56KHz -10% / +4% (0..85°C) 400nA STM32L4x ~8% 2% (-40 125°C) 110nA

9ET PULSE GENERATOR (min 20µs) IWDG RESET Firewall RESET Option byte loading RESET Software RESET BOR RESET Low power management RESET

92

Clocks: HSE(High-Speed External)

• HSE 4-48MHz

• External source (Bypass mode) up to 40 MHz • External Crystal/Ceramic resonator (4-48MHz)

93

• Clock Security System (CSS)

Clocks

• Peripheral clocks Enable registers:

RCC_AHBxENR, RCC_APBxENRy:

• Peripheral clock disable by default (except Flash) • After enable bit is set: 2 clock cycles delay before clock to be active • Registers read and write access not supported when clock is disable. • Caution: SRAM1 and SRAM2 do not have enable bit

91

HSI vs. MSI (design spec)

MSI Normal mode Over temperature: ±6% Accuracy (max) Over voltage: From 100 to 800 kHz : ±1% From 1 to 8 MHz : ±2% From 16 to 48 MHz : ±4% 100 kHz : 0.5 µA 800 kHz : 2µA Consumption (typ) 1 MHz : 5µA 8 MHz : 20 µA 16 MHz : 60 µA 48 MHz : 160 µA Startup time (typ) 100 kHz : 10 µs 48 MHz : 2.5 µs 1.25 ms for 5% of final freq. 0.9 µs 130 µA Better than 0.25% TBD PLL-mode HSI

Clocks: MSI (Multi-Speed Internal)

• MSI = clock at startup from Reset, Standby or Shutdown modes. • Programmable frequency : 12 ranges selected with MSIRANGE in RCC_CR:

Reset and clock control (RCC)

RESET Sources

86

• System RESET

• Resets all registers except some RCC registers, PWR registers and Backup domain • Sources

02/07/2015 PLLP from 2 to 31 in derivatives

94

5,6,7,8

System clock

• Selected between HSI/HSE/MSI/PLL • Maximum frequency 80 MHz • APB1 and APB2 up to 80 MHz • Clock source max frequency depending on voltage scaling:

Clocks: MSI (Multi-Speed Internal)

• Can be selected as clock at wakeup from Stop 1 or 2 modes / CSS backup clock • Normal mode and PLL-mode (=auto-calibration with LSE) PLL-mode : allows USB FS device functionality (0.25% accuracy) • Factory and user trimmed

Crystal (max)

Consumption (typ) 200 nA 260 nA 410 nA 540 nA

50kOhm/6pF 80kOhm/6pF 50kOhm/12.5pF 80kOhm/12.5pF

• Available in all low-power modes + VBAT

Clocks: LSI (Low-Speed Internal)

95

Clocks: LSE (Low-Speed External)

• LSE: programmable amplifier driving capability (4 modes)

96

Mode Ultra low power Medium low driving Medium high driving High driving

Consumption (typ)

• Available in all low-power modes except Shutdown and VBAT